JP5039923B2 - Electroplated interconnect structures on integrated circuit chips. - Google Patents

Electroplated interconnect structures on integrated circuit chips. Download PDFInfo

- Publication number

- JP5039923B2 JP5039923B2 JP2008314245A JP2008314245A JP5039923B2 JP 5039923 B2 JP5039923 B2 JP 5039923B2 JP 2008314245 A JP2008314245 A JP 2008314245A JP 2008314245 A JP2008314245 A JP 2008314245A JP 5039923 B2 JP5039923 B2 JP 5039923B2

- Authority

- JP

- Japan

- Prior art keywords

- plating

- less

- weight

- bath

- copper

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Landscapes

- Electroplating Methods And Accessories (AREA)

- Electrodes Of Semiconductors (AREA)

- Internal Circuitry In Semiconductor Integrated Circuit Devices (AREA)

- Electroplating And Plating Baths Therefor (AREA)

Description

本発明は集積回路(IC)チップなどの電子デバイス上の相互接続配線に関し、より詳細には、光沢のある平滑な低応力の付着を得るのに通常用いられている添加剤を含む浴でCu電気めっきして製作されるボイドのないシームレスなサブミクロン構造に関する。 The present invention relates to interconnect wiring on electronic devices such as integrated circuit (IC) chips, and more particularly to Cu in a bath containing additives commonly used to obtain glossy, smooth, low stress adhesion. It relates to a seamless submicron structure without voids produced by electroplating.

AlCuおよび関連する合金は、集積回路チップなどの電子デバイス上に相互接続を形成するための好ましい合金である。AlCu中のCuの量は通常0.3〜4パーセントの範囲にある。 AlCu and related alloys are the preferred alloys for forming interconnects on electronic devices such as integrated circuit chips. The amount of Cu in AlCu is usually in the range of 0.3 to 4 percent.

チップ相互接続材料としてのAlCuをCuおよびCu合金で置き換えると性能が向上する。性能が向上するのは、Cuおよびある種のCu合金の比抵抗がAlCuの比抵抗より小さく、したがって、より細いラインを用いることができ、より高い配線密度が実現できることによる。 Replacing AlCu as the chip interconnect material with Cu and Cu alloys improves performance. The performance is improved because the specific resistance of Cu and certain Cu alloys is smaller than the specific resistance of AlCu, so that thinner lines can be used and higher wiring densities can be realized.

Cuメタライゼーションの利点は半導体工業全体に認識されてきた。Materials Research Society (MRS) Bulletinの、本件に関する学問的研究を特集したMRS Bulletin、第18巻、6号(1993年6月)および産業的研究を特集したMRS Bulletin、第19巻、8号(1994年8月)の両号全体に記述されるように、銅メタライゼーションは広範な研究の対象となってきた。1993年のルーサ(Luther)らの論文「Planar Copper-Polyimide Back End of the Line Interconnections for ULSI Devices」、PROC. IEEE VLSI MULTILEVEL INTERCONNECTIONS CONF., Santa Clara, CA, June 8-9, 1993, p.15は、4つのメタライゼーション・レベルを有するCuチップ相互接続の製造を記述している。 The advantages of Cu metallization have been recognized throughout the semiconductor industry. Materials Research Society (MRS) Bulletin's MRS Bulletin, Vol. 18, No. 6 (June 1993) featuring academic research on the subject, and MRS Bulletin, Vol. 19, No. 8 (1994) featuring industrial research (August), copper metallization has been the subject of extensive research. 1993 Luther et al., “Planar Copper-Polyimide Back End of the Line Interconnections for ULSI Devices”, PROC. IEEE VLSI MULTILEVEL INTERCONNECTIONS CONF., Santa Clara, CA, June 8-9, 1993, p.15. Describes the fabrication of Cu chip interconnects with four metallization levels.

化学気相付着(CVD)および無電解めっきなどの方法はCuを付着するための一般的な方法である。どちらの付着方法も通常せいぜい共形付着を作成するだけで、リソグラフィまたは反応性イオン・エッチング(RIE)の不備のために、特にトレンチの上部が底部より狭い断面を有するとき、欠陥(ボイドおよびシーム)ができるのを避けられない。CVDの他の問題はリー(Li)らの「Copper-Based Metallization in ULSI Structures -Part II: Is Cu Ahead of its Time as an On-chip Material」、MRS BULL., 第19巻、15号(1994)に記述されている。無電解めっきにおいては低コストであるという利益が提供される一方、金属付着中の水素発生が、産業全体の実装にとって欠陥と見られている膨れやその他の欠陥をもたらす。 Methods such as chemical vapor deposition (CVD) and electroless plating are common methods for depositing Cu. Both deposition methods usually only produce conformal deposition at best, and defects (voids and seams) due to deficiencies in lithography or reactive ion etching (RIE), especially when the top of the trench has a narrower cross section than the bottom. ) Is unavoidable. Another issue of CVD is Li et al., “Copper-Based Metallization in ULSI Structures -Part II: Is Cu Ahead of its Time as an On-chip Material”, MRS BULL., Vol. 19, No. 15 (1994). ). While the benefits of low cost are provided in electroless plating, hydrogen generation during metal deposition results in blisters and other defects that are seen as defects for packaging throughout the industry.

半導体ウエハ上に銅、銀、または金を付着するための電解法が、1993年10月26日にJ.ポリス(Poris)に発行された米国特許第5256274号(’274号特許)に記述されている。’274号特許の第1A図には中央に「良」の説明を付けたシームのある銅の導体が示され、第1B図には中央に「不良」の説明を付けたボイドのある銅導体が示されている。このめっき浴は水約90.0g/l(1ガロン当たり12オンス)のCuSO4・5H2O、10体積%の濃硫酸、塩酸からの塩素イオン50ppm、およびTechnic Inc., P.O. Box 965, Providence, RI 02901提供のTECHNI−COPPER W添加剤0.4体積%を含む。めっきは不活性マスクを通して選択的に付着された。 An electrolysis method for depositing copper, silver, or gold on a semiconductor wafer was disclosed on October 26, 1993, in J. Am. U.S. Pat. No. 5,256,274 (the '274 patent) issued to Polis. 1274 of the '274 patent shows a copper conductor with a seam with a description of “good” in the center, and FIG. 1B shows a copper conductor with a void with an explanation of “bad” in the center. It is shown. This plating bath contains approximately 90.0 g / l water (12 ounces per gallon) CuSO 4 .5H 2 O, 10% by volume concentrated sulfuric acid, 50 ppm chloride from hydrochloric acid, and Technic Inc., PO Box 965, Providence. TECHNI-COPPER W additive provided by RI 02901. The plating was selectively deposited through an inert mask.

サブミクロン寸法のボイドのないシームレス導体を有する集積回路中の配線用の、低コストで信頼性の高いCu相互接続構造を製作する方法を記述する。この方法は、ウエハ上に絶縁材料を付着すること、その中に導体を付着させて最終的にラインまたはバイアを形成するために絶縁材料中にサブ・ミクロン寸法のトレンチまたはホールをリソグラフィによって画定および形成すること、シード層またはめっきベースとして働く薄い導電層を付着すること、添加物を含む浴から電気めっきによって導体を付着すること、および個々のラインまたはバイアあるいはその両方の電気的分離を実施するために得られた構造を平坦化または化学機械研磨することを含む。 A method for fabricating a low-cost and reliable Cu interconnect structure for wiring in an integrated circuit having sub-micron sized void-free seamless conductors is described. This method involves lithographically defining and sub-micron sized trenches or holes in the insulating material to deposit an insulating material on the wafer and deposit a conductor therein to ultimately form a line or via. Forming, depositing a thin conductive layer that acts as a seed layer or plating base, depositing conductors by electroplating from a bath containing additives, and performing electrical isolation of individual lines and / or vias To planarize or chemically mechanically polish the resulting structure.

本発明はさらに、絶縁領域と導電領域を有する基板上にシード層を形成するステップ、シード層上にパターン化レジスト層を形成するステップ、添加剤を含む浴からパターン化レジストで覆われていないシード層上に導電材料を電気めっきするステップ、およびパターン化レジストを除去するステップを含む、電子デバイス上に相互接続構造を製作する方法を提供する。 The present invention further includes forming a seed layer on a substrate having an insulating region and a conductive region, forming a patterned resist layer on the seed layer, a seed not covered with the patterned resist from a bath containing an additive. A method of fabricating an interconnect structure on an electronic device is provided that includes electroplating a conductive material on the layer and removing the patterned resist.

本発明はさらに、基板上に絶縁材料を形成するステップ、その中に相互接続導体材料を付着させるためにラインまたはバイアあるいはその両方をリソグラフィによって画定および形成するステップ、めっきベースとして働く導電層を形成するステップ、めっきベース上にパターン化レジスト層を形成するステップ、添加剤を含む浴からの電気めっきによって導体材料を付着させるステップ、およびレジストを除去するステップを含む、電子デバイス上にボイドのないシームレスな導体を有する相互接続構造を製作する方法を提供する。 The invention further includes forming an insulating material on the substrate, lithographically defining and forming lines and / or vias for depositing interconnect conductor material therein, and forming a conductive layer that serves as a plating base. Seamlessly without voids on the electronic device, including forming a patterned resist layer on the plating base, depositing a conductive material by electroplating from a bath containing additives, and removing the resist A method of fabricating an interconnect structure having a flexible conductor is provided.

本発明はさらに、絶縁領域と導電領域を有する基板上にシード層を形成するステップ、添加剤を含む浴から導体材料のブランケット層を形成させるステップ、ブランケット層上にパターン化レジスト層を形成するステップ、パターン化レジストで覆われていない場所の導体材料を除去するステップ、およびパターン化レジストを除去するステップを含む、電子デバイス上に相互接続を形成する方法を提供する。本発明はさらに、添加剤を含む浴からの電気めっきによって形成される、C(2重量%未満)、O(1重量%未満)、N(1重量%未満)、S(1重量%未満)、およびCl(1重量%未満)からなる群から選択した少量の材料を含有するCuを含む、電子デバイス上の相互接続用の導体を提供する。 The present invention further includes forming a seed layer on a substrate having an insulating region and a conductive region, forming a blanket layer of a conductor material from a bath containing an additive, and forming a patterned resist layer on the blanket layer. A method of forming an interconnect on an electronic device is provided that includes removing conductive material where it is not covered with a patterned resist, and removing the patterned resist. The invention further comprises C (less than 2% by weight), O (less than 1% by weight), N (less than 1% by weight), S (less than 1% by weight) formed by electroplating from a bath containing additives. And a conductor for interconnection on an electronic device comprising Cu containing a small amount of material selected from the group consisting of Cl (less than 1% by weight).

相互接続材料は、光沢のある平滑な低応力の付着物を生成するのに通常用いられる添加物を含む浴から電気めっきされるCuでよい。このような浴からのCu電気めっきの速度は他の場所よりキャビティ内の深部の方が大きい。したがって、このめっき法は独特な超充填特性を有し、他のいかなる方法でも得られないボイドのないシームレスな付着物を生じる。この方法で電気めっきされたCuでできた相互接続構造はエレクトロマイグレーション(electromigration)に対する抵抗が大きく、エレクトロマイグレーションの活性化エネルギーが1.0eVと等しいかこれより大きい。この導体は本質的にCuからなり、C(2重量%未満)、O(1重量%未満)、N(1重量%未満)、S(1重量%未満)、およびCl(1重量%未満)の少量の原子または分子断片あるいはその両方を含む。 The interconnect material may be Cu electroplated from a bath containing additives commonly used to produce a glossy, smooth, low stress deposit. The rate of Cu electroplating from such a bath is greater in the deep part of the cavity than elsewhere. Thus, this plating method has unique superfill properties and produces a void-free seamless deposit that cannot be obtained by any other method. An interconnect structure made of Cu electroplated in this way has a high resistance to electromigration and an electromigration activation energy equal to or greater than 1.0 eV. This conductor consists essentially of Cu, C (less than 2% by weight), O (less than 1% by weight), N (less than 1% by weight), S (less than 1% by weight), and Cl (less than 1% by weight) Of small amounts of atoms and / or molecular fragments.

エレクトロマイグレーション抵抗の大きいCuは、光沢および延性のある低応力のめっき付着物を生成するのに通常用いられる添加物を含むめっき溶液から電気めっきされる。 Cu with high electromigration resistance is electroplated from a plating solution containing additives commonly used to produce bright and ductile low stress plating deposits.

本発明の一目的は、相互接続配線などのCuの導体を、その導体の中心にシームまたはボイドを残すことなく電気めっきすることである。 One object of the present invention is to electroplat Cu conductors such as interconnect wiring without leaving a seam or void in the center of the conductor.

本発明の他の目的は、導体が1ミクロン以下および10ミクロン以上などと異なる幅を有し、実質的に均一な充填厚みを有するCuの導体を電気めっきすることである。導体の深さと幅の対比は1と等しいかまたはこれより大きい。バイアの深さと幅の対比は1を超えてもよい。 Another object of the present invention is to electroplate Cu conductors with conductors having different widths, such as less than 1 micron and greater than 10 microns, and having a substantially uniform fill thickness. The contrast between the depth and width of the conductor is equal to or greater than 1. The via depth / width contrast may exceed one.

本発明の他の目的は、1)電解めっきによるCuのブランケット付着、2)二重ダマシーン製造(2レベルのメタライゼーションを1回のブランケット付着ステップで製作する方法)、および3)化学機械研磨などの方法により上部表面を平坦化できる能力の相乗効果により集積回路の製作コストを下げることである。 Other objectives of the present invention include 1) Cu blanket deposition by electroplating, 2) double damascene fabrication (a method of fabricating two levels of metallization in one blanket deposition step), and 3) chemical mechanical polishing, etc. This is to reduce the manufacturing cost of the integrated circuit by the synergistic effect of the ability to planarize the upper surface by this method.

本発明の上記その他の特徴、目的、および利点は、以下の本発明の詳細な説明を図面と併せて読めば明らかになるであろう。ダマシーンめっき法は、ウエハ表面全体の上にめっきを行い、続いてフィーチャを分離し画定する平坦化プロセスを行うものである。めっきの前に、リソグラフィで画定された配線パターン全体にめっきベースを付着させる。接着を改善し導体と絶縁体の相互作用および拡散を防止する層をめっきベースと絶縁体の間に付着させる。本発明の概略図を第1図ないし第5図に示す。まずエッチング/平坦化層(窒化ケイ素)2および7で被覆した絶縁体層(酸化ケイ素、ポリマー)1をウエハ8上に付着させ、被覆した絶縁体上にレジスト・パターン3を形成して絶縁体にそれを転写し、続いてバリア材料4およびシード層(Cu)5を付着し、全てのフィーチャが充填されるようにCu6を電気めっきし、平坦化によってこの構造を第5図に示すような最終的形状にする。第6図に示すようにリソグラフィで多段のパターンを絶縁体上に画定することが可能であり、続いてこのコスト節約の製造法では同じ一連の層付着が行われる。

These and other features, objects and advantages of the present invention will become apparent from the following detailed description of the invention when read in conjunction with the drawings. Damascene plating involves plating over the entire wafer surface followed by a planarization process that separates and defines features. Prior to plating, a plating base is deposited over the entire lithographically defined wiring pattern. A layer is applied between the plating base and the insulator to improve adhesion and prevent conductor-insulator interaction and diffusion. Schematic diagrams of the present invention are shown in FIGS. First, an insulator layer (silicon oxide, polymer) 1 covered with an etching / planarizing layer (silicon nitride) 2 and 7 is deposited on the

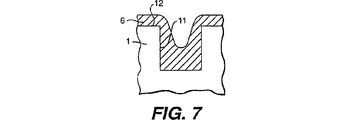

Cu6中のボイドまたはシームの形成を避けるために、電気めっき速度は、フィーチャの低いまたは深い所で他の場所より大きくなければならない。このことは金属付着の3つの可能なケースを示す第7図ないし第12図に示されている。第7図および第8図に示す第1のケースでは、めっき浴に添加剤を用いることによりフィーチャ11内の金属付着はフィーチャ11外部の点12より速くなり、第8図に示すようにボイドのないシームレスな付着物(超充填(super filling))が得られる。フィーチャ内部での優先的付着は、その場所における添加剤の移動速度が低く、そのためにCu付着の局部的速度が増加するからであろう。特に、内部の隅では添加剤の移動速度が最低で、したがって銅付着速度が最高になる。第9図および第10図に示す第2のケースでは、フィーチャ14の低い点16内での付着が付着するイオンの欠乏(depletion)度が高い浴から行われるため、フィーチャ14内部の金属付着がフィーチャ14外部の点15より遅く、ボイドおよび高い比抵抗のラインまたはバイアが生じる。より高いイオン欠乏度がめっき浴中での付着反応の局部的に高い過電圧を生じる。第11図および第12図に示す第3のケースでは、液状めっき浴内に局部的イオン欠乏がなく、かつ添加物およびその有利な効果(内部フィーチャにおける優先的付着)がないため、全ての場所で、フィーチャ17内部およびフィーチャ17外部の点18で付着速度が等しい(共形充填)。共形付着によりほぼ満足な付着が得られるが、高アスペクト比のラインおよびバイアではCu金属6中のシーム19が避けられない。凹型プロフィルでは共形充填が不可能でボイドが生じる。第7図および第8図に示す超充填を伴うめっきは、ダマシーン法にとって必要かつ好ましい方法であることは明らかである。適切に配合された溶液からの電解めっきは第7図および第8図に示すタイプの付着を達成するのに最良の方法の1つである。超充填およびそのCuメタライゼーションに対する関連は全く未知であり、たとえば、上に引用したリー(Li)らの論文では電解Cuめっきのバイア充填能力は「かなり劣る」と述べている。

In order to avoid the formation of voids or seams in Cu6, the electroplating rate must be greater at the lower or deeper features than elsewhere. This is illustrated in FIGS. 7-12 showing three possible cases of metal deposition. In the first case shown in FIGS. 7 and 8, by using an additive in the plating bath, the metal deposition within the

めっき浴中に添加剤を用いて超充填を行うと、リソグラフィ・プロセスで誘電層中1に第13図に示すように上部の方が底部より狭いフィーチャまたはキャビティ22が生じても、ボイドのないシームレスなラインおよびバイアを作成することが可能である。本発明による電気めっきはボイドのないシームレスなラインおよびバイアを得ることができる最良の方法の1つである。せいぜい共形形状を生じるに過ぎないCVDなどの他の付着方法は、この種のリソグラフィ上の欠陥、特に底部より上部で狭く、側壁23が上面26に対して垂直な基準線24と矢印27で示すように0〜20゜の角度を形成する、誘電体1中のフィーチャまたはキャビティ22が存在するとき、著しい欠陥を招くことは避けられない。

When superfilled with additives in the plating bath, even if the lithography process produces features or cavities 22 in the

粗い表面上に平坦な付着物を作成するのに通常用いられる添加剤を含む溶液からの銅めっきがサブミクロンのキャビティを充填するのに必要な超充填を達成するのに使用できる。好適な添加剤系の1つは、コネチカット州ニュー・ヘイブンのEnthone-OMI, Inc.から市販のもので、SelRex Cubath M Systemとして知られている。上記添加剤を製造業者はMHyと呼んでいる。別の好適な添加剤系はニューヨーク州フリーポートのLeaRonal, Inc.から市販のもので、Copper Gleam 2001系として知られる。この添加剤を製造業者はCopper Gleam 2001 Carrier、Copper Gleam 2001-HTL、およびCopper Gleam 2001 Levellerと呼んでいる。また別の好適な添加剤系はペンシルバニア州ステートパークのAtotech USA, Inc.から市販のもので、Cupracid HS systemとして知られる。この系の添加剤を製造業者はCupracid Brightener、およびCupracid HS Basic Levellerと呼んでいる。 Copper plating from solutions containing additives commonly used to create flat deposits on rough surfaces can be used to achieve the superfill required to fill submicron cavities. One suitable additive system is commercially available from Enthone-OMI, Inc. of New Haven, Connecticut and is known as the SelRex Cubath M System. The manufacturer calls the additive MHy. Another suitable additive system is commercially available from LeaRonal, Inc. of Freeport, NY and is known as the Copper Gleam 2001 system. Manufacturers call this additive Copper Gleam 2001 Carrier, Copper Gleam 2001-HTL, and Copper Gleam 2001 Leveller. Another suitable additive system is commercially available from Atotech USA, Inc. of State Park, Pennsylvania and is known as the Cupracid HS system. Manufacturers of this system call it Cupracid Brightener and Cupracid HS Basic Leveller.

本発明の浴に添加することができる具体的な添加剤の例はいくつかの特許に記載されている。故H−Gクロイツ(Creutz)らの1978年8月29日発行の「Electrodeposition of Copper」という名称の米国特許第4110176号は、水性酸性銅めっき浴から反応生成物として光沢があり延性が高く、低応力で平坦性のよい銅付着物を与える、ポリアルカノール第四級アンモニウム塩などのめっき浴添加剤の使用を記述しており、参照によりこの詳細を本明細書に合体する。 Examples of specific additives that can be added to the baths of the present invention are described in several patents. U.S. Pat. No. 4,101,176, entitled “Electrodeposition of Copper” issued on August 29, 1978 to the late HG Creutz et al., Is a glossy and highly ductile reaction product from an aqueous acidic copper plating bath, It describes the use of plating bath additives, such as polyalkanol quaternary ammonium salts, that provide copper deposits with low stress and good flatness, the details of which are incorporated herein by reference.

A.ワトソン(Watson)らの1983年3月15日発行の「Acid Copper Electroplating Baths Containing Brightening and Leveling Additives」という名称の米国特許第4376685号は、水性酸性銅めっき浴から反応生成物として光沢があり平坦な銅電解付着物を与えるアルキル化ポリアルキレンイミンなどのめっき浴添加剤の使用を記述しており、参照によりこの特許を本明細書に合体する。 A. Watson et al., US Pat. No. 4,376,685, entitled “Acid Copper Electroplating Baths Containing Brightening and Leveling Additives”, issued March 15, 1983, is a glossy and flat product from an aqueous acidic copper plating bath. Describes the use of plating bath additives such as alkylated polyalkyleneimines that provide copper electrolytic deposits, which is incorporated herein by reference.

W.ダームス(Dahms)らの1990年12月4日発行の「Aqueous Acidic Bath for Electrochemical Deposition of a Shiny and Tear-free Copper Coating and Method of Using Same」という名称の米国特許第4975159号は、付着銅の光沢および延性を最適化する量の少なくとも1つの置換アルコキシル化ラクタムをアミド基含有化合物として含む有機添加剤の組合せを水性酸性浴に添加することを記述しており、参照によりこの特許を本明細書に合体する。米国特許第4975159号の表Iに本発明の浴に添加することができるいくつかのアルコキシル化ラクタムをリストしてある。表IIは本発明の浴に添加することができる3−メルカプトプロパン−1−スルホン酸などの水溶性基を有するいくつかの含イオウ化合物をリストしてある。表IIIには本発明の浴に界面活性剤として添加することができるポリエチレングリコールなどのいくつかの有機化合物をリストしてある。 W. US Pat. No. 4,975,159 entitled “Aqueous Acidic Bath for Electrochemical Deposition of a Shiny and Tear-free Copper Coating and Method of Using Same”, issued December 4, 1990, by Dahms et al. And adding a combination of organic additives comprising an amount of at least one substituted alkoxylated lactam as an amide group-containing compound to optimize ductility to an aqueous acidic bath, and this patent is incorporated herein by reference. Merge. Table I of US Pat. No. 4,975,159 lists some alkoxylated lactams that can be added to the baths of the present invention. Table II lists some sulfur-containing compounds having water-soluble groups such as 3-mercaptopropane-1-sulfonic acid that can be added to the baths of the present invention. Table III lists some organic compounds, such as polyethylene glycol, that can be added as surfactants to the baths of the present invention.

H−Gクロイツらの1973年11月6日発行の「Electrodeposition of Copper from Acid Baths」という名称の米国特許第3770598号は、ポリエチレンイミンとアルキル化剤から第四級窒素を生成する光沢を与える量の反応生成物、少なくとも1個のスルホン基を有する有機イオウ化合物、およびポリプロピレングリコールなどのポリエーテルを溶解して含む、延性および光沢のある銅を得るための浴を記述しており、参照によりこの特許を本明細書に合体する。 US Pat. No. 3,770,598, entitled “Electrodeposition of Copper from Acid Baths”, issued November 6, 1973, by HG Kreuz et al., Provides a glossy amount to produce quaternary nitrogen from polyethyleneimine and an alkylating agent. A bath for obtaining ductile and shiny copper, comprising dissolved product of the reaction, an organic sulfur compound having at least one sulfone group, and a polyether such as polypropylene glycol. The patent is incorporated herein.

H−Gクロイツらの1967年6月27日発行の「Electrodeposition of Copper from Acid Baths」という名称の米国特許第3328273号は、R1およびR2が同じまたは異なる炭素数1〜6のポリメチレン基またはアルキン基、Xが水素またはスルホン基、nが2〜5の整数である式XR1−(Sn)−R2−SO3Hの有機イオウ化合物を含む、平坦性に優れた光沢のある低応力の付着物を得るための硫酸銅およびフルオロホウ酸塩の浴を記述しており、参照によりこの特許を本明細書に合体する。さらに、これらの浴はポリエーテル化合物、隣接イオウ原子を有する有機スルフィド、およびフェナジン染料を含むことができる。米国特許第3328273号の表Iに本発明の浴に添加することができるいくつかのポリスルフィド化合物がリストしてある。表IIには本発明の浴に添加することができるいくつかのポリエーテルをリストしてある。 U.S. Pat. No. 3,328,273 entitled “Electrodeposition of Copper from Acid Baths” issued June 27, 1967 to HG Kreutz et al. Including an organic sulfur compound of the formula XR 1 — (S n ) —R 2 —SO 3 H wherein X is a hydrogen or sulfone group and n is an integer of 2 to 5, Describes a copper sulfate and fluoroborate bath to obtain deposits, which is incorporated herein by reference. In addition, these baths can include polyether compounds, organic sulfides with adjacent sulfur atoms, and phenazine dyes. Table I of US Pat. No. 3,328,273 lists several polysulfide compounds that can be added to the baths of the present invention. Table II lists some polyethers that can be added to the baths of the present invention.

添加剤は種々の目的を達成するために浴に加えられる。浴は銅塩および鉱酸を含むことができる。膜厚またはランダムに配向した粒子に比して大きい粒子サイズを含む特定の膜微細構造が導体内で生じるように添加剤を含有させることができる。また、C、O、N、SおよびClからなる群から選択された原子を含む分子断片を導体材料中に取り込んで、純銅よりエレクトロマイグレーション抵抗を大きくするように添加剤を浴に添加することもできる。さらに、膜厚またはランダムに配向した粒子に比して大きい粒子サイズを含む特定の膜微細構造が導体内で生じて、エレクトロマイグレーション挙動が非電気めっき銅より改善されるように添加剤を浴に添加することもできる。 Additives are added to the bath to achieve various purposes. The bath can contain a copper salt and a mineral acid. Additives can be included so that a specific film microstructure, including a film size or particle size that is large compared to randomly oriented particles, occurs in the conductor. Also, an additive may be added to the bath so that a molecular fragment containing an atom selected from the group consisting of C, O, N, S, and Cl is taken into the conductor material and the electromigration resistance is higher than that of pure copper. it can. In addition, additives can be added to the bath so that certain film microstructures are formed in the conductor, including film thickness or particle size that is large compared to randomly oriented particles, and electromigration behavior is improved over non-electroplated copper. It can also be added.

第14図は0.3Mの硫酸第二銅および10体積%の硫酸を含む従来法のめっき溶液のキャビティ充填挙動の断面図を示す。キャビティが完全に充填される前にめっきを中断してフィーチャの様々な場所における付着厚みを測定し、それによって充填のタイプを決定した。Cu30の共形付着物が得られたことが分かった。しかし、同じ溶液に塩素イオンとMHy添加物を加えて得られた付着物は第15図に示すように超充填を示した。フィーチャ内の深部での付着速度は他の場所より大きく、最終的に第15図に示すCu36の付着物はフィーチャ外部よりフィーチャ内部のめっき速度が大きいためボイドがなくシームレスになる。超充填を生じるMHy濃度は約0.1〜約2.5体積%の範囲にある。塩素イオン濃度は10〜300ppmの範囲にある。

FIG. 14 shows a cross-sectional view of the cavity filling behavior of a conventional plating solution containing 0.3M cupric sulfate and 10% by volume sulfuric acid. The plating was interrupted before the cavities were completely filled and the deposit thickness at various locations of the feature was measured, thereby determining the type of filling. It was found that a conformal deposit of Cu30 was obtained. However, the deposits obtained by adding chloride ions and MHy additive to the same solution showed super-filling as shown in FIG. The deposition speed in the deep part in the feature is larger than that in other places. Finally, the deposit of

硫酸銅を0.1〜0.4Mの範囲、硫酸を10〜20体積%の範囲、塩素を10〜300ppmの範囲、LeaRonal添加剤Copper Gleam 2001 Carrierを0.1〜1体積%の範囲、Copper Gleam 2001 HTLを0.1〜1体積%の範囲、Copper Gleam 2001 Levellerを0.1〜1体積%の範囲で含む溶液から同様な超充填結果が得られる。最後に上記の範囲の硫酸銅、硫酸、塩素イオン、およびAtotech添加剤Cupracid Brightenerを0.5〜3体積%の範囲、Cupracid HS Basic Levellerを0.01〜0.5体積%の範囲で含む溶液からも同様の超充填結果が得られる。 Copper sulfate in the range of 0.1 to 0.4 M, sulfuric acid in the range of 10 to 20% by volume, chlorine in the range of 10 to 300 ppm, LeaRonal additive Copper Gleam 2001 Carrier in the range of 0.1 to 1% by volume, Copper Similar superfill results are obtained from solutions containing Gleam 2001 HTL in the range of 0.1 to 1% by volume and Copper Gleam 2001 Leveller in the range of 0.1 to 1% by volume. Finally, a solution containing copper sulfate, sulfuric acid, chloride ions and the Atotech additive Cupracid Brightener in the above ranges in the range of 0.5 to 3% by volume and Cupracid HS Basic Leveller in the range of 0.01 to 0.5% by volume. The same super-filling result can be obtained from.

これまでに述べた添加剤を用いるめっき法は、1994年5月17日発行のP.アンドリカコス(Andricacos)らの米国特許第5516412号、第5312532号および米国特許第3652442号に記載されているパドルめっきセルなど従来のめっきセル中で実施すると、サブミクロンの高アスペクト比のフィーチャまたはキャビティの超充填を生じる。しかし、基板表面を電解質の自由表面のみと接触して支持するめっきセル、たとえば、参照により本明細書に合体する1982年7月13日発行のS.アイゴ(Aigo)の米国特許第4339319号に記載されているカップめっきセル中でこの方法を実施すると、下記の利益がさらに得られる。その利益とは、狭い(サブミクロンの)フィーチャまたはキャビティの間に存在する可能性のある1〜100ミクロンの範囲の広いキャビティの超充填である。 The plating method using the additives described so far is disclosed in P.I. When implemented in a conventional plating cell, such as the paddle plating cell described in Andricacos et al., US Pat. Nos. 5,516,412 and 5,312,532 and US Pat. No. 3,652,442, a submicron high aspect ratio feature or cavity Causes superfilling. However, a plating cell that supports the substrate surface in contact with only the free surface of the electrolyte, such as S.D. issued July 13, 1982, which is incorporated herein by reference. Implementation of this method in the cup plating cell described in Aigo U.S. Pat. No. 4,339,319 further provides the following benefits. The benefit is superfilling of wide cavities in the 1-100 micron range that may exist between narrow (submicron) features or cavities.

基板が電解質中に浸されるめっきセル中では、1〜100ミクロンの範囲の広いフィーチャは、0.1ミクロン以上などの1ミクロン未満の幅を有する狭いフィーチャより充填が遅く、したがって、広いフィーチャは上部めっき表面に窪みや凹部のない平坦化構造を生成するにはより長いめっき時間および研磨時間を要する。 In plating cells in which the substrate is immersed in the electrolyte, wide features in the range of 1-100 microns are slower to fill than narrow features having a width of less than 1 micron, such as 0.1 microns or more, and thus wide features are A longer plating time and polishing time are required to produce a planarized structure having no depressions or recesses on the upper plating surface.

それとは対照的に、カップめっきセル中では、めっき中にめっきされる基板表面が電解質のメニスカスと接触して保持されるとき、1ミクロン以下や10ミクロン以上など幅が大きく異なるキャビティが迅速にかつ同じ速度で均一に充たされる。 In contrast, in cup plating cells, when the substrate surface to be plated during plating is held in contact with the meniscus of the electrolyte, cavities of significantly different widths such as 1 micron or less and 10 microns or more are rapidly and Filled uniformly at the same speed.

電解質のメニスカスは液柱の湾曲した上面である。この湾曲した上面は毛管によるように、または上昇流液などの液流により凸状になる。 The meniscus of the electrolyte is the curved upper surface of the liquid column. This curved upper surface becomes convex as by a capillary or by a liquid flow such as a rising liquid.

第16図は、ダマシーン配線用に形成された表面フィーチャまたはキャビティ62または63が内在する二酸化ケイ素などの誘電体61の上層を有する基板60の断面図である。キャビティ62は1ミクロン未満の幅を有し、キャビティ63は1〜100ミクロンの範囲の幅を有する。ライナ64が誘電体61との接着、および後でめっきする金属の拡散バリアを提供する。ライナ64は電気めっきのめっきベースの働きをするように導電性とすることができ、また別のめっきベース層を加えることもできる。

FIG. 16 is a cross-sectional view of a

第17図は、浸漬型のセルでめっきされた、キャビティ62を充填し、広いキャビティ63を充填するのに充分な金属の電解付着物66を有する基板60の断面図である。第17図において、広いフィーチャ63は狭いまたはサブミクロンのフィーチャ62より充填されるのが遅い。上面67は金属66の平均高さに対してフィーチャ63の上に窪み68を有する。

FIG. 17 is a cross-sectional view of a

第17図および第18図では第16図および第17図の装置に対応する機能に対して同じ記号を用いる。 In FIG. 17 and FIG. 18, the same symbols are used for functions corresponding to the apparatus of FIG. 16 and FIG.

第18図は、メニスカス型カップめっきセルでめっきされた、キャビティ62を充填し、広いキャビティ63を充填するのに充分なCuでよい金属66の電解付着物を有する基板60の断面図である。第18図に示すように、基板は浴の表面に接触して置くことができる。浴は浴表面で流動させることができる。

FIG. 18 is a cross-sectional view of a

第18図において、広いフィーチャ63は狭いフィーチャ62と同じ速度で充填される。上面69は金属66の平均高さに対して非常に小さい窪みをフィーチャ63の上に有する。したがって、カップめっきセル中でめっきを行い、狭いフィーチャおよび広いフィーチャの均等な超充填を達成する、本発明の態様が記述される。メニスカスめっきの優れた性能は、気液界面における界面活性添加剤分子の濃度がより高く、かつおそらく配向が異なることによると考えられる。これらの分子は、基板が導入されるとき再分配を開始する可能性があるが、数分間のめっき時間中はおそらく残留効果が持続する。

In FIG. 18, wide features 63 are filled at the same rate as narrow features 62. The

第17図および第18図に示す電気めっきCu金属66は本質的にCuからなるが、O(1重量%未満)、N(1重量%未満)、S(1重量%未満)、またはCl(1重量%未満)を含むC(2重量%未満)の少量の原子または分子断片あるいはその両方をも含むことができる。これらの付加成分は添加剤の分解によって生成し、次いで原子ではなく分子断片の形で付着66中に導入されるものと思われる。塩素は添加剤の作用を活性化する相乗作用により共吸着される。その結果これらの含有物は粒界にあり、そのためにめっきされた金属の比抵抗に影響を与えないと考えられる。実際、めっきされたCuの比抵抗測定の結果は2μΩcm未満である。また、Cuの粒界にあることから、同じ分子が他の方法で付着された純銅よりはるかに良好なエレクトロマイグレーション抵抗を電気めっき銅に与えると考えられる。

The electroplated

電気めっきされたCuの粒子サイズは一般に他のCu付着技法で生成したものより大きい(第19a図ないし第19d図および第20a図ないし第20d図参照)。第19a図ないし第19d図はそれぞれ厚み1ミクロンのCu膜の同じ領域の粒子配向マップ、粒子コントラスト・マップ、逆極点図、および(111)極点図である。粒子サイズは約1.4ミクロンで結晶組織はランダムである。第20a図ないし第20d図はそれぞれ厚み1ミクロンのPVDによるCu膜の同じ領域の粒子配向マップ、粒子コントラスト・マップ、逆極点図、および(111)極点図である。粒子サイズは約0.4ミクロンであり、この膜は強い(111)/(100)結晶組織を有する。 The particle size of the electroplated Cu is generally larger than that produced by other Cu deposition techniques (see FIGS. 19a-19d and 20a-20d). FIGS. 19a to 19d are a particle orientation map, a particle contrast map, an inverse pole figure, and a (111) pole figure of the same region of a 1 micron thick Cu film, respectively. The particle size is about 1.4 microns and the crystal structure is random. 20a to 20d are a particle orientation map, a particle contrast map, a reverse pole figure, and a (111) pole figure of the same region of a Cu film formed by PVD having a thickness of 1 micron. The particle size is about 0.4 microns and the membrane has a strong (111) / (100) crystal structure.

めっきされたCuの結晶配向(組織としても知られる)は非めっきCu膜よりかなりランダムである(第19a図ないし第19d図および第20a図ないし第20d図参照)。このランダムな配向は逆極点図または(111)極点図(第19a図ないし第19d図参照)中の粒子の均一な分布によって示される。これは非めっきCu膜で見られるのとは実質的に異なる。たとえば、このPVDのCu膜中に実質的な(100)および(111)組織がある第20a図ないし第20d図を参照されたい。 The crystallographic orientation (also known as texture) of the plated Cu is much more random than the unplated Cu film (see FIGS. 19a-19d and 20a-20d). This random orientation is indicated by the uniform distribution of particles in the reverse pole figure or (111) pole figure (see FIGS. 19a to 19d). This is substantially different from that seen with unplated Cu films. For example, see FIGS. 20a-20d, where there is substantial (100) and (111) texture in this PVD Cu film.

電気めっきCuおよび純Cuのエレクトロマイグレーション抵抗は、MRS Bulletin第18巻6号(1993年6月)、および第19巻8号(1994年8月)で参照され、参照によって本明細書に合体される方法によって測定される活性化エネルギーの関数である。電気めっきCuの活性化エネルギーは1.0eVと等しいか大きい。さらに、第21a図および第21b図はPVD膜に対するめっき膜のドリフト速度の比較を示す。明らかに、めっきCuは抵抗の経時変化をほとんど示さないが、PVDのCu膜の抵抗は劇的に増大する。抵抗の変化は、Cuライン中のエレクトロマイグレーションによる損傷の量に関係する。明らかに、めっきCuはPVDのCuより遙かに改善されたエレクトロマイグレーション挙動を有する。めっきCuの活性化エネルギーは1.1〜1.3eVであるが、PVDのCuの活性化エネルギーはかなり低い(0.7〜0.8eV)。 The electromigration resistance of electroplated Cu and pure Cu is referenced in MRS Bulletin Vol. 18 No. 6 (June 1993) and Vol. 19 No. 8 (August 1994), incorporated herein by reference. Is a function of the activation energy measured by the method. The activation energy of electroplated Cu is equal to or greater than 1.0 eV. Further, FIGS. 21a and 21b show a comparison of the plating film drift rate with respect to the PVD film. Apparently, the plated Cu shows little resistance over time, but the resistance of the PVD Cu film increases dramatically. The change in resistance is related to the amount of electromigration damage in the Cu line. Clearly, the plated Cu has a much improved electromigration behavior than PVD Cu. The activation energy of plated Cu is 1.1 to 1.3 eV, but the activation energy of PVD Cu is quite low (0.7 to 0.8 eV).

本発明の価値はダマシーン構造の実施にとどまらない。C、O、N、S、およびClを含む原子または分子断片あるいはその両方の存在に伴うエレクトロマイグレーションに対する抵抗の増大は、第22図ないし第26図に示すように平面ベース上にマスクを通してめっきすることにより、第22図および第27図ないし第31図に示すように穴のあるベース上にマスクを通してめっきすることにより、または第22図、第23図および第32図ないし第35図に示すようにブランケットめっきに続いてパターン化エッチングを行うことによって製作した導体素子でも同様に有利である。 The value of the present invention goes beyond the implementation of a damascene structure. Increased resistance to electromigration due to the presence of atoms and / or molecular fragments containing C, O, N, S, and Cl or both is plated through a mask on a planar base as shown in FIGS. By plating through a mask onto a base with holes as shown in FIGS. 22 and 27 to 31 or as shown in FIGS. 22, 23 and 32 to 35 Also advantageous is a conductor element fabricated by performing blanket plating followed by patterned etching.

平面ベース上にマスクを通してめっきする方法を第22図ないし第26図に示す。第22図は絶縁層1を示す。第23図は絶縁層1の上に形成されたシード層(Cu)5を示す。バリア材料4(図示せず)を絶縁層1とシード層5の間に置いてもよい。第24図はシード層5の上にパターン化されたレジスト71を示す。第25図はレジスト71を通して電気めっきした後のCu6を示す。第26図はレジスト71が除去され、Cu6で保護されていない場所のシード層5が除去された第25図の構造を示す。第26図はパターン化されたシード層5の上のパターン化されたCu層6を示す。

A method of plating through a mask on a flat base is shown in FIGS. FIG. 22 shows the insulating

穴のあるベース上にマスクを通してめっきする方法を第22図および第27図ないし第31図に示す。第22図は絶縁層1を示す。第27図は絶縁層1中に形成されたチャネル72を示す。第28図は絶縁層1の上に形成されたシード層(Cu)5を示す。バリア材料4(図示せず)をシード層(Cu)5の下に形成することもできる。第29図はシード層5の上にパターン化されたレジスト71を示す。第30図はマスクまたはレジスト71を通してめっきすることにより付着されたチャネル72内およびシード層5の上のCu6を示す。第31図はレジスト71が除去され、Cu6で保護されていない場所のシード層5が除去されたCu6を示す。本発明のめっき法の超充填属性により、ボイドまたはシームを残さずに、穴のあるベース中のキャビティまたはフィーチャを充填することが可能になることに留意されたい。

A method of plating through a mask on a base having holes is shown in FIGS. 22 and 27 to 31. FIG. FIG. 22 shows the insulating

ブランケットめっきに続いてパターン・エッチングするプロセスを絶縁層上へのパターン化ラインの形成について第22図、第23図および第32図ないし第35図に示す。第22図は絶縁層1を示す。第23図は絶縁層1の上に形成されたバリア層4を示す。シード層(Cu)5がバリア層4の上面上に形成される。Cuのブランケット層76は第32図に示すようにシード層5の上に電気めっきすることにより形成される。レジスト層71はブランケット層76の上に形成され、第33図に示すようにリソグラフィによりパターン化される。第34図は、レジスト71によって保護されていない場所をエッチングまたは他の方法による除去でパターン化されたブランケット層76を示す。第35図はレジスト71が除去されたパターン化されたブランケット層76を示す。

The process of pattern etching following blanket plating is shown in FIGS. 22, 23 and 32 to 35 for the formation of patterned lines on the insulating layer. FIG. 22 shows the insulating

第2図ないし第15図および第22図ないし第35図では、以前の図または第1図の装置の対応する機能と同様の名称を用いる。 2 to 15 and 22 to 35 use names similar to the corresponding functions of the apparatus of the previous figure or FIG.

電子デバイス上に相互接続構造を作る方法、並びにC、O、N、S、およびClの原子または分子断片あるいはその両方によるエレクトロマイグレーション抵抗を有し、膜厚に比較して大きい粒子サイズおよびランダムな結晶配向などの特定の微細構造フィーチャを有するCu導体を記述し図示したが、本明細書に添付の請求の範囲によってのみ制限される本発明の広い範囲から逸脱することなく修正および変更が可能であることは当業者には明らかであろう。 A method for making an interconnect structure on an electronic device, and electromigration resistance due to C, O, N, S, and Cl atoms and / or molecular fragments, large particle size and random compared to film thickness While Cu conductors having specific microstructure features such as crystal orientation have been described and illustrated, modifications and changes can be made without departing from the broad scope of the invention which is limited only by the claims appended hereto. It will be apparent to those skilled in the art.

Claims (10)

基板上に絶縁材料を形成するステップ、

前記絶縁材料中に、相互接続導体材料を付着するサブミクロン・ラインまたはサブミクロン・バイアあるいはその両方用のリセスをリソグラフィによって画定し形成するステップ、

前記絶縁材料上にめっきベースの働きをする導電層を形成するステップ、

ダマシーン・プロセスを使用して添加剤を含む浴からの電気めっきによって、継目なくボイド・フリーとなるように前記導体材料としてのCuを付着するステップであって、前記浴に添加される添加剤は、前記リセスの側壁に沿った深さ方向でのめっき速度を増加させることにより、銅を含む前記導体中の継目またはボイドの形成を防止し、膜厚に比して大きい粒子サイズを含む特定の膜微細構造を前記導体内で生じさせることにより、エレクトロマイグレーション挙動を非電気めっきCuより改善するステップ、および

得られた構造を平坦化して個々のラインまたはバイアあるいはその両方の電気的分離を実施するステップ、

を含む方法。 A method of manufacturing an interconnect structure having seamless conductors without voids on an electronic device, comprising:

Forming an insulating material on the substrate;

Lithographically defining and forming recesses in the insulating material for submicron lines and / or submicron vias to which the interconnect conductor material is deposited;

Forming a conductive layer serving as a plating base on the insulating material;

The step of depositing Cu as the conductor material by electroplating from a bath containing the additive using a damascene process so that it is seamlessly void free, the additive added to the bath being By increasing the plating rate in the depth direction along the side wall of the recess, it prevents the formation of seams or voids in the conductor containing copper, and includes a specific particle size that is larger than the film thickness. Producing a film microstructure within the conductor to improve electromigration behavior over non-electroplated Cu , and planarize the resulting structure to perform electrical isolation of individual lines and / or vias Step,

Including methods.

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008314245A JP5039923B2 (en) | 2008-12-10 | 2008-12-10 | Electroplated interconnect structures on integrated circuit chips. |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2008314245A JP5039923B2 (en) | 2008-12-10 | 2008-12-10 | Electroplated interconnect structures on integrated circuit chips. |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2004362864A Division JP4551206B2 (en) | 2004-12-15 | 2004-12-15 | Electroplated interconnect structures on integrated circuit chips. |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2009065207A JP2009065207A (en) | 2009-03-26 |

| JP5039923B2 true JP5039923B2 (en) | 2012-10-03 |

Family

ID=40559435

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2008314245A Expired - Lifetime JP5039923B2 (en) | 2008-12-10 | 2008-12-10 | Electroplated interconnect structures on integrated circuit chips. |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP5039923B2 (en) |

Families Citing this family (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP5419793B2 (en) * | 2010-04-22 | 2014-02-19 | インターナショナル・ビジネス・マシーンズ・コーポレーション | Electroplated interconnect structures on integrated circuit chips. |

| US20170145577A1 (en) * | 2015-11-19 | 2017-05-25 | Rohm And Haas Electronic Materials Llc | Method of electroplating low internal stress copper deposits on thin film substrates to inhibit warping |

| US11242610B2 (en) | 2017-10-19 | 2022-02-08 | Kyushu University, National University Corporation | Plating method, bubble ejection member, plating apparatus, and device |

| KR20200109549A (en) | 2019-03-13 | 2020-09-23 | 삼성전자주식회사 | Polishing slurry and method of manufacturing semiconductor device |

| US11424133B2 (en) | 2019-07-25 | 2022-08-23 | Samsung Electronics Co., Ltd. | Metal structure and method of manufacturing the same and metal wire and semiconductor device and electronic device |

Family Cites Families (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3328273A (en) * | 1966-08-15 | 1967-06-27 | Udylite Corp | Electro-deposition of copper from acidic baths |

| US3770598A (en) * | 1972-01-21 | 1973-11-06 | Oxy Metal Finishing Corp | Electrodeposition of copper from acid baths |

| JPS5819170Y2 (en) * | 1980-08-16 | 1983-04-19 | 征一郎 相合 | Semiconductor wafer plating equipment |

| JPH0246675B2 (en) * | 1986-07-04 | 1990-10-16 | Nippon Kagaku Sangyo Kk | SANSEIDOMETSUKYOKU |

| DE3836521C2 (en) * | 1988-10-24 | 1995-04-13 | Atotech Deutschland Gmbh | Aqueous acidic bath for the galvanic deposition of shiny and crack-free copper coatings and use of the bath |

| US5256274A (en) * | 1990-08-01 | 1993-10-26 | Jaime Poris | Selective metal electrodeposition process |

| JPH05171500A (en) * | 1991-12-26 | 1993-07-09 | Fujitsu Ltd | Method and device for plating |

| JP3064734B2 (en) * | 1993-04-01 | 2000-07-12 | 日本電気株式会社 | Method for manufacturing semiconductor device |

| JP3632981B2 (en) * | 1993-08-16 | 2005-03-30 | 株式会社東芝 | Multilayer wiring board and method for manufacturing multilayer wiring apparatus |

| JP3337876B2 (en) * | 1994-06-21 | 2002-10-28 | 株式会社東芝 | Method for manufacturing semiconductor device |

| JP5419793B2 (en) * | 2010-04-22 | 2014-02-19 | インターナショナル・ビジネス・マシーンズ・コーポレーション | Electroplated interconnect structures on integrated circuit chips. |

-

2008

- 2008-12-10 JP JP2008314245A patent/JP5039923B2/en not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| JP2009065207A (en) | 2009-03-26 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US6709562B1 (en) | Method of making electroplated interconnection structures on integrated circuit chips | |

| US20060017169A1 (en) | Electroplated interconnection structures on integrated circuit chips | |

| JP2000510289A (en) | Electroplating interconnect structures on integrated circuit chips | |

| US6344129B1 (en) | Method for plating copper conductors and devices formed | |

| US8197662B1 (en) | Deposit morphology of electroplated copper | |

| JP4888913B2 (en) | Copper electrical deposition method in microelectronics | |

| US5972192A (en) | Pulse electroplating copper or copper alloys | |

| US7968455B2 (en) | Copper deposition for filling features in manufacture of microelectronic devices | |

| JP4116781B2 (en) | Seed restoration and electrolytic plating bath | |

| JP3898013B2 (en) | Electrolytic solution for copper plating and electroplating method for copper wiring of semiconductor element using the same | |

| US7989347B2 (en) | Process for filling recessed features in a dielectric substrate | |

| US20050045486A1 (en) | Plating method and plating solution | |

| US6333120B1 (en) | Method for controlling the texture and microstructure of plated copper and plated structure | |

| KR20080100223A (en) | Copper electrodeposition in microelectronics | |

| EP1479793A2 (en) | Plating method | |

| JP5039923B2 (en) | Electroplated interconnect structures on integrated circuit chips. | |

| JP5419793B2 (en) | Electroplated interconnect structures on integrated circuit chips. | |

| KR20130108978A (en) | Copper-electroplating composition and process for filling a cavity in a semiconductor substrate using this composition | |

| US20050045485A1 (en) | Method to improve copper electrochemical deposition | |

| EP1477588A1 (en) | Copper Electroplating composition for wafers | |

| JP4551206B2 (en) | Electroplated interconnect structures on integrated circuit chips. | |

| KR20020029933A (en) | Galvanizing solution for the galvanic deposition of copper | |

| CN1181530C (en) | Electroplated interconnection structures on integrated circuit chips | |

| US7227265B2 (en) | Electroplated copper interconnection structure, process for making and electroplating bath | |

| US20020079232A1 (en) | Seed layer deposition |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081210 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20120104 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20120112 |

|

| A521 | Written amendment |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120402 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120508 |

|

| RD14 | Notification of resignation of power of sub attorney |

Free format text: JAPANESE INTERMEDIATE CODE: A7434 Effective date: 20120508 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120522 |

|

| R150 | Certificate of patent or registration of utility model |

Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150720 Year of fee payment: 3 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |