JP4980049B2 - 遷移後の薄層の緩和 - Google Patents

遷移後の薄層の緩和 Download PDFInfo

- Publication number

- JP4980049B2 JP4980049B2 JP2006502498A JP2006502498A JP4980049B2 JP 4980049 B2 JP4980049 B2 JP 4980049B2 JP 2006502498 A JP2006502498 A JP 2006502498A JP 2006502498 A JP2006502498 A JP 2006502498A JP 4980049 B2 JP4980049 B2 JP 4980049B2

- Authority

- JP

- Japan

- Prior art keywords

- layer

- strained

- vitreous

- substrate

- sio

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 230000007704 transition Effects 0.000 title 1

- 239000010410 layer Substances 0.000 claims description 507

- 239000000758 substrate Substances 0.000 claims description 136

- 238000000034 method Methods 0.000 claims description 119

- 239000000463 material Substances 0.000 claims description 65

- 229910004298 SiO 2 Inorganic materials 0.000 claims description 48

- 238000010438 heat treatment Methods 0.000 claims description 36

- 230000003647 oxidation Effects 0.000 claims description 27

- 238000007254 oxidation reaction Methods 0.000 claims description 27

- 239000002344 surface layer Substances 0.000 claims description 26

- 238000011282 treatment Methods 0.000 claims description 19

- 239000004065 semiconductor Substances 0.000 claims description 17

- 239000013078 crystal Substances 0.000 claims description 15

- 239000012212 insulator Substances 0.000 claims description 13

- 230000008569 process Effects 0.000 claims description 12

- 230000015572 biosynthetic process Effects 0.000 claims description 11

- 238000003486 chemical etching Methods 0.000 claims description 11

- 229910052710 silicon Inorganic materials 0.000 claims description 9

- 239000000126 substance Substances 0.000 claims description 8

- 238000000926 separation method Methods 0.000 claims description 7

- KRHYYFGTRYWZRS-UHFFFAOYSA-N Fluorane Chemical compound F KRHYYFGTRYWZRS-UHFFFAOYSA-N 0.000 claims description 6

- 239000005380 borophosphosilicate glass Substances 0.000 claims description 5

- 229910052814 silicon oxide Inorganic materials 0.000 claims description 3

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 39

- 238000009792 diffusion process Methods 0.000 description 18

- 238000000407 epitaxy Methods 0.000 description 15

- 238000003780 insertion Methods 0.000 description 14

- 230000037431 insertion Effects 0.000 description 14

- 238000000151 deposition Methods 0.000 description 12

- 238000005530 etching Methods 0.000 description 12

- 239000000203 mixture Substances 0.000 description 12

- 238000005516 engineering process Methods 0.000 description 11

- 238000005498 polishing Methods 0.000 description 11

- 238000000137 annealing Methods 0.000 description 10

- 230000008021 deposition Effects 0.000 description 9

- 238000004519 manufacturing process Methods 0.000 description 9

- 230000000694 effects Effects 0.000 description 8

- 230000007547 defect Effects 0.000 description 7

- 229910021417 amorphous silicon Inorganic materials 0.000 description 6

- 238000011161 development Methods 0.000 description 6

- 230000018109 developmental process Effects 0.000 description 6

- 238000005304 joining Methods 0.000 description 6

- QVGXLLKOCUKJST-UHFFFAOYSA-N atomic oxygen Chemical compound [O] QVGXLLKOCUKJST-UHFFFAOYSA-N 0.000 description 5

- 239000011521 glass Substances 0.000 description 5

- 238000009499 grossing Methods 0.000 description 5

- 238000002513 implantation Methods 0.000 description 5

- 239000001301 oxygen Substances 0.000 description 5

- 229910052760 oxygen Inorganic materials 0.000 description 5

- 230000008859 change Effects 0.000 description 4

- 238000011109 contamination Methods 0.000 description 4

- 239000002178 crystalline material Substances 0.000 description 4

- 239000007789 gas Substances 0.000 description 4

- 238000000227 grinding Methods 0.000 description 4

- 229910052739 hydrogen Inorganic materials 0.000 description 4

- 238000001451 molecular beam epitaxy Methods 0.000 description 4

- 125000000896 monocarboxylic acid group Chemical group 0.000 description 4

- 230000007420 reactivation Effects 0.000 description 4

- 230000002040 relaxant effect Effects 0.000 description 4

- 239000011345 viscous material Substances 0.000 description 4

- OKTJSMMVPCPJKN-UHFFFAOYSA-N Carbon Chemical compound [C] OKTJSMMVPCPJKN-UHFFFAOYSA-N 0.000 description 3

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 description 3

- 229910052799 carbon Inorganic materials 0.000 description 3

- 230000006835 compression Effects 0.000 description 3

- 238000007906 compression Methods 0.000 description 3

- 229910052732 germanium Inorganic materials 0.000 description 3

- 239000001307 helium Substances 0.000 description 3

- 229910052734 helium Inorganic materials 0.000 description 3

- 239000001257 hydrogen Substances 0.000 description 3

- 238000012545 processing Methods 0.000 description 3

- 239000010703 silicon Substances 0.000 description 3

- 238000005406 washing Methods 0.000 description 3

- IJGRMHOSHXDMSA-UHFFFAOYSA-N Atomic nitrogen Chemical compound N#N IJGRMHOSHXDMSA-UHFFFAOYSA-N 0.000 description 2

- UFHFLCQGNIYNRP-UHFFFAOYSA-N Hydrogen Chemical compound [H][H] UFHFLCQGNIYNRP-UHFFFAOYSA-N 0.000 description 2

- 229910003811 SiGeC Inorganic materials 0.000 description 2

- 125000004429 atom Chemical group 0.000 description 2

- 239000002800 charge carrier Substances 0.000 description 2

- 239000000470 constituent Substances 0.000 description 2

- 230000000875 corresponding effect Effects 0.000 description 2

- SWQJXJOGLNCZEY-UHFFFAOYSA-N helium atom Chemical compound [He] SWQJXJOGLNCZEY-UHFFFAOYSA-N 0.000 description 2

- 230000005693 optoelectronics Effects 0.000 description 2

- 238000011160 research Methods 0.000 description 2

- 238000005728 strengthening Methods 0.000 description 2

- WGTYBPLFGIVFAS-UHFFFAOYSA-M tetramethylammonium hydroxide Chemical compound [OH-].C[N+](C)(C)C WGTYBPLFGIVFAS-UHFFFAOYSA-M 0.000 description 2

- XLYOFNOQVPJJNP-UHFFFAOYSA-N water Substances O XLYOFNOQVPJJNP-UHFFFAOYSA-N 0.000 description 2

- VHUUQVKOLVNVRT-UHFFFAOYSA-N Ammonium hydroxide Chemical compound [NH4+].[OH-] VHUUQVKOLVNVRT-UHFFFAOYSA-N 0.000 description 1

- ZOXJGFHDIHLPTG-UHFFFAOYSA-N Boron Chemical compound [B] ZOXJGFHDIHLPTG-UHFFFAOYSA-N 0.000 description 1

- OAICVXFJPJFONN-UHFFFAOYSA-N Phosphorus Chemical compound [P] OAICVXFJPJFONN-UHFFFAOYSA-N 0.000 description 1

- 229910006990 Si1-xGex Inorganic materials 0.000 description 1

- 229910007020 Si1−xGex Inorganic materials 0.000 description 1

- LEVVHYCKPQWKOP-UHFFFAOYSA-N [Si].[Ge] Chemical compound [Si].[Ge] LEVVHYCKPQWKOP-UHFFFAOYSA-N 0.000 description 1

- 230000009471 action Effects 0.000 description 1

- 230000006978 adaptation Effects 0.000 description 1

- 239000000853 adhesive Substances 0.000 description 1

- 230000001070 adhesive effect Effects 0.000 description 1

- 239000000908 ammonium hydroxide Substances 0.000 description 1

- 229910052796 boron Inorganic materials 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 238000004140 cleaning Methods 0.000 description 1

- 230000000052 comparative effect Effects 0.000 description 1

- 239000000356 contaminant Substances 0.000 description 1

- 230000002596 correlated effect Effects 0.000 description 1

- 238000000354 decomposition reaction Methods 0.000 description 1

- 230000006837 decompression Effects 0.000 description 1

- 239000008367 deionised water Substances 0.000 description 1

- 229910021641 deionized water Inorganic materials 0.000 description 1

- 230000002542 deteriorative effect Effects 0.000 description 1

- 238000001312 dry etching Methods 0.000 description 1

- 239000012776 electronic material Substances 0.000 description 1

- 238000007730 finishing process Methods 0.000 description 1

- GNPVGFCGXDBREM-UHFFFAOYSA-N germanium atom Chemical compound [Ge] GNPVGFCGXDBREM-UHFFFAOYSA-N 0.000 description 1

- -1 helium ions Chemical class 0.000 description 1

- 150000002431 hydrogen Chemical class 0.000 description 1

- 238000011065 in-situ storage Methods 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- 238000003475 lamination Methods 0.000 description 1

- 239000007791 liquid phase Substances 0.000 description 1

- 238000001459 lithography Methods 0.000 description 1

- 230000000873 masking effect Effects 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 238000002488 metal-organic chemical vapour deposition Methods 0.000 description 1

- 238000002156 mixing Methods 0.000 description 1

- 229910021421 monocrystalline silicon Inorganic materials 0.000 description 1

- 229910052757 nitrogen Inorganic materials 0.000 description 1

- 230000006911 nucleation Effects 0.000 description 1

- 238000010899 nucleation Methods 0.000 description 1

- 230000003287 optical effect Effects 0.000 description 1

- 230000001590 oxidative effect Effects 0.000 description 1

- 238000006385 ozonation reaction Methods 0.000 description 1

- 229910052698 phosphorus Inorganic materials 0.000 description 1

- 239000011574 phosphorus Substances 0.000 description 1

- 238000000206 photolithography Methods 0.000 description 1

- 238000001020 plasma etching Methods 0.000 description 1

- 238000000623 plasma-assisted chemical vapour deposition Methods 0.000 description 1

- 238000011084 recovery Methods 0.000 description 1

- 238000002791 soaking Methods 0.000 description 1

- 239000007921 spray Substances 0.000 description 1

- 238000005507 spraying Methods 0.000 description 1

- 230000007847 structural defect Effects 0.000 description 1

- 230000003746 surface roughness Effects 0.000 description 1

- 238000004381 surface treatment Methods 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

- 238000001039 wet etching Methods 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/30—Treatment of semiconductor bodies using processes or apparatus not provided for in groups H01L21/20 - H01L21/26

- H01L21/324—Thermal treatment for modifying the properties of semiconductor bodies, e.g. annealing, sintering

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

- H01L21/76254—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques with separation/delamination along an ion implanted layer, e.g. Smart-cut, Unibond

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76251—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques

- H01L21/76259—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology using bonding techniques with separation/delamination along a porous layer

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- Computer Hardware Design (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Power Engineering (AREA)

- Recrystallisation Techniques (AREA)

Description

(1)ドナー基板上での半導体材料の薄層のエピタキシ;

(2)薄層における受け入れ基板の接合;

(3)ドナー基板の一部の除去。

・ステップ(1)の適用時;または

・その後の処理時に達成してもよい。

(a)ドナー基板の上で、半導体材料から選ばれた材料から成る弾性的に歪む層を成長させるステップと;

(b)歪み層の上、または受け入れ基板の上で、粘性温度から粘性をおびた材料で作製されるガラス質層を形成するステップと;

(c)受け入れ基板を、ガラス質層を介して歪み層に接合するステップと;

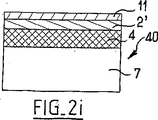

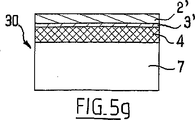

(d)ドナー基板の一部分を除去するステップであって、受け入れ基板と、ガラス質層と、歪み層と、結果的に表面層を形成することとなるドナー基板の除去されない部分とを備える構造を形成するステップと;

(e)粘性温度に近いか、それを上回る温度で構造を熱処理するステップと、を含む。

−ステップ(b)とステップ(c)とは、歪み層の材料の内少なくとも1種が実質的に拡散する前に、ストレスを受ける層が汚染する前、およびストレスを受ける層の表面が制御できないほど反応的になる前に実行する;

−ステップ(d)の後に被制御処理を施すことで、表面層の少なくとも一部分を第2の粘性温度から粘性を帯びる材料に変換し、その結果第2のガラス質層を形成する;

−ステップ(e)は、第2のガラス質層の形成の最中もしくはその後に続けて実行する;

−ステップ(e)の後には第2のガラス質層を除去するためのステップを施す;

−本方法はさらに、半導体材料から選ばれた材料の構造の上に施す最終結晶成長ステップを含む;

−受け入れ基板の上ではガラス質層を形成し、また本方法は、ステップ(c)より前に、厚みが歪み層の厚みに満たない薄層を歪み層の上で形成するステップをさらに含み;

−ステップ(b)は以下の2つの連続する操作、すなわち:

(b1)歪み層の上で半導電性層を成長させる操作と;

(b2)ステップ(b1)で形成した層の少なくとも一部分を、粘性温度から粘性を帯びる材料に変換するための被制御処理を実行し、その結果ガラス質層を形成する操作と、を含む;

−ステップ(c)より前に、受け入れ基板の上で接合層を形成するステップ;

−接合層はSiO2である;

−ステップ(d)の材料除去は、ドナー基板内にある脆化エリアにおける、表面層の厚みに近い深さにてエネルギーを供給することによる分離によって実質的に達成する;

−ステップ(c)より前に、ドナー基板の中に原子種を注入することによって脆化エリアを形成するステップ;

−ステップ(a)より前に、ドナー基板を形成するステップであって、かかるステップは以下の操作、すなわち:

・結晶性支持基板の上で有孔層を形成する操作、

・有孔層の上で結晶層を成長させる操作を含み;

その全体[支持基板/有孔層/結晶層]は前記ドナー基板に当り、有孔層はドナー基板内の脆化エリアにあたる。

−ステップ(d)の材料除去は選択的化学エッチングを含む;

−ステップ(b)で形成するガラス質層は電気的に絶縁する;

−ステップ(b)で形成するガラス質層はSiO2である;

−ドナー基板はSiであり、歪み層はSi1−xGexである;

−ドナー基板はSiバルク保持基板と、Siの格子パラメータをSi1−xGexに適合するバッファ構造とを備え、また歪み層はSi歪み層とz>xのSi1−zGez歪み層と、を備える;

−ステップ(b1)で成長させる層はSiであり、ステップ(b2)で施す被制御処理は、ステップ(b1)で形成した層のSiの少なくとも一部分をSiO2に変換し、その結果SiO2ガラス質層を形成する被制御熱酸化処理である;

−前記被制御処理は、表面層におけるSiの少なくとも一部分をSiO2に変換し、その結果第2のSiO2ガラス質層を形成する被制御熱酸化処理である;

−本方法はさらに、ステップ(e)より後に、フッ化水素酸に基づく化学処理によって第2のガラス質層を除去するステップを含む;

−ステップ(e)は熱処理を含む;

−第2のガラス質層の除去より後の構造の上での成長に用いる材料はSiである;

−ステップ(b)で形成するガラス質層は電気的に絶縁し、また形成される構造は絶縁体上半導体構造であり、その半導電性の厚みはステップ(e)で緩和または擬似緩和された歪み層を備える;

−本方法はさらに、コンポーネント製造のための準備をするステップ、及び歪み層において、その上で任意にエピタキシ成長した層においてコンポーネントを製造するステップの少なくとも一方を含む。

−歪み層2に含まれるゲルマニウムが大気中に拡散できる前;及び

−歪み層2がかなり汚染する前;及び

−歪み層2の表面が制御できないほど反応的になる前に;

ガラス質層4で覆うことが重要であり、その全体がRTAタイプのアニーリング処理や犠牲酸化処理等、高温での熱処理を受ける場合は特に重要である。

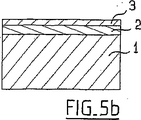

(b1)図1bを参照し、歪み層2の上で半導体材料層3を成長させるステップ;その後

(b2)図1cを参照し、ステップ(b1)で形成した層の少なくとも一部分を粘性温度から粘性を帯びる材料に変換し、その結果ガラス質層4を形成する被制御処理を施すステップ。

・歪み層2を形成するための温度が保たれる場合には歪み層2の形成の直後に;または

・歪み層2形成の直後に生じる室温への温度低下の後に続く温度上昇の直後、に施す。

・アモルフォスSi層を形成するためのアモルフォスSi原子種の沈着;また

・かかるアモルフォスSi層の熱酸化、それによりSiO2ガラス質層4を形成する。

・受け入れ基板7とガラス質層4との接合;

・ドナー基板1の一部分の除去。

・Si保持基板1A上での有孔層の形成;

・有孔層上でのSi層1Bの成長。

・約200Å乃至約800Åの厚みを得るための研磨;

・Ar/H2RTA高速アニーリングと、その後に続く約200Å乃至約800Åの厚みを得るための研磨;

・1回の高速RTAアニーリング;

・Ar/H2オーブンアニーリング。

・層3をガラス質層4に変換するステップは異なり、ここでは同ステップを、層3全体が変換されないように施す;

・表面層1Bを第2のガラス質層8に変換するステップは異なり、ここでは同ステップを、表面層1Bが変換されないよう施す。

−ステップ5bを参照し、歪み層2上のエピタキシ成長Si層3は極めて薄い層であり、その厚みは、典型的には100乃至300Åと、歪み層2のそれを大きく下回り;

−図5dを参照すると、ガラス質層4は、受け入れ基板7の上で形成される。

−上を覆うSiGe歪み層2を、Ge拡散、外来の汚染、そしてその表面の不制御の再活性化から保護すること;

−十分に極められていないSiGe向けの表面仕上げ手段に対し、完全に極められた表面仕上げ手段をSiに適用すること、尚それらの仕上げ技術(本明細書で既述)は、特に受け入れ基板7との良好な接合をもたらす。

・アモルフォスSi層を形成するためのアモルフォスSi原子種の沈着;その後

・かかるアモルフォスSi層の熱酸化、それによりSiO2ガラス質層4を形成する。

−歪み層2はその際少なくとも部分的には緩和層2になる;

−挿入層3はその際歪み挿入層3’になる。

・Siの保持基板1−1と上位層1−3のSi1−zGezの公称格子パラメータとの間での格子パラメータの適合;

・結晶欠陥の閉じ込め、その際、上位層1−3の表面では、欠陥が皆無となるか僅少となる。

4 ガラス質層

7 受け入れ基板

8 表面層(第2のガラス質層)

20 構造

Claims (21)

- 基板上に緩和または擬似緩和層を形成する方法であって、前記緩和または擬似緩和層(2’)はSi1−xGexからなる材料とし、その方法が以下のステップ、すなわち:

(a)ドナー基板(1)の上で、Si1−xGexから成る弾性的に歪む層(2)を成長させるステップと;

(b)前記歪み層(2)の上、または受け入れ基板(7)の上で、粘性温度から粘性を帯びかつBPSG、SiO2またはSiONから成る材料で作製されたガラス質層(4)を形成するステップと;

(c)前記ガラス質層(4)を介し前記受け入れ基板(7)を前記歪み層(2)に接合するステップと;

(d)前記ドナー基板(1)の一部分を除去するステップであって、前記受け入れ基板(7)と、前記ガラス質層(4)と、前記歪み層(2)と、結果的に表面層(1B)を形成することとなる前記ドナー基板(1)の除去されない部分とを備える構造を形成するステップと;

前記表面層(1B)の少なくとも一部分を第2の粘性温度から粘性を帯びるSiO2に変換して第2のガラス質層(8)を形成するように前記構造を処理し、

(e)前記ガラス質層(4)の粘性および弾性的な前記歪み層(2)の緩和を引き起こすために前記ガラス質層(4)の粘性温度を上回る温度で前記構造を熱処理し、前記緩和または擬似緩和層を得るステップと、を具備し、

ステップ(b)とステップ(c)とを、前記歪み層(2)から大気中へGeが拡散することを防止するために、前記歪み層(2)の露出前に行い、

ステップ(e)は、前記第2のガラス質層(8)の形成中、あるいは、その後に連続して行うことを特徴とする、方法。 - ステップ(e)より後に、前記第2のガラス質層(8)を除去するステップをさらに含むことを特徴とする、請求項1に記載の方法。

- 半導体材料から選ばれた材料の前記緩和または擬似緩和層(2’)の上にSi結晶を成長させる最終ステップをさらに含むことを特徴とする、請求項2に記載の方法。

- 前記ガラス質層(4)を前記受け入れ基板(7)の上で形成すること、および本方法がステップ(c)より前に、厚みが前記歪み層(2)の厚みに満たない薄層を前記歪み層(2)の上で形成するステップをさらに含むことを特徴とする、請求項1から請求項3のいずれかに記載の方法。

- ステップ(b)が以下の2つの連続する操作、すなわち:

(b1)前記歪み層の上で半導体材料層を成長させる操作;

(b2)ステップ(b1)で形成した層の少なくとも一部分を、粘性温度から粘性を帯びるSiO2に変換し、その結果前記ガラス質層を形成する被制御処理を実行する操作を含むことを特徴とする、請求項1から請求項4のいずれかに記載の方法。 - ステップ(e)の熱処理は、前記受け入れ基板(7)と前記ガラス質層との間の接合を強めるために適用されることを特徴とする、請求項1から請求項5のいずれかに記載の方法。

- 前記受け入れ基板(7)上にSiO2からなる接合層を形成するステップをさらに備えたことを特徴とする、請求項6に記載の方法。

- ステップ(d)の材料除去を、前記ドナー基板(1)内にある脆化エリアにおける、表面層(1B)の厚みに近い深さにてエネルギーを供給することによる分離によって達成することを特徴とする、請求項1から請求項7のいずれかに記載の方法。

- ステップ(c)より前に、前記ドナー基板(1)の中に原子種を注入することによって前記脆化エリアを形成するステップをさらに含むことを特徴とする、請求項8に記載の方法。

- ステップ(a)より前に、ドナー基板(1)を形成するステップをさらに含むことを特徴とし、前記ステップは以下の操作、すなわち:

結晶性保持基板(1A)の上で有孔層(6)を形成する操作と;

前記有孔層(6)の上で結晶層(1B)を成長させる操作と、を含み;

その全体[保持基板(1A)\有孔層(6)\結晶層(1B)]が前記ドナー基板(1)に当り、前記有孔層(6)が前記ドナー基板(1)内の脆化エリアにあたる、請求項8に記載の方法。 - ステップ(d)の材料除去が選択的化学エッチングを含むことを特徴とする、請求項1から請求項10のいずれかに記載の方法。

- ステップ(b)で形成する前記ガラス質層(4)が電気的に絶縁することを特徴とする、請求項1から請求項11のいずれかに記載の方法。

- ステップ(b)で形成する前記ガラス質層(4)がSiO2であることを特徴とする、請求項12に記載の方法。

- 前記ドナー基板(1)がSiであること;および

前記歪み層(2)がSi1−xGexであることを特徴とする、請求項1から請求項13のいずれかに記載の方法。 - 前記ドナー基板(1)がSiバルク保持基板(1−1)と、SiからSi1−zGezにかけて格子パラメータを適合するバッファ構造(1−2、1−3)とを備えること;

前記歪み層(2)がSi歪み層(2−1)とx>zのSi1−xGex歪み層(2−2)とを備えることを特徴とする、請求項1から請求項14のいずれかに記載の方法。 - ステップ(b1)で成長させる層がSiであること;

ステップ(b2)で施す被制御処理が、ステップ(b1)で形成した前記層のSiの少なくとも一部分をSiO2に変換し、その結果前記SiO2ガラス質層(4)を形成する被制御熱酸化処理であることを特徴とする、請求項5、請求項13、請求項14または15に記載の方法。 - 前記ドナー基板(1)がSiであり、前記被制御処理が、前記表面層(1B)におけるSiの少なくとも一部分をSiO2に変換し、その結果前記第2のSiO2ガラス質層を形成する被制御熱酸化処理であることを特徴とする、請求項5、請求項13から請求項15のいずれかに記載の方法。

- ステップ(e)より後に、フッ化水素酸に基づく化学処理により前記第2のガラス質層(8)を除去するステップをさらに含むことを特徴とする、請求項17に記載の方法。

- 前記第2のガラス質層(8)の除去より後の前記構造上での成長に用いる材料がSiであることを特徴とする、請求項3に記載の方法。

- ステップ(b)で形成するガラス質層(4)が電気的に絶縁すること、および形成された前記構造が絶縁体上半導体構造であることを特徴とし、該絶縁体上半導体構造の半導体部分がステップ(e)で緩和または擬似緩和された歪み層(2)を備える、請求項1から請求項19のいずれかに記載の方法。

- 前記緩和または擬似緩和層(2’)上に層をエピタキシャル成長させることをさらに含むことを特徴とする、請求項1から請求項19のいずれかに記載の方法。

Applications Claiming Priority (3)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| FR0302518 | 2003-02-28 | ||

| FR0302518A FR2851847B1 (fr) | 2003-02-28 | 2003-02-28 | Relaxation d'une couche mince apres transfert |

| PCT/IB2004/000927 WO2004077552A1 (en) | 2003-02-28 | 2004-03-01 | Relaxation of a thin layer after its transfer |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2006519488A JP2006519488A (ja) | 2006-08-24 |

| JP4980049B2 true JP4980049B2 (ja) | 2012-07-18 |

Family

ID=32843091

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2006502498A Expired - Lifetime JP4980049B2 (ja) | 2003-02-28 | 2004-03-01 | 遷移後の薄層の緩和 |

Country Status (4)

| Country | Link |

|---|---|

| EP (1) | EP1597758A1 (ja) |

| JP (1) | JP4980049B2 (ja) |

| FR (1) | FR2851847B1 (ja) |

| WO (1) | WO2004077552A1 (ja) |

Families Citing this family (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7235812B2 (en) | 2004-09-13 | 2007-06-26 | International Business Machines Corporation | Method of creating defect free high Ge content (>25%) SiGe-on-insulator (SGOI) substrates using wafer bonding techniques |

| JP4958797B2 (ja) * | 2005-02-24 | 2012-06-20 | ソイテック | SiGe層の表面領域を酸化させる方法、SGOI構造体内の少なくとも1つの接合境界面を安定化させる方法、及びSiGe層を半導体材料製の基板層と接合する方法 |

| EP2151852B1 (en) | 2008-08-06 | 2020-01-15 | Soitec | Relaxation and transfer of strained layers |

| TWI457984B (zh) * | 2008-08-06 | 2014-10-21 | Soitec Silicon On Insulator | 應變層的鬆弛方法 |

| EP2151856A1 (en) | 2008-08-06 | 2010-02-10 | S.O.I. TEC Silicon | Relaxation of strained layers |

| EP2159836B1 (en) * | 2008-08-25 | 2017-05-31 | Soitec | Stiffening layers for the relaxation of strained layers |

| CN102239538A (zh) * | 2008-09-24 | 2011-11-09 | S.O.I.探测硅绝缘技术公司 | 形成经松弛半导体材料层、半导体结构、装置的方法及包含经松弛半导体材料层、半导体结构、装置的工程衬底 |

| FR2936903B1 (fr) * | 2008-10-07 | 2011-01-14 | Soitec Silicon On Insulator | Relaxation d'une couche de materiau contraint avec application d'un raidisseur |

| EP2221853B1 (en) | 2009-02-19 | 2012-04-25 | S.O.I. TEC Silicon | Relaxation and transfer of strained material layers |

Family Cites Families (10)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5906951A (en) * | 1997-04-30 | 1999-05-25 | International Business Machines Corporation | Strained Si/SiGe layers on insulator |

| US5882987A (en) * | 1997-08-26 | 1999-03-16 | International Business Machines Corporation | Smart-cut process for the production of thin semiconductor material films |

| US20020089032A1 (en) * | 1999-08-23 | 2002-07-11 | Feng-Yi Huang | Processing method for forming dislocation-free silicon-on-insulator substrate prepared by implantation of oxygen |

| JP4226175B2 (ja) * | 1999-12-10 | 2009-02-18 | 富士通株式会社 | 半導体装置およびその製造方法 |

| KR100429869B1 (ko) * | 2000-01-07 | 2004-05-03 | 삼성전자주식회사 | 매몰 실리콘 저머늄층을 갖는 cmos 집적회로 소자 및기판과 그의 제조방법 |

| JP2002164520A (ja) * | 2000-11-27 | 2002-06-07 | Shin Etsu Handotai Co Ltd | 半導体ウェーハの製造方法 |

| US6940089B2 (en) * | 2001-04-04 | 2005-09-06 | Massachusetts Institute Of Technology | Semiconductor device structure |

| JP2002305293A (ja) * | 2001-04-06 | 2002-10-18 | Canon Inc | 半導体部材の製造方法及び半導体装置の製造方法 |

| JP3648466B2 (ja) * | 2001-06-29 | 2005-05-18 | 株式会社東芝 | 電界効果トランジスタ、半導体基板、電界効果トランジスタの製造方法及び半導体基板の製造方法 |

| JP2003031495A (ja) * | 2001-07-12 | 2003-01-31 | Hitachi Ltd | 半導体装置用基板の製造方法および半導体装置の製造方法 |

-

2003

- 2003-02-28 FR FR0302518A patent/FR2851847B1/fr not_active Expired - Lifetime

-

2004

- 2004-03-01 WO PCT/IB2004/000927 patent/WO2004077552A1/en active Application Filing

- 2004-03-01 EP EP04715981A patent/EP1597758A1/en not_active Withdrawn

- 2004-03-01 JP JP2006502498A patent/JP4980049B2/ja not_active Expired - Lifetime

Also Published As

| Publication number | Publication date |

|---|---|

| WO2004077552A1 (en) | 2004-09-10 |

| JP2006519488A (ja) | 2006-08-24 |

| FR2851847B1 (fr) | 2005-10-14 |

| EP1597758A1 (en) | 2005-11-23 |

| FR2851847A1 (fr) | 2004-09-03 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US8173512B2 (en) | Forming structures that include a relaxed or pseudo-relaxed layer on a substrate | |

| US20040192067A1 (en) | Method for forming a relaxed or pseudo-relaxed useful layer on a substrate | |

| EP1522097B1 (en) | Transfer of a thin layer from a wafer comprising a buffer layer | |

| US7348260B2 (en) | Method for forming a relaxed or pseudo-relaxed useful layer on a substrate | |

| JP4602475B2 (ja) | 歪み半導体材料から成る層の転移方法 | |

| JP4173884B2 (ja) | ゲルマニウム・オン・インシュレータ(GeOI)型ウェーハの製造方法 | |

| US7018910B2 (en) | Transfer of a thin layer from a wafer comprising a buffer layer | |

| US20070117350A1 (en) | Strained silicon on insulator (ssoi) with layer transfer from oxidized donor | |

| WO2004021420A9 (en) | Fabrication method for a monocrystalline semiconductor layer on a substrate | |

| US7001826B2 (en) | Wafer with a relaxed useful layer and method of forming the wafer | |

| JP4980049B2 (ja) | 遷移後の薄層の緩和 | |

| JP2006519489A (ja) | 薄層の、移動後の高温における弛緩 | |

| JP4654710B2 (ja) | 半導体ウェーハの製造方法 | |

| US20180005872A1 (en) | Preparation of silicon-germanium-on-insulator structures | |

| US20050023610A1 (en) | Semiconductor-on-insulator structure having high-temperature elastic constraints | |

| JP5032743B2 (ja) | バッファ層を有しないウエハからの緩和された有用層の形成 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20100402 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20100624 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20100701 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20101001 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110204 |

|

| A601 | Written request for extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A601 Effective date: 20110413 |

|

| A602 | Written permission of extension of time |

Free format text: JAPANESE INTERMEDIATE CODE: A602 Effective date: 20110420 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110712 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20111111 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20120106 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20120323 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20120418 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20150427 Year of fee payment: 3 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4980049 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| EXPY | Cancellation because of completion of term |