JP4888385B2 - 半導体装置及びその製造方法 - Google Patents

半導体装置及びその製造方法 Download PDFInfo

- Publication number

- JP4888385B2 JP4888385B2 JP2007505767A JP2007505767A JP4888385B2 JP 4888385 B2 JP4888385 B2 JP 4888385B2 JP 2007505767 A JP2007505767 A JP 2007505767A JP 2007505767 A JP2007505767 A JP 2007505767A JP 4888385 B2 JP4888385 B2 JP 4888385B2

- Authority

- JP

- Japan

- Prior art keywords

- active region

- region

- element isolation

- layer

- stress

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

- 239000004065 semiconductor Substances 0.000 title claims description 58

- 238000004519 manufacturing process Methods 0.000 title claims description 27

- 239000010410 layer Substances 0.000 claims description 102

- 229910052710 silicon Inorganic materials 0.000 claims description 75

- XUIMIQQOPSSXEZ-UHFFFAOYSA-N Silicon Chemical compound [Si] XUIMIQQOPSSXEZ-UHFFFAOYSA-N 0.000 claims description 74

- 239000010703 silicon Substances 0.000 claims description 74

- 239000000758 substrate Substances 0.000 claims description 52

- 239000011810 insulating material Substances 0.000 claims description 51

- 238000000034 method Methods 0.000 claims description 40

- 238000002955 isolation Methods 0.000 claims description 38

- 239000002344 surface layer Substances 0.000 claims description 23

- 239000000463 material Substances 0.000 claims description 12

- 230000035882 stress Effects 0.000 description 108

- 229910052581 Si3N4 Inorganic materials 0.000 description 42

- HQVNEWCFYHHQES-UHFFFAOYSA-N silicon nitride Chemical compound N12[Si]34N5[Si]62N3[Si]51N64 HQVNEWCFYHHQES-UHFFFAOYSA-N 0.000 description 42

- 230000015572 biosynthetic process Effects 0.000 description 41

- 125000006850 spacer group Chemical group 0.000 description 22

- 238000001459 lithography Methods 0.000 description 20

- 238000004380 ashing Methods 0.000 description 16

- 239000012535 impurity Substances 0.000 description 16

- 229910052814 silicon oxide Inorganic materials 0.000 description 15

- VYPSYNLAJGMNEJ-UHFFFAOYSA-N Silicium dioxide Chemical compound O=[Si]=O VYPSYNLAJGMNEJ-UHFFFAOYSA-N 0.000 description 12

- 229910000577 Silicon-germanium Inorganic materials 0.000 description 12

- QGZKDVFQNNGYKY-UHFFFAOYSA-N Ammonia Chemical compound N QGZKDVFQNNGYKY-UHFFFAOYSA-N 0.000 description 8

- 239000013078 crystal Substances 0.000 description 8

- 238000002474 experimental method Methods 0.000 description 7

- 150000002500 ions Chemical class 0.000 description 7

- 239000011229 interlayer Substances 0.000 description 6

- 238000000231 atomic layer deposition Methods 0.000 description 5

- 229910021529 ammonia Inorganic materials 0.000 description 4

- 230000007423 decrease Effects 0.000 description 4

- MROCJMGDEKINLD-UHFFFAOYSA-N dichlorosilane Chemical compound Cl[SiH2]Cl MROCJMGDEKINLD-UHFFFAOYSA-N 0.000 description 4

- 238000001039 wet etching Methods 0.000 description 4

- 230000001133 acceleration Effects 0.000 description 3

- 238000005452 bending Methods 0.000 description 3

- 238000001312 dry etching Methods 0.000 description 3

- 239000000243 solution Substances 0.000 description 3

- NBIIXXVUZAFLBC-UHFFFAOYSA-N Phosphoric acid Chemical compound OP(O)(O)=O NBIIXXVUZAFLBC-UHFFFAOYSA-N 0.000 description 2

- 230000004913 activation Effects 0.000 description 2

- 238000010586 diagram Methods 0.000 description 2

- 238000009792 diffusion process Methods 0.000 description 2

- 238000005530 etching Methods 0.000 description 2

- 238000010438 heat treatment Methods 0.000 description 2

- 239000007924 injection Substances 0.000 description 2

- 238000002347 injection Methods 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 230000003647 oxidation Effects 0.000 description 2

- 238000007254 oxidation reaction Methods 0.000 description 2

- 238000005498 polishing Methods 0.000 description 2

- 229910021420 polycrystalline silicon Inorganic materials 0.000 description 2

- -1 silicon oxide nitride Chemical class 0.000 description 2

- 239000000126 substance Substances 0.000 description 2

- 229910000147 aluminium phosphate Inorganic materials 0.000 description 1

- 229910052785 arsenic Inorganic materials 0.000 description 1

- RQNWIZPPADIBDY-UHFFFAOYSA-N arsenic atom Chemical compound [As] RQNWIZPPADIBDY-UHFFFAOYSA-N 0.000 description 1

- 238000005229 chemical vapour deposition Methods 0.000 description 1

- 238000000151 deposition Methods 0.000 description 1

- 230000008021 deposition Effects 0.000 description 1

- 230000009429 distress Effects 0.000 description 1

- 239000012212 insulator Substances 0.000 description 1

- 238000005468 ion implantation Methods 0.000 description 1

- LIVNPJMFVYWSIS-UHFFFAOYSA-N silicon monoxide Chemical class [Si-]#[O+] LIVNPJMFVYWSIS-UHFFFAOYSA-N 0.000 description 1

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26506—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/02—Manufacture or treatment of semiconductor devices or of parts thereof

- H01L21/04—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer

- H01L21/18—Manufacture or treatment of semiconductor devices or of parts thereof the devices having potential barriers, e.g. a PN junction, depletion layer or carrier concentration layer the devices having semiconductor bodies comprising elements of Group IV of the Periodic Table or AIIIBV compounds with or without impurities, e.g. doping materials

- H01L21/26—Bombardment with radiation

- H01L21/263—Bombardment with radiation with high-energy radiation

- H01L21/265—Bombardment with radiation with high-energy radiation producing ion implantation

- H01L21/26506—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors

- H01L21/26513—Bombardment with radiation with high-energy radiation producing ion implantation in group IV semiconductors of electrically active species

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/76—Making of isolation regions between components

- H01L21/762—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers

- H01L21/7624—Dielectric regions, e.g. EPIC dielectric isolation, LOCOS; Trench refilling techniques, SOI technology, use of channel stoppers using semiconductor on insulator [SOI] technology

- H01L21/76264—SOI together with lateral isolation, e.g. using local oxidation of silicon, or dielectric or polycristalline material refilled trench or air gap isolation regions, e.g. completely isolated semiconductor islands

- H01L21/76283—Lateral isolation by refilling of trenches with dielectric material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/84—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being other than a semiconductor body, e.g. being an insulating body

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/7842—Field effect transistors with field effect produced by an insulated gate means for exerting mechanical stress on the crystal lattice of the channel region, e.g. using a flexible substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L29/00—Semiconductor devices specially adapted for rectifying, amplifying, oscillating or switching and having potential barriers; Capacitors or resistors having potential barriers, e.g. a PN-junction depletion layer or carrier concentration layer; Details of semiconductor bodies or of electrodes thereof ; Multistep manufacturing processes therefor

- H01L29/66—Types of semiconductor device ; Multistep manufacturing processes therefor

- H01L29/68—Types of semiconductor device ; Multistep manufacturing processes therefor controllable by only the electric current supplied, or only the electric potential applied, to an electrode which does not carry the current to be rectified, amplified or switched

- H01L29/76—Unipolar devices, e.g. field effect transistors

- H01L29/772—Field effect transistors

- H01L29/78—Field effect transistors with field effect produced by an insulated gate

- H01L29/786—Thin film transistors, i.e. transistors with a channel being at least partly a thin film

- H01L29/78651—Silicon transistors

- H01L29/78654—Monocrystalline silicon transistors

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823807—Complementary field-effect transistors, e.g. CMOS with a particular manufacturing method of the channel structures, e.g. channel implants, halo or pocket implants, or channel materials

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/77—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate

- H01L21/78—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices

- H01L21/82—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components

- H01L21/822—Manufacture or treatment of devices consisting of a plurality of solid state components or integrated circuits formed in, or on, a common substrate with subsequent division of the substrate into plural individual devices to produce devices, e.g. integrated circuits, each consisting of a plurality of components the substrate being a semiconductor, using silicon technology

- H01L21/8232—Field-effect technology

- H01L21/8234—MIS technology, i.e. integration processes of field effect transistors of the conductor-insulator-semiconductor type

- H01L21/8238—Complementary field-effect transistors, e.g. CMOS

- H01L21/823878—Complementary field-effect transistors, e.g. CMOS isolation region manufacturing related aspects, e.g. to avoid interaction of isolation region with adjacent structure

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

- H01L27/02—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers

- H01L27/12—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body

- H01L27/1203—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate including semiconductor components specially adapted for rectifying, oscillating, amplifying or switching and having potential barriers; including integrated passive circuit elements having potential barriers the substrate being other than a semiconductor body, e.g. an insulating body the substrate comprising an insulating body on a semiconductor body, e.g. SOI

Landscapes

- Engineering & Computer Science (AREA)

- Physics & Mathematics (AREA)

- Power Engineering (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Computer Hardware Design (AREA)

- Condensed Matter Physics & Semiconductors (AREA)

- General Physics & Mathematics (AREA)

- Manufacturing & Machinery (AREA)

- High Energy & Nuclear Physics (AREA)

- Toxicology (AREA)

- Health & Medical Sciences (AREA)

- Chemical & Material Sciences (AREA)

- Crystallography & Structural Chemistry (AREA)

- Ceramic Engineering (AREA)

- Metal-Oxide And Bipolar Metal-Oxide Semiconductor Integrated Circuits (AREA)

- Thin Film Transistor (AREA)

- Element Separation (AREA)

Description

移動度を向上させるには、活性領域の表面近傍に歪みを導入することを要する。いわゆるバルク型のシリコン基板では、例えば層間絶縁膜により歪み導入を行う場合、シリコン基板の表面近傍で強い応力が加わり、シリコン基板の深部では応力は殆ど加わることはない(応力が深部で開放状態となる)。

本発明の半導体装置の別態様は、半導体基板と、前記半導体基板上に形成された絶縁層と、前記絶縁層上に形成されたシリコン層と、前記シリコン層に形成されたソース電極及びドレイン電極と、前記シリコン層上に形成されたゲート絶縁膜及びゲート電極と、前記シリコン層の少なくとも底面の一部に接し、前記シリコン層に第1応力を加える素子分離絶縁膜と、前記ソース電極、前記ドレイン電極及び前記ゲート電極を覆い、前記第1応力とは逆方向の応力である第2応力を前記シリコン層に加える応力絶縁膜とを含む。

本発明者は、活性領域がSOI基板のシリコン層のように極薄のものである場合でも、その表面近傍に局所的な歪みを導入すべく、半導体基板の活性領域に該たる表層部分(SOI基板ではシリコン層の活性領域)に、当該表層部分内の上方部位と下方部位とで逆方向の面内応力(表層部分の面内方向の応力)を印加し、これにより上方部位と下方部位とで結晶格子に逆方向の歪みを導入することに想到した。この場合、上方部位に当該トランジスタ構造の移動度向上に必要な方向の歪みを、下方部位にはこれとは逆の歪みをそれぞれ導入する。この技術思想を実現することにより、下方部位における上方部位と逆方向の歪みが当該上方部位の歪みを際立たせ、例えば厚みが10nm以下の極薄の表層部分であっても、必要な歪みを表層部分の表面近傍に局所的に導入することができる。

絶縁材料をその周囲の構造物よりも相対的により密となるように堆積すれば、活性領域に圧縮応力を与える傾向が強まり、逆に相対的により疎となるように堆積すれば、活性領域に引っ張り応力を与える傾向が強まる。従って、第1、第2の絶縁材料として同一のものを用いても良く、一方を相対的により密となるように、他方を相対的により疎となるように、しかもこれら疎密の度合いをそれぞれ調節して堆積することにより、各面内応力の方向及び大きさを所望に制御することができる。

この重畳量が多いほど、表層部分内の下方部位に印加する面内応力も増加する。下方部位に印加する面内応力が増加すれば、表層部分内の上方部位の歪みも助長されて大きくなる。従って、当該重畳量を調節するように第1の構造体を形成することにより、表層部分内の下方部位における面内応力の方向及び大きさを所望に制御し、必要な歪みを調節することができる。

以下、具体的な諸実施形態について、図面を参照しながら詳細に説明する。以下の各実施形態では、半導体装置としてCMOSトランジスタを例示し、説明の便宜上、CMOSトランジスタの構成をその製造方法と共に説明する。

図1A〜図1D及び図2A,図2Bは、第1の実施形態によるCMOSトランジスタの製造方法を工程順に示す概略断面図、図3A〜図3Dは図1及び図2中の所定の工程における状態を示す概略平面図である。ここで、図1及び図2中の破線I−Iに沿った断面が図3に対応する。

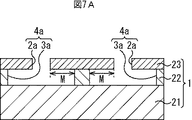

シリコン層23の素子分離領域をリソグラフィー及び絶縁層22をエッチングストッパーとしたドライエッチングにより加工し、形成領域Rpには溝2aを、形成領域Rnには2bを形成する。

溝2a,2bが形成されたシリコン層23をマスクとして、HF溶液等をエッチング液として用いて絶縁層22をウェットエッチングする。このウェットエッチングにより、溝2a,2bに整合して絶縁層22が除去され、絶縁層22に溝3a,3bが形成される。ここで、溝3a,3bは、エッチング液の回り込みにより溝2a,2bよりも幅広に形成される。溝2a,2bと溝3a,3bとは一体となるため、これらをまとめて溝4a,4bと称する。

先ず、例えばCVD法により、溝4a,4bの内壁面を覆うように、膜厚1nm程度の薄いシリコン酸化膜5を形成する。このシリコン酸化膜5は、後述する窒化シリコンとの密着性等を向上させるものである。

先ず、例えば熱酸化法等により活性領域23a,23bの表面に膜厚1nm程度のシリコン酸チッ化膜をそれぞれ成長し、ゲート絶縁膜8を形成する。次に、CVD法等により、全面に多結晶シリコン膜を膜厚100nm程度以下に堆積し、これをリソグラフィー及びドライエッチングにより加工して、活性領域23a,23b上にゲート絶縁膜8を介してゲート電極9a,9bをそれぞれ形成する。

先ず、リソグラフィーにより、活性領域23bのみを覆うレジストマスク(不図示)を形成する。この状態で、活性領域23a上でゲート電極9a及びサイドウォールスペーサ12を覆うように第2の絶縁材料、ここでは窒化シリコンを例えばALD(Atomic Layer Deposition)法により、例えば膜厚50nm〜100nm程度に堆積し、第2の構造体14aを形成する。ここでは、活性領域23a上で窒化シリコンの密度が比較的密となるように窒化シリコンの成膜条件を制御する。そして、レジストマスクをO2プラズマを用いた灰化処理等により除去する。

第1の構造体7a,7b及び第2の構造体14a,14bをその密度をそれぞれ調節して形成することにより、活性領域23a,23bの上下方部位に与える各面内応力の大きさを調節し、ひいては活性領域23a,23bの表面近傍における局所的な歪み量を制御する。

(2)

第1の構造体7a,7bと活性領域23a,23bとの重畳量を調節することにより、活性領域23a,23bの下方部位に与える各面内応力の大きさを調節し、ひいては活性領域23a,23bの表面近傍における局所的な歪み量を制御する。

各構造体が活性領域との関係で活性領域の上下方部位の一方に引っ張り応力を与える範囲内において、当該構造体を疎に形成するほど引っ張り応力が強まり、密に形成するほど引っ張り応力が弱まる。他方、各構造体が活性領域との関係で活性領域の上下方部位の一方に圧縮応力を与える範囲内において、当該構造体を密に形成するほど圧縮応力が強まり、疎に形成するほど圧縮応力が弱まる。従って、第1の構造体7a,7b及び第2の構造体14a,14bをその密度をそれぞれ調節して形成することにより、活性領域23a,23bの上下方部位に与える各面内応力の大きさを制御できる。

ここで、本実施形態によるCMOSトランジスタにおいて、そのP型MOSトランジスタを例に採り、(2)の手法の各実効について調べた実験について説明する。

図9A〜図9Dは、第2の実施形態によるCMOSトランジスタの製造方法のうち、第1の実施形態と異なる主要工程について順に示す概略断面図である。なお、第1の実施形態と同様の構成部材等については同符号を記す(以下の実施形態では、各工程においてRp形成、Rn形成の順で行うが、その順序に特に頓着するものではなく、Rn形成、Rp形成の順で行ってもよい。)。

先ず、例えばCVD法により、溝4a,4bの内壁面を覆うように、膜厚1nm程度の薄いシリコン酸化膜5を形成する。このシリコン酸化膜5は、第1の絶縁材料として用いる窒化シリコンとの密着性等を向上させるものである。

燐酸溶液等をエッチング液として用い、SOI基板1の表面をウェットエッチングして、溝4a,4bに充填された窒化シリコンのうち、溝2a,2bに充填された部分のみを除去する。このウェットエッチングにより、溝4a,4bのうち溝3a,3bのみを第1の絶縁材料である窒化シリコンで充填する(溝3a内では疎に、溝3b内では密にそれぞれ充填されている)第1の構造体7a,7bがそれぞれ形成される。

先ず、例えば熱酸化法により、形成領域Rp,Rnのシリコン層23の表面に膜厚1nm程度のシリコン酸チッ化膜をそれぞれ成長し、ゲート絶縁膜8を形成する。次に、CVD法等により、全面に多結晶シリコン膜を膜厚100nm程度以下に堆積し、これをリソグラフィー及びドライエッチングにより加工して、形成領域Rp,Rnのシリコン層23上にゲート絶縁膜8を介してゲート電極9a,9bをそれぞれ形成する。

先ず、リソグラフィーにより、活性領域23bのみを覆うレジストマスク(不図示)を形成する。この状態で、活性領域23a上でゲート電極9a及びサイドウォールスペーサ12を覆うように第2の絶縁材料、ここでは窒化シリコンを例えばALD法により、例えば膜厚50nm〜100nm程度に堆積し、第2の構造体14aを形成する。ここでは、活性領域23a上で窒化シリコンの密度が比較的密となるように窒化シリコンの成膜条件を制御する。そして、レジストマスクをO2プラズマを用いた灰化処理等により除去する。

Claims (10)

- 半導体基板と、

前記半導体基板上に形成されたトランジスタ構造と、

前記半導体基板の前記トランジスタ構造の下部に相当する表層部分の下部に形成された、当該表層部分内の下方部位に面内応力を印加する第1の構造体と、

前記半導体基板上で前記トランジスタ構造を覆うように、前記表層部分内の上方部位に前記面内応力を印加する第2の構造体と

を含み、

前記第1の構造体及び前記第2の構造体により、前記表層部分に、前記上方部位と前記下方部位とで逆方向の前記面内応力が印加されていることを特徴とする半導体装置。 - 前記第1の構造体と前記表層部分の下部との重畳量により、前記下方部位に印加される前記面内応力が調節されてなることを特徴とする請求項1に記載の半導体装置。

- 前記第1の構造体上に、前記表層部分を活性領域として画定する素子分離構造が当該第1の構造体と同一の材料で一体形成されていることを特徴とする請求項1に記載の半導体装置。

- 前記第1の構造体上に、前記表層部分を活性領域として画定する素子分離構造が当該第1の構造体と異なる材料で形成されていることを特徴とする請求項1に記載の半導体装置。

- 前記半導体基板は、絶縁層上に半導体層が設けられてなるSOI基板であり、前記半導体層の一部が前記表層部分とされていることを特徴とする請求項1に記載の半導体装置。

- 半導体基板と、

前記半導体基板上に形成された絶縁層と、

前記絶縁層上に形成されたシリコン層と、

前記シリコン層に形成されたソース電極及びドレイン電極と、

前記シリコン層上に形成されたゲート絶縁膜及びゲート電極と、

前記シリコン層の少なくとも底面の一部に接し、前記シリコン層に第1応力を加える素子分離絶縁膜と、

前記ソース電極、前記ドレイン電極及び前記ゲート電極を覆い、前記第1応力とは逆方向の応力である第2応力を前記シリコン層に加える応力絶縁膜と

を含むことを特徴とする半導体装置。 - 絶縁層上に半導体層が形成されてなるSOI基板において、前記半導体層の素子分離領域及び前記絶縁層の前記素子分離領域に整合し前記素子分離領域よりも幅広の第1の領域に溝を形成する工程と、

前記溝内に第1の絶縁材料を充填し、前記第1の領域に第1の構造体を、前記素子分離領域に素子分離構造を一体形成する工程と、

前記素子分離構造により画定された前記半導体膜の活性領域上に、トランジスタ構造を形成する工程と、

前記トランジスタ構造を覆うように、第2の絶縁材料からなる第2の構造体を形成する工程と

を含み、

前記第1及び第2の絶縁材料の密度をそれぞれ調節して前記第1及び第2の構造体を形成することにより、前記活性領域内の上方部位と下方部位とで逆方向の面内応力を印加することを特徴とする半導体装置の製造方法。 - 前記溝を形成するに際し、前記第1の領域の大きさを調節して、前記第1の構造体と前記活性領域の下部との重畳量により前記下方部位に印加される前記面内応力を制御することを特徴とする請求項7に記載の半導体装置の製造方法。

- 絶縁層上に半導体層が形成されてなるSOI基板において、前記半導体層の素子分離領域及び前記絶縁層の前記素子分離領域に整合し前記素子分離領域よりも幅広の第1の領域に溝を形成する工程と、

前記溝内に第1の絶縁材料を充填する工程と、

前記溝内の前記第1の絶縁材料のうち、前記素子分離領域に相当する部分を除去し、前記第1の領域に第1の構造体を形成する工程と、

前記第1の構造体上の前記溝内に、前記第1の絶縁材料と異なる第3の絶縁材料を充填し、前記素子分離領域に素子分離構造を一体形成する工程と、

前記素子分離構造により画定された前記半導体膜の活性領域上に、トランジスタ構造を形成する工程と、

前記トランジスタ構造を覆うように、第2の絶縁材料からなる第2の構造体を形成する工程と

を含み、

前記第1及び第2の絶縁材料の密度をそれぞれ調節して前記第1及び第2の構造体を形成することにより、前記活性領域内の上方部位と下方部位とで逆方向の面内応力を印加することを特徴とする半導体装置の製造方法。 - 前記溝を形成するに際し、前記第1の領域の大きさを調節して、前記第1の構造体と前記活性領域の下部との重畳量により前記下方部位に印加される前記面内応力を制御することを特徴とする請求項9に記載の半導体装置の製造方法。

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/JP2005/003394 WO2006092848A1 (ja) | 2005-03-01 | 2005-03-01 | 半導体装置及びその製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPWO2006092848A1 JPWO2006092848A1 (ja) | 2008-08-07 |

| JP4888385B2 true JP4888385B2 (ja) | 2012-02-29 |

Family

ID=36940894

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2007505767A Expired - Fee Related JP4888385B2 (ja) | 2005-03-01 | 2005-03-01 | 半導体装置及びその製造方法 |

Country Status (2)

| Country | Link |

|---|---|

| JP (1) | JP4888385B2 (ja) |

| WO (1) | WO2006092848A1 (ja) |

Families Citing this family (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4947914B2 (ja) * | 2005-04-06 | 2012-06-06 | ラピスセミコンダクタ株式会社 | 半導体装置およびその製造方法 |

| CN104465752B (zh) * | 2013-09-23 | 2017-06-23 | 中芯国际集成电路制造(上海)有限公司 | Nmos晶体管结构及其制造方法 |

| JP6254234B2 (ja) * | 2016-09-07 | 2017-12-27 | ラピスセミコンダクタ株式会社 | 半導体装置 |

| JP2018032877A (ja) * | 2017-11-29 | 2018-03-01 | ラピスセミコンダクタ株式会社 | 半導体装置 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003086708A (ja) * | 2000-12-08 | 2003-03-20 | Hitachi Ltd | 半導体装置及びその製造方法 |

| JP2004193596A (ja) * | 2002-12-12 | 2004-07-08 | Internatl Business Mach Corp <Ibm> | 応力チャネルを有する電界効果トランジスタおよびその製造方法 |

-

2005

- 2005-03-01 WO PCT/JP2005/003394 patent/WO2006092848A1/ja not_active Application Discontinuation

- 2005-03-01 JP JP2007505767A patent/JP4888385B2/ja not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2003086708A (ja) * | 2000-12-08 | 2003-03-20 | Hitachi Ltd | 半導体装置及びその製造方法 |

| JP2004193596A (ja) * | 2002-12-12 | 2004-07-08 | Internatl Business Mach Corp <Ibm> | 応力チャネルを有する電界効果トランジスタおよびその製造方法 |

Also Published As

| Publication number | Publication date |

|---|---|

| WO2006092848A1 (ja) | 2006-09-08 |

| JPWO2006092848A1 (ja) | 2008-08-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US10515856B2 (en) | Method of making a FinFET, and FinFET formed by the method | |

| US7575968B2 (en) | Inverse slope isolation and dual surface orientation integration | |

| TWI460859B (zh) | 半導體裝置及製造半導體裝置之方法 | |

| US7154118B2 (en) | Bulk non-planar transistor having strained enhanced mobility and methods of fabrication | |

| KR101811796B1 (ko) | 급경사 접합 프로파일을 갖는 소스/드레인 영역들을 구비하는 반도체 소자 및 그 제조방법 | |

| CN106033757B (zh) | 具有抗穿通层的高迁移率器件及其形成方法 | |

| US6882025B2 (en) | Strained-channel transistor and methods of manufacture | |

| CN105321822B (zh) | 用于非平面化合物半导体器件的沟道应变控制 | |

| US7928474B2 (en) | Forming embedded dielectric layers adjacent to sidewalls of shallow trench isolation regions | |

| JP5915181B2 (ja) | 半導体装置およびその製造方法 | |

| US7544548B2 (en) | Trench liner for DSO integration | |

| US20070235819A1 (en) | Semiconductor device and method for manufacturing the same | |

| US10204985B2 (en) | Structure and formation method of semiconductor device structure | |

| TW200929541A (en) | Transistor and method of fabricating the same | |

| JP6432090B2 (ja) | 異なる歪み状態を有するトランジスタチャネルを含む半導体層を製作する方法及び関連半導体層 | |

| CN111106160B (zh) | 半导体器件及其制造方法及包括该器件的电子设备 | |

| JP2007299951A (ja) | 半導体装置およびその製造方法 | |

| KR102465268B1 (ko) | 다양한 변형 상태를 갖는 핀 구조를 포함하는 반도체 구조를 제조하기 위한 방법, 및 관련 반도체 구조 | |

| JP2006332337A (ja) | 半導体装置及びその製造方法 | |

| US20090065807A1 (en) | Semiconductor device and fabrication method for the same | |

| US20090315115A1 (en) | Implantation for shallow trench isolation (STI) formation and for stress for transistor performance enhancement | |

| CN105448832A (zh) | 一种半导体器件的制作方法 | |

| KR20050051448A (ko) | 에스오아이 기판들을 제조하는 방법들, 이를 사용하여반도체 소자들을 제조하는 방법들 및 그에 의해 제조된반도체 소자들 | |

| US20150123211A1 (en) | NARROW DIFFUSION BREAK FOR A FIN FIELD EFFECT (FinFET) TRANSISTOR DEVICE | |

| US8748239B2 (en) | Method of fabricating a gate |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A711 | Notification of change in applicant |

Free format text: JAPANESE INTERMEDIATE CODE: A712 Effective date: 20080731 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110419 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20110620 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20110809 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20111011 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20111115 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20111128 |

|

| R150 | Certificate of patent or registration of utility model |

Ref document number: 4888385 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R150 Free format text: JAPANESE INTERMEDIATE CODE: R150 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20141222 Year of fee payment: 3 |

|

| S111 | Request for change of ownership or part of ownership |

Free format text: JAPANESE INTERMEDIATE CODE: R313111 |

|

| R350 | Written notification of registration of transfer |

Free format text: JAPANESE INTERMEDIATE CODE: R350 |

|

| LAPS | Cancellation because of no payment of annual fees |