JP4500530B2 - Insulated gate semiconductor device and manufacturing method thereof - Google Patents

Insulated gate semiconductor device and manufacturing method thereof Download PDFInfo

- Publication number

- JP4500530B2 JP4500530B2 JP2003375098A JP2003375098A JP4500530B2 JP 4500530 B2 JP4500530 B2 JP 4500530B2 JP 2003375098 A JP2003375098 A JP 2003375098A JP 2003375098 A JP2003375098 A JP 2003375098A JP 4500530 B2 JP4500530 B2 JP 4500530B2

- Authority

- JP

- Japan

- Prior art keywords

- region

- semiconductor device

- trench

- floating

- floating region

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Landscapes

- Electrodes Of Semiconductors (AREA)

- Insulated Gate Type Field-Effect Transistor (AREA)

Description

本発明は,トレンチゲート構造を有する絶縁ゲート型半導体装置およびその製造方法に関する。さらに詳細には,半導体層にかかる電界を緩和することにより,高耐圧化と低オン抵抗化との両立を図った絶縁ゲート型半導体装置およびその製造方法に関するものである。 The present invention relates to an insulated gate semiconductor device having a trench gate structure and a method for manufacturing the same. More specifically, the present invention relates to an insulated gate semiconductor device that achieves both high breakdown voltage and low on-resistance by relaxing an electric field applied to a semiconductor layer, and a method for manufacturing the same.

従来から,パワーデバイス用の絶縁ゲート型半導体装置として,トレンチゲート構造を有するトレンチゲート型半導体装置が提案されている。このトレンチゲート型半導体装置では,一般的に高耐圧化と低オン抵抗化とがトレードオフの関係にある。 Conventionally, a trench gate type semiconductor device having a trench gate structure has been proposed as an insulated gate type semiconductor device for power devices. In this trench gate type semiconductor device, a high breakdown voltage and a low on-resistance are generally in a trade-off relationship.

この点に着目したトレンチゲート型半導体装置としては,例えば特許文献1に開示されているものがある。このトレンチゲート型半導体装置は,概略,図26に示すように構成されている。すなわち,図26中の上面側にN+ ソース領域31が設けられ,下側にN+ ドレイン領域11が設けられている。そして,それらの間には上面側から,Pボディ領域41およびN- ドリフト領域12が設けられている。さらに,半導体装置の上面側の一部を掘り込むことで形成されたトレンチ21が設けられている。また,トレンチ21には,ゲート電極22が内蔵されている。また,トレンチ21の直下にPフローティング領域50が設けられている。また,ゲート電極22は,トレンチ21の壁面に形成されたゲート絶縁膜24によりPボディ領域41から絶縁されている。

As a trench gate type semiconductor device paying attention to this point, for example, there is one disclosed in

このトレンチゲート型半導体装置では,ゲート電圧のスイッチオフ時に,Pボディ領域41とN- ドリフト領域12との間のPN接合箇所からN+ ドレイン領域11に向けて空乏層が広がっていくとともにPフローティング領域50の下端部からもN+ ドレイン領域11に向けて空乏層が広がっていく。すなわち,Pフローティング領域50がN- ドリフト領域12の空乏化を促進するのである。これにより,ドレイン−ソース間の高耐圧化を図ることができるとされている。

In this trench gate type semiconductor device, when the gate voltage is switched off, a depletion layer spreads from the PN junction between the

また,この他のトレンチゲート型半導体装置としては,例えば特許文献2に記載されているものがある。このトレンチゲート型半導体装置には,図27に示すようにトレンチ21から離れた位置にPフローティング領域59が設けられている。このPフローティング領域59によっても,図26の絶縁ゲート型半導体装置と同様にドレイン−ソース間の高耐圧化を図ることができるとされている。

As another trench gate type semiconductor device, for example, there is one described in

前記した図27の半導体装置は,次のような手順で作製される。まず,N+ ドレイン領域11となるN+ 基板上に,N- 型ドリフト領域12となるN- 型シリコン層をエピタキシャル成長により形成する。このときN- 型シリコン層は,図27中のZの位置まで形成する。次に,Pフローティング領域59をイオン注入等により形成する。次に,再度エピタキシャル成長を行って残りのN- 型シリコン層を形成する。これにより,Pフローティング領域59がN- ドリフト領域12に完全に囲まれた半導体装置が形成される。なお,これらの工程を繰り返し行うことで,Pフローティング領域59を異なる深さで幾つも形成することができる。

The semiconductor device shown in FIG. 27 is manufactured by the following procedure. First, an N − type silicon layer to be an N −

また,これらのトレンチゲート型半導体装置の終端エリアは,一般的に図28に示すような構造を有している。すなわち終端エリアには,トレンチ21の深さと同等かもしくはそれ以上の深さのP終端拡散領域61が形成されている。これにより,ゲート電圧のスイッチオフ時に,P終端拡散領域61の周辺からも空乏層が形成される。これにより,終端部における電界の集中を緩和している。

しかしながら,前記した図26の半導体装置には,次のような問題点があった。すなわち,Pフローティング領域50は,トレンチ21の底部からのイオン注入により形成される。そのため,トレンチ21の底部には少なからず損傷が生じている。それ故,そのままゲート絶縁膜24を形成すると,素子特性の低下や信頼性の低下といった不具合を招いてしまう。また,ゲート電極22がPフローティング領域50と対面している。そのためオン時に,ゲート電極22内で,Pボディ領域41と対面している部分と,Pフローティング領域50と対面している部分とで電荷が分散してしまう。このため,オン抵抗が大きくなってしまう。

However, the semiconductor device shown in FIG. 26 has the following problems. That is, the

一方,図27の半導体装置では,Pフローティング領域59がトレンチ21から離れて形成されているため,上記の問題を回避して高耐圧化を図ることができる。しかしながら,N- ドリフト領域12に完全に囲まれたPフローティング領域54を形成する際には,少なくとも2回のN- 型シリコン層の形成工程(エピタキシャル成長工程)が必要であり,作製するのに非常に手間がかかる。

On the other hand, in the semiconductor device of FIG. 27, since the

また,終端エリアの電界の集中を緩和するためには,セルエリアに形成された各Pフローティング領域と厚さが異なるP終端拡散領域61を形成する工程が必要である。そのため,工程数が多く,作製するのに手間がかかる。また,熱負荷が大きいことからN- 型ドリフト領域12(エピタキシャル層)の不純物が拡散してその濃度にばらつきが生じる。そして,それを補うためにはN- 型ドリフト領域12の厚さを厚くする必要があり,その結果オン抵抗が大きくなってしまう。

Further, in order to alleviate the concentration of the electric field in the termination area, it is necessary to form a P

本発明は,前記した従来のトレンチゲート型半導体装置が有する問題点を少なくとも1つ解決するためになされたものである。すなわちその課題とするところは,高耐圧化と低オン抵抗化とを両立させ,簡便に作製することができる絶縁ゲート型半導体装置およびその製造方法を提供することにある。 The present invention has been made to solve at least one of the problems of the conventional trench gate type semiconductor device. That is, an object of the present invention is to provide an insulated gate semiconductor device and a method for manufacturing the same that can be easily manufactured while achieving both high breakdown voltage and low on-resistance.

この課題の解決を目的としてなされた絶縁ゲート型半導体装置は,半導体基板内の上面側に位置し第1導電型半導体であるボディ領域と,ボディ領域の下面と接し第2導電型半導体であるドリフト領域と,半導体基板の上面からボディ領域を貫通しその底部がボディ領域の下面より下方に位置するトレンチ部とを有する絶縁ゲート型半導体装置であって,ドリフト領域に囲まれるとともに第1導電型半導体であるフローティング領域を有し,トレンチ部の底部は,フローティング領域内に位置し,トレンチ部内には,絶縁物を堆積してなる堆積絶縁層と,堆積絶縁層上に位置し,ボディ領域と対面するゲート電極とが形成されており,堆積絶縁層の上端は,フローティング領域の上端よりも上方に位置し,ボディ領域の下面とフローティング領域の上端との間隔は,堆積絶縁層の下端とフローティング領域の下端との間隔よりも広く,ゲート電極の下端と堆積絶縁層の下端との間隔は,ボディ領域の下面とフローティング領域の上端との間隔よりも広く,堆積絶縁層の厚さは,その厚さ方向において,電界のピークが少なくとも2箇所に形成される厚さのものである。 An insulated gate semiconductor device for solving this problem includes a body region which is a first conductivity type semiconductor located on the upper surface side in a semiconductor substrate, and a drift which is a second conductivity type semiconductor in contact with the lower surface of the body region. An insulated gate semiconductor device having a region and a trench portion penetrating the body region from the upper surface of the semiconductor substrate and having a bottom portion located below the lower surface of the body region, and is surrounded by a drift region and is a first conductivity type semiconductor The bottom of the trench is located in the floating region, and in the trench is a deposited insulating layer formed by depositing an insulator, and is located on the deposited insulating layer and faces the body region. a gate electrode is formed, the upper end of the deposited insulating layer is located above the upper end of the floating region, the lower surface of the body region and the floating The distance between the lower end of the deposited insulating layer and the lower end of the floating region is larger than the distance between the lower end of the gate electrode and the lower end of the deposited insulating layer. The thickness of the deposited insulating layer is wider than the interval of (2), and the thickness is such that the electric field peaks are formed in at least two places in the thickness direction .

すなわち,本発明の絶縁ゲート型半導体装置は,ドリフト領域に囲まれたフローティング領域を有している。このフローティング領域により,オフ時のドリフト領域の空乏化を促進することができる。また,電界のピークを複数箇所に形成することができ,最大ピーク値の低減を図ることができる。また,トレンチ部の中に堆積絶縁層を有している。これにより,ゲート絶縁膜およびゲート電極は,トレンチ部の損傷の影響を受けない。よって,素子特性の劣化および信頼性の低下が抑止される。また,その堆積絶縁層の上端は,フローティング領域の上端よりも上方に位置している。これにより,ゲート電極とフローティング領域との対面が抑止され,オン抵抗の増大が防止される。 That is, the insulated gate semiconductor device of the present invention has a floating region surrounded by a drift region. This floating region can promote depletion of the drift region at the off time. In addition, electric field peaks can be formed at a plurality of locations, and the maximum peak value can be reduced. In addition, a deposited insulating layer is provided in the trench portion. As a result, the gate insulating film and the gate electrode are not affected by the damage of the trench portion. Therefore, deterioration of element characteristics and deterioration of reliability are suppressed. The upper end of the deposited insulating layer is located above the upper end of the floating region. As a result, the facing of the gate electrode and the floating region is suppressed, and an increase in on-resistance is prevented.

また,本発明の絶縁ゲート型半導体装置は,フローティング領域の上端よりも上方に位置し,ドリフト領域に囲まれるとともに第1導電型半導体である中間フローティング領域を有し,トレンチ部は,中間フローティング領域を貫通しており,堆積絶縁層の上端は,中間フローティング領域の上端よりも上方に位置することとするとよりよい。 The insulated gate semiconductor device of the present invention is located above the upper end of the floating region, is surrounded by the drift region and has an intermediate floating region which is the first conductivity type semiconductor, and the trench portion has the intermediate floating region. It is better that the upper end of the deposited insulating layer is located above the upper end of the intermediate floating region.

すなわち,ボディ領域とフローティング領域との間の位置にフローティング領域と同様の作用を有する中間フローティング領域を有している。これにより,電界のピークを少なくとも3箇所に形成でき,より最大ピーク値の低減を図ることができる。よって,より高耐圧化および低オン抵抗化を図ることができる。なお,中間フローティング領域は,1つに限らず複数設けてもよい。中間フローティング領域が多ければ多いほど電界のピークを数多く形成でき,より最大ピーク値の低減を図ることができる。 That is, an intermediate floating region having the same action as the floating region is provided between the body region and the floating region. As a result, electric field peaks can be formed in at least three locations, and the maximum peak value can be further reduced. Therefore, higher breakdown voltage and lower on-resistance can be achieved. Note that the number of intermediate floating regions is not limited to one, and a plurality of intermediate floating regions may be provided. The more intermediate floating regions, the more electric field peaks can be formed and the maximum peak value can be further reduced.

また,本発明の絶縁ゲート型半導体装置は,半導体基板の上面からボディ領域を貫通しその底部がボディ領域の下面より下方に位置し,内側が絶縁物で充填された補助トレンチ部と,ドリフト領域に囲まれるとともに第1導電型半導体である補助フローティング領域を有し,補助トレンチ部の底部は,補助フローティング領域内に位置することとするとよりよい。すなわち,フローティング領域と同様の作用を有する補助フローティング領域が複数形成される。これにより,補助フローティング領域を含むフローティング領域の密度が高いことから,フローティング領域等のサイズ等の製造マージンが大きい。 The insulated gate semiconductor device according to the present invention includes an auxiliary trench portion penetrating the body region from the upper surface of the semiconductor substrate and having a bottom portion located below the lower surface of the body region and filled with an insulator inside, and a drift region. It is better to have an auxiliary floating region that is surrounded by the first conductive type semiconductor and that the bottom of the auxiliary trench portion is located within the auxiliary floating region. That is, a plurality of auxiliary floating regions having the same action as the floating region are formed. Thereby, since the density of the floating region including the auxiliary floating region is high, the manufacturing margin such as the size of the floating region is large.

また,本発明の絶縁ゲート型半導体装置は,トレンチ部の深さと補助トレンチ部の深さとが異なることとするとよりよい。これにより,フローティング領域と補助フローティング領域とが厚さ方向に異なる位置に設けられる。従って,電界のピークを3箇所に形成でき,より最大ピーク値の低減を図ることができる。 In the insulated gate semiconductor device of the present invention, it is better that the depth of the trench portion and the depth of the auxiliary trench portion are different. Thereby, the floating region and the auxiliary floating region are provided at different positions in the thickness direction. Therefore, electric field peaks can be formed at three locations, and the maximum peak value can be further reduced.

一方,本発明の絶縁ゲート型半導体装置は,トレンチ部の深さと補助トレンチ部の深さとが同一であるとしてもよい。トレンチ部と補助トレンチ部とが同一の深さであることから,トレンチ部と補助トレンチ部とを同一の工程で形成することができる。そのため,工程数を削減することができる。また,隣り合うフローティングの間の距離が短く,ドリフト領域の濃度が高くても空乏層を確実に繋げることができる。そのため,低オン抵抗化を図ることができる。また,1つあたりのフローティング領域のサイズは小さくて済む。また,熱拡散処理も同一の工程で行うことができるため,不純物の拡散が少なく熱拡散処理によるオン抵抗の低下を抑制することができる。なお,ここでいう「同一」の深さとは,正確に一致していなければならないことを意味するものではない。すなわち,トレンチ形成時に生じる深さの多少のずれは,同一の範囲内である。 On the other hand, in the insulated gate semiconductor device of the present invention, the depth of the trench portion and the depth of the auxiliary trench portion may be the same. Since the trench part and the auxiliary trench part have the same depth, the trench part and the auxiliary trench part can be formed in the same process. Therefore, the number of processes can be reduced. Moreover, even if the distance between adjacent floating regions is short and the concentration of the drift region is high, the depletion layer can be connected reliably. Therefore, a low on-resistance can be achieved. Also, the size of each floating area can be small. In addition, since the thermal diffusion process can be performed in the same process, the diffusion of impurities is small and a decrease in on-resistance due to the thermal diffusion process can be suppressed. Note that the “same” depth here does not mean that it must match exactly. That is, a slight shift in the depth that occurs during trench formation is within the same range.

また,本発明の絶縁ゲート型半導体装置は,半導体基板の上面からボディ領域を貫通しその底部がボディ領域の下面より下方に位置し,内側が絶縁物で充填された補助トレンチ部と,ドリフト領域に囲まれるとともに第1導電型半導体である補助フローティング領域を有し,補助トレンチ部の底部は,補助フローティング領域内に位置するものであってもよい。 The insulated gate semiconductor device according to the present invention includes an auxiliary trench portion penetrating the body region from the upper surface of the semiconductor substrate and having a bottom portion located below the lower surface of the body region and filled with an insulator inside, and a drift region. an auxiliary floating region is a first conductive type semiconductor with surrounded by the bottom of the auxiliary trench portion may be I der those located in the auxiliary floating region.

すなわち,本発明の絶縁ゲート型半導体装置は,ドリフト領域に囲まれた補助フローティング領域を有している。この補助フローティング領域により,オフ時のドリフト領域の空乏化を促進することができる。また,補助フローティング領域は,補助フローティング領域用に形成された補助トレンチ部の下方に設けられている。そのため,補助フローティング領域の設計自由度は高い。一方,ゲート電極を内蔵するトレンチ部は,従来と同様の製造方法にて形成することができる。そのため,底部からのイオン注入はなく,素子特性の劣化および信頼性の低下等の問題は生じない。 That is, the insulated gate semiconductor device of the present invention has an auxiliary floating region surrounded by a drift region. This auxiliary floating region can promote the depletion of the drift region at the off time. The auxiliary floating region is provided below an auxiliary trench portion formed for the auxiliary floating region. For this reason, the design flexibility of the auxiliary floating region is high. On the other hand, the trench portion containing the gate electrode can be formed by the same manufacturing method as in the prior art. Therefore, there is no ion implantation from the bottom, and problems such as deterioration of device characteristics and deterioration of reliability do not occur.

また,本発明の絶縁ゲート型半導体装置は,補助フローティング領域の上端よりも上方に位置し,ドリフト領域に囲まれるとともに第1導電型半導体である補助中間フローティング領域を有し,補助トレンチ部は,中間補助フローティング領域を貫通しており,堆積絶縁層の上端は,中間補助フローティング領域の上端よりも上方に位置することとするとよりよい。これにより,電界のピークを少なくとも3箇所に形成でき,より最大ピーク値の低減を図ることができる。よって,より高耐圧化および低オン抵抗化を図ることができる。 The insulated gate semiconductor device of the present invention is located above the upper end of the auxiliary floating region, and is surrounded by the drift region and has an auxiliary intermediate floating region that is the first conductivity type semiconductor. It is better if the intermediate auxiliary floating region is penetrated and the upper end of the deposited insulating layer is located above the upper end of the intermediate auxiliary floating region. As a result, electric field peaks can be formed in at least three locations, and the maximum peak value can be further reduced. Therefore, higher breakdown voltage and lower on-resistance can be achieved.

また,本発明の絶縁ゲート型半導体装置は,補助トレンチ部とゲート電極を挟んで対向し,半導体基板の上面からボディ領域を貫通しその底部が前記ボディ領域の下面より下方に位置し,内側が絶縁物で充填された第2補助トレンチ部と,ドリフト領域に囲まれるとともに第1導電型半導体である第2補助フローティング領域を有し,補助トレンチ部と第2補助トレンチ部とは,互いに深さが異なることとするとよりよい。 Further, the insulated gate semiconductor device of the present invention is opposed to the auxiliary trench portion with the gate electrode interposed therebetween, penetrates the body region from the upper surface of the semiconductor substrate, the bottom portion is located below the lower surface of the body region, and the inner side is A second auxiliary trench portion filled with an insulator and a second auxiliary floating region which is surrounded by the drift region and is a first conductivity type semiconductor are provided, and the auxiliary trench portion and the second auxiliary trench portion are deep with respect to each other. It is better if they are different.

すなわち,補助トレンチ部と第2補助トレンチ部との深さが互いに異なることから,補助フローティング領域と第2フローティング領域とは厚さ方向の位置が互いに異なる。よって,電界のピークを3箇所に形成でき,最大ピーク値の低減を図ることができる。また,補助フローティング領域と第2フローティング領域とは同一の熱拡散処理にて形成することができるため,熱負荷が小さい。 That is, since the auxiliary trench portion and the second auxiliary trench portion have different depths, the auxiliary floating region and the second floating region have different positions in the thickness direction. Therefore, electric field peaks can be formed at three locations, and the maximum peak value can be reduced. Further, since the auxiliary floating region and the second floating region can be formed by the same thermal diffusion process, the thermal load is small.

また,本発明の絶縁ゲート型半導体装置の補助トレンチ部は,半導体基板の上方から見てドット形状に構成されていることとするとよりよい。これにより,電流経路が広く低オン抵抗化を図ることができる。 Further, it is better that the auxiliary trench portion of the insulated gate semiconductor device of the present invention is configured in a dot shape when viewed from above the semiconductor substrate. As a result, the current path is wide and low on-resistance can be achieved.

また,本発明の絶縁ゲート型半導体装置は,セル領域の周辺領域に位置し,内側が絶縁物で充填された終端トレンチ部と,ドリフト領域に囲まれるとともに第1導電型半導体である終端フローティング領域とを有し,終端トレンチ部の底部は,終端フローティング領域内に位置していることとするとよりよい。 In addition, the insulated gate semiconductor device of the present invention is located in the peripheral region of the cell region, and is surrounded by a termination trench portion filled with an insulator, and a termination floating region that is surrounded by a drift region and is a first conductivity type semiconductor. More preferably, the bottom of the termination trench is located in the termination floating region.

すなわち,終端エリアにも,フローティング領域と同様の作用を有する終端フローティング領域を設けている。これにより,終端エリアにおいても高耐圧化が図られている。また,終端フローティング領域は,セルエリア内のフローティング領域と同等のサイズである。従って,コンパクトであり,サイズの制御性もよい。また,終端フローティング領域は,フローティング領域と同一の工程にて形成することができることから,その形成も容易である。さらに,同一の工程にて形成されることから,従来の半導体装置と比較して熱負荷が小さい。 That is, a termination floating region having the same action as the floating region is provided also in the termination area. As a result, a high breakdown voltage is also achieved in the termination area. The terminal floating area is the same size as the floating area in the cell area. Therefore, it is compact and has good controllability of size. Further, since the terminal floating region can be formed in the same process as the floating region, the formation thereof is easy. Furthermore, since it is formed in the same process, the thermal load is small compared with the conventional semiconductor device.

また,本発明の絶縁ゲート型半導体装置の製造方法は,半導体基板内の上面側に位置し第1導電型半導体であるボディ領域と,前記ボディ領域の下面と接し第2導電型半導体であるドリフト領域と,ドリフト領域に囲まれるとともに第1導電型半導体であるフローティング領域と,半導体基板の上面からボディ領域を貫通しその底部がボディ領域より下方であってフローティング領域内に位置するトレンチ部と,トレンチ部の内側に位置し,フローティング領域と接し,絶縁物を堆積してなる堆積絶縁層と,トレンチ部の内側に位置しボディ領域と対面するゲート電極とを有し,堆積絶縁層の上端は,フローティング領域の上端よりも上方に位置し,ボディ領域の下面とフローティング領域の上端との間隔は,堆積絶縁層の下端とフローティング領域の下端との間隔よりも広く,ゲート電極の下端と堆積絶縁層の下端との間隔は,ボディ領域の下面とフローティング領域の上端との間隔よりも広く,堆積絶縁層の厚さは,その厚さ方向において,電界のピークが少なくとも2箇所に形成される厚さである絶縁ゲート型半導体装置の製造方法であって,ドリフト領域およびボディ領域が形成された半導体基板内にトレンチ部を形成するトレンチ部形成工程と,トレンチ部形成工程にて形成されたトレンチ部の底部から不純物を注入する不純物注入工程と,不純物注入工程にて不純物を注入した後に,トレンチ部内に絶縁物を堆積させる絶縁物堆積工程と,絶縁物堆積工程にて絶縁物を堆積させた後に,熱拡散処理を行うことでフローティング領域を形成するフローティング領域形成工程とを含んでいる。 The method of manufacturing an insulated gate semiconductor device according to the present invention includes a body region that is located on the upper surface side of the semiconductor substrate and is a first conductivity type semiconductor, and a drift that is in contact with the lower surface of the body region and is a second conductivity type semiconductor. a region, a trench portion located floating region and the floating region, the bottom through the body region from the upper surface of the semiconductor substrate is a lower than the body region a first conductivity type semiconductor with surrounded by the drift region, located inside the trench portion, the floating area and contact, and the deposited insulating layer formed by depositing an insulating material, located inside the trench portion have a gate electrode facing the body region, the upper end of the deposited insulating layer , Located above the upper end of the floating region. The distance between the lower surface of the body region and the upper end of the floating region is The distance between the lower end of the gate region and the lower end of the deposited insulating layer is wider than the distance between the lower surface of the body region and the upper end of the floating region, and the thickness of the deposited insulating layer is A method of manufacturing an insulated gate semiconductor device having a thickness in which at least two electric field peaks are formed in the thickness direction, wherein a trench portion is formed in a semiconductor substrate in which a drift region and a body region are formed. A trench portion forming step, an impurity implantation step for injecting impurities from the bottom of the trench portion formed in the trench portion formation step, and an insulator for depositing an insulator in the trench portion after the impurities are implanted in the impurity implantation step. Floating region forming process that forms a floating region by performing thermal diffusion treatment after depositing an insulator in the material deposition step and the insulator deposition step It includes the door.

この製造方法では,エピタキシャル成長等によってドリフト領域を形成した後,イオン注入等の不純物導入技術と熱拡散によりボディ領域を形成した半導体基板を出発材としている。そして,トレンチ部形成工程にて,ボディ領域を貫通するトレンチ部を形成している。そして,フローティング領域形成工程にて,そのトレンチ部から不純物を注入することによりフローティング領域を形成している。すなわち,フローティング領域がドリフト領域およびボディ領域の形成後に形成されるため,フローティング領域の形成後に再度エピタキシャル成長により単結晶シリコン層を形成する必要がない。従って,フローティング領域を有する絶縁ゲート型半導体装置を簡便に作製することができる。 In this manufacturing method, a drift region is formed by epitaxial growth or the like, and then a semiconductor substrate in which a body region is formed by impurity introduction technology such as ion implantation and thermal diffusion is used as a starting material. And the trench part which penetrates the body region is formed in the trench part forming step. In the floating region forming step, the floating region is formed by implanting impurities from the trench portion. That is, since the floating region is formed after the formation of the drift region and the body region, it is not necessary to form a single crystal silicon layer again by epitaxial growth after the formation of the floating region. Therefore, an insulated gate semiconductor device having a floating region can be easily manufactured.

また,本発明の絶縁ゲート型半導体装置の製造方法は,不純物注入工程にて不純物を注入した後に,トレンチ部の底部をさらに掘り下げるトレンチ部深堀工程と,トレンチ部深堀工程にて掘り下げられたトレンチ部の底部から再度不純物を注入する不純物再注入工程とを含むこととするとよりよい。これにより,1回のエピタキシャル成長により形成されたウェーハに対してその厚さ方向に複数段のフローティング領域を設けることができる。従って,簡便に高耐圧化と低オン抵抗化とを両立させることができる。 In addition, the method of manufacturing an insulated gate semiconductor device according to the present invention includes a trench portion deepening step for further deepening the bottom of the trench portion after the impurity is implanted in the impurity implantation step, and a trench portion deepened in the trench portion deepening step. It is better to include an impurity reinjection step of injecting impurities again from the bottom of the substrate. Thereby, a plurality of floating regions can be provided in the thickness direction of a wafer formed by one epitaxial growth. Therefore, it is possible to easily achieve both high breakdown voltage and low on-resistance.

本発明によれば,ドリフト領域に囲まれたフローティング領域により,高耐圧化と低オン抵抗化の両立を図ることができる。また,堆積絶縁層により,不純物の注入による影響を回避することができる。また,エピタキシャル成長によるシリコン層の形成を繰り返すことなくフローティング領域を形成することができる。よって,高耐圧化と低オン抵抗化とを両立させ,簡便に作製することができる絶縁ゲート型半導体装置およびその製造方法が提供されている。 According to the present invention, both a high breakdown voltage and a low on-resistance can be achieved by the floating region surrounded by the drift region. In addition, the deposited insulating layer can avoid the influence of impurity implantation. In addition, the floating region can be formed without repeating the formation of the silicon layer by epitaxial growth. Therefore, an insulated gate semiconductor device and a method for manufacturing the same that can be easily manufactured while achieving both high breakdown voltage and low on-resistance are provided.

以下,本発明を具体化した実施の形態について,添付図面を参照しつつ詳細に説明する。なお,本実施の形態は,絶縁ゲートへの電圧印加により,ドレイン−ソース間(以下,「DS間」とする)の導通をコントロールするパワーMOSに本発明を適用したものである。 DESCRIPTION OF THE PREFERRED EMBODIMENTS Embodiments embodying the present invention will be described below in detail with reference to the accompanying drawings. In the present embodiment, the present invention is applied to a power MOS that controls conduction between a drain and a source (hereinafter referred to as “between DS”) by applying a voltage to an insulated gate.

[第1の形態]

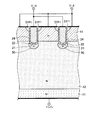

第1の形態に係る絶縁ゲート型半導体装置100(以下,「半導体装置100」とする)は,図1の断面図に示す構造を有している。なお,図1中,図26で示した従来の半導体装置と同一記号の構成要素は,その構成要素と同一機能を有するものである。また,本明細書においては,出発基板と,出発基板上にエピタキシャル成長により形成した単結晶シリコンの部分とを合わせた全体を半導体基板と呼ぶこととする。

[First embodiment]

An insulated

半導体装置100では,半導体基板内における図1中の上面側に,N+ ソース領域31およびコンタクト抵抗を下げるために高濃度に形成されたP+ ソース領域32が設けられている。一方,下面側にはN+ ドレイン領域11が設けられている。それらの間には上面側から,P- ボディ領域41およびN- ドリフト領域12が設けられている。なお,P- ボディ領域41およびN- ドリフト領域12を合わせた領域(以下,「エピタキシャル層」とする)の厚さは,およそ5.5μm(そのうち,P- ボディ領域41の厚さは,およそ1.2μm)である。

In the

また,半導体基板の上面側の一部を掘り込むことによりトレンチ21が形成されている。トレンチ21の深さはおよそ3.2μmであり,P- ボディ領域41を貫通している。トレンチ21の底部には,絶縁物の堆積による堆積絶縁層23が形成されている。具体的に堆積絶縁層23は,トレンチ21の底部からおよそ1.7μmの高さの位置まで酸化シリコンが堆積してできたものである。さらに,堆積絶縁層23上には,導体(例えば,ポリシリコン)の堆積によるゲート電極22が形成されている。ゲート電極22の下端は,P- ボディ領域41の下面より下方に位置している。そして,ゲート電極22は,トレンチ21の壁面に形成されているゲート絶縁膜24を介して,半導体基板のN+ ソース領域31およびP- ボディ領域41と対面している。すなわち,ゲート電極22は,ゲート絶縁膜24によりN+ ソース領域31およびP- ボディ領域41から絶縁されている。このような構造を持つ半導体装置100では,ゲート電極22への電圧印加によりP- ボディ領域41にチャネル効果を生じさせ,もってN+ ソース領域31とN+ ドレイン領域11との間の導通をコントロールしている。

Further, a

さらに,半導体基板には,N- ドリフト領域12に囲まれたPフローティング領域51が形成されている。Pフローティング領域51の断面は,図1の断面図に示したように,トレンチ21の底部を中心とした半径0.6μmの略円形形状となっている。また,各トレンチ21は,およそ3.0μmのピッチで形成されている。従って,隣り合うPフローティング領域51,51間には,十分なスペースがある。よって,オン状態において,Pフローティング領域51の存在がドレイン電流に対する妨げとなることはない。また,Pフローティング領域51の半径(およそ0.6μm)は,堆積絶縁層23の厚さ(およそ1.7μm)の1/2以下である。従って,堆積絶縁層23の上端は,Pフローティング領域51の上端よりも上方に位置する。よって,堆積絶縁層23上に堆積するゲート電極22とPフローティング領域51とは対面していない。

Further, a

本形態の半導体装置100は,ゲート電極22を内蔵するトレンチ21の下方にPフローティング領域51が設けられていることにより,それを有しない絶縁ゲート型半導体装置と比較して,次のような特性を有する。すなわち,ゲート電圧のスイッチオフ時には,DS間の電圧によって,N- ドリフト領域12内ではP- ボディ領域41との間のPN接合箇所から空乏層が形成される。そして,そのPN接合箇所の近傍が電界強度のピークとなる。空乏層の先端がPフローティング領域51に到達すると,Pフローティング領域51がパンチスルー状態となってその電位が固定される。また,DS間の印加電圧が高い場合には,Pフローティング領域51の下端部からも空乏層が形成される。そして,P- ボディ領域41との間のPN接合箇所とは別に,Pフローティング領域51の下端部の近傍も電界強度のピークとなる。すなわち,電界のピークを2箇所に形成でき,最大ピーク値の低減を図ることができる。よって,高耐圧化が図られる。また,高耐圧であることから,N- ドリフト領域12の不純物濃度を上げて低オン抵抗化を図ることができる。

The

また,半導体装置100は,トレンチ21内に堆積絶縁層23が設けられていることにより次のような特性を有する。すなわち,Pフローティング領域51は,後述するようにトレンチ21の底部からのイオン注入等により形成されるため,トレンチ21の底部には少なからず損傷が生じている。しかしながら,堆積絶縁層23の存在によって,トレンチ21の底部の損傷による影響を回避し,素子特性の劣化や信頼性の低下といった不具合を防止している。また,堆積絶縁層23にてゲート電極22とPフローティング領域51との対面による影響を緩和し,P- ボディ領域41内のオン抵抗を低減している。また,堆積絶縁層23を設けない場合と比較して,ゲート電極22が小さいため,ゲート−ドレイン間容量Cgdが小さく,スイッチングスピードが速い。

In addition, the

なお,前述したPフローティング領域を半導体装置の厚さ方向に複数設けてもよい。例えば,図2に示すようにPフローティング領域を2段設けた構造としてもよい。図2に示した半導体装置101では,図1に示した半導体装置100よりも深い深さ(8.5μm程度)のエピタキシャル層およびトレンチ21が設けられている。そして,トレンチ21の底部を中心とするPフローティング領域51と,Pフローティング領域51とP- ボディ領域41との間に位置するPフローティング領域52とが設けられている。これにより,P- ボディ領域41との間のPN接合箇所から形成された空乏層は,一旦Pフローティング領域52に到達した後にPフローティング領域51に到達する。そのため,P- ボディ領域41との間のPN接合箇所とは別に,Pフローティング領域52の下端部およびPフローティング領域51の下端部でも電界強度のピークとなる。従って,電界のピークを3箇所に形成でき,より最大ピーク値の低減を図ることができる。なお,Pフローティング領域51とP- ボディ領域41との間に位置するPフローティング領域52の数を増やすほど電界のピーク箇所を多くすることができる。そのため,Pフローティング領域52の数が多いほど高耐圧化および低オン抵抗化を図ることができる。

A plurality of the P floating regions described above may be provided in the thickness direction of the semiconductor device. For example, as shown in FIG. 2, a structure in which two P floating regions are provided may be employed. In the

また,Pフローティング領域を半導体装置の終端エリアに設けてもよい。例えば,図3に示すように終端エリアにトレンチ62およびPフローティング領域52を設けた構造としてもよい。図3に示した半導体装置102では,トレンチ62内が絶縁物(酸化シリコン等)で充填されている。また,Pフローティング領域51と同様の作用を有するPフローティング領域53が形成されている。半導体装置102では,トレンチ62およびそれに対応するPフローティング領域53によってセルエリアと同様に高耐圧化を図っている。また,Pフローティング領域53のサイズが従来のP終端拡散領域61と比較して小さい。そのため,そのサイズの制御性がよく,半導体装置自体のコンパクト化を図ることができる。また,Pフローティング領域53は,従来の半導体装置(図28参照)のP終端拡散領域61と比較して熱負荷が小さい。そのため,N- ドリフト領域12(エピタキシャル層)の厚さを薄くでき,オン抵抗を小さくすることができる。

Further, the P floating region may be provided in the terminal area of the semiconductor device. For example, as shown in FIG. 3, a structure in which a

次に,図1に示した半導体装置100の製造プロセスを図4により説明する。まず,N+ ドレイン領域11となるN+ 基板上に,N- 型シリコン層をエピタキシャル成長により形成する。このN- 型シリコン層(エピタキシャル層)は,N- ドリフト領域12,P- ボディ領域41,N+ ソース領域31の各領域となる部分である。そして,その後のイオン注入等によりP- ボディ領域41およびN+ ソース領域31が形成される。これにより,図4(a)に示すようなN+ ドレイン領域11上にエピタキシャル層を有する半導体基板が作製される。

Next, a manufacturing process of the

次に,図4(b)に示すようにP- ボディ領域41を貫通してその底部がN- ドリフト領域12にまで到達するトレンチ21を形成する。その後,熱酸化処理を行うことにより,トレンチ21の壁面に厚さが50nm程度の酸化膜95を形成する。次に,図4(c)に示すようにトレンチ21の底面からイオン注入を行う。酸化膜95の形成後にイオン注入を行うのは,トレンチ21の側壁にイオン注入を行わないようにするためである。イオン注入後は,トレンチ21内の酸化膜95を除去する。なお,酸化膜の埋込みを行う際,界面基準の問題がある場合や,シリコン表面に薄い酸化膜が形成されていた方が絶縁物の埋込み性が良い場合には,50nm程度の薄い熱酸化膜を形成してから絶縁物の埋込みを行うとよい。シリコン表面が露出していた方が絶縁物の埋込み性が良い場合には,その必要はない。

Next, as shown in FIG. 4B, a

次に,図4(d)に示すようにトレンチ21内にCVDにて絶縁物(酸化シリコン等)23を堆積させる。その後,絶縁物の焼きしめとPフローティング領域51の形成とを兼ねて熱拡散処理を行う。これにより,Pフローティング領域51が形成される。なお,Pフローティング領域51のサイズは,トレンチ21の底部の寸法により決められる。さらに,Pフローティング領域51の厚さ方向の位置は,トレンチの深さにより決められる。すなわち,Pフローティング領域51は,寸法精度が高いトレンチ21を基に形成されることからその寸法精度が高い。次に,図4(e)に示すように絶縁物を堆積した状態の半導体基板に対してエッチングを行うことで絶縁物の一部を除去する。これにより,ゲート電極22を形成するためのスペースを確保する。

Next, as shown in FIG. 4D, an insulator (silicon oxide or the like) 23 is deposited in the

次に,半導体基板の上面およびトレンチ21の壁面に熱酸化により酸化膜24を形成する。これがゲート酸化膜24となる。そして,先の工程にて確保したスペースに導体(ポリシリコン等)を堆積させることで,図4(f)に示すようなゲート電極22が形成される。そして,最後にソース電極およびドレイン電極を形成することにより,図4(g)に示すような絶縁ゲート型半導体装置,すなわち半導体装置100が作製される。

Next, an

また,図2に示した半導体装置101は,図5のような製造プロセスにより作製される。トレンチ21を形成した後にイオン注入を行う(図4(c)に相当)までは,図1に示した半導体装置100の製造プロセスと同様である。その段階の半導体基板に対して,絶縁物を堆積させることなく,熱拡散処理を行う。これにより,図5(d)に示すようにPフローティング領域52が形成される。

The

次に,図5(e)に示すように再びエッチングを行うことでトレンチ21を掘り下げる。次に,図5(f)に示すように熱酸化処理を行うことでトレンチ21の壁面に酸化膜95を形成する。その後,トレンチ21の底面から再びイオン注入を行う。イオン注入後は,トレンチ21内の酸化膜95を除去する。なお,酸化膜の埋込みを行う際,界面基準の問題がある場合や,シリコン表面に薄い酸化膜が形成されていた方が絶縁物の埋込み性が良い場合には,50nm程度の薄い熱酸化膜を形成してから絶縁物の埋込みを行うとよい。シリコン表面が露出していた方が絶縁物の埋込み性が良い場合には,その必要はない。

Next, the

次に,図5(g)に示すようにトレンチ21内にCVDにて絶縁物(酸化シリコン等)23を堆積させる。その後,絶縁物の焼きしめとPフローティング領域51の形成とを兼ねて熱拡散処理を行う。これにより,Pフローティング領域51が形成される。

Next, as shown in FIG. 5G, an insulator (silicon oxide or the like) 23 is deposited in the

次に,図4(e)以降に示した工程と同様の作業を行うことで,図5(h)に示すようなトレンチ21に内蔵されたゲート電極22が形成される。そして,最後にソース電極およびドレイン電極を形成することにより,図5(i)に示すような絶縁ゲート型半導体装置,すなわち半導体装置101が作製される。なお,Pフローティング領域52の数は,図5(d)から図5(f)までの工程を繰り返すことにより厚さ方向に増やすことが可能である。

Next, the

また,図3に示した終端エリアのPフローティング領域53もセルエリアのPフローティング領域51と同じ工程で作製することができる。そのため,終端エリアの高耐圧化が図られた半導体装置102を,少ない工程で簡便に作製することができる。

Also, the

続いて,図1に示した半導体装置100について,DS間の耐圧およびオン抵抗の測定結果について説明する。図6は,ゲート電圧Vgを0Vに固定したときの,DS間における電圧Vdsと電流Idsとの関係を示したグラフである。図6に示すように電圧Vdsが10Vから70Vまでの間は,電流Idsの値がほぼ一定であることがわかる。そして,電圧Vdsが72Vを超えることで急激に電流Idsが大きくなっている。すなわち,およそ72Vでブレークダウンが発生したことがわかる。図7は,ゲート電圧Vgを変えて,DS間における電圧Vdsと電流値Idsとの関係をシミュレートしたときのグラフである。このグラフの傾きがDS間のオン抵抗に相当する。一般的に,シリコン限界(ユニポーラリミット)は,次の式(1)で計算されるオン抵抗(Ron)で示される。なお,式(1)中のVbは耐圧を示す。

Ron=8.33×10-9(Vb)2.5 (1)

例えば,耐圧72Vの場合は,オン抵抗36.6mΩ・mm2 がユニポーラリミットである。ここで本形態の,例えばゲート電圧Vg=15Vの時のオン抵抗は,図7のVg=15Vのグラフの傾きより34.0mΩ・mm2 であった。従って,本形態の絶縁ゲート型半導体装置は,ユニポーラリミットを超えて,より低オン抵抗化が図られたことがわかる。

Next, with respect to the

Ron = 8.33 × 10 −9 (Vb) 2.5 (1)

For example, in the case of a withstand voltage of 72 V, the on-resistance of 36.6 mΩ · mm 2 is a unipolar limit. Here, for example, the on-resistance when the gate voltage Vg = 15 V in this embodiment is 34.0 mΩ · mm 2 from the slope of the graph of Vg = 15 V in FIG. Therefore, it can be seen that the insulated gate semiconductor device of this embodiment has a lower on-resistance than the unipolar limit.

[第2の形態]

第2の形態に係る絶縁ゲート型半導体装置200(以下,「半導体装置200」とする)は,図8の断面図に示す構造を有している。本形態の半導体装置200の特徴は,Pフローティング領域用のトレンチを設け,そのトレンチの底部がPフローティング領域内に位置している点である。この点,ゲート電極が内蔵されているトレンチの底部がPフローティング領域に位置する半導体装置100(図1参照)と異なる。なお,図8中,図1で示した半導体装置100と同一記号の構成要素は,その構成要素と同一機能を有するものである。

[Second form]

An insulated gate semiconductor device 200 (hereinafter referred to as “

半導体装置200では,第1の形態の半導体装置100と同様に,N+ ソース領域31,N+ ドレイン領域11,P- ボディ領域41およびN- ドリフト領域12が設けられている。また,半導体装置200の上面側の一部を掘り込むことで形成されたトレンチ21が設けられている。また,トレンチ21には,ゲート電極22が内蔵されている。ゲート電極22は,トレンチ21の壁面に形成されたゲート絶縁膜24によりP- ボディ領域41から絶縁されている。半導体装置200では,ゲート電極22への電圧印加によりP- ボディ領域41にチャネル効果を生じさせ,もってN+ ソース領域31とN+ ドレイン領域11との間の導通をコントロールしている。

The

また,半導体基板には,ゲート電極22が内蔵されたトレンチ21の他,トレンチ21を挟んで両側にトレンチ25,25が設けられている。各トレンチ25内は,絶縁物にて充填されている。さらに,トレンチ25の底部と接するとともにN- ドリフト領域12に囲まれたPフローティング領域54が形成されている。Pフローティング領域54の断面は,図8の断面図に示したように,トレンチ25の底部を中心とした略円形形状となっている。なお,本明細書では,ゲート電極22用のトレンチを「トレンチ21」とし,Pフローティング領域54用のトレンチを「トレンチ25」とする。

In addition to the

本形態の半導体装置200では,第1の形態の半導体装置100と同様に,Pフローティング領域54を設けることで電界のピークを2箇所に形成でき,最大ピーク値の低減を図ることができる。また,第1の形態の半導体装置100と比較して,次のような特性を有する。すなわち,ゲート電極22の構造が従来のものと同じであるため,その形成が容易である。また,ゲート電極22とPフローティング領域54との間の距離が第1の半導体装置100と比較して長い。そのため,電流経路を確保し易く,低オン抵抗化を図ることができる。また,ゲート電極22と対向するPフローティング領域を設けていないことから,イオン注入の影響やオン抵抗の増大といった問題が生じない。

In the

なお,第1の形態の半導体装置100と同様に,Pフローティング領域を半導体装置の厚さ方向に複数設けてもよい。例えば,図9に示すように2段構造のPフローティング領域としてもよい。図9に示した半導体装置201では,図8に示した半導体装置200よりも深い深さのトレンチ25が設けられている。なお,ゲート電極22用のトレンチ21は,図8に示した半導体装置200と同様の深さである。半導体装置201では,トレンチ25の底部を中心とするPフローティング領域54と,Pフローティング領域54とP- ボディ領域41との間に位置するPフローティング領域55とが設けられている。これにより,電界のピークを3箇所に形成でき,より高耐圧化および低オン抵抗化を図ることができる。

As with the

また,図10に示すようにゲート電極22を挟んでトレンチ25と深さが異なるトレンチ26を設けてもよい。このトレンチ26も内部が絶縁物で充填されており,その底部がPフローティング領域56内に位置している。すなわち,Pフローティング領域56がPフローティング領域54と厚さ方向に異なる位置に設けられている。よって,図9に示した半導体装置201と同様に電界のピークを3箇所に設けた構造とすることができる。従って,高耐圧化および低オン抵抗化を図ることができる。なお,半導体装置202では,幅方向に空乏層が確実に繋がるようにするため,トレンチ間のピッチが半導体装置201と比較して若干狭く設計されている。半導体装置202では,各トレンチに接するPフローティング領域はそれぞれ1つであるため,各Pフローティング領域を形成するためのイオン注入および熱拡散処理は1回でよい。そのため,熱拡散処理による特性劣化を最小限にすることができる。また,各トレンチ内の充填処理は1度に行うことができるため,製造工程が少ない。

Further, as shown in FIG. 10, a

また,各トレンチの形状は,紙面奥行き方向に長いストライプ形状のものの他,メッシュ形状やドット形状のものであってもよい。なお,高耐圧化を図るためには,図11に示すようなストライプ形状のものや,図12に示すようなメッシュ形状のものが効果的である。 The shape of each trench may be a mesh shape or a dot shape in addition to a stripe shape that is long in the depth direction of the drawing. In order to increase the breakdown voltage, a stripe shape as shown in FIG. 11 or a mesh shape as shown in FIG. 12 is effective.

次に,図9に示した半導体装置201の製造プロセスを図13により説明する。なお,半導体装置201中のゲート電極22およびトレンチ21は一般的な構造であり,公知の製造方法にて形成される。まず,図13(a)に示すようにP- ボディ領域を貫通してその底部がN- ドリフト領域12にまで到達するトレンチ25が形成される。その後,トレンチ25の底面からイオン注入を行い,その後,熱拡散処理を行う。これにより,Pフローティング領域55が形成される。なお,この状態の半導体基板を基に,トレンチ25内に絶縁物を堆積させ,ソース電極およびドレイン電極を形成することにより,図8に示した半導体装置200が作製される。

Next, a manufacturing process of the

次に,図13(b)に示すように再びエッチングを行うことでトレンチ25を掘り下げる。その後,トレンチ25の底面から再びイオン注入を行う。次に,図13(c)に示すようにトレンチ21内にCVDにて絶縁物23を堆積させる。その後,絶縁物の焼きしめとPフローティング領域54の形成とを兼ねて熱拡散処理を行う。これにより,Pフローティング領域54が形成される。そして,最後にソース電極およびドレイン電極を形成することにより,図13(d)に示すような絶縁ゲート型半導体装置,すなわち半導体装置201が作製される。

Next, as shown in FIG. 13B, the

[第3の形態]

第3の形態に係る絶縁ゲート型半導体装置300(以下,「半導体装置300」とする)は,図14の断面図に示す構造を有している。本形態の半導体装置300の特徴は,Pフローティング領域が,ゲート電極用のトレンチおよびPフローティング領域用のトレンチのそれぞれ下方に形成されている点である。この点,Pフローティング領域がゲート電極用のトレンチ21の下方のみに形成されている半導体装置100(図1参照)や,Pフローティング領域用のトレンチ25の下方のみに形成されている半導体装置200(図8参照)と異なる。なお,図14中,図1で示した半導体装置100や図8で示した半導体装置200と同一記号の構成要素は,その構成要素と同一機能を有するものである。

[Third embodiment]

An insulated

半導体装置300では,第1の形態の半導体装置100や第2の形態の半導体装置200と同様に,N+ ソース領域31,N+ ドレイン領域11,P- ボディ領域41およびN- ドリフト領域12が設けられている。また,半導体装置300の上面側の一部を掘り込むことで形成されたトレンチ21が設けられている。トレンチ21の底部には,絶縁物の堆積による堆積絶縁層23が形成されている。さらに,堆積絶縁層23上には,導体の堆積によるゲート電極22が形成されている。ゲート電極22は,トレンチ21の壁面に形成されたゲート絶縁膜24によりP- ボディ領域41から絶縁されている。半導体装置200では,ゲート電極22への電圧印加によりP- ボディ領域41にチャネル効果を生じさせ,もってN+ ソース領域31とN+ ドレイン領域11との間の導通をコントロールしている。

In the

また,半導体基板には,ゲート電極22が内蔵されたトレンチ21の他,トレンチ21を挟んだ両側にトレンチ21より深い深さのトレンチ25,25が設けられている。トレンチ25内は,絶縁物にて充填されている。さらに,N- ドリフト領域12に囲まれたPフローティング領域51,54が形成されている。Pフローティング領域51,54の断面は,図14の断面図に示したように,トレンチ21もしくはトレンチ25の底部を中心とした略円形形状となっている。なお,本明細書では,ゲート電極用のトレンチ21の底部が位置するPフローティング領域を「Pフローティング領域51」とし,Pフローティング領域用のトレンチ25の底部が位置するPフローティング領域を「Pフローティング領域54」とする。

In addition to the

隣り合うPフローティング領域51,54は,互いに接しないように配置されている。隣り合うPフローティング領域同士が接していると,オン時の電流経路が狭くなりオン抵抗が大きくなるためである。また,Pフローティング領域51は,オフ時にP- ボディ領域41とN- ドリフト領域12とのPN接合部から下方に広がる空乏層がブレークダウンの発生前にPフローティング領域51に到達するぎりぎりの位置に配置されている。これは,耐圧が空乏層の深さに比例するため,P- ボディ領域41とPフローティング領域51との間の距離が短いと耐圧が低くなってしまうからである。また,Pフローティング領域54は,Pフローティング領域51から下方に広がる空乏層がブレークダウンの発生前にPフローティング領域54に到達するぎりぎりの位置に配置されている。これも最適な高耐圧化を図るためである。

Adjacent

本形態の半導体装置300では,ゲート電極用のトレンチ21の底部とPフローティング領域用のトレンチ25の底部とのそれぞれにPフローティング領域51,54を設け,さらにトレンチ21とトレンチ25との深さを異にすることで,図9に示した半導体装置201や図10に示した半導体装置202と同様に電界のピークを3箇所に設けた構造となっている。そのため,高耐圧化および低オン抵抗化が図られている。

In the

なお,Pフローティング領域51,54は,必ずしも図14に示した半導体装置300のように,Pフローティング領域51を上方にし,Pフローティング領域54を下方にする配置に限るものではない。例えば,図15に示すようにPフローティング領域51を下方にし,Pフローティング領域54を上方にした配置であってもよい。このように配置された半導体装置301であっても電界のピークを3箇所に形成でき,最大ピーク値の低減を図ることができる。

The

また,図14および図15に示した半導体装置と異なり,図16に示す半導体装置302のようにゲート電極用のトレンチ21の深さとPフローティング領域用のトレンチ25の深さとを同一としてもよい。このような半導体装置302では,次のような利点を生じる。すなわち,両トレンチを同一の工程で形成することができる。そのため,工程数を削減することができる。また,隣り合うPフローティングの間の距離が短く,N- ドリフト領域12の濃度が高くても空乏層を確実に繋げることができる。そのため,低オン抵抗化を図ることができる。また,数多くのPフローティング領域51,54にて高耐圧化を図るため,1つあたりのPフローティング領域51,54のサイズは小さくて済む。よって,イオン注入時の加速電圧を低くすることができ,イオン注入によるダメージを抑制することができる。また,トレンチの深さの異なる半導体装置と比較して,エピタキシャル層の厚さを小さくすることができる。また,熱拡散処理の回数が少ないため,不純物が必要以上に拡散されることを抑制でき,熱拡散処理によるオン抵抗の増大を抑制できる。

14 and 15, unlike the

また,図16に示した半導体装置302の各トレンチの形状は,他の半導体装置と同様にストライプ形状(図11参照),メッシュ形状(図12参照),ドット形状等のいずれであってもよい。なお,半導体装置302は,各Pフローティング領域の密度が高いことから,他の構造のものと比較してサイズ等の製造マージンが大きい。この利点を活用した配列として,図17に示すようにトレンチ25をドット形状とするとよりよい。この配列では,部分的にPフローティング領域54が切れているため,電流経路が広く低オン抵抗化を図ることができる。なお,空乏層の広がりを均等とするためには,各トレンチ間の距離を均等とする。また,図18に示すようにトレンチ25の切れ目にトレンチ21を設けてメッシュ形状とすることで,ゲート電極22の面積が広くなり低オン抵抗化を図ることができる。なお,図17中のA−A断面あるいは図18中のB−B断面が図16に示した半導体装置302に相当する。

Further, the shape of each trench of the

次に,図14に示した半導体装置300の製造プロセスを図19により説明する。なお,半導体装置300中のゲート電極22およびトレンチ21は,図1の半導体装置100と同一の構造であり,図4に示した製造方法にて形成される。まず,図19(a)に示すように再びエッチングを行うことで,トレンチ21よりも深い深さのトレンチ25を形成する。その後,熱酸化処理を行うことにより,トレンチ25の壁面に酸化膜95を形成する。次に,トレンチ25の底面から再びイオン注入を行う。イオン注入後,トレンチ25内の酸化膜95を除去する。なお,酸化膜の埋込みを行う際,界面基準の問題がある場合や,シリコン表面に薄い酸化膜が形成されていた方が絶縁物の埋込み性が良い場合には,50nm程度の薄い熱酸化膜を形成してから絶縁物の埋込みを行うとよい。シリコン表面が露出していた方が絶縁物の埋込み性が良い場合には,その必要はない。

Next, a manufacturing process of the

次に,トレンチ25内に絶縁物を堆積させる。その後,絶縁物の焼きしめとPフローティング領域54の形成とを兼ねて熱拡散処理を行う。これにより,Pフローティング領域51に対して厚さ方向の位置が異なるPフローティング領域54が形成される。これにより,図19(b)に示すようにトレンチ25内に堆積絶縁層23が形成される。そして,最後にソース電極およびドレイン電極を形成することにより,図19(c)に示すような絶縁ゲート型半導体装置,すなわち半導体装置300が作製される。なお,図15に示した半導体装置301についても,各トレンチの深さを変更するだけで同様のプロセスで作製することが可能である。

Next, an insulator is deposited in the

なお,ゲート電極用のトレンチ21とPフローティング領域用のトレンチ25とでは,トレンチ21を先に形成しているが,これは熱負荷を減らすためである。しかし,ゲート酸化温度を低くする等によりトレンチ25を先に形成することも可能である。

The

次に,図16に示した半導体装置302の製造プロセスを図20により説明する。まず,図20(a)に示すようにP- ボディ領域41を貫通してその底部がN- ドリフト領域12にまで到達するトレンチ21およびトレンチ25が形成される。各トレンチは,一度に形成されるため,その深さが同一である。その後,熱酸化処理を行うことにより,各トレンチの壁面に酸化膜95を形成する。その後,各トレンチの底面からイオン注入を行う。イオン注入後,各トレンチ内の酸化膜95を除去する。なお,酸化膜の埋込みを行う際,界面基準の問題がある場合や,シリコン表面に薄い酸化膜が形成されていた方が絶縁物の埋込み性が良い場合には,50nm程度の薄い熱酸化膜を形成してから絶縁物の埋込みを行うとよい。シリコン表面が露出していた方が絶縁物の埋込み性が良い場合には,その必要はない。

Next, a manufacturing process of the

次に,各トレンチ内に絶縁物を堆積させる。これにより,各トレンチ内に堆積絶縁層23が形成される。その後,絶縁物の焼きしめとPフローティング領域51およびPフローティング領域54の形成とを兼ねて熱拡散処理を行う。すなわち,Pフローティング領域51およびPフローティング領域54が1度の熱拡散処理でまとめて形成される。これにより,図20(b)に示すようにトレンチ21の下方にはPフローティング領域51が,トレンチ25の下方にはPフローティング領域54がそれぞれ形成される。

Next, an insulator is deposited in each trench. Thereby, the deposited insulating

次に,トレンチ21内の堆積絶縁層23に対してエッチングを行うことで,堆積絶縁層23の一部が除去される。さらに,トレンチ21の壁面に熱酸化により酸化膜24が形成される。これがゲート酸化膜24となる。そして,トレンチ21の内部に導体を堆積させることにより,図20(c)に示すようなトレンチ21に内蔵されたゲート電極22が形成される。そして,最後にソース電極およびドレイン電極を形成することにより,図20(d)に示すような絶縁ゲート型半導体装置,すなわち半導体装置302が作製される。

Next, by etching the deposited insulating

以上詳細に説明したように第1の形態の半導体装置100(図1)では,1回のエピタキシャル成長工程によりエピタキシャル層(N- ドリフト領域12)を形成し,さらにイオン注入,熱拡散等によりそのエピタキシャル層内にP- ボディ領域41を形成することとしている。そして,そのエピタキシャル層を有する半導体基板に対してトレンチ21を形成し,そのトレンチの底部からイオン注入を行うことによりPフローティング領域51を形成することとしている。すなわち,Pフローティング領域51を形成するに際し,エピタキシャル成長工程は1回のみでよい。このことは,半導体装置101(図2)のように厚さ方向に複数のPフローティング領域52を作製する場合や,半導体装置102(図3)のように終端エリアにPフローティング領域53を作製する場合でも同様である。そして,Pフローティング領域51によりゲート電圧のスイッチオフ時におけるN- ドリフト領域12の空乏化を促進するとともに電界の集中を緩和することができている。これにより,高耐圧化と低オン抵抗化とを両立させ,簡便に作製することができる絶縁ゲート型半導体装置およびその製造方法が実現されている。

As described in detail above, in the

また,トレンチ21内に堆積絶縁層23を形成することとしている。これにより,イオン注入による影響を受けることなく,ゲート絶縁膜24およびゲート電極22を形成することができる。これにより,素子特性の劣化および信頼性の低下を抑止することができる。また,堆積絶縁層23の上端は,Pフローティング領域51の上端よりも上方に位置している。よって,ゲート電極22とPフローティング領域51との対面が抑止されている。これにより,オン抵抗の増大を防止することができている。

Further, the deposited insulating

また,半導体装置101(図2)では,P- ボディ領域41とPフローティング領域51との間の位置にPフローティング領域52を有することとしている。これにより,電界のピークを3箇所に形成でき,より最大ピーク値の低減を図ることができる。よって,Pフローティング領域52を設けることで,より高耐圧化および低オン抵抗化を図ることができる。

In the semiconductor device 101 (FIG. 2), the

また,半導体装置102(図3)では,終端エリアにもPフローティング領域53を有することとしている。これにより,終端エリアでもセルエリアと同様に高耐圧化を達成することができる。このPフローティング領域53は,セルエリアのPフローティング領域51と同じ工程で形成される。また,Pフローティング領域53は,従来の半導体装置と比較してそれほどスペースを必要としない。従って,サイズの制御性がよく,半導体装置自体がコンパクトである。

In the semiconductor device 102 (FIG. 3), the

また,第2の形態の半導体装置200(図8)では,Pフローティング領域用のトレンチ25を設けることとしている。そして,ゲート電極22が内蔵されているトレンチ21の下方にはPフローティング領域を設けていない。そのため,イオン注入の影響やオン抵抗の増大といった問題が生じない。また,Pフローティング領域54は,Pフローティング領域用に形成されたトレンチ25の下方に設けられている。そのため,ゲート電極22の位置やサイズを考慮する必要がなく,設計自由度が高い。また,ゲート電極22とPフローティング領域54との間の距離が第1の半導体装置100と比較して長い。これにより,第1の形態の半導体装置100と同様に高耐圧化を図るとともに,電流経路を確保し易く,低オン抵抗化を図ることができる。

In the

また,半導体装置201(図9)では,P- ボディ領域41とPフローティング領域54との間の位置にPフローティング領域55を有することとしている。これにより,電界のピークを3箇所に形成でき,より最大ピーク値の低減を図ることができる。また,半導体装置202(図10)では,異なる深さのトレンチ25を設け,各トレンチの下方に1つずつPフローティング領域54を設けることとしている。これにより,熱拡散処理による特性劣化を最小限にするとともに,高耐圧化および低オン抵抗化を図ることができる。

In the semiconductor device 201 (FIG. 9), a

また,第3の形態の半導体装置300(図14)では,ゲート電極用のトレンチ21とPフローティング領域用のトレンチ25とを設け,さらに両トレンチの下方にPフローティング領域51,54をそれぞれ設けることとしている。さらに,トレンチ21の深さとトレンチ25の深さとを異にすることとしている。これにより,電界のピークを複数箇所に形成でき,より最大ピーク値の低減を図ることができる。

Further, in the

また,半導体装置302(図16)では,トレンチ21の深さとトレンチ25の深さとを同一にすることとしている。半導体装置302では,トレンチ21とトレンチ25とを同一の工程で形成することができる。そのため,工程数を削減することができる。また,熱拡散処理の回数が少ないため,不純物の拡散が少なく熱拡散処理によるオン抵抗の低下を抑制することができる。

In the semiconductor device 302 (FIG. 16), the depth of the

なお,本実施の形態は単なる例示にすぎず,本発明を何ら限定するものではない。したがって本発明は当然に,その要旨を逸脱しない範囲内で種々の改良,変形が可能である。例えば,各半導体領域については,P型とN型とを入れ替えてもよい。また,ゲート絶縁膜24については,酸化膜に限らず,窒化膜等の他の種類の絶縁膜でもよいし,複合膜でもよい。また,半導体についても,シリコンに限らず,他の種類の半導体(SiC,GaN,GaAs等)であってもよい。

Note that this embodiment is merely an example, and does not limit the present invention. Therefore, the present invention can naturally be improved and modified in various ways without departing from the gist thereof. For example, for each semiconductor region, P-type and N-type may be interchanged. Further, the

また,図3に示した半導体装置102では,終端エリア内のトレンチ62内が完全に絶縁物で充填されているが,セルエリア内のトレンチ21と同様に一部の絶縁物を除去して導体を堆積させてもよい。この場合,トレンチ62内の導体は,ゲート配線と電気的に接続されていない。このような半導体装置であっても,少ない工程数で終端エリアの高耐圧化を図ることができる。

Further, in the

また,実施の形態の絶縁ゲート型半導体装置は,図21に示すようなP型基板13を用いた伝導度変調型パワーMOSに対しても適用可能である。

The insulated gate semiconductor device of the embodiment can also be applied to a conductivity-modulated power MOS using a P-

また,実施の形態の絶縁ゲート型半導体装置は,これまでに述べた特性に加え,次のような特性を有している。すなわち,Pフローティング領域51にホールが蓄積するため,Pフローティング領域51がホールの供給源となる。その結果,N- ドリフト領域12の表面領域,具体的にはPフローティング領域51よりも上方に位置する領域のホールの濃度を上げることができる。従って,低損失化が図られる。また,ゲート電極22の下方に堆積絶縁層23が形成されているため,ゲート−ドレイン間容量(Cgd)が小さい。よって,発信防止や駆動損失を低減できる。

In addition to the characteristics described so far, the insulated gate semiconductor device of the embodiment has the following characteristics. That is, since holes accumulate in the

また,Pフローティング領域51からも空乏層が形成されるため,負荷短絡時の耐圧が向上する。すなわち,Pフローティング領域51を有しない従来の絶縁ゲート型半導体装置では,負荷短絡時に図11に示すようにP- ボディ領域41とN- ドリフト領域12との間のPN接合箇所からドレイン側に空乏層15が形成され,トレンチ21の下方の領域で電流が流れる(図22の矢印参照)。一方,本形態の絶縁ゲート型半導体装置100では,ゲート電極22の下に堆積絶縁層23が形成されており,図23に示すようにトレンチ21に沿って電流が流れる。また,Pフローティング領域51からも空乏層15が形成される。従って,負荷短絡時の電流経路が非常に狭い(図23の矢印参照)。その結果,短絡電流が低減し,負荷短絡時の耐圧が向上する。

Further, since a depletion layer is formed also from the

また,図24あるいは図25に示すようにP- ボディ領域41とN- ドリフト領域12との間にホールのバリアとして作用するNホールバリア領域18が形成されたパワーMOSに対しても適用可能である。このNホールバリア領域18が形成されたパワーMOSの場合,Nホールバリア領域18内で空乏層の広がりが狭い。そのため,耐圧が低下してしまうおそれがある。しかしながら,本形態のようにPフローティング領域51を備えたパワーMOSでは,P- ボディ領域41とN- ドリフト領域12との間のPN接合箇所から形成される空乏層に加え,Pフローティング領域51からも空乏層が形成されるため,耐圧の低下が抑制される。

Further, the present invention can also be applied to a power MOS in which an N

11 N+ ドレイン領域

12 N- ドリフト領域(ドリフト領域)

21 トレンチ(トレンチ部)

22 ゲート電極

23 堆積絶縁層

24 ゲート絶縁膜

25 トレンチ(補助トレンチ部)

26 トレンチ(第2補助トレンチ部)

31 N+ ソース領域

41 P- ボディ領域(ボディ領域)

51 Pフローティング領域(フローティング領域)

52 Pフローティング領域(中間フローティング領域)

53 Pフローティング領域(終端フローティング領域)

54 Pフローティング領域(補助フローティング領域)

55 Pフローティング領域(中間補助フローティング領域)

56 Pフローティング領域(第2補助フローティング領域)

62 トレンチ(終端トレンチ部)

11 N + drain region 12 N − drift region (drift region)

21 trench (trench part)

22

26 trench (second auxiliary trench part)

31 N + source region 41 P - body region (body region)

51 P floating area (floating area)

52 P floating area (intermediate floating area)

53 P floating area (terminal floating area)

54 P floating area (auxiliary floating area)

55 P floating area (intermediate auxiliary floating area)

56 P floating area (second auxiliary floating area)

62 Trench (Terminal Trench)

Claims (12)

前記ドリフト領域に囲まれるとともに第1導電型半導体であるフローティング領域を有し,

前記トレンチ部の底部は,前記フローティング領域内に位置し,

前記トレンチ部内には,

絶縁物を堆積してなる堆積絶縁層と,

前記堆積絶縁層上に位置し,前記ボディ領域と対面するゲート電極とが形成されており,

前記堆積絶縁層の上端は,前記フローティング領域の上端よりも上方に位置し,

前記ボディ領域の下面と前記フローティング領域の上端との間隔は,前記堆積絶縁層の下端と前記フローティング領域の下端との間隔よりも広く,

前記ゲート電極の下端と前記堆積絶縁層の下端との間隔は,前記ボディ領域の下面と前記フローティング領域の上端との間隔よりも広く,

前記堆積絶縁層の厚さは,その厚さ方向において,電界のピークが少なくとも2箇所に形成される厚さであることを特徴とする絶縁ゲート型半導体装置。 A body region that is a first conductivity type semiconductor located on the upper surface side in the semiconductor substrate, a drift region that is in contact with the lower surface of the body region and is a second conductivity type semiconductor, and penetrates the body region from the upper surface of the semiconductor substrate; In an insulated gate semiconductor device having a trench portion whose bottom is located below the lower surface of the body region,

A floating region surrounded by the drift region and being a first conductivity type semiconductor;

The bottom of the trench is located in the floating region;

In the trench part,

A deposited insulating layer formed by depositing an insulator;

A gate electrode located on the deposited insulating layer and facing the body region is formed;

The upper end of the deposited insulating layer is located above the upper end of the floating region ,

The interval between the lower surface of the body region and the upper end of the floating region is wider than the interval between the lower end of the deposited insulating layer and the lower end of the floating region,

The gap between the lower end of the gate electrode and the lower end of the deposited insulating layer is wider than the gap between the lower surface of the body region and the upper end of the floating region,

2. The insulated gate semiconductor device according to claim 1, wherein the thickness of the deposited insulating layer is such that electric field peaks are formed in at least two places in the thickness direction.

前記フローティング領域の上端よりも上方に位置し,前記ドリフト領域に囲まれるとともに第1導電型半導体である中間フローティング領域を有し,

前記トレンチ部は,前記中間フローティング領域を貫通しており,

前記堆積絶縁層の上端は,前記中間フローティング領域の上端よりも上方に位置することを特徴とする絶縁ゲート型半導体装置。 The insulated gate semiconductor device according to claim 1,

An intermediate floating region that is located above the upper end of the floating region, is surrounded by the drift region and is a first conductivity type semiconductor,

The trench portion passes through the intermediate floating region,

An insulated gate semiconductor device, wherein an upper end of the deposited insulating layer is located above an upper end of the intermediate floating region.

半導体基板の上面から前記ボディ領域を貫通しその底部が前記ボディ領域の下面より下方に位置し,内側が絶縁物で充填された補助トレンチ部と,

前記ドリフト領域に囲まれるとともに第1導電型半導体である補助フローティング領域を有し,

前記補助トレンチ部の底部は,前記補助フローティング領域内に位置することを特徴とする絶縁ゲート型半導体装置。 The insulated gate semiconductor device according to claim 1,

An auxiliary trench portion penetrating the body region from the upper surface of the semiconductor substrate, the bottom portion thereof being located below the lower surface of the body region, and the inside being filled with an insulator;

An auxiliary floating region that is surrounded by the drift region and is a first conductivity type semiconductor;

2. The insulated gate semiconductor device according to claim 1, wherein a bottom portion of the auxiliary trench portion is located in the auxiliary floating region.

前記トレンチ部の深さと前記補助トレンチ部の深さとが異なることを特徴とする絶縁ゲート型半導体装置。 In the insulated gate semiconductor device according to claim 3,

2. The insulated gate semiconductor device according to claim 1, wherein a depth of the trench portion is different from a depth of the auxiliary trench portion.

前記トレンチ部の深さと前記補助トレンチ部の深さとが同一であることを特徴とする絶縁ゲート型半導体装置。 In the insulated gate semiconductor device according to claim 3,

2. The insulated gate semiconductor device according to claim 1, wherein a depth of the trench portion and a depth of the auxiliary trench portion are the same.

半導体基板の上面から前記ボディ領域を貫通しその底部が前記ボディ領域の下面より下方に位置し,内側が絶縁物で充填された補助トレンチ部と,

前記ドリフト領域に囲まれるとともに第1導電型半導体である補助フローティング領域を有し,

前記補助トレンチ部の底部は,前記補助フローティング領域内に位置することを特徴とする絶縁ゲート型半導体装置。 In the insulated gate semiconductor device according to any one of claims 1 to 5 ,

An auxiliary trench portion penetrating the body region from the upper surface of the semiconductor substrate, the bottom portion thereof being located below the lower surface of the body region, and the inside being filled with an insulator;

An auxiliary floating region that is surrounded by the drift region and is a first conductivity type semiconductor;

2. The insulated gate semiconductor device according to claim 1, wherein a bottom portion of the auxiliary trench portion is located in the auxiliary floating region.

前記補助フローティング領域の上端よりも上方に位置し,前記ドリフト領域に囲まれるとともに第1導電型半導体である補助中間フローティング領域を有し,

前記補助トレンチ部は,前記中間補助フローティング領域を貫通しており,

前記堆積絶縁層の上端は,前記中間補助フローティング領域の上端よりも上方に位置することを特徴とする絶縁ゲート型半導体装置。 In the insulated gate semiconductor device according to claim 6,

The auxiliary floating region is located above the upper end of the auxiliary floating region, and is surrounded by the drift region and has an auxiliary intermediate floating region that is a first conductivity type semiconductor,

The auxiliary trench portion passes through the intermediate auxiliary floating region,

An insulated gate semiconductor device, wherein an upper end of the deposited insulating layer is located above an upper end of the intermediate auxiliary floating region.

前記補助トレンチ部と前記ゲート電極を挟んで対向し,半導体基板の上面から前記ボディ領域を貫通しその底部が前記ボディ領域の下面より下方に位置し,内側が絶縁物で充填された第2補助トレンチ部と,

前記ドリフト領域に囲まれるとともに第1導電型半導体である第2補助フローティング領域を有し,

前記補助トレンチ部と前記第2補助トレンチ部とは,互いに深さが異なることを特徴とする絶縁ゲート型半導体装置。 In the insulated gate semiconductor device according to claim 6,

A second auxiliary which is opposed to the auxiliary trench portion with the gate electrode interposed therebetween, penetrates the body region from the upper surface of the semiconductor substrate, has a bottom portion located below the lower surface of the body region, and is filled with an insulator inside. A trench,

A second auxiliary floating region that is surrounded by the drift region and is a first conductivity type semiconductor;

2. The insulated gate semiconductor device according to claim 1, wherein the auxiliary trench part and the second auxiliary trench part have different depths.

前記補助トレンチ部は,半導体基板の上方から見てドット形状に構成されていることを特徴とする絶縁ゲート型半導体装置。 In the insulated gate semiconductor device according to claim 3 or 6,

2. The insulated gate semiconductor device according to claim 1, wherein the auxiliary trench portion is formed in a dot shape when viewed from above the semiconductor substrate.

セル領域の周辺領域に位置し,内側が絶縁物で充填された終端トレンチ部と,

前記ドリフト領域に囲まれるとともに第1導電型半導体である終端フローティング領域とを有し,

前記終端トレンチ部の底部は,前記終端フローティング領域内に位置していることを特徴とする絶縁ゲート型半導体装置。 In the insulated gate semiconductor device according to any one of claims 1 to 9,

A termination trench located in the peripheral region of the cell region and filled with an insulator inside;

A terminal floating region that is surrounded by the drift region and is a first conductivity type semiconductor;

2. The insulated gate semiconductor device according to claim 1, wherein a bottom portion of the termination trench portion is located in the termination floating region.

前記ドリフト領域および前記ボディ領域が形成された半導体基板内に前記トレンチ部を形成するトレンチ部形成工程と,

前記トレンチ部形成工程にて形成されたトレンチ部の底部から不純物を注入する不純物注入工程と,

前記不純物注入工程にて不純物を注入した後に,トレンチ部内に絶縁物を堆積させる絶縁物堆積工程と,

前記絶縁物堆積工程にて絶縁物を堆積させた後に,熱拡散処理を行うことでフローティング領域を形成するフローティング領域形成工程とを含むことを特徴とする絶縁ゲート型半導体装置の製造方法。 A body region which is located on the upper surface side of the semiconductor substrate and is a first conductivity type semiconductor, a drift region which is in contact with the lower surface of the body region and is a second conductivity type semiconductor, and is surrounded by the drift region and the first conductivity type semiconductor a floating region is a trench portion positioned in the floating region its bottom through the body region from the upper surface of the semiconductor substrate is a lower than the body region, located on the inside of the trench portion, the floating region and in contact with, an insulating material and formed by depositing deposited insulating layer, located on the inside of the trench portion have a gate electrode that faces the body region, the upper end of the deposited insulating layer, an upper end of the floating region The distance between the lower surface of the body region and the upper end of the floating region is higher than the lower end of the deposited insulating layer and the floating region. A gap between the lower end of the gate region and the lower end of the deposited insulating layer is wider than an interval between the lower surface of the body region and the upper end of the floating region; thickness, in the thickness direction, in the manufacturing method of the thickness of the insulated gate semiconductor device in which the peak of the electric field is formed in at least two positions,

A trench part forming step of forming the trench part in the semiconductor substrate in which the drift region and the body region are formed;

An impurity implantation step of implanting impurities from the bottom of the trench portion formed in the trench portion formation step;

An insulator deposition step of depositing an insulator in the trench portion after implanting impurities in the impurity implantation step;

And a floating region forming step of forming a floating region by performing a thermal diffusion process after depositing the insulator in the insulator depositing step.

前記不純物注入工程にて不純物を注入した後に,トレンチ部の底部をさらに掘り下げるトレンチ部深堀工程と,

前記トレンチ部深堀工程にて掘り下げられたトレンチ部の底部から再度不純物を注入する不純物再注入工程とを含むことを特徴とする絶縁ゲート型半導体装置の製造方法。 In the manufacturing method of the insulated gate semiconductor device according to claim 11,

A trench deep-drilling step of further digging the bottom of the trench after injecting impurities in the impurity implantation step;

A method of manufacturing an insulated gate semiconductor device, comprising: an impurity re-injection step of injecting impurities again from the bottom of the trench portion dug down in the trench portion deep-drilling step.

Priority Applications (5)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003375098A JP4500530B2 (en) | 2003-11-05 | 2003-11-05 | Insulated gate semiconductor device and manufacturing method thereof |

| PCT/JP2004/015179 WO2005036650A2 (en) | 2003-10-08 | 2004-10-06 | Insulated gate type semiconductor device and manufacturing method thereof |

| EP04792407.1A EP1671374B1 (en) | 2003-10-08 | 2004-10-06 | Insulated gate type semiconductor device and manufacturing method thereof |

| US10/573,793 US7470953B2 (en) | 2003-10-08 | 2004-10-06 | Insulated gate type semiconductor device and manufacturing method thereof |

| KR1020067006685A KR100767078B1 (en) | 2003-10-08 | 2004-10-06 | Insulated gate type semiconductor device and manufacturing method thereof |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2003375098A JP4500530B2 (en) | 2003-11-05 | 2003-11-05 | Insulated gate semiconductor device and manufacturing method thereof |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JP2005142243A JP2005142243A (en) | 2005-06-02 |

| JP4500530B2 true JP4500530B2 (en) | 2010-07-14 |

Family

ID=34686555

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2003375098A Expired - Fee Related JP4500530B2 (en) | 2003-10-08 | 2003-11-05 | Insulated gate semiconductor device and manufacturing method thereof |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP4500530B2 (en) |

Families Citing this family (21)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP4734968B2 (en) * | 2005-03-04 | 2011-07-27 | トヨタ自動車株式会社 | Insulated gate semiconductor device |

| JP4735224B2 (en) * | 2005-12-08 | 2011-07-27 | トヨタ自動車株式会社 | Insulated gate semiconductor device and manufacturing method thereof |

| JP4453671B2 (en) | 2006-03-08 | 2010-04-21 | トヨタ自動車株式会社 | Insulated gate semiconductor device and manufacturing method thereof |

| JP5767857B2 (en) * | 2011-05-20 | 2015-08-19 | 新電元工業株式会社 | Trench-type MOSFET and manufacturing method thereof |

| JP5751213B2 (en) * | 2012-06-14 | 2015-07-22 | 株式会社デンソー | Silicon carbide semiconductor device and manufacturing method thereof |

| DE102013217768A1 (en) | 2013-09-05 | 2015-03-05 | Robert Bosch Gmbh | Method for producing a substrate, substrate, metal-oxide-semiconductor field effect transistor with a substrate, microelectromechanical system with a substrate, and motor vehicle |

| CN106796955B (en) | 2014-09-30 | 2020-05-26 | 三菱电机株式会社 | Semiconductor device with a plurality of semiconductor chips |

| JP6715567B2 (en) * | 2014-12-16 | 2020-07-01 | 富士電機株式会社 | Semiconductor device |

| JP6269588B2 (en) * | 2015-06-15 | 2018-01-31 | 株式会社豊田中央研究所 | Semiconductor device |

| US10332990B2 (en) | 2015-07-15 | 2019-06-25 | Fuji Electric Co., Ltd. | Semiconductor device |

| JP6668798B2 (en) * | 2015-07-15 | 2020-03-18 | 富士電機株式会社 | Semiconductor device |

| WO2017174603A1 (en) * | 2016-04-07 | 2017-10-12 | Abb Schweiz Ag | Short channel trench power mosfet |

| JP7251914B2 (en) * | 2016-10-17 | 2023-04-04 | 富士電機株式会社 | semiconductor equipment |

| CN110366782B (en) * | 2017-03-06 | 2023-04-28 | 三菱电机株式会社 | Silicon carbide semiconductor device and method for manufacturing same, and power conversion device and method for manufacturing same |

| JP6377309B1 (en) * | 2017-03-06 | 2018-08-22 | 三菱電機株式会社 | Silicon carbide semiconductor device, power conversion device, method for manufacturing silicon carbide semiconductor device, and method for manufacturing power conversion device |

| CN110431669B (en) | 2017-03-07 | 2023-03-28 | 三菱电机株式会社 | Semiconductor device and power conversion device |

| JP6910944B2 (en) * | 2017-12-27 | 2021-07-28 | ルネサスエレクトロニクス株式会社 | Semiconductor device |

| JP7076222B2 (en) | 2018-02-21 | 2022-05-27 | 三菱電機株式会社 | Semiconductor devices and their manufacturing methods, power conversion devices |

| JP2020072158A (en) * | 2018-10-30 | 2020-05-07 | ローム株式会社 | Semiconductor device |

| DE112021004621T5 (en) * | 2021-05-11 | 2023-06-22 | Fuji Electric Co., Ltd. | SEMICONDUCTOR DEVICE |

| WO2023140254A1 (en) * | 2022-01-20 | 2023-07-27 | 富士電機株式会社 | Semiconductor device |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6194741B1 (en) * | 1998-11-03 | 2001-02-27 | International Rectifier Corp. | MOSgated trench type power semiconductor with silicon carbide substrate and increased gate breakdown voltage and reduced on-resistance |

Family Cites Families (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH0783118B2 (en) * | 1988-06-08 | 1995-09-06 | 三菱電機株式会社 | Semiconductor device and manufacturing method thereof |

| JPH09181304A (en) * | 1995-12-21 | 1997-07-11 | Toyota Motor Corp | Semiconductor device and its manufacture |

| JPH1098188A (en) * | 1996-08-01 | 1998-04-14 | Kansai Electric Power Co Inc:The | Insulated gate semiconductor device |

| JPH1187698A (en) * | 1997-09-02 | 1999-03-30 | Kansai Electric Power Co Inc:The | Semiconductor device having high breakdown strength and power converter employing the same |

| US6649477B2 (en) * | 2001-10-04 | 2003-11-18 | General Semiconductor, Inc. | Method for fabricating a power semiconductor device having a voltage sustaining layer with a terraced trench facilitating formation of floating islands |

| US6686244B2 (en) * | 2002-03-21 | 2004-02-03 | General Semiconductor, Inc. | Power semiconductor device having a voltage sustaining region that includes doped columns formed with a single ion implantation step |

-

2003

- 2003-11-05 JP JP2003375098A patent/JP4500530B2/en not_active Expired - Fee Related

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6194741B1 (en) * | 1998-11-03 | 2001-02-27 | International Rectifier Corp. | MOSgated trench type power semiconductor with silicon carbide substrate and increased gate breakdown voltage and reduced on-resistance |

Also Published As

| Publication number | Publication date |

|---|---|

| JP2005142243A (en) | 2005-06-02 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US7470953B2 (en) | Insulated gate type semiconductor device and manufacturing method thereof | |

| JP4538211B2 (en) | Insulated gate semiconductor device and manufacturing method thereof | |

| JP4500530B2 (en) | Insulated gate semiconductor device and manufacturing method thereof | |

| JP4414863B2 (en) | Insulated gate semiconductor device and manufacturing method thereof | |

| KR101404906B1 (en) | Lateral power devices with self-biasing electrodes | |

| JP4721653B2 (en) | Insulated gate semiconductor device | |

| JP4744958B2 (en) | Semiconductor device and manufacturing method thereof | |

| US20150011065A1 (en) | Semiconductor device and method for manufacturing the same | |

| US9064952B2 (en) | Semiconductor device | |

| JP2008124346A (en) | Power semiconductor element | |

| JP4404709B2 (en) | Insulated gate semiconductor device and manufacturing method thereof | |

| KR20040078149A (en) | Cellular mosfet devices and their manufacture | |

| JP4735224B2 (en) | Insulated gate semiconductor device and manufacturing method thereof | |

| JP2019079833A (en) | Switching element and method for manufacturing the same | |

| JP2009246225A (en) | Semiconductor device | |

| KR100731141B1 (en) | Semiconductor device and method for fabricating the same | |

| JP4735235B2 (en) | Insulated gate semiconductor device and manufacturing method thereof | |

| JP4447474B2 (en) | Semiconductor device and manufacturing method thereof | |

| JP2006093457A (en) | Insulated gate type semiconductor device | |

| JP4734968B2 (en) | Insulated gate semiconductor device | |

| JP2005252203A (en) | Insulated gate type semiconductor device and its manufacturing method | |

| KR102464348B1 (en) | Power semiconductor device with dual shield structure in Silicon Carbide and manufacturing method thereof | |

| JP7156425B2 (en) | semiconductor equipment | |

| JP2020096083A (en) | Manufacturing method for trench gate switching element | |

| KR20180046214A (en) | Semiconductor device and method manufacturing the same |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20060802 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20091110 |

|

| A521 | Request for written amendment filed |

Free format text: JAPANESE INTERMEDIATE CODE: A523 Effective date: 20091216 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20100413 |

|

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20100419 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130423 Year of fee payment: 3 |

|

| R151 | Written notification of patent or utility model registration |

Ref document number: 4500530 Country of ref document: JP Free format text: JAPANESE INTERMEDIATE CODE: R151 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20130423 Year of fee payment: 3 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20140423 Year of fee payment: 4 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| R250 | Receipt of annual fees |

Free format text: JAPANESE INTERMEDIATE CODE: R250 |

|

| LAPS | Cancellation because of no payment of annual fees |