JP3557078B2 - 不揮発性半導体記憶装置 - Google Patents

不揮発性半導体記憶装置 Download PDFInfo

- Publication number

- JP3557078B2 JP3557078B2 JP17225197A JP17225197A JP3557078B2 JP 3557078 B2 JP3557078 B2 JP 3557078B2 JP 17225197 A JP17225197 A JP 17225197A JP 17225197 A JP17225197 A JP 17225197A JP 3557078 B2 JP3557078 B2 JP 3557078B2

- Authority

- JP

- Japan

- Prior art keywords

- conductivity type

- data

- voltage pulse

- source

- writing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/32—Timing circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/04—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS

- G11C16/0483—Erasable programmable read-only memories electrically programmable using variable threshold transistors, e.g. FAMOS comprising cells having several storage transistors connected in series

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C16/00—Erasable programmable read-only memories

- G11C16/02—Erasable programmable read-only memories electrically programmable

- G11C16/06—Auxiliary circuits, e.g. for writing into memory

- G11C16/08—Address circuits; Decoders; Word-line control circuits

Landscapes

- Engineering & Computer Science (AREA)

- Microelectronics & Electronic Packaging (AREA)

- Read Only Memory (AREA)

Description

【発明の属する技術分野】

本発明は、電荷蓄積用の浮遊ゲート電極と制御ゲート電極が積層された構造の電気的書き換え可能なメモリセルを用いた不揮発性半導体記憶装置に係り、特に複数の該メモリセルを直列に接続したNAND構成の不揮発性半導体記憶装置に関するものである。

【0002】

【従来の技術】

従来より、電気的に書き換え可能で且つ高集積化が可能な不揮発性半導体記憶装置(EEPROM :Electrically Erasable Programmable ROM)として、複数個のメモリセルを直列に接続したNANDセル型のEEPROMが知られている。

【0003】

このようなNANDセル型のEEPROMにおいて、その1つのメモリセルは、半導体基板上に絶縁膜を介して浮遊ゲート電極と制御ゲート電極が積層された「スタックゲート構造」を有している。そして、複数個のメモリセルが、隣接するもの同士でソース−ドレインを共有する形で直列に接続され、これを1単位としてビット線に接続されてNANDセルが構成されている。更に、かかるNANDセルがマトリクス状に配置されてメモリセルアレイが構成されている。

【0004】

そして、上記メモリセルアレイの列方向に並ぶNANDセルの一端側のドレインは、それぞれ選択ゲート電極を介してデータ線たるビット線に接続されており、他端側は選択ゲート電極を介してソース線、さらには基準電位配線たる共通ソース線に接続されている。また、各メモリセルの制御ゲート電極及び選択ゲート電極は、上記メモリセルアレイの行方向に、それぞれワード線たる制御ゲート線、選択ゲート線となって共有に接続されている。

【0005】

このようなNANDセル型のEEPROMの書き込み動作方式においては、より低電圧動作を実現することで、即ちビット線に接続されているカラムデコーダ等を構成するトランジスタを全てVcc系トランジスタで構成することができ、従って、その周辺回路の面積を小さくすることが可能となる。かかる点に着目して、チップ面積の縮小を可能にする「セルフブースト書き込み方式」に関する種々の技術が提案され、既に実用化に至っている。

【0006】

以下、上記セルフブースト書き込み方式による動作を説明する。

図19は上記NANDセル型のEEPROMのメモリセル部の等価回路の構成を示す図である。同図において、符号BLはビット線、符号SGは選択ゲート線、符号CGはワード線、符号SLはソース線をそれぞれ示している。

【0007】

複数のデータを行方向の複数のメモリセルに対して一括して書き込む場合において、通常の書き込み動作では、ビット線BLから離れた位置のメモリセルから動作が行われ、ランダム書き込み動作では、ビット線BLとソース線SLの間の任意のメモリセルの書き込みがランダムに行われる。即ち、先ずソース線SL側の選択ゲート線SG2に0Vを与えて当該トランジスタをカットオフさせた状態において、“0”データを書き込むべきメモリセルが接続されているNANDセルのビット線BL1乃至BLnに0Vを与える。そして、“1”データを書き込むメモリセルが接続されているNANDセルのビット線BL1乃至BLnには、ドレイン側の選択ゲート電圧と同じ電圧、それ以上の電圧、或いはドレイン側の選択ゲート電圧より小さくてもドレイン側の選択ゲートが十分カットオフする電位を与えて、各ビット線BL1乃至BLnにおいて、書き込みの選択と非選択(書き込み禁止)の区別を行うことになる。

【0008】

このような状態において、選択ブロックの全てのワード線CG1乃至CGnにメモリセルがON状態となる電位、即ち書き込みパルス電圧Vpp或いは非選択ワード線の転送電圧パルスVpassが与えられるときに、該電圧パルスの立上がりの過程の所定の電位においてメモリセルがON状態となる電位が与えられると、“0”書き込みを行うビット線BL1乃至BLnに接続されたNANDセルのチャネルには0Vが転送されることになる。

【0009】

こうして、“0”データの書き込みを行うメモリセルが接続されている選択ワード線CG1乃至CGnに書き込み電圧パルスVppが与えられると、0Vが与えられている選択ビット線BL1乃至BLnに接続されている選択メモリセルには“0”データが書き込まれる。

【0010】

また、“1”データの書き込みを行うビット線BL1乃至BLnに接続されたNANDセルのチャネルには、ビット線BL1乃至BLnから、該ビット線側の選択ゲート線SG1を介してビット線BL1乃至BLnの電位から当該選択ゲートトランジスタのしきい値分だけを差し引いた所定の初期電位が転送された状態でビット線側の選択ゲートトランジスタがカットオフしフローティングとなる。この時、ソース線SLには、0V或いはソース側の選択ゲートを十分カットオフさせる為に、所定の正の電位が与えられている。

【0011】

ここで、書き込み電圧パルスVppが与えられる選択ワード線に接続され、且つ“1”データの書き込みを行う書き込み非選択メモリセル、即ちビット線側の選択ゲートトランジスタがカットオフし、チャネルがフローティング状態となっているメモリセルのチャネル電位は、“0”データの書き込みが行われないように、即ちしきい値変動が許容範囲以下であるように、十分大きい必要がある。これは、このメモリセルに対しては、書き込み電圧パルスVppとチャネル電位Vchの差が大きい程、しきい値の変動は少ないからである。

【0012】

この為、書き込みを行わない非選択ワード線には、所定の転送電圧パルスVpassを与え、ゲートチャネル間容量を利用してチャネルの電位を初期電位からある電位まで上昇させている。従って、この転送電圧パルスVpassが大きい程、このメモリのしきい値変動は少なくなる。

【0013】

然るして、ビット線BL1乃至BLnのうち0Vが与えられている選択ビット線に接続されているメモリセルで、“0”データの書き込みを行わないメモリセルに対しても、この転送電圧パルスVpassが与えられることになる。従って、この転送電圧パルスVpassが大きい程、しきい値の変動が起こり易くなる。これらを考慮して、転送電圧パルスVpassの最小値と最大値が決定される。

【0014】

通常、この転送電圧パルスVpassと書き込み電圧パルスVppは“0”データのメモリセルのしきい値の分布を小さくし、且つ誤書き込みを少なくする為に、各所定の初期電圧やステップ電圧、最終電圧、パルス幅等が最適化されている「ステップアップ方式」で行われている。

【0015】

一方、データ消去では、NAND型セル内の全てのメモリセルに対して同時に行われる「一括消去」か、或いは所定のバイト単位毎に行われる「ブロック消去」のいずれかが行われる。即ち、全ての或いは選択されたブロック内において全ての制御ゲートを0Vとし、ブロック消去の場合は、非選択ブロックの制御ゲート及び選択ゲートに書き込み電圧パルスVpp(例えば、20V)を印加し、ビット線及びソース線を浮遊状態とし、pウエルに例えば20Vといった高電圧を印加する。これにより、全ての或いは選択されたブロック内の全てのメモリセルにおいて浮遊ゲートの電子がpウエルに放出され、しきい値が負方向に移動する。さらに、データの読み出しは、選択ゲートトランジスタ及び選択メモリセル以外の非選択メモリセルのワード線に読み出し電圧(例えば、4.5V)を印加することによりオン状態とし、選択メモリセルのワード線に0Vが与えられる。この時、ビット線BL1乃至BLn側に流れる電流を検出することにより、“0”、“1”の判定がなされる。

【0016】

【発明が解決しようとする課題】

しかしながら、上述したような従来技術に係るNANDセル型のEEPROMの書き込み方式である「セルフブースト書き込み方式」においては、以下に説明するような問題が生じており、その解決が嘱望されていた。

【0017】

図20はフローティングチャネル書き込み時のメモリセルの各電極、及びメモリセルA、メモリセルBを示すNANDセル型のEEPROMの等価回路の構成を示す図である。上記メモリセルAは、チャネルがフローティング且つワード線に書き込み電圧パルスVppが与えられ、“1”データ書き込みが行われる書き込み非選択メモリセルである。上記メモリセルBは、ビット線に0V、且つワード線に転送電圧パルスVpassが与えられ、書き込みを行わない非選択メモリセルである。ここで、VBLはビット線に与えられる電圧、VSGは選択ゲート線に与えられる電圧、VCGはワード線に与えられる電圧、VSLはソース線に与えられる電圧を示している。ここでは、ビット線BL1乃至BLn側から数えて2番目のメモリセルを選択ワード線としたが、通常動作時は任意のメモリセルが選択される。

【0018】

以下、図21のタイミングチャートを参照して、図20に対応する各電極の電圧とそのタイミングを詳細に説明する。

先ず、ビット線BL1乃至BLnには、書き込むべきデータに対応して、0V或いはVcc(例えば、3.3V)が与えられ、ビット線BL1乃至BLn側の選択ゲートSG1にはVcc(例えば、3.3V)、ソース線SL側の選択ゲートSG2には0Vが与えられる。この状態で、“1”データを書き込むビット線(VBL1 )のNANDセルのチャネルはチャネル電位Vchinitが転送された後、フローティングとなっている。この後、選択ワード線に書き込み電圧パルスVpp、非選択ワード線に転送電圧パルスVpassが与えられ、フローティング状態となっているチャネルが所定の電位Vchにブートされることになる。この時のチャネル電位Vchと各電極の電位との関係は次の式(1)で示される。

【0019】

Vch=Vsg−Vsgth(Vchinit)+Cr1(Vpass−Vpassth−Vchinit)+Cr2(Vpp−Vpassth−Vchinit)

−(Tpw/(16Cins +Cch)・I(1)

尚、上記(1)式において、Vsgth(Vchinit)はチャネル電位がVchinitである時のドレイン側の選択ゲートのしきい値を示し、Cr1はチャネルのブート比(転送電圧パルスVpassが与えられるメモリセルの容量と該パルスVpassによりチャネル下に広がる空乏層容量の比)を示し、Cr2はチャネルのブート比(書き込み電圧パルスVppが与えられるメモリセルの容量と該パルスVppによりチャネル下に広がる空乏層容量の比)を示し、Vpassthはチャネル電位がVchinitである時の転送電圧パルスVpassが与えられるメモリセルがON状態になるために必要な電位を示している。また、Tpwは書き込み電圧パルス幅、Cins はメモリセル1個あたりの容量、Cchはチャネル下に広がる空乏層容量、Iはチャネルからウエルや隣接ビット線に抜ける電流を示している。

【0020】

ここで、上記選択ゲートSG1,SG2やメモリセル、及びこれらを形成する半導体基板中の不純物濃度(pェルに形成するときは、ボロンの不純物濃度等)のプロファイル、選択ゲートSG1,SG2やメモリセルのチャネル部に導入されるチャネルインプラ等の不純物濃度、選択ゲートSG1、SG2やメモリセルのソース・ドレイン拡散層の濃度プロファイル等の選択ゲートやメモリセルを形成する際の様々な条件により、ビット線BL1乃至BLnからチャネルに転送される初期電圧Vchinitの低下、チャネル下の空乏層やその他の0V端子−チャネル間の容量の増大によるチャネルブート効率(Cr1,Cr2)の低下等により、十分なチャネル電位が得られず、“1”データ書き込みのメモリセルのしきい値が変動し、誤書き込みが起こることがある。

【0021】

図22は前述した書き込みを行う場合の転送電圧パルスVpassと“1”データ書き込みのメモリセル(メモリセルA)のしきい値の関係を示す図である。

同図において、縦軸はしきい値を、横軸はVpassを示しており、符号AはセルAの特性を示し、符号BはセルBの特性を示している。

【0022】

この図に示されるように、転送電圧パルスVpassを十分大きくしないとメモリセルAのしきい値は正側に変動する。これに対して、転送電圧パルスVpassを余り大きくしてやると、今度はメモリセルBのしきい値が変動してしまう。

【0023】

このようなしきい値の変動は、メモリセルのゲート幅、ゲート長、ウイング幅、トンネル酸化膜厚、インターポリ絶縁膜(層間絶縁膜)厚等の不均一さに起因する書き込み特性のばらつきが大きくなると、それに従って大きくなる傾向にあり、特に書き込み時の選択ブロックのビット数が大きくなる程、起こり易くなってくる。

【0024】

さらに、フローティング状態のチャネルやソース・ドレイン拡散層とウエル間、或いは隣接ビット線間のリーク電流が大きいと、上記しきい値変動は更に大きくなってしまう。また、ビット線電位をチャネルに転送する、選択ゲートトランジスタの特性のばらつきも大きく影響することになる。

【0025】

このように、メモリセルや選択ゲートトランジスタの特性が誤書き込み特性を悪化させることが判っており、その改善のためには、プロセス上或いは構造上、動作上の改善(文献「1996 Symposium on VLSI Technology Digest of Technical Papaers 」のD.J.Kim 等著の”Process Integration for the High Speed NAND Flash Memory Cell”や”A Novel Booster Plate Technology in High Density NAND Flash Memories for Voltage Scaling −Down and Zero Program Disturbance ”参照)が必要となり、その為、工程の複雑化、工程数の増大、チップ面積の増大等の問題が生じてくる。また、このしきい値の変動が存在すると、読み出しや放置時のメモリセルのデータ保持特性に大きく影響し、信頼性の低下を招くという問題もある。

【0026】

然るに、このような誤書き込みに関する従来の対策法においては、書き込み電圧パルスVppや非選択ワード線の転送電圧パルスVpassを与えるタイミングや立ち上がり、立ち下がり時間に関する記述は無く、実用化もされていない。

【0027】

特に、従来は、書き込み電圧パルスVppと転送電圧パルスVpassに関して、チャネルの電位を該パルスVpassによりブートしている間に上記パルスVppを与えることが最も誤書き込みを小さくするものと考えられていた為、逆に誤書き込みをより大きくしていたという問題があった。

【0028】

ここで、図23は従来の書き込み電圧パルスVppと転送電圧パルスVpassのタイミングを示す図である。同図(a)はVppを、同図(b)はVpassを示す。

同図において、t1,t1’は、それぞれパルスVpp,Vpassを発生する時間、t2,t2’はパルスが立ち上がり、最大値に達する時間、t3,t3’は立ち下がりを開始する時間、t4,t4’は完全にパルスが立ち下がる時間を示している。このような従来技術によれば、パルスVpp、Vpassは、略同時に与えられるか、或いはパルスVppよりもパルスVpassの方が先に出ている必要があるとの考えからパルスVppの方が遅れて与えられ(t1≧t1’)、その為、若干、パルスVpassの方が早めに立ち上がる(t2’<t2)。また、立ち下がりに関しては、同時か或いはパルスVppがでている間はパルスVpassがでている必要が有るという考えから、パルスVpassの方が遅れて立ち下がる(t3≦t3、t4≦t4’)。しかしながら、実際には、ばらつきも含めて厳密にパルスのタイミングが制御されておらず、上記の様なタイミングで、全メモリセルが動作しているとは限らない。この為、より誤書き込みが起こり易くなっていたことが考えられる。

本発明は上記問題に鑑みてなされたもので、その目的とするところは、誤書き込み特性を著しく改善した不揮発性半導体記憶装置を提供することにある。

【0029】

【課題を解決するための手段】

上記目的を達成するために、本発明の第1の態様による不揮発性半導体記憶装置は、ゲートとソースとドレイン及び電荷蓄積層を有する電気的に書き換え可能な複数のメモリセルがマトリクス状に配置されたメモリセルアレイと、前記メモリセルにデータを書き込むデータ書込手段と、前記メモリセルのデータを読み出すデータ読出手段と、前記メモリセルのデータを消去するデータ消去手段と、を有し、前記メモリセルへのデータの書き込みの際、書き込み禁止される所定のメモリセルに対し、ゲートに第1の信号を印加し、ソース及びドレインの少なくともいずれかに容量結合したノードに第2の信号を印加する不揮発性半導体記憶装置において、前記第1の信号が前記第2の信号より遅れて立ち下がるように制御されることを特徴とする。

【0030】

第2の態様による不揮発性半導体記憶装置は、第1の導電型半導体基板及び第2の導電型半導体基板に形成された第1の導電型ウエルの少なくともいずれかに第2の導電型ウエルが形成され、前記第2の導電型ウエル内に形成された第1の導電型のソース、ドレイン拡散層、当該ソース、ドレイン拡散層に挟まれた領域にトンネル絶縁膜を介して形成された電荷蓄積層である浮遊ゲート、及びこの浮遊ゲート上に層間絶縁膜を介して積層された制御ゲートを有し、前記電荷蓄積層と第2の導電型ウエルとの間の電荷の授受によりデータ書き換えを行う書き換え可能な複数のメモリセルが、前記第2の導電型ウエルに配置され、前記複数のメモリセルは、そのソース、ドレインを隣接するもの同士で共用するような形で直列接続されてNANDセルを構成し、これがマトリクスに配列されメモリセルアレイを構成し、上記各NANDセルの一端部のドレインは、選択ゲートを介して列方向に配置されたビット線に接続され、他端部のソースは、選択ゲートを介して複数のNANDセルに共有されたソース線に接続され、各NANDセル内の制御ゲートは行方向に並ぶNANDセルについて連続的に配設されてワード線を構成し、上記各メモリセルに対して、その浮遊ゲートに蓄えられる電荷量により所望のデータを記憶させる為の書き込み動作時に、ソース側の選択ゲートトランジスタをカットオフさせながら、書き込みを行うNANDセルのビット線には、ドレイン側の選択ゲートトランジスタをカットオフさせない第1の電圧を与える一方、書き込み禁止されるNANDセルのビット線には、ドレイン側の選択ゲートトランジスタをカットオフさせる第2の電位を与え、複数のデータについて一括して書き込みを行う不揮発性半導体記憶装置において、書き込みを行うワード線に所定の書き込み電圧パルスが与えられ、書き込みを行わないワード線に所定の転送電圧パルスが与えられる際、これら2つのパルスの立ち下がりのタイミングに関して、書き込み電圧パルスが立ち下がりを開始する時間よりも転送電圧パルスが立ち下がりを開始する時間を早く設定することを特徴とする。

【0031】

第3の態様による不揮発性半導体記憶装置は、第1の導電型半導体基板及び第2の導電型半導体基板に形成された第1の導電型ウエルの少なくともいずれかに第2の導電型ウエルが形成され、前記第2の導電型ウエル内に形成された第1の導電型のソース、ドレイン拡散層、当該ソース、ドレイン拡散層に挟まれた領域にトンネル絶縁膜を介して形成された電荷蓄積層である浮遊ゲート、及びこの浮遊ゲート上に層間絶縁膜を介して積層された制御ゲートを有し、前記電荷蓄積層と第2の導電型ウエルとの間の電荷の授受によりデータ書き換えを行う書き換え可能な複数のメモリセルが、前記第2の導電型ウエルに配置され、前記複数のメモリセルは、そのソース、ドレインを隣接するもの同士で共用するような形で直列接続されてNANDセルを構成し、これがマトリクスに配列されメモリセルアレイを構成し、上記各NANDセルの一端部のドレインは、選択ゲートを介して列方向に配置されたビット線に接続され、他端部のソースは、選択ゲートを介して複数のNANDセルに共有されたソース線に接続され、各NANDセル内の制御ゲートは行方向に並ぶNANDセルについて連続的に配設されてワード線を構成し、上記各メモリセルに対して、その浮遊ゲートに蓄えられる電荷量により所望のデータを記憶させる為の書き込み動作時に、ソース側の選択ゲートトランジスタをカットオフさせながら、書き込みを行うNANDセルのビット線には、ドレイン側の選択ゲートトランジスタをカットオフさせない第1の電圧を与える一方、書き込み禁止されるNANDセルのビット線には、ドレイン側の選択ゲートトランジスタをカットオフさせる第2の電位を与え、複数のデータについて一括して書き込みを行う不揮発性半導体記憶装置において、書き込みを行うワード線に所定の書き込み電圧パルスが与えられ、書き込みを行わないワード線に所定の転送電圧パルスが与えられる際、これら2つのパルスの立ち下がりのタイミングに関して、書き込み電圧パルスが最小値に達する時間よりも転送電圧パルスが最小値に達する時間の方を早く設定することを特徴とする。

【0032】

第4の態様による不揮発性半導体記憶装置は、第1の導電型半導体基板及び第2の導電型半導体基板に形成された第1の導電型ウエルの少なくともいずれかに第2の導電型ウエルが形成され、前記第2の導電型ウエル内に形成された第1の導電型のソース、ドレイン拡散層、当該ソース、ドレイン拡散層に挟まれた領域にトンネル絶縁膜を介して形成された電荷蓄積層である浮遊ゲート、及びこの浮遊ゲート上に層間絶縁膜を介して積層された制御ゲートを有し、前記電荷蓄積層と第2の導電型ウエルとの間の電荷の授受によりデータ書き換えを行う書き換え可能な複数のメモリセルが、前記第2の導電型ウエルに配置され、前記複数のメモリセルは、そのソース、ドレインを隣接するもの同士で共用するような形で直列接続されてNANDセルを構成し、これがマトリクスに配列されメモリセルアレイを構成し、上記各NANDセルの一端部のドレインは、選択ゲートを介して列方向に配置されたビット線に接続され、他端部のソースは、選択ゲートを介して複数のNANDセルに共有されたソース線に接続され、各NANDセル内の制御ゲートは行方向に並ぶNANDセルについて連続的に配設されてワード線を構成し、上記各メモリセルに対して、その浮遊ゲートに蓄えられる電荷量により所望のデータを記憶させる為の書き込み動作時に、ソース側の選択ゲートトランジスタをカットオフさせながら、書き込みを行うNANDセルのビット線には、ドレイン側の選択ゲートトランジスタをカットオフさせない第1の電圧を与える一方、書き込み禁止されるNANDセルのビット線には、ドレイン側の選択ゲートトランジスタをカットオフさせる第2の電位を与え、複数のデータについて一括して書き込みを行う不揮発性半導体記憶装置において、書き込みを行うワード線に所定の書き込み電圧パルスが与えられ、書き込みを行わないワード線に所定の転送電圧パルスが与えられる際、これら2つのパルスの立ち下がりのタイミングに関して、書き込み電圧パルスが立ち下がりを開始する時間よりも転送電圧パルスが立ち下がりを開始する時間を早く設定し、上記2つのパルスの立ち上がりのタイミングに関して、書き込み電圧パルスが立ち上がりを開始する時間よりも転送電圧パルスが立ち上がりを開始する時間の方を早く設定する、ことを特徴とする。

【0033】

【発明の実施の形態】

以下、図面を参照して、本発明の実施の形態について説明する。

本発明の実施の形態は、セルフブースト書き込み方式を用いる全てのEEPROMに対して有効であり、メモリセルの構造、素子分離の構造(LOCOS、トレンチ)、選択ゲートの構造や数、メモリセルに記憶できるデータの数(2値メモリ)、製造方法等に依存せず、その効果を発揮する。

【0034】

図1は本発明に係る不揮発性半導体記憶装置の構成を示す図である。

同図に示される不揮発性半導体記憶装置1において、アドレスレジスタ6の出力は、ワード線駆動回路7、ロウデコーダ4、カラムデコーダ9の入力に接続されており、ワード線駆動回路7の出力はロウデコーダ4の入力に、カラムデコーダ9の出力はビット線制御回路5及びI/Oバッファ10の入力にそれぞれ接続されている。一方、コマンドレジスタ8の出力は、上記ワード線駆動回路7、ロウデコーダ4、I/Oバッファ10、ビット線制御回路5、ウエル電圧制御回路2、ソース線駆動回路11の入力にそれぞれ接続されており、ビット線制御回路5とI/Oバッファ10は相互に接続されている。上記ロウデコーダ4、ウエル電圧制御回路2、ソース線駆動回路11,ビット線制御回路5の出力はメモリセルアレイ3の入力にそれぞれ接続されている。尚、上記メモリセルアレイ3は、詳細には、マトリクス状に形成された複数の不揮発性メモリセルからなる。

【0035】

このような構成において、上記メモリセルアレイ3は、データの書き込み、読み出し又は消去を行う為のものである。ビット線制御回路5は、書き込み時にメモリセルアレイ3のメモリセルに書き込むべきデータをラッチし、或いは読み出し時にビット線に現れる読み出しデータをセンスし、ラッチするものである。I/Oバッファ10は、書き込み時に不揮発性半導体記憶装置1の外部からデータを入力し、ビット線制御回路5に出力するものである。上記カラムデコーダ9は、複数のビット線制御回路5と1つのI/Oバッファ10を相互に接続させるものである。上記ロウデコーダ4は、メモリセルアレイ3の中から入力されたアドレスのブロックを選択するものである。ワード線駆動回路7は、その選択されたメモリセルのワード線に与える電圧を出力するものである。また、上記アドレスレジスタ6は、外部より入力されたアドレスデータをラッチし、選択された特定のメモリセルのワード線とビット線を、カラムデコーダ9,ロウデコーダ4,ワード線駆動回路7を介して選択するものである。上記ウエル電圧制御回路2とソース線駆動回路11は、データの読み出しや書き込み等の動作モードに応じてメモリセルアレイ3のウエルとソースの電位を制御するものである。コマンドレジスタ8は、入力された所定のコマンドに係る読み出し、書き込み、消去命令に応じて本装置の各制御回路に所定の指示信号を送出するものである。

【0036】

ここで、図2は上記メモリセルアレイ3を構成するNANDセルの「ストリング」の詳細な構成を示す図である。

同図に示されるように、1つのストリングでは、M個のメモリセルMC1〜MC4が相互に直列に接続されており、それら接続の両端には選択トランジスタMN13,MN14が接続されている。この選択トランジスタMN13は、更にビット線BLijに接続されており、選択トランジスタMN14は、ソース線SLに接続されている。上記メモリセルMC1からMC4と選択トランジスタMN13,MN14は全て同一のウエル上に形成されている。各メモリセルの制御ゲートは、ワード線WLn1〜WLnM(n=1,・・・,N)に接続される。尚、同一のnに属するメモリセルの集合は、ブロックを構成し、データの操作、即ち書き込み、読み出し及び消去は、ブロック単位で行われる。

【0037】

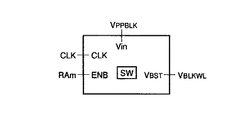

次に図3に上記ロウデコーダ4の具体例の構成を示し説明する。

同図において、選択されたブロックはロウアドレスRAnがHighレベル、選択されないブロックはロウアドレスRAnがLowレベルとなる。図中、点線で囲まれた回路はブースター回路であり、図4はそのブロック構成図である。選択されたブースター回路は、入力クロックCLKによって入力電圧VBLK を昇圧し、信号線VBLKWL に出力する。VBLK の値は、読み出し時にはVread、書き込み時にはVpgm 、消去時にはVccである。

【0038】

ここで、上記Vread、Vpgm は、それぞれ4〜5V、16〜20V程度の大きさであり、Vccは電源電圧である。このように、選択されたロウデコーダでは、転送ゲートトランジスタMN5乃至MN9がオンし、全ブロックに共通な信号GSGD、GWL1乃至GWLM、GSGSは、それぞれSGDn、Wln1乃至WlnM、SGSnに接続される。

【0039】

次に図5はGWL駆動回路の構成を示す図である。

同図において、 第1のブースター回路BST1は、クロック信号RCLKの入力を受ける端子CLKと、信号EreadのインバータI5を介した反転入力と信号Tmの入力を受けたNOR回路G7の信号が入力される端子ENBと、信号Vreadを受ける端子Vinを有しており、これらの入力信号の状態により端子VBST より所定の信号を出力し、トランジスタMN18の状態を制御する。

【0040】

第2のブースター回路BST2は、クロック信号WCLKの入力を受ける端子CLKと、信号Epgm と信号Tmの入力を受けたNAND回路G2の信号のインバータ回路I3を介した反転入力を受ける端子ENBと、信号Vpgm の入力を受ける端子Vinを有し、これらの入力信号状態により端子VBST より所定の信号を出力し、トランジスタMN15の状態を制御する。

【0041】

同様に、第3のブースター回路BST3は、クロック信号WCLKの入力を受ける端子CLKと、信号Evpass のインバータI4を介した反転入力と信号Tmの入力を受けたNOR回路G3の信号の入力を受ける端子ENBと、信号Vpassの入力を受ける端子Vinを有し、これらの状態により端子VBST より信号を出力し、トランジスタMN16の状態を制御する。

【0042】

そして、信号Tmと信号Ereadの入力を受けるNAND回路G6の出力信号のインバータI6を介した信号はトランジスタMN19のゲートに接続されており、この出力信号の状態によりトランジスタMN19の状態が制御される。さらに、上記トランジスタMN18を介した信号Vreadと、トランジスタMN15を介した信号Vpgm と、トランジスタMN16を介した信号Vpassと、トランジスタMN19を介した信号Vmon は、出力端子GWLm へと導かれる同一の信号線に接続されている。

【0043】

更に、同信号線には、そのゲートに信号Tmと信号Evpass の入力を受けるNOR回路G5の出力が接続されたトランジスタMN21のドレインと、そのゲートに信号Tmの反転入力とEvpgmの入力を受けるNOR回路G4の出力が接続されたトランジスタMN20のドレインが接続されている。上記トランジスタMN21とMN20のソースは相互に接続され、その接続端はトランジスタMN22のドレインに接続されている。このトランジスタMN22のゲートには、信号Epgm が入力され、ソースは設置されている。

【0044】

この他、上記信号線には、トランジスタMN17のドレインが接続されており、このトランジスタMN17のゲートには信号Epgm と信号Ereadの入力を受けるNOR回路G0の出力が接続され、そのソースは設置されている。

【0045】

このような構成において、トランジスタMN15,MN16,MN18,MN19の状態に応じて、Vpgm 、Vpass、Vread、Vmon のいずれかが信号GWLmとして後述するタイミングで出力されることになる。

【0046】

図6はGSGD駆動回路の構成を示す図である。

同図に示されるように、この駆動回路では、クロック信号RCLKの入力を受ける端子CLKと、信号Ereadの入力を受ける端子ENBと、信号Vreadの入力を受ける端子Vinを有するブースター回路の端子VBST からの信号によりトランジスタMN23の状態が制御される。上記トランジスタMN23のドレインは信号Vreadの入力端子に接続され、ソースは出力GSGDへと導かれる。上記トランジスタMN23のソースとGSGD端との間にはトランジスタMD1を介して電圧Vcc端が接続されており、このトランジスタMD1のゲートには、信号EreadのインバータI8を介した反転入力が接続される。即ち、EreadによりトランジスタMD1の状態が制御されることになる。このような構成において、トランジスタMN23、MD1の状態に応じてVread、Vccのいずれかが後述する所定のタイミングで出力GSGDより出力されることになる。

【0047】

図7はGSGS駆動回路の構成を示す図である。

同図に示されるように、クロック信号RCLKの入力を受ける端子CLKと信号Ereadの入力を受ける端子ENBと信号Vreadの入力を受ける端子Vinを有するブースター回路の出力端子VBST は、トランジスタMN24のゲートに接続されている。このトランジスタMN24のドレインは、信号Vreadの入力を受け、ソースはトランジスタMN25のドレインに接続されている。信号Eera と信号Ereadの入力を受けるNOR回路G8の出力はトランジスタMN25のゲートに接続されており、このトランジスタMN25のソースは接地されている。信号Eera の入力はトランジスタMD2のゲートに、信号Eera の反転入力はトランジスタMP1のゲートにそれぞれ接続され、このトランジスタMP1のドレインは電圧Vcc端に、ソースはトランジスタMD2のドレインに接続されている。そして、このトランジスタMD2のソースと、上記トランジスタMN24とMN25の接続端は出力GSGSへと導かれている。

【0048】

このような構成において、トランジスタMN24,MN25、トランジスタMP1、MD2の状態に応じて、電圧Vread、Vccのいずれかが出力GSGSより後述するような所定のタイミングで出力されることになる。

【0049】

図8はSL駆動回路の構成を示す図である。

同図に示されるように、信号Epgm のインバータI10を介した出力はトランジスタMP2のゲートに接続され、信号Epgm の出力はトランジスタMD3のゲートに接続されている。トランジスタMP2のドレインは電圧Vcc端に接続され、ソースはトランジスタMD3のドレインに接続されている。一方、信号Ereadの入力端子は、トランジスタMN26のゲートに接続されており、ソースは接地されている。上記トランジスタMD3とMN26の接続端は出力SLへと導かれている。このような構成において、トランジスタMP2,MD3,MN26の状態に応じて、電圧Vccが出力SLとして、後述するような所定のタイミングで出力されることになる。

【0050】

図9はウエル駆動回路の構成を示す図である。

同図に示されるように、信号ECLKの入力を受ける端子CLKと信号Eera の入力を受ける端子ENBと信号Vera の入力を受ける端子Vinを有するブースター回路の出力端子VBST は、トランジスタMN27のゲートに接続されている。このトランジスタMN27のドレインは信号Vera の入力端に、ソースはトランジスタMN28のドレインに接続されている。このトランジスタMN28のゲートには上記信号Eera の反転入力が接続され、ソースは接地されている。そして、トランジスタMN27とMN28の接続端は出力Well側に導かれている。このような構成において、トランジスタMN27,MN28の状態に応じて電圧Vera がウエルに後述するタイミングで出力されることになる。

【0051】

図10はビット線制御回路の構成を示す図である。

同図に示されるように、信号BLijの入力端は、トランジスタMN31、MN30、インバータI12,I13、トランジスタMN29を介して信号IOj の入力端子に接続されている。信号VPRE の入力端はトランジスタMN30を介して上記トランジスタMN31とMN30の接続端に接続されると共にトランジスタMN32のゲートに接続されている。上記インバータI12,I13の接続端はトランジスタMN33、MN34に接続されており、このトランジスタMN33とMN34の接続端はトランジスタMN32のドレインに接続される。上記トランジスタMN31のゲートは信号BLCの入力を受け、トランジスタMN30のゲートは信号PREを入力を受け、トランジスタMN40のゲートは信号BLWRTの入力を受け、トランジスタMN33,34のゲートは信号LCH2,1の入力を受け、トランジスタMN29のゲートは信号CAi の入力を受けるように構成されている。上記インバータI12とトランジスタMN29の接続端はトランジスタMN50のゲートに接続されており、このトランジスタMN50のドレインは信号PFの入力を受けるように構成されている。

【0052】

図14は、GWL駆動回路の二つの入力信号Evpass 、Evpgmを発生する回路の5つの例を示す図である。図中、GはNOR回路、Iはインバータ回路である。図14(a),(b)においては、信号Evpass とEvpgm は略同時にHighレベルになるが、信号Evpgm はEvpassより遅延時間TD だけ遅れて立ち下がる。尚、ここでの遅延回路12の代表的な構成例を図14(f)に示す。また、図14(c)は、信号Evpass 、Evpgm の発生回路としてクロックCLK の周期の2倍、4倍・・・の周期を持った複数のクロックCLK1−Nを発生するバイナリカウンタ(BC)13と、該複数のクロックの論理演算をする論理回路(L1,L2)14で構成した例を示している。さらに、図14(a)、(b)では、立ち上がりはEvpgm、Evpass が略同時にHighレベル、立ち下がりはEvpass が先にLowとなるものであるのに対し、図14(d)、(e)では、それぞれ立ち上がりと立ち下がりともEvpass を早くする回路の構成を示している。尚、図14(c)では、クロック信号を制御することで、どちらのバリエーションも実現可能である。

【0053】

以下、図11乃至図13のタイミングチャートを参照して、本発明の不揮発性半導体記憶装置による書き込み、読み出し及び消去の動作を説明する。

先ず図11を参照して、書き込み動作について説明する。

【0054】

書き込み動作を示す信号Epgm がHighレベルになると、書き込みデータ入力動作が開始される。この書き込みデータは、I/Oバッファ10を介してIO線(IOj)に現れる。選択カラムアドレスCAiがHighレベルになるタイミングで、書き込みデータは、インバータI12、I13で構成されるラッチ回路にラッチされる。ここで、”0”書き込みデータは、ノードN1がLowレベル、ノードN2がHighレベルに対応し、”1”書き込みデータは、ノードN1がHighレベル、ノードN2がLowレベルに対応する。

【0055】

こうしてデータロードが終了すると、メモリセルへの書き込み動作が始まる。制御信号Evpgm、Evpass がHighレベルとなって、クロックCLK、WCLKが動き出すと、選択ワード線には電圧Vpgm が、非選択ワード線には電圧Vpass(〜10V)が印加される。一方、ビット線制御回路の制御信号BLC、BLWRTは、書き込みビット線電圧0Vと書き込み非選択ビット線電圧Vccをビット線に転送するため、電圧Vpassが印加される。書き込み選択されたメモリセルのゲート−チャネル間の電位差はVpgm であり、トンネル電流が流れる結果、メモリセルのデータは”0”となる。

【0056】

書き込みを行わないメモリセル及び書き込み非選択のメモリセルのゲート−チャネル間の電位差は、それぞれVpass又はVpass−Vboast とVpgm −Vboast であり、実質的にトンネル電流が流れないので、メモリセルのデータが保持される。ここで、電圧Vboast は、選択ゲートSGDのソースフォロワでストリングのチャネルに転送された電位がワード線との容量結合によって上昇した電圧を示す。その後、信号Evpass がLowレベルになり、非選択ワード線は0Vになる。さらに、所定時間TD 経過の後、信号EvpgmはLowレベルになり、選択ワード線は0Vになる。書き込み動作を示す信号Epgm がLowレベルになったところで書き込み動作を終了することとなる。

【0057】

次に図12を参照して、書込むべきメモリセルにデータが書き込まれたか否かを確認するためのベリファイ読み出し動作を説明する。

ベリファイ動作は、図12において通常の読み出し動作と異なった部分のみの点線で示し、同じ動作の部分は実線で示す。

【0058】

VPRE はHighレベルとなってビット線BLijはプリチャージされる。PREがLowレベルとなってビット線はフローティングにされる。信号EreadがHighレベルになり、クロックCLK、RCLKが動作し始めると、選択ワード線はVvrfy(〜1V)に、非選択ワード線、選択ゲートGSGD、GSGSはVreadに、それぞれされる。選択ワード線に接続するメモリセルのデータが”1”であればビット線の電位は低下し、一方、”0”であればビット線の電位はプリチャージされたままとなる。直前の書き込み動作のときに”0”ラッチされていた(ビット線に0Vを出力するようにラッチされていた)場合、ビット線に現れたデータが”0”データである場合にはLCH1がHighレベルでラッチは反転し、”1”データである場合にはLCH2がHighレベルでラッチは反転しない。この場合には、直後の書き込み動作時には”1”ラッチ状態(ビット線にVccを出力する)になる。また、直前の書き込み動作時に”1”ラッチされていた場合にはLCH1によってラッチに影響はない。

【0059】

このように、”0”ラッチされていて、且つベリファイ読み出し動作で”1”データであったラッチのみ”0”ラッチ状態を維持し、その他の組み合わせの場合いは”1”ラッチとなる。書き込み対象のメモリセル全てが書き込まれた場合にのみ、プリチャージされフローティングにされた信号PFはHighレベルを維持し、これによって書き込みは終了になる。

【0060】

一方、書き込むべきセルのうちひとつでも書き込み不十分なセルがあるとそのセルに対応したラッチ回路のノードN2はHighレベルであるため、トランジスタMN50はオンし、信号PFはLowレベルになる。信号PFがLowレベルの場合、再書き込み動作が開始する。再書き込み動作及びその後のベリファイ読み出し動作は、信号PFがHighレベルとなったら終了する。

【0061】

次に図12を参照して読み出し動作を説明する。

即ち、ラッチ回路のプリセット動作は以下の通りである。

BLCがLowレベル、VPRE、PRE、LCH2がHighレベルとなって、全てのラッチ回路のノードN1がHighレベル、ノードN2がLowレベルにプリセットされる。その後、ビット線はVPREによってプリチャージされフローティングにされる。信号EreadがHighレベルになり、クロックCLK,RCLKが動作し始めると、選択ワード線は0Vに、非選択ワード線、選択ゲートGSGD,GSGSはVreadに、それぞれされる。

【0062】

選択のメモリセルのデータが”1”であればビット線の電位は低下し、一方、”0”であればビット線の電位はプリチャージされたままとなる。ビット線に現れたデータは、LCH1がHighレベルとなってラッチ回路に取り込まれる。”0”データであればトランジスタMN32はオンするため、ノードN1はLowレベルに反転することになる。

【0063】

一方、”1”データであれば、トランジスタMN32はオフするため、ラッチは反転しない。このラッチされたデータはカラムアドレス信号CAi がHighレベルとなってIO線に転送され、I/Oバッファを介して外部に出力されることになる。

【0064】

次に図13を参照して消去動作を詳細に説明する。

消去動作を示す信号Eera がHighレベルになると、クロックECLK によってメモリセルのウエルの電圧Wellは消去電圧Vera (〜20V)になる。選択されたブロックの全てのワード線は0Vに固定され、ゲート−ウエル間の電位差Vera によってフローティングゲートの電子はウエルに引き抜かれ”1”データとなる。一方、非選択ブロック中のメモリセルのワード線はフローティングのためウエルとの容量比でVera 近くまで上昇する。これらのメモリセルでは、ゲート−ウエル間の電位差が小さいので電子はフローティングゲートに閉じ込められたままでデータは変わらない。

【0065】

以下、上記回路により達成される本発明の実施の形態を説明する。

先ず本発明の第1の実施の形態について説明する。

図15は第1の実施の形態に係る不揮発性半導体記憶装置の書き込み電圧パルスVppと転送電極パルスVpassの立ち上がりに係るタイミングを示したタイミングチャートである。同図(a)はVppを、(b)はVpassを示している。

【0066】

同図に示されるように、この実施の形態では、非選択ワード線の転送電圧パルスVpass(例えば、8V)を与える時間を、選択ワード線の書き込み電圧パルスVpp(例えば、18V)を与える時間よりも十分早くする(t1’<t1且つt2’<t2)。さらに、各メモリセルでのパルスのばらつきを考えて、パルスの立ち上がり時間を例えば5μs とした場合、例えばt1−t1’=3μsとする。

【0067】

これにより、書き込み電圧パルスVppが転送電圧パルスVpassよりも先に出ることはなく、メモリセルのデータパターンによらず、書き込み電圧パルスVppが与えられる“1”書き込みのメモリセルのしきい値変動は少なくなる。ここで、書き込み電圧パルスVpp、転送電圧パルスVpassの立ち下がりのタイミングは、図11に示される通りである。

【0068】

次に本発明の第2の実施の形態について説明する。

図16は第2の実施の形態に係る不揮発性半導体記憶装置の書き込み電圧パルスVppと転送電圧パルスVpassの立ち下がりに係るタイミングを示したタイミングチャートである。同図(a)はVppを、(b)はVpassを示している。

【0069】

同図に示されるように、この実施の形態では、非選択ワード線の転送電圧パルスVpass(例えば8V)が立ち下がりを始める時間を選択ワード線の書き込み電圧パルスVpp(例えば18V)が立ち下がりを始める時間よりも十分早くする(t3’<t3)。さらに、各メモリセルでのパルスのばらつきを考えて、パルスの立ち下がり時間を例えば5μsとした場合、例えば、t3−t3’=3μsとする。これにより、書き込み電圧パルスVppが転送電圧パルスVpassよりも先に下がることはなくなり、書き込み電圧パルスVppが与えられる“1”書き込みのメモリセルのしきい値変動は少なくなる。ここで、書き込み電圧パルスVpp、転送電圧パルスVpassの立ち上がりのタイミングは任意でよいことは勿論である。

【0070】

次に本発明の第3の実施の形態について説明する。

ここでも、図16のタイミングチャートを参照して説明する。

同図に示されるように、この実施の形態では、非選択ワード線の転送電圧パルスVpass(例えば8V)が十分立ち下がる時間を選択ワード線の書き込み電圧パルスVpp(例えば18V)が十分立ち下がる時間よりも十分早くする(t4’<t4)。さらに、各メモリセルでのパルスのばらつきを考えて、パルスの立ち下がり時間を例えば5μsとした場合、例えば、t4−t4’=3μsとする。 これにより、書き込み電圧パルスVppが転送電圧パルスVpassよりも先に立ち下がることはなくなり、書き込み電圧パルスVppが与えられる“1”書き込みのメモリセルのしきい値変動は少なくなる。ここで、書き込み電圧パルスVpp,転送電圧パルスVpassの立ち上がりのタイミングは任意でよいことは勿論である。

【0071】

次に本発明の第4の実施の形態について説明する。

図17は第4の実施の形態に係る不揮発性半導体記憶装置の書き込み電圧パルスVppと転送電圧パルスVpassのタイミングチャートである。この実施の形態では、上記第1及び第2の実施の形態を組み合わせたものであり、より誤書き込みが少ない特性が得られる。同図に示されるように、非選択ワード線の転送電圧パルスVpass(例えば8V)を与える時間を選択ワード線の書き込み電圧パルスVpp(例えば18V)を与える時間よりも十分早くする(t1’<t1かつt2’<t2)。各メモリセルでのパルスのばらつきを考えて、パルスの立ち上がり時間を例えば5μsとした場合、例えば、t1−t1’=3μsとする。

【0072】

また、非選択ワード線の転送電圧パルスVpass(例えば8V)が立ち下がりをはじめる時間を選択ワード線の書き込み電圧パルスVpp(例えば18V)が立ち下がりをはじめる時間よりも十分早くする(t3’<t3)。各メモリセルでのパルスのばらつきを考えて、パルスの立ち下がり時間を例えば5μsとした場合、例えば、t3−t3’=3μsとする。

【0073】

これらにより、書き込み電圧パルスVppが転送電圧パルスVpassよりも先に出ることはなく、かつ、書き込み電圧パルスVppが転送電圧パルスVpassよりも先に立ち下がることはなくなり、メモリセルのデータパターンによらず、書き込み電圧パルスVppが与えられる“1”書き込みのメモリセルのしきい値変動は少なくなる。

【0074】

次に本発明の第5の実施の形態について説明する。

ここでも、図17のタイミングチャートを参照して説明する。

この実施の形態は、上記第1の実施の形態及び第3の実施の形態を組み合わせたものであり、より誤書き込みが少ない特性が得られる。尚、同図(a)はVppを、(b)はVpassを示している。

【0075】

同図に示されるように、この実施の形態では、非選択ワード線の転送電圧パルスVpass(例えば8V)を与える時間を選択ワード線の転送電圧パルスVpp(例えば18V)を与える時間よりも十分早くする(t1’<t1かつt2’<t2)。さらに、各メモリセルでのパルスのばらつきを考えて、パルスの立ち上がり時間を例えば5μsとした場合、例えば、t1−t1’=3μsとする。

【0076】

また、非選択ワード線の転送電圧パルスVpass(例えば8V)が十分立ち下がる時間を選択ワード線の書き込み電圧パルスVpp(例えば18V)が十分立ち下がる時間よりも十分早くする(t4’<t4)。各メモリセルでのパルスのばらつきを考えて、パルスの立ち下がり時間を例えば5μsとした場合、例えば、t4−t4’=3μsとする。

【0077】

これらにより、書き込み電圧パルスVppが転送電圧パルスVpassよりも先に出ることはなく、且つ書き込み電圧パルスVppが転送電圧パルスVpassよりも先に立ち下がることはなくなり、メモリセルのデータパターンによらず、書き込み電圧パルスVppが与えられる“1”書き込みのメモリセルのしきい値変動は少なくなる。

【0078】

以上説明したように、本発明の不揮発性半導体記憶装置によれば、以下に示すような各種の効果を得る(図18参照)。尚、図18において、符号A’は従来方式に係るセルAの特性を示し、符号Aは本発明の方式によるセルAの特性を示し、Vthは“0”データと“1”データの境界を示している。

【0079】

即ち、第1に、本発明によれば、セルフブースト書き込み方式において、パルスVppが立ち下がりを開始する時間よりも、パルスVpassが立ち下がりを開始する時間を早くすること、あるいは、パルスVppが最小値に達する時間よりもパルスVpassが最小値に達する時間の方を早くすることにより、パルスVppが与えられる選択ワード線に接続されている、“1”書き込みを行う書き込み禁止メモリセルのしきい値変動を非常に小さくすることができる。

【0080】

この場合、各パルスVpp,Vpassの立ち上がりのタイミングにはあまり依存せず、絶大な効果が得られる。しかし、この効果はパルスVppが与えられる選択ワード線よりもビット線に近いメモリセルのうち、チャネルがフローティング状態となる。ビット線に接続されているメモリセルのデータがすべて“1”データであるときには十分に得られるが、“0”データが1つでもあると、その効果は小さくなってしまう。

【0081】

従って、ランダムプログラムを許さず、ソース側から順に書き込んで行く書き込み方式の場合に用いられることが望ましい。しかし、ランダムプログラムを許す場合においても、通常のソース側からの書き込み時のしきい値変動が少ないため、誤書き込みはかなりの改善が見られると考えられる。

【0082】

また、この効果は、ソース側から書き込みを行う場合において、一番ビット線に近いワード線が選択されたとき、かつ、チャネルがフローティングとなる書き込み非選択のビット線に接続されているメモリセルのうち、選択ワード線よりもソース線側のすべてのメモリセルが“0”データの場合にもっとも大きくなる。このパターンはランダムプログラムを許さない条件において、もっとも誤書き込みされやすい場合である。

【0083】

従って、大規模のメモリセルを考えたときには大幅なチップの誤書き込み特性の改善が得られ、また、誤書き込みされない場合でも、“1”データのしきい値の変動がより少なくなり、リードディスターブ(読み出し時のしきい値の変動)や、リテンション(室温、高温放置時のしきい値の変動)特性の大幅な改善も期待できる。

【0084】

第2に、本発明によれば、パルスVppが立ち上がりを開始する時間よりもパルスVpassが立ち上がりを開始する時間の方を早くすること、またはパルスVppが最大値に達する時間よりもパルスVpassが最大値に達する時間の方を早くすることにより、メモリセルのデータパターンによらず、さらに誤書き込み特性を改善することができる。

【0085】

この効果は、チャネルがフローティングとなる書き込み非選択のビット線に接続されているメモリセルのデータが“1”データの時で、そのしきい値が負の方向に大きいほど絶大な効果がある。仮に、パルスVppが与えられる選択ワード線以外の非選択ワード線に接続されているメモリセルのデータがすべて“0”データであった場合、パルスVppが選択ワード線に与えられたときにパルスVpassが0Vであると(パルスVppが先に立ち上がった場合)、選択ワード線及び書き込み非選択のビット線に接続されている“1”書き込みの非選択メモリセル以外のメモリセルはカットオフ状態となり、“1”書き込みを行うメモリセルは、ローカルセルフブースト状態となる為、しきい値の変動はほとんどないことになる。

【0086】

一方、この場合より“0”データの数が減るとそれだけカットオフするメモリセルの数が減るために、しきい値の変動が大きくなる。さらに、これらのメモリセルがすべて“1”データの場合は、そのしきい値によりローカルセルフブースト状態になったりならなかったりするので(“1”データでもしきい値が負の側にあまり大きくない場合はメモリセルはカットオフするし、負の側にしきい値が大きい場合はカットオフしない)、しきい値の変動が大きくなる。

【0087】

これらのしきい値の変動は、パルスVpassが立ち上がる前、即ち、フローティング状態であるチャネルがパルスVpassによって持ち上がる前にパルスVppが選択ワード線に与えられるので、この状態の時はチャネルと選択ワード線間の電位差が大きくなるために起こる。従って、パルスVppが立ち上がる前にパルスVpassを十分立ち上がらせておくことにより、データパターンによらず、しきい値変動、及び誤書き込みを少なくできる。

【0088】

即ち、本発明は、上記第1及び第2の効果を組み合わせることにより、“1”書き込み時(パルスVppが与えられる選択ワード線及びチャネルがフローティングとなる書き込みの非選択ビット線に接続されているメモリセルに対する書き込み)におけるしきい値の変動や誤書き込みを大幅に改善する。

【0089】

尚、以上では、パルスVppが与えられる選択ワード線、及びチャネルがフローティングとなる書き込み非選択のビット線に接続されている“1”データを書き込む非選択メモリセルのしきい値変動や誤書き込みについてその改善効果を説明したが、その結果として、0Vが転送されているビット線、及びパルスVpassが与えられている非選択ワード線に接続されているデータを保持すべき非選択メモリセルのしきい値変動や誤書き込みに対しても大きく改善する効果があることは勿論である。

【0090】

即ち、上記第1乃至第2の効果により、パルスVpassをそれほど大きくしなくても良くなる。従って、パルスVpassが誤書き込みの要因となるビット線に0V、ワード線にパルスVpassが与えられる非選択メモリセルについて、パルスVpassが小さくしてしきい値の変動や誤書き込みを少なくすることができる。この結果、“1”データの変動や“0”データへの誤書き込みが大幅に改善され、特により大規模のメモリセルの信頼性が向上する。また、しきい値の変動があると、書き込み後の読み出し(リードディスターブ)や常温、高温放置時(リテンション)の際のマージンも少なくなり、信頼性が劣化するが、本発明により、メモリセルのデータ保持時間の向上も期待できる。

【0091】

【発明の効果】

以上詳述したように、本発明によれば、誤書き込み特性を著しく改善した不揮発性半導体記憶装置を提供することができる。

【図面の簡単な説明】

【図1】本発明に係る不揮発性半導体記憶装置の構成を示す図である。

【図2】メモリセルアレイ3を構成するNANDセルの「ストリング」の詳細な構成を示す図である。

【図3】ロウデコーダ4の具体例の構成を示す図である。

【図4】ロウデコーダ4のブースター回路のブロック構成図である。

【図5】GWL駆動回路の構成を示す図である。

【図6】GSGD駆動回路の構成を示す図である。

【図7】GSGS駆動回路の構成を示す図である。

【図8】SL駆動回路の構成を示す図である。

【図9】ウエル駆動回路の構成を示す図である。

【図10】ビット線制御回路の構成を示す図である。

【図11】本発明の不揮発性半導体記憶装置による書き込み動作を説明するためのタイミングチャートである。

【図12】本発明の不揮発性半導体記憶装置による読み出し動作、及び書き込むべきメモリセルにデータが書き込まれたか否かを確認するためのベリファイ読み出し動作を説明するためのタイミングチャートである。

【図13】本発明の不揮発性半導体記憶装置による消去動作を説明するためのタイミングチャートである。

【図14】GWL駆動回路の二つの入力信号Evpass 、Evpgmを発生する回路の5つの例及び遅延回路12の代表的な構成例を示す図である。

【図15】第1の実施の形態に係る書き込み電圧パルスVppと転送電圧パルスVpassのタイミングチャートを示す図である。

【図16】第2及び第3の実施の形態に係る書き込み電圧パルスVppと転送電圧パルスVpassのタイミングチャートを示す図である。

【図17】第4及び第5の実施の形態に係る書き込み電圧パルスVppと転送電圧パルスVpassのタイミングチャートを示す図である。

【図18】本発明の効果を説明するための図である。

【図19】従来技術に係るNAND型EEPROMメモリセル部の等価回路図である。

【図20】従来技術に係るセルフブースト書き込み方式の各電位を示す等価回路図である。

【図21】従来方式のセルフブースト書き込み方式時の各電位のタイミングチャートである。

【図22】従来方式の誤書き込みを示す図である。

【図23】従来方式の書き込み電圧パルスVppと転送電圧パルスVpassのタイミングチャートを示す図である。

【符号の説明】

1 不揮発性半導体記憶装置

2 ウエル電圧制御回路

3 メモリセルアレイ

4 ロウデコーダ

5 ビット線制御回路

6 アドレスレジスタ

7 ワード線駆動回路

8 コマンドレジスタ

9 カラムデコーダ

10 I/Oバッファ

11 ソース線駆動回路

Claims (10)

- ゲートとソースとドレイン及び電荷蓄積層を有する電気的に書き換え可能な複数のメモリセルがマトリクス状に配置されたメモリセルアレイと、

前記メモリセルにデータを書き込むデータ書込手段と、

前記メモリセルのデータを読み出すデータ読出手段と、

前記メモリセルのデータを消去するデータ消去手段と、

を有し、前記メモリセルへのデータの書き込みの際、書き込み禁止される所定のメモリセルに対し、ゲートに第1の信号を印加し、ソース及びドレインの少なくともいずれかに容量結合したノードに第2の信号を印加する不揮発性半導体記憶装置において、前記第1の信号が前記第2の信号より遅れて立ち下がるように制御されることを特徴とする不揮発性半導体記憶装置。 - 前記第1の信号を起動する信号を、前記第2の信号を起動する信号に対して遅延させる回路を更に有することを特徴とする請求項1に記載の不揮発性半導体記憶装置。

- 前記第1及び第2の信号を起動する信号は、それぞれ第3の信号から得られることを特徴とする請求項2に記載の不揮発性半導体記憶装置。

- 前記第1及び第2の信号を起動する信号を、クロックを発振するクロック発振回路と、このクロックの入力を受け複数のクロックを出力するバイナリカウンタと、前記複数のクロックの論理演算結果を出力する論理回路によって得ることを特徴とする請求項1に記載の不揮発性半導体記憶装置。

- 前記複数のメモリセルのソース及びドレインのいずれかは、互いに直列に接続されていることを特徴とする請求項1に記載の不揮発性半導体記憶装置。

- 前記ノードは、メモリセルのゲート・チャネル間容量を介して前記ソース及びドレインの少なくともいずれかに容量結合することを特徴とする請求項5に記載の不揮発性半導体記憶装置。

- 前記ノードは、前記ソース及びドレインのいずれかが互いに直列に接続された前記複数のメモリセルのうち、書込を行わない所定のメモリセルのゲートであることを特徴とする請求項6に記載の不揮発性半導体記憶装置。

- 第1の導電型半導体基板及び第2の導電型半導体基板に形成された第1の導電型ウエルの少なくともいずれかに第2の導電型ウエルが形成され、

前記第2の導電型ウエル内に形成された第1の導電型のソース、ドレイン拡散層、当該ソース、ドレイン拡散層に挟まれた領域にトンネル絶縁膜を介して形成された電荷蓄積層である浮遊ゲート、及びこの浮遊ゲート上に層間絶縁膜を介して積層された制御ゲートを有し、前記電荷蓄積層と第2の導電型ウエルとの間の電荷の授受によりデータ書き換えを行う書き換え可能な複数のメモリセルが、前記第2の導電型ウエルに配置され、

前記複数のメモリセルは、そのソース、ドレインを隣接するもの同士で共用するような形で直列接続されてNANDセルを構成し、これがマトリクスに配列されメモリセルアレイを構成し、

上記各NANDセルの一端部のドレインは、選択ゲートを介して列方向に配置されたビット線に接続され、他端部のソースは、選択ゲートを介して複数のNANDセルに共有されたソース線に接続され、各NANDセル内の制御ゲートは行方向に並ぶNANDセルについて連続的に配設されてワード線を構成し、

上記各メモリセルに対して、その浮遊ゲートに蓄えられる電荷量により所望のデータを記憶させる為の書き込み動作時に、ソース側の選択ゲートトランジスタをカットオフさせながら、書き込みを行うNANDセルのビット線には、ドレイン側の選択ゲートトランジスタをカットオフさせない第1の電圧を与える一方、書き込み禁止されるNANDセルのビット線には、ドレイン側の選択ゲートトランジスタをカットオフさせる第2の電位を与え、複数のデータについて一括して書き込みを行う不揮発性半導体記憶装置において、

書き込みを行うワード線に所定の書き込み電圧パルスが与えられ、書き込みを行わないワード線に所定の転送電圧パルスが与えられる際、これら2つのパルスの立ち下がりのタイミングに関して、書き込み電圧パルスが立ち下がりを開始する時間よりも転送電圧パルスが立ち下がりを開始する時間を早く設定することを特徴とする不揮発性半導体記憶装置。 - 第1の導電型半導体基板及び第2の導電型半導体基板に形成された第1の導電型ウエルの少なくともいずれかに第2の導電型ウエルが形成され、

前記第2の導電型ウエル内に形成された第1の導電型のソース、ドレイン拡散層、当該ソース、ドレイン拡散層に挟まれた領域にトンネル絶縁膜を介して形成された電荷蓄積層である浮遊ゲート、及びこの浮遊ゲート上に層間絶縁膜を介して積層された制御ゲートを有し、前記電荷蓄積層と第2の導電型ウエルとの間の電荷の授受によりデータ書き換えを行う書き換え可能な複数のメモリセルが、前記第2の導電型ウエルに配置され、

前記複数のメモリセルは、そのソース、ドレインを隣接するもの同士で共用するような形で直列接続されてNANDセルを構成し、これがマトリクスに配列されメモリセルアレイを構成し、

上記各NANDセルの一端部のドレインは、選択ゲートを介して列方向に配置されたビット線に接続され、他端部のソースは、選択ゲートを介して複数のNANDセルに共有されたソース線に接続され、各NANDセル内の制御ゲートは行方向に並ぶNANDセルについて連続的に配設されてワード線を構成し、

上記各メモリセルに対して、その浮遊ゲートに蓄えられる電荷量により所望のデータを記憶させる為の書き込み動作時に、ソース側の選択ゲートトランジスタをカットオフさせながら、書き込みを行うNANDセルのビット線には、ドレイン側の選択ゲートトランジスタをカットオフさせない第1の電圧を与える一方、書き込み禁止されるNANDセルのビット線には、ドレイン側の選択ゲートトランジスタをカットオフさせる第2の電位を与え、複数のデータについて一括して書き込みを行う不揮発性半導体記憶装置において、

書き込みを行うワード線に所定の書き込み電圧パルスが与えられ、書き込みを行わないワード線に所定の転送電圧パルスが与えられる際、これら2つのパルスの立ち下がりのタイミングに関して、書き込み電圧パルスが最小値に達する時間よりも転送電圧パルスが最小値に達する時間の方を早く設定することを特徴とする不揮発性半導体記憶装置。 - 第1の導電型半導体基板及び第2の導電型半導体基板に形成された第1の導電型ウエルの少なくともいずれかに第2の導電型ウエルが形成され、

前記第2の導電型ウエル内に形成された第1の導電型のソース、ドレイン拡散層、当該ソース、ドレイン拡散層に挟まれた領域にトンネル絶縁膜を介して形成された電荷蓄積層である浮遊ゲート、及びこの浮遊ゲート上に層間絶縁膜を介して積層された制御ゲートを有し、前記電荷蓄積層と第2の導電型ウエルとの間の電荷の授受によりデータ書き換えを行う書き換え可能な複数のメモリセルが、前記第2の導電型ウエルに配置され、

前記複数のメモリセルは、そのソース、ドレインを隣接するもの同士で共用するような形で直列接続されてNANDセルを構成し、これがマトリクスに配列されメモリセルアレイを構成し、

上記各NANDセルの一端部のドレインは、選択ゲートを介して列方向に配置されたビット線に接続され、他端部のソースは、選択ゲートを介して複数のNANDセルに共有されたソース線に接続され、各NANDセル内の制御ゲートは行方向に並ぶNANDセルについて連続的に配設されてワード線を構成し、

上記各メモリセルに対して、その浮遊ゲートに蓄えられる電荷量により所望のデータを記憶させる為の書き込み動作時に、ソース側の選択ゲートトランジスタをカットオフさせながら、書き込みを行うNANDセルのビット線には、ドレイン側の選択ゲートトランジスタをカットオフさせない第1の電圧を与える一方、書き込み禁止されるNANDセルのビット線には、ドレイン側の選択ゲートトランジスタをカットオフさせる第2の電位を与え、複数のデータについて一括して書き込みを行う不揮発性半導体記憶装置において、

書き込みを行うワード線に所定の書き込み電圧パルスが与えられ、書き込みを行わないワード線に所定の転送電圧パルスが与えられる際、これら2つのパルスの立ち下がりのタイミングに関して、書き込み電圧パルスが立ち下がりを開始する時間よりも転送電圧パルスが立ち下がりを開始する時間を早く設定し、

上記2つのパルスの立ち上がりのタイミングに関して、書き込み電圧パルスが立ち上がりを開始する時間よりも転送電圧パルスが立ち上がりを開始する時間の方を早く設定する、

ことを特徴とする不揮発性半導体記憶装置。

Priority Applications (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP17225197A JP3557078B2 (ja) | 1997-06-27 | 1997-06-27 | 不揮発性半導体記憶装置 |

| US09/104,163 US6252798B1 (en) | 1997-06-27 | 1998-06-25 | Nonvolatile semiconductor memory device capable of controlling mutual timing of write voltage pulse and transfer voltage pulse |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP17225197A JP3557078B2 (ja) | 1997-06-27 | 1997-06-27 | 不揮発性半導体記憶装置 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| JPH1116381A JPH1116381A (ja) | 1999-01-22 |

| JP3557078B2 true JP3557078B2 (ja) | 2004-08-25 |

Family

ID=15938434

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP17225197A Expired - Fee Related JP3557078B2 (ja) | 1997-06-27 | 1997-06-27 | 不揮発性半導体記憶装置 |

Country Status (2)

| Country | Link |

|---|---|

| US (1) | US6252798B1 (ja) |

| JP (1) | JP3557078B2 (ja) |

Families Citing this family (94)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR100388179B1 (ko) | 1999-02-08 | 2003-06-19 | 가부시끼가이샤 도시바 | 불휘발성 반도체 메모리 |

| JP3575683B2 (ja) | 2000-10-05 | 2004-10-13 | 松下電器産業株式会社 | 多素子型磁気抵抗素子 |

| US7324393B2 (en) | 2002-09-24 | 2008-01-29 | Sandisk Corporation | Method for compensated sensing in non-volatile memory |

| US7196931B2 (en) * | 2002-09-24 | 2007-03-27 | Sandisk Corporation | Non-volatile memory and method with reduced source line bias errors |

| US7327619B2 (en) * | 2002-09-24 | 2008-02-05 | Sandisk Corporation | Reference sense amplifier for non-volatile memory |

| US6987693B2 (en) * | 2002-09-24 | 2006-01-17 | Sandisk Corporation | Non-volatile memory and method with reduced neighboring field errors |

| US7046568B2 (en) * | 2002-09-24 | 2006-05-16 | Sandisk Corporation | Memory sensing circuit and method for low voltage operation |

| US7443757B2 (en) * | 2002-09-24 | 2008-10-28 | Sandisk Corporation | Non-volatile memory and method with reduced bit line crosstalk errors |

| US8755222B2 (en) | 2003-08-19 | 2014-06-17 | New York University | Bipolar spin-transfer switching |

| US7064980B2 (en) * | 2003-09-17 | 2006-06-20 | Sandisk Corporation | Non-volatile memory and method with bit line coupled compensation |

| KR100632637B1 (ko) * | 2004-11-11 | 2006-10-11 | 주식회사 하이닉스반도체 | 낸드 플래시 메모리 소자의 소거 검증방법 및 그 낸드플래시 메모리 소자 |

| US7304890B2 (en) * | 2005-12-13 | 2007-12-04 | Atmel Corporation | Double byte select high voltage line for EEPROM memory block |

| US7349261B2 (en) * | 2006-06-19 | 2008-03-25 | Sandisk Corporation | Method for increasing programming speed for non-volatile memory by applying counter-transitioning waveforms to word lines |

| JP2009094354A (ja) | 2007-10-10 | 2009-04-30 | Toshiba Corp | 不揮発性半導体記憶装置 |

| US9812184B2 (en) | 2007-10-31 | 2017-11-07 | New York University | Current induced spin-momentum transfer stack with dual insulating layers |

| US8218381B2 (en) * | 2009-11-24 | 2012-07-10 | Sandisk Technologies Inc. | Programming memory with sensing-based bit line compensation to reduce channel-to-floating gate coupling |

| US9082950B2 (en) | 2012-10-17 | 2015-07-14 | New York University | Increased magnetoresistance in an inverted orthogonal spin transfer layer stack |

| US9082888B2 (en) | 2012-10-17 | 2015-07-14 | New York University | Inverted orthogonal spin transfer layer stack |

| US8982613B2 (en) | 2013-06-17 | 2015-03-17 | New York University | Scalable orthogonal spin transfer magnetic random access memory devices with reduced write error rates |

| US9263667B1 (en) | 2014-07-25 | 2016-02-16 | Spin Transfer Technologies, Inc. | Method for manufacturing MTJ memory device |

| US9337412B2 (en) | 2014-09-22 | 2016-05-10 | Spin Transfer Technologies, Inc. | Magnetic tunnel junction structure for MRAM device |

| US9728712B2 (en) | 2015-04-21 | 2017-08-08 | Spin Transfer Technologies, Inc. | Spin transfer torque structure for MRAM devices having a spin current injection capping layer |

| US10468590B2 (en) | 2015-04-21 | 2019-11-05 | Spin Memory, Inc. | High annealing temperature perpendicular magnetic anisotropy structure for magnetic random access memory |

| US9853206B2 (en) | 2015-06-16 | 2017-12-26 | Spin Transfer Technologies, Inc. | Precessional spin current structure for MRAM |

| US9773974B2 (en) | 2015-07-30 | 2017-09-26 | Spin Transfer Technologies, Inc. | Polishing stop layer(s) for processing arrays of semiconductor elements |

| US10163479B2 (en) | 2015-08-14 | 2018-12-25 | Spin Transfer Technologies, Inc. | Method and apparatus for bipolar memory write-verify |

| US9741926B1 (en) | 2016-01-28 | 2017-08-22 | Spin Transfer Technologies, Inc. | Memory cell having magnetic tunnel junction and thermal stability enhancement layer |

| JP2018045750A (ja) | 2016-09-16 | 2018-03-22 | 東芝メモリ株式会社 | 半導体記憶装置 |

| US11119936B2 (en) | 2016-09-27 | 2021-09-14 | Spin Memory, Inc. | Error cache system with coarse and fine segments for power optimization |

| US10628316B2 (en) | 2016-09-27 | 2020-04-21 | Spin Memory, Inc. | Memory device with a plurality of memory banks where each memory bank is associated with a corresponding memory instruction pipeline and a dynamic redundancy register |

| US11151042B2 (en) | 2016-09-27 | 2021-10-19 | Integrated Silicon Solution, (Cayman) Inc. | Error cache segmentation for power reduction |

| US10446210B2 (en) | 2016-09-27 | 2019-10-15 | Spin Memory, Inc. | Memory instruction pipeline with a pre-read stage for a write operation for reducing power consumption in a memory device that uses dynamic redundancy registers |

| US10818331B2 (en) | 2016-09-27 | 2020-10-27 | Spin Memory, Inc. | Multi-chip module for MRAM devices with levels of dynamic redundancy registers |

| US10366774B2 (en) | 2016-09-27 | 2019-07-30 | Spin Memory, Inc. | Device with dynamic redundancy registers |

| US10991410B2 (en) | 2016-09-27 | 2021-04-27 | Spin Memory, Inc. | Bi-polar write scheme |

| US10546625B2 (en) | 2016-09-27 | 2020-01-28 | Spin Memory, Inc. | Method of optimizing write voltage based on error buffer occupancy |

| US10360964B2 (en) | 2016-09-27 | 2019-07-23 | Spin Memory, Inc. | Method of writing contents in memory during a power up sequence using a dynamic redundancy register in a memory device |

| US11119910B2 (en) | 2016-09-27 | 2021-09-14 | Spin Memory, Inc. | Heuristics for selecting subsegments for entry in and entry out operations in an error cache system with coarse and fine grain segments |

| US10437491B2 (en) | 2016-09-27 | 2019-10-08 | Spin Memory, Inc. | Method of processing incomplete memory operations in a memory device during a power up sequence and a power down sequence using a dynamic redundancy register |

| US10437723B2 (en) | 2016-09-27 | 2019-10-08 | Spin Memory, Inc. | Method of flushing the contents of a dynamic redundancy register to a secure storage area during a power down in a memory device |

| US10460781B2 (en) | 2016-09-27 | 2019-10-29 | Spin Memory, Inc. | Memory device with a dual Y-multiplexer structure for performing two simultaneous operations on the same row of a memory bank |

| US10665777B2 (en) | 2017-02-28 | 2020-05-26 | Spin Memory, Inc. | Precessional spin current structure with non-magnetic insertion layer for MRAM |

| US10672976B2 (en) | 2017-02-28 | 2020-06-02 | Spin Memory, Inc. | Precessional spin current structure with high in-plane magnetization for MRAM |

| US10032978B1 (en) | 2017-06-27 | 2018-07-24 | Spin Transfer Technologies, Inc. | MRAM with reduced stray magnetic fields |

| US10481976B2 (en) | 2017-10-24 | 2019-11-19 | Spin Memory, Inc. | Forcing bits as bad to widen the window between the distributions of acceptable high and low resistive bits thereby lowering the margin and increasing the speed of the sense amplifiers |

| US10656994B2 (en) | 2017-10-24 | 2020-05-19 | Spin Memory, Inc. | Over-voltage write operation of tunnel magnet-resistance (“TMR”) memory device and correcting failure bits therefrom by using on-the-fly bit failure detection and bit redundancy remapping techniques |

| US10489245B2 (en) | 2017-10-24 | 2019-11-26 | Spin Memory, Inc. | Forcing stuck bits, waterfall bits, shunt bits and low TMR bits to short during testing and using on-the-fly bit failure detection and bit redundancy remapping techniques to correct them |

| US10529439B2 (en) | 2017-10-24 | 2020-01-07 | Spin Memory, Inc. | On-the-fly bit failure detection and bit redundancy remapping techniques to correct for fixed bit defects |

| US10679685B2 (en) | 2017-12-27 | 2020-06-09 | Spin Memory, Inc. | Shared bit line array architecture for magnetoresistive memory |

| US10891997B2 (en) | 2017-12-28 | 2021-01-12 | Spin Memory, Inc. | Memory array with horizontal source line and a virtual source line |

| US10395711B2 (en) | 2017-12-28 | 2019-08-27 | Spin Memory, Inc. | Perpendicular source and bit lines for an MRAM array |

| US10360962B1 (en) | 2017-12-28 | 2019-07-23 | Spin Memory, Inc. | Memory array with individually trimmable sense amplifiers |

| US10516094B2 (en) | 2017-12-28 | 2019-12-24 | Spin Memory, Inc. | Process for creating dense pillars using multiple exposures for MRAM fabrication |

| US10424726B2 (en) | 2017-12-28 | 2019-09-24 | Spin Memory, Inc. | Process for improving photoresist pillar adhesion during MRAM fabrication |

| US10395712B2 (en) | 2017-12-28 | 2019-08-27 | Spin Memory, Inc. | Memory array with horizontal source line and sacrificial bitline per virtual source |

| US10811594B2 (en) | 2017-12-28 | 2020-10-20 | Spin Memory, Inc. | Process for hard mask development for MRAM pillar formation using photolithography |

| US10840436B2 (en) | 2017-12-29 | 2020-11-17 | Spin Memory, Inc. | Perpendicular magnetic anisotropy interface tunnel junction devices and methods of manufacture |

| US10784439B2 (en) | 2017-12-29 | 2020-09-22 | Spin Memory, Inc. | Precessional spin current magnetic tunnel junction devices and methods of manufacture |

| US10546624B2 (en) | 2017-12-29 | 2020-01-28 | Spin Memory, Inc. | Multi-port random access memory |

| US10270027B1 (en) | 2017-12-29 | 2019-04-23 | Spin Memory, Inc. | Self-generating AC current assist in orthogonal STT-MRAM |

| US10367139B2 (en) | 2017-12-29 | 2019-07-30 | Spin Memory, Inc. | Methods of manufacturing magnetic tunnel junction devices |

| US10199083B1 (en) | 2017-12-29 | 2019-02-05 | Spin Transfer Technologies, Inc. | Three-terminal MRAM with ac write-assist for low read disturb |

| US10360961B1 (en) | 2017-12-29 | 2019-07-23 | Spin Memory, Inc. | AC current pre-charge write-assist in orthogonal STT-MRAM |

| US10424723B2 (en) | 2017-12-29 | 2019-09-24 | Spin Memory, Inc. | Magnetic tunnel junction devices including an optimization layer |

| US10236047B1 (en) | 2017-12-29 | 2019-03-19 | Spin Memory, Inc. | Shared oscillator (STNO) for MRAM array write-assist in orthogonal STT-MRAM |

| US10840439B2 (en) | 2017-12-29 | 2020-11-17 | Spin Memory, Inc. | Magnetic tunnel junction (MTJ) fabrication methods and systems |

| US10236048B1 (en) | 2017-12-29 | 2019-03-19 | Spin Memory, Inc. | AC current write-assist in orthogonal STT-MRAM |

| US10886330B2 (en) | 2017-12-29 | 2021-01-05 | Spin Memory, Inc. | Memory device having overlapping magnetic tunnel junctions in compliance with a reference pitch |

| US10236439B1 (en) | 2017-12-30 | 2019-03-19 | Spin Memory, Inc. | Switching and stability control for perpendicular magnetic tunnel junction device |

| US10141499B1 (en) | 2017-12-30 | 2018-11-27 | Spin Transfer Technologies, Inc. | Perpendicular magnetic tunnel junction device with offset precessional spin current layer |

| US10255962B1 (en) | 2017-12-30 | 2019-04-09 | Spin Memory, Inc. | Microwave write-assist in orthogonal STT-MRAM |

| US10319900B1 (en) | 2017-12-30 | 2019-06-11 | Spin Memory, Inc. | Perpendicular magnetic tunnel junction device with precessional spin current layer having a modulated moment density |

| US10339993B1 (en) | 2017-12-30 | 2019-07-02 | Spin Memory, Inc. | Perpendicular magnetic tunnel junction device with skyrmionic assist layers for free layer switching |

| US10229724B1 (en) | 2017-12-30 | 2019-03-12 | Spin Memory, Inc. | Microwave write-assist in series-interconnected orthogonal STT-MRAM devices |

| US10468588B2 (en) | 2018-01-05 | 2019-11-05 | Spin Memory, Inc. | Perpendicular magnetic tunnel junction device with skyrmionic enhancement layers for the precessional spin current magnetic layer |

| US10438996B2 (en) | 2018-01-08 | 2019-10-08 | Spin Memory, Inc. | Methods of fabricating magnetic tunnel junctions integrated with selectors |

| US10438995B2 (en) | 2018-01-08 | 2019-10-08 | Spin Memory, Inc. | Devices including magnetic tunnel junctions integrated with selectors |

| US10446744B2 (en) | 2018-03-08 | 2019-10-15 | Spin Memory, Inc. | Magnetic tunnel junction wafer adaptor used in magnetic annealing furnace and method of using the same |

| US10388861B1 (en) | 2018-03-08 | 2019-08-20 | Spin Memory, Inc. | Magnetic tunnel junction wafer adaptor used in magnetic annealing furnace and method of using the same |

| US11107978B2 (en) | 2018-03-23 | 2021-08-31 | Spin Memory, Inc. | Methods of manufacturing three-dimensional arrays with MTJ devices including a free magnetic trench layer and a planar reference magnetic layer |

| US10784437B2 (en) | 2018-03-23 | 2020-09-22 | Spin Memory, Inc. | Three-dimensional arrays with MTJ devices including a free magnetic trench layer and a planar reference magnetic layer |

| US11107974B2 (en) | 2018-03-23 | 2021-08-31 | Spin Memory, Inc. | Magnetic tunnel junction devices including a free magnetic trench layer and a planar reference magnetic layer |

| US20190296228A1 (en) | 2018-03-23 | 2019-09-26 | Spin Transfer Technologies, Inc. | Three-Dimensional Arrays with Magnetic Tunnel Junction Devices Including an Annular Free Magnetic Layer and a Planar Reference Magnetic Layer |

| US10411185B1 (en) | 2018-05-30 | 2019-09-10 | Spin Memory, Inc. | Process for creating a high density magnetic tunnel junction array test platform |

| US10593396B2 (en) | 2018-07-06 | 2020-03-17 | Spin Memory, Inc. | Multi-bit cell read-out techniques for MRAM cells with mixed pinned magnetization orientations |

| US10692569B2 (en) | 2018-07-06 | 2020-06-23 | Spin Memory, Inc. | Read-out techniques for multi-bit cells |

| US10600478B2 (en) | 2018-07-06 | 2020-03-24 | Spin Memory, Inc. | Multi-bit cell read-out techniques for MRAM cells with mixed pinned magnetization orientations |

| US10559338B2 (en) | 2018-07-06 | 2020-02-11 | Spin Memory, Inc. | Multi-bit cell read-out techniques |

| US10650875B2 (en) | 2018-08-21 | 2020-05-12 | Spin Memory, Inc. | System for a wide temperature range nonvolatile memory |

| US10699761B2 (en) | 2018-09-18 | 2020-06-30 | Spin Memory, Inc. | Word line decoder memory architecture |

| US10971680B2 (en) | 2018-10-01 | 2021-04-06 | Spin Memory, Inc. | Multi terminal device stack formation methods |

| US11621293B2 (en) | 2018-10-01 | 2023-04-04 | Integrated Silicon Solution, (Cayman) Inc. | Multi terminal device stack systems and methods |

| US10580827B1 (en) | 2018-11-16 | 2020-03-03 | Spin Memory, Inc. | Adjustable stabilizer/polarizer method for MRAM with enhanced stability and efficient switching |

| US11107979B2 (en) | 2018-12-28 | 2021-08-31 | Spin Memory, Inc. | Patterned silicide structures and methods of manufacture |

Family Cites Families (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| KR960008823B1 (en) * | 1993-11-30 | 1996-07-05 | Samsung Electronics Co Ltd | Non-volatile semiconductor memory device |

| KR0145475B1 (ko) * | 1995-03-31 | 1998-08-17 | 김광호 | 낸드구조를 가지는 불휘발성 반도체 메모리의 프로그램장치 및 방법 |

| KR0172441B1 (ko) * | 1995-09-19 | 1999-03-30 | 김광호 | 불휘발성 반도체 메모리의 프로그램 방법 |

-

1997

- 1997-06-27 JP JP17225197A patent/JP3557078B2/ja not_active Expired - Fee Related

-

1998

- 1998-06-25 US US09/104,163 patent/US6252798B1/en not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| US6252798B1 (en) | 2001-06-26 |

| JPH1116381A (ja) | 1999-01-22 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP3557078B2 (ja) | 不揮発性半導体記憶装置 | |

| JP3886673B2 (ja) | 不揮発性半導体記憶装置 | |

| US6285591B1 (en) | Method for programming an electrically erasable and programmable non-volatile semiconductor memory with automatic write-verify controller | |

| US8493785B2 (en) | Page-buffer and non-volatile semiconductor memory including page buffer | |

| US6856544B2 (en) | Semiconductor memory device in which source line potential is controlled in accordance with data programming mode | |

| JP3940570B2 (ja) | 半導体記憶装置 | |

| JPH076593A (ja) | 不揮発性半導体メモリ装置 | |

| JP2004127346A (ja) | 不揮発性半導体メモリ装置 | |

| JPH09106686A (ja) | 不揮発性半導体メモリのプログラム方法 | |

| JP2008140488A (ja) | 半導体記憶装置 | |

| JPH11177071A (ja) | 不揮発性半導体記憶装置 | |

| US7382651B2 (en) | Nonvolatile semiconductor memory device | |

| JP2010073246A (ja) | 不揮発性半導体記憶装置 | |

| JPH10144892A (ja) | 不揮発性半導体メモリ装置 | |

| KR20050008725A (ko) | 선 소거 단계를 이용하여 플래시 메모리를 소거하는 방법 | |

| JP4426082B2 (ja) | 読出時間を短縮させる不揮発性半導体メモリ装置 | |

| CN112530486B (zh) | 半导体存储装置 | |

| JPH10188578A (ja) | 不揮発性半導体記憶装置とその制御方法、メモリカード、及び記憶システム | |

| WO2006059375A1 (ja) | 半導体装置および半導体装置の制御方法 | |

| US20110075489A1 (en) | Non-volatile semiconductor memory device | |

| US7692967B2 (en) | Method of programming a nonvolatile memory device using hybrid local boosting | |

| JP3350308B2 (ja) | 不揮発性半導体記憶装置 | |

| JP2009301691A (ja) | 不揮発性半導体記憶装置 | |

| KR20100022228A (ko) | 불휘발성 메모리 소자 및 그 동작 방법 | |

| JP2006331476A (ja) | 不揮発性半導体記憶装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20040319 |

|

| TRDD | Decision of grant or rejection written | ||

| A01 | Written decision to grant a patent or to grant a registration (utility model) |

Free format text: JAPANESE INTERMEDIATE CODE: A01 Effective date: 20040511 |

|

| A61 | First payment of annual fees (during grant procedure) |

Free format text: JAPANESE INTERMEDIATE CODE: A61 Effective date: 20040514 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090521 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20090521 Year of fee payment: 5 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20100521 Year of fee payment: 6 |

|

| FPAY | Renewal fee payment (event date is renewal date of database) |

Free format text: PAYMENT UNTIL: 20110521 Year of fee payment: 7 |

|

| LAPS | Cancellation because of no payment of annual fees |