JP2007180428A - 電子部品及びその製造方法 - Google Patents

電子部品及びその製造方法 Download PDFInfo

- Publication number

- JP2007180428A JP2007180428A JP2005379684A JP2005379684A JP2007180428A JP 2007180428 A JP2007180428 A JP 2007180428A JP 2005379684 A JP2005379684 A JP 2005379684A JP 2005379684 A JP2005379684 A JP 2005379684A JP 2007180428 A JP2007180428 A JP 2007180428A

- Authority

- JP

- Japan

- Prior art keywords

- electronic component

- unfired

- laminate

- conductor pattern

- terminal electrodes

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Landscapes

- Manufacturing Cores, Coils, And Magnets (AREA)

- Coils Or Transformers For Communication (AREA)

- Fixed Capacitors And Capacitor Manufacturing Machines (AREA)

Abstract

【課題】電子部品が低背化しても電子部品の強度を十分に確保することができ、しかも設計上の自由度及び電気的特性を向上させることができる電子部品を提供する。

【解決手段】本発明の電子部品10は、複数の絶縁層11Aが積層された積層体11と、この積層体11内に形成された導体パターン12と、この導体パターン12の両端部と電気的に接続され且つ積層体11の両側面に形成された一対の外部電極13A、13Bと、を備え、積層体11の実装面の両端部に埋められた一対の端子電極14A、14Bを有し、これらの端子電極14A、14Bは積層体11の実装面の実装面で露出していると共にその実装面と同一面を形成している。

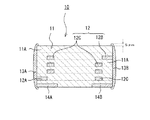

【選択図】図1

【解決手段】本発明の電子部品10は、複数の絶縁層11Aが積層された積層体11と、この積層体11内に形成された導体パターン12と、この導体パターン12の両端部と電気的に接続され且つ積層体11の両側面に形成された一対の外部電極13A、13Bと、を備え、積層体11の実装面の両端部に埋められた一対の端子電極14A、14Bを有し、これらの端子電極14A、14Bは積層体11の実装面の実装面で露出していると共にその実装面と同一面を形成している。

【選択図】図1

Description

本発明は、携帯電話や電子機器等に使用されるインダクタ等の電子部品及びその製造方法に関し、更に詳しくは、電子部品が低背化しても設計上の自由度を向上させて所望の特性を得ることができる電気的特性に優れた電子部品及びその製造方法に関するものである。

この種の技術としては、例えば特許文献1に記載に記載されたインダクタ及びその製造方法がある。この技術では概ね以下のようにしてインダクタを製造する。例えばキャリアフィルム上に外装として絶縁基板の代わりに感光性絶縁ペーストを印刷、露光して硬化させて未焼成の絶縁層を形成する。その上に感光性導体ペーストを塗布し、露光、現像を行い未焼成の導体パターン層を形成する。引き続き、感光性絶縁ペーストを用いて印刷、露光、現像を行い、層間接続用のスルーホールをもつ絶縁層を形成する。この工程を繰り返し、所望の特性に応じて絶縁層と導体パターン層を交互に積層した後、外装を形成して未焼成の積層体を作製する。次いで、個々の電子部品となるように未焼成の積層体を分割し、一括して焼成して個々の積層体を得る。その後、例えば導体ペーストを用いてディップ方式で積層体の両側面に外部電極の下地層及び端子電極を形成した後、メッキ処理を行ってメッキ層を形成し、インダクタを得る。このような構成により、配線パターンの多ターン化と多層化とを可能し、高インダクタンス化と低直流抵抗化とを実現したインダクタを得ることができる。

また、特許文献2には特許文献1のインダクタと同種のチップ部品に関する技術が記載されている。この技術では、絶縁膜と導体パターンを適宜な順に積層し、内部に導体パターンが螺旋状に繋がったコイルを内蔵するチップ本体を得る。そして、チップ本体の対向二面に内蔵コイルのコイル軸に沿う外部電極を設けて積層インダクタを得る。チップ本体の上面、底面で外部電極面に隣接する両縁部に、端面側が深くて順次浅くなる略テーパ形状の凹所を形成し、次いで外部電極をディップ方式で形成する。これにより、隣接4面の一部(凹所を含む)を導体膜が隙間なく満たして平坦な表面が得られ、転がり難く天地の向き姿勢を正しく得ることができ、方向性を有するチップ部品を得ることができる。

しかしながら、特許文献1のインダクタでは、図4で模式的に示すようにディップ方式でインダクタ本体1の両側面に外部電極2A、2Bと端子電極3A、3Bとを同時に形成する際に端子電極3A、3Bとして十分な接続部を確保するために、インダクタ本体1の両側面を導体ペースト内に深く浸漬しなくては端子電極3A、3Bとしての接続部を十分に確保することができない。また、外部電極2A、2Bとしては、通常厚膜導体ペーストを使用する関係上、インダクタ本体1を厚膜導体ペーストに深く浸漬すると外部電極2A、2Bが厚くなり、しかも他の4面への導体ペーストの回り込み量が多くなって、端子電極3A、3Bがインダクタ本体1の他の4面の端部において大きく盛り上がり、同図に示すようにインダクタ本体1からの突出量が例えば20μm程度の高さになり、インダクタ等の電子部品の低背化を障害するばかりでなく、上下の突出量分だけインダクタ本体1の高さ(厚さ)を犠牲にせざるを得ない。その結果、インダクタとしての強度が低下し、しかもその電気的特性が制限されて設計上の自由度が低下することになる。尚、図4において、4はインダクタ本体1内で矩形状の螺旋状に形成されたコイルであり、4A、4Bはそれぞれ外部電極2に接続された引き出し電極である。

また、特許文献2のチップ部品は、チップ部品本体の上面、底面で外部電極面に隣接する両縁部に端面側が深くて順次浅くなる略テーパ形状の凹所を形成し、その後ディップ方式で外部電極を形成するため、端子電極となる部分はチップ本体から突出しないが、チップ部品本体の端部に凹所を設けるために特殊な材料を使用したり、特殊な工法を採用しなくてはならないなど製造工程が煩雑になる。しかも、チップ部品本体の導体パターンをスクリーン印刷で形成するため、チップ部品が小型化するほどスクリーン印刷で導体パターンを形成することが難しくなる。

本発明は、上記課題を解決するためになされたもので、電子部品が低背化しても電子部品の強度を十分に確保することができ、しかも設計上の自由度及び電気的特性を向上させることができる電子部品及びその製造方法を提供することを目的としている。

本発明の請求項1に記載の電子部品は、複数の絶縁層が積層された積層体と、この積層体内に形成された導体パターンと、この導体パターンの両端部と電気的に接続され且つ上記積層体の両側面に形成された一対の外部電極と、を備え、上記積層体の実装面の両端部に埋められた一対の端子電極を有し、上記各端子電極は上記実装面で露出していると共に上記実装面と同一面を形成していることを特徴とするものである。

また、本発明の請求項2に記載の電子部品は、請求項1に記載の発明において、上記各端子電極は、上記積層体の両側面に露出していることを特徴とするものである。

また、本発明の請求項3に記載の電子部品の製造方法は、未焼成の絶縁層と未焼成の導体パターン層とを交互に積層して焼成し導体パターンを内蔵する積層体を作製する第1の工程と、上記積層体の両側面全面に一対の外部電極を設けると共にこれらの外部電極を上記導体パターンの両端と電気的に接続する第2の工程と、を備えた電子部品の製造方法において、上記第1の工程は、上記積層体となる未焼成の絶縁層の実装面側の両端部を未焼成の一対の端子電極で埋める工程を有することを特徴とするものである。

また、本発明の請求項4に記載の電子部品の製造方法は、請求項3に記載の発明において、上記第1の工程は、キャリアフィルム上に上記未焼成の各端子電極を形成する工程と、上記キャリアフィルム上で上記各端子電極をそれぞれ覆って上記未焼成の絶縁層を形成する工程と、を有することを特徴とするものである。

また、本発明の請求項5に記載の電子部品の製造方法は、請求項3または請求項4に記載の発明において、上記第1の工程では、未焼成の上記絶縁層と未焼成の上記導体パターン層とを積層する際のアライメントマークを上記未焼成の各端子電極と同時に形成することを特徴とするものである。

また、本発明の請求項6に記載の電子部品の製造方法は、請求項3〜請求項5に記載の発明において、上記未焼成の各端子電極は、上記未焼成の積層体の両側面に露出していることを特徴とするものである。

本発明の請求項1〜請求項6に記載の発明によれば、電子部品が低背化しても電子部品の強度を十分に確保することができ、しかも設計上の自由度及び電気的特性を向上させることができる電子部品及びその製造方法を提供することができる。

以下、図1〜図3に示す実施形態に基づいて本発明について説明する。

本実施形態の電子部品10は、例えば図1、図2に示すように、複数の絶縁層11Aが積層された積層体11と、積層体11の内部に上下方向に略矩形状の螺旋状に形成された導体パターン12と、導体パターン12の両端部と電気的に接続され且つ積層体11の左右両側面に形成された一対の外部電極13A、13Bと、を備えている。

積層体11の下面は、図1に示すように電子部品10をマザーボード等の実装基板に実装する時の実装面として形成され、この実装面を形成する絶縁層11Aの左右両端部には一対の端子電極14A、14Bが設けられている。これらの端子電極14A、14Bは、それぞれ絶縁層11Aの両端部を埋めて絶縁層11Aの実装面と同一面を形成すると共に、それぞれの外側の端面が絶縁層11Aの左右両端面の一部として露出している。即ち、最下層の絶縁層11Aの両端部には切欠部が形成され、これらの切欠部に左右一対の端子電極14A、14Bが埋め込まれている。

導体パターン12は、例えば図2で積層体11を分解して示すように、所定の渦巻状に形成された導体パターン層12Cが上下の絶縁層11A、11Aの界面に配置して複数積層して形成されている。上下の導体パターン層12C、12Cはそれぞれ該当する絶縁層11Aを所定のパターンで貫通するスルーホール導体12Dによって電気的に接続されている。従って、導体パターン12は、全体として複数の導体パターン層12Cとスルーホール導体12Dとで上下方向に延びる螺旋状のコイルとして形成されている。最下層の導体パターン層12Cには左側の外部電極13Aに接続された引き出し電極12Aが積層体11の左側面に露出して形成され、最上層の導体パターン層12Cには右側の外部電極13Bに接続された引き出し電極12Bが積層体11の右側面に露出して形成されている。

一対の外部電極13A、13Bは、図1に示すように、積層体11の左右両側面全面を被覆するように形成され、それぞれの外周縁部が積層体11の両側面を除く他の4面の端部全周を覆っている。従って、これらの外部電極13A、13Bの端部は、積層体11の実装面及び両側面に露出した一対の端子電極14A、14Bに電気的に接続されている。

本実施形態では端子電極14A、14Bは、上述したように積層体11の実装面の両端部を埋め、それぞれの外側端面が積層体11の両側面に露出していると共に下面全面が実装面として露出しているため、外部電極13A、13Bで少なくとも積層体11の左右両側面を被覆するだけで、外部電極13A、13Bとそれぞれの端子電極14A、14Bとを確実に接続することができる。従って、後述するようにディップ方式で積層体11の両端面に外部電極13A、13Bを形成する場合でも、従来のように積層体11の両側面を導体ペースト内に深く浸漬する必要がなく、導体ペーストの回り込み量が少なく、外部電極13A、13Bの積層体11の両側面以外の他の4面からの突出量を従来と比較して格段に低くし、例えば0.4mm×0.2mmサイズの積層インダクタでは5μm程度の突出量で済ますことができ、従来の1/4程度に抑制することができる。従って、外部電極13A、13Bの突出量が低くなった分だけ積層体11自体を高く(厚く)して、設計上の自由度及び電気的特性を向上させることができ、電子部品が低背化しても電子部品の強度を十分に確保することができる。

而して、絶縁層11Aは、セラミック粉末を含む感光性絶縁ペーストから形成することができる。セラミック粉末は、特に制限されないが、セラミック粉末として、例えば、主成分としてK2O−B2O3−SiO2系ガラス粉末を含み、副成分としてBi2O3−B2O3−SiO2系ガラス粉末を含むものを使用することができる。副成分であるBi2O3−B2O3−SiO2系ガラス粉末は、軟化点が450〜550℃でK2O−B2O3−SiO2系ガラス粉末と比較して融点が低いため、本発明では、セラミック粉末の主成分より融点の低いガラス粉末を低融点ガラス粉末として定義する。

また、導体パターン12、外部電極13A、13B及び端子電極14A、14Bは、いずれも金属粉末を含む感光性導体ペーストから形成することができる。金属粉末は、特に制限されないが、金属粉末として、例えば、銀粉末、銅粉末等を使用することができる。また、セラミック粉末としては、上述したK2O−B2O3−SiO2系ガラス粉末の他、銀粉末、銅粉末等の金属粉末と同時焼成可能なセラミックガラス粉末を二種以上適宜組み合わせて使用しても良い。

次に、図3を参照しながら本発明の電子部品の製造方法の一実施形態について説明する。本実施形態の電子部品10は、フォトリソグラフィ法を用いて製造することができる。

本実施形態では、予め、積層体11を作製するためのベース基材としてキャリアフィルムを準備する。また、感光性導体ペーストとしては、例えば粒径0.5〜3.0μmの銀粉末を含むものを準備し、感光性絶縁ペーストとしては、例えば粒径0.5〜3.0μmのセラミック粉末を含むもの準備する。セラミック粉末は、例えば、K2O−B2O3−SiO2系ガラス粉末を主成分として含み、Bi2O3−B2O3−SiO2系ガラス粉末を副成分として含んでいる。本実施形態では、低融点ガラス粉末がセラミック粉末中に5wt%含まれている。

電子部品10を製造する場合には、図3の(a)に示すように例えば4インチ角で50μmのキャリアフィルム100を配置し、このキャリアフィルム100の上面に、スクリーン印刷で導体ペーストを所定のパターンで塗布して、0.4mm×0.2mmサイズの積層インダクタの未焼成の端子電極114A、114Bを形成すると同時にアライメントマーク115を所定のパターンで形成する。アライメントマーク115は、後述のように順次積層する未焼成の絶縁層及び導体パターンを形成するためのフォトマスクの位置決めを行うためのマークである。尚、4インチ角サイズのキャリアフィルム上には積層インダクタとなる未焼成の積層体が同時に複数個形成される。

次いで、図3の(b)に示すようにキャリアフィルム100の上面に感光性絶縁ペーストを塗布して未焼成の端子電極114A、114Bを覆った後、全面に紫外線等の光を照射して感光性絶縁ペーストを硬化させて積層インダクタの外装となる絶縁層部111Aを形成する。この時、未焼成の端子電極114A、114Bの外側の端面は絶縁層111Aの端面と実質的に一致して形成されている。

その後、絶縁層部111A全面に感光性導体ペーストを塗布して感光性導体ペースト層部を形成した後、引き出し電極12A及び渦巻状の導体パターン層12Cに即した透孔を有するフォトマスク(図示せず)を絶縁層部111Aの上方に配置し、アライメントマーク115を基準に位置決めを行う。位置決め後、感光性導体ペースト層部にフォトマスクを介して光を照射し、図3の(c)に示すように感光性導体ペースト層の引き出し電極部112Aと導体パターン層部112Cとを一体的に硬化させ、未硬化の部分を現像処理により除去して、引き出し電極部112Aと

導体パターン層部121Cとを同時に形成すると共に絶縁層部111Aを露出させる。

導体パターン層部121Cとを同時に形成すると共に絶縁層部111Aを露出させる。

引き続き、フォトマスクを介してレーザ光を所定のパターンで照射するフォトリソグラフィ法を用いて、絶縁層部111Aの上面にスルーホールを有する絶縁層部111Aと導体パターン層部112Cをこの順序で交互に必要な層数だけ積層する。そして、最終的に最上層の導体パターン層部112C及び引き出し電極部112Bを形成した後、積層インダクタの外装としての絶縁層部111Aを最上層に形成して、図3の(d)に示す未焼成の積層体111を得る。この未焼成の積層体111からキャリアフィルム100を剥離して、同図の(e)に示す未焼成の積層体111を得る。この未焼成の積層体111を個々の積層インダクタになるように所定の大きさにダイシングにより分割した後、所定の温度、例えば850〜900℃の温度で個々の未焼成の積層体111を焼成して図1に示す0.4mm×0.2mmサイズの積層体11を得る。

一対の端子電極14A、14Bは、積層体11の実装面の両端部で露出していると共に積層体11の両側面に露出しているため、導体ペーストを積層体11の両側面に塗布して外部電極13A、13Bを形成するだけで、導体パターン12は、外部電極13A、13Bを介して端子電極端子14A、14Bに接続される。従って、外部電極13A、13Bを積層体11の両側面に形成する場合には、積層体11の両側面(導体パターン12の引き出し電極12A、12Bが露呈する側面)を、それぞれ導体ペーストに浅く漬けるだけで導体パターン12と端子電極14A、14Bを接続する外部電極13A、13Bの下地層部を形成することができる。

外部電極13A、13Bの下地層部を形成した後、下地層部を所定の温度で積層体11に焼き付けて下地層を形成し、更に、この下地層に上層としてメッキ処理を施してメッキ層を形成して図1に示す外部電極13A、13Bを有する積層インダクタ10を得ることができる。

以上説明したように本実施形態によれば、複数の絶縁層11Aが積層された積層体11と、この積層体11内に形成された導体パターン12と、この導体パターン12の両端と電気的に接続され且つ積層体11の両側面に形成された一対の外部電極13A、13Bと、を備え、積層体11の実装面の両端部に埋められた一対の端子電極14A、14Bを有し、これらの端子電極14A、14Bは積層体11の実装面で露出していると共にその実装面と同一面を形成しているため、導体ペーストを用いて一対の端子電極14A、14Bを形成する必要がなく、外部電極13A、13Bの外周端部の積層体11の4面からの突出量を抑制することができ、延いては積層インダクタ10を低背化しても積層体11の強度を十分に確保することができ、積層インダクタ10の設計上の自由度及び電気的特性を向上させることができる。また、各端子電極14A、14Bは、積層体11の両側面に露出しているため、積層体11の両側面に外部電極13A、13Bを形成すれば、導体パターン12の両端部と端子電極14A、14Bとを電気的に確実に接続することができる。

また、本実施形態の電子部品の製造方法によれば、未焼成の絶縁層111Aと未焼成の導体パターン層112Cとを交互に積層して焼成し導体パターン12を内蔵する積層体11を作製する第1の工程と、積層体11の両側面全面に一対の外部電極13A、13Bを設けると共にこれらの外部電極13A、13Bを導体パターン12の両端と電気的に接続する第2の工程と、を備え、第1の工程は、積層体11となる未焼成の絶縁層111Aの実装面の両端部を未焼成の一対の端子電極114A、114Bで埋める工程を有するため、外部電極13A、13Bを形成する際に、端子電極14A、14Bに相当する部分を外部電極13A、13Bと同時に形成する必要がなく、外部電極13A、13Bの積層体11からの突出量を抑制し、その分だけ積層体11の厚みを確保して設計上の自由度及び電気的特性を向上させることができる。

また、本実施形態によれば、第1の工程は、キャリアフィルム100上に未焼成の各端子電極114A、114Bを形成する工程と、キャリアフィルム100上で各端子電極114A、114Bをそれぞれ覆って未焼成の絶縁層111Aを形成する工程と、を有するため、積層体11となる未焼成の絶縁層111Aの実装面の両端部を未焼成の一対の端子電極114A、114Bで確実に埋めることができる。

また、第1の工程では、未焼成の絶縁層111Aと未焼成の導体パターン層111Cとを積層する際のアライメントマーク115を未焼成の各端子電極114A、114Bと同時に形成するため、未焼成の各端子電極114A、114Bに、その他の未焼成の絶縁層111A及び導体パターン層112C等を、アライメントマーク115を基準にして積層することができ、積層インダクタ10を高精度に製造することができる。また、未焼成の各端子電極114A、114Bは、未焼成の積層体111の両側面に露出しているため、積層体11の両側面に露出した端子電極14A、14Bを得ることができ、延いては外部電極13A、13Bを積層体11の両側面に形成するだけで導体パターン12の両端部と端子電極14A、14Bとを電気的に確実に接続することができる。

尚、上記実施形態では電子部品として積層インダクタを製造する場合について説明したが、表面実装電子部品であれば、本発明を適用することができる。

本発明は、携帯電話や電子機器等に使用される電子部品、特に表面実装電子部品に好適に利用することができる。

10 電子部品

11 積層体

11A 絶縁層

12 導体パターン

12A、12B 引き出し電極部(導体パターンの端部)

13A、13B 外部電極

14A、14B 端子電極

13A、13B 外部電極

100 キャリアフィルム

111 未焼成の積層体

111A 未焼成の絶縁層

112C 未焼成の導体パターン層

114A、114B 未焼成の端子電極

11 積層体

11A 絶縁層

12 導体パターン

12A、12B 引き出し電極部(導体パターンの端部)

13A、13B 外部電極

14A、14B 端子電極

13A、13B 外部電極

100 キャリアフィルム

111 未焼成の積層体

111A 未焼成の絶縁層

112C 未焼成の導体パターン層

114A、114B 未焼成の端子電極

Claims (6)

- 複数の絶縁層が積層された積層体と、この積層体内に形成された導体パターンと、この導体パターンの両端部と電気的に接続され且つ上記積層体の両側面に形成された一対の外部電極と、を備え、上記積層体の実装面の両端部に埋められた一対の端子電極を有し、上記各端子電極は上記実装面で露出していると共に上記実装面と同一面を形成していることを特徴とする電子部品。

- 上記各端子電極は、上記積層体の両側面に露出していることを特徴とする請求項1に記載の電子部品。

- 未焼成の絶縁層と未焼成の導体パターン層とを交互に積層して焼成し導体パターンを内蔵する積層体を作製する第1の工程と、上記積層体の両側面全面に一対の外部電極を設けると共にこれらの外部電極を上記導体パターンの両端と電気的に接続する第2の工程と、を備えた電子部品の製造方法において、上記第1の工程は、上記積層体となる未焼成の絶縁層の実装面側の両端部を未焼成の一対の端子電極で埋める工程を有することを特徴とする電子部品の製造方法。

- 上記第1の工程は、キャリアフィルム上に上記未焼成の各端子電極を形成する工程と、上記キャリアフィルム上で上記各端子電極をそれぞれ覆って上記未焼成の絶縁層を形成する工程と、を有することを特徴とする請求項3に記載の電子部品の製造方法。

- 上記第1の工程では、未焼成の上記絶縁層と未焼成の上記導体パターン層とを積層する際のアライメントマークを上記未焼成の各端子電極と同時に形成することを特徴とする請求項3または請求項4に記載の電子部品の製造方法。

- 上記未焼成の各端子電極は、上記未焼成の積層体の両側面に露出していることを特徴とする請求項3〜請求項5に記載の電子部品の製造方法。

Priority Applications (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005379684A JP2007180428A (ja) | 2005-12-28 | 2005-12-28 | 電子部品及びその製造方法 |

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP2005379684A JP2007180428A (ja) | 2005-12-28 | 2005-12-28 | 電子部品及びその製造方法 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| JP2007180428A true JP2007180428A (ja) | 2007-07-12 |

Family

ID=38305288

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| JP2005379684A Pending JP2007180428A (ja) | 2005-12-28 | 2005-12-28 | 電子部品及びその製造方法 |

Country Status (1)

| Country | Link |

|---|---|

| JP (1) | JP2007180428A (ja) |

Cited By (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012104745A (ja) * | 2010-11-12 | 2012-05-31 | Tdk Corp | 積層型電子部品及び積層型電子部品の製造方法 |

| JP2013069829A (ja) * | 2011-09-22 | 2013-04-18 | Toko Inc | 積層型電子部品 |

| JP2013098281A (ja) * | 2011-10-31 | 2013-05-20 | Toko Inc | 積層型電子部品 |

| JP2015095496A (ja) * | 2013-11-11 | 2015-05-18 | パナソニックIpマネジメント株式会社 | 積層部品 |

| JP2016032093A (ja) * | 2014-07-29 | 2016-03-07 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | チップ電子部品及びその実装基板 |

| JP2018107412A (ja) * | 2016-12-28 | 2018-07-05 | 株式会社村田製作所 | 積層型電子部品の製造方法および積層型電子部品 |

| JP2018107411A (ja) * | 2016-12-28 | 2018-07-05 | 株式会社村田製作所 | 積層型電子部品の製造方法および積層型電子部品 |

| JP2019046936A (ja) * | 2017-08-31 | 2019-03-22 | 株式会社村田製作所 | コイル部品 |

Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6314414A (ja) * | 1986-07-04 | 1988-01-21 | 株式会社村田製作所 | 単板コンデンサの製造方法 |

| JPH05152133A (ja) * | 1991-11-26 | 1993-06-18 | Matsushita Electric Ind Co Ltd | インダクタンス部品用グリーンシートおよびそれを用いたインダクタンス部品 |

| JPH11214235A (ja) * | 1998-01-27 | 1999-08-06 | Murata Mfg Co Ltd | 積層セラミック電子部品及びその製造方法 |

| JP2001155938A (ja) * | 1999-09-17 | 2001-06-08 | Fdk Corp | 積層インダクタおよびその製造方法 |

| JP2001203119A (ja) * | 2000-01-18 | 2001-07-27 | Matsushita Electric Ind Co Ltd | 積層部品の製造方法およびそれに用いるキャリアフィルム |

| JP2004179585A (ja) * | 2002-11-29 | 2004-06-24 | Murata Mfg Co Ltd | 積層チップ部品の製造方法 |

-

2005

- 2005-12-28 JP JP2005379684A patent/JP2007180428A/ja active Pending

Patent Citations (6)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS6314414A (ja) * | 1986-07-04 | 1988-01-21 | 株式会社村田製作所 | 単板コンデンサの製造方法 |

| JPH05152133A (ja) * | 1991-11-26 | 1993-06-18 | Matsushita Electric Ind Co Ltd | インダクタンス部品用グリーンシートおよびそれを用いたインダクタンス部品 |

| JPH11214235A (ja) * | 1998-01-27 | 1999-08-06 | Murata Mfg Co Ltd | 積層セラミック電子部品及びその製造方法 |

| JP2001155938A (ja) * | 1999-09-17 | 2001-06-08 | Fdk Corp | 積層インダクタおよびその製造方法 |

| JP2001203119A (ja) * | 2000-01-18 | 2001-07-27 | Matsushita Electric Ind Co Ltd | 積層部品の製造方法およびそれに用いるキャリアフィルム |

| JP2004179585A (ja) * | 2002-11-29 | 2004-06-24 | Murata Mfg Co Ltd | 積層チップ部品の製造方法 |

Cited By (11)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2012104745A (ja) * | 2010-11-12 | 2012-05-31 | Tdk Corp | 積層型電子部品及び積層型電子部品の製造方法 |

| JP2013069829A (ja) * | 2011-09-22 | 2013-04-18 | Toko Inc | 積層型電子部品 |

| JP2013098281A (ja) * | 2011-10-31 | 2013-05-20 | Toko Inc | 積層型電子部品 |

| JP2015095496A (ja) * | 2013-11-11 | 2015-05-18 | パナソニックIpマネジメント株式会社 | 積層部品 |

| JP2016032093A (ja) * | 2014-07-29 | 2016-03-07 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | チップ電子部品及びその実装基板 |

| JP2019024113A (ja) * | 2014-07-29 | 2019-02-14 | サムソン エレクトロ−メカニックス カンパニーリミテッド. | チップ電子部品及びその実装基板 |

| JP2018107412A (ja) * | 2016-12-28 | 2018-07-05 | 株式会社村田製作所 | 積層型電子部品の製造方法および積層型電子部品 |

| JP2018107411A (ja) * | 2016-12-28 | 2018-07-05 | 株式会社村田製作所 | 積層型電子部品の製造方法および積層型電子部品 |

| US10886061B2 (en) | 2016-12-28 | 2021-01-05 | Murata Manufacturing Co., Ltd. | Multilayer electronic component manufacturing method and multilayer electronic component |

| US10886060B2 (en) | 2016-12-28 | 2021-01-05 | Murata Manufacturing Co., Ltd. | Multilayer electronic component manufacturing method and multilayer electronic component |

| JP2019046936A (ja) * | 2017-08-31 | 2019-03-22 | 株式会社村田製作所 | コイル部品 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| JP6519561B2 (ja) | インダクタ部品およびその製造方法 | |

| KR101503144B1 (ko) | 박막 인덕터 소자 및 이의 제조방법 | |

| JP5182448B2 (ja) | 部品内蔵基板 | |

| JP2023011909A (ja) | インダクタ部品 | |

| JP2009206110A (ja) | 電子部品 | |

| JP2009277972A (ja) | コイル部品およびその製造方法 | |

| JP7163882B2 (ja) | インダクタ部品および電子部品 | |

| US8058561B2 (en) | Circuit board and manufacturing method thereof | |

| US10395814B2 (en) | Coil electronic component and method of manufacturing the same | |

| JP2007180428A (ja) | 電子部品及びその製造方法 | |

| KR102545033B1 (ko) | 코일 전자 부품 | |

| US10499512B2 (en) | Multi-layer circuit board and manufacturing method thereof | |

| JP2005294697A (ja) | 電子部品及びその製造方法 | |

| JP5585576B2 (ja) | 電子部品の製造方法 | |

| KR20180046270A (ko) | 코일 전자 부품 | |

| JP2008010674A (ja) | 電子部品の製造方法及び電子部品 | |

| JP4535126B2 (ja) | 電子部品 | |

| JP2008177254A (ja) | インダクタ及びその製造方法 | |

| JP4618442B2 (ja) | 電子部品の構成に用いられるシートの製造方法 | |

| JP4577479B2 (ja) | 多層配線基板形成に用いられる異材質部を有するシート形成方法および異材質部を有するシート | |

| US20240186056A1 (en) | Coil component and manufacturing method therefor | |

| JP2007184631A (ja) | 受動素子を備えた配線板の製造方法 | |

| JP2006128224A (ja) | 積層基板の製造方法及び積層基板 | |

| JP2024080316A (ja) | コイル部品及びその製造方法 | |

| JP2006041320A (ja) | 積層型インダクタ |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| A621 | Written request for application examination |

Free format text: JAPANESE INTERMEDIATE CODE: A621 Effective date: 20081008 |

|

| A977 | Report on retrieval |

Free format text: JAPANESE INTERMEDIATE CODE: A971007 Effective date: 20101108 |

|

| A131 | Notification of reasons for refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A131 Effective date: 20101130 |

|

| A02 | Decision of refusal |

Free format text: JAPANESE INTERMEDIATE CODE: A02 Effective date: 20110412 |