(19) **日本国特許庁(JP)**

# (12)特許公報(B2)

(11)特許番号

特許第4773822号 (P4773822)

(45) 発行日 平成23年9月14日(2011.9.14)

(24) 登録日 平成23年7月1日(2011.7.1)

FL(51) Int. CL.

HO3K 17/08 (2006, 01) HO3K 17/08 HO3K 17/687 (2006, 01) HO3K 17/687

> 請求項の数 9 (全 21 頁)

特願2005-372018 (P2005-372018) (21) 出願番号

(22) 出願日 平成17年12月26日 (2005.12.26)

(65) 公開番号 特開2007-174490 (P2007-174490A) (43) 公開日 平成19年7月5日(2007.7.5) 審查請求日

平成20年7月16日 (2008.7.16)

||(73)特許権者 395011665

C

Α

株式会社オートネットワーク技術研究所

三重県四日市市西末広町1番14号

|(73)特許権者 000183406

住友電装株式会社

三重県四日市市西末広町1番14号

|(73)特許権者 000002130

住友電気工業株式会社

大阪府大阪市中央区北浜四丁目5番33号

||(74)代理人 110001036

特許業務法人暁合同特許事務所

(72)発明者 高橋 成治

三重県四日市市西末広町1番14号 株式 会社オートネットワーク技術研究所内

最終頁に続く

(54) 【発明の名称】電力供給制御装置

# (57)【特許請求の範囲】

### 【請求項1】

電源と負荷との間に設けられて前記電源から前記負荷への電力供給制御を行う電力供給制 御装置であって、

前記電源から前記負荷への通電路に配される半導体スイッチ素子と、

所定の異常状態に基づき異常信号を出力する異常検出回路と、

定電圧を生成する定電圧電源回路と、

前記定電圧電源回路によって生成された定電圧が供給されることで動作可能となり、前 記異常信号に基づき前記半導体スイッチ素子に遮断動作をさせるための遮断信号を出力し 、前記遮断信号の出力状態を保持する出力保持回路と、

前記遮断信号の出力状態の保持後に外部からの第1オフ指令信号の入力状態が基準待機 時間だけ継続したことを条件に第2オフ指令信号を出力するオフ指令出力回路と、

外部からのオン指令信号に基づき前記定電圧電源回路の通電を開始し、前記遮断信号の 出力状態の保持後に前記第2オフ指令信号が出力されたことを条件に前記定電圧電源回路 の通電を停止する通電制御回路と、を備える電力供給制御装置。

### 【請求項2】

前記異常検出回路は、前記半導体スイッチ素子に流れる負荷電流を検出する電流検出素子

前記電流検出素子からの検出信号に基づき前記半導体スイッチ素子に流れる負荷電流が 所定の閾値を超えている場合に前記異常信号として異常電流信号を出力する異常電流検出

回路と、を備えて構成されている請求項1に記載の電力供給制御装置。

#### 【請求項3】

前記半導体スイッチ素子はパワーFETであると共に、前記電流検出素子は前記パワーFETに流れる負荷電流に対し所定関係のセンス電流が流れるセンスFETとされ、前記異常電流検出回路は、前記センス電流と前記所定の閾値とに基づいて前記異常電流信号の出力を行う構成である請求項2に記載の電力供給制御装置。

#### 【請求項4】

前記異常検出回路は、前記半導体スイッチ素子の温度を検出する温度検出素子と、

前記温度検出素子からの検出信号に基づき前記半導体スイッチ素子の温度が所定の閾値を超えている場合に前記異常信号として異常温度信号を出力する異常温度検出回路と、を備えて構成されている請求項1から請求項3のいずれかに記載の電力供給制御装置。

#### 【請求項5】

前記遮断信号の出力状態の保持前において、前記異常信号が出力されていない正常状態が 基準正常時間だけ継続したことを条件にクリア信号を出力する正常時間積算回路を備え、

前記通電制御回路は、前記遮断信号の出力状態の保持前において、前記第1オフ指令信号が入力され、かつ、前記クリア信号が出力されたことを条件に前記定電圧電源回路の通電を停止する構成である請求項1から請求項4のいずれかに記載の電力供給制御装置。

### 【請求項6】

前記出力保持回路は、前記異常信号が出力されている異常時間を積算し、その積算時間が基準異常時間に達したことを条件に前記遮断信号を出力し、前記遮断信号の出力状態を保持する異常時間積算回路を備える構成とされている請求項 5 に記載の電力供給制御装置。

#### 【請求項7】

前記異常時間積算回路は、前記遮断信号の出力状態の保持前において、前記正常時間積算回路から前記クリア信号が出力されたことを条件に前記異常時間の積算時間をクリアする請求項 6 に記載の電力供給制御装置。

### 【請求項8】

前記正常時間積算回路は、前記遮断信号の出力状態の保持後において、前記オン指令信号の入力状態で前記正常時間が初期値にリセットされ、前記第1オフ指令信号が入力されたときに前記正常時間積算回路の動作を開始し、当該正常時間積算回路の正常時間が前記基準正常時間に達したことを条件に前記クリア信号を前記第2オフ指令信号として出力する構成とされることで前記オフ指令出力回路として機能する請求項<u>5</u>から請求項<u>7</u>のいずれかに記載の電力供給制御装置。

### 【請求項9】

前記オン指令信号と前記第1オフ指令信号とが交互に繰り返し入力され、前記オン指令信号を受けたときに前記半導体スイッチ素子に通電動作をさせ、前記第1オフ指令信号を受けたときに前記半導体スイッチ素子に遮断動作をさせるスイッチ制御回路とを備え、

前記基準正常時間は、前記各オフ指令信号の入力により前記半導体スイッチ素子が継続して遮断している遮断時間よりも長い時間である請求項<u>5</u>から請求項<u>8</u>のいずれかに記載の電力供給制御装置。

### 【発明の詳細な説明】

【技術分野】

### [0001]

本発明は、電力供給制御装置に関する。

### 【背景技術】

# [0002]

従来、電源と負荷とを接続する通電路に、例えばパワーMOSFETなどの大電力用半導体スイッチ素子を介設し、この半導体スイッチ素子をオンオフさせることにより負荷への電力供給を制御するようにした電力供給制御装置が提供されている。このような電力供給制御装置では、過電流が流れると上記半導体スイッチ素子の制御端子の電位を制御して当該半導体スイッチ素子をオフにすることにより、上記半導体スイッチ素子自体を保護す

10

20

30

30

40

る自己保護機能を有するものが知られている。具体的には、例えば下記特許文献1に示すように、電流検出抵抗を負荷端子(例えばMOSFETであればソースまたはドレイン)に直列に接続し、この抵抗における電圧降下に基づき半導体スイッチ素子を流れる負荷電流を検出して、この負荷電流が所定の閾値以上になると過電流と判定するようなものがある。そして、上述の自己保護機能に基づく電流遮断は、遮断後に所定時間が経過すれば、当該半導体スイッチ素子は再びオン状態に自己復帰する構成とされている。これは、半導体スイッチ素子自体が過熱状態に陥ることを回避するために設けられている機能であるところ、異常電流を遮断すれば、元々備えられている放熱装置によって半導体スイッチ素子は速やかに温度が低下するはずだからである。

【特許文献1】特開2001-217696公報

# 【発明の開示】

【発明が解決しようとする課題】

### [0003]

ところで、上記電力供給制御装置において、例えば過電流異常が長時間解消されず、上記自己保護機能に基づく半導体スイッチ素子の遮断及び復帰の動作が所定回数以上繰り返されたときには、半導体スイッチ素子を遮断状態に保持すべき場合がある。このような処理を行う制御回路を電力供給制御装置に備えようとした場合、定電圧電源回路を設けてこれによって生成される定電圧を供給することによって制御回路を安定的に動作させることが望ましい。

# [0004]

20

10

ここで、定電圧電源回路を常時通電させた状態とすると、バッテリー等の外部電源からの暗電流が流れてしまう。これを防止するためには、半導体スイッチ素子に遮断動作させるためのオフ指令信号が外部から入力されているときには定電圧電源回路の通電を停止させることが望ましい。

#### [0005]

しかしながら、このような構成とした場合、上記半導体スイッチ素子の遮断保持状態になった後に、外部からオフ指令信号が入力されると定電圧電源回路の通電が停止され、その時点で制御回路も停止され半導体スイッチ素子の遮断保持状態が解除されてしまう。従って、その後間もなくオン指令信号が入力された場合、未だ半導体スイッチ素子を遮断状態に保持すべき異常状態にあるにもかかわらず、半導体スイッチ素子が通電状態になってしまうという問題があった。

30

# [0006]

また、上記オン指令信号とオフ指令信号とが交互に繰り返されるオンオフ信号(たとえばPWM信号)を外部から入力して、これに基づき半導体スイッチ素子をオンオフ制御する構成では、オフ指令信号が入力されるごとに定電圧電源回路の通電が停止されるため、半導体スイッチ素子を遮断保持状態にすることができないという問題があった。

# [0007]

本発明は上記のような事情に基づいて完成されたものであって、その目的は、暗電流を抑制しつつオフ指令信号の入力時に半導体スイッチ素子の遮断保持状態が解除されることを防止することが可能な電力供給制御装置を提供するところにある。

40

# 【課題を解決するための手段】

#### [00008]

上記の目的を達成するための手段として、請求項1の発明に係る電力供給制御装置は、電源と負荷との間に設けられて前記電源から前記負荷への電力供給制御を行う電力供給制御装置であって、前記電源から前記負荷への通電路に配される半導体スイッチ素子と、所定の異常状態に基づき異常信号を出力する異常検出回路と、定電圧を生成する定電圧電源回路と、前記定電圧電源回路によって生成された定電圧が供給されることで動作可能となり、前記異常信号に基づき前記半導体スイッチ素子に遮断動作をさせるための遮断信号を出力し、前記遮断信号の出力状態を保持する出力保持回路と、前記遮断信号の出力状態の保持後に外部からの第1オフ指令信号の入力状態が基準待機時間だけ継続したことを条件

に第2オフ指令信号を出力するオフ指令出力回路と、外部からのオン指令信号に基づき前記定電圧電源回路の通電を開始し、前記遮断信号の出力状態の保持後に前記第2オフ指令信号が出力されたことを条件に前記定電圧電源回路の通電を停止する通電制御回路と、を備える。

## [0009]

請求項<u>2</u>の発明は、請求項<u>1 に</u>記載の電力供給制御装置において、前記異常検出回路は、前記半導体スイッチ素子に流れる負荷電流を検出する電流検出素子と、前記電流検出素子からの検出信号に基づき前記半導体スイッチ素子に流れる負荷電流が所定の閾値を超えている場合に前記異常信号として異常電流信号を出力する異常電流検出回路と、を備えて構成されている。

### [0010]

請求項<u>3</u>の発明は、請求項<u>2</u>に記載の電力供給制御装置において、前記半導体スイッチ素子はパワーFETであると共に、前記電流検出素子は前記パワーFETに流れる負荷電流に対し所定関係のセンス電流が流れるセンスFETとされ、前記異常電流検出回路は、前記センス電流と前記所定の閾値とに基づいて前記異常電流信号の出力を行う構成である

#### [0011]

請求項4の発明は、請求項1から請求項3のいずれかに記載の電力供給制御装置において、前記異常検出回路は、前記半導体スイッチ素子の温度を検出する温度検出素子と、前記温度検出素子からの検出信号に基づき前記半導体スイッチ素子の温度が所定の閾値を超えている場合に前記異常信号として異常温度信号を出力する異常温度検出回路と、を備えて構成されている。

### [0012]

請求項<u>5</u>の発明は、請求項1から請求項<u>4</u>のいずれかに記載の電力供給制御装置において、前記遮断信号の出力状態の保持前において、前記異常信号が出力されていない正常状態が基準正常時間だけ継続したことを条件にクリア信号を出力する正常時間積算回路を備え、前記通電制御回路は、前記出力状態の保持前において、前記第1オフ指令信号が入力され、かつ、前記クリア信号が出力されたことを条件に前記定電圧電源回路の通電を停止する構成である。

請求項6の発明は、請求項5に記載の電力供給制御装置において、前記出力保持回路は、前記異常信号が出力されている異常時間を積算し、その積算時間が基準異常時間に達したことを条件に前記遮断信号を出力し、その出力状態を保持する異常時間積算回路を備える構成とされている。

### [0013]

請求項<u>7</u>の発明は、請求項<u>6</u>に記載の電力供給制御装置において、前記異常時間積算回路は、前記遮断信号の出力状態の保持前において、前記正常時間積算回路から前記クリア信号が出力されたことを条件に前記異常時間の積算時間をクリアする。

### [0014]

請求項<u>8</u>の発明は、請求項<u>5</u>から請求項<u>7</u>のいずれかに記載の電力供給制御装置において、前記正常時間積算回路は、前記出力状態の保持後において、前記オン指令信号の入力状態で前記正常時間が初期値にリセットされ、前記第1オフ指令信号が入力されたときに前記正常時間積算回路の動作を開始し、当該正常時間積算回路の正常時間が前記基準正常時間に達したことを条件に前記クリア信号を前記第2オフ指令信号として出力する構成とされることで前記オフ指令出力回路として機能する。

#### [0015]

請求項<u>9</u>の発明は、請求項<u>5</u>から請求項<u>8</u>のいずれかに記載の電力供給制御装置において、前記オン指令信号と前記第1オフ指令信号とが交互に繰り返し入力され、前記オン指令信号を受けたときに前記半導体スイッチ素子に通電動作をさせ、前記第1オフ指令信号を受けたときに前記半導体スイッチ素子に遮断動作をさせるスイッチ制御回路とを備え、前記基準正常時間は、前記各オフ指令信号の入力により前記半導体スイッチ素子が継続し

10

20

30

40

て遮断している遮断時間よりも長い時間である。

### 【発明の効果】

### [0016]

<請求項1の発明>

本構成によれば、遮断信号の出力状態が保持された後、外部からのオフ指令信号(例えば定電圧電源回路の通電停止を指示する信号)を受けている状態が基準待機時間継続したことを条件に定電圧電源回路の通電が停止される。従って、出力状態が保持された後にオフ指令信号を受けても、そのオフ入力状態が基準待機時間継続しない限り定電圧電源回路の通電が継続され、半導体スイッチ素子の遮断状態を保持し続けることができる。一方、オフ入力状態が基準待機時間継続したときには、定電圧電源回路の通電が停止されるための暗電流を防止できる。

10

20

30

#### [0017]

<請求項2の発明>

本構成は、過電流異常に基づき異常信号を出力する構成である。

## [0018]

<請求項3の発明>

本構成は、電流検出素子として、パワーFETに流れる負荷電流に対し所定関係のセンス電流が流れるセンスFETを用いて、このセンス電流に基づき過電流異常を検出する構成であり、この構成に対しても本発明を適用し同様の効果を得ることができる。

### [0019]

<請求項4の発明>

本構成は、過温度異常に基づき異常信号を出力する構成である。

# [0020]

< 請求項5,6の発明>

本構成によれば、異常時間積算回路の積算動作中にオフ指令信号を受けても、基準正常時間内にオン指令信号を受ければ定電圧電源回路の通電が維持されるため、異常時間積算回路の積算時間がリセットされることを防止できる。

#### [0021]

<請求項7の発明>

本構成は、例えば通電路に流れる負荷電流(または温度)が所定の閾値を超えたときに 異常時間の積算を開始し、その異常時間が異常基準時間に達したときに半導体スイッチ素 子に遮断動作をさせる。一方、少なくとも異常信号が出力されていない正常状態が基準正 常時間継続した場合には、それまで積算された異常時間積算回路の積算時間をクリア(現 在の積算時間を初期値または現在の積算値よりも初期値に近い値に戻す)して半導体スイッチの遮断動作をさせない。従って、例えば連続的な異常電流は勿論、断続的な異常電流 でその異常電流の発生間隔が正常基準時間より短いチャタリングショートも検出して外部 回路(負荷、電線)の保護を図ることができる。本構成によれば、このような外部回路の 保護機能(ヒューズ機能)で使用される正常時間積算回路からのクリア信号を利用して、 定電圧電源回路の通電制御を行うことができる。

[0022]

40

<請求項8の発明>

本構成によれば、正常時間積算回路をオフ指令出力回路として機能させることができる

# [0023]

<請求項9の発明>

本構成によれば、オン指令信号とオフ指令信号とが交互に繰り返されるオンオフ信号(たとえばPWM信号)を外部から入力して、これに基づき半導体スイッチ素子をオンオフ制御するものにおいて、オフ指令信号の入力時に半導体スイッチ素子の遮断保持状態が解除されることを防止できる。

### 【発明を実施するための最良の形態】

#### [0024]

本発明の一実施形態を図1~図11を参照しつつ説明する。

<電力供給制御装置の構成>

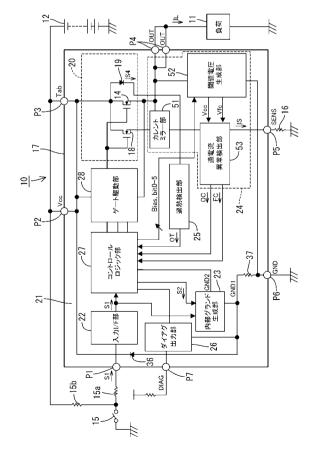

図1は、本実施形態に係る電力供給制御装置10の全体構成のブロック図である。この電力供給制御装置10は図示しない車両に搭載され、その車両用電源(以下、「電源12」)から負荷11として例えば車両用のランプ、クーリングファン用モータやデフォッガー用ヒータなどへの電力供給制御を行うために使用される。なお、以下では、「負荷」は電力供給制御装置10の制御対象装置であって、電力供給制御装置10とその制御対象装置との間に連なる電線30を含まない意味とし、「外部回路」を負荷11と電線30とを含めた意味として説明する。

[0025]

具体的には、電力供給制御装置10は、電源12から負荷11への通電路13中に設けられるパワーMOSFET14(「半導体スイッチ素子、パワーFET」に相当)を備えている。そして、電力供給制御装置10は、パワーMOSFET14のゲートに定電圧信号、或いは、PWM(Pulse Width Modulation。パルス幅変調)制御信号などの制御信号S1を与えてオンオフ動作させることで、そのパワーMOSFET14の出力側に連なる負荷11への電力供給を制御するように構成されている。なお、本実施形態では、この電力供給制御装置10は、入力端子P1が外部の操作スイッチ15に接続される構成をなし、この操作スイッチ15がオンとなることで動作するようになっている。具体的には、入力端子P1は、抵抗15aを介して操作スイッチ15に接続され、抵抗15aと操作スイッチ15との接続点が抵抗15bを介して電源12に接続され、入力端子P1は、操作スイッチ15がオフしているときは、電源電圧Vcc側にプルアップされている。

[0026]

電力供給制御装置10は、図1に示すように、上記入力端子P1と、電源12に接続される電源(Vcc)端子P2及びタブ端子P3と、負荷11に接続される負荷接続端子P4と、電流電圧変換回路としての外付け抵抗16を介してグランド(GND)に接続される外部端子P5と、グランド(GND)に直接接続されるグランド端子P6と、ダイアグ出力端子P7とが設けられた半導体スイッチ装置17(半導体ディバイス)として構成されている。本実施形態では、パワーMOSFET14、後述するセンスMOSFET18(「電流検出素子、センスFET」に相当)、及び、温度検出素子としての温度センサ19(本実施形態では例えばダイオード)がパワーチップ20としてワンチップ化され、それ以外の回路が搭載された制御チップ21に組み付けられて構成されている。

[0027]

パワーチップ20は、ドレインが共通接続されてタブ端子P3に接続される複数のMOSFETが配列され、ほとんどのMOSFET群が、ソースを後述するカレントミラー部51のパワーFET用入力51a及び負荷接続端子P4に共通接続することでパワーMOSFET14を構成し、一部のMOSFET群が、ソースをカレントミラー部51のセンスFET用入力51bに共通接続することでセンスMOSFET18を構成している。なお、パワーMOSFET14を構成するMOSFET 18を構成するMOSFET 18を構成するMOSFET 18を構成するMOSFET群の数との比が概ねセンス比である。

[0028]

制御チップ21には、主として、入力インターフェース部22、内部グランド生成部23、電流検出部24、過熱検出部25、ダイアグ出力部26、過電流保護回路及び過熱保護回路として機能するコントロールロジック部27、ゲート駆動部28が搭載されている

[0029]

(入力インターフェース部)

入力インターフェース部22は、入力側が入力端子P1に接続されており、操作スイッチ15がオフしているときにハイレベルの制御信号S1が、オンしているときにローレベルの制御信号S1が内部グランド生成部23及びコントロ

10

20

30

40

ールロジック部27に与えられる。電力供給制御装置10は、後述するように、電流異常も温度異常も発生していない正常状態においては、上記ローレベルの制御信号S1を受けるとゲート駆動部28によってパワーMOSFET14をターンオンして通電状態とする一方で、ハイレベルの制御信号S1を受けるとゲート駆動部28によってパワーMOSFET14をターンオフして遮断状態にする。従って、本実施形態では、ローレベルの制御信号S1が「オン指令信号」に相当し、ハイレベルの制御信号S1が「(第1)オフ指令信号」に相当し、ゲート駆動部28が「スイッチ制御回路」として機能する。

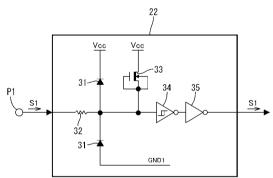

### [0030]

具体的には、入力インターフェース部22は、図2に示すように、電源端子P2と内部グランドGND1(0<GND1<Vcc)との間に、カソード側が高電位側に配された1対のダイオード31、31が直列接続され、これらの接続点に抵抗32を介して入力端子P1が接続されている。高電位側のダイオード31には、ゲートとソースとが短絡接続されたFET33が並列接続されている。入力端子P1にハイレベルの制御信号S1が入力されており、ハイレベルの制御信号S1に応じたハイレベルの信号(本実施形態では説明を簡略するためにハイレベルの制御信号S1とする)がヒステリシスコンパレータ34及び反転回路35を介して出力される。一方、入力端子P1にローレベルの制御信号S1が入力されると、FET33からの定電流が抵抗32を介して入力端子P1側に流れて、ローレベルの制御信号S1に応じたローレベルの信号(本実施形態では説明を簡略するためにローレベルの制御信号S1とする)がヒステリシスコンパレータ34及び反転回路35を介して出力される。

### [0031]

なお、入力端子P1に負電圧(<GND1)の制御信号S1が入力されたときには、内部グランドGND1から低電位側のダイオード31及び抵抗32を介して入力端子P1側に電流が流れて、やはリローレベルの制御信号S1を出力するようになっている。また、図1に示すように、電源端子P2とグランド端子P6との間には、カソード側が高電位側に配されたダイオード36と抵抗37とが直列接続され、これらの接続点が上記内部グランドGND1とされている。このような構成であれば、誤ってグランド端子P6側が電源電圧Vcc側に接続された場合でも、この電力供給制御装置10の回路内に流れる電流をダイオード36によって一定レベル以下に規制することができる。

### [0032]

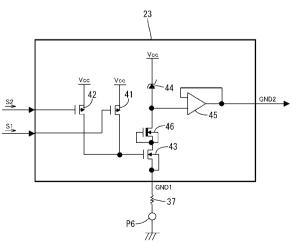

### (内部グランド生成部)

内部グランド生成部23(「定電圧電源生成回路」に相当)は、入力インターフェース部22からローレベルの制御信号S1(オン指令信号)、及び、後述するクリアカウンタ72からローレベルの出力信号S2(クリアカウンタ72がオーバーフローしていない状態)のいずれかを受けているときに通電して、電源電圧Vccよりも所定電圧分低い内部グランドGND2を生成する。換言すれば、内部グランド生成部23は、入力インターフェース部22からハイレベルの制御信号S1(オフ指令信号)を受けても、クリアカウンタ72からローレベルの出力信号S2を受けている限り、通電状態が継続され内部グランドGND2を生成し続ける。そして、電源電圧Vccから内部グランドGND2を差し引いた定電圧がコントロールロジック部27に供給されることで、このコントロールロジック部27が動作可能な状態となる。

#### [0033]

具体的には、内部グランド生成部23は、図3に示すように、ローレベルの制御信号S1を受けてオン動作するスイッチ素子としてのFET41と、ローレベルの出力信号S2を受けてオン動作するスイッチ素子としてのFET42とをそれぞれ備えている。これら両FET41,42の出力側はスイッチ素子としてのFET43の制御端子に接続されている。このFET43は入力側(ドレイン側)がツェナーダイオード44を介して電源端子P2に接続され、出力側(ソース側)が上記抵抗37を介してグランド端子P6に接続されている。従って、FET41,42が「通電制御回路」として機能する。

# [0034]

10

20

30

そして、内部グランド生成部23は、上記したローレベルの制御信号S1またはローレベルの出力信号S2が入力されたときには、FET43がオンして通電し、電源電圧Vccからツェナーダイオード44のツェナー電圧分だけ低い内部グランドGND2を生成し、これをボルテージフォロワ接続されたオペアンプ45を介してコントロールロジック部27に与える。なお、本実施形態では、ツェナーダイオード44及びFET43が連なる通電路中にソースとゲートとが短絡接続されたFET46を接続することで、FET43のオン時においてツェナーダイオード44に定電流が流れるようにして内部グランドGND2をより安定させるようにしている。

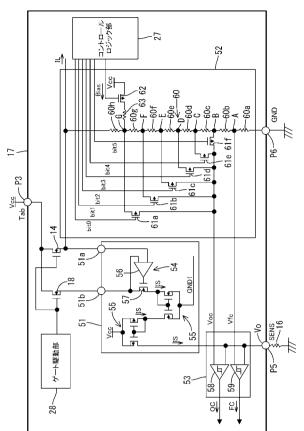

### [0035]

(電流検出部)

電流検出部24は、図1に示すように、カレントミラー部51と、閾値電圧生成部52 と、過電流異常検出部53とを備えて構成されている。図4は、カレントミラー部51、 閾値電圧生成部52及び過電流異常検出部53を拡大して示す回路であり、他の回路構成は一部省略されている。

### [0036]

a . カレントミラー部

カレントミラー部 5 1 は、パワーMOSFET14 とセンスMOSFET18 との出力 側電位(ソース電位)を同電位に保持するための電位制御回路 5 4 と、1 対のカレントミ ラー回路 5 5 , 5 5 とを備えている。

### [0037]

電位制御回路54は、パワーFET用入力51a(パワーMOSFET14のソース)とセンスFET用入力51b(センスMOSFET18のソース)とが1対の入力端子それぞれに接続されるオペアンプ56、センスFET用入力51bと外部端子P5との間に接続され制御端子にオペアンプ56の出力が与えられるスイッチ素子としてのFET57を備えている。より具体的には、パワーFET用入力51aは、オペアンプ56の逆相入力に接続され、センスFET用入力51bは、オペアンプ56の正相入力に接続されている。このオペアンプ56の差動出力は、FET57のゲート・ドレイン間を介して、正相入力にフィードバックされている。

# [0038]

このようにオペアンプ56の差動出力をフィードバックすることによって、オペアンプ56の正相入力の電位と逆相入力の電位とがほとんど同じになるイマジナリーショート状態となる。このため、パワーMOSFET14及びセンスMOSFET18のドレイン同士、ソース同士が互いに同電位となり、パワーMOSFET14に流れる負荷電流電流ILに対して安定した一定比率(上記センス比)のセンス電流IS(「電流検出素子からの検出信号」に相当)をセンスMOSFET18に流すことができる。

### [0039]

電位制御回路54からのセンス電流Isは上記1対のカレントミラー回路55,5及び外部端子P5を介して外付け抵抗16に流れ、このセンス電流Isに応じて外部端子P5の端子電圧Voが変化する。

### [0040]

# b. 過電流異常検出部

過電流異常検出部53(「異常電流検出回路、通電検出回路」に相当)は、複数(本実施形態では2つ)の比較回路58,59(本実施形態では、ヒステリシスコンパレータ)とを備え、外部端子P5の端子電圧Voが比較回路58の一方の入力端子に与えられると共に、比較回路59の一方の入力端子に与えられる。

# [0041]

比較回路58は、他方の入力端子に閾値電圧生成部52からの第1異常用閾値電圧Vocを受けて、この第1異常用閾値電圧Vocを端子電圧Voが超えたときにローレベルの第1 異常電流信号OC(「異常信号」に相当)をコントロールロジック部27に出力する。なお、以下では、端子電圧Voが第1異常用閾値電圧Vocに達したときにパワーMOSFE 10

20

30

40

T14に流れる電流異常時の負荷電流ILを、「第1異常用閾値電流ILoc」とし、このときの電流異常を「オーバーカレント」という。

### [0042]

比較回路 5 9 は、他方の入力端子に閾値電圧生成部 5 2 からの第 2 異常用閾値電圧 V fc ( < Voc ) を受けて、この第 2 異常用閾値電圧 V fcを端子電圧 V o が超えたときにローレベルの第 2 異常電流信号 F C (「異常信号、通電検出信号」に相当)をコントロールロジック部 2 7 に出力する。なお、以下では、端子電圧 V o が第 2 異常用閾値電圧 V fcに達したときにパワーMOSFET14に流れる電流異常時の負荷電流 I L を、「第 2 異常用閾値電流 I L fc」とし、このときの電流異常を「ヒューズカレント」という。

## [0043]

# c. 閾値電圧生成部

閾値電圧生成部52(「閾値変更回路」に相当)は、基準電圧を複数の抵抗で分圧する分圧回路を備え、この分圧回路によって生成される複数の分圧電圧から選択する分圧電圧を変更することで過電流異常検出部53に与える異常用閾値電圧を変更できるようになっている。具体的には、閾値電圧生成部52は、図4に示すように、パワーMOSFET14のソースとグランド端子P6との間に接続された分圧回路60を備える。この分圧回路60は、複数の抵抗(本実施形態では8つの抵抗60a~60h)を直列接続して構成されており、抵抗60aと抵抗60bとの接続点Aの分圧電圧が上記第2異常用閾値電圧Vfcとして出力される。

# [0044]

また、閾値電圧生成部52は、上記比較回路58の他方の入力端子を、抵抗60b~60hの各接続点B~Gに選択的に接続可能とするスイッチ素子としての複数のFET61a~61fを備えている。従って、FET61aからFET61fまで選択的に順次オンさせることで、上記第1異常用閾値電圧Vocを段階的にレベルダウンさせることができる。各FET61a~61fは、後述するようにコントロールロジック部27によってオンオフ制御される。

### [0045]

なお、本実施形態では、分圧回路60はパワーMOSFET14のソース電圧Vsを分圧する構成としたが、ソース電圧以外の所定電圧を分圧する構成であってもよい。但し、本実施形態のような構成であれば、パワーMOSFET14のソース電圧Vsの増減に応じて増減するように各異常用閾値電圧を設定できる。従って、ソース電圧の変動にかかわらず固定レベルの閾値を設定するような構成と比較して、例えば負荷11の短絡等が生じた場合に、電源電圧Vccの大小にかかわらず外付け抵抗16の端子電圧Voが即座に異常用閾値電圧に達することとなり、各電流異常を迅速に検出できる。更に、この実施形態では、パワーMOSFET14がオフしているときでもソース電圧Vsが0[V]にならないようにバイアスするため、コントロールロジック部27からのバイアス信号Biasによってオン動作するスイッチ素子としてのFET62によって電源12からの電流を抵抗63を介して分圧回路60に流すようになっている。なお、このバイアス信号Biasは、ローレベルの制御信号S1またはローレベルの出力信号S2が出力されたときにコントールロジック部27から出力され、上記FET62がオンする。

# [0046]

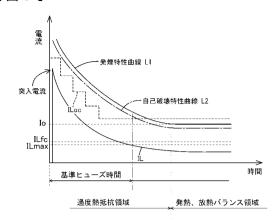

ここで、図5は、上記第1異常用閾値電流ILocと第2異常用閾値電流ILfcとの設定レベルを説明するためのグラフである。このグラフには、電力供給制御装置10に接続され得る電線30(例えば電線被覆材)の発煙特性について、定常電流レベルと通電時間(溶断時間)との関係を示した発煙特性曲線L1が示されている。つまり、任意の一定電流(ワンショット電流)と、それを電線30に流したときに当該電線30の被覆材の焼損が発生するまでの時間との関係を示す発煙特性曲線L1が図示されている。また、同グラフには、任意の一定電流(ワンショット電流)と、それをパワーMOSFET14に流したときに当該パワーMOSFET14が破壊してしまうまでの時間との関係を示す自己破壊特性曲線L2も図示されている。そして、第2異常用閾値電流ILfcは、発煙特性曲線L

10

20

30

40

20

30

40

50

1及び自己破壊特性曲線 L 2よりも電流レベルが低い領域内に設定されている。また、第1異常用閾値電流 I Locは、ヒューズ時間カウンタ 7 3が初期値からのカウントアップの開始後、後述する基準ヒューズ時間よりも短い時間内において、発煙特性曲線 L 1及び自己破壊特性曲線 L 2よりも電流レベルが低い領域内に設定されている。

### [0047]

なお、同グラフは、電力供給制御装置10に接続され得る電線30の中から選択された一の電線30の発煙特性を示している。また、電力供給制御装置10に接続される外部回路(電線等の配線部材、負荷)によって発煙特性は異なり、これに対応して上記異常電流信号FC,OCを出力するときの負荷電流IL及びセンス電流Isも異なってくるが、この調整は、前述した外付け抵抗64の抵抗値を変更することにより容易に行うことができる。

[0048]

同グラフ中、ILmaxは負荷11の定格電流(設計時に保証される機器の使用限度)であり、Ioは電線30における発熱と放熱とのバランスがとれた熱平衡状態で流すことが可能な平衡時限界電流である。この平衡時限界電流Ioよりも高いレベルの電流を流す場合には、過度熱抵抗領域となり、電流レベルと焼損までの時間とが略反比例関係となる。そして、上記第2異常用閾値電流ILfcは、図5に示すように、負荷電流IL(センス電流Is)が負荷11の定格電流ILmaxよりもやや高いレベルに設定されており、比較回路59は、負荷電流IL(センス電流Is)が第2異常用閾値電流ILfcに達したヒューズカレントを検出して第2異常電流信号FCを出力する。このように負荷電流ILが第2異常用閾値電流ILfc程度である場合には、後述するように、パワーMOSFET15を即時的に遮断しなくても、そのヒューズカレント状態がある程度継続したときに遮断すればよい。

[0049]

これに対して、上記第1異常用閾値電流ILocは、第2異常用閾値電流ILfcよりも高いレベルに設定されている。比較回路58は、負荷電流IL(センス電流Is)が第1異常用閾値電流ILocに達したオーバーカレントを検出して第1異常電流信号OCを出力する。このように負荷電流ILが第1異常用閾値電流ILocを超える高いレベルである場合には、後述するようにパワーMOSFET15を即時的に遮断する必要がある。閾値電圧生成部52は、図5に示すように、この第1異常用閾値電流ILocを、当初は突入電流に備えてそれよりも高い初期レベルに設定しておき、後述するように、ヒューズカレントが検出されることを条件にその後、経時的にレベルダウンしていく。

[0050]

(過熱検出部)

過熱検出部25(「異常温度検出回路」に相当)は、パワーチップ20に設けられた温度センサ19から当該パワーチップ20の温度に応じた温度信号S4(「温度検出素子からの検出信号」に相当)を受ける。そして、過熱検出部25は、所定の温度閾値を超える異常温度を示す温度信号S4を受けたときに温度異常を検出してローレベルの異常温度信号OT(「異常信号」に相当)をコントロールロジック部27に与える。

[0051]

なお、ダイアグ出力回路26は、後述するように電流異常或いは温度異常が発生し、コントロールロジック部27によってパワーMOSFET14に後述する第1及び第2の強制遮断動作を行わせている間、ハイレベルのダイアグ信号Diagをコントロールロジック部27から受けることでダイアグ出力端子P7をローレベルにプルダウンさせてダイアグ出力を実行する。これにより、パワーMOSFET14が電流異常や温度異常の発生、ヒューズ機能の実行によって強制遮断状態になっていることを外部に通知することが可能となる。

[0052]

(コントロールロジック部)

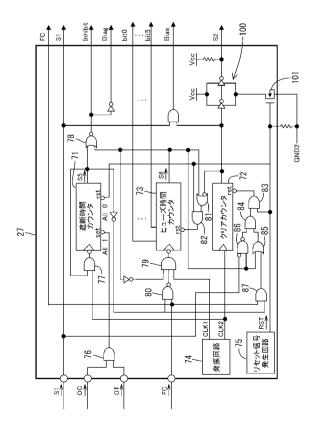

図6は、コントロールロジック部27の回路図である。このコントロールロジック部2

7は、主として、遮断時間カウンタ71、クリアカウンタ72、ヒューズ時間カウンタ73、発振回路74及びリセット信号発生回路75を備える。また、コントロールロジック部27は、前述したように、入力インターフェース部22からの制御信号S1、電流検出部24からの第1異常電流信号OC及び第2異常電流信号FC、過熱検出部25からの異常温度信号OTを受ける。

### [0053]

a. 発振回路及びリセット信号発生回路

発振回路 7 4 は、例えば 2 つ異なる周期のクロック信号 C L K 1 (例えば 1 2 5 μ s e c ) , クロック信号 C L K 2 (例えば 4 m s e c )を生成して出力する。リセット信号発生回路 7 5 は、上記内部グランド生成部 2 3 が通電しこのコントロールロジック部 2 7 が動作するのに十分な定電圧を生成し、上記発振回路 7 4 のクロック発生動作が安定する前まではローレベルの出力信号 R S T を出力する。

## [0054]

b. 遮断時間カウンタ

遮断時間カウンタ71は、電流検出部24からのローレベルの第1異常電流信号OC、及び、過熱検出部25からのローレベルの異常温度信号OTのうち少なくともいずれか一方を受けたことを条件に、パワーMOSFET14に所定の基準遮断時間(カウント値を「n」から「0」までカウントダウンするまでの時間 具体的には32msec)だけ強制的に遮断動作させた後に、その強制遮断状態を解除するものである。なお、本実施形態において、強制遮断とは、電力供給制御装置10がローレベルの制御信号S1(オン指令信号)を受けていてもパワーMOSFET14を遮断状態にすることをいう。

### [0055]

具体的には、遮断時間カウンタ71は、上記クロック信号CLK2のクロックに同期して初期値nから0までカウントダウンするものである。遮断時間カウンタ71は、そのリセット端子にリセット信号発生回路75から出力信号RSTを反転した信号が入力されるようになっており、ローレベルの出力信号RSTが出力されている間は、n個のカウンタが全て「0」(カウント値を初期値「n」)にリセットされた状態となり、ハイレベルの出力信号RSTを受けるようになるとリセット状態が解除される。また、遮断時間カウンタ71は、n個のカウンタが全て「0」のとき(リセット状態或いはカウント値のオーバーフロー状態)、ローレベルの出力信号S5を出力し、これ以外の場合には、パワーMOSFET14に強制遮断動作をさせるためのハイレベルの出力信号S5を出力する。

#### [0056]

また、遮断時間カウンタ71は、第1異常電流信号OC、及び、異常温度信号OTが入力されるAND回路76の出力信号を反転した信号をセット端子に受ける。これにより、遮断時間カウンタ71は、上記オーバーカレントが発生してローレベルの第1異常電流信号OCを受けたとき、または、温度異常が発生してローレベルの異常温度信号OTを受けたときに、n個のカウンタをすべて「1」にセットする。これにより、遮断時間カウンタ71は、ハイレベルの出力信号S5を出力するようになり、AND回路77において発振回路74からのクロック信号CLK2が有効化され、このクロックに同期したタイミングでカウントダウン動作を開始する。なお、遮断時間カウンタ71は、各クロックの立下りエッジでカウントダウンを行う。

## [0057]

そして、遮断時間カウンタ71がカウントダウンを開始した後、「0」までカウントダウンしてオーバーフローする前までは、ハイレベルの出力信号S5を出力するから、クロック信号CLK2はAND回路77にて有効化されて遮断時間カウンタ71のクロック端子に入力される。このとき、このハイレベルの出力信号S5を受けたOR回路78からローレベルの出力信号Inhibitがゲート駆動部28に与えられ、パワーMOSFET14の強制遮断動作が実行される。

### [0058]

50

10

20

30

20

30

40

50

これに対して、遮断時間カウンタ71が「0」までカウントダウンしてオーバーフローするとローレベルの出力信号S5を出力し、これに伴ってクロック信号CLK2の入力がAND回路77にて禁止される。このとき、ローレベルの出力信号S5を受けたOR回路78からハイレベルの出力信号Inhibitがゲート駆動部28に与えられ、パワーMOSFET14の強制遮断状態が解除される。従って、電力供給制御装置10がローレベルの制御信号S1(オン指令信号)を受けていれば、パワーMOSFET14は通電状態に復帰する。

### [0059]

以上のように、遮断時間カウンタ71は、図10(OCチョッピング期間参照)に示すように、例えばオーバーカレント状態となってローレベルの第1異常電流信号OCが電流検出部24から出力される毎に、パワーMOSFET15に即時的に強制遮断動作をさせて、nカウント分カウントダウンした後に、その強制遮断動作を解除する役割を果たす。以下、このように、遮断時間カウンタ71によって所定の基準遮断時間後に通電状態に復帰される強制遮断を、「第1強制遮断」という。

# [0060]

#### c . ヒューズ時間カウンタ

ヒューズ時間カウンタ73(「異常時間積算回路」に相当)は、電流検出部24からのローレベルの第2異常電流信号FCを受けているとき、及び、上記遮断時間カウンタ71によってパワーMOSFET14が強制遮断されているときの双方の異常時間(以下、「ヒューズ時間」という)を積算していき、この積算時間が所定の基準ヒューズ時間(>上記基準遮断時間 カウント値を「0」から「m(>n)」までカウントアップするまでの時間 具体的には1024msec 「基準異常時間」に相当)に達したことを条件に、パワーMOSFET15に強制遮断動作をさせるものである。

## [0061]

具体的には、ヒューズ時間カウンタ73は、上記クロック信号CLK1のクロックに同期して初期値0からmまでカウントアップするものである。なお、ヒューズ時間カウンタ73は、各クロックの立下リエッジでカウントアップを行う。より具体的には、ヒューズ時間カウンタ73は、カウントアップ動作中は、ローレベルの出力信号S6を出力し、「m」までカウントアップしてオーバーフローすると、ハイレベルの出力信号S6(「遮断信号」に相当)を出力する。発振回路74からのクロック信号CLK1を有効化させるためのAND回路79には、ヒューズ時間カウンタ73の出力信号S6をレベル反転した信号と、NAND回路80の出力信号とが入力される。このNAND回路80は、ローレベルの第2異常電流信号FCを受けたとき、または、遮断時間カウンタ71がカウントダウン動作中でハイレベルの出力信号S5をレベル反転したローレベルの信号を受けたときに、ハイレベル信号を出力する。

### [0062]

従って、ヒューズ時間カウンタ73は、オーバーフローする前までは、ローレベルの第2異常電流信号FCが出力されたとき、または、遮断時間カウンタ71がカウントダウン動作中のときにAND回路79にてクロック信号CLK1が有効化されることでカウントアップ動作を進行させる。そして、ヒューズ時間カウンタ73は、カウント値「m」までカウントアップしてオーバーフローした後は、ハイレベルの出力信号S6を出力する。このハイレベルの出力信号S6を受けたOR回路78からローレベルの出力信号Inhibitがゲート駆動部28に与えられ、パワーMOSFET14の強制遮断動作が実行される。以下、このように、ヒューズ時間カウンタ73のオーバーフローによる強制遮断を、「第2強制遮断」という。それとともに、ヒューズ時間カウンタ73は、ハイレベルの出力信号S6が出力したことによってクロック信号CLK1の入力が禁止され、このオーバーフロー状態を保持する。従って、このヒューズ時間カウンタ73は、出力保持回路として機能する。

### [0063]

また、ヒューズ時間カウンタ73は、リセット信号発生回路75からローレベルの出力

20

30

40

50

信号RSTが出力されている(リセット状態)とき、または、クリアカウンタ72からハイレベルの出力信号S2(「クリア信号」に相当)が出力された(クリアカウンタ72がオーバーフローした)ときにカウンタ値が初期値「0」にリセットされる。具体的には、OR回路81にクリアカウンタ72からの出力信号S2をレベル反転した信号と、ヒューズ時間カウンタ73の出力信号S6とが入力され、このOR回路81の出力信号とリセット信号発生回路75から出力信号RSTとがAND回路82に入力され、この出力信号がレベル反転されてヒューズ時間カウンタ73のリセット端子に入力される。従って、ヒューズ時間カウンタ73は、リセット信号発生回路75からローレベルの出力信号RSTが出力されているときは、常にカウンタ値が初期値「0」にリセットされる。

### [0064]

一方、リセット信号発生回路75からハイレベルの出力信号RSTが出力されているときは、ヒューズ時間カウンタ73がオーバーフローするまでは、クリアカウンタ72からハイレベルの出力信号S2が出力されることでカウンタ値が初期値「0」にリセットされる。これに対して、ヒューズ時間カウンタ73がオーバーフローすると、クリアカウンタ72からハイレベルの出力信号S2が出力されてもカウンタ値がリセットされず、上記第2強制遮断状態が保持される。

### [0065]

また、ヒューズ時間カウンタ73は、図7に示すように、カウントアップ動作によって積算される積算時間(カウンタ値)に応じた信号、具体的には「bit 0」から「bit 5」のローレベルのビット信号を順次出力する。これにより、閾値電圧生成部52において、FET61aからFET61fまで順次選択的にオンされて、第1異常用閾値電圧 Vocを上記積算時間に応じて経時的にレベルダウンさせることができる。

### [0066]

d . クリアカウンタ

クリアカウンタ72(「正常時間積算回路、オフ指令出力回路」に相当)は、主として、ヒューズ時間カウンタ73がカウントアップ動作を開始した後、オーバーフローするまでの間に、上記電流異常及び温度異常のいずれも発生しなくなった正常状態が所定の基準正常時間(カウント値を「0」から「q」までカウントダウンするまでの時間 具体的には512msec)継続したことを条件に、ヒューズ時間カウンタ73の積算時間(カウンタ値)を初期値「0」にクリアするものである。具体的には、クリアカウンタ72は、上記クロック信号CLK2のクロックに同期して初期値「0」から「q(<n)」までカウントアップするものである。なお、クリアカウンタ72は、各クロックの立上りエッジでカウントアップを行う。また、基準正常時間(基準待機時間)は、例えばヒューズカレントやオーバーカレント状態が解消され負荷等の過熱状態が解消するまでの時間に基づいて定められている。

# [0067]

また、クリアカウンタ72は、リセット信号発生回路75からローレベルの出力信号RSTが出力されている(リセット状態)ときにカウンタ値が初期値「0」にリセットされる。更に、ヒューズ時間カウンタ73がカウントアップ動作を開始した後、オーバーフローする前までは、電流検出部24からのローレベルの第2異常電流信号FCを受けているとき、または、上記遮断時間カウンタ71によってパワーMOSFET14が強制遮断されているときにリセットされる。一方、ヒューズ時間カウンタ73がオーバーフローした後は、ローレベルの制御信号S1(オン指令信号)を受けているときはリセットされる。

# [0068]

具体的には、クリアカウンタ72には、発振回路74からのクロック信号CLK2が直接入力されており、通常はローレベルの出力信号S2を出力し、「q」までカウントアップしてオーバーフローすると例えば1クロック分のハイレベルの出力信号S2(第2オフ指令信号)を出力する。AND回路83は、リセット信号発生回路75からの出力信号RSTが入力されるとともに、その出力信号をレベル反転した信号がクリアカウンタ72のリセット端子に与えられる。従って、リセット信号発生回路75からローレベルの出力信

号RSTが出力されているときにカウンタ値が初期値「0」にリセットされる。

### [0069]

また、AND回路83には、AND回路84の出力信号が入力され、このAND回路84には、OR回路85の出力信号とNAND回路86の出力信号とが入力される。OR回路85は、AND回路87の出力信号と、ヒューズ時間カウンタ73の出力信号S6とが入力される。AND回路87には、第2異常電流信号FCと遮断時間カウンタ71の出力信号S5をレベル反転した信号とが入力される。このような構成により、クリアカウンタ72は、上述したように、ヒューズ時間カウンタ73がカウントアップ動作を開始した後、オーバーフローする前までは、ローレベルの第2異常電流信号FCを受けているとき、または、遮断時間カウンタ71によってパワーMOSFET14が強制遮断されているときにカウンタ値がリセットされる。

[0070]

また、NAND回路86は、ヒューズ時間カウンタ73の出力信号S6と、制御信号S1をレベル反転した信号とが入力される。これにより、クリアカウンタ72は、上述したように、ヒューズ時間カウンタ73のオーバーフロー後において、ローレベルの制御信号S1(オン指令信号)を受けているときはリセットされる。

### [0071]

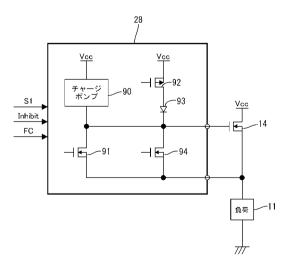

(ゲート駆動部)

図8は、ゲート駆動部28の構成を示した概要図である。ゲート駆動部28は、コントールロジック部27から制御信号S1、第2異常電流信号FC及び出力信号Inhibitとが入力される。ゲート駆動部28は、電源端子P2とパワーMOSFET14及びセンスMOSFET18のゲートとの間に接続されたチャージポンプ90と、パワーMOSFET14及びセンスMOSFET18のゲートとソースの間に接続された通常放電用FET91とを備える。更に、ゲート駆動部28は、電源端子P2とパワーMOSFET14及びセンスMOSFET18のゲートとの間に接続された異常時急速充電用FET94とを備える。

[0072]

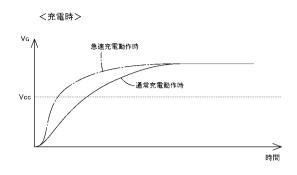

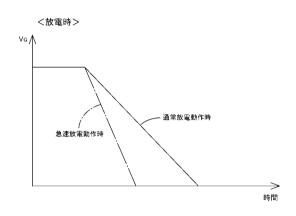

そして、電流異常も温度異常も発生していない正常状態時には、ローレベルの制御信号 S1(オン指令信号)を受けることで、チャージポンプ90のみを駆動させて電源電圧 Vccよりも高いレベルに昇圧した電圧をパワーMOSFET14及びセンスMOSFET18の各ゲート・ソース間に与えてオンして通電動作にさせる通常充電動作を行う(図9<充電時>参照)。一方、ハイレベルの制御信号S1(オフ指令信号)を受けることで、チャージポンプ90の昇圧動作をオフするとともに、通常放電用FET91のみをオンしてパワーMOSFET14及びセンスMOSFET18の各ゲート・ソース間の電荷を放電し、遮断動作させる通常放電動作を行う(図9<放電時>参照)。

[0073]

これに対して、ローレベルの第2異常電流信号FCを受けた状態で、ローレベルの制御信号S1(オン指令信号)を受けたときには、チャージポンプ90とともに異常時急速充電用FET92をオンして、電源電圧Vccまでの昇圧速度を速くする急速充電動作を行う(図9<充電時>参照)。また、ローレベルの第2異常電流信号FCを受けた状態で、ハイレベルの制御信号S1(オフ指令信号)を受けたときには、通常放電用FET91とともに異常時急速放電用FET94をオンして、パワーMOSFET14及びセンスMOSFET18の各ゲート・ソース間の電荷を急速に放電し、遮断動作させる急速放電動作を行う(図9<放電時>参照)。

[0074]

更に、ゲート駆動部28は、ローレベルの出力信号Inhibitを受けたとき(上記第1及び第2の強制遮断時)には、やはり上記急速放電動作を行う。

### [0075]

<本実施形態の作用効果>

10

20

30

40

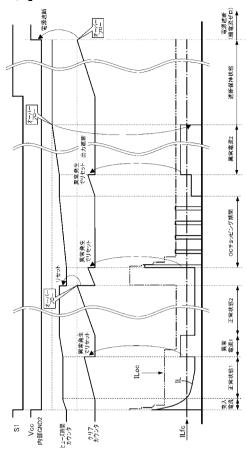

図10は、電力供給制御装置10が、ローレベルの定電圧信号を制御信号S1として受ける場合のタイムチャートである。まず、ローレベルの制御信号S1を受けると、内部グランド生成部23において内部グランドGND2が生成される。そして、この内部グランドGND2が安定するとリセット信号発生回路75からハイレベルの出力信号RSTが出力されて各カウンタ71~73のリセット状態が解除される。

### [0076]

また、ローレベルの制御信号 S 1 がゲート駆動部 2 8 に与えられてパワーMOSFET 1 4 等がオンして通電状態になる。このとき、パワーMOSFET 1 4 には、第 2 異常用 閾値電流 I L fcよりも高い突入電流が流れる。しかし、第 1 異常用閾値電流 I L ocは、突入電流よりも高い初期レベルにあるため、この突入電流によってパワーMOSFET 1 4 等に上記第 1 強制遮断動作を行わせることを防止できる。

#### [0077]

また、突入電流の発生により、ヒューズ時間カウンタ73のカウントアップ動作が開始され、負荷電流 I L が第2異常用閾値電流 I L fcを下回るまで、そのカウンタ値が積算され、これに伴って第1異常用閾値電流 I L bc fcを下回って正常状態(図10で「正常状態1」参照)になると、クリアカウンタ72のカウントアップ動作が開始されるが、この正常状態は上記基準正常時間までは続かず、負荷電流 I L が第2異常用閾値電流 I L fcを上回った時点(同図で「異常電流1」参照)でクリアカウンタ72のカウント値がリセットされるため、ハイレベルの出力信号S2によってヒューズ時間カウンタ73のカウント値がクリアされることはない。

#### [0078]

一方、正常状態が基準正常時間だけ継続したときには(同図で「正常状態2」参照)、クリアカウンタ72がオーバーフローしてハイレベルの出力信号S2が出力され、ヒューズ時間カウンタ73のカウント値がリセットされる。これに伴って、第1異常用閾値電流 I Locも上記初期レベルに復帰する。ここで、例えば、通電路13中において、パワーMOSFET14の下流側(負荷11側)に別の半導体スイッチ素子が設けられ、パワーMOSFET14がオンした状態で、この半導体スイッチ素子が所定の時間間隔(基準正常時間以上の時間間隔)で複数回オンオフされる構成とした場合、突入電流が複数回発生することがある。この場合であっても、各突入電流の発生時に第1異常用閾値電流 I Locを初期レベルに復帰させて、各突入電流によってパワーMOSFET14等に第1強制遮断動作を行わせることを防止できる。

### [0079]

次に、例えば負荷11が短絡などして電流異常が発生した場合、負荷電流ILが第2異常用閾値電流ILfcを上回った時点でヒューズ時間カウンタ73のカウントアップ動作が初期値から再開され、これに伴って第1異常用閾値電流ILocも再び経時的に低いレベルに変更されていく。そして、この異常時の負荷電流ILが第1異常用閾値電流ILocを上回ったときに、パワーMOSFET14等の第1強制遮断動作が実行され、遮断カウンタ73がオーバーフローしたとき(基準遮断時間経過後)にパワーMOSFET14等が通電状態に復帰される。そして、この電流異常状態が継続する限り、第1強制遮断動作と通電状態への復帰とが繰り返される(図10の「OCチョッピング期間」参照)。この間も、ヒューズ時間カウンタ73がカウントアップ動作を行っており、これによって第1異常用閾値電流ILocは第2異常用閾値電流ILfc近くの低いレベルまで低下している。従って、この低い第1異常用閾値電流ILocによってオーバーカレント状態を検出することができる。

# [0080]

そして、その後、間もなく負荷電流ILが少なくとも第2異常用閾値電流ILfcを上回るヒューズカレント状態がある程度継続し(同図で「異常電流2」参照)、ヒューズ時間カウンタ73がオーバーフローすると、パワーMOSFET14等に第2強制遮断動作を行わせる。

10

20

30

40

20

30

40

50

#### [ 0 0 8 1 ]

ここで、第2異常用閾値電流ILfcを負荷11の定格電流ILmaxよりもやや高いレベルとしている。そして、基準ヒューズ時間は、この第2異常用閾値電流ILfcを超えるヒューズカレントが基準正常時間よりも短い時間間隔で断続的に検出された場合に配線30が発煙するまでの時間よりも短い時間に設定されている。このため、配線30の一部のより線が短絡してその一部のより線のみに異常電流が上記基準正常時間よりも短い時間間隔で流れるチャタリングショートを、配線30が発煙に至る前に検出し、パワーMOSFET14に第2強制遮断動作をさせることができるのである。

#### [0082]

上記第2強制遮断の保持状態において、クリアカウンタ72は、ローレベルの制御信号S1を受けている間はカウンタ値がリセットされ、ローレベルの出力信号S2を出力した状態となる。従って、ローレベルの制御信号S1が入力されている限り、ヒューズ時間カウンタ73のカウンタ値はクリアされない状態となる(同図で「ラッチ状態」参照)。そして、電力供給制御装置10がハイレベルの制御信号S1(オフ指令信号)を受けると、クリアカウンタ72がカウントアップ動作を開始する。

#### [0083]

ここで、内部グランド生成部23は、ハイレベルの制御信号S1を受けることでFET41がオフするが、ローレベルの出力信号S2を受けることでFET42がオンしており、通電状態が継続される。従って、例えば上記第2強制遮断がされた後に、ハイレベルの制御信号S1(オフ指令信号)を入力させ、その直後にローレベルの制御信号S1(オン指令信号)を入力させる操作を運転手が行った場合であっても、その時間間隔が基準正常時間内であれば上記第2強制遮断状態を保持することができる。

# [0084]

一方、入力端子P1にハイレベルの制御信号S1(オフ指令信号)が継続して基準正常時間だけ入力されたときには、クリアカウンタ72がオーバーフローしてハイレベルの出力信号S2が内部グランド生成部23に与えられ、その通電が停止される。従って、その後において、電源12から暗電流が内部グランド生成部23を介してグランドに流れて電源12(車両用バッテリー)の充電量を低下させることを防止できる。なお、このとき、リセット信号発生回路75からローレベルの出力信号RSTが出力され、これにより各カウンタ71~73のカウント値がリセットされる。また、ローレベルの出力信号RSTが出力されると、このローレベルの出力信号RSTを受けてFET101がオフしてハイレベル保持回路100が機能して出力信号S2はハイレベルに固定されるため、クリアカウンタ72のカウント値がリセットされても内部グランド生成部23による内部グランドGND2の生成をオフする。

### [0085]

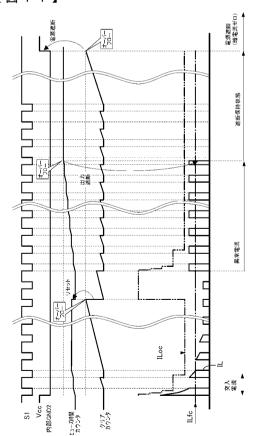

図11は、電力供給制御装置10が、ハイレベルとローレベルとを繰り返すPWM信号を制御信号S1として受ける場合のタイムチャートである。ここで、上記基準正常時間は、PWM信号のオフ時間(ハイレベルが継続する時間)よりも長い時間に設定されている。従って、入力端子P1にPWM信号としての制御信号S1が入力されている状態で、ハイレベルの制御信号S1が入力されている各オフ時間内に、クリアカウンタ72がオーバーフローしてハイレベルの出力信号S2が出力されることはない。従って、PWM信号の入力中に、内部グランド生成部23の通電が停止されることを防止できる。また、異常状態の発生後にPWM信号のハイレベルの入力によってヒューズ時間カウンタ73のカウンタ値がクリアされて第1異常用閾値電流ILocが初期レベルに復帰することを防止でき、低いレベルの第1異常用閾値電流ILocでオーバーカレントを検出できる。

# [0086]

### <他の実施形態>

本発明は上記記述及び図面によって説明した実施形態に限定されるものではなく、例えば次のような実施形態も本発明の技術的範囲に含まれる。

(1)上記実施形態では、半導体スイッチ素子としてパワーMOSFET14としたが

、これに限らず、他のユニポーラトランジスタであっても、バイポーラトランジスタであってもよい。

### [0087]

(2)上記実施形態では、電流検出素子としてセンスMOSFET18を利用した、いわゆるセンス方式としたが、これに限らず、例えば通電路にシャント抵抗を設けてこの電圧降下分に基づき負荷電流を検出する、いわゆるシャント方式であってもよい。

#### [0088]

(3)上記実施形態では、電流異常及び温度異常に基づき異常信号を出力して、この異常信号に基づき異常検出回路として、パワーMOSFET14に強制遮断動作をさせる構成であったが、これに限らず、電流異常及び温度異常のうちいずれか一方の異常に基づきパワーMOSFET14に強制遮断動作をさせる構成であってもよい。さらに、これ以外の異常によって遮断させる構成であってもよい。例えば、電動スライドドアの閉動作時に人が挟まれるなどの異常が検出された場合に、半導体スイッチ素子を遮断する構成が考えれる。この場合も、運転者によってオフ指令信号とオン指令信号との入力が短時間で繰り返されることで、半導体スイッチ素子の遮断保持状態がクリアされて一時的に閉動作が再開されてしまうことを防止できる。

### [0089]

(4)上記実施形態では、異常状態が検出されたから基準異常時間を経過したことを条件にパワーMOSFET14を強制遮断保持状態にする構成であったが、これに限らず、 異常状態が検出された時点でパワーMOSFET14に強制遮断保持状態にする構成であってもよい。

#### [0090]

(5)上記実施形態では、クリアカウンタ72が、本発明のオフ指令出力回路及び正常時間積算回路として機能する構成としたが、これに限らず、オフ指令出力回路と、正常時間積算回路とが別個の回路でもよい。また、パワーMOSFET14に強制遮断保持の前後で、クリアカウンタ72がオーバーフローするまでの時間間を異ならせる、つまり、本発明でいう「基準正常時間」と「基準待機時間」とを異ならせる構成であってもよい。

【図面の簡単な説明】

[0091]

- 【図1】本発明の一実施形態に係る電力供給制御装置の全体構成を示すブロック図

- 【図2】入力インターフェース部の回路図

- 【図3】内部グランド生成部の回路図

- 【図4】カレントミラー部、閾値電圧生成部及び過電流異常検出部の回路図

- 【図5】第1異常用閾値電流と第2異常用閾値電流との設定レベルを説明するためのグラフ

- 【図6】コントロールロジック部の回路図

- 【図7】ヒューズ時間カウンタのカウンタ値とビット信号との対応関係を示した表

- 【図8】ゲート駆動部の構成を示した概要図

- 【図9】充電時及び放電時のゲート電圧と時間との関係を示すグラフ

- 【図10】電力供給制御装置がローレベルの定電圧信号を制御信号として受ける場合のタ 40 イムチャート

【図11】電力供給制御装置がPWM信号を制御信号として受ける場合のタイムチャート 【符号の説明】

[0092]

- 10…電力供給制御装置

- 11...負荷

- 12...電源

- 13...通電路

- 1 4 ... パワーMOSFET(半導体スイッチ素子、パワーFET)

- 18…センスMOSFET (電流検出素子、センスFET)

50

10

20

- 19…温度センサ(温度検出素子)

- 23…内部グランド生成部(定電圧電源生成回路)

- 25...過熱検出部(異常温度検出回路)

- 28…ゲート駆動部(スイッチ制御回路)

- 3 0 ... 電線

- 5 2 ... 閾値電圧生成部(閾値変更回路)

- 5 3 ...過電流異常検出部(異常電流検出回路)

- 73…ヒューズ時間カウンタ(異常時間積算回路)

- OC, FC...異常電流信号

- O T ... 異常温度信号

- I L ... 負荷電流

- ILoc...第1異常用閾値電流(第1閾値)

- ILfc...第2異常用閾値電流(第2閾値)

- Is…センス電流(検出信号)

- S 1 ...制御信号

- S 2 ... 出力信号

【図3】

# 【図5】

# 【図6】

# 【図7】

| カウンタ値     | bit0 | bit1 | bit2 | bit3 | bit4 | bit5 |

|-----------|------|------|------|------|------|------|

| 0≦ m<8    | Lo   | Hi   | Hi   | Hi   | Hi   | Hi   |

| 8≦ m<16   | Hi   | Lo   | Hi   | Hi   | Hi   | Hi   |

| 16≦ m<32  | Hi   | Hi   | Lo   | Hi   | Hi   | Hi   |

| 32≦ m<64  | Hi   | Hi   | Hi   | Lo   | Hi   | Hi   |

| 64≦ m<128 | Hi   | Hi   | Hi   | Hi   | Lo   | Hi   |

| 128≦ m    | Hi   | Hi   | Hi   | Hi   | Hi   | Lo   |

【図8】

【図9】

【図10】

【図11】

## フロントページの続き

# (72)発明者 加藤 雅幸

三重県四日市市西末広町1番14号 株式会社オートネットワーク技術研究所内

# 審査官 栗栖 正和

(56)参考文献 特開2004-048498(JP,A)

特開2002-111465(JP,A)

特開2003-318713(JP,A)

特開2005-323489(JP,A)

特開2003-332446(JP,A)

(58)調査した分野(Int.CI., DB名)

H03K 17/00-17/70