#### (19) **日本国特許庁(JP)**

(51) Int. Cl.

## (12) 公 開 特 許 公 報(A)

$\mathbf{F}$  L

(11)特許出願公開番号

テーマコード (参考)

特開2014-191836 (P2014-191836A)

(43) 公開日 平成26年10月6日(2014.10.6)

5C080 AA06 AA10 BB05 DD09 DD22

CE01 CF07 DA02 DA06

CC26 CC35 CC39 CC63 CD013

JJ02 JJ03 JJ04

AB18 BA11 BA17

FF07 HH09

JJ05 5C380 AA01 AB06

| \ /       |       |                                |                            |         |           |                    |          |         |  |

|-----------|-------|--------------------------------|----------------------------|---------|-----------|--------------------|----------|---------|--|

| G11C      | 19/28 | (2006.01)                      | G11C                       | 19/28   | D         |                    | 5C006    |         |  |

| G11C      | 19/00 | (2006.01)                      | G11C                       | 19/00   | K         |                    | 5C080    |         |  |

| G09G      | 3/20  | (2006.01)                      | G11C                       | 19/00   | J         |                    | 5C38O    |         |  |

| G09G      | 3/36  | (2006.01)                      | GO9G                       | 3/20    | 622E      |                    |          |         |  |

| G09G      | 3/30  | (2006.01)                      | GO9G                       | 3/36    |           |                    |          |         |  |

|           |       | •                              | 審査請求 未                     | 請求請     | 求項の数 9    | OL                 | (全 26 頁) | 最終頁に続く  |  |

| (21) 出願番号 |       | 特願2013-64788 (I                | P2013-64788)               | (71) 出願 | 人 0000066 | 633                |          |         |  |

| (22) 出願日  |       | 平成25年3月26日 (2013.3.26) 京セラ株式会社 |                            |         |           |                    |          |         |  |

|           |       |                                |                            |         | 京都府       | 京都市休               | 見区竹田鳥羽   | 羽殿町 6番地 |  |

|           |       |                                |                            | (74) 代理 | 人 1000891 | 118                |          |         |  |

|           |       |                                |                            |         | 弁理士       | 酒井                 | 宏明       |         |  |

|           |       |                                |                            | (72) 発明 | 者 市村 !    | 照彦                 |          |         |  |

|           |       |                                |                            |         | 京都府       | 京都府京都市伏見区竹田鳥羽殿町6番地 |          |         |  |

|           |       |                                |                            |         | 京セラ       | 株式会社               | :内       |         |  |

|           |       |                                | F ターム (参考) 5C006 BF03 FA41 |         |           |                    |          |         |  |

(54) 【発明の名称】シフトレジスタ回路および画像表示装置

## (57)【要約】

【課題】シフトレジスタ回路を多段に接続したドライバ 回路の回路規模を縮小させることを課題とする。

【解決手段】シフトレジスタ回路 2 0 は、ノード 2 1 の電位が上昇することに応じてノード 2 2 の電位を降下させるトランジスタ 1 と、ノード 2 2 の電位が上昇することに応じてノード 2 1 の電位を降下させるトランジスタ 2 とを有する。シフトレジスタ回路 2 0 は、「 $CLK_1$ 」が入力された際にソースの電位を上昇させるトランジスタ 3 と、ノード 2 1 の電位が上昇することに応じてトランジスタ 3 のソースの電位を ノード 2 3 に供給するトランジスタ 4 とを有する。シフトレジスタ回路 2 0 は、ノード 2 3 の電位が上昇することに応じて「 $OUT_1$ 」を出力させるトランジスタ 5 と、 $OUT_2$ 」を出力させるトランジスタ 6 とを有する。

【選択図】図1

#### 【特許請求の範囲】

#### 【請求項1】

ゲートが第1の導電経路に接続されて、ドレインが第2の導電経路に接続されるとともにソースが低電位端子に接続された、前記第1の導電経路の電位が上昇することに応じて前記第2の導電経路の電位を降下させる第1のトランジスタと、

ゲートが前記第2の導電経路に接続されて、ドレインが前記第1の導電経路に接続されるとともにソースが低電位端子に接続された、前記第2の導電経路の電位が上昇することに応じて前記第1の導電経路の電位を降下させる第2のトランジスタと、

ゲートおよびドレインが第1のクロック信号の入力端子に接続された、前記第1のクロック信号が入力された際にソースの電位を上昇させる第3のトランジスタと、

ゲートが前記第1の導電経路に接続され、ドレインが前記第3のトランジスタのソースに接続されるとともにソースが第3の導電経路に接続された、前記第1の導電経路の電位が上昇することに応じて前記第3のトランジスタのソースの電位を前記第3の導電経路に供給する第4のトランジスタと、

ゲートが前記第3の導電経路に接続され、ドレインが前記第1のクロック信号を所定量遅延させた第2のクロック信号の入力端子に接続されるとともにソースが第1の出力端子に接続された、前記第3の導電経路の電位が上昇することに応じて前記第2のクロック信号を第1の出力信号として前記第1の出力端子から出力させる第5のトランジスタと、

ゲートが前記第3の導電経路に接続され、ドレインが前記第2のクロック信号を所定量遅延させた第3のクロック信号の入力端子に接続されるとともにソースが第2の出力端子に接続された、前記第3の導電経路の電位が上昇することに応じて前記第3のクロック信号を第2の出力信号として前記第2の出力端子から出力させる第6のトランジスタと

を有することを特徴とするシフトレジスタ回路。

#### 【請求項2】

ゲートが次段のシフトレジスタ回路が前記第1の出力信号に対応する信号を出力する出力端子に接続され、ドレインが前記第3の導電経路に接続されるとともにソースが低電位端子に接続された、前記次段のシフトレジスタ回路が出力した信号の電位に応じて前記第3の導電経路の電位を降下させる第7のトランジスタをさらに有することを特徴とする請求項1に記載のシフトレジスタ回路。

## 【請求項3】

ゲートが前記第3の導電経路に接続されて、ドレインが第4の導電経路に接続されるとともにソースが低電位端子に接続された、前記第3の導電経路の電位が上昇することに応じて前記第4の導電経路の電位を降下させる第8のトランジスタと、

ゲートが前記第4の導電経路に接続され、ドレインが前記第3の導電経路に接続されるとともにソースが低電位端子に接続された、前記第4の導電経路の電位が上昇することに応じて前記第3の導電経路の電位を降下させる第9のトランジスタとをさらに有することを特徴とする請求項1または2に記載のシフトレジスタ回路。

#### 【請求項4】

ゲートが前記第1のクロック信号の位相をずらして前記第3のクロック信号と同じタイミングで立ち上がる第4のクロック信号の入力端子に接続されて、ドレインが高電位端子に接続されるとともにソースが前記第4の導電経路に接続された、前記第4のクロック信号の入力に応じて前記第4の導電経路の電位を上昇させる第10のトランジスタをさらに有することを特徴とする請求項1乃至請求項3のいずれか1つに記載のシフトレジスタ回路。

#### 【請求項5】

ゲートが前記第4のクロック信号の入力端子に接続されて、ドレインが高電位端子に接続されるとともにソースが前記第2の導電経路に接続された、前記第4のクロック信号の入力に応じて前記第2の導電経路の電位を上昇させる第11のトランジスタをさらに有することを特徴とする請求項4に記載のシフトレジスタ回路。

#### 【請求項6】

10

20

30

ゲートが前記第2の導電経路に接続され、ドレインが前記第1の出力端子に接続されるとともにソースが低電位端子に接続された、前記第2の導電経路の電位が上昇することに応じて前記第1の出力端子の電位を降下させる第12のトランジスタと、

ゲートが前記第2の導電経路に接続され、ドレインが前記第2の出力端子に接続されるとともにソースが低電位端子に接続された、前記第2の導電経路の電位が上昇することに応じて前記第2の出力端子の電位を降下させる第13のトランジスタとをさらに有することを特徴とする請求項1乃至請求項5のいずれか1つに記載のシフトレジスタ回路。

#### 【請求項7】

ゲートが入力信号の入力端子に接続され、ドレインが高電位端子に接続されるとともに ソースが前記第1の導電経路に接続された、前記入力信号の電位に応じて前記第1の導電 経路の電位を上昇させる第15のトランジスタをさらに有することを特徴とする請求項1 乃至請求項6のいずれか1つに記載のシフトレジスタ回路。

#### 【請求項8】

請求項1乃至請求項7のいずれか1つに記載のシフトレジスタ回路を有するドライバ回路と、

前記ドライバ回路が出力する信号に従って発光する発光素子によって画像を表示する表示 パネルと

を備えたことを特徴とする画像表示装置。

#### 【請求項9】

請求項1乃至請求項7のいずれか1つに記載のシフトレジスタ回路を有するドライバ回路と、

前記ドライバ回路が出力する信号に従って画像を表示する液晶パネルと を備えたことを特徴とする画像表示装置。

【発明の詳細な説明】

## 【技術分野】

## [0001]

本発明は、シフトレジスタ回路および画像表示装置に関する。

#### 【背景技術】

#### [0002]

従来、前段の回路が出力した信号を後段の回路へ伝達するシフトレジスタ回路が知られている。このようなシフトレジスタ回路は、LCD(Liquid Crystal Display)や有機EL(Electro-Luminescence)ディスプレイ等の表示素子を順次操作するためのドライバ回路として用いられている。

#### [0003]

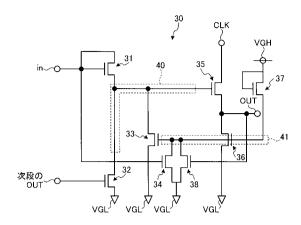

以下、図14を用いて、シフトレジスタ回路の動作について説明する。図14は、従来のシフトレジスタ回路を説明する回路図である。例えば、図14に示すシフトレジスタ回路30は、複数のトランジスタ31~38、ノード40、41を有する。なお、図14に示す例では、トランジスタ31、37は、ゲート(ベース)およびドレイン(コレクタ)がダイオード接続されている。

#### [0004]

このようなシフトレジスタ回路30では、前段の回路から入力された信号を次段の回路に出力しない非選択時においては、ノード40の電位がLow状態となり、ノード41の電位がHigh状態となる。また、シフトレジスタ回路30では、前段の回路から入力された信号を次段の回路に出力する選択時においては、ノード40の電位がHigh状態となり、ノード41の電位がLow状態となる。

#### [0005]

ここで、シフトレジスタ回路30は、前段の回路から入力信号である「in」のパルスが入力されると、ダイオードとして動作するトランジスタ31を介し、パルスをノード40に入力する。このような場合には、ノード40の電位がHigh状態となり、トランジスタ35がオン状態となる結果、シフトレジスタ回路30は、クロック信号である「CL

10

20

30

40

K」を出力信号である「OUT」として出力する。

[0006]

また、シフトレジスタ回路30は、「in」のパルスをトランジスタ34のゲート(ベース)に入力する。このような場合には、トランジスタ34がオン状態となり、ノード41の電位が「VGL(低電位)」へと降下する。また、シフトレジスタ回路30は、クロック信号のパルスをトランジスタ38のゲートに入力する。この結果、トランジスタ38がオン状態になり、ノード41の電位が「VGL」へと降下し、トランジスタ33がオフ状態となり、ノード40の電位がHigh状態となる。

[0007]

また、シフトレジスタ回路30は、次段の回路が出力した「OUT」を、トランジスタ32のゲートに入力する。すると、トランジスタ32がオン状態となるので、ノード40の電位が「VGL」へと降下する。また、シフトレジスタ回路30の動作終了後は、トランジスタ34、38がオフ状態となり、ノード41の電位がLow状態からHigh状態へと遷移し、トランジスタ33、36がオン状態となる結果、ノード40が安定してLow状態となる。

【先行技術文献】

【特許文献】

[00008]

【特許文献1】特開2003-046090号公報

【発明の概要】

【発明が解決しようとする課題】

[0009]

しかしながら、上述したシフトレジスタ回路30では、1つの「in」に対して1つの「OUT」しか出力できないので、シフトレジスタ回路を多段に設置するドライバ回路の回路規模を増大させてしまうという問題がある。

[0010]

例えば、LCDや有機ELディスプレイ等の表示素子を操作するドライバ回路にシフトレジスタ回路30を適用する場合は、シフトレジスタ回路30を走査線の数だけ設置しなければならず、回路規模が増大する結果、狭額縁化を図ることができない。

[0011]

開示の技術は、上記に鑑みてなされたものであって、シフトレジスタ回路を多段に接続したドライバ回路の回路規模を縮小させることができるシフトレジスタ回路および画像表示装置を提供することを目的とする。

【課題を解決するための手段】

[0012]

10

20

30

40

せる第5のトランジスタと、ゲートが前記第3の導電経路に接続され、ドレインが前記第2のクロック信号を所定量遅延させた第3のクロック信号の入力端子に接続されるとともにソースが第2の出力端子に接続された、前記第3の導電経路の電位が上昇することに応じて前記第3のクロック信号を第2の出力信号として前記第2の出力端子から出力させる第6のトランジスタとを有する。

#### 【発明の効果】

#### [ 0 0 1 3 ]

本発明に係るシフトレジスタ回路および画像表示装置は、シフトレジスタ回路を多段に接続したドライバ回路の回路規模を縮小させることができる。

#### 【図面の簡単な説明】

[0014]

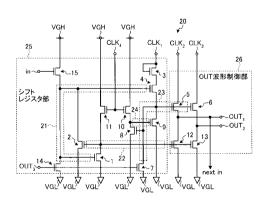

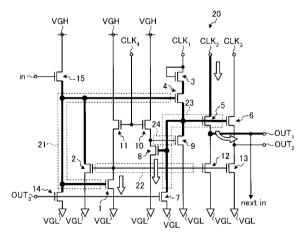

- 【図1】第1形態のシフトレジスタ回路を示す回路図である。

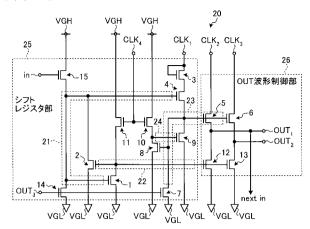

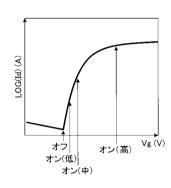

- 【図2】トランジスタの電流特性を説明するグラフである。

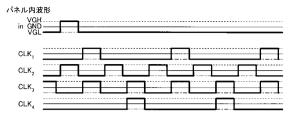

- 【図3】シフトレジスタ回路に入力される信号波形を説明する図である。

- 【図4】シフトレジスタ回路の動作を説明する図である。

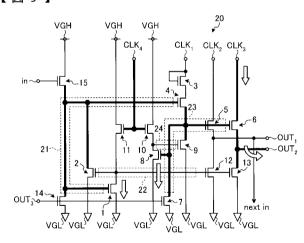

- 【図5】期間T0におけるシフトレジスタ回路の状態を説明する図である。

- 【図6】期間T1におけるシフトレジスタ回路の状態を説明する図である。

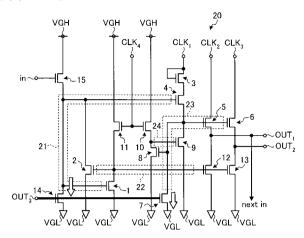

- 【図7】期間T3におけるシフトレジスタ回路の状態を説明する図である。

- 【図8】期間T5におけるシフトレジスタ回路の状態を説明する図である。

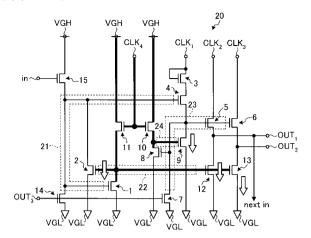

- 【図9】期間T7におけるシフトレジスタ回路の状態を説明する図である。

- 【図10】期間T9におけるシフトレジスタ回路の状態を説明する図である。

- 【図11】期間T15におけるシフトレジスタ回路の状態を説明する図である。

- 【図12】シフトレジスタ回路の適用例を説明する第1の図である。

- 【図13】シフトレジスタ回路の適用例を説明する第2の図である。

- 【図14】従来のシフトレジスタ回路を説明する回路図である。

- 【発明を実施するための形態】

## [ 0 0 1 5 ]

以下に、本発明に係るシフトレジスタ回路および画像表示装置の実施例を図面に基づいて詳細に説明する。なお、この実施例によりこの発明が限定されるものではない。そして、以下に例示する実施形態は、形状を矛盾させない範囲で適宜変更、組み合わせることが可能である。

## [0016]

#### 「第1形態]

## [シフトレジスタ回路の構造]

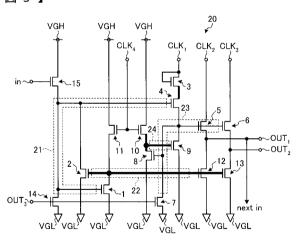

図1を用いて、シフトレジスタ回路の第1形態を説明する。図1は、第1形態のシフトレジスタ回路を示す回路図である。図1に示したように、シフトレジスタ回路20は、シフトレジスタ部25と、OUT波形制御部26とからなる。具体的には、シフトレジスタ回路20は、複数のトランジスタ1~15と、複数のノード21~24を有する。また、シフトレジスタ回路20は、前段のシフトレジスタ回路が出力した信号である「in」、クロック信号である「CLK」」、「CLK」、「CLK」、「CLK」の入力端子を有する。

#### [0017]

また、シフトレジスタ回路20は、シフトレジスタ回路20の出力である「OUT」」、「OUT」」の出力端子を有する。すなわち、シフトレジスタ回路20は、1つの入力信号「in」に対して、2つの信号「OUT」」、「OUT」」を順に出力する。例えば、シフトレジスタ回路20は、画像表示装置のドライバ回路に適用される場合には、「OUT」」、「OUT」」の出力端子から、画像表示領域の連続する2つのゲート線に信号を順次出力する。

#### [0018]

また、シフトレジスタ回路20は、「OUT」」および「OUT」」の出力後に、待機

10

20

30

40

状態へと遷移するために、「OUT $_3$ 」が入力される入力端子を有する。「OUT $_3$ 」は、次段のシフトレジスタ回路において、上記シフトレジスタ回路 $_2$ 0の「OUT $_1$ 」に対応する出力信号である。なお、次段のシフトレジスタ回路では、上記シフトレジスタ回路 $_2$ 0の「CLK $_1$ 」が「CLK $_4$ 」に対応し、「CLK $_2$ 」が「CLK $_2$ 」に対応し、「

## [0019]

また、シフトレジスタ回路 2 0 は、電位が所定の閾値よりも高い値「VGH」に保たれている高電位端子と、電位が所定の閾値よりも低い値「VGL」に保たれている低電位端子とを有する。なお、以下の説明では、「VGH」の値はGND(グランド)よりも高い値とし、例えば、8 (  $\vee$ ) ~ 2 0 (  $\vee$ )、「VGL」の値はGNDよりも低い値とし、例えば、-5 (  $\vee$ ) ~ -15 (  $\vee$ ) とする。

[0020]

また、各トランジスタ 1 ~ 1 5 は、例えば、 n チャンネルの M O S F E T (Metal-Oxid e-Semiconductor Field-Effect Transistor)であるが、本発明はこれに限定されるものではない。例えば、各トランジスタ 1 ~ 1 5 は、N P N 型のトランジスタや、キャリアが電子であるタイプ ( n 型 ) の M I S (Metal Insulator Semiconductor ) 構造を採用した電界効果トランジスタ (FET:Field Effect Transistor) であってもよい。

## [0021]

また、各トランジスタ  $1 \sim 15$  は、FETの一種である薄膜トランジスタ (TFT: Thin Film Transistor)、すなわち n - M ISFETTFTであってもよい。また、PNP型のトランジスタやキャリアが正孔である(P型)のFET、又はTFT等を用いて、シフトレジスタ回路 20 と同等の機能を発揮する回路を構成してもよい。

[ 0 0 2 2 ]

ここで、各トランジスタ1~15は、ゲート、ソース、ドレインの3つの電極が存在するが、ソース、およびドレインは、トランジスタの導電性及び相対的な電位関係によって定義される。このため、以下の説明では、各トランジスタ1~15がnチャンネルのMOSFETであるものとし、各トランジスタ1~15が有する端子のうち、高電位側の端子をドレイン、低電位側の端子をソースと記載する。

[0023]

「接続関係]

ここで、図1に示したシフトレジスタ回路20における各トランジスタ1~15、ノード21~24の接続関係について説明する。

[0024]

ノード 2 1 は、トランジスタ 1 、 2 、 4 、 1 4 、 1 5 を接続する導電経路である。詳細には、ノード 2 1 は、トランジスタ 1 のゲート、トランジスタ 2 のドレイン、トランジスタ 4 のゲート、トランジスタ 1 5 のソースに接続される。 【 0 0 2 5 】

ノード 2 2 は、トランジスタ 1 、 2 、 1 1 、 1 2 、 1 3 を接続する導電経路である。詳細には、ノード 2 2 は、トランジスタ 1 のドレイン、トランジスタ 2 のゲート、トランジスタ 1 3 のゲートに接続される

[0026]

ノード23は、トランジスタ4、5、6、7、8、9を接続する導電経路である。詳細には、ノード23は、トランジスタ4のソース、トランジスタ5のゲート、トランジスタ6のゲート、トランジスタ7のドレイン、トランジスタ8のゲート、トランジスタ9のドレインに接続される。

[0027]

ノード 2 4 は、トランジスタ 8 、 9 、 1 0 を接続する導電経路である。詳細には、ノード 2 4 は、トランジスタ 8 のドレイン、トランジスタ 9 のゲート、トランジスタ 1 0 のソースに接続される。

10

20

30

40

[0028]

トランジスタ1は、ゲートがノード21に接続されて、ドレインがノード22に接続されるとともにソースが低電位端子に接続される。そして、トランジスタ1は、ノード21の電位が所定の閾値よりも高い場合には、オン状態となる。この結果、ノード22の電位が「VGL」へ引き下げられる。

[0029]

トランジスタ2は、ゲートがノード22に接続されて、ドレインがノード21に接続されるとともにソースが低電位端子に接続される。そして、トランジスタ2は、ノード22の電位が所定の閾値よりも高い場合には、オン状態となる。この結果、ノード21の電位が「VGL」へ引き下げられる。

[0030]

トランジスタ3は、ゲートおよびドレインが「CLK」」の入力端子に接続されて、ソースがトランジスタ4のドレインに接続される。そして、トランジスタ3は、「CLK」」の電位が所定の閾値よりも高い場合には、オン状態となる。この結果、トランジスタ4に「VGH」が供給される。

[0031]

トランジスタ4は、ゲートがノード21に接続され、ドレインがトランジスタ3のソースに接続されるとともにソースがノード23に接続される。そして、トランジスタ4は、ノード21の電位が所定の閾値よりも高い場合に、オン状態となる。この結果、「CLK」の電位が所定の閾値よりも高く、ノード21の電位が所定の閾値よりも高い場合に、トランジスタ3から供給される「VGH」がノード23へ供給され、ノード23の電位が上昇する。

[0032]

トランジスタ5は、ゲートがノード23に接続され、ドレインが「CLK<sub>2</sub>」の入力端子に接続されるとともにソースが「OUT<sub>1</sub>」に接続される。そして、トランジスタ5は、ノード23の電位が所定の閾値よりも高い場合に、オン状態となる。この結果、「CLK<sub>2</sub>」が「OUT<sub>1</sub>」として出力される。

[0033]

トランジスタ6は、ゲートがノード23に接続され、ドレインが「CLK<sub>3</sub>」の入力端子に接続されるとともにソースが「OUT<sub>2</sub>」に接続される。そして、トランジスタ6は、ノード23の電位が所定の閾値よりも高い場合に、オン状態となる。この結果、「CLK<sub>3</sub>」が「OUT<sub>2</sub>」として出力される。

[0034]

トランジスタ7は、ゲートが「OUT<sub>3</sub>」の入力端子に接続され、ドレインがノード23に接続されるとともにソースが低電位端子に接続される。そして、トランジスタ7は、「OUT<sub>3</sub>」の電位が所定の閾値よりも高い場合には、オン状態となる。この結果、ノード23の電位が「VGL」へと引き下げられる。

[0035]

トランジスタ8は、ゲートがノード23に接続されて、ドレインがノード24に接続されるとともにソースが低電位端子に接続される。そして、トランジスタ8は、ノード23の電位が所定の閾値よりも高い場合に、オン状態となる。この結果、ノード24の電位が「VGL」へ引き下げられる。

[0036]

トランジスタ9は、ゲートがノード24に接続され、ドレインがノード23に接続されるとともにソースが低電位端子に接続される。そして、トランジスタ9は、ノード24の電位が所定の閾値よりも高い場合に、オン状態となる。この結果、ノード23の電位が「VGL」へ引き下げられる。

[0037]

トランジスタ10は、ゲートが「CLK<sub>4</sub>」の入力端子に接続されて、ドレインが高電位端子に接続されるとともにソースがノード24に接続される。そして、トランジスタ1

10

20

30

40

0 は、「 C L K  $_4$  」の電位が所定の閾値よりも高い場合に、オン状態となる。この結果、 ノード 2 4 に「 V G H 」が供給されて、ノード 2 4 の電位が上昇する。

#### [0038]

トランジスタ11は、ゲートが「CLK 4 」の入力端子に接続されて、ドレインが高電位端子に接続されるとともにソースがノード22に接続される。そして、トランジスタ11は、「CLK 4 」の電位が所定の閾値よりも高い場合に、オン状態となる。この結果、ノード22に「VGH」が供給されて、ノード22の電位が上昇する。

#### [0039]

トランジスタ12は、ゲートがノード22に接続され、ドレインにトランジスタ5のソースおよび「OUT」」の出力端子が接続され、ソースに低電位端子が接続される。そして、トランジスタ12は、ノード22の電位が所定の閾値よりも高い場合に、オン状態となる。この結果、トランジスタ5のソース、すなわち「OUT」」の出力端子における電位が「VGL」へ引き下げられる。

## [0040]

トランジスタ13は、ゲートがノード22に接続され、ドレインにトランジスタ6のソースおよび「OUT<sub>2</sub>」の出力端子が接続され、ソースに低電位端子が接続される。そして、トランジスタ13は、ノード22の電位が所定の閾値よりも高い場合に、オン状態となる。この結果、トランジスタ6のソース、すなわち「OUT<sub>2</sub>」の出力端子における電位が「VGL」へ引き下げられる。

## [0041]

トランジスタ14は、ゲートに「OUT<sub>3</sub>」の入力端子が接続され、ドレインにノード21が接続され、ソースに低電位端子が接続されている。そして、トランジスタ14は、「OUT<sub>3</sub>」の電位が所定の閾値よりも高い場合には、オン状態となる。この結果、ノード21の電位が「VGL」へと引き下げられる。

#### [0042]

トランジスタ15は、ゲートに信号「in」の入力端子が接続され、ドレインに高電位端子が接続され、ソースにノード21が接続される。そして、トランジスタ15は、信号「in」の電位が所定の閾値よりも高い場合には、オン状態となる。この結果、ノード21に「VGH」が供給され、ノード21の電位が上昇する。

## [0043]

このように、シフトレジスタ回路20は、ノード21の電位の上昇に伴って、ノード22の電位を下降させるトランジスタ1と、ノード22の電位の上昇に伴って、ノード21の電位を下降させるトランジスタ2とを有する。また、シフトレジスタ回路20は、トランジスタ3とトランジスタ4により、「CLK」」の電位が高く、ノード21の電位が高い場合に、「VGH」をノード23に供給する。このとき、ノード21の電位を降下させるトランジスタ2、14がオフ状態となり、さらに、トランジスタ15もオフ状態となることから、ブートストラップによりノード21の電位が上昇し、ノード23へ安定的に「VGH」が供給される。

## [0044]

また、シフトレジスタ回路20は、ノード23の電位の上昇に伴って、「CLK<sub>2</sub>」を「OUT<sub>1</sub>」として出力するトランジスタ5と、「CLK<sub>3</sub>」を「OUT<sub>2</sub>」として出力するトランジスタ6とを有する。このとき、ノード23の電位を降下させるトランジスタ7、9がオフ状態となることから、さらに、トランジスタ3もオフ状態となることから、ブートストラップによりノード23の電位が上昇し、各OUTを安定的に出力することができる。

## [0045]

ここで、各トランジスタ1~15のドレイン、ソース間に流れる電流は、ゲート、ソース間の電位に応じて変化する。このため、各トランジスタ1~15は、ゲートの電位が所定の閾値よりも十分に高い場合は、完全なオン状態となるが、所定の閾値よりも十分に高くない場合は、完全なオン状態とはならない。また、各トランジスタ1~15は、ゲート

10

20

30

40

の電位が所定の閾値よりも十分に低い場合は、完全なオフ状態となるが、ゲートの電位が 所定の閾値よりも十分に低くない場合は、完全なオフ状態とはならない。

#### [0046]

例えば、図2は、トランジスタの電流特性を説明するグラフである。なお、図2に示すグラフは、横軸を各トランジスタ1~15のゲート、ソース間の電位 Vg(V:Volt)とし、縦軸にドレイン、ソース間の電流 Id(A:Ampere)を対数表示した。図2に示すように、各トランジスタ1~15は、電位 Vgが十分に低い場合には、電流 Idをほぼ流さないオフ状態となる。

## [ 0 0 4 7 ]

また、各トランジスタ1~15は、電位 Vgが十分に低くない場合には、電流 Idが流れるオン(低)状態となる。また、各トランジスタ1~15は、電位 Vgが十分に高くない場合には、電流 Idが十分に流れないオン(中)状態となる。また、各トランジスタ1~15は、電位 Vgが十分に高い場合には、電流 Idが飽和し、完全なオン状態であるオン(高)状態となる。

#### [0048]

このため、図14に例示した従来のシフトレジスタ回路30は、各トランジスタ31~38のゲートに印加される電位が所定の閾値よりも十分に高くない場合には、各トランジスタ31~38がオン(高)状態とはならず、動作不良を引き起こす場合がある。また、従来のシフトレジスタ回路30は、各トランジスタ31~38のゲートに印加される電位が所定の閾値よりも十分に低くない場合には、オフ状態とはならず、動作不良を引き起こす場合がある。

#### [0049]

一方、本発明のシフトレジスタ回路20は、「OUT」」の電位にではなく、ノード21の電位に応じてノード22の電位を下げる。この結果、シフトレジスタ回路20は、「OUT」」および「OUT2」を出力する際に、ノード22の電位を確実に下げることができる。さらに、シフトレジスタ回路20は、「OUT」」および「OUT2」を出力する際に、ブートストラップによるカップリングによって、ノード23の電位を「VGH」以上にすることができる。この結果、ノード23の電位を十分高い状態に保てることで、信号出力の降下を防ぐことができる。

## [0050]

[シフトレジスタ回路20の動作の流れ]

このようなシフトレジスタ回路 2 0 の動作の流れを説明する。まず、図 3 を用いて、シフトレジスタ回路 2 0 に入力する信号について説明する。図 3 は、シフトレジスタ回路に入力される信号波形を説明する図である。例えば、図 3 に示す例では、シフトレジスタ回路 2 0 には、「in」として、例えば「VST」(垂直走査開始信号:Vertical Start Technology)が入力されるとともに、複数のクロック信号「CLK」」、「CLK」」、「CLK」」が入力される。

#### [0051]

ここで、「VST」とは、シフトレジスタ回路20の前段に他のシフトレジスタ回路が存在しない場合に、「in」としてシフトレジスタ回路20に入力される信号であり、複数のシフトレジスタが信号を伝達する処理の開始を示す信号である。

#### [0052]

また、「 $CLK_1$ 」とは、電位がVGHからVGLまで周期的に変化する第1のクロック信号であり、シフトレジスタ回路 2 0 が「 $OUT_1$ 」および「 $OUT_2$ 」を出力する期間を示す信号である。この「 $CLK_1$ 」は、特許請求の範囲の「第1のクロック信号」の一例である。

#### [0053]

また、「CLK $_2$ 」とは、電位がVGHからVGLまで周期的に変化し、「CLK $_1$ 」を所定量遅延させた信号であり、シフトレジスタ回路20が「OUT $_1$ 」を出力するタイミングを示すクロック信号である。この「CLK $_2$ 」は、特許請求の範囲に記載の「第2

10

20

30

40

のクロック信号」の一例である。

## [0054]

また、「CLK<sub>3</sub>」とは、電位がVGHからVGLまで周期的に変化し、「CLK<sub>2</sub>」を所定量遅延させた信号であり、シフトレジスタ回路20が「OUT<sub>2</sub>」を出力するタイミングを示すクロック信号である。この「CLK<sub>3</sub>」は、特許請求の範囲に記載の「第3のクロック信号」の一例である。

#### [ 0 0 5 5 ]

また、「CLK $_4$ 」とは、電位がVGHからVGLまで周期的に変化し、「CLK $_1$ 」の位相をずらして「CLK $_3$ 」と同じタイミングで立ち上がる信号である。この「CLK $_4$ 」は、特許請求の範囲に記載の「第4のクロック信号」の一例である。

[0056]

すなわち、「CLK $_2$ 」は、「in」と同期してシフトレジスタ回路 2 0 へ入力される。「CLK $_1$ 」と「CLK $_4$ 」は、「CLK $_3$ 」と同じタイミングで立ち上がる信号であるが、位相がずれており、「CLK $_3$ 」と同じタイミングで交互に立ち上がる。「CLK $_2$ 」は、「CLK $_3$ 」を反転させた信号であり、「CLK $_3$ 」が「VGH」のときに「VGL」となる。

#### [0057]

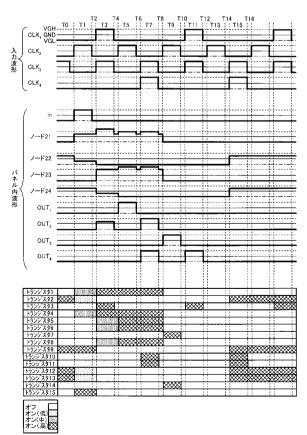

次に、図4を用いて、各信号が入力された際のシフトレジスタ回路20の動作について説明する。図4は、シフトレジスタ回路の動作を説明する図である。なお、図4には、シフトレジスタ回路20に入力される「CLK」」、「CLK2」、「CLK3」、「CLK4」および「in」の入力波形と、ノード21~24の電位変化、「OUT<sub>1</sub>」、「OUT<sub>2</sub>」、「OUT<sub>3</sub>」、「OUT<sub>4</sub>」の波形を示した。

[0058]

ここで、「OUT<sub>3</sub>」は、次段の回路が「in」の入力後、最初に出力する信号であり、シフトレジスタ回路20が出力する「OUT<sub>1</sub>」に対応する信号である。また「OUT<sub>4</sub>」は、次段の回路が「in」の入力後、2番目に出力する信号であり、シフトレジスタ回路20が出力する「OUT<sub>2</sub>」に対応する信号である。

[0059]

また、図4には、各トランジスタ1~15がオン(高)状態となる範囲を網かけで示し、オン(中)状態となる範囲を濃い点描で示し、オン(低)状態となる範囲を薄い点描で示す。また、各トランジスタ1~15がオフ状態となる範囲は、白抜きで示す。また、図4の期間T1よりも前の状態では、ノード21、23の電位が「VGL」であり、ノード22、24の電位が「VGH」付近の電位であるものとする。

[0060]

このような状態において、シフトレジスタ回路 20 が、周期的に変化する「 $CLK_2$ 」と同期した「in」が入力されたことに応じて、「 $OUT_1$ 」および「 $OUT_2$ 」を順次出力し、後段のシフトレジスタ回路から入力される「 $OUT_3$ 」によって出力を停止する一連の流れを示す。ここでは、図 4 の T 1  $\sim$  T 1 6 に示した期間におけるトランジスタ 1  $\sim$  1 5 の状態を用いて、上記一連の流れを具体的に説明する。

[0061]

(期間T0)期間T0は、「in」が入力される前の非選択期間である。具体的には、「in」、「CLK」」、「CLK」」の電位がそれぞれ「VGL」となり、「CLK」の電位が「VGH」となる期間である。

[0062]

図 5 は、期間T0におけるシフトレジスタ回路の状態を説明する図である。なお、図 5 - 図 1 1 では、電位がVGLより高いノードを太線で表し、電位がVGLとなるノードを細線で表すこととする。図 5 に示すように、期間T0では、ノード22とノード24が「VGH」を保持しており、トランジスタ2と9がオン状態であることから、ノード21とノード23は「VGL」状態を維持している。このように、期間T0は、ノード22およびノード24の電位を「VGH」に維持することで、ノード21およびノード23の電位

10

20

30

40

を「VGL」に維持し、各OUTの出力を抑制する非選択期間の一例である。

#### [0063]

具体的には、図4に示すように、ノード22およびノード24の電位が「VGH」であることから、トランジスタ2、9、12、13がオン(高)状態となる。そして、ノード21は、「VGH」が供給されていない状態で、トランジスタ2がオン(高)状態であることから、「VGL」に引っ張られる。この結果、ノード21の電位は「VGL」となる。また、ノード23は、「CLK」」も「VGH」も供給されていない状態で、トランジスタ9がオン(高)状態であることから、「VGL」に引っ張られる。この結果、ノード23の電位は「VGL」となる。

#### [0064]

すなわち、期間 T 0 の状態では、トランジスタ 2 、 9 、 1 2 、 1 3 がオン ( 高 ) 状態となり、その他のトランジスタがオフ状態となる。また、ノード 2 1 およびノード 2 3 の電位は、「 V G L 」となり、ノード 2 2 およびノード 2 4 の電位は、「 V G H 」付近の高電位となる。

#### [0065]

(期間T1)期間T1は、上段のシフトレジスタ回路から出力されたOUTが「in」に入力される、または、最上段の場合はスタートパルスが「in」に入力される期間である。具体的には、「in」の電位が「VGH」となり、「CLK」」の電位が「VGL」となり、「CLK」の電位が「VGH」から「VGL」へ遷移し、「CLK」」の電位が「VGL」となる期間である。

#### [0066]

図6は、期間T1におけるシフトレジスタ回路の状態を説明する図である。図6に示すように、シフトレジスタ回路20の「in」が入力されると、ノード21に「VGH」が供給され、トランジスタ1がオン状態となるので、ノード22の保持されていた「VGH」が「VGL」に引っ張られる。したがって、ノード22の電位が下降し、ノード21の電位が上昇する。

## [0067]

具体的には、図4に示すように、「in」の電位が「VGH」となることから、トランジスタ15がオン(高)状態となり、ノード21に「VGH」が供給されはじめる。そして、ノード21の電位が上昇することにより、ノード21の電位をゲートに入力するトランジスタ1およびトランジスタ4がオン(中)状態となる。

## [0068]

また、トランジスタ1がオン(中)状態となることから、ノード22の電位が「VGL」へ引っ張られる。したがって、ノード22の電位は、「VGH」から降下し、「VGL」よりも高く「GND」よりも低い電位となる。また、トランジスタ2、12、13は、ゲートに入力されるノード22の電位が「VGH」よりも降下するので、オン(高)状態からオン(低)状態となる。したがって、ノード21は、トランジスタ2によって、若干「VGL」へ引っ張られる。この結果、ノード21の電位は、「VGH」よりも低く「GND」よりも高くなる。なお、ノード24の電位は、引き続き「VGH」を維持するので、トランジスタ9は、オン(高)状態を維持する。

## [0069]

すなわち、期間T1の状態では、トランジスタ9および15がオン(高)状態となり、トランジスタ1および4がオン(中)状態となり、トランジスタ2、12、13がオン(低)状態となり、その他のトランジスタがオフ状態となる。また、ノード21の電位は、「VGH」よりも低く「GND」よりも高くなり、ノード22の電位は、「GND」よりも低い電位となり、ノード23の電位は、「VGL」となり、ノード24の電位は、期間T0から引き続き、「VGH」付近の高電位となる。

## [0070]

(期間T2)期間T2は、「in」が「VGL」となる期間である。具体的には、「in」、「CLK」」、「CLK」、「CLK」、「CLK」の各電位が「VGL」と

10

20

30

40

20

30

40

50

なる期間である。期間T2は、期間T1から「in」が「VGL」となる期間なので、トランジスタ15がオフ状態となる。しかし、ノード21は、いずれのトランジスタからも「VGL」へ引っ張られない。したがって、ノード21の電位は、T1期間の電位を保持する。

[0071]

(期間T3)期間T3は、「CLK」」と「CLK」」の電位が「VGH」となる期間である。具体的には、「in」の電位が「VGL」となり、「CLK」」の電位が「VGH」となり、「CLK」」の電位が「VGH」となり、「CLK」」の電位が「VGL」となる期間である。

[0072]

図 7 は、期間 T 3 におけるシフトレジスタ回路の状態を説明する図である。図 7 に示すように、「 C L K  $_1$  」により、ノード 2 3 に「 V G H 」が供給されるので、トランジスタ 8 がオン状態となり、ノード 2 4 が「 V G L 」に引っ張られる。そして、トランジスタ 4 においてブートストラップが発生し、ノード 2 1 が「 V G H 」よりも高い電位となる。このため、トランジスタ 1 がよりオン状態となり、ノード 2 2 が「 V G L 」となる。また、ノード 2 3 が「 V G H 」であることから、「 C L K  $_3$  」のパルスは、トランジスタ 6 を介して「 O U T  $_2$  」へ出力される。この結果、前段の「 O U T  $_2$  」と同じように表示エリアのゲートがオンし、前段の画素に書き込まれる電位がこの画素にも書き込まれる。しかし、これはプリチャージの役割を果たす。

[0073]

具体的には、図4に示すように、「CLK」」の電位が「VGH」となることから、トランジスタ3がオン(高)状態となり、トランジスタ4のドレインに「VGH」が供給される。一方で、トランジスタ2および14がオフ状態であることから、ノード21は「VGL」へ引っ張られない。これらの結果、トランジスタ4を介してノード21でブートストラップが発生し、カップリングによってノード21の電位が「VGH」以上となる。例えば、ノード21の電位は、「VGH」に対して1.3~1.5倍程度に上昇する。

[0074]

そして、ノード 2 1 の電位上昇に伴って、トランジスタ 1 がオン ( 高 ) 状態となり、ノード 2 2 の電位が「VGL」へ引っ張られる。このため、ノード 2 2 の電位は、完全に「VGL」へと引き下げられる。このようにノード 2 2 の電位が「VGL」となることから、トランジスタ 2 、 1 2 、 1 3 は、オフ状態となる。

[0075]

また、トランジスタ3および4がオン状態となるので、ノード23へ「VGH」が供給され、ノード23の電位が「VGH」となる。そして、ノード23の電位が「VGH」となることから、トランジスタ8がオン(中)状態となり、ノード24の電位が「VGL」へと引っ張られる。この結果、ノード24の電位は、「VGL」よりも高く「GND」よりも低くなる。このノード24の電位降下に伴ってトランジスタ9はオフ状態となる。

[0076]

[0077]

すなわち、期間T3の状態では、トランジスタ1、3、4がオン(高)状態となり、トランジスタ5、6、8がオン(中)状態となり、その他のトランジスタがオフ状態となる。また、ノード21の電位が「VGL」となり、ノード23の電位が「VGL」となり、ノード24の電位が「VGL」よりも高く「GND」よりも低くなる。さらに、プリチャージとして「OUTヵ」が出力される。

[0078]

(期間 T 4 )期間 T 4 は、「C L K  $_1$  」と「C L K  $_3$  」が「V G H 」から「V G L 」となる期間である。具体的には、「i n 」、「C L K  $_1$  」、「C L K  $_2$  」、「C L K  $_3$  」、「

20

30

40

50

$CLK_4$ 」の各電位が「VGL」となる期間である。期間 T4 は、「 $CLK_1$ 」と「 $CLK_3$ 」が「VGL」となるので、トランジスタ 3 がオフ状態となる。一方で、ノード 2 1 および 2 3 の電位は「VGH」を保持し、ノード 2 2 および 2 4 の電位は「VGL」を保持する。

[0079]

(期間T5)期間T5は、「CLK $_2$ 」のパルスが「VGL」から「VGH」へ切り替る期間である。具体的には、「CLK $_2$ 」の電位が「VGH」となり、その他の「in」、「CLK $_1$ 」、「CLK $_3$ 」、「CLK $_4$ 」の各電位が「VGL」となる期間である。

[0800]

図 8 は、期間 T 5 におけるシフトレジスタ回路の状態を説明する図である。図 8 に示すように、「 C L K  $_2$  」の電位が「 V G H 」となることから、トランジスタ 5 のドレイン・ゲート間容量によって、ブートストラップが発生し、ノード 2 3 が「 V G H 」よりも高い電位に持ち上げられる。これにより、「 C L K  $_2$  」のパルスは電圧降下もなく「 O U T  $_1$  」へ出力される。

[0081]

具体的には、図4に示すように、「CLK」」が「VGL」であることから、トランジスタ3がオフ状態となり、トランジスタ4におけるブートストラップが終了し、ノード21の電位が「VGH」であることから、トランジスタ1は引き続きオン(高)状態を維持する。このため、ノード22は、「VGL」へ引き続き引っ張られるので、「VGL」を維持する。したがって、トランジスタ2、12、13は、オフ状態を維持する。

[0082]

そして、ノード23には、期間T3からトランジスタ4を介して「VGH」が供給される。また、ノード23が高電位であることから、トランジスタ8がオン(高)状態となり、ノード24が「VGL」を維持するので、トランジスタ9もオフ状態を維持する。このように、ノード23の電位を降下させる各トランジスタおよびトランジスタ3がオフ状態のときに、「CLK2」の電位が「VGH」となることから、ノード23においてブートストラップが発生する。この結果、ノード23の電位がカップリングによって「VGH」以上となる。したがって、トランジスタ5が完全にオン(高)状態となり、電圧降下もなく、「CLK2」が「OUT1」から出力される。なお、ノード23の電位は、例えば「VGH」に対して1.3~1.5倍程度に上昇する。

[0083]

すなわち、期間T5の状態では、トランジスタ1、4、5、6、8がオン(高)状態となり、その他のトランジスタがオフ状態となる。また、ノード21の電位が「VGH」となり、ノード22の電位が「VGL」となり、ノード23の電位が「VGL」以上となり、ノード24の電位が「VGL」となる。さらに、「CLK<sub>2</sub>」が「OUT<sub>1</sub>」として出力される。

[0084]

(期間T6)期間T6は、「CLK $_2$ 」のパルスが「VGH」から「VGL」に切り替る期間である。具体的には、「in」、「CLK $_1$ 」、「CLK $_2$ 」、「CLK $_3$ 」、「CLK $_4$ 」の各電位が「VGL」となる期間である。期間T6では、「OUT $_1$ 」が「CLK $_2$ 」により「VGH」から「VGL」へ引かれる。また、ノード23もカップリングの影響を受けブートストラップ前の電位まで降下する。

[ 0 0 8 5 ]

(期間T7)期間T7は、「CLK $_3$ 」と「CLK $_4$ 」のパルスが「VGL」から「VGH」へと切り替る期間である。具体的には、「in」、「CLK $_1$ 」、「CLK $_2$ 」の電位が「VGL」となり、「CLK $_3$ 」および「CLK $_4$ 」の電位が「VGH」となる期間である。

[0086]

図9は、期間T7におけるシフトレジスタ回路の状態を説明する図である。図9に示す

20

30

40

50

ように、「CLK $_3$ 」は、トランジスタ6を介して「OUT $_2$ 」へ出力される時にブートストラップ効果により、ノード23が「VGH」よりも高い電位に持ち上げられる。この結果、「CLK $_3$ 」のパルスが、「VGH」から電位の降下もなく「OUT $_2$ 」へ出力される。また、「CLK $_4$ 」も電位が「VGL」から「VGH」へと切り替り、トランジスタ10および11がオン状態となり、ノード22とノード24へ「VGH」が供給される。ところが、トランジスタ1およびトランジスタ8がオン状態であることから、ノード22とノード24の電位が「VGL」から変化することなく、そのままの電位を維持する。

具体的には、図4に示すように、「CLK $_4$ 」の電位が「VGH」であることから、トランジスタ10および11がオン(高)状態となり、ノード22およびノード24へ「VGH」が供給される。一方で、ノード21の電位が「VGH」であることから、トランジスタ1がオン(高)状態となり、ノード22は「VGL」へ引っ張られる。したがって、ノード22の電位は「VGL」を維持する。また、ノード23の電位が「VGH」であることから、トランジスタ8がオン(高)状態となり、ノード24は「VGL」へ引っ張られる。したがって、ノード24の電位は「VGL」を維持する。

[ 0 0 8 8 ]

[0087]

ノード24が「VGL」を維持するので、トランジスタ9もオフ状態を維持する。このように、ノード23の電位を降下させる各トランジスタおよびトランジスタ3がオフ状態のときに、「CLK₃」の電位が「VGH」となることから、ノード23においてプートストラップが発生する。この結果、ノード23の電位がカップリングによって「VGH」以上となる。したがって、トランジスタ6が完全にオン(高)状態となり、電圧降下もなく、「CLK₃」が「OUTヵ」から出力される。

[0089]

すなわち、期間T7の状態では、トランジスタ1、4、5、6、8、10、11がオン(高)状態となり、その他のトランジスタがオフ状態となる。また、ノード21の電位が「VGL」となり、ノード23の電位が「VGL」となり、ノード23の電位が「VGL」となる。さらに、「CLK $_3$ 」が「OUT $_2$ 」として出力される。なお、期間T7では、次段のシフトレジスタ回路において「OUT $_4$ 」が出力される。

[0090]

(期間T8)期間T8は、「CLK $_4$ 」と「CLK $_3$ 」のパルスが「VGH」から「VGL」となる期間である。具体的には、「in」、「CLK $_1$ 」、「CLK $_2$ 」、「CLK $_3$ 」、「CLK $_4$ 」の各電位が「VGL」となる期間である。期間T8では、「OUT $_2$ 」が「「CLK $_3$ 」により「VGH」から「VGL」へ引っ張られる。また、ノード23もカップリングの影響を受けブートストラップ前の電位まで降下する。また、「CLK $_4$ 」の電位は「VGH」から「VGL」となるので、トランジスタ10および11がオン(高)状態からオフ状態となり、ノード22とノード24への「VGH」の供給が停止する

[0091]

(期間T9)期間T9は、次段の「OUT<sub>3</sub>」が出力される期間である。具体的には、期間T5と同様、「CLK $_2$ 」の電位が「VGH」となり、その他の「in」、「CLK $_1$ 」、「CLK $_3$ 」、「CLK $_4$ 」の各電位が「VGL」となるとともに、「OUT $_3$ 」の電位が「VGH」となる期間である。

[0092]

図 1 0 は、期間T9におけるシフトレジスタ回路の状態を説明する図である。図 1 0 に示すように、「OUT<sub>3</sub>」のパルスによって、トランジスタ 7 および 1 4 がオン状態となり、ノード 2 1 とノード 2 3 が「VGL」へ引かれる。また、ノード 2 1 およびノード 2 3 の電位が降下することにより、トランジスタ 1 、 4 、 5 、 6 、 8 がオフ状態となる。

[ 0 0 9 3 ]

具体的には、図4に示すように、「OUT₃」の電位が「VGH」となることから、ト

20

30

40

50

ランジスタ 7 および 1 4 がオン(高)状態となる。このため、ノード 2 1 の電位は、トランジスタ 1 4 のオンに伴って、「VGL」に引っ張られるので、完全な「VGL」となる。また、ノード 2 3 の電位も、トランジスタ 7 のオンに伴って、「VGL」に引っ張られるので、完全な「VGL」となる。

[0094]

そして、ノード21の電位が「VGL」になることから、トランジスタ1および4もオフ状態となる。同様に、ノード23の電位が「VGL」になることから、トランジスタ5、6、8もオフ状態となる。

[0095]

すなわち、期間T9の状態では、トランジスタ7および14がオン(高)状態となり、その他のトランジスタがオフ状態となる。また、ノード21の電位は、「VGL」へ降下し、ノード22の電位は、「VGL」を維持し、ノード23の電位は、「VGL」へ降下し、ノード24の電位は、「VGL」を維持する。

[0096]

(期間T10)期間T10は、期間T9から「CLK $_2$ 」が「VGL」に切り替り、「OUT $_3$ 」が「VGL」に切り替る期間である。具体的には、「in」、「CLK $_1$ 」、「CLK $_2$ 」、「CLK $_3$ 」、「CLK $_4$ 」、「OUT $_3$ 」の各電位が「VGL」となる期間である。

[0097]

この期間T10は、期間T9の状態から変化しない。

[0098]

(期間T11)期間T11は、期間T10から「CLK」」および「CLK」」が「VGH」に切り替わる期間であり、「OUT」」が「VGH」に切り替る期間である。具体的には、「CLK」」の電位が「VGL」となり、「CLK」」の電位が「VGL」となり、「CLK」」の電位が「VGL」となり、「CLK」」の電位が「VGL」となる期間である。なお、この期間では、次段のシフトレジスタ回路において「OUT」」が出力される。

[0099]

図 4 に示すように、期間 T 1 1 では、「 C L K  $_3$  」が「 V G H 」となるが、トランジスタの状態に影響を及ぼさない。一方、「 C L K  $_1$  」が「 V G H 」となるので、トランジスタ 3 がオン(高)状態となる。

[0100]

(期間 T 1 2 )期間 T 1 2 は、期間 T 1 1 から「 C L K  $_1$  」および「 C L K  $_3$  」が「 V G L 」に切り替る期間である。具体的には、「 C L K  $_1$  」、「 C L K  $_2$  」、「 C L K  $_3$  」、「 C L K  $_4$  」の各電位が「 V G L 」となる期間である。したがって、トランジスタ 3 がオン(高)状態からオフ状態になる。

[0101]

(期間T13)期間T13は、期間T12から「CLK<sub>2</sub>」が「VGH」に切り替る期間である。具体的には、「CLK<sub>1</sub>」の電位が「VGL」となり、「CLK<sub>2</sub>」の電位が「VGL」となり、「CLK<sub>2</sub>」の電位が「VGL」となり、「CLK<sub>4</sub>」の電位が「VGL」となる期間である。図4に示すように、期間T13では、「CLK<sub>2</sub>」が「VGH」となるが、トランジスタの状態に影響を及ぼさないので、期間T12の状態から各トランジスタの状態および各ノードの状態は変化しない。

[0102]

(期間T14)期間T14は、期間T13から「CLK $_2$ 」が「VGL」に切り替る期間である。具体的には、「CLK $_1$ 」、「CLK $_2$ 」、「CLK $_3$ 」、「CLK $_4$ 」の各電位が「VGL」となる期間である。したがって、期間T13の状態から各トランジスタの状態および各ノードの状態は変化しない。

[ 0 1 0 3 ]

(期間 T 1 5 ) 期間 T 1 5 は、「C L K ₄ 」が「 V G L 」から「 V G H 」へ切り替る期間

20

30

40

50

である。具体的には、「CLK  $_1$  」および「CLK  $_2$  」の電位が「VGL」となり、「CLK  $_3$  」および「CLK  $_4$  」の電位が「VGH」となる期間である。

## [0104]

図11は、期間T15におけるシフトレジスタ回路の状態を説明する図である。図11に示すように、「CLK $_4$ 」が「VGH」となることから、トランジスタ10および11がオン状態となり、「VGH」がノード22とノード24へ供給される。このため、トランジスタ2、9、12、13がオン状態となり、ノード21とノード23が安定して「VGL」となる。したがって、「CLK $_1$ 」や「CLK $_2$ 」や「CLK $_3$ 」が「VGL」から「VGH」へ切り替っても影響を受けず誤動作することはない。この「CLK $_4$ 」は定期的に「VGL」から「VGH」へ切り替るので、電位供給も定期的に行われる。このため、ノード22とノード24は、安定して「VGH」を保つ。

[0105]

具体的には、「CLK $_4$ 」が「VGH」となることから、トランジスタ10および11がオン(高)状態となる。このため、ノード22へ「VGH」が供給されるとともに、ノード24へ「VGH」が供給され、ノード22およびノード24が「VGH」付近の高電位となる。ノード22の電位が高電位になるので、ノード22の電位をゲートに入力するトランジスタ2、12、13がオン(高)状態となる。この結果、ノード21の電位は、トランジスタ2を介して「VGL」へ引っ張られるので、安定して「VGL」を保つ。また、「OUT $_1$ 」および「OUT $_2$ 」についても、それぞれトランジスタ12およびトランジスタ13によって「VGL」へ引っ張られる。

[0106]

そして、ノード23が「VGL」であることから、トランジスタ8はオフ状態であるので、ノード24は、供給される「VGH」を維持する。このため、ノード24の電位をゲートに入力するトランジスタ9がオン(高)状態となり、ノード23は、安定して「VGL」を保つ。さらに、ノード23の電位が「VGL」で安定するので、トランジスタ5およびトランジスタ6もオフ状態を維持する。

[0107]

すなわち、期間 T 1 5 の状態では、トランジスタ 2 、 9 、 1 0 、 1 1 、 1 2 、 1 3 がオン ( 高 ) 状態となり、その他のトランジスタがオフ状態となる。また、ノード 2 1 およびノード 2 3 の電位が「 V G L 」となり、ノード 2 2 およびノード 2 4 の電位が「 V G H 」付近の高電位となる。

[0108]

(期間T16)期間T16は、期間T15の状態から、「CLK  $_3$  」および「CLK  $_4$  」が「VGH」から「VGL」へ切り替る期間である。具体的には、「CLK  $_1$  」、「CLK  $_2$  」、「CLK  $_3$  」、「CLK  $_4$  」の各電位が「VGL」となる期間である。

[0109]

図 4 に示すように、「CLK  $_4$  」が「VGL」となることから、トランジスタ 1 0 および 1 1 がオフ状態となる。このため、ノード 2 2 およびノード 2 4 への「VGH」の供給が抑制される。ところが、ノード 2 2 またはノード 2 4 を「VGL」へ降下させるトランジスタがいずれもオフ状態であることから、ノード 2 2 およびノード 2 4 の電位は、期間 T 1 5 から引き続き「VGH」を維持する。

[0110]

「シフトレジスタ回路20の効果]

上述したように、シフトレジスタ回路20は、1つの「in」に対して、「OUT<sub>1</sub>」および「OUT<sub>2</sub>」を出力することができるので、シフトレジスタ回路20からなるドライバ回路の回路規模を縮小させることができる。例えば、シフトレジスタ回路20は、表示素子を操作するドライバ回路に適用した場合は、ドライバ回路の回路規模を縮小させる結果、狭額縁化を図ることができる。

[0111]

また、「CLK」」が「VGH」のときにノード21を「VGL」へ引っ張るトランジ

スタがオフ状態となるので、ノード21にブートストラップが発生し、ノード23へ「VGH」を維持した「CLK」」が安定的に出力することができる。また、「CLK」」が「VGH」のときにノード23を「VGL」へ引っ張るトランジスタがオフ状態とすることができる。さらに、このときに、トランジスタ3が「CLK」」によってオフ状態となることから、ノード23の「VGH」がノード23内に留まることができるので、ノード23にブートストラップを発生させることができる。したがって、「OUT」」を安定的に出力することができる。

## [0112]

同様に、「CLK<sub>3</sub>」が「VGH」のときにノード23を「VGL」へ引っ張るトランジスタがオフ状態とすることができる。さらに、このときに、トランジスタ3が「CLK<sub>1</sub>」によってオフ状態となることから、ノード23の「VGH」がノード23内に留めることができるので、ノード23にブートストラップを発生させることができる。したがって、「OUT<sub>2</sub>」を安定的に出力することができる。

[0113]

また、シフトレジスタ回路20は、ゲートが「OUT<sub>3</sub>」の入力端子に接続され、ドレインがノード23に接続されるとともにソースが低電位端子に接続された、「OUT<sub>3</sub>」の電位に応じてノード23の電位を降下させるトランジスタ7を有する。このため、シフトレジスタ回路20の非選択期間では、ノード23の電位を降下させることができるので、信号の出力を正確に抑制できる。

[0114]

すなわち、「CLK」」はノード23に「VGH」を出力した後には「VGL」となり、また、トランジスタ3はダイオード接続となっている。このため、「CLK  $_2$  」を「OUT」」へ出力する時にはトランジスタ5のゲート・ドレイン間容量によってブートストラップを発生させることができ、「CLK  $_3$  」を「OUT  $_2$  」へ出力する時にはトランジスタ6のゲート・ドレイン間容量によってブートストラップを発生させることができる。この結果、ノード23の電位が「VGH」以上に高くなり、「OUT」」は「CLK  $_2$  」と同じ電位を出力することができ、「OUT  $_2$  」は「CLK  $_3$  」と同じ電位を出力することができる。

[0115]

また、シフトレジスタ回路20は、ノード23の電位に応じてノード24の電位を降下させるトランジスタ8と、ノード24の電位に応じてノード23の電位を降下させるトランジスタ9を有する。このため、シフトレジスタ回路20が選択期間、すなわち、ノード23が「VGH」などの高電位の場合には、ノード24の電位を「VGL」へ降下させることができるので、ノード23を高電位に維持することができ、安定的に出力することができる。また、シフトレジスタ回路20が非選択期間、すなわち、ノード23が「VGL」などの低電位の場合には、ノード24の電位を「VGH」に維持することができるので、ノード23を低電位にすることができ、安定的に出力を抑制することができる。

[0116]

また、シフトレジスタ回路 2 0 は、ゲートが「CLK」」と位相をずらして「CLK」 と同じタイミングで立ち上がる「CLK」の入力に応じてノード 2 4 の電位を上昇させるトランジスタ 1 0 を有する。このため、ノード 2 4 へ安定的に「VGH」を供給することができる。

[0117]

また、シフトレジスタ回路 2 0 は、「CLK  $_4$  」の入力に応じてノード 2 2 の電位を上昇させるトランジスタ 1 1 を有する。このため、ノード 2 2 へ安定的に「VGH」を供給することができる。そして、ノード 2 2 の電位上昇に伴って、「OUT  $_1$  」または「OUT  $_2$  」の電位を「VGL」へ降下させるトランジスタ 1 2 および 1 3 を有する。このため、シフトレジスタ回路 2 0 は、オフ状態の際に、誤った「OUT  $_1$  」および「OUT  $_2$  」の出力を防ぐことができる。

[0118]

10

20

30

また、シフトレジスタ回路20は、次段の回路が出力した「OUT<sub>3</sub>」の電位が上昇することに応じて、ノード21の電位を降下させるトランジスタ14を有する。このため、シフトレジスタ回路20は、後段の回路が信号を出力した際に、確実に非選択状態に遷移することができる。また、シフトレジスタ回路20は、「in」の電位が上昇することに応じて、ノード21の電位を上昇させるトランジスタ15を有する。このため、シフトレジスタ回路20は、「in」が入力された際にノード21の電位を上昇させ、選択状態に遷移することができる。

## [0119]

#### [適用範囲]

例えば、上記の実施形態で例示したシフトレジスタ回路 2 0 は、液晶パネルや有機 E L (Electro-Luminescence) パネルを用いた画像表示装置を動作させるドライバ回路に好適に適用される。また、シフトレジスタ回路 2 0 は、上述したドライバ回路以外の回路にも適用することができる。また、シフトレジスタ回路 2 0 は、複数のトランジスタと、各素子を順次駆動するためのドライバ回路とを有するセンサ装置、発光素子アレイ、サーマルヘッド等、任意の装置に適用することができる。

#### [ 0 1 2 0 ]

#### (液晶パネルへの適用)

以下の説明では、シフトレジスタ回路20の適用例として、液晶パネルを用いた画像表示装置を動作させるドライバ回路にシフトレジスタ回路20を適用する例について説明する。

#### [0121]

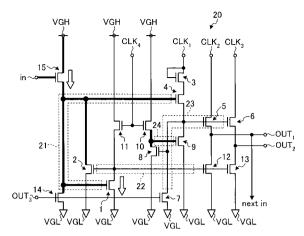

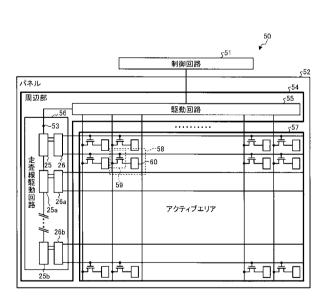

図12は、シフトレジスタ回路の適用例を説明する第1の図である。図12に示す例では、画像表示装置50は、制御回路51とパネル52とを有する。なお、画像表示装置50は、バックライト等の光源装置、カラーフィルタ基板、偏光方向が互いに異なる偏光板等を有するが、図12では、理解を容易にするため、それらの記載を省略した。

#### [0122]

制御回路 5 1 は、例えば、パネル 5 2 に配置される F P C (Flexible Printed Circuits)上に設けられたり、または、パネル 5 2 の外部回路基板上に設けられており、パネル 5 2 を駆動させるための制御信号を駆動回路 5 5 に出力する。なお、図 1 2 では、F P C 、または外部回路基板についての図示を省略した。

#### [0123]

また、パネル 5 2 には、液晶パネルが用いられており、一対の基板から構成されている。例えば、パネル 5 2 は、アクティブエリア 5 7 に薄膜トランジスタが形成されたアレイ基板とアレイ基板に対向するカラーフィルタ基板とからなる一対のガラス基板で構成されている。また、アクティブエリア 5 7 のアレイ基板の周辺には、周辺部 5 4 が形成されている。周辺部 5 4 には、駆動回路 5 5 および走査線駆動回路 5 6 が設けられており、走査線駆動回路 5 6 はアレイ基板のガラス上に形成されている。また、駆動回路 5 5 と走査線駆動回路 5 6 とは走査線制御線 5 3 で接続されている。

#### [0124]

駆動回路55は、駆動用の半導体素子からなり、アクティブエリア上に延在されたデータ線に画像信号を出力する信号線駆動回路、走査線制御回路および対向電位駆動回路等で構成されている。なお、駆動回路55は、アクティブエリア57の周辺部54にCOG(Chip On Glass)方式で実装されている。

## [0125]

また、パネル 5 2 の周辺部 5 4 に設けられた走査線駆動回路 5 6 には、第 1 形態において説明したシフトレジスタ回路 2 0 と同じ機能を発揮する複数の回路が適用されている。 具体的には、走査線駆動回路 5 6 には、シフトレジスタ部 2 5 と同様の機能を発揮するシフトレジスタ部 2 5 ~ 2 5 b が多段に接続され、各シフトレジスタ部 2 5 ~ 2 5 b には、OUT波形制御部 2 6 ~ 2 6 b が接続されている。 10

20

30

20

30

40

50

#### [0126]

なお、シフトレジスタ部 2 5 ~ 2 5 b は、パネル 5 2 のアレイ基板上に一体的に形成された走査線駆動回路 5 6 上に形成されている。また、走査線駆動回路 5 6 は、シフトレジスタ部 2 5 ~ 2 5 b、および O U T 波形制御部 2 6 ~ 2 6 b 以外にも、複数のシフトレジスタ部、および O U T 波形制御部の組からなるシフトレジスタ回路を有するが、図 1 2 では、理解を容易にするため、記載を省略した。また、各 O U T 波形制御部 2 6 ~ 2 6 b のそれぞれには、アクティブエリア 5 7 上に延設された走査線が 2 つずつ接続されている。また、図 1 2 に示す例では、理解を容易にするため、「C L K 1 」~「C L K 4 」の入力線については、記載を省略した。

#### [0127]

駆動回路 5 5 は、走査線制御線 5 3 で走査線駆動回路 5 6 と接続されており、走査線制御線 5 3 を介して初段のシフトレジスタ部 2 5 に制御信号を出力する。

#### [0128]

アクティブエリア 5 7 は、マトリックス状に配置した画素 5 8 を複数有する。詳細には、アクティブエリア 5 7 には、複数のデータ線が列方向に延在され、複数の走査線が行方向に延在されている。そして、アクティブエリア 5 7 には、データ線と走査線との交差に対応して、それぞれ画素 5 8 が形成されている。

## [0129]

ここで、画素 5 8 は、アクティブ素子として動作する薄膜トランジスタ 5 9 と、画素電極 6 0 とを有する。画像表示装置 5 0 は、アレイ基板に設けられた画素電極 6 0 とカラーフィルタ基板に設けられた共通電極(図示せず)との間に印加された電圧によって液晶分子を制御して画像表示する。ここでは、パネル 5 2 は、アレイ基板に画素電極 6 0 が設けられ、カラーフィルタ基板に共通電極が設けられた縦電界方式で説明しているが、これに限らず、例えば、アレイ基板の画素 5 8 内に画素電極 6 0 および共通電極が設けられた横電界方式であってもよい。

#### [0130]

走査線駆動回路56は、第1形態に係わるシフトレジスタ部25と同様のシフトレジスタ部25~25bたのUT波形制御部26~26bを接続した回路により構成される。ここで、走査線駆動回路56は、上述したシフトレジスタ部25の動作によりOUT波形制御部26が出力する「OUT」よおび「OUT」をアクティブエリア57上に延在する走査線に順次入力する。

## [0131]

また、シフトレジスタ部 2 5 が有する「〇UT」」の電位は、シフトレジスタ部 2 5 a に「in」として入力されているので、走査線駆動回路 5 6 は、シフトレジスタ回路 2 5 a の動作により〇UT波形制御部 2 6 a が出力する「〇UT<sub>3</sub>」および「〇UT<sub>4</sub>」をアクティブエリア 5 7 上に延在する走査線に順次入力する。このように、多段に設置されたシフトレジスタ部 2 5 ~ 2 5 b が信号を順次シフトさせ、各〇UT波形制御部 2 6 ~ 2 6 b が 2 つの信号を順次出力する。このため、走査線駆動回路 5 6 は、駆動回路 5 5 から走査線制御線 5 3 を介して、制御信号が入力された場合には、アクティブエリア 5 7 上の各走査線に対して上方向から順に電圧を印加する。

## [0132]

例えば、走査線駆動回路 5 6 は、制御信号を受信すると、シフトレジスタ部 2 5 、および O U T 波形制御部 2 6 の動作により、「O U T 」」を 1 段目の走査線に出力し、次に「O U T 2 」を 2 段目の走査線に出力する。次に、走査線駆動回路 5 6 は、シフトレジスタ部 2 5 a および O U T 波形制御部 2 6 a の動作により、「O U T 3 」を 3 段目の走査線に出力し、次に「O U T 4 」を 4 段目の走査線に出力する。この結果、走査線駆動回路 5 6 は、アクティブエリア 5 7 上の各走査線に対して、順番に電圧を印加する。

## [0133]

ここで、従来のシフトレジスタ回路を用いて、走査線駆動回路 5 6 を構成する場合には、アクティブエリア 5 7 上に延設された走査線と同数のシフトレジスタ回路を多段に接続

し、各シフトレジスタ回路から各走査線上に信号を出力する。しかしながら、シフトレジスタ部 2 5 と O U T 波形制御部 2 6 からなるシフトレジスタ回路 2 0 を用いて、走査線駆動回路 5 6 を構成した場合には、1 つのシフトレジスタ回路 2 0 から 2 つの走査線に対して信号を出力することができるので、走査線駆動回路 5 6 の回路規模を減少させ、画像表示装置 5 0 の狭額縁化を実現することができる。

## [0134]

また、シフトレジスタ回路 2 0 は、ブートストラップ効果により、出力する信号の電位を下げることなく出力することができるので、走査線駆動回路 5 6 が各走査線に印加する電圧の低下を防ぐことができる。この結果、画像表示装置 5 0 は、アクティブエリア 5 7 の大型化や画素 5 8 の細密化により走査線の数が増加した場合にも、各画素 5 8 に印加する電圧の低下を防ぐことができるので、正常に動作することができる。

#### [ 0 1 3 5 ]

薄膜トランジスタ59は、画素58が形成された位置に応じたデータ線とソースとが接続され、画素58が形成された位置に応じた走査線とゲートとが接続されている。そして、走査線駆動回路56から対応する走査線に電圧が印加されるとともに、駆動回路55から対応するデータ線に電圧が印加された場合に、データ線に印加された電圧が薄膜トランジスタ59を介して画素電極60に印加される。

## [0136]

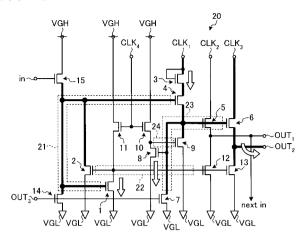

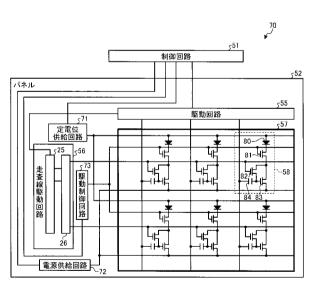

なお、図12では、液晶パネルを用いた画像表示装置にシフトレジスタ回路20を適用する例について説明した。しかしながら、実施の形態はこれに限定されるものではない。例えば、有機ELパネルを用いた画像表示装置にシフトレジスタ回路20を適用してもよい。例えば、図13は、シフトレジスタ回路20の適用例を説明する第2の図である。

#### [ 0 1 3 7 ]

#### (有機 E L への適用)

図13に示す例では、シフトレジスタ部25、およびOUT波形制御部26を有する走査線駆動回路56を有し、有機ELパネルを用いた画像表示装置70について記載した。また、図13に示す例では、理解を容易にするため、シフトレジスタ部25、およびOUT波形制御部26からなるシフトレジスタ回路20を有する走査線駆動回路56を記載したが、走査線駆動回路56は、シフトレジスタ回路20と同様の回路を複数有するものとする。具体的には、走査線駆動回路56は、アクティブエリア57上に延設する走査線の数の半分の数だけシフトレジスタ回路20と同様の回路を多段に接続することで構成すればよい。なお、上述の液晶パネルを用いた画像表示装置50と同様に、シフトレジスタ回路20は、パネル52のアレイ基板上の周辺部に一体的に形成されている。

## [0138]

図13に示す例では、画素58は、アノードが定電位供給回路71と電気的に接続された発光素子80と、発光素子80のカソードに一方の電極が接続されたトランジスタ81とを有する。また、画素58は、n型の薄膜トランジスタによって形成され、ドレインがトランジスタ82のドレインに接続され、ソースが電源供給回路72と電気的に接続されたドライバ素子83とを有する。また、画素58は、ドライバ素子83を形成する薄膜トランジスタのゲート・ドレイン間の導通状態を制御するトランジスタ82と静電容量84とを有する。

#### [0139]

また、図13に示す例では、各画素58内に備わる発光素子80のアノードに対して一定のオン電位を供給する定電位供給回路71と、制御線を介して、画素58内に備わるトランジスタ81の駆動を制御する駆動制御回路73と、ドライバ素子83のソースにオン電位または0電位を供給する電源供給回路72とを有する。

#### [0140]

発光素子80は、電流注入によって発光する機構を有し、例えば有機EL素子によって 形成される。有機EL素子は、Al、Cu、ITO(Indium Tin Oxide)等によって形成 されたアノード層およびカソード層と、アノード層とカソード層との間にフタルシアニン 10

20

30

40

、トリスアルミニウム錯体、ベンゾキノリノラト、ベリリウム錯体等の有機系の材料によって形成された発光層とを少なくとも備えた構造を有し、発光層に注入された正孔と電子とが発光再結合することによって光を生じる機能を有する。

#### [ 0 1 4 1 ]

トランジスタ81は、発光素子80とドライバ素子83との間の導通を制御する機能を有し、本実施形態1では、n型の薄膜トランジスタによって形成される。すなわち、薄膜トランジスタのドレインとソースとがそれぞれ発光素子80、ドライバ素子83に接続される一方で、ゲートが駆動制御回路73と電気的に接続された構成を有し、駆動制御回路73から供給される電位に基づいて、発光素子80とドライバ素子83との間の導通状態を制御している。

[0142]

ドライバ素子83は、発光素子80に流れる電流を制御するための機能を有する。具体的には、ドライバ素子83は、閾値以上の電位差に応じて発光素子80に流れる電流を制御する機能を有する。本実施形態1では、ドライバ素子83は、n型の薄膜トランジスタによって形成され、ゲートとソースとの間に印加される電位差に応じて発光素子80の発光輝度を制御している。

[0143]

このような画素 5 8 においては、駆動回路 5 5 が信号線に印加した電圧により静電容量 8 4 に電荷が蓄積される。そして、駆動制御回路 7 3 がトランジスタ 8 1 のゲートに電圧を印加している間、静電容量 8 4 に蓄積した電荷に応じた電流が発光素子 8 0 に流れ、発光素子 8 0 が発光する。

[ 0 1 4 4 ]

このように、各画素 5 8 が発光素子 8 0 を有する場合であっても、走査線駆動回路 5 6 は、シフトレジスタ部 2 5 、および O U T 波形制御部 2 6 からなるシフトレジスタ回路 2 0 が、 2 つの走査線に各画素の出力信号を出力する。このため、画像表示装置 7 0 は、画素 5 8 が有機 E L パネルを有する場合にも、走査線駆動回路 5 6 の回路規模を減少させ、狭額緑化を図ることができる。また、シフトレジスタ回路 2 0 は、走査線上に出力する信号の電位の低下を防ぐので、アクティブエリア 5 7 上の画素数に係わらず、画像表示装置 7 0 を正常に動作させることができる。

## 【符号の説明】

[ 0 1 4 5 ]

1~15 トランジスタ

20 シフトレジスタ回路

21~24 *J*-F

25、25a、25b シフトレジスタ部

26、26a、26b OUT波形制御部

10

30

【図1】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

## 【図12】

## 【図13】

# 【図14】

フロントページの続き

(51) Int.CI.

F I

テーマコード(参考)

G 0 9 G 3/30 J