## (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第6580020号 (P6580020)

(45) 発行日 令和1年9月25日 (2019.9.25)

(24) 登録日 令和1年9月6日(2019.9.6)

| (51) Int.Cl.                                            |      |                                                                                                         | F I  |                                  |                                                                                                                                                                |          |            |

|---------------------------------------------------------|------|---------------------------------------------------------------------------------------------------------|------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|

| нозн                                                    | 9/25 | (2006.01)                                                                                               | нозн | 9/25                             | Α                                                                                                                                                              |          |            |

| нозн                                                    | 9/64 | (2006.01)                                                                                               | нозн | 9/64                             | Z                                                                                                                                                              |          |            |

| нозн                                                    | 9/17 | (2006.01)                                                                                               | нозн | 9/17                             | $\mathbf{F}$                                                                                                                                                   |          |            |

| нозн                                                    | 9/02 | (2006.01)                                                                                               | нозн | 9/02                             | G                                                                                                                                                              |          |            |

| нозн                                                    | 9/54 | (2006.01)                                                                                               | нозн | 9/54                             | Z                                                                                                                                                              |          |            |

|                                                         |      |                                                                                                         |      |                                  | 請求項の数 10                                                                                                                                                       | (全 14 頁) | 最終頁に続く     |

| (21) 出願番号<br>(22) 出願日<br>(65) 公開番号<br>(43) 公開日<br>審査請求日 |      | 平成28年12月5日 (2016.12.5)<br>特開2018-93389 (P2018-93389A)<br>平成30年6月14日 (2018.6.14)<br>平成30年3月5日 (2018.3.5) |      | (73) 特許権(74) 代理人(72) 発明者(72) 発明者 | 第 000204284<br>太陽誘電株式会社<br>東京都中央区京橋二丁目7番19号<br>100087480<br>弁理士 片山 修平<br>中澤 秀太郎<br>東京都台東区上野6丁目16番20号 太<br>陽誘電株式会社内<br>松田 隆志<br>東京都台東区上野6丁目16番20号 太<br>陽誘電株式会社内 |          |            |

|                                                         |      |                                                                                                         |      | 審査官                              | 橋本 和志                                                                                                                                                          |          |            |

|                                                         |      |                                                                                                         |      |                                  |                                                                                                                                                                | 昻        | と<br>経頁に続く |

(54) 【発明の名称】電子部品

## (57)【特許請求の範囲】

# 【請求項1】

第1基板と、

下面に機能素子が設けられ、前記機能素子が前記第1基板の上面と空隙を挟み対向するように、前記第1基板上に実装された第2基板と、

前記第1基板の上面に設けられ、平面視において前記機能素子の少なくとも一部と重なり、前記機能素子と前記空隙を介し対向し、膜厚が前記機能素子の下面と前記第1基板の上面との距離の半分以上であり、空気の熱伝導率の5倍以上の熱伝導率を有する有機絶縁体である絶縁膜と、

を具備する電子部品。

# 【請求項2】

第1基板と、

下面に機能素子が設けられ、前記機能素子が前記第1基板の上面と空隙を挟み対向するように、前記第1基板上に実装された第2基板と、

前記第1基板の上面に設けられ、平面視において前記機能素子の少なくとも一部と重なり、前記機能素子と前記空隙を介し対向し、膜厚が前記機能素子の下面と前記第1基板の上面との距離の半分以上である絶縁膜と、

## を具備し、

前記第2基板の下面に複数の機能素子が設けられ、

前記絶縁膜は、平面視において前記複数の機能素子の一部と重なり前記複数の機能素子の

他と重ならない電子部品。

## 【請求項3】

前記機能素子は弾性波素子である請求項1または2記載の電子部品。

#### 【請求項4】

第1基板と、

下面に弾性波素子である機能素子が設けられ、前記機能素子が前記第1基板の上面と空 隙を挟み対向するように、前記第1基板上に実装された第2基板と、

前記第1基板の上面に設けられ、平面視において前記機能素子の少なくとも一部と重な り、前記機能素子と前記空隙を介し対向し、膜厚が前記機能素子の下面と前記第1基板の 上面との距離の半分以上である絶縁膜と、

## を具備し、

入力端子と出力端子との間に直列に接続され前記弾性波素子である1または複数の直列 共振器と、

前記入力端子と前記出力端子との間に並列に接続され前記弾性波素子である1または複 数の並列共振器と、

## を具備し、

平面視において前記絶縁膜は前記1または複数の直列共振器の少なくとも1つと重なり 、前記1または複数の直列共振器および前記1または複数の並列共振器のうち他の共振器 の少なくとも一部と重ならない電子部品。

## 【請求項5】

平面視において前記絶縁膜は前記1または複数の直列共振器のうち両側に直列共振器が 接続された直列共振器と重なり、前記1または複数の直列共振器および前記1または複数 の並列共振器のうち他の共振器の少なくとも一部と重ならない請求項4記載の電子部品。

#### 【請求項6】

前記第1基板の上面に高周波信号が伝搬する金属層が設けられ、

平面視において前記絶縁膜は前記金属層とは重ならない請求項1から5のいずれか一項 記載の電子部品。

## 【請求項7】

前記第1基板の上面に金属層が設けられ、

平面視において前記絶縁膜は全ての前記金属層とは重ならない請求項1から5のいずれ か一項記載の電子部品。

# 【請求項8】

前記絶縁膜は前記第1基板の上面に接触している請求項1から7のいずれか一項記載の 電子部品。

## 【請求項9】

前記弾性波素子を含むフィルタを具備する請求項3から5のいずれか一項記載の電子部 品。

#### 【請求項10】

前記フィルタを含むマルチプレクサを具備する請求項9記載の電子部品。

## 【発明の詳細な説明】

#### 【技術分野】

## [00001]

本発明は、電子部品に関し、例えば基板上に機能素子を有する基板が実装された電子部 品に関する。

## 【背景技術】

#### [0002]

圧電薄膜共振器(FBAR: Film Bulk Acoustic Resonator)または弾性表面波(SA W: Surface Acoustic Wave) 共振器等の弾性波素子は、携帯電話に代表される45MH zから4GHzの周波数帯の無線信号を処理する各種回路におけるバンドパスフィルタ等 に用いられる。

10

20

30

40

#### [00003]

このような弾性波素子等の機能素子の実装方法として、基板上に下面に機能素子を有するチップをフリップチップ実装することが知られている(例えば特許文献 1 から 4 )。弾性波素子等の機能素子は空隙を挟み基板の上面と対向する。基板の上面に設けられたインダクタと弾性波素子との短絡を抑制するため基板の上面に絶縁膜を設けることが知られている(例えば特許文献 4 )。

#### 【先行技術文献】

#### 【特許文献】

## [0004]

【特許文献 1 】特開 2 0 1 5 - 2 0 4 5 3 1 号公報

【特許文献2】特開2005-223580号公報

【特許文献3】特開2015-103888号公報

【特許文献 4 】特開 2 0 1 6 - 5 8 9 6 4 号公報

## 【発明の概要】

【発明が解決しようとする課題】

#### [0005]

例えば弾性波素子等を有する電子部品は、携帯電話やスマートフォン等の多機能化に伴い、小型化が求められている。一方、電波を送信するためのパワーアンプのハイパワー化に伴い、高耐電力化が求められている。電子部品の小型化かつ高耐電力化のため、機能素子からの放熱性を高めることが考えられる。しかしながら、機能素子が空隙を介し基板の上面に対向していると、機能素子の下面から放熱することができない。

#### [0006]

本発明は、上記課題に鑑みなされたものであり、機能素子からの放熱性を向上させることを目的とする。

# 【課題を解決するための手段】

#### [0007]

本発明は、第1基板と、下面に機能素子が設けられ、前記機能素子が前記第1基板の上面と空隙を挟み対向するように、前記第1基板上に実装された第2基板と、前記第1基板の上面に設けられ、平面視において前記機能素子の少なくとも一部と重なり、前記機能素子と前記空隙を介し対向し、膜厚が前記機能素子の下面と前記第1基板の上面との距離の半分以上であり、空気の熱伝導率の5倍以上の熱伝導率を有する有機絶縁体である絶縁膜と、を具備する電子部品である。

## [0008]

上記構成において、前記第1基板の上面に高周波信号が伝搬する金属層が設けられ、平面視において前記絶縁膜は前記金属層とは重ならない構成とすることができる。

#### [0009]

上記構成において、前記第1基板の上面に金属層が設けられ、平面視において前記絶縁膜は全ての前記金属層とは重ならない構成とすることができる。

## [0010]

本発明は、第1基板と、下面に機能素子が設けられ、前記機能素子が前記第1基板の上面と空隙を挟み対向するように、前記第1基板上に実装された第2基板と、前記第1基板の上面に設けられ、平面視において前記機能素子の少なくとも一部と重なり、前記機能素子と前記空隙を介し対向し、膜厚が前記機能素子の下面と前記第1基板の上面との距離の半分以上である絶縁膜と、を具備し、前記第2基板の下面に複数の機能素子が設けられ、前記絶縁膜は、平面視において前記複数の機能素子の一部と重なり前記複数の機能素子の他と重ならない電子部品である。

#### [0011]

上記構成において、前記絶縁膜は前記第1基板の上面に接触している構成とすることができる。

## [0012]

10

20

30

上記構成において、前記機能素子は弾性波素子である構成とすることができる。

## [0013]

本発明は、第1基板と、下面に弾性波素子である機能素子が設けられ、前記機能素子が 前記第1基板の上面と空隙を挟み対向するように、前記第1基板上に実装された第2基板 と、前記第1基板の上面に設けられ、平面視において前記機能素子の少なくとも一部と重 なり、前記機能素子と前記空隙を介し対向し、膜厚が前記機能素子の下面と前記第1基板 の上面との距離の半分以上である絶縁膜と、を具備し、入力端子と出力端子との間に直列 に接続され前記弾性波素子である1または複数の直列共振器と、前記入力端子と前記出力 端子との間に並列に接続され前記弾性波素子である1または複数の並列共振器と、を具備 し、平面視において前記絶縁膜は前記1または複数の直列共振器の少なくとも1つと重な り、前記1または複数の直列共振器のよび前記1または複数の並列共振器のうち他の共振 器の少なくとも一部と重ならない電子部品である。

[0014]

上記構成において、平面視において前記絶縁膜は前記1または複数の直列共振器のうち両側に直列共振器が接続された直列共振器と重なり、前記1または複数の直列共振器および前記1または複数の並列共振器のうち他の共振器の少なくとも一部と重ならない構成とすることができる。

[0015]

上記構成において、前記弾性波素子を含むフィルタを具備する構成とすることができる -

[0016]

上記構成において、前記フィルタを含むマルチプレクサを具備する構成とすることができる。

【発明の効果】

[0017]

本発明によれば、機能素子からの放熱性を向上させることができる。

【図面の簡単な説明】

[0018]

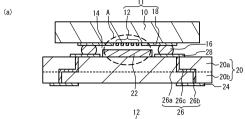

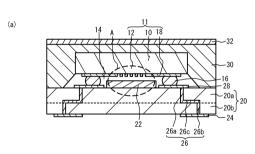

【図1】図1(a)は、実施例1に係る電子部品の断面図、図1(b)は、図1(a)の領域Aの拡大図、図1(c)は、実施例1の変形例1に係る電子部品の断面図、図1(d)は、図1(c)の領域Aの拡大図である。

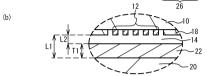

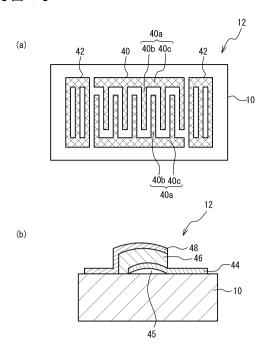

【図2】図2(a)は、実施例1における機能素子を示す平面図、図2(b)は、実施例1の変形例1における機能素子を示す断面図である。

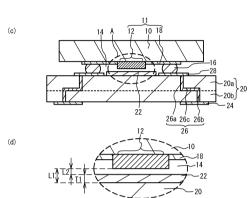

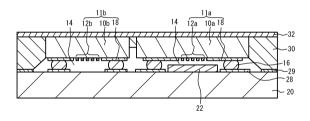

【図3】図3(a)および図3(b)は、実施例1の変形例2および3に係る電子部品の断面図である。

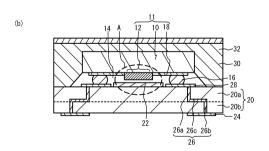

【図4】図4は、実施例2に係るデュプレクサの断面図である。

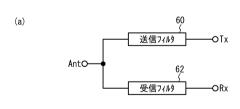

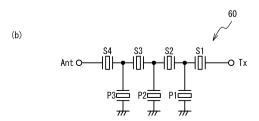

【図5】図5(a)は、実施例2に係るデュプレクサの回路図、図5(b)は、送信フィルタの回路図である。

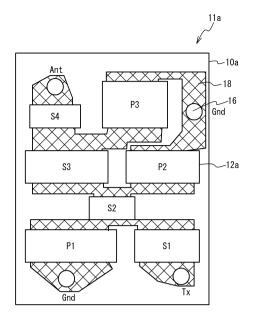

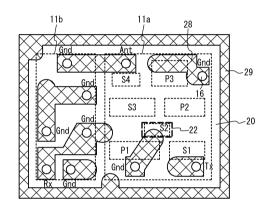

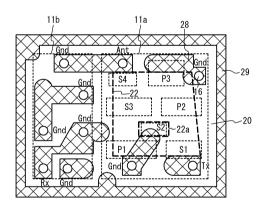

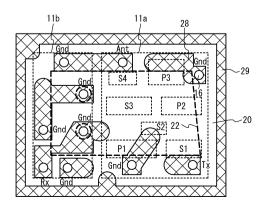

【図6】図6は、実施例2におけるデバイスチップの平面図である。

【図7】図7は、実施例2における基板の平面図である。

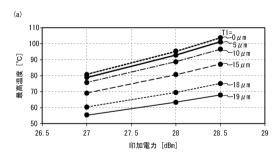

【図8】図8(a)は、印加電力に対する最高温度を示す図、図8(b)は、印加電力に対する温度降下量を示す図である。

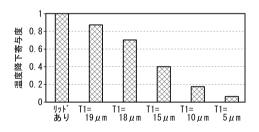

【図9】図9は、温度降下寄与度を示す図である。

【図10】図10は、送信端子から共通端子への通過特性を示す図である。

【図11】図11は、実施例2の変形例1における基板の平面図である。

【図12】図12は、実施例2の変形例2における基板の平面図である。

【図13】図13は、実施例2の変形例3における基板の平面図である。

【図14】図14は、実施例2の変形例4における基板の平面図である。

【図15】図15は、実施例2の変形例5における基板の平面図である。

【図16】図16は、実施例2の変形例6における基板の平面図である。

10

20

30

40

#### 【発明を実施するための形態】

## [0019]

以下図面を参照し実施例について説明する。

#### 【実施例1】

#### [0020]

図1(a)は、実施例1に係る電子部品の断面図、図1(b)は、図1(a)の領域Aの拡大図、図1(c)は、実施例1の変形例1に係る電子部品の断面図、図1(d)は、図1(c)の領域Aの拡大図である。

#### [0021]

図 1 (a) および図 1 (c) に示すように、基板 2 0 の上面に、基板 1 0 が実装されている。基板 2 0 は、絶縁基板であり、例えばHTCC (High Temperature Co-fired Ceramic) またはLTCC (Low Temperature Co-fired Ceramic) 等のセラミックス基板または樹脂基板である。基板 2 0 は積層された複数の絶縁層 2 0 a および 2 0 b を有する。絶縁層 2 0 a および 2 0 b の上面にそれぞれ金属層 2 8 および 2 6 c が形成されている。絶縁層 2 0 b の下面に金属層 2 4 が形成されている。絶縁層 2 0 a および 2 0 b を貫通するビア配線 2 6 a および 2 6 b が形成されている。ビア配線 2 6 a は、金属層 2 8 と 2 6 c とを電気的に接続し、ビア配線 2 6 b は、金属層 2 6 c と 2 4 とを電気的に接続する。

## [0022]

基板 2 0 の上面に設けられた金属層 2 8 は例えばバンプ 1 6 が接合するパッドおよび配線である。金属層 2 4 は、例えば外部と電気的に接続するための外部端子であり、例えばフットパッドである。ビア配線 2 6 a、 2 6 b および金属層 2 6 c は、金属層 2 4 と 2 8 とを接続する内部配線 2 6 を形成する。金属層 2 4、 2 8 および内部配線 2 6 は、銅層、金層またはアルミニウム層等の金属層である。基板 2 0 の上面に絶縁膜 2 2 が設けられている。絶縁膜 2 2 は例えば樹脂等の有機絶縁体または酸化シリコン等の無機絶縁体である。絶縁膜 2 2 が樹脂膜の場合、絶縁膜 2 2 は例えば基板 2 0 上に印刷法により形成され、加熱処理することにより乾燥される。

#### [0023]

デバイスチップ11は、基板10、機能素子12および金属層18を有する。機能素子12および金属層18は基板10の下面に設けられている。機能素子12は図1(a)および図1(b)では弾性表面波素子であり、図1(c)および図1(d)では圧電薄膜共振器である。金属層18は、バンプ16が接合するパッドおよび配線である。

# [0024]

デバイスチップ11はバンプ16を介し基板20上にフリップチップ(フェースダウン)実装されている。機能素子12は空隙14を挟み基板20の上面および絶縁膜22の上面に対向している。機能素子12が空隙14に露出されているため、機能素子12の振動等が抑制されない。バンプ16は、例えば銅バンプ、金バンプまたは半田バンプである。

# [0025]

図1(b)および図1(d)に示すように、基板20の上面と機能素子12の下面の距離をL1、絶縁膜22の上面と機能素子12の下面との距離をL2、絶縁膜22の膜厚をT1とする。実施例1およびその変形例1では、L1>T1 L1/2であり、T1 L2である。このように、機能素子12と絶縁膜22との距離L2が小さい。これにより、機能素子12において発生した熱を絶縁膜22を介し放出することができる。

## [0026]

図 2 (a)は、実施例 1 における機能素子を示す平面図、図 2 (b)は、実施例 1 の変形例 1 における機能素子を示す断面図である。図 2 (a)に示すように、基板 1 0 上に I D T (Interdigital Transducer) 4 0 と反射器 4 2 が形成されている。 I D T 4 0 は、互いに対向する 1 対の櫛型電極 4 0 a を有する。櫛型電極 4 0 a は、複数の電極指 4 0 b と複数の電極指 4 0 b を接続するバスバー 4 0 c とを有する。反射器 4 2 は、 I D T 4 0 の両側に設けられている。 I D T 4 0 が基板 1 0 に弾性表面波を励振する。基板 1 0 は、例えばタンタル酸リチウム基板またはニオブ酸リチウム基板等の圧電基板である。 I D T

10

20

30

40

10

20

30

40

50

4 0 および反射器 4 2 は例えばアルミニウム膜または銅膜により形成される。基板 1 0 は、サファイア基板、アルミナ基板、スピネル基板またはシリコン基板等の支持基板の下面に接合されていてもよい。IDT 4 0 および反射器 4 2 を覆う保護膜または温度補償膜が設けられていてもよい。この場合、保護膜または温度補償膜を含め機能素子 1 2 として機能する。

## [0027]

図2(b)に示すように、基板10上に圧電膜46が設けられている。圧電膜46を挟むように下部電極44および上部電極48が設けられている。下部電極44と基板10との間に空隙45が形成されている。下部電極44および上部電極48は圧電膜46内に、厚み縦振動モードの弾性波を励振する。下部電極44および上部電極48は例えばルテニウム膜等の金属膜である。圧電膜46は例えば窒化アルミニウム膜である。基板10は例えばシリコン基板もしくは砒化ガリウム等の半導体基板、またはサファイア基板、アルミナ基板、スピネル基板またはガラス基板等の絶縁基板である。図2(a)および図2(b)のように、機能素子12は弾性波を励振する電極を含む。このため、弾性波を規制しないように、機能素子12は空隙14に覆われている。

#### [0028]

図3(a)および図3(b)は、実施例1の変形例2および3に係る電子部品の断面図である。図3(a)および図3(b)の領域Aの拡大図はそれぞれ図1(b)および図1(d)と同じである。

# [0029]

図3(a)および図3(b)に示すように、平面視において基板10を囲むように封止部30が設けられている。封止部30は基板20の上面に接合されている。封止部30および基板10上にリッド32が設けられている。封止部30は半田等の金属または樹脂等の絶縁体である。リッド32は金属板または絶縁板である。封止部30により、機能素子12が空隙14に気密封止される。その他の構成は実施例1およびその変形例1と同じであり説明を省略する。

## 【実施例2】

#### [0030]

実施例 2 は、デュプレクサの例である。図 4 は、実施例 2 に係るデュプレクサの断面図である。図 4 に示すように、基板 2 0 上にデバイスチップ 1 1 a および 1 1 b がフリップチップ実装されている。デバイスチップ 1 1 a および 1 1 b において、それぞれ基板 1 0 a および 1 0 b の下面に機能素子 1 2 a および 1 2 b が設けられている。基板 2 0 の上面にはデバイスチップ 1 1 a および 1 1 b を囲むように環状金属層 2 9 が設けられている。デバイスチップ 1 1 a および 1 1 b を囲むように封止部 3 0 が設けられている。封止部 3 0 は半田であり、環状金属層 2 9 に接合されている。封止部 3 0、デバイスチップ 1 1 a および 1 1 b の上面にリッド 3 2 が設けられている。機能素子 1 2 a は基板 2 0 の上面に設けられた絶縁膜 2 2 に空隙 1 4 を挟み対向している。その他の構成は実施例 1 の変形例 2 と同じであり説明を省略する。

# [0031]

図5(a)は、実施例2に係るデュプレクサの回路図、図5(b)は、送信フィルタの回路図である。図5(a)に示すように、共通端子Antと送信端子Txとの間に送信フィルタ60が設けられている。共通端子Antと受信端子Rxとの間に受信フィルタ62が設けられている。送信フィルタ60は、送信端子Txから入力した高周波信号のうち送信信号を共通端子Antに通過させ他の周波数の信号を抑圧する。受信フィルタ62は、共通端子Antから入力した高周波信号のうち受信信号を受信端子Rxに通過させ他の周波数の信号を抑圧する。送信フィルタ60は、デバイスチップ11aに形成されており、機能素子12bを含む。受信フィルタ62は、デバイスチップ11bに形成されており、機能素子12bを含む。

## [0032]

図5(b)に示すように、送信フィルタ60は直列共振器51から54および並列共振

10

20

30

40

50

器 P 1 から P 3 を有する。直列共振器 S 1 から S 4 は、送信端子 T x と共通端子 A n t の間に直列に接続されている。並列共振器 P 1 から P 3 は送信端子 T x と共通端子 A n t の間に並列に接続されている。

#### [0033]

図6は、実施例2におけるデバイスチップの平面図である。デバイスチップ11aの下面を上から透視した平面図である。図6に示すように、基板10aの下面に、複数の機能素子12aは図2(a)に示した弾性表面波共振器である。複数の機能素子12aは直列共振器51から54および並列共振器P1からP3を含む。金属層18は配線およびパッドである。配線は複数の機能素子12a間を接続する。パッドは機能素子12aに接続されている。パッドにはバンプ16が設けられている。バンプ16は、共通端子Ant、送信端子Txおよびグランド端子Gndに対応する。

#### [0034]

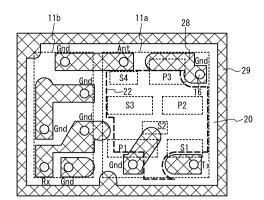

図7は、実施例2における基板の平面図である。デバイスチップ11aおよび11b並びにデバイスチップ11a内の共振器を破線で図示し、絶縁膜22を太破線で図示する。図7に示すように、基板20の上面には金属層28および環状金属層29が設けられている。環状金属層29は、基板20の上面の周縁に設けられている。金属層28は配線およびパッドである。配線はパッド間を接続する。パッドにはバンプ16が設けられている。バンプ16は、共通端子Ant、送信端子Tx、受信端子Rxおよびグランド端子Gndに対応する。絶縁膜22は、平面視においてデバイスチップ11aの共振器と重なり、デバイスチップ11bとは重なっていない。絶縁膜22は、直列共振器S2の全てと重なり、でもよい。と重なっていてもよいし、各々の共振器において共振器の少なくとも一部に重なっていてもよい。

#### [0035]

基板 1 0 a内の温度をシミュレーションした。シミュレーション条件は以下である。基板 1 0 a および 1 0 b を厚さが 2 5 0  $\mu$  mの 4 2 °回転 Y カット X 伝搬 タンタル酸リチウム基板とした。基板 2 0 を厚さが 1 6 6  $\mu$  mの L T C C 基板とした。封止部 3 0 は A g S n 半田とした。基板 2 0 上面と基板 1 0 a の下面の距離を 2 0  $\mu$  m とした。機能素子 1 2 a である弾性表面波共振器の電極指の厚さは 1  $\mu$  m 未満である。基板 1 0 の上面と機能素子 1 2 a の下面との距離は 1 9  $\mu$  m と 2 0  $\mu$  m の間となる。リッド 3 2 を設けず、封止部 3 0 およびデバイスチップ 1 1 a の上面が空気に露出している。絶縁膜 2 2 は、熱伝導率が約 0 . 2 5 W / m・K の樹脂膜とし、膜厚 T 1 を 5 、 1 0 、 1 5 、 1 8 および 1 9  $\mu$  m とした。

## [0036]

送信フィルタ 6 0 および受信フィルタ 6 2 は、E - U T R A (Evolved Universal Terr estrial Radio Access) Operating Bandのバンド 8 (送信帯域: 8 8 0 - 9 1 5 M H z 、受信帯域: 9 2 5 - 9 6 0 M H z )の送信フィルタおよび受信フィルタとした。送信端子 T x にバンド 8 の送信信号を入力した。印加電力を 2 7 d B m 、 2 8 d B m および 2 8 . 5 d B m とした。共通端子 A n t および受信端子 R x は 5 0 に終端した。基板 1 0 a 内の下面の最高温度をシミュレーションした。

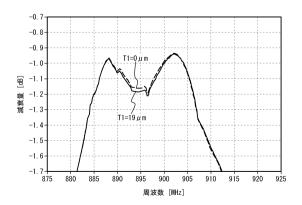

#### [0037]

図 8 ( a )は、印加電力に対する最高温度を示す図、図 8 ( b )は、印加電力に対する温度降下量を示す図である。図 8 ( a )は、絶縁膜 2 2 の膜厚 T 1 を 0  $\mu$  m から 1 9  $\mu$  m まで変えたときの基板 1 0 a の下面での最高温度を示している。図 8 ( b )は、絶縁膜 2 2 の膜厚 T 1 を 5  $\mu$  m から 1 9  $\mu$  m まで変えたときの温度降下量を示している。温度降下量は、膜厚 T 1 が 0  $\mu$  m ときの基板 1 0 a の下面における最高温度から絶縁膜 2 2 を設けたときの基板 1 0 a の下面における最高温度を引いた量である。

## [0038]

図8(a)および図8(b)に示すように、絶縁膜22の膜厚T1が厚くなると最高温

度が下がる。特に、 T 1 が 1 0  $\mu$  mを越えると、最高温度は絶縁膜 2 2 を設けないときに比べ大きく低下する。なお、最高温度となる箇所は図 6 の直列共振器 S 2 に対応する箇所である。

#### [0039]

図9は、温度降下寄与度を示す図である。温度降下寄与度は、印加電力を27dBmとし絶縁膜22を設けずリッド32(膜厚が25μmのコバール)を設けた場合の最高温度の温度降下量を1.0とし、リッド32を設けず絶縁膜22を設けた時の温度降下量を規格化した値である。図9に示すように、絶縁膜22の膜厚を19μmとすると、温度降下寄与度はリッド32を設けた場合の約0.86であり、ほぼ同程度である。

#### [0040]

図 1 0 は、送信端子から共通端子への通過特性を示す図である。絶縁膜 2 2 の膜厚T 1 が 0  $\mu$  m および 1 9  $\mu$  m の通過特性をそれぞれ破線および実線で示す。図 1 0 に示すように、絶縁膜 2 2 を設けることによる 8 9 4 . 5 M H z における挿入損失の増加は 0 . 0 2 3 d B である。このように、絶縁膜 2 2 を設けても挿入損失はあまり大きくならない。

#### [0041]

実施例1および2によれば、下面に機能素子12または12 aが設けられた基板10または10 a (第2基板)を、機能素子12または12 aが基板20 (第1基板)の上面と空隙14を挟み対向するように、実装する。基板20の上面に、平面視において機能素子12または12 a と空隙14を介し対向する絶縁膜を設ける。

#### [0042]

機能素子12または12aが空隙14を介し基板20と対向する場合、機能素子12または12aに近づければ、機能素子12または12aにおいて発生した熱が放射または対流により基板20に伝わり、機能素子12または12aの温度を低下できる。しかし、基板20と基板10との間に空隙14を設けるため、バンプ16を設ける。このため、機能素子12または12aの下面と基板20の上面との距離L1を小さくすることができない。よって、機能素子12または12aの下面からの放熱量を大きくできない。そこで、基板20の上面に絶縁膜22を設ける。これにより、機能素子12または12aの下面と絶縁膜22の上面との距離L2を小さくできる。よって、機能素子12または12aにおいて発生した熱を絶縁膜22を介し放出できる。なお、絶縁膜22の代わりに金属膜を用いると、機能素子12または12aの近くに金属膜の上面が設けられる。このため機能素子12または12aの特性が劣化する。

## [0043]

機能素子12または12aから効率的に放熱するため、絶縁膜22の膜厚T1は、距離L1の半分以上であることが好ましい。これにより、図8(a)から図9のように、基板10a内の最高温度を低くできる。T1はL1の75%以上が好ましく、90%以上がより好ましい。また、機能素子12または12aの下面と絶縁膜22の上面との距離L2は、T1以下が好ましく、T1/4以下がさらに好ましい。

#### [0044]

絶縁膜22の熱伝導率は、空気の熱伝導率である0.025W/m・Kより大きければよいが、より放熱効果を高めるため、空気の熱伝導率の5倍以上が好ましく、10倍以上がより好ましい。熱伝導率の大きな絶縁膜22として、エポキシ樹脂、ポリイミド樹脂、シリコーン、ソルダーレジスト、窒化ホウ素、窒化アルミニウム、酸化亜鉛または酸化シリコン等を用いることができる。放熱性向上のため絶縁膜22は基板20の上面に直接接触していることが好ましい。

#### [0045]

放熱性のためには、絶縁膜22はバンプ16を除く基板20の上面の全面に設けられていることが好ましい。しかし、機能素子12または12aおよび/または高周波信号が伝搬する配線近くに絶縁膜22が設けられると、特性が劣化する可能性がある。そこで、絶

10

20

30

40

縁膜22は、放熱性に寄与し特性が劣化しない程度に設けることが好ましい。

## [0046]

発熱するデバイスチップ11aは送信フィルタ60が設けられているチップである。そこで、図7のように、絶縁膜22は送信フィルタ60を形成する機能素子12aの全てと重なるように設け、受信フィルタ62が設けられたデバイスチップ11bには重ならないようにする。また、絶縁膜22は、高周波信号が伝搬する送信端子Txおよび共通端子Antに接続された金属層28上には設けない。これにより、特性の劣化を抑制しかつ放熱性を高めることができる。

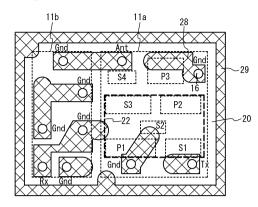

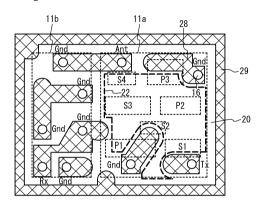

## [0047]

図11は、実施例2の変形例1における基板の平面図である。図11に示すように、絶縁膜22は、バンプ16から所定距離内には設けない。これにより、バンプ16の合わせマージンを確保できる。その他の構成は実施例2と同じであり説明を省略する。

#### [0048]

図12は、実施例2の変形例2における基板の平面図である。図12に示すように、絶縁膜22は、金属層28の全てと重なっていない。絶縁膜22が金属層28と重なる領域では、絶縁膜22の上面が機能素子12aおよび/または金属層18と接触する可能性がある。これにより、機能素子12aの特性が劣化する可能性がある。そこで、実施例2の変形例2のように、絶縁膜22は全ての金属層28と重ならない。これにより、特性の劣化を抑制できる。その他の構成は実施例2と同じであり説明を省略する。

## [0049]

図13は、実施例2の変形例3における基板の平面図である。最高温度となる共振器は直列共振器52である。そこで、図13に示すように、絶縁膜22を、平面視において直列共振器52に隣接する直列共振器51から53および並列共振器P1およびP2に重ね、直列共振器52に隣接しない直列共振器54および並列共振器P3には重ねない。これにより、直列共振器52から効率的に放熱し、かつ絶縁膜22と重なることによる特性の劣化を抑制できる。絶縁膜22は、直列共振器51から53および並列共振器P1およびP2の各々の共振器において共振器全てに重なっていてもよいが、各々の共振器において共振器の一部のみに重なっていてもよい。その他の構成は実施例2と同じであり説明を省略する。

## [0050]

図14は、実施例2の変形例4における基板の平面図である。図14に示すように、絶縁膜22を、平面視において直列共振器S2に重なり直列共振器S1、S3、S4および並列共振器P1からP3には重ならない。これにより、直列共振器S2から効率的に放熱し、かつ絶縁膜22と重なることによる特性の劣化を抑制できる。絶縁膜22は、直列共振器S2の全てに重なっていてもよいが、直列共振器S2の一部のみに重なっていてもよい。その他の構成は実施例2と同じであり説明を省略する。

# [0051]

実施例2の変形例3および4のように、絶縁膜22を平面視において複数の機能素子12aの一部と重なり複数の機能素子12aの他と重ならないように設ける。これにより、放熱性を高めかつ特性の劣化を抑制できる。

# [0052]

ラダー型フィルタでは、直列共振器が並列共振器より発熱しやすい。そこで、絶縁膜22を平面視において1または複数の直列共振器 S1からS4の少なくとも1つと重なり、1または複数の直列共振器 S1からS4および1または複数の並列共振器 P1からP3のうち他の共振器の少なくとも一部と重ならないようにする。これにより、放熱性を高めかつ特性の劣化を抑制できる。

#### [0053]

また、直列共振器 S 1 から S 4 のうち両側に直列共振器が接続された共振器は発熱しやすい。そこで、絶縁膜 2 2 を 1 または複数の直列共振器 S 1 から S 4 のうち両側に直列共振器 S 1 および S 3 が接続された直列共振器 S 2 と重なり、 1 または複数の直列共振器 S

10

20

30

40

1 からSS4および1または複数の並列共振器P1からP3のうち他の共振器の少なくと も一部と重ならないようにする。これにより、放熱性を高めかつ特性の劣化を抑制できる

## [0054]

図15は、実施例2の変形例5における基板の平面図である。図15に示すように、平面視において直列共振器S2に重なる絶縁膜22aを他の直列共振器S1、S3、S4および並列共振器P1からP3に重なる絶縁膜22より厚くする。これにより、直列共振器S2から効率的に放熱し、かつ特性の劣化を抑制できる。その他の構成は実施例2と同じであり説明を省略する。

# [0055]

図16は、実施例2の変形例6における基板の平面図である。図16に示すように、絶縁膜22は、デバイスチップ11bの機能素子12bに重なるように設ける。基板20上に複数の基板10aおよび10bが実装され、絶縁膜22は、複数の基板10aおよび10bに設けられた機能素子12aおよび12bの全てと重なってもよい。その他の構成は実施例2と同じであり説明を省略する。

#### [0056]

実施例 2 およびその変形例として、機能素子 1 2 a および 1 2 b が弾性表面波共振器の例を説明したが、機能素子 1 2 a および 1 2 b は圧電薄膜共振器でもよい。ラダー型フィルタの直列共振器および並列共振器の数は任意に設定できる。フィルタとしてラダー型フィルタを例に説明したが、フィルタは多重モードフィルタでもよい。マルチプレクサとしてデュプレクサの例を説明したが、トリプレクサまたはクワッドプレクサでもよい。

#### [0057]

実施例1、2およびその変形例において、機能素子12は、アンプおよび/またはスイッチのような能動素子でもよい。また、機能素子12は、インダクタおよび/またはキャパシタ等の受動素子でもよい。

#### [0058]

以上、本発明の実施例について詳述したが、本発明はかかる特定の実施例に限定される ものではなく、特許請求の範囲に記載された本発明の要旨の範囲内において、種々の変形 ・変更が可能である。

# 【符号の説明】

[0059]

- 10、10a、10b、20 基板

- 11,11a、11b デバイスチップ

- 12、12a、12b 機能素子

- 1 4 空隙

- 16 バンプ

- 18、28 金属層

- 2 2 絶縁膜

- 60 送信フィルタ

- 62 受信フィルタ

20

10

30

# 【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

(b)

0 26. 5

【図9】

40 35 25 19 μm 12 20 18 μm 15 15 μm 10 10 μm

27.5 28 印加電力 [dBm] 28. 5

【図10】

【図11】

【図13】

【図12】

【図14】

【図15】

【図16】

# フロントページの続き

(51) Int.CI. F I

**H 0 1 L 23/36 (2006.01)** H 0 1 L 23/36 C

(56)参考文献 特開2008-016909(JP,A)

特開2016-058964(JP,A)

特開2010-074418(JP,A)

特開2007-028172(JP,A)

(58)調査した分野(Int.CI., DB名)

H 0 3 H 9 / 2 5

H01L 23/36

H 0 3 H 9 / 0 2

H 0 3 H 9 / 1 7 H 0 3 H 9 / 5 4

H 0 3 H 9 / 6 4