(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

FI

(11) 特許番号

特許第5298393号 (P5298393)

(45) 発行日 平成25年9月25日 (2013.9.25)

(24) 登録日 平成25年6月28日 (2013.6.28)

(51) Int . Cl .

GO6F 3/06 (2006.01)

GO6F 3/06 3O5C

請求項の数 26 (全 19 頁)

(21) 出願番号 特願2010-534958 (P2010-534958) (86) (22) 出願日 平成20年11月20日 (2008.11.20)

(65) 公表番号 特表2011-504269 (P2011-504269A) (43) 公表日 平成23年2月3日 (2011.2.3)

(86) 国際出願番号 PCT/US2008/012944 (87) 国際公開番号 W02009/070235

(87) 国際公開日 平成21年6月4日 (2009.6.4) 審査請求日 平成23年11月17日 (2011.11.17)

(31) 優先権主張番号 60/989,670

(32) 優先日 平成19年11月21日 (2007.11.21)

(33) 優先権主張国 米国(US)

|(73)特許権者 502188642

マーベル ワールド トレード リミテッ

ĸ

バルバドス国 ビービー14027, セン トマイケル、ブリトンズ ヒル、ガンサイ

トロード、エル ホライズン

|(74) 代理人 | 110000877

龍華国際特許業務法人

|(72)発明者||プルーチ、アービンド

アメリカ合衆国、95054 カリフォル ニア州、サンタ クララ、マーベル レー ン 5488 マーベル セミコンダクタ

ー インコーポレイテッド内

審査官 坂東 博司

最終頁に続く

(54) 【発明の名称】並列リードソロモンRAID (RS-RAID) アーキテクチャ、デバイス、および方法

# (57)【特許請求の範囲】

# 【請求項1】

分散データ記憶デバイスであって、

複数の並列データ記憶クラスタであって、

複数のデータシンボルを記憶する複数のデータ記憶デバイス、および、

前記複数のデータ記憶デバイスのそれぞれに結合し、前記複数のデータシンボルからローカルな中間チェックサムを計算し、前記ローカルな中間チェックサムを含む複数の中間チェックサムに基づいて前記複数のデータシンボルのチェックサムを計算するよう構成されたRAIDコントローラを含む、複数の並列データ記憶クラスタと、

前記複数の並列データ記憶クラスタのそれぞれに結合し、前記複数の中間チェックサムを前記複数の並列データ記憶クラスタに配信する通信ファブリックとを備える分散データ記憶デバイス。

【請求項2】

前記RAIDコントローラは、前記複数のデータシンボルの重み付き和に基づいて前記ローカルな中間チェックサムを計算する、請求項1に記載の分散データ記憶デバイス。

### 【請求項3】

前記複数の並列データ記憶クラスタの複数のRAIDコントローラの少なくとも1つは、他の並列データ記憶クラスタから前記中間チェックサムを受信し、前記複数の並列なデータ記憶クラスタの複数のデータ記憶デバイスのうちの1つに記憶するためのチェックサムを、前記受信した中間チェックサムと、前記ローカルな中間チェックサムとに基づいて

# 生成する、請求項1又は2に記載の分散データ記憶デバイス。

#### 【請求項4】

前記RAIDコントローラは、前記チェックサムをデータ記憶デバイスに記憶するようさらに構成される請求項1から3のいずれか1項に記載の分散データ記憶デバイス。

# 【請求項5】

前記通信ファブリックは、前記複数のデータシンボルを含む複数の情報シンボルを前記 複数の並列データ記憶クラスタに配信するようさらに構成される請求項1<u>から4のいずれ</u> か1項に記載の分散データ記憶デバイス。

### 【請求項6】

前記RAIDコントローラは、前記複数の情報シンボルのサブセットから前記複数のデータシンボルを選択するRAIDコントロールユニットをさらに備える請求項<u>5</u>に記載の分散データ記憶デバイス。

### 【請求項7】

前記RAIDコントロールユニットは、前記複数のデータ記憶デバイスから作動可能なデータ記憶デバイスのリストを確定する記憶デバイス故障センスユニットをさらに備える請求項6に記載の分散データ記憶デバイス。

# 【請求項8】

前記RAIDコントロールユニットは、作動可能なデータ記憶デバイスの前記リストに基づいてデータ回復行列を計算するようさらに構成される請求項<u>7</u>に記載の分散データ記憶デバイス。

# 【請求項9】

前記通信ファブリックは、作動可能なデータ記憶デバイスの前記リストが変化すると、前記データ回復行列を前記複数の並列データ記憶クラスタに配信するようさらに構成される請求項8に記載の分散データ記憶デバイス。

#### 【請求項10】

前記RAIDコントローラは、作動可能なデータ記憶デバイスのリストに基づいて前記中間チェックサムを計算するよう構成された中間和デバイスをさらに備える請求項<u>6</u>に記載の分散データ記憶デバイス。

# 【請求項11】

前記中間和デバイスは、データシンボルが変化すると、前記ローカルな中間チェクサムを更新するよう構成された再計算器をさらに備える請求項<u>10</u>に記載の分散データ記憶デバイス。

#### 【請求項12】

前記RAIDコントロールユニットは、前記データ回復行列を計算するために、添加された単位行列とファンデルモンデ行列の逆行列を求めるようさらに構成される請求項<u>8</u>に記載の分散データ記憶デバイス。

# 【請求項13】

中間和デバイスは、前記データ回復行列に基づく中間データシンボル、ならびに、前記記憶デバイスから読出されるリードデータシンボルおよびリードチェックサムシンボルの少なくとも一方のベクトルを計算するようさらに構成される請求項<u>12</u>に記載の分散データ記憶デバイス。

#### 【請求項14】

前記RAIDコントロールユニットは、前記添加された単位行列とファンデルモンデ行列の行の集合ならびに作動可能なデータ記憶デバイスの前記リストに基づくベクトルを選択し、前記データ回復行列を形成するために前記行の集合の逆行列を求めるようさらに構成される請求項12に記載の分散データ記憶デバイス。

### 【請求項15】

前記RAIDコントローラは、中間和デバイスに中間データシンボルを計算させるメッセージを前記複数の並列データ記憶クラスタに送出するようさらに構成される請求項<u>14</u>に記載の分散データ記憶デバイス。

20

10

30

40

#### 【請求項16】

前記通信ファブリックは、前記中間データシンボルを前記複数の並列データ記憶クラスタのそれぞれに配信するようさらに構成される請求項<u>15</u>に記載の分散データ記憶デバイス。

# 【請求項17】

前記RAIDコントローラは、複数の中間データシンボルから、回復されるデータシンボルを計算するようさらに構成される請求項16に記載の分散データ記憶デバイス。

# 【請求項18】

前記ローカルな中間チェックサムは、前記RAIDコントローラに割当てられた前記複数のデータ記憶デバイスに対応する前記複数のデータシンボルの部分集合の部分和(partial sum)である請求項1から17のいずれか1項に記載の分散データ記憶デバイス。

### 【請求項19】

前記中間データシンボルは、前記RAIDコントローラに割当てられた前記データ記憶デバイスに対応する前記データシンボルの部分集合および前記リードチェックサムシンボルの部分和である請求項13に記載の分散データ記憶デバイス。

### 【請求項20】

データ記憶方法であって、

複数のデータ記憶デバイスを複数の並列データ記憶クラスタに割当てること、 前記複数の並列データ記憶クラスタのそれぞれに複数のデータシンボルを記憶すること

則記後数の业列テータ記憶クラスタのそれそれに後数のテータシンボルを記憶すること

前記複数の並列データ記憶クラスタのそれぞれ<u>に含まれる複数のRAIDコントローラのそれぞれが</u>、前記複数のデータシンボルの重み付き和から中間チェックサムを計算すること、

前記複数のRAIDコントローラの少なくとも1つが、前記複数のRAIDコントローラの他のRAIDコントローラのそれぞれから前記中間チェックサムを受信すること、

前記複数のRAIDコントローラの少なくとも1つが、計算した前記中間チェックサム および前記他のRAIDコントローラのそれぞれから受信した前記中間チェックサムに基 づいて前記複数のデータシンボルのチェックサムを計算すること、および、

前記複数のデータ記憶デバイスの少なくとも 1 つに前記チェックサムを記憶することを 含むデータ記憶方法。

# 【請求項21】

情報シンボルの部分集合から前記複数のデータシンボルを選択すること、および、 通信ファブリックを使用して、前記複数の並列データ記憶クラスタに前記選択されたデータシンボルを配信することをさらに含む請求項20に記載のデータ記憶方法。

# 【請求項22】

前記複数の並列データ記憶クラスタのそれぞれの中の作動可能なデータ記憶デバイスの集合を検知することをさらに含む請求項21に記載のデータ記憶方法。

# 【請求項23】

作動可能なデータ記憶デバイスの前記集合に基づくデータ回復行列を、前記複数の並列データ記憶クラスタのそれぞれに配信することをさらに含む請求項<u>22</u>に記載のデータ記憶方法。

#### 【請求項24】

前記データ回復行列に基づく中間データシンボルならびに前記記憶デバイスから読出されるリードデータシンボルおよびリードチェックサムシンボルの少なくとも一方のベクトルを計算することをさらに含む請求項23に記載のデータ記憶方法。

# 【請求項25】

前記中間データシンボルを前記複数の並列データ記憶クラスタのそれぞれに配信すること、および、

前記中間データシンボルの和から、回復されるデータシンボルを計算することをさらに 含む請求項 2 4 に記載のデータ記憶方法。 10

20

30

- -

40

#### 【請求項26】

分散データアーキテクチャにおける誤り訂正のための方法であって、

複数のデータ記憶デバイスを複数の並列データ記憶クラスタに割当てる構成行列を読出 すこと、

複数のデータシンボルを前記複数の並列データ記憶クラスタに記憶すること、

前記複数の並列データ記憶クラスタのそれぞれに含まれる複数のRAIDコントローラのそれぞれが、前記割当てられたデータ記憶デバイスに記憶された前記複数のデータシンボルから中間チェックサムを計算することであって、それにより、少なくとも1つの中間チェックサムがそれぞれのデータ記憶クラスタについて計算される、計算すること、

前記複数のRAIDコントローラの少なくとも1つが、前記複数のRAIDコントローラの他のRAIDコントローラのそれぞれから前記中間チェックサムを受信すること、

チェックサムを形成するために、<u>前記複数のRAIDコントローラの少なくとも1つが</u>、計算した前記中間チェックサムおよび前記他のRAIDコントローラのそれぞれから受信した前記中間チェックサムを合計すること、および、

前記チェックサムを少なくとも1つのデータ記憶デバイスに記憶する方法。

### 【発明の詳細な説明】

# 【技術分野】

### [0001]

本出願は、2007年11月21日に出願された米国仮出願第60/989,670号「Parallel RAID Implementation for RAID6 and Reed-Solomon Code」の利益を主張し、参照によりその全体が本明細書に組込まれる全ての引用された参考文献を含む。

# 【背景技術】

#### [00002]

RAID(redundant array of inexpensive disks)アーキテクチャは、ハードディスクなどのデータ記憶ユニットのグループを使用して、耐故障性を有するデータ記憶装置を提供する。RAIDアーキテクチャは、誤りおよびディスク故障から情報を保護するために、前方誤り訂正(forward errorcorrection)(FEC)コードおよび予備のデータ記憶ユニットを使用する。情報シンボルは、ビット、バイト、またはワードであってよい。情報シンボルは、符合化されて、データおよびチェックサムまたはパリティシンボルを含むコードシンボルを形成しうる。組織的な前方誤り訂正コードの場合、情報シンボルは、コードシンボルのデータシンボル部分において明示的に表されうる。

### [0003]

リードソロモンコードは、チェックサムシンボルの数に等しい記憶ユニットの故障の数を許容するために、RAIDアーキテクチャ(RS-RAID)で使用されうる。たとえば、データ用に20の記憶ユニットを、チェックサム用に4つの記憶ユニットを割当てる4重誤り訂正RS-RAIDアーキテクチャは、4つを含む4つまでの記憶デバイスにおける故障を許容しうる。

### [0004]

RS-RAIDアーキテクチャは、通常、データ記憶ユニットに書込まれるデータシンボルを保護するために単一のRAIDコントローラを使用する。単一のRAIDコントローラが使用されて、チェックサム、符号化、および復号化計算を実施するとき、RAIDアーキテクチャのスループットまたはデータ記憶量および取出し速度は、RAIDでなくかつ耐故障性を有さないデータ記憶アーキテクチャと比べて低減される可能性がある。

# 【発明の概要】

【発明が解決しようとする課題】

### [0005]

したがって、高スループットで耐故障性を有する分散型のデータ記憶アーキテクチャが 望ましい場合がある。 10

20

30

30

40

20

40

# 【課題を解決するための手段】

# [0006]

高性能記憶アーキテクチャでは、複数のRAIDコントローラは、通信ファブリックと呼ぶ通信経路の共通集合を通じて互いに通信してもよい。通信ファブリックは、RAIDコントローラと所与のRAIDコントローラに割当てられた記憶デバイスとの間の通信経路と比較して高いレーテンシを有する可能性がある。レーテンシの高い通信ファブリックは、RAIDコントローラ間のデータ、メッセージ、構成などのトラフィックが、耐故障性を有する分散データ記憶装置のタスクに整合しなければ、RAIDデータ記憶アーキテクチャのスループットを減少させる可能性がある。通信ファブリックと割当てられたデータ記憶デバイスの集合との間に介在してもよい、それぞれのRAIDコントローラは、データ記憶アーキテクチャのノードと呼ばれてもよい。RAIDコントローラおよび割当てられたデータ記憶デバイスは、データ記憶クラスタと呼ばれてもよい。

### [0007]

リードソロモン(Reed-Solomon)RAID(RS-RAID)アーキテクチャは、冗長なデータ記憶デバイスを含むことによって、ハードディスクなどの記憶デバイスに書込まれ、また、記憶デバイスから読出される情報シンボルを保護しうる。 mのチェックサムデバイスを使用するRS-RAIDアーキテクチャは、データ記憶デバイスの m程度の同時故障を許容しうる。 mのチェックサムシンボルは  $c_1$ ,  $c_2$ 、…、 $c_m$ で示されてもよい。RS-RAIDアーキテクチャはまた、 $d_1$ ,  $d_2$ 、…、 $d_n$ で示す情報保持またはデータシンボル用の数 n のデータ記憶デバイスを含みうる。

### [00008]

チェックサムおよびデータ記憶デバイスは、データおよびチェックサムシンボルを、ビット、バイト、ワードなどとして記憶してもよい。リードソロモン(RS)コードなどのあるタイプの前方誤り訂正コード(forward error correction codes)(FEC)は、通常、バイトを使用することが留意されてもよい。たとえば、RSコードは、255のバイトブロック内の233のデータバイトと32のチェックサムバイトに233の情報バイトを符合化するブロックなどのバイトブロックに作用しうる。

# [0009]

RS-RAIDアーキテクチャは、対応するデータ記憶デバイス $D_1$ 、 $D_2$ 、…、 $D_n$ によって保持されるデータシンボル $D_1$ 、 $D_2$ 、…、 $D_n$  で使用して、 $D_n$  ではいるデェックサムシンボル $D_n$  を使用して、 $D_n$  では記憶されるチェックサムシンボル $D_n$  では、 $D_n$  での記憶デバイスのうちの任意のm以下の記憶デバイスが故障する場合、故障したデバイスのうちの任意のデバイスがないまたは故障したデバイスから再構築されるように各 $D_n$  ( $D_n$ ) を確定しうる。RS-RAIDアーキテクチャは、ファンデルモンデ行列の特性により耐故障性を有する演算を提供することができ、ファンデルモンデ行列は、チェックサムシンボルを計算し維持し、記憶デバイスから読出したデータおよびチェックサムシンボルから情報を回復するのに使用される。RS-RAIDコントローラは、記憶デバイスが故障しても、添加されるかまたは拡大されたファンデルモンデ行列を単位行列の( $D_n$ ) 部分の逆行列を計算することによって、記憶デバイスにおけるデータおよび/またはチェックサムシンボルを回復しうる。

# [0010]

チェックサムシンボルを生成するために、RS-RAIDアーキテクチャは、データシンボルを、ファンデルモンデ行列の要素で重み付けし、式 1 によって線形関数  $F_i$  を使用して重み付けされたデータシンボルを合計しうる。関数  $F_i$  は、ファンデルモンデ行列の要素の i 番目の行から得られうるため、 $F_i$  =  $[f_{i,1}; f_{i,2}; ...; f_{i,n}]^\mathsf{T}$ である。

$$c_i = \sum_{j=1}^n d_j f_{i,j} \quad \vec{x} \quad 1$$

換言すれば、データおよびチェックサムシンボルが、それぞれ、(n×1)次元および  $(m \times 1)$  次元ベクトルD =  $[d_1, d_2, ..., d_n]$  T および C =  $[c_1, c_2, ..., d_n]$  $c_m$ ]  $^\intercal$  として表され、また、関数 F,が行列 F の行として表される場合、 R S - R A IDアーキテクチャは、チェックサムシンボルを式2aによって符合化しうる。

(6)

C = F D (式2a)

式 2 a は、

# 【数2】

$$\begin{bmatrix} c_1 \\ c_2 \\ \vdots \\ c_m \end{bmatrix} = \begin{bmatrix} f_{1,1} & f_{1,2} & \dots & f_{1,n} \\ f_{2,1} & f_{2,2} & \dots & f_{2,n} \\ \vdots & \vdots & & \vdots \\ f_{m,1} & f_{m,2} & \dots & f_{m,n} \end{bmatrix} \begin{bmatrix} d_1 \\ d_2 \\ \vdots \\ d_n \end{bmatrix}. \quad \not\equiv 2 b$$

に等しい。

# [0011]

有利に設計されたRS-RAID FECコードの場合、F行列は、要素:f,,= i<sup>i.1</sup>を有する(m×n)ファンデルモンデ行列でありうる。式中、インデックスi= 1、2、...、mおよび j = 1、2、...、n は、それぞれ、ファンデルモンデ行列の行およ び列に対応し、代数演算は、ガロア体の特性を使用して実施される。たとえば、(3×4 )ファンデルモンデ行列は、

【数3】

$$F = \begin{bmatrix} 1 & 1 & 1 & 1 \\ 1 & 2 & 3 & 4 \\ 1 & 4 & 9 & 16 \end{bmatrix} \quad \vec{x} \ \vec{x} \ \vec{3}$$

として書かれうる。

[0012]

誤りを含む可能性があるコードワードまたはコードシンボルから(nx1)情報ベクト ル

【数4】

$$\widetilde{D} = \left[\widetilde{d}_1, \widetilde{d}_2, ..., \widetilde{d}_n\right]^T$$

を回復するために、並列RS-RAIDアーキテクチャは、ファンデルモンデ行列およ 40 びIで示す添加された((n-m)×(n-m))単位行列を含む拡大されるかまたは分 割された行列Aの逆行列を求め、Aの逆行列に、作動可能な記憶ユニットから読出される データおよびチェックサムシンボルの集合 D および C をそれぞれ右から乗算し(post - multiply)うる。記号的には、回復される情報ベクトル

【数5】

$\widetilde{D}$

は、

10

20

30

40

50

# 【数6】

$$\widetilde{D} = Inv(A) \cdot \mid E \mid$$

から得られうる。式中、拡大行列は

【数7】

$$A \triangleq \begin{bmatrix} I \\ \overline{F} \end{bmatrix}$$

であり、 10

【数8】

$$E \underline{\triangle} \begin{bmatrix} \underline{D} \\ \underline{C} \end{bmatrix}$$

は、拡大されたデータおよびチェックサムシンボルベクトルである。表記Inv(A)は、正則な(nxn)正方行列を形成するAの行の部分集合の逆行列などのAに基づく逆行列をもたらし、また、以下で述べるように、

#### 【数9】

$\lfloor E \rfloor$

で示す列行列 E の n の行の、対応する選択されるかまたは選抜された集合に共形的である関数であると理解されてもよい。 A 行列の逆行列を求めるプロセスは、 A の行の選択された集合の反転とみなされてもよく、選択は、作動可能なデータ記憶デバイスのリストおよび行列にベクトルを掛ける計算における共形性についての要件によって確定される。 (n+m)×n)拡大行列 A の n の行の全ての部分集合は、 F がファンデルモンデ行列であるため反転可能であることが留意されてもよい。

[0013]

拡張形態では、式

# 【数10】

$$\widetilde{D} = Inv(A) \cdot |E|$$

は、

# 【数11】

$$\begin{bmatrix} \widetilde{d}_{1} \\ \widetilde{d}_{2} \\ \vdots \\ \widetilde{d}_{n} \end{bmatrix} = Inv \begin{pmatrix} \begin{bmatrix} 1 & 0 & 0 & \cdots & 0 \\ 0 & 1 & 0 & \cdots & 0 \\ \vdots & \vdots & \vdots & & \vdots \\ 0 & 0 & 0 & \cdots & 1 \\ 1 & 1 & 1 & \cdots & 1 \\ 1 & 2 & 3 & \cdots & n \\ \vdots & \vdots & \vdots & & \vdots \\ 1 & 2^{m-1} & 3^{m-1} & \cdots & n^{m-1} \end{pmatrix} \cdot \begin{pmatrix} \begin{bmatrix} d_{1} \\ d_{2} \\ \vdots \\ \frac{d_{n}}{c_{1}} \\ c_{2} \\ \vdots \\ c_{m} \end{pmatrix}$$

として表されうる。式中、共形性は、行列Aの選択された部分を反転する前に、EおよびAの対応する行を選択することによって実施される。

# [0014]

換言すれば、RS-RAIDアーキテクチャの各記憶デバイスは、拡大行列Aの行および列ベクトルE=[d<sub>1</sub>、d<sub>2</sub>、…、d<sub>n</sub>、c<sub>1</sub>、c<sub>2</sub>、…、c<sub>m</sub>]<sup>T</sup>の対応する要素によって表されうる。mの冗長記憶デバイス中のいずれの冗長記憶デバイスも故障しない場合、回復される情報シンボルは、Aのnの行の任意の部分集合およびEのnの対応する要素を選択することによって確定されて、データ回復行列として記述されてもよい正方行列

30

A 'および対応するデータ記憶ユニットから読出されるデータのベクトル 【数 1 2 】

$$E'=\mid E\mid$$

.

が形成されうる。換言すれば、Inv(A)=(A¹)  $^{-1}$  であり、また、

# 【数13】

$$\widetilde{D} = (A')^{-1} \cdot E'$$

である。たとえば、 4+2RS-RAID アーキテクチャの場合、回復されるかまたは 復号化されるデータ

复号化されるデータ 【数14】

$\widetilde{D}$

は、

# 【数15】

$$\begin{bmatrix} \widetilde{d}_{1} \\ \widetilde{d}_{2} \\ \widetilde{d}_{3} \\ \widetilde{d}_{4} \end{bmatrix} = Inv \begin{pmatrix} \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \\ \frac{1}{1 - 1} & \frac{1}{1 - 1} \\ \frac{1}{1 - 2} & \frac{3}{3} & 4 \end{pmatrix} \cdot \begin{bmatrix} d_{1} \\ d_{2} \\ d_{3} \\ \frac{d_{4}}{c_{7}} \\ \vdots \\ c_{2} \end{bmatrix} = \begin{bmatrix} d_{1} \\ d_{2} \\ d_{3} \\ \vdots \\ d_{4} \end{bmatrix} \quad \text{ $\overrightarrow{T}$ 5}$$

によって、拡大されたファンデルモンデ行列の最初の4つの行および記憶デバイスアレイから読出されたデータおよびチェックサムの最初の4つのエンティティから抽出された回復されるデータシンボルのベクトルでありうる。

# [0015]

たとえば、第3の、第5の、または、第3と第5の両方のデータ記憶デバイスが故障する場合、

【数16】

$\widetilde{D}$ ,

は、以下の通りに、作動可能なデバイスに対応する4つの行を選択することによって、 E'から回復されうる。

# 【数17】

$$\begin{bmatrix} \widetilde{d}_{1} \\ \widetilde{d}_{2} \\ \widetilde{d}_{3} \\ \widetilde{d}_{4} \end{bmatrix} = Inv \begin{pmatrix} \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \\ 1 & 1 & 1 & 1 \\ 1 & 2 & 3 & 4 \end{pmatrix} \cdot \begin{bmatrix} d_{1} \\ d_{2} \\ \frac{d_{3}}{d_{4}} \\ c_{1} \\ c_{2} \end{bmatrix}$$

$\neq$  6 a 40

$$= \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 1 & 1 & 1 & 1 \end{bmatrix} \begin{bmatrix} d_1 \\ d_2 \\ d_4 \\ c_1 \end{bmatrix}$$

20

30

50

# 【数18】

$$\begin{bmatrix} \widetilde{d}_1 \\ \widetilde{d}_2 \\ \widetilde{d}_3 \\ \widetilde{d}_4 \end{bmatrix} = Inv \begin{pmatrix} \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \\ \frac{1}{1} & \frac{1}{1} & \frac{1}{1} & \frac{1}{1} \\ \frac{1}{2} & \frac{3}{3} & \frac{4}{3} \end{pmatrix} \quad \vec{x} \in b$$

$$= \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \end{bmatrix}^{-1} \begin{bmatrix} d_1 \\ d_2 \\ d_3 \\ d_4 \end{bmatrix}$$

# 【数19】

$$\begin{bmatrix} \widetilde{d}_1 \\ \widetilde{d}_2 \\ \widetilde{d}_3 \\ \widetilde{d}_4 \end{bmatrix} = Inv \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 1 \\ \frac{1}{1} & \frac{1}{1} & \frac{1}{1} & \frac{1}{1} \\ 1 & 2 & 3 & 4 \end{bmatrix} \cdot \begin{bmatrix} d_1 \\ d_2 \\ \frac{d_3}{d_3} \\ d_4 \\ \frac{c_7}{c_2} \end{bmatrix}$$

$\neq$  6 e

$$= \begin{bmatrix} 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 1 & 2 & 3 & 4 \end{bmatrix} \begin{bmatrix} d_1 \\ d_2 \\ d_4 \\ c_2 \end{bmatrix}$$

式中、2重末梢線は記憶デバイスの故障を示し、1重末梢線は、逆行列を形成し、その後の計算を実施するための記憶デバイスの選択解除を示しうる。逆行列は、ガウス消去法または別の方法によって計算されてもよい。

# 【数20】

$\widetilde{D}$ ,

の値が得られると、回復されるかまたは推定される任意のチェックサムベクトル 【数 2 1 】

$\widetilde{C}$

が、

【数22】

$$\widetilde{C} = F\widetilde{D}$$

を使用して、データベクトル

【数23】

$\widetilde{D}$ ,

に基づいて計算されてもよい。

# [0016]

並列RS-RAIDデータ記憶アーキテクチャは、各クラスタ内のデータおよびチェックサムを、全てのクラスタに転送されるかまたは配信される中間または部分和に集計しうる。中間データシンボル、中間チェックサムシンボル、データ記憶デバイスのクラスタへ

20

30

40

50

の割当てに関するクラスタ構成情報、およびデータ記憶デバイスの作動に関する状態などの使用は、並列RS-RAID分散データ記憶アーキテクチャのスケーラビリティおよびスループットを向上させながら、誤り訂正計算についての計算負荷およびレーテンシを低減しうる。

# [0017]

本開示は、同じ数字が同じ要素を表す添付図面を参照することになる。

【図面の簡単な説明】

[0018]

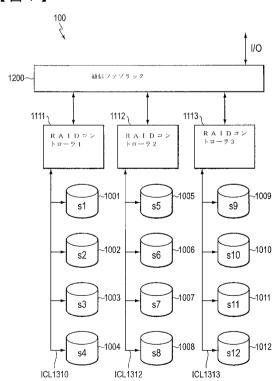

【図1】並列RS-RAID (Reed-Solomon redundant array of inexpensive disk)の例を示す図である。

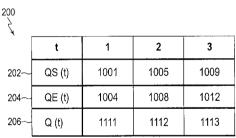

【図2】構成行列の例を示す図である。

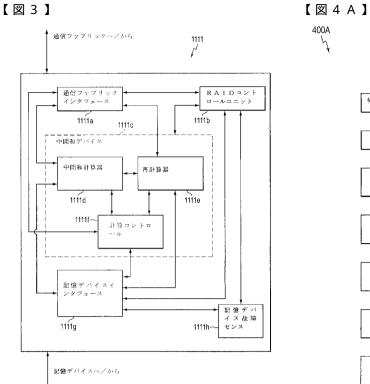

【図3】RAIDコントローラの例を示す図である。

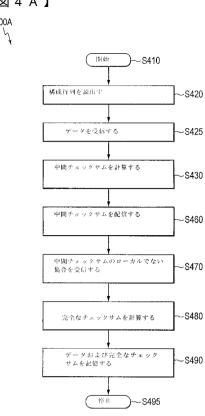

【図4A】チェックサムプログラムの例のフローチャートである。

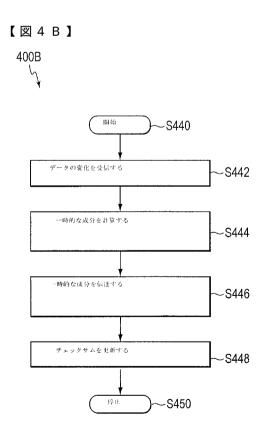

【図4B】チェックサム更新プログラムの例のフローチャートである。

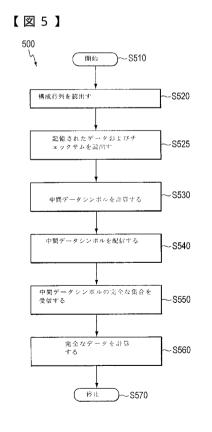

【図5】データプログラムの例のフローチャートである。

【発明を実施するための形態】

[0019]

図1は、データ記憶のための並列RS-RAIDアーキテクチャ100の例である。並列RS-RAIDアーキテクチャ100は、通信ファブリック1200、RAIDコントローラ1111~1113、および記憶デバイス1001~1012を含みうる。記憶デバイス1001~1004、1005~1008、および1009~1012は、それぞれ、RAIDコントローラ1111~1113に結合されうる。換言すれば、記憶デバイス1001~1012の部分集合またはクラスタは、それぞれの対応するRAIDコントローラ1111~1113に結合しうる記憶デバイスの数は、等しくても、等しくなくてもよく、また、耐故障性を改善する、スループットを改善するなどのために、記憶デバイスのRAIDコントローラに対する構成またはマッピングは動的に変わってもよい。たとえば、記憶デバイス1001~1012のRAIDコントローラ1111~1113に対する割当ては、構成行列または同様のデータ構造によって確定されてもよい。

[0020]

図2は、変数「t」を含みうる構成行列200の例を示し、変数「t」は、RAIDコントローラの数のインデックスまたはカウンタである。たとえば、構成行列200の行206は、RAIDコントローラインデックス番号「t」と、RAIDコントローラ111~113などのそれぞれのRAIDコントローラとの間のマッピング関数Q(t)を示す。行202はRAID記憶デバイス開始インデックスQS(t)を示し、行204はRAID記憶デバイス開始インデックスQS(t)を示し、行204はRAID記憶デバイス開始インデックスQS(t)を示し、行204はRAID記憶デバイス開始インデックスQS(t)を示し、で2)=1005であり、QE(2)=1008である。デバイス番号のオフセットが、関数J(35であり、Cを表し、で2)=100記憶デバイスが第2の記憶デバイスクラスタで開始することを示しうることが留意であれてもよいた構成行列200は、記憶デバイスのどの部分集合またはクラスタが、所与のRAIDコントローラに割当てられるかを確定するかまたは制御しうる。計算のために、構成行列200は、以下で述べるように、コードワードを符合化するかまたは復号化しうる重み付き部分和の始まりと終わりを確定しうる、チェックサムおよびデータを更新するかまたは維持しうるなどを行いうる。

[0021]

通信ファブリック 1 2 0 0 は、RAIDコントローラ 1 1 1 1 ~ 1 1 1 3 間で、また、並列 RS-RAIDアーキテクチャ 1 0 0 と外部デバイスとの間で入力および出力(I/O)デジタル信号を結合しうる。たとえば、通信ファブリック 1 2 0 0 は、RAIDコントローラ 1 1 1 1 ~ 1 1 1 3 間で、データシンボル、チェックサムシンボル、中間データ

20

30

40

50

およびチェックサムシンボルなどのようなデジタル信号を結合しうる。通信ファブリック 1 2 0 0 は、並列バス構造、直列データリンク、光バックプレーンなどを使用してもよい。通信ファブリック 1 2 0 0 は、外部通信用に 1 つのタイプのバス、リンク、またはバックプレーン構造を、RAIDコントローラ 1 1 1 1 ~ 1 1 1 3 間の通信用に別のタイプを使用してもよい。

### [0022]

RAIDコントローラ 1 1 1 1 ~ 1 1 1 3 は、構成行列 2 0 0 などの構成行列または他のデータ構造によって与えられた、割当てられた記憶デバイスの部分集合またはクラスタ内の各記憶デバイスについてデータチェックサムシンボルを計算しうる。 RAIDコントローラ 1 1 1 1 ~ 1 1 1 3 は、誤り訂正コード計算の部分和を集計するかまたは蓄積し、集計されたデータおよびパリティ計算結果を、通信ファブリック 1 2 0 0 を通じて、並列RS - RAIDアーキテクチャ 1 0 0 内の他のRAIDコントローラに報告しうる。データおよびチェックサムシンボルについての部分和計算の詳細が、特定のRAIDコントローラを参照して述べられてもよいが、対応する計算は、RAIDコントローラ 1 1 1 1 などの、並列RS - RAIDアーキテクチャ 1 0 0 内の任意のRAIDコントローラによって実施されてもよい。

# [0023]

図3は、通信ファブリックインタフェース1111a、RAIDコントロールユニット1111b、中間和デバイス1111c、記憶デバイスインタフェース1111g、および記憶デバイス故障センスユニット1111hを含みうるRAIDコントローラ1110の例を示す。通信ファブリックインタフェース1111aは、通信ファブリック1200などの通信ファブリックへのまた通信ファブリックからの信号を、中間和デバイス1111c、記憶デバイスインタフェース1111g、および記憶デバイス故障センスユニット1111hに結合しうる。記憶デバイスインタフェース1111g、および記憶デバイス故障センスユニット11111b、中間和デバイスインタフェース111115、中間和デバイスカ障センスユニット111115、中間和デバイスカロコントローラ111115、中間和デバイスカロコントローラ111115。RAIDコントローラ11111 は、先に述べたように、通信ファブリック1200へまた通信ファブリック1200から結合し、記憶デバイスインタフェース1111gを介して記憶デバイス1001~1004などの記憶デバイスへまた記憶デバイスから結合しうる。

#### [0024]

中間和デバイス1111cは、中間和計算器1111d、再計算器1111e、および計算コントロール1111fを含みうる。中間和計算器1111dは、通信ファブリックインタフェース1111g、再計算器1111 e、および計算コントロール1111fに結合しうる。再計算器1111eは、通信ファブリックインタフェース1111a、中間和計算器1111d、計算コントロール1111f、および記憶デバイスインタフェース1111gに結合しうる。計算コントロール11111f、および記憶デバイスインタフェース1111gに結合しうる。計算コントロール1111fは、中間和計算器1111d、再計算器1111e、および記憶デバイスインタフェース1111gに結合しうる。

# [0025]

通信ファブリックインタフェース111aは、並列RS-RAIDアーキテクチャ100と外部デバイスとの間で情報シンボルを転送し、通信ファブリック1200とRAIDコントローラ1111の要素との間で、情報シンボル、情報シンボルの所定部分、データシンボル、中間チェックサムシンボルなどのチェックサムシンボル、コントロール信号、クロック信号などを結合しうる。通信ファブリックインタフェース1111aは、情報シンボルをビットからバイト、ワード、または他のシンボルにリフォーマットしうる、信号を多重化し逆多重化しうる、データ転送を同期化しうる、ラインドライバおよび受信機によって信号をバッファリングしうるなどを行いうる。換言すれば、通信ファブリックインタフェース1111aは、デジタルバスなどの通信ファブリックを通じて送信するためにデジタル信号を調節しうる、データ転送をバッファリングしうるなどを行いうる。

### [0026]

RAIDコントロールユニット1111bは、通信ファブリックインタフェース1111aおよび記憶デバイスから信号を受信しうる、情報シンボルの部分集合からデータシンボルを選択しうる、記憶デバイスにわたってデータおよびチェックサムシンボルをストライピングしうる、前方誤り訂正コード(forward-error correction code)(FECcode)によって中間和デバイス11111cの作動を制御しうるなどを行いうる。たとえば、情報シンボルの部分集合は、データシンボルによって表され、かつ、RAIDコントローラ1111によって制御される作動可能なデータ記憶デバイスに記憶される情報シンボルでありうる。中間和デバイス11111cは、記憶デバイス故障センスユニット1111hから状態情報を得ることができるRAIDコントロールユニット1111bから作動可能な記憶デバイスの数に関する状態情報を受信してもよい

10

### [0027]

記憶デバイス故障センスユニット1111hは、RAIDコントローラ1111に結合する任意の記憶デバイスの作動に関する状態を確定し、作動可能な記憶デバイスのリストを確定しうる。換言すれば、記憶デバイス故障センスユニット1111hは、所与の記憶デバイスが、データおよびチェックサムの確実な記憶に適さなくなったかどうかを判定しうる。記憶デバイス故障センスユニット1111hは、信頼性のある作動について記憶デバイスを試験しうる、所与の記憶デバイスがオンラインであるかどうかを判定しうる、所与の記憶デバイスがあらの記憶デバイスがあらの応答が、所定のタイムアウト間隔内に受信されない場合、ユニットオフラインを宣言しうる、信号品質メトリックが、記憶デバイスから読出されたデラタについて闘品質より小さいかどうかを判定しうる、作動可能な記憶デバイス故障センスユニット1111hは、こうした試験の結果を記録し、RAIDコントロールユニット1111bなどのRAIDコントローラ111の要素のために、作動可能な記憶デバイスのリストを配信しうる。

20

# [0028]

中間和計算器1111dは、中間的でローカルで部分的な和を計算することができ、この和内に、チェックサムおよびデータについての誤り訂正コード計算が、式8および式13に関してそれぞれ述べたように分解されうる。中間的なまたは部分的な和は、RAIDコントローラ1111に報告するクラスタ内の作動可能な記憶デバイスから読出されるシンボルの重み付き和であってよい。たとえば、記憶デバイスのクラスタおよびこうした部分和の合計の対応する制限は、構成行列200などの構成行列または他のデータ構造から確定されてもよい。中間和計算器1111dは、RAIDコントローラ1112またはRAIDコントローラ1113などの他のRAIDコントローラから対応する部分和を受信した後、データおよびチェックサムシンボルを計算しうる。

30

### [0029]

再計算器1111 e は、R A I D コントローラ1111 に直接結合する記憶デバイスからのデータに基づいて中間的なローカルのチェックサムを、また、通信ファブリックインタフェース1111 a を通して転送される他のR A I D コントローラからのローカルでない中間チェックサムを再計算しうる。換言すれば、データまたはチェックサムシンボルの変化が、R A I D コントローラ1111に直接結合するローカルの記憶デバイスにおいて起こるか、または、通信ファブリック1200を通じてR A I D コントローラ1111に送信される中間チェックサムによって起こると、再計算器1111 e は、中間和計算器1111 d からの結果を相応して修正しうる。

40

#### [0030]

計算コントロール 1 1 1 1 f は、中間チェックサム計算結果または再計算されたチェックサムが、FECのために使用されるべきかどうかを判定するために、中間和計算器 1 1 1 1 d と再計算器 1 1 1 1 e の両方を制御しうる。RAIDコントロール 1 1 1 1 b は、中間和計算器 1 1 1 1 d の結果と再計算器 1 1 1 1 e の結果のいずれが計算されるかを判定するために、直接にまたは通信ファブリックインタフェース 1 1 1 1 a を通して計算コ

30

40

ントロール 1 1 1 1 f に合図し(signal) うる。 R A I D コントロール 1 1 1 1 b は、記憶 デバイス故障センスユニット 1 1 1 1 h から、データ記憶デバイスに関する作動に関する 状態などの状態情報を得ることができる。

#### [0031]

並列RAIDコントローラ1111~1113は、

# 【数24】

# [0032]

RAIDコントローラ1111などのt番目のRS-RAIDコントローラは、

# 【数25】

$$c_{i,t} = \sum_{j=J(QS(t))}^{J(QE(t))} d_j f_{i,j} \quad \vec{x} 8$$

によって、中間チェックサムci、tを計算しうる。

#### [0033]

### [0034]

中間チェックサムおよび全チェックサムを計算することに加えて、並列 R S - R A I D アーキテクチャ 1 0 0 は、データシンボルが変化すると、チェックサムシンボルを修正するかまたは維持しうる。たとえば、データシンボルが、 d  $_j$  から d  $_j$  に変化すると、チェックサムは、

$$c'_{i} = c_{i} + f_{i}_{i} (d'_{i} - d_{i})$$

式 9

によって、再計算されうる。式 9 の計算を実施するとき、 R A I D コントローラ 1 1 1 1 は、データ差( d '  $_{\rm j}$  - d  $_{\rm j}$  )を計算し、ファンデルモンデ要素 f  $_{\rm i}$   $_{\rm j}$  、すなわち、 【数 2 6 】

によって、データ差に重み付けしうる。

#### [0035]

個々の並列RAIDコントローラ1111~1113は、一時的な成分 c '<sub>i,t</sub>を R AIDコントローラ1111~1113の他のコントローラに送出しうる。

### [0036]

RS-RAIDコントローラ1111~1113は、

# 【数27】

によって、それぞれの割当てられた記憶デバイスを更新しうる。

### [0037]

記憶デバイスが故障する、たとえば、記憶デバイス故障センスユニット1111hがハ ードディスククラッシュを検出すると、拡大行列の逆行列Inv(A)が、並列RAID コントローラ1111~1113によって修正されて、残りのまたは作動可能なデータ記 憶デバイスに対応する逆行列Inv(A')が形成される。行列Inv(A')は、記憶デ バイスのさらなる故障が起こらない限り、静的データ構造である可能性がある。別の記憶 デバイスが故障すると、Inv(A')が一回計算され、その後、RAIDコントローラ 1 1 1 1 ~ 1 1 1 3 などの全ての作動可能な R A I D コントローラにブロードキャストさ れうる。より多くの記憶デバイスが後で故障する場合、新しい逆行列Inv(A'')が、 再計算され、全てのRAIDコントローラにブロードキャストされてもよい。

### [0038]

並列RS-RAIDアーキテクチャ100は、記憶デバイスが故障しても、各RAID コントローラにおいてローカルで計算される中間和または部分和を使用して、データシン ボルを回復しうる。回復されるデータ

# 【数28】

$$\widetilde{D} = \left[ \in \widetilde{d}_1, \widetilde{d}_2, ..., \widetilde{d}_n \right]^T$$

# 【数29】

は、

から回復される可能性がある。式中、Inv(A')の要素は、a<sub>i i</sub> (1 i n および 1 j n)で示されてもよい。対応するデータおよびチェックサムシンボル E' = [ e <sub>1</sub> 、 e <sub>2</sub> 、…、 e <sub>n</sub> ] <sup>T</sup> の要素は、作動可能でかつ選択されたデータ記憶デバイス から読出されうる。並列RS-RAIDアーキテクチャ100は、Eの行ならびに添加さ れた単位行列とファンデルモンデ行列の対応する部分集合を選択するかまたは選抜して、 それぞれ、E'およびInv(A')が形成されうる。換言すれば、並列RS-RAIDア ーキテクチャ100は、データ回復計算を、

# 【数30】

$$\widetilde{d}_{i,t} = \sum_{j=J(QS(t))}^{J(QE(t))} a_{i,j} \cdot e_j \quad \vec{\exists} \quad 1 \quad 3$$

によって、部分和または中間データシンボルの集合に分解しうる。式中、eiは、t番 目のRS-RAIDコントローラの制御下にある全てのデータまたはチェックサムシンボ ルの集合であると理解される。

### [0039]

他の並列RS-RAIDコントローラから、中間データシンボルなどのメッセージを受 信すると、個々のRAIDコントローラは、最初に中間データシンボル

# 【数31】

$\widetilde{d}_{i,t}$

を計算し、次に、

10

20

30

40

20

30

40

50

# 【数32】

$$\widetilde{d}_i = \sum_{t=1}^r \widetilde{d}_{i,t}$$

.  $\sharp 1 4$

によって、回復されるデータ

#### 【数33】

αì

を計算しうる。

# [0040]

図4Aは、データ記憶用の並列RS-RAIDアーキテクチャのためのチェックサムプログラムフローチャート400Aの例を示す。プログラムフローチャート400Aは、プログラムステップS410で開始し、並列RS-RAIDアーキテクチャの構成行列が読出されうるプログラムステップS420に進みうる。たとえば、構成行列は、図2に関して述べた構成行列などの、所与のRAIDコントローラに関連する記憶デバイスについての開始デバイス番号と終了デバイス番号を指定しうる。各RAIDコントローラは、構成行列のローカルなコピーを記憶しうる、構成行列を他のRAIDコントローラと調和させうる、構成行列を、高レベルのRAIDデバイスまたはネットワークコントローラから受信しうるなどを行いうることが理解されてもよい。

# [0041]

プログラムステップS420から、プログラムフローは、プログラムステップS425に進むことができ、プログラムステップS425にて、プログラムは、外部デバイスから、記憶される情報保持データシンボルを読出すことができる。たとえば、プログラムは、通信ファブリックを通じて受信される2Kビットのデータブロックの集合をフラッシュドライブから受信しうる。

# [0042]

プログラムステップS425から、プログラムは、中間チェックサムが計算されうるプログラムステップS430に進むことができる。たとえば、中間チェックサムまたはデータおよびパリティ計算は、式8およびガロア体の特性を使用した、データワードの線形結合から計算されうる。プログラムステップS430は、中間チェックサムを計算し、1)所与のRAIDコントローラにコードワードシンボルの所定部分を供給する個々の作動可能な記憶ユニットからの記憶されたコードワードシンボルを使用して中間チェックサムを更新するかまたは維持し、2)通信ファブリックを通じて所与のRAIDコントローラからの中間チェックサムを集計しうる。換言すれば、ローカルな部分集合データ記憶ユニットからの低レーテンシのデータおよびパリティビット、バイト、またはワードは、他のデータ記憶ユニットからの、ci,tの形態の、高レーテンシの、蓄積されるかまたは部分的に合計されたデータおよびパリティと結合されうる。その後、プログラムは、プログラムステップS460に進む。

# [0043]

ステップS460にて、プログラムは、中間チェックサムを異なるRS-RAIDコントローラに配信しうる。たとえば、Q(t)= tである場合、プログラムステップS46 0 は、第1のRAIDコントローラからの第1の中間チェックサム c <sub>1 , 1</sub> を第2および 第3のRAIDコントローラに配信しうる。

# [0044]

プログラムステップS460から、プログラムフローは、プログラムステップS470に進むことができ、プログラムステップS470にて、プログラムは、他のRAIDコントローラから中間チェックサムを受信しうる。プログラムステップS470から、プログラムはプログラムステップS480に進みうる。中間チェックサムの集合によって、各RAIDコントローラが、式8によって完全なチェックサムciを計算し、その後の誤り訂正および検出計算についてciを記憶することが可能になる。たとえば、プログラムは、第2および第3の中間チェックサムci,2およびci,3を受信することができ、第2

20

30

40

50

および第3の中間チェックサム  $c_{i,2}$  および  $c_{i,3}$  は、ローカルに計算された第1のチェックサム  $c_{i,1}$  と共に、  $c_{1}$  を計算するためのチェックサムの十分な集合を形成しうる。

[0045]

プログラムステップS480から、プログラムフローは、プログラムステップS490に進むことができ、プログラムステップS490にて、プログラムは、プログラムを実行するRAIDコントローラに割当てられるデータおよび完全なチェックサムシンボルを記憶しうる。たとえば、プログラムは、ディスクのアレイにわたってデータおよびチェックサムシンボルをストライピングしうる。プログラムステップS490から、プログラムフローは、プログラム実行が停止しうるプログラムステップS495に進みうる。

[0046]

図4 B は、データ記憶用の並列 R S - R A I D アーキテクチャのためのチェックサム更新プログラムフローチャート 4 0 0 B の例を示す。プログラムフローチャート 4 0 0 B は、ステップ S 4 4 0 で開始し、ステップ S 4 4 2 に進む。

[0047]

ステップS442にて、並列RS-RAIDアーキテクチャは、データの変化を受信する可能性がある。たとえば、記憶デバイスは、古いデータシンボルを置換するために新しいデータシンボルを受信してもよい。その後、プログラムフローはステップS444に進みうる。

[0048]

ステップS444にて、記憶デバイスに結合するRAIDコントローラは、式10によって、一時的な成分を計算しうる。RAIDコントローラは、新しいデータシンボルと古いデータシンボルとのデータ差を得、ファンデルモンデ行列要素によってデータ差に重み付けしてもよい。その後、プログラムフローはステップS446に進みうる。

[0049]

ステップS446にて、一時的な成分は、他のRAIDコントローラに伝達されうる。ある実施形態では、通信ファブリックは、種々のRAIDコントローラを結合してもよい。通信ファブリックは、データ変化に対応する一時的な成分を、チェックサムを記憶する記憶デバイスを制御するRAIDコントローラに伝達しうる。その後、プログラムフローはステップS448に進みうる。

[0050]

ステップS448にて、チェックサムを記憶する記憶デバイスを制御するRAIDコントローラは、たとえば、式11によって、受信した一時的な成分に基づいてチェックサムを更新してもよい。その後、プログラムフローはステップS450に進み、停止しうる。

[0051]

図5は、データ記憶用の並列RS-RAIDアーキテクチャのためのデータプログラムフローチャート500の例を示す。プログラムフローチャート500は、ステップS510で開始し、ステップS520に進むことができ、ステップS520にて、並列RS-RAIDアーキテクチャの構成行列が、図4Aに関して説明したように読出されうる。プログラムステップS525に進むことができ、プログラムステップS525に進むことができ、プログラムステップS525に進むことができ、プログラムステップS525に進むことができ、プログラムステップS525にて、データおよびチェックサムシンボルが、記憶デバイスから読出されうる。たとえば、8つのデータおよび4つのチェックサムシンボルは、12の記憶デバイスから読出されうる。この例では、少なくとも8つのデータまたはチェックサムシンボルが、作動可能な記憶デバイスから読出されうる。

[0052]

プログラムステップS425から、プログラムフローは、プログラムステップS530に進むことができ、プログラムステップS530にて、プログラムは、中間データシンボルを計算しうる。たとえば、プログラムは、式13によって、中間データシンボルを計算しうる。式13で使用される重み係数  $a_{i,j}$  は、予め計算され、RAIDコントローラに配信されるか、または、プログラムステップS520において構成行列を読出した後な

どに、必要に応じて再計算されてもよいことが理解されてもよい。プログラムステップ S 5 3 0 から、プログラムフローは、プログラムステップ S 5 4 0 に進むことができ、プログラムステップ S 5 4 0 にて、プログラムは、中間データシンボルを並列 R A I D コントローラに配信しうる。

# [0053]

プログラムステップS540から、プログラムフローは、プログラムステップS550に進むことができ、プログラムステップS550にて、プログラムは、並列RAIDコントローラから中間データシンボルを受信しうる。プログラムステップS550から、プログラムフローは、プログラムステップS560に進むことができ、プログラムステップS560にて、プログラムは、ローカルなRAIDコントローラと並列RAIDコントローラの両方から来た中間データシンボルから、回復されるデータシンボルを計算しうる。換言すれば、プログラムは、式14によって、中間データシンボルを合計しうるプログラムステップS560から、プログラムフローは、プログラム実行が停止しうるプログラムステップS570に進むことができる。

# [0054]

本発明は、本発明の特定の例示的な実施形態に関連して述べられたが、多くの代替、修正、および変形が当業者に明らかになることが明らかである。したがって、本明細書で述べる本発明の実施形態は、制限的でなく、例証的であることを意図される。本発明の精神および範囲から逸脱することなく行われてもよい変更が存在する。

【図2】

# フロントページの続き

(56)参考文献 特開2007-257630(JP,A)

特開2003-131818(JP,A)

米国特許出願公開第2007/0245173(US,A1)

(58)調査した分野(Int.CI., DB名)

G06F 3/06