## (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2019/089050 A1

(51) International Patent Classification: *H01L 29/772* (2006.01) *H01L 21/8234* (2006.01)

H01L 29/73 (2006.01)

(21) International Application Number:

PCT/US2017/060113

(22) International Filing Date:

06 November 2017 (06.11.2017)

(25) Filing Language:

English

(26) Publication Language:

English

- (71) Applicant: INTEL CORPORATION [US/US]; 2200 Mission College Boulevard, Santa Clara, California 95054 (US).

- (72) Inventors: CHU-KUNG, Benjamin; 4220 NW 192nd Avenue, Portland, Oregon 97229 (US). KAVALIEROS, Jack

T.; 3734 NW Bronson Crest Loop, Portland, Oregon 97229 (US). SUNG, Seung Hoon; 2459 NW Parnell Terrace, Portland, Oregon 97229 (US). CHOUKSEY, Siddharth; 4876 NW Olivares Ter., Portland, Oregon 97229 (US). KENNEL, Harold W.; 7320 SW Hunt Club Drive, Portland, Oregon 97223 (US). BASU, Dipanjan; 1190 Moonlight Ave, Hillsboro, Oregon 97123 (US). AGRAWAL, Ashish; 7177 NE Ronler Way Apt. 0321, Hillsboro, Oregon 97124 (US). GLASS, Glenn A.; 5009 NW 124th Avenue, Portland, Oregon 97229 (US). GHANI, Tahir; 14191 NW Stonebridge Drive, Portland, Oregon 97229 (US). MURTHY, Anand S.; 10934 NW Lucerne Court, Portland, Oregon 97229 (US).

(74) Agent: MALONEY, Neil F.; Finch & Maloney PLLC, Gateway One, 50 Commercial Street - Suite 300, Manchester, New Hampshire 03101 (US).

#### (54) Title: REDUCING BAND-TO-BAND TUNNELING IN SEMICONDUCTOR DEVICES

FIG. 1a

(57) Abstract: Integrated circuit transistor structures are disclosed that reduce band-to-band tunneling between the channel region and the source/drain region of the transistor, without adversely increasing the extrinsic resistance of the device. In an example embodiment, the structure includes one or more spacer configured to separate the source and/or drain from the channel region. The spacer(s) regions comprise a semiconductor material that provides a relatively high conduction band offset (CBO) and a relatively low valence band offset (VBO) for PMOS devices, and a relatively high VBO and a relatively low CBO for NMOS devices. In some cases, the spacer includes silicon, germanium, and carbon (e.g., for devices having germanium channel). The proportions may be at least 10% silicon by atomic percentage, at least 85% germanium by atomic percentage, and at least 1% carbon by atomic percentage. Other embodiments are implemented with III-V materials.

WO 2019/089050

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

### **Declarations under Rule 4.17:**

— of inventorship (Rule 4.17(iv))

#### **Published:**

— with international search report (Art. 21(3))

# REDUCING BAND-TO-BAND TUNNELING IN SEMICONDUCTOR DEVICES

### BACKGROUND

Semiconductor devices are electronic components that exploit the electronic properties of semiconductor materials, such as silicon, germanium, and gallium arsenide. A field-effect transistor (FET) is a semiconductor device that includes three terminals: a gate, a source, and a drain. A FET uses an electric field applied by the gate to control the electrical conductivity of a channel through which charge carriers (e.g., electrons or holes) flow from the source to the drain. In instances where the charge carriers are electrons, the FET is referred to as an n-channel device, and in instances where the charge carriers are holes, the FET is referred to as a p-channel device. Some FETs have a fourth terminal called the body or substrate, which can be used to bias the transistor. In addition, metal-oxide-semiconductor FETs (MOSFETs) include a gate dielectric between the gate and the channel. MOSFETs may also be known as metal-insulator-semiconductor FETs (MISFETSs) or insulated-gate FETs (IGFETs). Complementary MOS (CMOS) structures use a combination of p-channel MOSFET (PMOS) and n-channel MOSFET (NMOS) to implement logic gates and other integrated circuits. When a MOSFET device is biased in the OFF-state, for example in an n-MOS with the gate held in a low state and the drain held in a high state, there will be a relatively large electric field in the channel-drain region which can result in a phenomenon known as band-to-band tunneling (BTBT). BTBT can cause a number of non-trivial issues.

### BRIEF DESCRIPTION OF THE DRAWINGS

**[0002]** Features and advantages of embodiments of the claimed subject matter will become apparent as the following Detailed Description proceeds, and upon reference to the Drawings, wherein like numerals depict like parts.

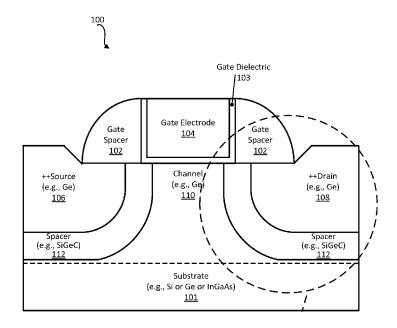

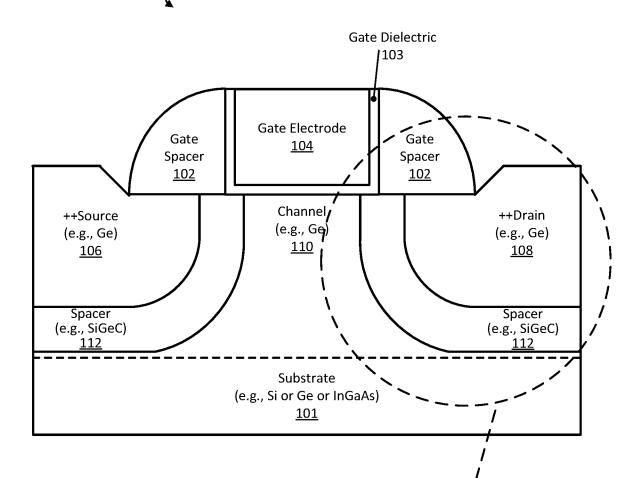

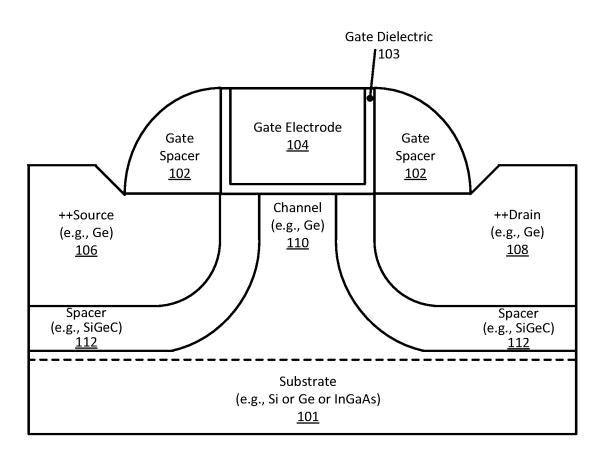

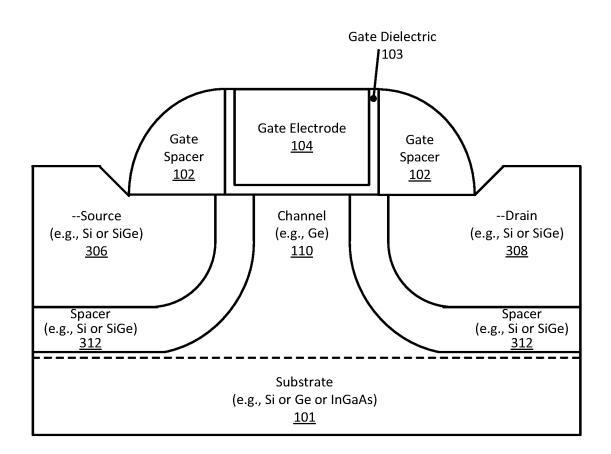

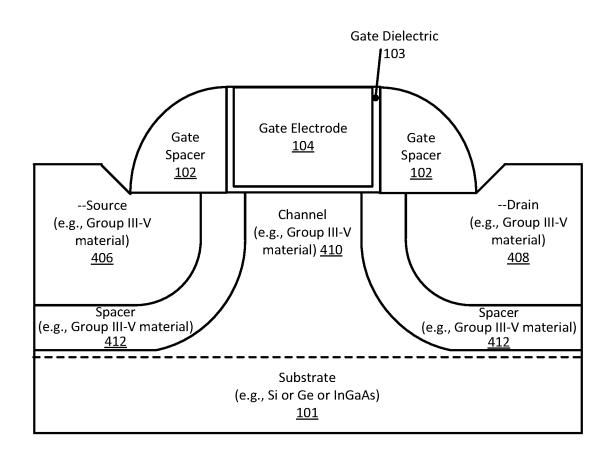

[0003] Figures 1a-1b each illustrates an example cross-sectional view of an integrated circuit transistor structure, configured in accordance with certain embodiments of the present disclosure.

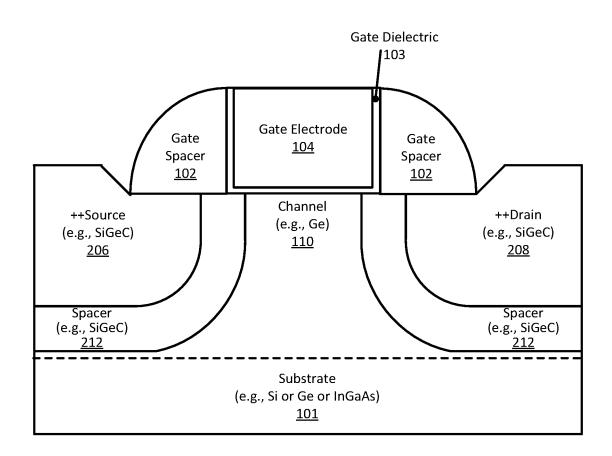

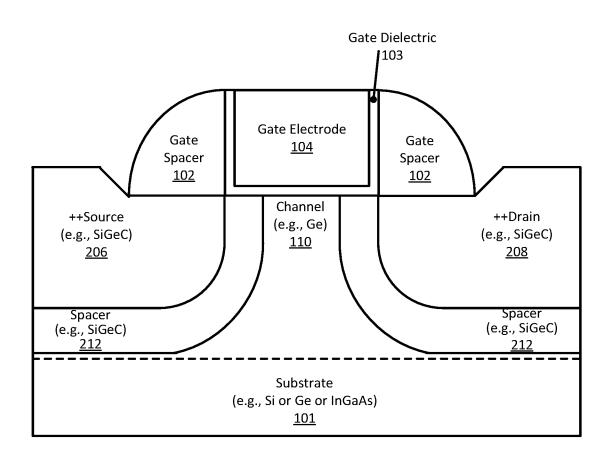

**[0004]** Figures 2a-2b each illustrates an example cross-sectional view of another integrated circuit transistor structure, configured in accordance with certain other embodiments of the present disclosure.

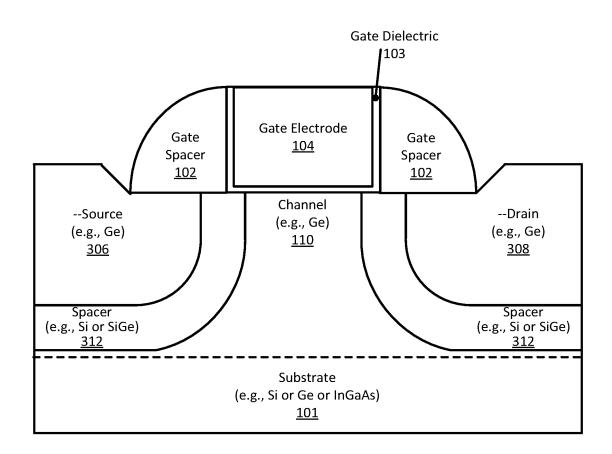

[0005] Figures 3a-3c each illustrates an example cross-sectional view of another integrated circuit transistor structure, configured in accordance with certain other embodiments of the present disclosure.

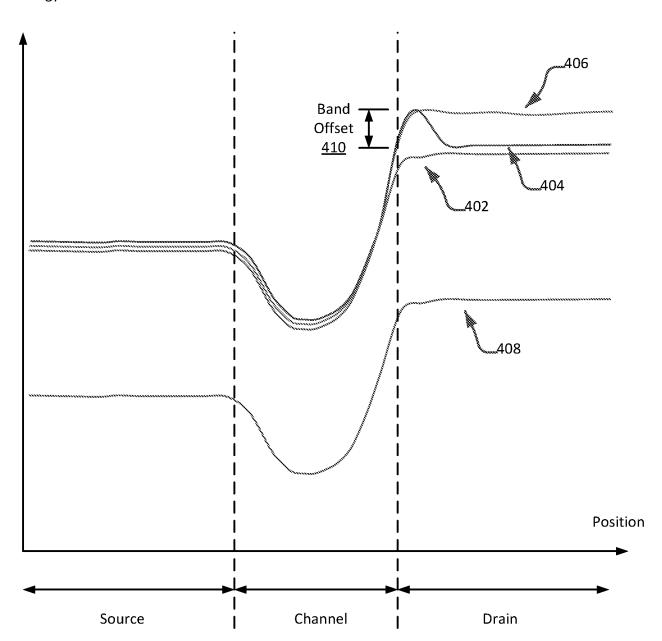

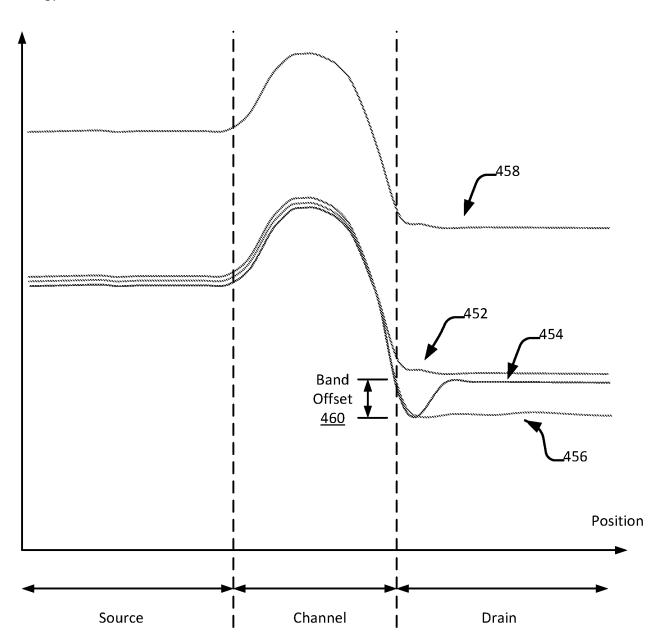

**[0006]** Figures 4a-4b each illustrates plots of conduction band energy and valence band energy, in accordance with example embodiments of the present disclosure.

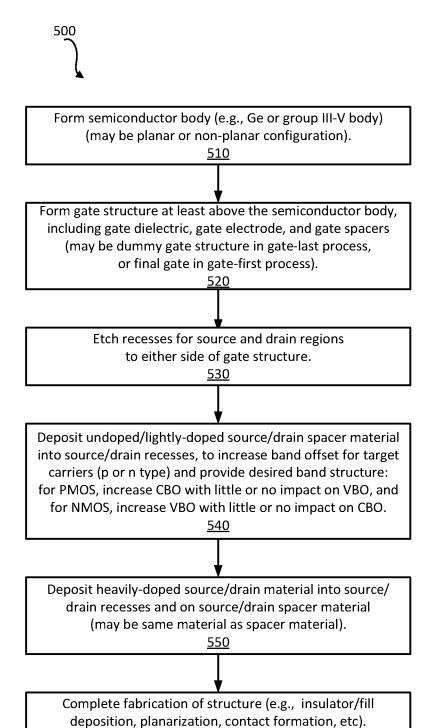

**[0007]** Figure 5 illustrates a method for forming an integrated circuit transistor structure to reduce band-to-band tunneling, in accordance with certain embodiments of the present disclosure.

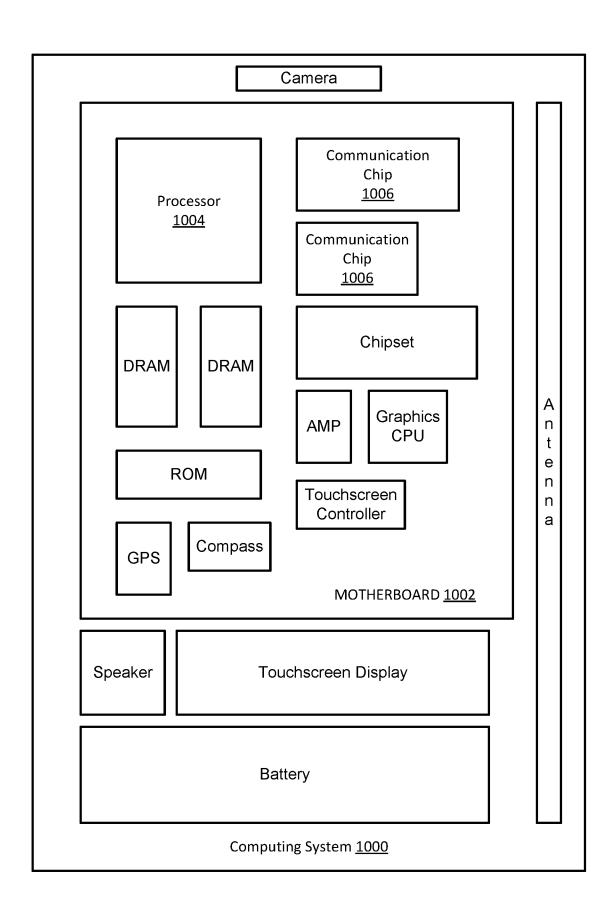

**[0008]** Figure 6 illustrates a computing system implemented with integrated circuit structures and/or transistor devices formed using the techniques disclosed herein, in accordance with some embodiments of the present disclosure.

[0009] Although the following Detailed Description will proceed with reference being made to illustrative embodiments, many alternatives, modifications, and variations thereof will be apparent in light of this disclosure.

## **DETAILED DESCRIPTION**

**[0010]** Techniques are disclosed for reducing band-to-band tunneling in integrated circuit transistor devices. The techniques can be implemented, for example, to reduce band-to-band tunneling between the channel region and the source/drain regions of the transistor or source-to-drain tunneling, without increasing the extrinsic resistance of the device, according to some embodiments. This may in turn improve device performance and efficiency, and lower the OFF-state current. The techniques include epitaxially providing undoped or lightly-doped

semiconductor spacers along with heavily-doped semiconductor materials in the source/drain regions. The source/drain semiconductor spacers are disposed in the source/drain recesses prior to deposition of the heavily-doped source/drain materials, such that the source/drain spacers are between the heavily-doped source/drain regions and the channel region. As will be appreciated in light of this disclosure, the semiconductor material of the source/drain spacers is selected so as to increase the band offset for the carriers that are conducting, without adversely impacting the other band. In an embodiment, the spacer includes a semiconductor material having a bandgap that is greater than the channel bandgap. So, for instance, in PMOS devices, the source/drain spacers comprise a semiconductor material that provides a relatively high conduction band offset (CBO) and a zero or otherwise relatively low valence band offset (VBO), and in NMOS devices, the source/drain spacers comprise a semiconductor material that provides a relatively high VBO and a zero or otherwise relatively low CBO. In some cases, the heavily-doped source/drain material is the same as the source/drain spacer material, except that the spacer material is undoped or only lightly-doped, relative to the subsequently deposited heavily-doped source/drain material. In such cases, note that the dopant can be adjusted by one or more process knobs in step-like or graded fashion, during one continuous source/drain epitaxial deposition process. In other cases, the heavily-doped source/drain material is compositionally distinct from the undoped or lightlydoped source/drain spacer material (i.e., the spacer material is compositionally different, in addition to being differently doped). In any such cases, the arrangement of selected materials provides a band structure configured to reduce the band-to-band tunneling without significant impact to the extrinsic resistance. Numerous configurations will be apparent in light of this disclosure.

# General Overview

**[0011]** As previously explained, band-to-band tunneling (BTBT) can cause a number of non-trivial issues. For instance, in the PMOS case of BTBT a hole tunnels from the drain to the channel, and in the NMOS case of BTBT an electron tunnels from the drain to the channel. This can create undesirable effects in the device, including an unacceptable degree of OFF-state current.

[0012] To this end, techniques are provided herein to reduce BTBT between the channel region and the source/drain region of transistors. Advantageously, the reduction in BTBT can be accomplished without adversely increasing the extrinsic resistance of the device, according to some embodiments. In an embodiment, an integrated circuit transistor structure

includes heavily-doped semiconductor material in the source/drain regions, but with an undoped/lightly-doped source/drain semiconductor spacer between the heavily-doped source/drain semiconductor material and the channel region. The source/drain spacer material is a semiconductor material that increases the band offset for the target carriers, such as a semiconductor material having a bandgap that is greater than the channel bandgap. So, for a PMOS device the source/drain spacer material inhibits tunneling from the valence band of the drain to the conduction band of the channel, and for an NMOS device the source/drain spacer material inhibits tunneling from the conduction band of the drain to the valence band of the channel. For example, in PMOS devices, the source/drain spacers comprise a semiconductor material that provides a relatively high CBO and a relatively low VBO. So, for instance, in some embodiments the semiconductor spacer material for a PMOS device provides a CBO of 0.1 eV or greater (e.g.,  $\geq$  150 meV, or  $\geq$  180 meV, or  $\geq$  200 meV) while simultaneously providing a VBO of less than 50 meV (e.g., -0.045 to 0.045 meV, or -0.035 to 0.035 meV, or -0.025 to 0.025 meV, or -0.015 to 0.015 meV, or -0.01 to 0.01 meV). On the other hand, for NMOS devices, the source/drain spacers comprise a semiconductor material that provides a relatively low CBO and a relatively high VBO. So, for instance, in some embodiments the semiconductor spacer material for an NMOS device provides a VBO of 0.1 eV or greater (e.g.,  $\geq$  150 meV, or  $\geq$  180 meV, or  $\geq$  200 meV) while simultaneously providing a CBO of less than 50 meV (e.g., -0.045 to 0.045 meV, or -0.035 to 0.035 meV, or -0.025 to 0.025 meV, or -0.015 to 0.015 meV, or -0.01 to 0.01 meV). Such selection criteria provide a desirable band structure.

[0013] Note that such band properties can be temperature dependent, and therefore can be measured at an appropriate temperature as will be appreciated. In some embodiments, for instance, the band properties discussed herein are measured at a temperature in the range of about 300 Kelvin (K), so about 300 +/- 5 K (e.g., 300 K or 302 K). Appropriate measurement temperature can vary from embodiment to the embodiment, and the present disclosure is not intended to be limited by temperature. As will be further appreciated, offsets may be scaled based on the measurement temperature.

[0014] In some example cases, the source/drain spacer material is the same as the heavily-doped source/drain material (e.g., dopant concentration in excess of 1E18cm<sup>3</sup>), except that the source/drain spacer material is undoped or only lightly-doped (e.g., dopant concentration of less 1E18cm<sup>3</sup>). For instance, in one such example embodiment having a germanium channel region, boron-doped silicon germanium carbon (b-doped SiGe:C) is used for the

heavily-doped source/drain material, and the same SiGe:C compound is used in an undoped/lightly-doped state (no or relatively low boron concentration) for the source/drain spacers. In some such cases, the germanium concentration is in the range of 80 to 90 atomic percent. In other example cases, the heavily-doped source/drain material is compositionally distinct from the source/drain spacer material (i.e., beyond just being differently doped). For example, in one such embodiment having a germanium channel region, boron-doped germanium is used for the heavily-doped source/drain material, and undoped/lightly-doped SiGe:C having a germanium concentration in the range of 80 to 90 atomic percent is used for the source/drain spacers. Note that the carbon is included with a colon because it is a relatively small amount, relative to the silicon and germanium (e.g., 4 atomic percent or less). To this end, the colon could be left out as well (SiGeC).

[0015] As previously noted, the source/drain spacers are either undoped or lightly-doped, relative to the highly-doped source/drain regions. A highly-doped source/drain material may be, for example, a p-doped semiconductor having a germanium concentration in range of 80 to 100 atomic percent and a boron concentration in excess of 1E18cm³ or 1E20cm³ or 1E21cm³ or 2E21cm³, according to some embodiments. In contrast, an undoped or lightly-doped source/drain spacer material may be, for example, p-doped SiGe:C having a germanium concentration in the range of 80 to 90 atomic percent and a boron concentration of less than 1E18cm³ or 1E17cm³ or 1E16cm³, according to some embodiments. Similar dopant concentration can be applied to n-doped transistor devices as well. As will be appreciated in light of this disclosure, any number of materials and doping schemes can be used in conjunction with source/drain spacers that meet the selection criteria as variously provided herein with respect to band structure.

[0016] As will be further appreciated, the concentrations of the elements making up the spacer can vary from one embodiment to the next. For instance, in some embodiments having source/drain spacers comprising SiGe:C, those spacers include 10 to 16 atomic percent silicon, 80 to 90 atomic percent germanium, and 1 to 4 atomic percent carbon. In a more general sense, a PMOS transistor configuration having a germanium channel according to an embodiment herein can be implemented with any material system arranged to provide a highly-doped semiconductor source/drain region in conjunction with an undoped/lightly-doped source/drain semiconductor spacer material that provides a CBO of 0.1 eV or greater and a VBO of less than 0.04eV (e.g., -0.04 eV < VBO < +0.04 eV). Note that these offsets (CBO and VBO) of the source/drain spacer are relative to the channel region. In any such

PMOS cases, the high CBO of the selected source/drain semiconductor spacer material provides an increased energy gap at the channel/drain boundary which reduces or prevents BTBT, while the low VBO ensures that the extrinsic resistance of the device remains low, as will be explained herein. In a similar fashion, an NMOS transistor configuration having a germanium or group III-V material channel according to an embodiment herein can be implemented with any material system arranged to provide a highly-doped semiconductor source/drain region in conjunction with a undoped/lightly-doped semiconductor source/drain spacer material that provides a VBO of 0.1 eV or greater and a CBO of less than 0.04eV (e.g., 0.0 eV +/- 0.04 eV). In any such NMOS cases, the high VBO of the selected source/drain semiconductor spacer material provides an increased energy gap at the channel/drain boundary which reduces or prevents BTBT, while the low CBO ensures that the extrinsic resistance of the device remains low, as will be explained herein.

[0017] In accordance with an embodiment, a methodology to implement these techniques includes forming a semiconductor body and a gate structure at least on that semiconductor body, thereby defining a channel region in the body underneath the gate structure. The semiconductor body can be planar or non-planar (e.g., FinFET or nanowire channel configuration), and in some embodiments is germanium. The gate structure is disposed at least above the semiconductor body (in planar devices), but may further be disposed on opposing sidewalls of the semiconductor body (in FinFET devices) or completely surrounding the semiconductor body (in nanowire devices). The gate structure includes a gate dielectric, gate electrode, and gate spacers, and may be implemented in a gate-first or gate-last process. Note that the gate dielectric may include a high-k gate dielectric, in some embodiments. The method further includes etching source and drain recesses adjacent to the gate structure, such that the source/drain recesses undercut the gate structure. Thus, each source/drain recess extends vertically down into the substrate or semiconductor body upon which it is being formed as well as laterally underneath the gate spacers and gate electrode (and gate dielectric). The undoped/lightly-doped source/drain semiconductor spacer (S/D spacer) material is then deposited into the source/drain recesses, at least proximate the channel region, followed by a deposition of heavily-doped source/drain material. Note this deposition process can be a continuous process where the dopant concentration is graded or stepped from about zero during the S/D spacer portion of the deposition to in excess of say 1E18cm<sup>3</sup> for the bulk of the highly-doped S/D portion. As will be further appreciated, the thickness of the S/D spacer material deposition can vary, but in some embodiments is in the

range of 3 nm to 50 nm (e.g., 5 to 30 nm, or 5 to 25 nm, or 5 to 20 nm, or 3 to 10 nm). In some such cases, the thickness of the S/D spacer material deposition makes up about 25% or less of the overall thickness of the total S/D structure (the overall thickness including the undoped/lightly-doped S/D spacer and the highly-doped source/drain portion), and the highly-doped S/D material makes up about 50% to 95% of the overall thickness of the S/D structure. Further note that the highly-doped S/D material deposition may be used to form so-called raised S/D regions, such that the S/D regions extend beyond (above) the recess opening and are taller than the channel region therebetween. In addition, recall that, for PMOS transistor devices, the S/D spacer semiconductor material is selected to provide a relatively high CBO (e.g., exceeding 150 or 180 mEV) and a relatively low VBO (e.g., 0 eV, +/-0.025 eV), and for NMOS transistor devices, the S/D spacer semiconductor material is selected to provide a relatively high VBO (e.g., exceeding 150 or 180 mEV) and a relatively low CBO (e.g., 0 eV, +/-0.025 eV). Numerous PMOS and NMOS transistor structures meeting these criteria can be formed.

## Architecture

[0018] The transistor structures provided herein can be implemented with any number of material systems that meet the criteria provided herein with respect to the channel and source and/or drain materials. In some embodiments the channel and source and/or drain materials are group IV semiconductor materials (e.g., silicon, germanium, SiGe, SiGe:C), while in other embodiments the channel and source and/or drain materials are group III-V semiconductor materials (e.g., indium aluminum arsenide - InAlAs, indium arsenic phosphide - InAsP, indium gallium phosphide - InGaAsP, gallium antimonide - GaSb, gallium aluminum antimonide - GaAlSb, indium gallium antimonide - InGaSb, indium gallium phosphorus antimonide - InGaPSb, indium gallium antimonide - InGaSb, indium gallium arsenide - InGaAs, and indium arsenide - InAs, or other group III-V semiconductor materials or compounds). Figures 1a-b, 2a-b, 3a-b and Table 1 illustrate various example group IV semiconductor embodiments, and Figure 3c and Table 2 illustrate various example group III-V semiconductor embodiments.

**[0019]** Figures 1a and 1b each illustrates an example cross-sectional view of an integrated circuit transistor structure, in accordance with certain embodiments of the present disclosure. As can be seen, each of the example structures 100 and 100' shows a PMOS transistor device that includes a semiconductor substrate 101 and a semiconductor body that includes channel region 110. A gate stack or structure is formed over the channel region 110 and includes a

gate dielectric 103 and a gate electrode 104. In addition, gate spacers 102 are provided to either side of the gate stack. As can be further seen, a source recess has been filled with a combination of an undoped/lightly-doped source/drain spacer 112 and a highly-doped source region 106, and a drain recess has been filled with a combination of an undoped/lightlydoped source/drain spacer 112 and a highly-doped drain region 108. Other transistor features, such as the source and drain contacts and insulator fill material, local interconnect, and interconnect/metal layers, are not shown but will be readily apparent in light of this disclosure. As will be further appreciated in light of this disclosure, the spacers 112 operate in conjunction with the source region 106 and the drain region 108 to provide an overall band structure or scheme (with respect to the channel region) configured to reduce band-to-band tunneling without adversely affecting the extrinsic resistance of the transistor structure 100 or 100'. As will be further appreciated, note that the cross-section shown may be either a planar channel architecture or a non-planar channel architecture. For instance, for a non-planar finbased or nanowire channel structure, the cross-section shown is taken through and parallel to the fin/semiconductor body (and perpendicular to the gate). Due to the nature of the crosssection, the multiple sides of the gate structure about the non-planar semiconductor fin/body cannot be seen, but again will be readily apparent to those skilled in the art.

**[0020]** The substrate 101 can be any suitable semiconductor substrate, such as a bulk silicon, or bulk germanium or bulk group III-V material (e.g., indium gallium arsenide - InGaAs, or gallium arsenide - GaAs) substrate. Alternatively, the substrate 101 may be a multilayer structure, such as a semiconductor-on-insulator configuration (e.g., germanium-on-oxide, or GaAs-on-oxide), or a first semiconductor layer (e.g., germanium) on a second semiconductor layer (e.g., silicon or SiGe layer). In a more general sense, any number of substrate configurations can be used, and the present disclosure is not intended to be limited to any particular type.

[0021] Note that the channel region 110 may be native to the substrate 101 (i.e., the channel region 110 is made from and part of the substrate 101), but may also be compositionally different from the underlying substrate (e.g., a germanium fin or body 110 on an InGaAs substrate 101). This optional compositional difference is generally depicted in the figures as a dashed line between the channel region 110 and the substrate 101. In some such embodiments, the compositionally different semiconductor fin or body that will ultimately include channel region 110 is epitaxially grown from trenches after removal of sacrificial native fins, in a so-called aspect ratio trapping (ART) based fin forming process.

Example ART-based semiconductor fin forming techniques are provided, for instance, in U.S. Patent Application Publication 2014/0027860. In some such ART-based cases, the replacement fin material is provided as alternating layers of desired channel material and sacrificial/inactive material such as described in U.S. Patent Application Publication 2016/0260802. Such multilayer fins are particularly useful for forming nanowire transistors (e.g., during final gate processing, prior to deposition of final gate materials). In some ART-based cases, a first set of fins or wires is formed with a first semiconductor material system (e.g., for p-type devices), and a second set of fins or wires is formed with a second semiconductor material system (e.g., for n-type devices). Any number of fin forming processes can be used in the context of the present disclosure, so long as a suitable band structure as variously described herein can be provisioned so as to mitigate or otherwise reduce band-to-band tunneling.

[0022] The gate structure can be implemented with any suitable processes and materials. For instance, the gate structure may have been formed during a replacement metal gate process (or so-called gate-last process) where dummy gate materials are initially provisioned and then removed later in the process to make way for the final gate materials. Alternatively, the gate structure can be formed during a so-called gate-first process where the desired final gate materials are provided earlier in the process. In the embodiment shown, the gate dielectric 103 is provided between the gate spacers 102 and gate electrode 104, so as to provide a u-shape in the cross-section shown. In other embodiments, however, the gate dielectric is only between the gate electrode 104 and the channel region 110, such that the gate spacers may be in direct contact with opposing sidewalls of the gate electrode 104. The gate stack may further include a hard mask on top of the gate electrode (and any exposed gate dielectric). Any number of gate stack configurations can be used.

[0023] The gate spacers 102 may be, for example, silicon nitride or silicon dioxide. The gate dielectric 103 may be, for example, any suitable gate dielectric material such as silicon dioxide or high-k gate dielectric materials. Examples of high-k gate dielectric materials include, for instance, hafnium oxide, hafnium silicon oxide, lanthanum oxide, lanthanum aluminum oxide, zirconium oxide, zirconium silicon oxide, tantalum oxide, titanium oxide, barium strontium titanium oxide, barium titanium oxide, strontium titanium oxide, yttrium oxide, aluminum oxide, lead scandium tantalum oxide, and lead zinc niobate. In some embodiments, an annealing process may be carried out on the gate dielectric 103 to improve its quality when a high-k material is used. Further, the gate electrode 104 may comprise a

wide range of materials, such as polysilicon, silicon nitride, silicon carbide, or various suitable metals or metal alloys, such as aluminum, tungsten, titanium, tantalum, copper, titanium nitride, or tantalum nitride, for example.

[0024] In some embodiments, the gate dielectric and/or gate electrode may include a multilayer structure of two or more material layers or components. For instance, in one such embodiment, the gate dielectric is a bi-layer structure having a first dielectric material (e.g., silicon dioxide) in contact with the channel region and a second dielectric material (e.g., hafnium oxide) in contact with the first dielectric material, the first dielectric material having a dielectric constant that is lower than the dielectric constant of the second dielectric material. Likewise, the gate electrode structure may include a central metal plug portion (e.g., tungsten) with one or more outer work function layers and/or barrier layers (e.g., tantalum, tantalum nitride), and/or a resistance reducing cap layer (e.g., copper, gold). In some embodiments, the gate dielectric and/or gate electrode may include grading (increasing or decreasing, as the case may be) of the concentration of one or more materials therein. Numerous different gate structure configurations can be used, as will be apparent in light of this disclosure.

[0025] In some embodiments fabricated using a gate-last process, the source/drain recesses are formed adjacent the channel region 110, after a dummy gate stack is provided (e.g., polysilicon gate electrode 104, silicon dioxide gate dielectric 103, and silicon nitride gate spacers 102). In other embodiments having a gate-first process, however, the source/drain recesses may be formed adjacent the channel region, after that final gate stack is provided (e.g., tungsten gate electrode 104, hafnium dioxide gate dielectric 103, and silicon nitride gate spacers 102). In any case, note that the source drain recesses undercut the gate structure, such that the recesses extend under the gate spacers 102 as well as the gate electrode 104. Any suitable etch can be used, including wet and/or dry etches, isotropic and/or anisotropic etches, and selective etch schemes. The degree of the undercut will vary from one embodiment to the next, depending on factors such as the desired distance between the source recess and the drain recess (or lateral length of channel region 110) as well as the desired thickness of the spacer layers 112. In some cases, the thickness of the source layers 112 is less than 20% of the overall thickness of the source/drain structure (i.e. combined thickness of 112 and 106 for the source structure, and 112 and 108 for the drain structure), or less than 15%, or less than 10%, or less than 5%. Further note that, while the recesses shown in Figures 1a-1b provide a rounded profile proximate the channel region, other embodiments

may provide more faceted or angular source/drain recesses, depending on factors such as the crystal orientation of the channel material and the etch process employed, as will be appreciated.

[0026] The source/drain spacers 112 are deposited into the recesses first (prior to the heavily-doped source/drain regions 106/108), so as to effectively provide a BTBT inhibiter between the channel region 110 and the respective source region 106 and drain region 108. As previously explained, the spacers 112 comprise a semiconductor material selected to effectively increase the band offset for the target carriers (i.e., either holes for PMOS devices or electrons for NMOS devices). So, for PMOS devices like this example embodiment, the spacer 112 material selected has a relatively high CBO and a zero or otherwise relatively low VBO. As will be appreciated, these offsets (CBO and VBO) of the spacer 112 are relative to the channel region 110. In an embodiment, the spacer material has a bandgap that is greater than the bandgap of the channel material. In any such cases, the spacer 112 material selected may also be amenable to doping to provide a desired level of conductivity and/or polarity, particularly in embodiments where that same material is used in the heavily-doped source/drain regions 106/108.

[0027] In some embodiments, the source/drain semiconductor spacer material is selected for a PMOS device such that the CBO exceeds a threshold value of at least 150 millielectronvolts (meV) or at least 180 meV, and the VBO is less than a threshold value of 20 meV or less than 10 meV or less than 5 meV (or otherwise relatively close to 0 meV). In some such embodiments having a germanium channel region, the selected semiconductor material for the spacer 112 is silicon-germanium-carbon (SiGe:C), although other semiconductor materials that exhibit the aforementioned desired characteristics may also be used. In some such embodiments, the selected semiconductor spacer material composition may be one of, or otherwise comparable to, the following: Si<sub>0.16</sub>Ge<sub>0.80</sub>C<sub>0.04</sub>, Si<sub>0.15</sub>Ge<sub>0.83</sub>C<sub>0.02</sub>, Si<sub>0.14</sub>Ge<sub>0.85</sub>C<sub>0.01</sub>, Si<sub>0.13</sub>Ge<sub>0.85</sub>C<sub>0.02</sub>, Si<sub>0.11</sub>Ge<sub>0.88</sub>C<sub>0.01</sub>, or Si<sub>0.10</sub>Ge<sub>0.89</sub>C<sub>0.01</sub>. Other example embodiments will be apparent such as any of those having a germanium concentration in the range of about 80 to 90 atomic percent, a silicon concentration in the range of about 1 to 4 atomic percent.

[0028] In some such embodiments having SiGe:C spacers 112, the channel can be, for example, bulk germanium (undoped/lightly-doped), and the source/drain regions 106/108 are boron-doped germanium or SiGe or SiGe:C having a germanium concentration that is different from the spacers 112. The underlying substrate can be any number of materials,

such as silicon, Ge, SiGe, or InGaAs, to name a few examples. In embodiments of this first example, as illustrated in Figure 1a, the spacers 112 are either undoped or relatively lightly-doped in comparison to the source region 106 and drain region 108, which are relatively more heavily-doped. If doped at all, the doping of the spacers 112 may be, for example, one or more orders of magnitude lower than the heavily-doped source drain regions 106 and 108.

[0029] As shown in the example embodiment of Figure 1a, the spacers 112, are disposed under the gate electrode 104. Note that the spacers 112 need not align to the gate spacer 102. In Figure 1b, however, the spacers 112 are aligned to the gate spacer 102. Such alignment is not needed; rather, any degree overlap between the source/drain spacers 112 and the gate electrode 104 and/or gate dielectric 103 can help mitigate BTBT. In embodiments where the gate dielectric 103 is also disposed on sidewalls of the gate 104, the spacers 112 may only be under the gate dielectric 103. The distance of the overlap can vary from embodiment to embodiment, but in some cases is in the range of 0.1 nm to 5 nm of overlap between the gate electrode 104 and/or gate dielectric 103 and each source/drain spacer 112. Note that, because the source/drain spacers 112 under the gate electrode 104 and/or gate dielectric 103 are lightly doped or undoped, most of the band bending will happen in the lightly/undoped regions and it is desired that the band bending occur in the region with high offsets.

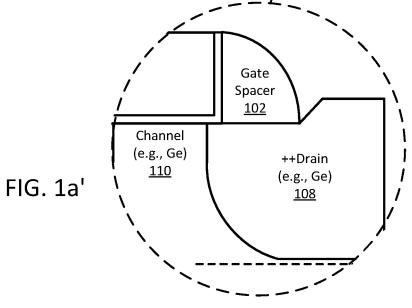

[0030] Figure 1a' shows alternate embodiments to any of the embodiments provided herein, although shown in the context of Figure 1a. In particular, note that both the source and drain regions need not have a spacer as provided herein; rather, in some embodiments only the source region includes the spacer and the drain region is a regular drain structure, while in other embodiments only the drain region includes the spacer and the source region is a regular source structure. The same alternate embodiments can be applied to any of the embodiments discussed herein with respect to Figures 1b, 2a-b, and 3a-c, as well as the example methodology of Figure 5.

[0031] Figures 2a and 2b each illustrates an example cross-sectional view of another integrated circuit transistor structure, in accordance with certain embodiments of the present disclosure. As can be seen, the structures 200 and 200' are similar to the structures 100 and 100', respectively, except that the highly-doped source and drain regions 206/208 are formed from the same semiconductor material selected for the undoped/lightly-doped spacers 212 (same semiconductor composition, but not counting the dopant concentration). So for example, for purposes of this particular discussion, undoped/lightly-doped SiGe:C and heavily-doped SiGe:C having the same germanium-silicon-carbon concentrations may be

considered compositionally the same despite having different boron concentrations, while undoped/lightly-doped SiGe:C and heavily-doped SiGe are compositionally different. Regarding the similarities between Figures 1a-b and 2a-b, the previous relevant discussion with respect to the gate structure (including gate electrode 104, gate dielectric 103, and gate spacers 102), channel region 110, and substrate 101 is equally applicable here.

[0032] In some such example embodiments, both the source/drain spacers 212 and the source/drain regions 206/208 are formed from SiGe:C for PMOS devices. However, the source/drain regions 206/208 are heavily-doped SiGe:C relative to the undoped/lightly-doped SiGe:C spacer 212. As previously explained, the spacers 212 are deployed to separate the source region 206 and drain region 208 from the channel region 110 to inhibit BTBT. In an embodiment, the spacer material has a bandgap that is greater than the bandgap of the channel material (or simply, channel bandgap).

[0033] As shown in the example embodiment of Figure 2a, the source/drain spacers 212, are disposed under the gate electrode 204, but do not need to align with the gate spacers 202. Just as explained with respect to Figures 1a-b, the source/drain spacers 212 need not align to gate spacers 202. In the example embodiment of Figure 2b, source/drain spacers 212 are aligned to gate spacer 202. The previous relevant discussion with respect to the degree of overlap between the source/drain spacers 112 and gate electrode 104 and/or gate dielectric 103 is equally applicable here.

[0034] Figures 3a and 3b each illustrates an example cross-sectional view of an integrated circuit transistor structure, in accordance with still other embodiments of the present disclosure. As can be seen, each of the example structures 300 and 300' shows a NMOS transistor device that includes a semiconductor substrate 101 and a semiconductor body that includes channel region 110. A gate stack or structure is formed over the channel region 110 and includes a gate dielectric 103 and a gate electrode 104. In addition, gate spacers 102 are provided to either side of the gate stack. As can be further seen, a source recess has been filled with a combination of an undoped/lightly-doped source/drain spacer 312 and a highly-doped source region 306, and a drain recess has been filled with a combination of an undoped/lightly-doped source/drain spacer 312 and a highly-doped drain region 308. Regarding the similarities between Figures 1a-b and 3a-b, the previous relevant discussion with respect to the gate structure (including gate electrode 104, gate dielectric 103, and gate spacers 102), channel region 110, and substrate 101 is equally applicable here.

[0035] The source/drain spacers 312 are deposited into the recesses first, so as to effectively provide a BTBT inhibiter between the channel region 110 and the respective source region 306 and drain region 308. As previously explained, the spacers 312 comprise a semiconductor material selected to effectively increase the band offset for the target carriers (i.e., either holes for PMOS devices or electrons for NMOS devices). So, for NMOS devices such as this example embodiment, the spacer 312 material selected has a relatively high VBO and a zero or otherwise relatively low CBO. As will be appreciated, these offsets (CBO and VBO) of the spacer 312 are relative to the channel region 110. In an embodiment, the spacer material has a bandgap that is greater than the bandgap of the channel material. In any such cases, the spacer 312 material selected may also be amenable to doping to provide a desired level of conductivity and/or polarity, particularly in embodiments where that same material is used in the heavily-doped source/drain regions 306/308.

[0036] In some embodiments, the source/drain semiconductor spacer material is selected for an NMOS device such that the VBO exceeds a threshold value of at least 150 millielectronvolts (meV) or at least 180 meV, and the CBO is less than a threshold value of 10 meV or less than 5 meV (or otherwise relatively close to 0 meV). In some such embodiments having a germanium channel region, the selected semiconductor material for the spacer 312 is silicon germanium (SiGe) or silicon, although other semiconductor materials that exhibit the aforementioned desired characteristics may also be used. In some such embodiments, the selected semiconductor spacer 312 material composition may be one of, or otherwise comparable to, the following:  $Si_{0.80}Ge_{0.20}$ ,  $Si_{0.85}Ge_{0.15}$ ,  $Si_{0.87}Ge_{0.13}$ , or  $Si_{0.90}Ge_{0.10}$ . example embodiments will be apparent such as any of those having a silicon concentration in the range of about 80 to 90 atomic percent, and a germanium concentration in the range of about 10 to 20 atomic percent. In still other embodiments, the source/drain spacers 312 can be all silicon. In some such embodiments having undoped or lightly-doped SiGe or silicon spacers 312, the channel can be, for example, bulk germanium (undoped/lightly-doped), and the heavily-doped source/drain regions 306/308 are phosphorus-doped germanium as shown in the example embodiment of Figure 3a. In other such example embodiments, the heavilydoped source/drain regions 306/308 are the same materials as the source/drain spacer 312 (except for the doping, as will be appreciated), as shown in Figure 3b.

[0037] Table 1 illustrates a number of specific example embodiments for both PMOS and NMOS configurations, using Group IV semiconductor material systems including silicon and germanium. As will be appreciated with respect to Table 1, polarity doping for p-type

source/drain regions (PMOS devices) is indicated as the first component in a given material followed by a colon. For instance, example p-type dopants for group IV source/drain materials include boron, gallium, and aluminum, to name a few types. So, for example, a boron-doped germanium source or drain region is represented as B:Ge, and a lightly-doped boron SiGe:C source spacer or drain spacer is represented as B:SiGe:C. Likewise, example n-type dopants for group IV source/drain materials (NMOS devices) include phosphorus, arsenic, and antimony, to name a few types. So, for example, a phosphorus-doped silicon source or drain region is represented as P:Si, and a lightly-doped phosphorus SiGe:C source spacer or drain spacer is represented as P:SiGe:C. As will be further appreciated with respect to Table 1, although the channel is indicated as undoped in each of the examples, in still other embodiments the channel of any of these examples may be lightly-doped (either p-type or ntype, depending on factors such as desired performance, transistor type, and mode of operation). Also, if the atomic percentage of a given component of a semiconductor material is provided as a range, then expressly stated example embodiments include compounds/alloys having any weight value within that given range. For example, a source/drain spacer  $Si_xGe_y$ :  $C_z$  wherein  $8 \le x \le 16$ ,  $80 \le y \le 90$ , and  $1 \le z \le 4$ , then various example embodiments include any SiGe:C alloy that is fully represented (not including dopant, if present, to provide n-type/p-type polarity) by: any first atomic percentage of silicon in the range of 8 to 16 atomic percent, any second atomic percentage of germanium in the range of 80 to 90 atomic percent, and any third atomic percentage of carbon in the range of 1 to 4 atomic percent, wherein the first, second, and third atomic percentages equal 100 percent. Numerous variations in material systems and alternative embodiments will be appreciated in light of this disclosure.

| PMOS<br>NMOS | <u>S/D</u><br><u>Spacer</u>                       | <u>S/D</u><br><u>Region</u> | Channel | <u>Notes</u>                                                                                                                                                                                                                                 |

|--------------|---------------------------------------------------|-----------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PMOS         | Si <sub>x</sub> Ge <sub>y</sub> :C <sub>z</sub>   | B:Ge                        | Ge      | Different composition for S/D spacer and S/D region. For example: $8 \le x \le 16$ ; $80 \le y \le 90$ ; $1 \le z \le 4$ ; $x+y+z=100$ ; Also, S/D spacer is undoped, while S/D region is heavily-doped with boron (B).                      |

| PMOS         | B:Si <sub>x</sub> Ge <sub>y</sub> :C <sub>z</sub> | B:Ge                        | Ge      | Different composition for S/D spacer and S/D region. For example: $8 \le x \le 16$ ; $80 \le y \le 90$ ; $1 \le z \le 4$ ; $x+y+z=100$ ; Also, S/D spacer is lightly-doped with boron (B), while S/D region is heavily-doped with boron (B). |

| PMOS | Si <sub>x</sub> Ge <sub>y</sub> :C <sub>z</sub>   | B:Si <sub>1-a</sub> Ge <sub>a</sub>               | Ge | Different composition for S/D spacer and S/D region. For example: $8 \le x \le 16$ ; $80 \le y \le 90$ ; $1 \le z \le 4$ ; $x+y+z=100$ ; $0.75 \le a \le 0.99$ ; Also, S/D spacer is undoped, while S/D region is heavily-doped with boron (B).                      |

|------|---------------------------------------------------|---------------------------------------------------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PMOS | B:Si <sub>x</sub> Ge <sub>y</sub> :C <sub>z</sub> | B:Si <sub>1-a</sub> Ge <sub>a</sub>               | Ge | Different composition for S/D spacer and S/D region. For example: $8 \le x \le 16$ ; $80 \le y \le 90$ ; $1 \le z \le 4$ ; $x+y+z=100$ ; $0.75 \le a \le 0.99$ ; Also, S/D spacer is lightly-doped with boron (B), while S/D region is heavily-doped with boron (B). |

| PMOS | Si <sub>x</sub> Ge <sub>y</sub> :C <sub>z</sub>   | B:Si <sub>x</sub> Ge <sub>y</sub> :C <sub>z</sub> | Ge | Same composition for S/D spacer and S/D region. For example: $8 \le x \le 16$ ; $80 \le y \le 90$ ; $1 \le z \le 4$ ; $x+y+z=100$ ; Also, S/D region is heavily-doped with boron (B) and S/D spacer is undoped.                                                      |

| PMOS | B:Si <sub>x</sub> Ge <sub>y</sub> :C <sub>z</sub> | B:Si <sub>x</sub> Ge <sub>y</sub> :C <sub>z</sub> | Ge | Same composition for S/D spacer and S/D region. For example: $8 \le x \le 16$ ; $80 \le y \le 90$ ; $1 \le z \le 4$ ; $x+y+z=100$ ; Also, S/D spacer is lightly-doped with boron (B), while S/D region is heavily-doped with boron (B).                              |

| NMOS | Si <sub>x</sub> Ge <sub>y</sub>                   | P:Si<br>or<br>P:Ge                                | Ge | Different composition for S/D spacer and S/D region. For example: $80 \le x \le 100$ ; $0 \le y \le 20$ ; $x+y=100$ ; Also, S/D spacer is undoped, while S/D region is heavily-doped with phosphorus (P).                                                            |

| NMOS | P:Si <sub>x</sub> Ge <sub>y</sub>                 | P:Si<br>or<br>P:Ge                                | Ge | Different composition for S/D spacer and S/D region. For example: $80 \le x \le 100$ ; $0 \le y \le 20$ ; $x+y=100$ ; Also, S/D spacer is lightly-doped with phosphorus (P), while S/D region is heavily-doped with phosphorus (P).                                  |

| NMOS | Si <sub>x</sub> Ge <sub>y</sub>                   | P:Si <sub>a</sub> Ge <sub>1-a</sub>               | Ge | Different composition for S/D spacer and S/D region. For example: $80 \le x \le 100$ ; $0 \le y \le 20$ ; $x+y=100$ ; $0.75 \le a \le 0.99$ ; Also, S/D spacer is undoped, while S/D region is heavily-doped with phosphorus (P).                                    |

| NMOS | P:Si <sub>x</sub> Ge <sub>y</sub> | P:Si <sub>a</sub> Ge <sub>1-a</sub> | Ge | Different composition for S/D spacer and S/D region. For example: $80 \le x \le 100$ ; $0 \le y \le 20$ ; $x+y=100$ ; $0.75 \le a \le 0.99$ ; Also, S/D spacer is lightly-doped with phosphorus (P), while S/D region is heavily-doped with phosphorus (P). |

|------|-----------------------------------|-------------------------------------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NMOS | Si <sub>x</sub> Ge <sub>y</sub>   | P:Si <sub>x</sub> Ge <sub>y</sub>   | Ge | Same composition for S/D spacer and S/D region. For example: $80 \le x \le 100$ ; $0 \le y \le 20$ ; $x+y=100$ ; Also, S/D region is heavily-doped with phosphorus (P) and S/D spacer is undoped.                                                           |

| NMOS | P:Si <sub>x</sub> Ge <sub>y</sub> | P:Si <sub>x</sub> Ge <sub>y</sub>   | Ge | Same composition for S/D spacer and S/D region. For example: $80 \le x \le 100$ ; $0 \le y \le 20$ ; $x+y=100$ ; Also, S/D region is heavily-doped with phosphorus (P) and S/D spacer is lightly-doped with phosphorus (P).                                 |

Table 1: Example Group IV Material Systems to Reduce BTBT

While Figures 1a through 3b refer to group IV semiconductor materials in the channel and source/drain regions, Figure 3c refers to group III-V semiconductor materials in the channel and source/drain regions, in accordance with still other embodiments of the present disclosure. As can be seen, each of the example structure 300" shows a NMOS transistor device that includes a semiconductor substrate 101 and a semiconductor body that includes channel region 410. A gate stack or structure is formed over the channel region 410 and includes a gate dielectric 103 and a gate electrode 104. In addition, gate spacers 102 are provided to either side of the gate stack. As can be further seen, a source recess has been filled with a combination of an undoped/lightly-doped source/drain spacer 412 and a highlydoped source region 406, and a drain recess has been filled with a combination of an undoped/lightly-doped source/drain spacer 412 and a highly-doped drain region 408. Generally speaking, the previous relevant discussion with respect to the transistor components and BTBT mitigation is equally applicable here, as will be appreciated. In a more general sense, different materials that will be apparent in light of this disclosure can be used for any of the various transistor components depicted, and the present disclosure is not intended to be limited to just the specific example embodiments provided herein.

[0039] Table 2 illustrates a number of specific example embodiments for NMOS configurations, using Group IV semiconductor material systems including silicon and

germanium. As will be appreciated with respect to Table 2, polarity doping for n-type or ptype source/drain regions is indicated as the first component in a given material followed by a colon, as explained with reference to Table 1. Example p-type dopants for group III-V source/drain materials include magnesium, beryllium, and carbon, and example n-type dopants for group III-V source/drain materials include silicon and tellurium. As will be further appreciated with respect to Table 2, although the channel is indicated as undoped in each of the examples, in still other embodiments the channel of any of these examples may be lightly-doped (either p-type or n-type, depending on factors such as desired performance, transistor type, and mode of operation). Also, if the atomic percentage of a given component of a semiconductor material is provided as a range, then expressly stated example embodiments include compounds/alloys having any weight value within that given range. For example, a source/drain spacer  $In_yAl_{1-y}As$  wherein  $0.60 \le y \le 1.00$ , then various example embodiments include any InAlAs compound that is fully represented (not including dopant, if present, to provide n-type/p-type polarity) by: any first atomic percentage of indium in the range of 60 to 100 atomic; and any second atomic percentage of aluminum in the range of 0 to 40 atomic percent germanium, wherein the first and second atomic percentages equal 100 percent. Further note that 0 atomic percent implies that particular element is not in the compound. Numerous variations in material systems and alternative embodiments will be appreciated in light of this disclosure.

| <u>NMOS</u> | S/D Spacer                              | S/D Region                              | <u>Channel</u>                       | <u>Notes</u>                                                                                                                                                                                                                        |

|-------------|-----------------------------------------|-----------------------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NMOS        | In <sub>y</sub> AI <sub>1-y</sub> As    | Si:In <sub>y</sub> AI <sub>1-y</sub> As | In <sub>x</sub> Ga <sub>1-x</sub> As | Same or different composition for S/D spacer and S/D region. For example: $0.51 \le x \le 0.55$ ; $0.60 \le y \le 1.00$ ; Also, S/D spacer is undoped, while S/D region is heavilydoped with silicon (Si).                          |

| NMOS        | Si:In <sub>y</sub> Al <sub>1-y</sub> As | Si:In <sub>y</sub> Al <sub>1-y</sub> As | In <sub>x</sub> Ga <sub>1-x</sub> As | Same or different composition for S/D spacer and S/D region. For example: $0.51 \le x \le 0.55$ ; $0.60 \le y \le 1.00$ ; Also, S/D spacer is lightly-doped with silicon (Si), while S/D region is heavily-doped with silicon (Si). |

| NMOS        | InAs <sub>y</sub> P <sub>1-y</sub>      | Si:InAs <sub>y</sub> P <sub>1-y</sub>   | In <sub>x</sub> Ga <sub>1-x</sub> As | Same or different composition for S/D spacer and S/D region.                                                                                                                                                                        |

|      |                                                                       | Γ                                                                     | I                                    | Τ                                                                                                                                                                          |

|------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                                                       |                                                                       |                                      | For example:                                                                                                                                                               |

|      |                                                                       |                                                                       |                                      | $0.51 \le x \le 0.55$ ; $0.10 \le y \le 1.00$ ;                                                                                                                            |

|      |                                                                       |                                                                       |                                      | Also, S/D spacer is undoped, while S/D region is heavilydoped with silicon (Si).                                                                                           |

| NMOS | Si:InAs <sub>y</sub> P <sub>1-y</sub>                                 | Si:InAs <sub>y</sub> P <sub>1-y</sub>                                 | In <sub>x</sub> Ga <sub>1-x</sub> As | Same or different composition for S/D spacer and S/D region. For example:                                                                                                  |

|      |                                                                       |                                                                       |                                      | $0.51 \le x \le 0.55$ ; $0.10 \le y \le 1.00$ ;                                                                                                                            |

|      |                                                                       |                                                                       |                                      | Also, S/D spacer is lightly-<br>doped with silicon (Si), while<br>S/D region is heavily-doped<br>with silicon (Si).                                                        |

| NMOS | In <sub>y</sub> Ga <sub>1-y</sub> As <sub>z</sub> P <sub>1-z</sub>    | Si:In <sub>y</sub> Ga <sub>1-y</sub> As <sub>z</sub> P <sub>1-z</sub> | In <sub>x</sub> Ga <sub>1-x</sub> As | Same or different composition for S/D spacer and S/D region. For example:                                                                                                  |

|      |                                                                       |                                                                       |                                      | $0.51 \le x \le 0.55;$                                                                                                                                                     |

|      |                                                                       |                                                                       |                                      | $0.25 \le y \le 1.00; 0.50 \le z \le 1.00;$                                                                                                                                |

|      |                                                                       |                                                                       |                                      | Also, S/D spacer is undoped, while S/D region is heavilydoped with silicon (Si).                                                                                           |

| NMOS | Si:In <sub>y</sub> Ga <sub>1-y</sub> As <sub>z</sub> P <sub>1-z</sub> | Si:In <sub>y</sub> Ga <sub>1-y</sub> As <sub>z</sub> P <sub>1-z</sub> | In <sub>x</sub> Ga <sub>1-x</sub> As | Same or different composition for S/D spacer and S/D region. For example:                                                                                                  |

|      |                                                                       |                                                                       |                                      | $0.51 \le x \le 0.55;$                                                                                                                                                     |

|      |                                                                       |                                                                       |                                      | $0.25 \le y \le 1.00; 0.50 \le z \le 1.00;$                                                                                                                                |

|      |                                                                       |                                                                       |                                      | Also, S/D spacer is lightly-<br>doped with silicon (Si), while<br>S/D region is heavily-doped<br>with silicon (Si).                                                        |

| NMOS | GaSb                                                                  | Mg:GaSb                                                               | InAs                                 | Same composition for S/D spacer and S/D region. Broken bandgap contact to channel, where the valence band of ptype S/D region is above the conduction band of the channel. |

|      |                                                                       |                                                                       |                                      | Also, S/D spacer is undoped, while S/D region is heavily-doped with magnesium (Mg).                                                                                        |

| NMOS | Mg:GaSb                                                               | Mg:GaSb                                                               | InAs                                 | Same composition for S/D spacer and S/D region. Broken bandgap contact to n-type                                                                                           |

|      |                                         |                                         |      | channel, where the valence band of p-type S/D region is above the conduction band of the channel.  Also, S/D spacer is lightly-doped with magnesium (Mg), while S/D region is heavily-doped with magnesium (Mg).                                                                                                                        |

|------|-----------------------------------------|-----------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NMOS | Ga <sub>x</sub> Al <sub>1-x</sub> Sb    | Mg:Ga <sub>x</sub> Al <sub>1-x</sub> Sb | InAs | Same or different composition for S/D spacer and S/D region. For example: 0.01 ≤ x ≤ 0.20; Broken bandgap contact to ntype channel, where the valence band of p-type S/D region is above the conduction band of the channel. Also, S/D region is heavily-doped with magnesium (Mg) and S/D spacer is undoped.                           |

| NMOS | Mg:Ga <sub>x</sub> Al <sub>1-x</sub> Sb | Mg:Ga <sub>x</sub> Al <sub>1-x</sub> Sb | InAs | Same or different composition for S/D spacer and S/D region. For example: 0.01 ≤ x ≤ 0.20; Broken bandgap contact to ntype channel, where the valence band of p-type S/D region is above the conduction band of the channel. Also, S/D region is heavily-doped with magnesium (Mg) and S/D spacer is lightly-doped with magnesium (Mg). |

| NMOS | In <sub>x</sub> Ga <sub>1-x</sub> Sb    | Mg:In <sub>x</sub> Ga <sub>1-x</sub> Sb | InAs | Same or different composition for S/D spacer and S/D region. For example: 0.25 ≤ x ≤ 1.00; Broken bandgap contact to ntype channel, where the valence band of p-type S/D region is above the conduction band of the channel. Also, S/D region is heavily-doped with magnesium (Mg) and S/D spacer is undoped.                           |

| NMOS | Mg:In <sub>x</sub> Ga <sub>1-x</sub> Sb | Mg:ln <sub>x</sub> Ga <sub>1-x</sub> Sb | InAs | Same or different composition for S/D spacer and S/D region.                                                                                                                                                                                                                                                                            |

|      |                                                                       |                                                                       |      | For example: 0.25 ≤ x ≤ 1.00; Broken bandgap contact to n- type channel, where the valence band of p-type S/D region is above the conduction band of the channel.                                                                |

|------|-----------------------------------------------------------------------|-----------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                                                       |                                                                       |      | Also, S/D region is heavily-doped with magnesium (Mg) and S/D spacer is lightly-doped with magnesium (Mg).                                                                                                                       |

| NMOS | In <sub>x</sub> Ga <sub>1-x</sub> P <sub>y</sub> Sb <sub>1-y</sub>    | Si:In <sub>x</sub> Ga <sub>1-x</sub> P <sub>y</sub> Sb <sub>1-y</sub> | GaSb | Same or different composition for S/D spacer and S/D region. For example: $0.25 \le x \le 1.00$ ; $0.00 \le y \le 0.10$ ; Also, S/D region is heavilydoped with silicon (Si) and S/D spacer is undoped.                          |

| NMOS | Si:In <sub>x</sub> Ga <sub>1-x</sub> P <sub>y</sub> Sb <sub>1-y</sub> | Si:In <sub>x</sub> Ga <sub>1-x</sub> P <sub>y</sub> Sb <sub>1-y</sub> | GaSb | Same or different composition for S/D spacer and S/D region. For example: $0.25 \le x \le 1.00$ ; $0.00 \le y \le 0.10$ ; Also, S/D region is heavily-doped with silicon (Si) and S/D spacer is lightly-doped with silicon (Si). |

Table 2: Example Group III-V Material Systems to Reduce BTBT

[0040] Note that the broken bandgap contact referred to for some examples of Table 2 means that the valence band of the spacer material being above the conduction band of the channel material. Since the valence band of the source/drain regions is above the conduction band of the channel, carriers can travel between the two materials with minimal (almost unmeasurable) or otherwise reduced resistance. This type of interface is sometimes referred to as a broken-gap heterostructure. So, while the other entries of Table 2 have n-type doped source/drain regions making contact to an n-type channel (meaning the channel is undoped or lightly-p-doped), these particular examples have p-type doped source/drain regions making contact to an n-type channel. Further note that in these particular cases, the transistors are still NMOS transistors, even though the source/drain regions are p-type doped, which is a property unique to broken bandgap materials.

[0041] Figure 4a shows a collection of plots 400 that illustrate conduction band energy and valence band energy for various PMOS transistor devices, some configured in accordance

with an embodiment of the present disclosure. Each of the three top plots 402, 404, 406 show conduction band energy as a function of position through the source region, channel region, and drain region (from left to right). The bottom plot 408 shows valence band energy as a function of position through the source region, channel region, and drain region (from left to right).

[0042] In more detail, plot 402 shows the conduction band energy for a standard integrated circuit transistor structure, that is to say a structure that does not employ source/drain spacers that facilitate a band structure as variously provided herein (e.g., in PMOS devices the source/drain spacers comprise a semiconductor material that provides a relatively high CBO and a relatively low VBO). Plot 404 shows the conduction band energy for the integrated circuit transistor structure illustrated in Figures 1a-b, as described above, which employs a lightly-doped SiGe:C spacer 112 between a germanium channel and heavily p-doped germanium source and drain regions 106, 108. Plot 406 shows the conduction band energy for the integrated circuit transistor structure illustrated in Figures 2a-b, as described above, which employs a lightly-doped SiGe:C spacer 210 between a germanium channel and heavily-doped SiGe:C source and drain regions 206, 208. The dopant is boron, but any number of dopants can be used, depending on desired polarity and desired conductivity.

[0043] As can be seen in a comparison of plots 404 and 406 relative to plot 402, the use of the SiGe:C semiconductor material provides an increased band offset, which corresponds to an increased conduction band offset (CBO) for the p-type carriers, which in turn eliminates or otherwise reduces undesirable tunneling (such as band-to-band tunneling from drain to channel, as well as source to the drain tunneling). Plot 408 shows the valence band energy which remains substantially the same for all three cases (e.g., standard device structure, SiGe:C spacer with germanium source/drain case, and SiGe:C for both spacer and source/drain case) at a relatively low level. This indicates that the extrinsic resistance of the transistor device does not materially increase with the use of SiGe:C spacers as provided in this example case.

**[0044]** Figure 4b shows a collection of plots 450 that illustrate conduction band energy and valence band energy for NMOS transistor devices, in accordance with certain embodiments of the present disclosure. Each of the three top plots 452, 454, 456 show valence band energy as a function of position through the source region, channel region, and drain region (from left to right). The bottom plot 458 shows conduction band energy as a function of position through the source region, channel region, and drain region (from left to right).

[0045] In more detail, plot 452 shows the valence band energy for a standard integrated circuit transistor structure, that is to say a structure that does not employ source/drain spacers that facilitate a band structure as variously provided herein (e.g., in NMOS devices the source/drain spacers comprise a semiconductor material that provides a relatively high VBO and a relatively low CBO). Plot 454 shows the valence band energy for the integrated circuit transistor structure illustrated in Figures 3a, as described above, which employs a lightly-doped SiGe spacer 312 between a germanium channel and heavily n-doped germanium source and drain regions 306, 308. Plot 456 shows the conduction band energy for the integrated circuit transistor structure illustrated in Figures 3b, as described above, which employs a lightly-doped SiGe spacer 312 between a germanium channel and heavily-doped SiGe source and drain regions 306, 308. The dopant is phosphorus, in this example case.

[0046] As can be seen in a comparison of plots 454 and 456 relative to plot 452, the use of the SiGe semiconductor material provides an increased band offset, which corresponds to an increased valence band offset (VBO) for the n-type carriers, which in turn eliminates or otherwise reduces undesirable tunneling (such as band-to-band tunneling from drain to channel, as well as source to the drain tunneling). Plot 458 shows the conduction band energy which remains substantially the same for all three cases (e.g., standard device structure, SiGe spacer with germanium source/drain case, and SiGe for both spacer and source/drain case) at a relatively low level. This indicates that the extrinsic resistance of the transistor device does not materially increase with the use of SiGe spacers as provided in this example case.

## Methodology

**[0047]** Figure 5 illustrates a method for fabricating or forming an integrated circuit transistor structure to reduce band-to-band tunneling, in accordance with certain embodiments of the present disclosure. As can be seen, the example method includes a number of phases and sub-processes, the sequence of which may vary from one embodiment to another. However, when considered in the aggregate, these phases and sub-processes form a process for creation of an integrated circuit transistor structure with reduced band-to-band tunneling in accordance with certain of the embodiments disclosed herein. Note that the methodology may be used with a gate-first process or a gate-last process. Numerous variations and alternative configurations will be apparent in light of this disclosure.

[0048] As illustrated in Figure 5, in an embodiment, method 500 for forming an integrated circuit transistor structure commences, at operation 510, by forming a semiconductor body,

for example from germanium or III-V material. The semiconductor body may be planar (for planar transistor architecture), such as a bulk substrate or blanket layer. Alternatively, the semiconductor body may be non-planar, such as a fin. In any such cases, a channel region can be manifested within the semiconductor body, as will be appreciated. Next, at operation 520, a gate structure is formed and disposed at least above the semiconductor body. As previously explained, the gate structure is disposed above the semiconductor body (in planar devices), but may further be disposed on opposing sidewalls of the semiconductor body (in FinFET devices) or completely surrounding the semiconductor body (in gate-all-around devices). In any such cases, the gate structure generally includes a gate dielectric, gate electrode, and opposing gate spacers as previously explained.

[0049] As previously noted, one example embodiment refers to a gate-first process at 520, where the final gate materials are provided prior to the source/drain structures being formed. However, in other example embodiments, dummy gate materials may be provided at 520, such as silicon dioxide for the dummy gate dielectric and polysilicon for the dummy gate electrode. In such cases, the dummy gate materials are effectively a place holder for the final gate material and can be removed later in the process, such as after the source/drain regions are formed at 550 and dielectric fill material has been provided and planarized down to the dummy gate stack. Once the dummy gate stack is isolated (by applying a protective mask over the source/drain structures and dielectric fill material), the exposed dummy gate materials can be removed with an appropriate etch scheme, and replaced with the final gate structure materials, which could be the same materials as provided in a gate-first process (e.g., a high-k gate dielectric such as hafnium oxide and a gate electrode such as a tungsten plug with one or more titanium and/or titanium nitride layers for work function tuning). The methodology may then continue at 560, as will be discussed in turn.

**[0050]** At operation 530, a source recess and a drain recess are formed to either side of the gate structure, so as to allow for formation respectively therein of source and drain structures (including undoped/lightly-doped source/drain spacers and heavily-doped source/drain regions). As previously explained, the source and drain recesses will each undercut at least one of the gate electrode and/or gate dielectric according to some embodiments, and may be provisioned using any number of suitable etching schemes, including wet and/or dry isotropic and/or anisotropic etches.

[0051] At operation 540, an undoped/lightly-doped source/drain spacer material is epitaxially deposited into each of the source/drain recesses formed at 530. As previously

explained, the source/drain spacer is configured to increase band offset for target carriers (p or n type) and provide desired band structure: for PMOS, increase CBO with little or no impact on VBO, and for NMOS, increase VBO with little or no impact on CBO. As such, the channel region of the semiconductor body will be separated from the forthcoming heavily-doped source and drain regions by the respective source/drain spacers.

[0052] At operation 550, heavily-doped source/drain material is epitaxially deposited into the source/drain recesses and at least partially on the source/drain spacer material provided at 540. Note that, in some embodiments, the heavily-doped source/drain material may be the same material as the undoped/lightly-doped spacer material, while in other embodiments the heavily-doped source/drain material is a compositionally different from the undoped/lightly-doped spacer material. As previously explained, compositionally different is intended to mean that the heavily-doped source/drain material is different from the undoped/lightly-doped spacer above and beyond any difference in polarity-based doping provisioned for purposes of configuring a p-type device or an n-type device.

[0053] In some embodiments, the semiconductor material selected for the source/drain spacers is undoped or lightly-doped silicon-germanium-carbon, for PMOS devices having a germanium channel, or undoped or lightly-doped silicon-germanium, for NMOS devices having a germanium channel. In other embodiments, the semiconductor material selected for the source/drain spacers is undoped or lightly-doped indium aluminum arsenide, for NMOS devices having an indium gallium arsenide channel. Tables 1 and 2 describe a number of other example embodiments for group IV and group III-V source/drain spacer materials. In any such embodiments, the heavily-doped source/drain regions may be the same composition (but be heavily-doped with the desired impurity), or alternatively may be compositionally different as explained herein.

[0054] Note that one or more of the components of the source/drain structures provided herein may be graded. In such cases, the S/D structure may include one or more graded buffers or graded sections. In some such cases, there may be a bulk portion between the graded portions, the bulk portion having a relatively fixed composition. Any number of grading schemes can be used.

[0055] At 560, the structure can be completed using standard or proprietary fabrication techniques, which may include, for example, provisioning of fill materials, planarization, contact structure formation, etc. One or more interconnect layers may be formed on a device

layer including the transistors formed as provided herein. Numerous integrated circuit structures can be fabricated to include such transistors.