### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第4425301号 (P4425301)

(45) 発行日 平成22年3月3日(2010.3.3)

(24) 登録日 平成21年12月18日 (2009.12.18)

|                                             | •                       |                    |       |

|---------------------------------------------|-------------------------|--------------------|-------|

| (51) Int.Cl.                                | F I                     |                    |       |

| G 1 1 C 29/56 (2006.01)                     | G 1 1 C 29/             | /00 652            |       |

| HO1L 21/66 (2006.01)                        | HO1L 21/                | /66 W              |       |

| GO 1 R 31/28 (2006.01)                      | GO1R 31/                | /28 B              |       |

| HO1L 21/8247 (2006.01)                      | HO1L 27/                | 7/10 4 3 4         |       |

| HO1L 27/115 (2006.01)                       | HO1L 29/                | /78 371            |       |

|                                             |                         | 請求項の数 6 (全 19 頁) 最 | 終頁に続く |

| (21) 出願番号 特願2007-254362 (P2007-254362) (73) |                         | 5) 特許権者 308033711  |       |

| (22) 出願日 平成19年9月2                           | 8日 (2007. 9. 28)        | OKIセミコンダクタ株式会社     |       |

| (65) 公開番号 特開2009-87430 (P2009-87430A)       |                         | 東京都八王子市東浅川町550首    | 季地 1  |

| (43) 公開日 平成21年4月2                           | 3日 (2009. 4. 23)   (74) | )代理人 100079049     |       |

| 審査請求日 平成21年3月1                              | 6日 (2009. 3. 16)        | 弁理士 中島 淳           |       |

|                                             | (74)                    | ) 代理人 100084995    |       |

|                                             |                         | 弁理士 加藤 和詳          |       |

|                                             | (74)                    | ) 代理人 100085279    |       |

|                                             |                         | 弁理士 西元 勝一          |       |

|                                             | (74)                    | ) 代理人 100099025    |       |

|                                             |                         | 弁理士 福田 浩志          |       |

|                                             | (72)                    | )発明者 廣田 彰宏         |       |

|                                             |                         | 東京都港区虎ノ門1丁目7番12    | 2号 沖電 |

|                                             |                         | 気工業株式会社内           |       |

|                                             |                         | 最終了                | 頁に続く  |

(54) 【発明の名称】半導体検査装置及び半導体検査方法

#### (57)【特許請求の範囲】

## 【請求項1】

浮遊ゲートと制御ゲートによって電荷を蓄積することで情報を記憶するメモリ機能を有した複数の通常セルと、前記通常セルと同一構造かつ同一機能とされ、前記通常セル動作状態の基準対象となるリファレンスセルと、を備えたデバイスを、被検査対象として装着部へ装着することで当該デバイスへ電源供給すると共に、前記デバイスの動作状態を検査するための半導体検査装置であって、

前記通常セルを対象として、擬似的に動作させて、前記リファレンスセルを基準とした当該セルの機能試験を行う機能試験実行手段と、

前記機能試験実行手段の実行終了後、前記装着部から前記デバイスへの前記電源供給を停止させ、かつ、所定時間後に再び電源供給するように制御する電源供給制御手段と、を有し、

前記機能試験実行手段は、前記電源供給制御手段による再電源供給後に、前記機能試験 実行手段に基づき、少なくとも1回の前記機能試験を行うことで前記リファレンスセルの 動作の良否を判定することを特徴とする半導体検査装置。

## 【請求項2】

浮遊ゲートと制御ゲートによって電荷を蓄積することで情報を記憶するメモリ機能を有した複数の通常セルと、前記通常セルと同一構造かつ同一機能とされ、前記通常セル動作状態の基準対象となるリファレンスセルと、を備えたデバイスを、被検査対象として装着部へ装着することで当該デバイスへ電源供給すると共に、前記デバイスの動作状態を検査

するための半導体検査装置であって、

前記装着部と前記デバイスのパッド又は端子との電気的導通を判定する接触試験を、全ての前記パッド又は前記端子に対して行う接触試験実行手段と、

前記デバイスの入出力における直流電流特性の状態を検査する直流電流試験を、全ての セルに対して行う直流電流試験実行手段と、

前記通常セルを対象として、擬似的に動作させて、前記リファレンスセルを基準とした当該セルの機能試験を行う機能試験実行手段と、

前記接触試験実行手段、前記直流電流試験実行手段、及び前記機能試験実行手段の各実行終了後、前記装着部から前記デバイスへの前記電源供給を停止させ、かつ、所定時間後に再び電源供給するように制御する電源供給制御手段と、を有し、

前記機能試験実行手段は、前記電源供給制御手段による再電源供給後に、前記機能試験 実行手段に基づき、少なくとも1回の前記機能試験を行うことで前記リファレンスセルの 動作の良否を判定することを特徴とする半導体検査装置。

## 【請求項3】

前記複数の通常セルを複数組に分類し、各組に1個の前記リファレンスセルを設け、前記機能試験実行手段は、各組毎に当該セルの機能試験を行うことを特徴とする請求項1又は請求項2に記載の半導体検査装置。

## 【請求項4】

前記所定時間経過後、かつ、再電源供給前に前記接触試験実行手段を実行することを特徴とする請求項2又は請求項3に記載の半導体検査装置。

#### 【請求項5】

浮遊ゲートと制御ゲートによって電荷を蓄積することで情報を記憶するメモリ機能を有した複数の通常セルと、前記通常セルと同一構造かつ同一機能とされ、前記通常セル動作状態の基準対象となるリファレンスセルと、を備えたデバイスを、被検査対象として装着部へ装着することで当該デバイスへ電源供給すると共に、前記デバイスの動作状態を検査するための半導体検査方法であって、

前記通常セルを対象として、擬似的に動作させて、前記リファレンスセルを基準とした 当該セルの機能試験を行う機能試験実行工程と、

前記機能試験実行工程の実行終了後、前記装着部から前記デバイスへの前記電源供給を停止させ、かつ、所定時間後に再び電源供給するように制御する電源供給制御工程と、

前記電源供給制御工程による再電源供給後に、前記機能試験実行工程に基づき、少なくとも1回の前記機能試験を行うことで前記リファレンスセルの動作の良否を判定する判定工程と、

を有する半導体検査方法。

## 【請求項6】

浮遊ゲートと制御ゲートによって電荷を蓄積することで情報を記憶するメモリ機能を有した複数の通常セルと、前記通常セルと同一構造かつ同一機能とされ、前記通常セル動作状態の基準対象となるリファレンスセルと、を備えたデバイスを、被検査対象として装着部へ装着することで当該デバイスへ電源供給すると共に、前記デバイスの動作状態を検査するための半導体検査方法であって、

<u>前記装着部と前記デバイスのパッド又は端子との電気的導通を判定する接触試験を、全</u>ての前記パッド又は前記端子に対して行う接触試験実行工程と、

前記デバイスの入出力における直流電流特性の状態を検査する直流電流試験を、全ての セルに対して行う直流電流試験実行工程と、

前記通常セルを対象として、擬似的に動作させて、前記リファレンスセルを基準とした 当該セルの機能試験を行う機能試験実行工程と、

前記接触試験実行工程、前記直流電流試験実行工程、及び前記機能試験実行工程の各実 行終了後、前記装着部から前記デバイスへの前記電源供給を停止させ、かつ、所定時間後 に再び電源供給するように制御する電源供給制御工程と、

前記電源供給制御工程による再電源供給後に、前記機能試験実行工程に基づき、少なく

10

20

30

40

<u>とも1回の前記機能試験を行うことで前記リファレンスセルの動作の良否を判定する判定</u> 工程と、

を有する半導体検査方法。

【発明の詳細な説明】

【技術分野】

[0001]

本発明は、半導体検査装置及び半導体検査方法に係り、特に、不揮発性半導体メモリのスクリーニングに関する。

【背景技術】

[00002]

10

従来、半導体メモリのテスト方法では、メモリアレイ中に不良メモリセルがある場合、 半導体メモリ内に設けたヒューズをブローすることにより予備のメモリアレイと置換する レーザーリペア工程のプリテストのテスト結果を半導体メモリに記憶し、以降の工程であ るウェハテストにおいて、前記メモリに記憶されたテスト結果を読み出し、不要なテスト を省略する。そのときの半導体メモリのテスト工程として、コンタクトテスト(Cont act Test:接触試験)、DCテスト(Direct Current Test :直流電流試験)、FCテスト(FunCtion Test:機能試験)の順番で行われ、半導体メモリの良否判定が行われている構成が提案されている(特許文献1参照)。

【特許文献1】特開平08-023016号公報

【発明の開示】

【発明が解決しようとする課題】

[0003]

しかしながら、特許文献1のような半導体メモリのテスト工程では、必ずしも良否を正確に判定できるわけではない。

[0004]

本願発明は、上記事実を考慮し、半導体メモリの良否を確実に判定することができる半 導体検査装置及び半導体検査方法を得ることが目的である。

【課題を解決するための手段】

[0005]

30

20

請求項1に記載の発明は、浮遊ゲートと制御ゲートによって電荷を蓄積することで情報を記憶するメモリ機能を有した複数の通常セルと、前記通常セルと同一構造かつ同一機能とされ、前記通常セル動作状態の基準対象となるリファレンスセルと、を備えたデバイスを、被検査対象として装着部へ装着することで当該デバイスへ電源供給すると共に、前記では、前記明であって、前記通常セルを対象として、擬似的に動作させて、前記リファレンスセルを基準とした当該セルの機能試験を行う、機能試験実行手段と、前記機能試験実行手段の実行終了後、前記装着部から前記デバイスの前記電源供給を停止させ、かつ、所定時間後に再び電源供給するように制御する電源供給制御手段と、を有し、前記機能試験実行手段は、前記電源供給制御手段による再電源供給後に、前記機能試験実行手段に基づき、少なくとも1回の前記機能試験を行うことで前記リファレンスセルの動作の良否を判定することを特徴としている。

[0006]

40

50

請求項2に記載の発明は、浮遊ゲートと制御ゲートによって電荷を蓄積することで情報を記憶するメモリ機能を有した複数の通常セルと、前記通常セルと同一構造かつ同一機能とされ、前記通常セル動作状態の基準対象となるリファレンスセルと、を備えたデバイスを、被検査対象として装着部へ装着することで当該デバイスへ電源供給すると共に、前記デバイスの動作状態を検査するための半導体検査装置であって、前記装着部と前記デバイスのパッド又は端子との電気的導通を判定する接触試験を、全ての前記パッド又は前記端子に対して行う接触試験実行手段と、前記デバイスの入出力における直流電流特性の状態を検査する直流電流試験を、全てのセルに対して行う直流電流試験実行手段と、前記通常セルを対象として、擬似的に動作させて、前記リファレンスセルを基準とした当該セルの

機能試験を行う機能試験実行手段と、前記接触試験実行手段、前記直流電流試験実行手段、及び前記機能試験実行手段の各実行終了後、前記装着部から前記デバイスへの前記電源供給を停止させ、かつ、所定時間後に再び電源供給するように制御する電源供給制御手段と、を有し、前記機能試験実行手段は、前記電源供給制御手段による再電源供給後に、前記機能試験実行手段に基づき、少なくとも1回の前記機能試験を行うことで前記リファレンスセルの動作の良否を判定することを特徴としている。

#### [0007]

請求項3に記載の発明は、請求項1又は請求項2に記載の発明において、前記複数の通常セルを複数組に分類し、各組に1個の前記リファレンスセルを設け、前記機能試験実行手段は、各組毎に当該セルの機能試験を行うことを特徴としている。

## [0008]

請求項4に記載の発明は、請求項2又は請求項3に記載の発明において、前記所定時間 経過後、かつ、再電源供給前に前記接触試験実行手段を実行することを特徴としている。

## [0013]

請求項<u>5</u>に記載の発明は、浮遊ゲートと制御ゲートによって電荷を蓄積することで情報を記憶するメモリ機能を有した複数の通常セルと、前記通常セルと同一構造かつ同一機能とされ、前記通常セル動作状態の基準対象となるリファレンスセルと、を備えたデバイスを、被検査対象として装着部へ装着することで当該デバイスへ電源供給すると共に、前記で、擬似的に動作させて、前記リファレンスセルを基準とした当該セルの機能試験を行う機能試験実行工程と、前記機能試験実行工程の実行終了後、前記装着部から前記デバイスの前記電源供給を停止させ、かつ、所定時間後に再び電源供給するように制御する電源供給制御工程と、前記機能試験実行工程による再電源供給後に、前記機能試験実行工程に基づき、少なくとも1回の前記機能試験を行うことで前記リファレンスセルの動作の良否を判定する判定工程と、を有することを特徴としている。

#### [0014]

請求項<u>6</u>に記載の発明は、浮遊ゲートと制御ゲートによって電荷を蓄積することで情報を記憶するメモリ機能を有した複数の通常セルと、前記通常セルと、を備えたデバイスを、被検査対象として装着部へ装着することで当該デバイスへ電源供給すると共に、前記であって、被検査対象として装着部へ装着することで当該デバイスへ電源供給すると共にデバイスの動作状態を検査するための半導体検査方法であって、前記装着部と前記パッド又は端子との電気的導通を判定する接触試験を、全ての前記パッド又は前部イスのパッド又は端子との電気的導通を判定する接触試験を、全ての前記パッド又は前部である直流電流試験実行工程と、前記リファレンスセルを基準とした当ででは、を対象として、擬似的に動作させて、前記リファレンスセルを基準とした当でででが表として、機能試験を行う機能試験実行工程と、前記接触試験実行工程、前記でが記述を停止させ、かつ、所定時間後に再び電源供給するように制御する電源供給制御工程による再電源供給後に、前記機能試験実行工程に基づき、公とも1回の前記機能試験を行うことで前記リファレンスセルの動作の良否を判定する判定工程と、を有することを特徴としている。

#### 【発明の効果】

## [0018]

以上説明したように、本願発明によれば、半導体メモリの良否を確実に判定することができるという効果が得られる。

【発明を実施するための最良の形態】

#### [0019]

## (本願発明の第1実施形態)

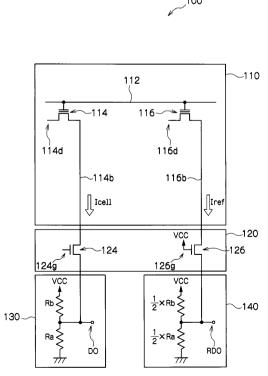

図1は、本願発明の第1実施形態におけるデバイスである不揮発性半導体メモリ100の構成図である。

10

20

30

40

#### [0020]

デバイスである不揮発性半導体メモリ100は、ワンタイムPROM(One Time Programmable Read Only Memory)とも呼ばれ、以下、OTP100と称する。

#### [0021]

OTP100は、紫外線消去型EPROM(UV-EPROM: Ultra Violet-Erasable Programmable Read Only Memoryのことであり、以下、EPROMと称する)を紫外線が透過しないプラスチックパッケージに封止(樹脂封止)したものである。また、OTP100は、EPROMのように紫外線照射により記憶内容を消去することができないため、書き込み回数が1回に限定されるが、プラスチックパッケージを使用することによって、他のEPROMと比較して非常に安価である。

#### [0022]

なお、この不揮発性半導体メモリ100は、OTP100として説明するが、EEPROM(Electric Erasable Programmable Read Only Memory)、又はフラッシュメモリであってもよい。また、EPROMでは、EPROMイレーサを用いて全てのデータを一括消去し、PROMライターでもう一度データを書き込むが、EEPROMでは、ワード線及びビット線を用いて任意の1ビットを指定して電気的にデータの消去及び書き込みをするものである。そして、フラッシュメモリでは、データの消去は所定バイトなどのブロック単位でしか行えないが、書き込みは1ビット単位で可能である。

#### [0023]

OTP100は、メモリセルアレイ110、カラムスイッチ群120、ディテクタ130、及びリファレンスディテクタ140で構成されている。

#### [0024]

メモリセルアレイ110は、カラムスイッチ群120と接続されており、カラムスイッチ群120は、ディテクタ130及びリファレンスディテクタ140と接続されている。 【 0 0 2 5 】

メモリセルアレイ110では、選択ワードライン(以下、選択WLと称する)112、通常セルトランジスタ114、及びリファレンスセルトランジスタ116で構成されている。なお、通常セルトランジスタ114及びリファレンスセルトランジスタ116は、浮遊ゲートと制御ゲートによって電荷を蓄積することで情報を記憶するメモリ機能を有しており、同一構造かつ同一機能を持っている。

## [0026]

選択WL112には、リファレンスセルトランジスタ116及び通常セルトランジスタ114の制御ゲートが接続されており、共用されている。なお、リファレンスセルトランジスタ116は選択WL112に1つ接続されている場合もあれば、複数接続されている場合もある。また、通常セルトランジスタ114は、選択WL112に複数接続されている。さらに、このメモリアレイ110には、選択WL112が複数存在して構成されており、その選択WL112の本数、選択WL112に接続されている通常セルトランジスタ114の量によってメモリアレイ110の容量が決まる。

#### [0027]

通常セルトランジスタ114の一方にはセルドレイン114dが接続されており、ドレイン電圧が供給されるようになっている。また、リファレンスセルトランジスタ116でも、通常セルトランジスタ114と同様に、リファレンスセルトランジスタ116の一方にセルドレイン116dが接続されており、ドレイン電圧が供給されるようになっている

## [0028]

さらに、通常セルの他方には、ビット線114bが接続されており、通常セル電流Icellが流れるようになっている。また、リファレンスセルトランジスタ116でも、リ

10

20

30

40

ファレンスセルトランジスタ 1 1 6 の他方にリファレンスビット線 1 1 6 b が接続されており、リファレンスセル電流 I r e f が流れるようになっている。

[0029]

さらに、ビット線114bは、カラムスイッチ群120のカラムスイッチトランジスタ124を介し、ディテクタ130の分圧抵抗Ra及び分圧抵抗Rbの間(ディテクタ出力DO)に接続されている。また、ビット線116bは、カラムスイッチ群120のカラムスイッチトランジスタ126を介し、リファレンスディテクタ140の分圧抵抗Ra/2及び分圧抵抗Rb/2の間(リファレンスディテクタ出力RDO)に接続されている。

[0030]

図1を参照して、OTP100の読み出し動作を説明する。

10

20

30

[0031]

図1は、OTP100の読み出し時の回路図を簡略化したものである。

[0032]

メモリセルアレイ 1 1 0 内の 1 つの通常セルトランジスタ 1 1 4 はセルドレイン 1 1 4 d からドレイン電圧を供給されている。また、リファレンスセルトランジスタ 1 1 6 はセルドレイン 1 1 6 d からドレイン電圧を供給されている。

[0033]

通常セルトランジスタ114が選択される際、選択WL112が立ち上がり、かつカラムスイッチ群120内でビット線114bに接続されているカラムスイッチトランジスタ124がカラムアドレスにより選択(ゲート124gに電圧が印加)されると、セルドレイン114dからビット線114bを介してディテクタ130に通常セル電流Icellが流れ込む。例えば、選択WL112が立ち上がる際には、選択WL112に3.6Vの電圧をかけ、セルドレイン114dには1.0Vの電圧がかかり、ビット線114bを介してディテクタ130に通常セル電流Icellが流れ込む。

[0034]

ディテクタ130は、図1に示しているような等価回路によって簡略化されており、ディテクタ出力D〇の電圧は、Ra(VCC/(Ra+Rb)+Icell)と表すことができる。

[0035]

一方で、リファレンスセルトランジスタ116も選択W L 1 1 2 が立ち上がることでリファレンスビット線116 b を介してリファレンスディテクタ140にリファレンスセル電流 I r e f が流れ込む。このとき、リファレンスビット線116 b に接続されているリファレンスカラムスイッチトランジスタ126のゲート126gは電源 V C C に接続されており、カラムアドレスによらずリファレンスセルトランジスタ116はリファレンスセル電流 I r e f を流す。

[0036]

例えば、通常電圧VCCが3.3V(例えば、規格は、3.3V±0.3V)であり、カラムスイッチトランジスタ124及びリファレンスカラムスイッチトランジスタ126のそれぞれのトランジスタには通常電圧VCCの3.3Vがゲート124g、126gに印加されてオン状態(アクティブ状態)になる。なお、リファレンスカラムスイッチトランジスタ126のゲート126gには、ノーマリーオンの状態(常時オン状態)であり、常時3.3Vの電圧がかかる。

40

[0037]

リファレンスカラムスイッチトランジスタ126のゲート126gが電源VCCに接続されている理由は、リファレンスセルトランジスタ116から流れるリファレンスセル電流 Irefと、通常セルトランジスタ114から流れる通常セル電流 Icellと比較するためである。そのため、カラムアドレスによらず、常に電流を流す必要があり、また、通常セルトランジスタ114の電流経路と差異が生じないように、リファレンスカラムスイッチトランジスタ126を介する必要があるからである。

[0038]

20

30

40

50

リファレンスセル電流 I r e f も通常セル電流 I c e l l と同様にリファレンスディテクタ 1 4 0 へ流れ込むが、リファレンスディテクタ 1 4 0 では、ディテクタ 1 3 0 と比較して、電源間の抵抗が 1 / 2 になっており、リファレンスディテクタ出力 R D O は、R a ( V C C / ( R a + R b ) + I r e f / 2 )となる。

## [0039]

OTP100の通常セルトランジスタ114に蓄積された電荷により、"0"及び"1"は、上記のリファレンスディテクタ出力RDOとディテクタ出力DOを比較することで判定している。

#### [0040]

通常セルトランジスタ1 1 4 が " 0 " (書き込み状態)の場合、選択WL 1 1 2 の電圧レベルよりも通常セルトランジスタ1 1 4 の閾値電圧 V t が高く、通常セル電流 I c e 1 1 が流れない。このとき、DO-RDO=-Ra(Iref/2)となる。なお、書き込み状態にて、データ " 0 "を記録する場合、通常セルトランジスタ1 1 4 のドレイン及びゲートに高電圧をかけて熱電子が浮遊ゲート内に注入される。また、読み出し状態にて、データ " 0 "を読み出す場合、通常セルトランジスタ1 1 4 のゲートに電圧をかけても浮遊ゲート内の電子に邪魔されてトランジスタがオンにならず、ドレイン・ソース間に電流が流れない。

## [0041]

通常セルトランジスタ114が、"1"(ブランク状態)の場合、選択WL112の電圧レベルよりも通常セルトランジスタ114の閾値電圧Vtが低く、通常セル電流Icel1が流れる。なお、ブランク状態にて、データ"1"になる場合、通常セルトランジスタ114の浮遊ゲート内には電子が放出されている。例えば、UV-EPROMの場合、紫外線照射により浮遊ゲート内に閉じ込められた電子を放出し、データは消去("1"になる)される。同様にEEPROMの場合も電気的にデータは消去("1"になる)される。また、読み出し状態にて、データ"1"を読み出す場合、通常セルトランジスタ114のゲートに電圧をかけると、トランジスタがオンになり、ドレイン・ソース間に電流が流れる。

#### [0042]

従って、このとき、通常セルトランジスタ114とリファレンスセルトランジスタ116の閾値電圧Vtは同等であり、Icell=Irefとなるため、DO-RDO=Ra(Iref/2)となる。

## [0043]

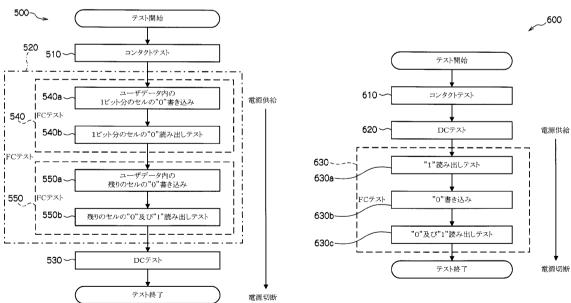

ところで、図6は、従来技術でのウェハレベルのテスト工程600を示している。なお、図6のテスト工程600は、プローブカードを用いて、ウェハレベルのOTP100をテストする場合を示している。

#### [0044]

OTP100のテスト工程では、ステップ610のコンタクトテスト、ステップ620のDCテスト、ステップ630のFCテスト(ファンクションテスト)の3工程に大別される。また、ステップ630のFCテストは、さらに、ステップ630aの"1"読み出しテスト、ステップ630bの"0"書き込み、ステップ630cの"0"及び"1"読み出しテストの3工程からなる。

#### [0045]

コンタクトテストは、接触試験のことであり、OTP100等の実際のデバイスであるDUT(Device Under Test:被試験デバイス)のパッド(又は端子)と半導体試験装置(以下、LSIテスタと呼ぶ)の検査用端子が接触していることを試験する。詳細には、ウェハのコンタクトテストの場合は、パッドとLSIテスタの検査用端子との接触試験を実行し、プラスチックパッケージ又はセラミックパッケージ等のパッケージにされたIC(集積回路:Integrated Circuit)のコンタクトテストの場合は、ICの端子とLSIテスタの検査用端子の接触試験を実行する。さらに、通常セル及び通常セルの基準対象となるリファレンスセルを備えたDUTを被検査対象と

20

30

50

してLSIテスタの装着部(プローブカード又は検査用ボードを介する)へ装着して検査を行う。なお、ICの端子がチップ内部のパッドと接続されていないNC(Non Conect)端子がある場合、NC端子のコンタクトテストはしない。

#### [0046]

前記デバイスの入出力における直流電流特性の状態を検査する直流電流試験であるDCテストは、DCパラメトリックテストとも言い、直流電流特性を測定する。例えば、DCテストには、入力リークテスト、出力リークテスト、電源電流テスト、静止電源電流テスト、入力電流テスト、及び出力電流テスト等がある。

#### [0047]

ファンクションテスト(以下、FCテストと称する)は、OTP100(デバイス)の検査する対象のセルに対し、擬似的に動作させて対象のセルの機能試験をする(実動作条件での機能試験を行う)ことを意味している。また、詳細には、FCテストは機能試験又は実動作試験のことを指し、IC又はLSI(Large Scale Inegrated circuit:大規模集積回路)等に搭載されている各回路ブロック毎(又は集積回路全体)の実動作における機能試験をする。

#### [0048]

OTP100では、"0"(書き込み状態)から"1"(ブランク状態)へ戻すには、UV(Ultra-Violet:紫外線)照射が必要であるため、一般的にステップ630aの"1"読み出しテストを実行してから、ステップ630bの"0"書き込み、最後にステップ630cの"0"及び"1"読み出しテストを実行している。なお、ここでは、"0"及び"1"のデータは、固定されたパターンのデータ(所定の定められたパターンデータであり、以下、固定パターンデータと称する)を用いている。

## [0049]

詳細には、初期状態がブランク状態であるので、そのブランク状態を検査する際、ステップ630aの"1"読み出しテストをまず実行する(デバイスが不良の場合、初期状態においてブランク状態の"1"ではない場合があるため)。次に、ステップ630bの固定パターンデータにおける"0"書き込みを実行する。最後に、ステップ630cの"0"及び"1"読み出しテストを実行する。なお、ステップ630bにおいて、固定パターンデータの"0"が正しく書き込まれない場合、又は固定パターンデータの"1"が誤って"0"に書き換えられてしまう場合があるためステップ630cの"0"及び"1"読み出しテストを実行する。また、ステップ630のFCテストはテスト時間が長いため、よりテスト時間の短いステップ610のコンタクトテスト、及びステップ620のDCテストをステップ630のFCテストの前に実行されている。

#### [0050]

また、パッケージにされた状態のOTP100の場合の説明は、図7を参照して説明する。図7は、従来技術でのパッケージされたテスト工程700を示している。なお、パッケージ状態のOTP100(1回書き込みしかできないEPROM)は、UV照射を用いて記憶されたデータを消去することはできない。

#### [ 0 0 5 1 ]

ステップ710のコンタクトテストは、図60のステップ610のコンタクトテストと同様のテストを行い、ステップ720のDCテストは、図60のステップ620のDCテストと同様のテストを行う。

## [0052]

ステップ 7300 F C テストは、基本的には、図 600 ステップ 6300 F C テストと同様のテストである。しかし、図 600 ステップ 6300 F C テストとは違い、固定パターンデータを用いるのではなく、ステップ 730a0 a の書き込みにおいて、予め用意されている特定のユーザデータを、O T P 1000 の持つ複数の通常セルに書き込む処理を実行する。そして、ステップ 730b0 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000 000

#### [0053]

しかし、上記テスト工程では、電源供給から試験開始までの時間に依存する、以下のような不良をスクリーニングできない。

#### [0054]

図6及び図7では、OTP100のテスト工程における電源供給タイミングも示しており、ステップ620及びステップ720のDCテスト以降は電源が継続してオンとなっているか、又は試験後に一旦電源を落としても、次の試験を実行するために再度すぐに電源がオンとなる。このことから、ステップ630及びステップ730のFCテストでは、テスト実行前から電源がオンになっている時間が長くなっている。

#### [0055]

図8は、従来技術におけるリファレンスカラムスイッチトランジスタ126のゲート126gの不具合の状態を示している。

## [0056]

図1のような回路構成のOTP100において、リファレンスカラムスイッチトランジスタ126のゲートレベルに接続されている配線もしくはVia(ビア:多層配線において、上層の配線と下層の配線を電気的に繋ぐ接続領域)が、高抵抗もしくは断線している場合であるとする。

## [0057]

このような場合、図 8 (a)は電源供給直後のノーマリーオントランジスタであるリファレンスカラムスイッチトランジスタ 1 2 6 の状態を示している。このときには、配線又は Viaの高抵抗もしくは断線により、ゲートレベルが印加されず、トランジスタに電流が流れない。

#### [0058]

図8(b)は電源供給したまましばらく放置していたときのノーマリーオントランジスタであるリファレンスカラムスイッチトランジスタ126の状態を示している。このときには、配線又はViaの高抵抗もしくは断線が存在するが、電源供給後、時間経過と共にゲートレベルが充電されるため、トランジスタがオン状態になり、トランジスタに電流が流れてしまう。

## [0059]

このため、図6及び図7の従来技術のテスト工程600、700でテストした場合、ゲート126gが電源に直結しているリファレンスカラムスイッチトランジスタ126では、FCテスト630、730が実行されるまでに、ノーマリーオントランジスタであるリファレンスカラムスイッチトランジスタ126のゲート126gが充電され、不良とならず、電流が流れてしまう可能性がある。

### [0060]

以下、本願発明の第1実施形態の作用を説明する。

## [0061]

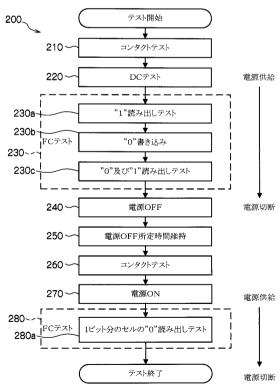

図2は、本願発明の第1実施形態におけるウェハレベルのOTP100を検査するための第1のフローチャート200を示している。なお、第1のフローチャート200におけるOTP100の検査は、プローブカードを用いて、ウェハレベルのOTP100をテストする場合を示している。

#### [0062]

ステップ210では、コンタクトテストを行う。詳細には、LSIテスタの検査端子と接続(装着)されたプローブカードの検査端子である検査針と、LSIテスタの装着部へ装着された被検査対象(デバイス)であるウェハレベルのOTP100のパッドが接触されているかどうかのコンタクトテストを実行する。

#### [0063]

ステップ220では、DCテストを行う。詳細には、LSIテスタからプローブカードを介してウェハレベルのOTP100に電源が供給され、OTP100のDCテストが行われ、OTP100の直流電流特性を測定する。

10

20

30

40

20

30

40

50

[0064]

ステップ230では、FCテストを行う。詳細には、従来のFCテスト(図6のステッ プ630のFCテストと同様のテスト)が実行される。ステップ230aの初期状態の " 1 " 読み出しテスト、ステップ230bの固定パターンデータの " 0 " 書き込み、ステッ プ230cの固定パターンデータの"0"及び"1"読み出しテストが実行される。なお 、ステップ230cにおいて、再び"1"読み出しテストを行う理由は、図6及び図7に おける従来のFCテスト630c、730bのときと同じである。また、ステップ230 a、230b、230cにおいて、通常セルトランジスタ114の"0"又は"1"は、 通常セルのディテクタ出力DOとリファレンスセルのリファレンスディテクタ出力RDO とを比較することで判定しており、"1、読み出しテスト、"0、書き込み、"0、及び "1"読み出しテストが行われている。比較の方法は、ディテクタ出力D0-リファレン スディテクタ出力RDOの電圧値に基づいて判定されている。さらに、通常セルは、図1 に図示されている通常セルトランジスタ114、カラムスイッチ群120のカラムスイッ チトランジスタ124、及びディテクタ130を総称している。そして、リファレンスセ ルは、図1に図示されているリファレンスセルトランジスタ116、カラムスイッチ群1 2 0 のリファレンスカラムスイッチトランジスタ 1 2 6 、及びリファレンスディテクタ 1 40を総称している。

[0065]

ステップ240では、電源OFFする。詳細には、電荷がチャージされているかもしれないリファレンスカラムスイッチトランジスタ126のゲート126gの電荷を開放するため、ここで検査装置からOTP100に供給されていた電源を切断する。

[0066]

ステップ250では、電源OFFを所定時間維持する。詳細には、ステップ240に記載したように、リファレンスカラムスイッチトランジスタ126のゲート126gのチャージされている電荷を開放するために約数分間(具体的には、約5分から約10分の間)電源を落としておく。

[0067]

ステップ260では、コンタクトテストを実行する。詳細には、これはステップ210と全く同様の操作を行う。なお、ここで、コンタクトテストを実行するのは、ステップ230のFCテストで長時間電源を供給し、LSIテスタとOTP100とのデータのやり取りを行っていたため、プローブカードの検査針やOTP100のパッドに熱が発生していた可能性がある。そのため、ステップ230のFCテスト終了後に電源を所定時間落とした場合、検査針またはパッドが熱膨張されていた状態から収縮されてコンタクト(接触)が外れる場合(コンタクトテストが通らなくなる可能性)があるのでもう一度コンタクトテストを行う。

[0068]

ステップ 2 7 0 では、電源 O N する。詳細には、ステップ 2 8 0 以降のテストのために 電源供給する。

[0069]

ステップ280では、1ビット分のセルのFCテストを実行する。詳細には、ステップ280aの1ビット分のセルの"0"読み出しテストを実行する。そこで、リファレンスセルは、少なくとも選択WL112に1つ以上存在し、複数の通常セルがそれぞれ対応して接続されている。例えば、選択WL112に存在する1つのリファレンスセルは所定数の通常セルと接続されている場合、その通常セルのどれか1つと、対応するリファレンスセルの1つとを比較し、"0"読み出しテストを実行する。このことを1ビット分のセルの"0"読み出しテストを実行すると表現しており、通常セルの機能試験に基づき、少なくとも1回の機能試験を行うことでリファレンスセルの良否を判定している。なお、ステップ280のFCテスト(ステップ280aのFCテスト)では、全てのリファレンスセルぞれに対して、それぞれのリファレンスセルに対応する複数の通常セルの中で、1つずつ"0"読み出しテストをリファレンスセルの分だけ実行する。

20

30

40

50

[0070]

そして、ステップ280でOTP100の良否判定を行い、テスト終了させて電源を切断する。

[0071]

なお、リファレンスセルの良否に関して、このステップ280aの "0 "の読み出しテストによって判定することができる。

[0072]

従って、本願発明の第1実施形態によれば、ノーマリーオントランジスタであるリファレンスカラムスイッチトランジスタ126のゲートの断線又は高抵抗によるリファレンスビット線116bの不良をスクリーニングすることができる。

[0073]

図3は、本願発明の第1実施形態におけるパッケージされたOTP100を検査するための第2のフローチャート300を示している。なお、第2のフローチャート300におけるOTP100の検査は、検査用ボードを用いて、パッケージにされたOTP100をテストする場合を示している。

[0074]

ステップ310のコンタクトテストは、図2のステップ210のコンタクトテストと同様のテストである。詳細には、被検査対象が図2のステップ210の場合はウェハレベルのOTP100であり、図3のステップ310の場合はパッケージされたOTP100である点に違いがある。そこで、ステップ310のコンタクトテストでは、LSIテスタの検査端子と接続(装着)された検査用ボードの検査端子(ICソケット)と、LSIテスタの装着部へ装着された検査用ボードのICソケットにセットされたOTP100(パッケージングされたIC)の端子が接触されているかどうかのコンタクトテストを実行する

[0075]

ステップ320のDCテストは、図2のステップ220と同様のDCテストである。

[0076]

ステップ 3 3 0 の F C テストと図 2 のステップ 2 3 0 の F C テストは、基本的には同じだが、パッケージにされた O T P 1 0 0 では、ステップ 3 3 0 a でユーザデータを書き込み、書き込まれたユーザデータが正しいかどうかをステップ 3 3 0 b の " 0 " 及び " 1 " 読み出しテストによって判定する。

[0077]

ステップ340の電源OFFは、図2のステップ240と同様の処理である。

[0078]

ステップ 3 5 0 の電源 O F F 所定時間維持は、図 2 のステップ 2 5 0 と同様の処理である。

[0079]

ステップ360のコンタクトテストは、ステップ310のコンタクトテストと同様のテストである。

[0800]

ステップ370の電源ONは、図2のステップ270と同様の処理である。

[0081]

ステップ380のFCテストは、図2のステップ280のFCテストと同様のFCテストである(ステップ380aのFCテストも図2のステップ280aのFCテストと同様のFCテストである)。

[0082]

そして、ステップ380でOTP100の良否判定を行い、テスト終了させて電源を切断する。

[0083]

本願発明の第1実施形態によれば、リファレンスセルの良否に関して、このステップ3

8 0 によって判定することで、ノーマリーオントランジスタであるリファレンスカラムスイッチトランジスタ 1 2 6 のゲートの断線又は高抵抗によるリファレンスビット線 1 1 6 b の不良をスクリーニングすることができる。

### [0084]

なお、ノーマリーオントランジスタであるリファレンスカラムスイッチトランジスタ126のゲートにチャージされた電荷を短時間で強制的に開放するような方法を用いて電源を落としている時間を短縮させてもよい。

(本願発明の第2実施形態)

以下、本願発明の第2実施形態の作用を説明する。

[0085]

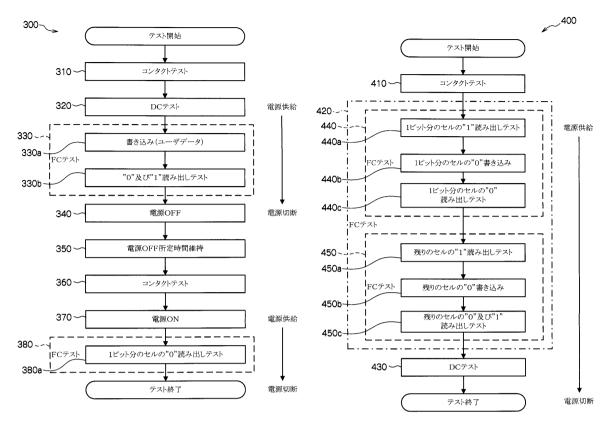

図4は、本願発明の第2実施形態におけるウェハレベルのOTP100を検査するための第3のフローチャート400を示している。

[0086]

本願発明の第2実施形態におけるOTP100を検査するための第3のフローチャート400を示している図4は、リファレンスビット線116bに図8での説明でしたような不良がある場合のスクリーニング方法である。

[0087]

検査工程は、ステップ410のコンタクトテスト、ステップ420のFCテスト420 、ステップ430のDCテストに大別されている。

[0088]

また、ステップ 4 2 0 の F C テストは、ステップ 4 4 0 の F C テスト及びステップ 4 5 0 の F C テストの 2 つの工程から成っている。

[0089]

詳細には、ステップ440のFCテストは、ステップ440aのFCテスト、ステップ440bのFCテスト、及びステップ440cのFCテストの3つの工程から成っている。そして、ステップ450のFCテストはステップ450aのFCテスト、ステップ450bのFCテスト、及びステップ450cのFCテストの3つの工程から成っている。

[0090]

ステップ410では、コンタクトテストを実行する。詳細には、図2のステップ210 及びステップ260の工程と同様である。

[0091]

ステップ 4 2 0 では、 F C テストを実行する。詳細には、ステップ 4 2 0 の F C テストでは、ステップ 4 4 0 の F C テスト、及びステップ 4 5 0 の F C テストを実行する。

[0092]

まず、ステップ440のFCテストでは、ステップ440aのFCテストでは、1ビット分のセルの初期状態の"1"読み出しテストを行い、次に、ステップ440bのFCテストでは、1ビット分のセルの固定パターンデータの"0"書き込みを行い、最後に、ステップ440cのFCテストでは、1ビット分のセルの固定パターンデータの"0"読み出しテストを行う。

[0093]

例えば、リファレンスセルは、少なくとも選択WL112に1つ以上存在し、複数の通常セルがそれぞれ対応して接続されている。そして、選択WL112に存在する1つのリファレンスセルは所定数の通常セルと接続されている場合、その通常セルのどれか1つと、対応するリファレンスセルの1つとを比較し、"1"読み出しテストを実行する。このことを1ビット分のセルの"1"読み出しテストを実行すると表現している。また、通常セルのどれか1つに"0"を書き込み、その"0"が書き込まれた通常セルと、対応するリファレンスセルの1つとを比較し、"0"読み出しテストを実行する。このことを1ビット分のセルの"0"読み出しテストを実行すると表現しており、通常セルの機能試験に基づき、少なくとも1回の機能試験を行うことでリファレンスセルの良否を判定している

10

20

30

40

20

30

40

50

[0094]

なお、ステップ 4 4 0 の F C テストでは、ステップ 4 4 0 a 、 4 4 0 b 、 4 4 0 c の F C テストの工程を全てのリファレンスセルに対して実行される。

[0095]

そして、ステップ450のFCテストを実行する。ステップ450aのFCテストでは、ステップ440のFCテスト以外の残りの全ての通常セルに対して初期状態の"1 "読み出しテストを行う。次に、FCテスト450bのFCテストでは、ステップ440のFCテスト以外の残りの全ての通常セルに対して固定パターンデータの"0 "書き込みを行う。最後に、ステップ450cのFCテストでは、ステップ440のFCテスト以外の残りの全ての通常セルに対して固定パターンデータの"0 "及び"1 "読み出しテストを行う。なお、ステップ450のFCテストの"0 "及び"1 "のデータは固定パターンデータを使用する。

[0096]

ステップ430では、DCテストを行う。詳細には、ステップ420のFCテストに含まれる6工程(ステップ440a、440b、440c、450a、450b、450c)の終了後に実行される。

[0097]

従って、本願発明の第2実施形態によれば、電源供給からステップ440cの1ビット分のセルの固定パターンデータの"0"読み出しテスト開始までの時間を短縮し、リファレンスビット線不良のスクリーニングをすることができる。

[0098]

図5は、本願発明の第2実施形態におけるパッケージされたOTP100を検査するための第4のフローチャート500を示している。なお、第4のフローチャート500におけるOTP100の検査は、検査用ボードを用いて、パッケージにされたOTP100をテストする場合を示している。

[0099]

ステップ 5 1 0 のコンタクトテストは、図 4 のステップ 4 1 0 のコンタクトテストと同様のテストである。詳細には、被検査対象が図 4 のステップ 4 1 0 の場合はウェハレベルのOTP 1 0 0 であり、図 5 のステップ 5 1 0 の場合はパッケージされたOTP 1 0 0 である点に違いがある。そこで、ステップ 5 1 0 のコンタクトテストでは、LSIテスタの検査端子と接続(装着)された検査用ボードに搭載されているICソケットと、LSIテスタの装着部へ装着された検査用ボードのICソケットにセットされたOTP 1 0 0 (パッケージングされたIC)の端子が接触されているかどうかのコンタクトテストを実行する。

[0100]

[0101]

ステップ 5 4 0 の F C テストにおいては、ステップ 5 4 0 a 及びステップ 5 4 0 b で構成されている。ステップ 5 4 0 a では、ユーザデータ内の 1 ビット分のセルの " 0 "を書き込み、ステップ 5 4 0 b では、リファレンスセルの良否を 1 ビットのセルの " 0 "読み出しテストによって判定する。

[0102]

ステップ 5 5 0 においては、ステップ 5 5 0 a 及びステップ 5 5 0 b で構成されている。ステップ 5 5 0 a では、ユーザデータ内の残りのセルの " 0 "の書き込みを行う。詳細には、テスト終了した以外の残りの全ての通常セルに対し、ステップ 5 4 0 a で書き込まれた以外のユーザデータ内の全データの " 0 "の書き込みを行う。ステップ 5 5 0 b では、ステップ 5 5 0 a で書き込まれたユーザデータが正しいか否かを " 0 "及び " 1 "読み

20

40

50

出しテストによって判定する。

[0103]

なお、ステップ 5 4 0 の F C テストでは、ステップ 5 4 0 b の F C テストの工程を全てのリファレンスセルに対して実行される。

[0104]

ステップ530のDCテストは、図4のステップ430と同様のDCテストである。

[0105]

なお、本願発明の第2実施形態によれば、機能試験に基づき、少なくとも1回の機能試験を行うことでリファレンスセルの動作の良否を判定することを優先して実行する。

[0106]

本願発明の第2実施形態によれば、電源供給からステップ540bの1ビット分のセルの"0"読み出しテスト開始までの時間を短縮し、リファレンスビット線不良のスクリーニングをすることができる。

[0107]

以下に、リファレンスビット線不良がスクリーニングできる理由を説明する。

[0108]

図8を用いて説明したように、電源供給直後であれば、リファレンスカラムスイッチトランジスタ126のゲートレベルは充電されておらず、リファレンスビット線116bにリファレンスセル電流Irefが流れない。

[0109]

従来技術の説明でしたように、この場合、通常セルトランジスタ114が″1″(ブランク状態)であれば、ディテクタ130とリファレンスディテクタ140の出力電圧の差は、DO-RDO=Ra(VCC/(Ra+Rb)+Icell)-Ra(VCC/(Ra+Rb)+Iref/2)=Ra×Iref>0となり、読み出しテストはPASSとなる。しかし、通常セルトランジスタ114が″0″(書き込み状態)であれば、ディテクタ130とリファレンスディテクタ140の出力電圧の差は、DO-RDO=Ra(VCC/(Ra+Rb)+Iref/2)=0となり、読み出しテストはFAILとなる。

[0110]

以上のことから、リファレンスカラムスイッチトランジスタ126のゲート126gの 断線又は高抵抗によるリファレンスビット線116bの不良は"1"読み出しテストでは 不良を検出できず、"0"読み出しテスト(ステップ440c及びステップ540bにお ける1ビット分のセルの"0"読み出しテスト)で不良が検出できる。

[0111]

上記から、リファレンスビット線116bの不良のスクリーニング検出率を向上させるためには、図4及び図5に示したように、電源供給からステップ440c及びステップ540bの1ビット分のセルの " 0 "読み出しテスト開始までの時間を短くする必要がある

[0112]

そのため、ステップ430及びステップ530のDCテストをステップ420及びステップ520のFCテストの後に実行し、さらに多くの時間を要しないようにステップ44 0 b の 1 ビット分のセルの " 0 "書き込み(ステップ540aのユーザデータ内の 1 ビット分のセルの " 0 "書き込み)をし、ステップ440c及びステップ540bの1ビット分のセルの " 0 "読み出しテストを実行している。

[0113]

なお、1ビット分のセル(全てのリファレンスセルに対応する通常セルを1つずつ)のみのテストで上記のようなリファレンスビット線116の不良をスクリーニングできる理由は、図1のリファレンスカラムスイッチトランジスタ126はカラムアドレス及びロウアドレス(選択WL112)によらず、常にオンとなっており、どのようなアドレスが選択されても不良となるためである。

[0114]

従って、本願発明の第2実施形態によれば、メモリセルアレイ110に対して最初にス テップ440aの1ビット分のセルの"1"読み出しテスト、ステップ440bの1ビッ ト分のセルの"0 "書き込み、ステップ440cの1ビット分のセルの"0 "読み出しテ ストを実行することで、電源供給からステップ440cの1ビット分のセルの"0"読み 出しテスト開始までの時間を大幅に短縮できる。さらに、メモリセルアレイ110に対し て最初にステップ 5 4 0 a のユーザデータ内の 1 ビット分のセルの " 0 "書き込み、ステ ップ540bの1ビット分のセルの"0"読み出しテストを実行することで、電源供給か らステップ 5 4 0 b の 1 ビット分のセルの " 0 "読み出しテスト開始までの時間を大幅に 短縮できる。また、その結果、ノーマリーオントランジスタであるリファレンスカラムス イッチトランジスタ126のゲート126gの断線又は高抵抗によるリファレンスビット 線116bの不良をスクリーニングすることができる。

【図面の簡単な説明】

[ 0 1 1 5 ]

【図1】本願発明の第1実施形態におけるデバイスである不揮発性半導体メモリの構成図

【図2】本願発明の第1実施形態におけるウェハレベルのOTPを検査するための第1の フローチャートを示している。

【図3】本願発明の第1実施形態におけるパッケージされたOTPを検査するための第2 のフローチャートを示している。

【図4】本願発明の第2実施形態におけるウェハレベルのOTPを検査するための第3の フローチャートを示している。

【図5】本願発明の第2実施形態におけるパッケージされたOTPを検査するための第4 のフローチャートを示している。

【図6】従来技術でのウェハレベルのテスト工程を示している。

【図7】従来技術でのパッケージされたテスト工程を示している。

【図8】従来技術におけるリファレンスカラムスイッチトランジスタのゲートの不具合の 状態を示している。

【符号の説明】

[0116]

1 0 0 OTP

1 1 0 メモリセルアレイ

通常セルトランジスタ 1 1 4

1 1 6 リファレンスセルトランジスタ

1 2 4 カラムスイッチトランジスタ

1 2 6 リファレンスカラムスイッチトランジスタ

1 3 0 ディテクタ

1 4 0 リファレンスディテクタ

DOディテクタ出力

リファレンスディテクタ出力 RDO

2 1 0 、 2 6 0 、 4 1 0 、 3 1 0 、 3 6 0 、 5 1 0 コンタクトテスト (接触試験 実行手段、接触試験実行工程)

2 2 0 、 4 3 0 、 3 2 0 、 5 3 0 D C テスト (直流電流試験実行手段、直流電流 試験実行工程)

230、230a、230b、230c、440、440a、440b、440c、 3 3 0 、 3 3 0 a 、 3 3 0 b 、 5 4 0 、 5 4 0 a 、 5 4 0 b F C テスト (機能試験実 行手段、機能試験実行工程)

2 4 0 、 3 4 0 電源OFF(電源供給制御手段、電源供給制御工程)

250、350 電源OFF所定時間維持(電供給源制御手段、電源供給制御工程 )

10

20

30

40

270、370

電源ON(電源供給制御手段、電源供給制御工程)

280、280a、380、380a、450、450a、450b、450c、5

50、550a

FCテスト(機能試験実行手段、判定工程、判定優先実行工程)

430

FCテスト(機能試験実行手段、判定工程、判定優先実行工程)

420、520 FCテスト(機能試験実行手段、機能試験実行工程、判定工程、 判定優先実行工程)

[図1] [図2]

【図3】 【図4】

【図5】 【図6】

# 【図7】

## 【図8】

# (a) 電源供給直後 配線又はViaか「VCC 高抵抗であるか」 断線している 126g 電流は流れない

(b)

## フロントページの続き

(51) Int.CI. F I

H 0 1 L

29/788

(2006.01)

G 1 1 C

17/00

6 0 1 Z

H 0 1 L

29/792

(2006.01)

G 1 1 C

17/00

6 3 4 E

G 1 1 C 16/02 (2006.01) G 1 1 C 16/06 (2006.01)

審査官 小林 紀和

(56)参考文献 特開2004-062922(JP,A)

特開2005-285281(JP,A)

特開平05-136361(JP,A)

(58)調査した分野(Int.CI., DB名)

G11C 29/56