## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2004-111872 (P2004-111872A)

(43) 公開日 平成16年4月8日 (2004. 4.8)

東京都大田区中馬込1丁目3番6号 株式

BB11 BD07 BF01 BF07 CB07

最終頁に続く

| (51) Int.C1. <sup>7</sup> | F I                          |          | テーマコード(参考)                |

|---------------------------|------------------------------|----------|---------------------------|

| HO1L 29/786               | HO1L                         | 29/78 €  | 626A 5FO48                |

| HO1L 21/823               | 4 HO1L                       | 29/78 €  | 652F 5F110                |

| HO1L 21/823               | 8 HO1L                       | 29/78 €  | 6 5 2 T                   |

| HO1L 27/088               | HO1L                         | 29/28    |                           |

| HO1L 27/092               | HO1L                         | 27/08 1  | 1 O 2 E                   |

|                           | 審査請求 未                       | 請求 請求項   | 『の数 10 OL (全 17 頁) 最終頁に続く |

| (21) 出願番号                 | 特願2002-276058 (P2002-276058) | (71) 出願人 | 000006747                 |

| (22) 出願日                  | 平成14年9月20日 (2002.9.20)       |          | 株式会社リコー                   |

|                           |                              |          | 東京都大田区中馬込1丁目3番6号          |

|                           |                              | (74) 代理人 | 100060690                 |

|                           |                              |          | 弁理士 瀧野 秀雄                 |

|                           |                              | (72) 発明者 | 近藤 浩                      |

|                           |                              |          | 東京都大田区中馬込1丁目3番6号 株式       |

|                           |                              |          | 会社リコー内                    |

|                           |                              | (72) 発明者 | 秋山善一                      |

(54) 【発明の名称】縦型電界効果トランジスタ及びその製造方法並びにそれを有する演算素子

## (57)【要約】

【課題】実行的電界移動度を向上させることができ、しかも、素子の集積化が容易となると共に、素子に大きな電流を流すことが可能となる縦型電界効果トランジスタ及びその製造方法並びにそれを有する演算素子を低コストで提供する。

【解決手段】ソース電極層1、半導体層2及びドレイン電極層3が順次積層され、そして、それらの層の一方の側壁に接するように垂直方向に立てて設けたゲート電気絶縁層4及びゲート電極層5を順次有する電界効果型トランジスタにおいて、前記ソース電極層1及びドレイン電極層3を、6回回転対称軸を有する構造(正六角形)とする。

【選択図】 図1

会社リコー内

Fターム(参考) 5F048 AA08 AB03 AC04 BB04 BB09

#### 【特許請求の範囲】

## 【請求項1】

ソース電極層、半導体層及びドレイン電極層が順次積層され、そして、それらの層の一方の側壁に接するように垂直方向に立てて設けたゲート電気絶縁層及びゲート電極層を順次有する電界効果型トランジスタにおいて、前記ソース電極層、半導体層及びドレイン電極層を、6回回転対称軸を有する構造としたことを特徴とする縦形電界効果トランジスタ。

#### 【 請 求 項 2 】

前記半導体層が、有機半導体材料で構成されていることを特徴とする請求項1に記載の縦型電界効果トランジスタ。

#### 【請求項3】

前記有機半導体材料が、 1 ナフタレン、アントラセン、テトラセン、ペンタセン、ヘキサセン及びそれらの誘導体よりなる群から選択されるアセン分子材料、 2 フタロシアニン系化合物、アゾ系化合物及びペリレン系化合物よりなる群から選択される顔料及びその誘導体、 3 ヒドラゾン化合物、トリフェニルメタン化合物、ジフェニルメタン化合物、ジフェニルメタン化合物、スチルベン化合物、アリールビニル化合物、ピラゾリン化合物、トリフェニルアミン化合物、フェニレン誘導体及びトリアリールアミン化合物よりなる群から選択される低分子化合物並びにそれらの誘導体、或いは、 4 ポリ・N・ビニルカルバゾール、ハロゲン化ポリ・N・ビニルカルバゾール、ポリビニルピレン、ポリビニルアントラセン、ポリチオフェン誘導体、チオフェンオリゴマー誘導体、ピレンホルムアルデヒド樹脂、ポリアセチレン誘導体、及び、エチルカルバゾールホルムアルデヒド樹脂よりなる群から選択される高分子化合物、であることを特徴とする請求項2に記載の縦型電界効果トランジスタ。

## 【請求項4】

前記半導体層が、無機半導体材料で構成されていることを特徴とする請求項 1 に記載の縦型電界効果トランジスタ。

## 【請求項5】

前記無機半導体材料が、酸化亜鉛、酸化スズ等の金属酸化物、或いは、チタン酸ストロンチウム等の複合酸化物よりなる群から選択される無機半導体材料であることを特徴とする請求項4に記載の縦型電界効果トランジスタ。

#### 【請求項6】

前記ゲート電気絶縁層が、有機電気絶縁材料で構成されていることを特徴とする請求項 1~5のいずれかに記載の縦型電界効果トランジスタ。

#### 【請求項7】

前記有機電気絶縁材料が、ポリビニルアルコール、ポリビニルブチラール、フェノール樹脂、ノボラック樹脂等の水酸基を有する電気絶縁性のポリマー、及び、ポリアクリロニトリル等のシアノ基を有する電気絶縁性のポリマーよりなる群から選択される少なくとも 1種の有機電気絶縁材料であることを特徴とする請求項 6 に記載の縦型電界効果トランジスタ。

## 【請求項8】

前記ソース電極層、ドレイン電極層及びゲート電極層が、クロム(Cr)、タリウム(Ta)、チタン(Ti)、銅(Cu)、アルミニウム(Al)、モリブデン(Mo)、タングステン(W)、ニッケル(Ni)、金(Au)、パラジウム(Pd)、白金(Pt)、銀(Ag)、錫(Sn)、導電性ポリアニリン、導電性ポリピロール、導電性ポリチアジル及び導電性ポリマよりなる群から選択される少なくとも1種の導電性材料で構成されていることを特徴とする請求項1~7のいずれかに記載の縦型電界効果トランジスタ。

## 【請求項9】

(イ)基板の上にソース電極層を形成する工程、

(ロ)前記ソース電極層の右側壁に接するように垂直方向に立てたゲート電気絶縁層、前記ソース電極層の左側壁に接するように立てた第1の素子分離電気絶縁層、及び、前記ソース電極層の右側壁よりゲート電気絶縁層の幅だけ離して垂直方向に立てた第2の素子間

10

20

30

40

30

40

50

分離電気絶縁層、を形成する工程、

(ハ)前記ゲート電気絶縁層と第1の素子間分離電気絶縁層との間の前記ソース電極層の上に半導体層を形成する工程、

(二)前記ゲート電気絶縁層と第2の素子間分離電気絶縁層との間の前記基板の上にゲート電極層を形成する工程、

(ホ)前記ゲート電気絶縁層と第1の素子間分離電気絶縁層との間の前記半導体層の上に ドレイン電極層を形成する工程、

を順次有することを特徴とする縦型電界効果トランジスタの製造方法。

#### 【請求項10】

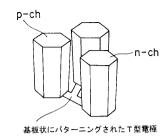

基板上にパターニングされたT型電極上に、p‐ch、n‐ch及び導電部材(Vout)を互いに導通するように有し、そして、前記p‐ch及びn‐chのゲート電極層に密着するよう設けられたゲート電圧を印加する導電部材(Vin)を有する演算素子であって、前記p‐chが、請求項1~8のいずれかに記載の有機半導体層を正孔輸送材料で構成した縦型電界効果トランジスタで形成され、そして、前記n‐chが、請求項1~8のいずれかに記載の有機半導体層を電子輸送材料で構成した縦型電界効果トランジスタで形成されていることを特徴とする演算素子。

### 【発明の詳細な説明】

### [0001]

### 【発明の属する技術分野】

本発明は、縦型電界効果トランジスタ及びその製造方法並びにそれを有する演算素子に関し、さらに、詳しくは、ソース電極層、半導体層及びドレイン電極層が順次積層された、電気信号によって電流値を制御するトランジスタ性能の向上を実現させた、縦型電界効果トランジスタ及びその製造方法並びにそれを有する、シートディスプレイ、シートコンピュータ装置等に用いられる、演算素子に関する。

### [0002]

#### 【従来の技術】

半導体層(活性層)を無機半導体材料で構成した薄膜電界効果型トランジスタは、斯界で知られている(非特許文献 1 参照)。

## [0003]

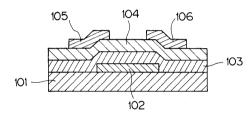

かかる半導体層(活性層)を無機半導体材料で構成した薄膜電界効果型トランジスタは、すでに、工業製品としても製造されている。図13は、従来の半導体層を無機半導体材料で構成した薄膜電界効果型トランジスタは、基板101に対し、横方向に配置されている。ソース電極層105及びドレイン電極層106は、電気的に中性である無機半導体層(チャネル層領域)104により分離されて設けられている。ゲート電極102は、ゲート電気絶縁層103により無機半導体層104と電気的に分離されて、基板101の上に配置している。無機半導体層104を構成する半導体材料としては、無機アモルファス材料(水素化アモルファスSi)、無機多結晶材料等の無機材料が用いられている。

### [0004]

また、半導体層を有機半導体材料で構成した薄膜電界効果型トランジスタも、斯界で知られている(非特許文献 2 参照)。

## [0005]

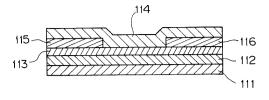

図14は、従来の半導体層を有機半導体材料で構成した薄膜電界効果型トランジスタである。図14に示すように、従来の半導体層を有機半導体材料で構成した薄膜電界効果型トランジスタも、前記半導体層を有機半導体材料で構成した薄膜電界効果型トランジスタと同様に、基板111に対し、横方向に配置されている。ソース電極層115及びドレイン電極層116は、電気的に中性である有機半導体層(チャネル層領域)114により分離されて設けられている。ゲート電極112は、ゲート電気絶縁層113により有機半導体層114と電気的に分離されて、基板111の上に配置している。有機半導体層114を

構成する半導体材料としては、 電子共役系の高分子化合物、芳香族化合物等の有機材料が用いられてきた。

[0006]

【特許文献1】

特開平10-270712号公報

【特許文献2】

特開平10-190001号公報

【非特許文献1】

D. B. Thomasson & al., IEEE El. Dev.Lett., Vol. 18, p.117; March 1997

【非特許文献2】

A. Dodabalapur & al., Appl. Phys. Lett., Vol. 69, pp. 4227-29, December 1996

[0007]

【発明が解決しようとする課題】

これらの薄膜電界効果型トランジスタは、ゲート電気絶縁層を介してゲート電極層より印可された電界が半導体層(チャネル部)に作用して、ソース電極層とドレイン電極層に有間に流れる電流を制御することによりトランジスタ動作を実現している。半導体層に有機材料を用いた薄膜電界効果型トランジスタと比べて、 1 真空を用いないで素子を作製できること、 2 広い面積の均一な素子を作製できること、 3 ソース/ドレイン領域の形成を行わずに電極配線ができること、等による製造方法の簡便さのために、製造コストを低減できる、という利点を有している。しかしながら、半導体層に有機材料を用いた薄膜電界効果型トランジスタは、半導体層に水素化アモルファスSiのような無機材料を用いた薄膜電界効果型トランジスタと比べて、(a)キャリア移動度(トランジスタ性能を示す)が低いこと、(b)大電流を流せないこと、(c)高速動作ができないこと、等の問題があった。

[0008]

従来、このような問題を解決するために開発された技術としては、例えば、 共役高分子の共役状態を制御する技術、分子電気伝導異方性を用いる技術、等の有機半導体材料に係わる技術、及び、蒸着法にて有機高分子膜を得る際に高い結晶性を実現させる技術があった。

[0009]

前記図13に示される従来の半導体層を無機半導体材料で構成した薄膜電界効果型トランジスタは、ソース電極層とドレイン電極層との間に電圧を印加した状態でゲート電極に電圧を印加して、ゲート電気絶縁層と半導体層との界面にチャネルを誘起させることにより、ソース電極層とドレイン電極との間に電流を流すものである。この時のソース電極層とドレイン電極層との間の電流(Id )は、一般に、次の数式で表すことができる。

[0010]

【数1】

$I_d = \frac{W \cdot C_{ox}}{2 \cdot I} \mu \left( V_g - V_{th} \right)^2 \tag{1}$

但し、数式中における  $C_{ox}$  ,  $\mu$  ,  $V_{g}$  及び  $V_{th}$  は、次のとおりのものである。

C<sub>o x</sub> : ゲート容量 ( F / m<sup>2</sup> )

μ : 電界効果移動度(cm²/Vs)

V g : ゲート電圧(V) V t h : しきい値電圧(V )

50

40

10

20

#### [0011]

限られたトランジスタ寸法(W:ゲート幅、L:ゲート長)内でトランジスタ性能を向上させるには、より高いId 値を実現すればよい。式(1)より、Id を向上させるW,L以外の因子としては、Соx、 $\mu$ の増加が考えられる。従来においては、比誘電率の高い材料を用いて実効的なСоxを向上させたもの(前記特許文献1参照)、 共役系高分子材料の開発により $\mu$ を向上させたもの(前記特許文献2参照。)等が報告されているが、式(1)において、特に、Lを減少させることは、高いId を得るのに得策である

### [0012]

Siテクノロジーにおいては、当初10μm幅のゲート長が、現在では0.1μm程度まで縮小されつつある。これはCoxやμの開発を行わなくて、Id 値において100倍の増加をもたらすこととなる。この短ゲート長の傾向は、これまでは、リソグラフィー加工限界の向上に主に依存してきた。前記図14に示される従来の半導体層を有機半導体材料で構成した薄膜電界効果型トランジスタでは、ゲート長が10~5μm幅であるものがもっぱら試作されているが、リソグラフィー加工技術では、それ以上にゲート長を短くすることは難しいという問題があった。

#### [0013]

有機半導体材料をトランジスタの製造に用いる利点は、低製造コストであるところ、Siテクノロジーで開発されたリソグラフィー加工技術を有機半導体材料を用いたトランジスタの製造に用いることは、有機トランジスタの利点である低製造コストの概念から反するものとなるので、この技術を積極的に採用することはありえないと考えられる。ソフトリソグラフィーなる概念の工法を用いて有機トランジスタを製造することが提案されているが、この工法を用いても前述のとおり10~5μmのゲート長のものしか製造できないのが現状であるので、ゲート長を短くすることは難しいという問題があった。

#### [ 0 0 1 4 ]

本発明は、かかる問題を解決することを目的としている。

即ち、本発明は、実行的電界移動度を向上させることができ、しかも、素子の集積化が容易となると共に、素子に大きな電流を流すことが可能となる縦型電界効果トランジスタ及びその製造方法並びにそれを有する演算素子を低コストで提供することを目的としている

#### [0015]

## 【課題を解決するための手段】

本発明者は、電界効果トランジスタの構造を工夫することにより、キャリア移動度の向上と、素子の集積化とを同時に達成できないかとと考えて、電界効果トランジスタの構造について探求したところ、ソース電極層、半導体層及びドレイン電極層が順次積層され、そして、それらの層の一方の側壁に接するように垂直方向に立てて設けたゲート電気絶縁層及びゲート電極層を順次有する電界効果型トランジスタにおいて、前記ソース電極層、半導体層及びドレイン電極層を、6回回転対称軸を有する構造(正六角形)としたところ、実行的電界移動度を向上させることができ、しかも、素子の集積化が容易となると共に、素子に大きな電流を流すことが可能となることを見いだして、本発明を完成するに至った

## [0016]

即ち、請求項1に記載された発明は、上記目的を達成するために、ソース電極層、半導体層及びドレイン電極層が順次積層され、そして、それらの層の一方の側壁に接するように垂直方向に立てて設けたゲート電気絶縁層及びゲート電極層を順次有する電界効果型トランジスタにおいて、前記ソース電極層、半導体層及びドレイン電極層を、6回回転対称軸を有する構造としたことを特徴とする縦形電界効果トランジスタである。

## [0017]

請求項2に記載された発明は、請求項1に記載された発明において、前記半導体層が、有機半導体材料で構成されていることを特徴とするものである。

20

30

[0018]

請求項3に記載された発明は、請求項2に記載された発明において、前記有機半導体材料が、 1 ナフタレン、アントラセン、テトラセン、ペンタセン、ヘキサセン及びそれらの誘導体よりなる群から選択されるアセン分子材料、 2 フタロシアニン系化合物、アゾ系化合物及びペリレン系化合物よりなる群から選択される顔料及びその誘導体、 3 ヒドラゾン化合物、トリフェニルメタン化合物、ジフェニルメタン化合物、スチルベンと合物、アリールビニル化合物、ピラゾリン化合物、トリフェニルアミン化合物、フェニレン誘導体及びトリアリールアミン化合物よりなる群から選択される低分子化合物並びにそれらの誘導体、或いは、 4 ポリ・N・ビニルカルバゾール、ポリビニルピレン、ポリビニルアントラセン、ポリチオフェン誘導体、エチオフェンオリゴマー誘導体、ピレンホルムアルデヒド樹脂、ポリアセチレン誘導体、及び、エチルカルバゾールホルムアルデヒド樹脂よりなる群から選択される高分子化合物、であることを特徴とするものである。

[0019]

請求項4に記載された発明は、請求項1に記載された発明において、前記半導体層が、無機半導体材料で構成されていることを特徴とするものである。

[ 0 0 2 0 ]

請求項5に記載された発明は、請求項4に記載された発明において、前記無機半導体材料が、酸化亜鉛、酸化スズ等の金属酸化物、或いは、チタン酸ストロンチウム等の複合酸化物よりなる群から選択される無機半導体材料であることを特徴とするものである。

[0021]

請求項6に記載された発明は、請求項1~5のいずれかに記載された発明において、前記ゲート電気絶縁層が、有機電気絶縁材料で構成されていることを特徴とするものである。

[0022]

請求項7に記載された発明は、請求項6に記載された発明において、前記有機半導体材料が、ポリビニルアルコール、ポリビニルブチラール、フェノール樹脂、ノボラック樹脂等の水酸基を有する電気絶縁性のポリマー、及び、ポリアクリロニトリル等のシアノ基を有する電気絶縁性のポリマーよりなる群から選択される少なくとも1種の有機半導体材料であることを特徴とするものである。

[ 0 0 2 3 ]

請求項8に記載された発明は、請求項1~7のいずれかに記載された発明において、前記ソース電極層、ドレイン電極層及びゲート電極層が、クロム(Cr)、タリウム(Ta)、チタン(Ti)、銅(Cu)、アルミニウム(Al)、モリブデン(Mo)、タングステン(W)、ニッケル(Ni)、金(Au)、パラジウム(Pd)、白金(Pt)、銀(Ag)、錫(Sn)、導電性ポリアニリン、導電性ポリピロール、導電性ポリチアジル及び導電性ポリマよりなる群から選択される少なくとも1種の導電性材料で構成されていることを特徴とするものである。

[0024]

請求項9に記載された発明は、

(イ)基板の上にソース電極層を形成する工程、

(ロ)前記ソース電極層の右側壁に接するように垂直方向に立てたゲート電気絶縁層、前記ソース電極層の左側壁に接するように立てた第1の素子分離電気絶縁層、及び、前記ソース電極層の右側壁よりゲート電気絶縁層の幅だけ離して垂直方向に立てた第2の素子間分離電気絶縁層、を形成する工程、

(ハ)前記ゲート電気絶縁層と第1の素子間分離電気絶縁層との間の前記ソース電極層の 上に半導体層を形成する工程、

(二)前記ゲート電気絶縁層と第2の素子間分離電気絶縁層との間の前記基板の上にゲート電極層を形成する工程、

(ホ)前記ゲート電気絶縁層と第1の素子間分離電気絶縁層との間の前記半導体層の上にドレイン電極層を形成する工程、

20

30

50

を順次有することを特徴とする縦型電界効果トランジスタの製造方法である。

#### [0025]

請求項10に記載された発明は、基板上にパターニングされたT型電極上に、p‐ch、n‐ch及び導電部材(Vout )を互いに導通するように有し、そして、前記p‐ch及びn‐chのゲート電極層に密着するよう設けられたゲート電圧を印加する導電部材(Vin)を有する演算素子であって、前記p‐chが、請求項1~8のいずれかに記載の有機半導体層を正孔輸送材料で構成した縦型電界効果トランジスタで形成され、そして、前記n‐chが、請求項1~8のいずれかに記載の有機半導体層を電子輸送材料で構成した縦型電界効果トランジスタで形成されていることを特徴とする演算素子である。

#### [0026]

【発明の実施の形態】

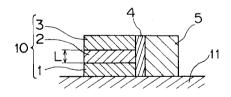

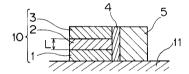

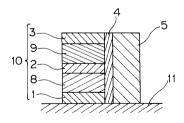

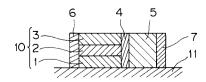

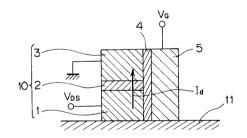

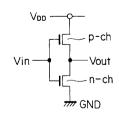

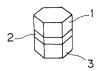

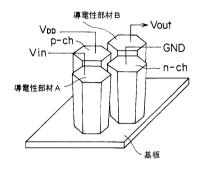

図1は、本発明の一実施の形態を示す縦型電界効果トランジスタの断面図である。図2は、本発明の他の一実施の形態を示す縦型電界効果トランジスタの断面図である。図3は、本発明の他の一実施の形態を示す縦型電界効果トランジスタの断面図である。図4は、本発明の縦型電界効果トランジスタを駆動させるための電気的接続と動作を説明するための説明図である。図5は、演算素子が有する論理回路の説明図である。図6は、演算素子の論理演算回路におけるp-ch及びn-chが有する縦型電界効果トランジスタの説明図である。図7は、本発明の一実施の形態を示す縦型電界効果トランジスタを有する演算素子の説明図である。図8は、p-ch、n-ch及びVoutを接続するT型電極の説明図である。図9は、本発明の一実施の形態を示す縦型電界効果トランジスタの製造工程を説明するための説明図である。図10は、マイクロコンタクトプリンティングの工程を説明するための説明図である。

### [0027]

図1に示されているように、本発明の縦型電界効果トランジスタは、ソース電極層1、半導体層2及びドレイン電極層3が順次積層された、そして、それらの層の一方の側壁に接するように垂直方向に立てて設けたゲート電気絶縁層4及びゲート電極層5を順次有している。そして、前記ソース電極層、半導体層及びドレイン電極層は、6回回転対称軸を有する構造(正六角形)とされている。

## [0028]

図4に示されているように、ソース・ドレイン電圧VDSにより、ソース電極層1とドレイン電極層3の間に流れる電流Id はゲート電極層5にゲート電圧VG を印加したとき、ゲート電気絶縁層4を介し、電界による半導体層2とゲート電気絶縁層との界面にチャネルが形成され、電流Idが流れる.この電流Idは、配置されているソース電極層1及びドレイン電極層3を流れるので、基板11の面に直行するように電流が流れる.

## [ 0 0 2 9 ]

図1,4に示されているように、本発明の縦型電界効果トランジスタによれば、電流(Id)を基板11の面に直交する方向に流し、そして、活性領域10の一方の外側に設けられた第3の電極層から第1の電気絶縁層4を介して半導体層2、即ち、半導体領域に電界が印可する構造となっているので、半導体層2の膜厚(上記式(1)におけるゲート長Lに相当する)をいっそう薄くすることができ、そのために、フォトリソグラフィー加工を用いなくても、ゲート長Lを短くして飛躍的な短チャネル長を構造的に実現でき、よって、トランジスタ性能、即ち、実行的電界移動度を向上させることができる。また、縦型電界効果トランジスタの構造がシンプルであるので、製造工程を簡略化することができ、そのために、縦型電界効果トランジスタの製造コストを低減することができる。

#### [0030]

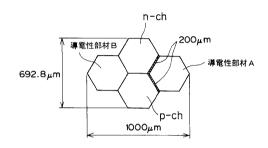

本発明の縦型電界効果トランジスタを有する演算素子は、図5に示される論理回路を有している。この縦型電界効果トランジスタは、図7に示されているように、ドレイン電極、半導体層(この厚みがチャネル)、ソース電極を順次積層したものであり、この導電性部材Aと接する面は、ゲート電気絶縁層(図1の1参照)によって覆われている。本発明の縦型電界効果トランジスタを有する演算素子は、図7、8に示されているように、基板上

10

20

30

40

30

40

50

にパターニングされたT型電極上にp‐ch、n‐ch及び導電性部材(Vout )Bを互いに導通するように有し、そして、前記p‐ch及びn‐chのゲート電極層に密着するよう設けられたゲート電圧を印加する導電部材(Vin)を有している。前記「p‐ch」は、有機半導体層を正孔輸送材料で構成した縦型電界効果トランジスタによって形成され、そして、前記「n‐ch」は、有機半導体層を電子輸送材料で構成した縦型電界効果トランジスタによって形成される。図7において、VDDは、電源である。

[ 0 0 3 1 ]

このように、縦型電界効果トランジスタにおけるソース電極層 1 及びドレイン電極層 3 が、6回回転対称軸構造(正六角形)を有していることにより、円柱形状となっているもの、又は、対称軸を有していないものと比較して、素子の集積化が容易となる。さらに、ゲート電極層(図 1 の 5 参照)については、ゲート電気絶縁層(図 1 の 4 参照)を介して面で半導体層 2 にゲート電圧を印加できるので、チャネル幅を増加させることが可能となり、素子に大きな電流を流すことが可能となる。

[0032]

[0033]

図3に示すように、本発明の縦型電界効果トランジスタは、前記ソース電極1、半導体層2及びドレイン電極層3の他方の側壁、即ち、活性領域10の他方の側壁に接するように、垂直方向に立てて設けた素子間分離電気絶縁層6、及び、前記ゲート電極層5の外側の側壁に接するように垂直方向に設けた素子間分離電気絶縁層7を有することができる。このような素子間分離電気絶縁層7は、素子分離をするのに有効であり、また、本発明の縦型電界効果トランジスタを製造する際において、ソース電極層1、半導体層2及びドレイン電極層3を縦方向に順次、成膜するための型枠として、また、ゲート電極層5を成膜するための型枠として有効に作用する。

[0034]

本発明における半導体層 2 は、有機半導体材料で構成される。かかる有機半導体材料は、好ましくは、 1 ナフタレン、アントラセン、テトラセン、ペンタセン、ヘキサセン及びそれらの誘導体よりなる群から選択されるアセン分子材料、 2 フタロシアニン系化合物、アゾ系化合物及びペリレン系化合物よりなる群から選択される顔料及びその誘導体、 1 ヒドラゾン化合物、トリフェニルメタン化合物、ジフェニルメタン化合物、ストリフェニルアミン化合物、アリールビニル化合物、ピラゾリン化合物、トリフェニルアミン化合物、ステルベン化合物、アリールアミン化合物よりなる群から選択される低分子化ポリュニートの誘導体、或いは、 4 ポリ・N・ビニルカルバゾール、パロゲン化ポリン誘導体、チオフェンオリゴマー誘導体、ピレンホルムアルデヒド樹脂、ポリアセチレン誘導体、及び、エチルカルバゾールホルムアルデヒド樹脂よりなる群から選択される高分子化合物である。また、フルオレノン系、ジフェノキノン系、ベンゾキノン系、アントラ

キノン系、インデノン系化合物も使用可能である。このように、半導体層 2 を構成する材料が有機半導体材料であると、高分子有機半導体材料では、その溶液を印刷法、インクジェット法等の手段により成膜することができ、また、低分子有機半導体材料では、これを真空蒸着法等の手段により成膜することができるので、極めて薄い有機半導体層を低コストで形成することができる。

[0035]

また、本発明における半導体層2は、無機半導体材料で構成される。かかる無機半導体材料は、好ましくは、酸化亜鉛、酸化スズ等の金属酸化物、或いは、チタン酸ストロンチウム等の複合酸化物よりなる無機半導体材料である。このように、半導体層2を構成する材料が無機半導体材料であると、有機半導体材料を用いたものと比較し、高速応答の可能な縦型電界効果トランジスタが作製可能となる。

[0036]

本発明におけるゲート電気絶縁層4は、有機電気絶縁材料で構成されている。かかる有機電気絶縁材料は、好ましくは、ポリビニルアルコール、ポリビニルブチラール、フェノール樹脂、ノボラック樹脂等の水酸基を有する電気絶縁性のポリマー、及び、ポリアクリロニトリル等のシアノ基を有する電気絶縁性のポリマーよりなる群から選択される少なくとも1種の有機電気絶縁材料である。このように、ゲート電気絶縁層が有機電気絶縁材料で構成されていると、真空真空蒸着法を用いることなく、印刷法、インクジェット法等の手段を用いて、ゲート電気絶縁層を形成することができるので、装置コスト及び製造コストを低減することができる。

[0037]

本発明における前記ソース電極層1、ドレイン電極層3及びゲート電極層5は、クロム(Cr)、タリウム(Ta)、チタン(Ti)、銅(Cu)、アルミニウム(Al)、モリブデン(Mo)、タングステン(W)、ニッケル(Ni)、金(Au)、パラジウム(Pd)、白金(Pt)、銀(Ag)、錫(Sn)、導電性ポリアニリン、導電性ポリピロール、導電性ポリチアジル及び導電性ポリマよりなる群から選択される少なくとも1種の導電性材料で構成されている。

[0038]

本発明の縦型電界効果トランジスタは、例えば、絶縁性基板11上に形成される。

[0039]

本発明の縦型電界効果トランジスタの好ましい製造例

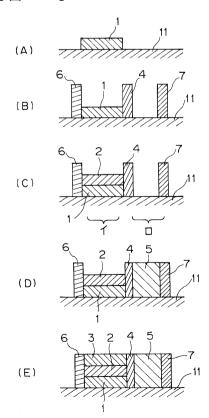

本発明の縦型電界効果トランジスタは、図11(A)~(E)に示されるように、

(イ)基板の上にソース電極層を形成する工程(A)、

(ロ)前記ソース電極層の右側壁に接するように垂直方向に立てたゲート電気絶縁層、前記ソース電極層の左側壁に接するように立てた第1の素子分離電気絶縁層、及び、前記ソース電極層の右側壁よりゲート電気絶縁層の幅だけ離して垂直方向に立てた第2の素子間分離電気絶縁層、を形成する工程(B)、

(ハ)前記ゲート電気絶縁層と第1の素子間分離電気絶縁層との間の前記ソース電極層の上に半導体層を形成する工程(C)、

(二)前記ゲート電気絶縁層と第2の素子間分離電気絶縁層との間の前記基板の上にゲート電極層を形成する工程(D)、

(ホ)前記ゲート電気絶縁層と第1の素子間分離電気絶縁層との間の前記半導体層の上にドレイン電極層を形成する工程(E)、

を順次経て製造される。

なお、図11(C)において、イは、活性層領域であり、口はゲート電極領域である。

[0040]

前記(イ)工程においては、第1の電極層1は、例えば、ガラス基板(11)の上に金(Au)を蒸着法等の周知の薄膜形成法により成膜することにより形成される。一般に、ガラス基板とAu膜は密着力が乏しいので、密着層として、クロム(Cr)、チタン(Ti)、タリウム(Ta)等の金属膜を配置するのが好ましい。Au膜を用いる場合には、ア

20

30

50

ルカンチオール系有機材料が A u 膜表面に自己制御単分子吸着膜を形成するので、マイクロコンタクトプリンティング法を用いて、基板上の全面に成膜した A u 膜の所望する領域にアルカンチオールの転写を行い、続いて、ウェットエッチングにより露出している部分の A u 膜を除去して、電極パターン、即ち、ソース電極層 1 を形成する。

#### [ 0 0 4 1 ]

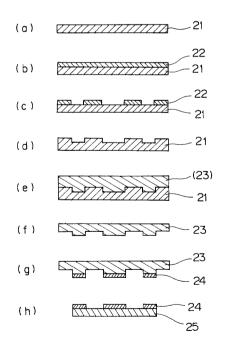

前記「マイクロコンタクトプリンティング法」は、図10(a)~(h)に示すように、

- 1 マスター(主として、Si基板)21を準備する工程(a)、

- 2 前記マスター 2 1 の上にレジスト 2 2 を全面に被覆する工程(b)、

- 3 フォトリソグラフィ・エッチングにて前記レジスト 2 2 の所望箇所を除去してマスター 2 1 にパターンを形成する工程( c )、

- 4 残余の前記レジスト22を除去する工程(d)

- 5 このパターンを形成したマスター 2 1 の上にポリジメチルシロキサン( 2 3 )を流し込み、これを熱処理する工程( e )、

- 6 この熱処理したポリジメチルシロキサン 2 3 をマスター 2 1 から剥がして版 2 3 を 形成する工程( f )、

- 7 このようにして形成した版 2 3 にアルカンチオールインク 2 4 を付ける工程(g)

- 8 このアルカンチオールインク 2 4 をインク付けした版 2 3 を用いて基板に成膜された A u 蒸着膜上に転写する工程(h)、

を順次へて行われる。

#### [0042]

前記ポリジメチルシロキサンは、柔軟な樹脂であるが、マスターパターンからの転写する条件を適正化すれば、この樹脂で形成した版は、5μm程度の解像度を有している。このようにして形成した版にアルカンチオールインクを付け、Au蒸着膜に転写することで、アルカンチオール自己制御組織化膜が形成される。この組織化膜は、Auとチオール基が結合し、両面にはアルキル基が露出しているために、よう素/よう化アンモニウム水溶液のような極性溶媒エッチング液にAu蒸着膜基板を浸漬すると、アルカンチオールの無い部位のみがエッチングされる(前記本発明の(A)工程参照)。従来のフォトリソグラフィ・エッチングでは、その都度、レジスト塗布、露光、現像、エッチング、及び、レジスト剥離を順次経てパターン膜を得る方法と比較すると、このような「マイクロコンタクトプリンティング法」を用いれば、一度、版を作製するのみで、多量の膜加工が出来、製造コストの低減に好適である。

#### [0043]

前記(ロ)の工程においては、好ましくは、フォトレジストをスピンコートしてフォトレジスト膜を形成した後、ゲート電気絶縁層4、素子間分離電気絶縁層6及び素子間分離電気絶縁層7の幅に露光、現像して、ゲート電気絶縁層4、素子間分離電気絶縁層6及び素子間分離電気絶縁層7を形成する。このようなゲート電気絶縁層4、素子間分離電気絶縁層6及び素子間分離電気絶縁層7は、本発明の縦型電界効果トランジスタを製造する際において、ソース電極層1、半導体層2及びドレイン電極層3を縦方向に順次、成膜するための型枠として、また、ゲート電極層5を成膜するための型枠として有効に作用する。しかし、素子間分離電気絶縁層6及び素子間分離電気絶縁層7は、素子分離膜として用いないのであれば、すべての膜を形成した後に、除去してもかまわない。

## [0044]

前記ゲート電気絶縁層4の材料は、前記式(1)で示されるC。×を高めるため、比誘電率の高いものが好ましい。有機材料は、各種加工性に優れているので、このような電気絶縁層に特に好ましい。ノボラック樹脂にナフトキノンジアジド紫外線感光基を導入した、所謂ポジ型フォトレジストは、有機材料の中では、比較的比誘電率が高いので好ましい。前記基板11の上に、フォトレジストを塗布、プリベークした後、高圧水銀ランプにて露光処理、現像処理、及び、ポストベーク処理を順次施して、これらの電気絶縁層を形成する。この際、後工程でのレジスト膜変質を防ぐためにUVキュア処理、280 以下のハ

10

20

30

30

40

50

ードベーク処理を行ってもよい。

### [0045]

本発明においては、好ましくは、前記(八)の工程で、高分子有機半導体材料の溶液をインクジェット法、凸版印刷法、凹版印刷法、オフセット印刷法、スクリーン印刷法等の手段により成膜するか、又は、低分子有機半導体材料を真空蒸着法、分子線蒸着法等の手段により成膜して、半導体層を形成する。また、真空成膜法を用いる場合には、酸化亜鉛、酸化スズ等の金属酸化物、チタン酸ストロンチウム等の複合酸化物からなる無機半導体材料も成膜出来る。

### [0046]

本発明においては、好ましくは、前記(イ)の工程、(二)の工程及び(ホ)の工程で、 ソース電極層、ドレイン電極層及びゲート電極層を、高分子導電性材料の溶液を印刷法、 インクジェット法、凸版印刷法、凹版印刷法、オフセット印刷法、スクリーン印刷法等の 手段により成膜するか、又は、金属を真空蒸着法、イオンプレーティング法、スパッタリ ング法、メッキ法等の手段により成膜して、ソース電極層、ドレイン電極層及びゲート電 極層を形成する。

### [0047]

本発明の縦型電界効果トランジスタは、前記(イ)工程~(ホ)工程を経て製造するので、 1 半導体層の膜厚をいっそう薄くすることができるので、実行的電界移動度を向上させることができ、 2 ソース電極層、半導体層及びドレイン電極層を6回回転対称軸を有する構造(正六角形)とするので、素子の集積化が容易となり、また、 3 チャネル幅を増加させることが可能となり、素子に大きな電流を流すことができる。

#### [0.048]

本発明においては、縦型電界効果トランジスタの製造において、基板の上に垂直方向に立てて設けた一対の電気絶縁層の間に有機半導体材料の溶液を塗布して有機半導体層及び/又は無機半導体及び/又は導電層を形成する。このように、基板の上に垂直方向に立てて設けた一対の電気絶縁層の間に有機半導体材料の溶液を塗布して有機半導体層及び/又は無機半導体及び/又は導電層を形成すると、基板の上に垂直方向に立てて設けた一対の電気絶縁層が有機半導体層及び/又は無機半導体及び/又は導電層を成膜するための型枠として有効に作用するので、有機半導体層及び/又は無機半導体及び/又は導電層を低コストで成膜することができる。

#### [0049]

本発明の演算素子は、基板上にパターニングされたT型電極上に、p‐ch、n‐ch及び導電部材(Vout )Bを互いに導通するように有し、そして、前記p‐ch及びn‐chのゲート電極層に密着するよう設けられたゲート電圧を印加する導電部材(Vin)Aを有している。そして、前記p‐chが、請求項1~8のいずれかに記載の有機半導体層を正孔輸送材料で構成した縦型電界効果トランジスタで形成され、そして、前記n‐chが、請求項1~8のいずれかに記載の有機半導体層を電子輸送材料で構成した縦型電界効果トランジスタで形成されている。

## [0050]

本発明の演算素子は、このように、基板上にパターニングされたT型電極上に、p‐ch、n‐ch及び導電部材(Vout )Bを互いに導通するように有し、そして、前記専部材(Vin)Aを有し、しかも、前記p‐chが、請求項1~8のいずれかに記載の有機半導体層を正孔輸送材料で構成した縦型電界効果トランジスタで形成され、そしてした。前記n‐chが、請求項1~8のいずれかに記載の有機半導体層を電子輸送材料で構成した縦型電界効果トランジスタで形成されているので、 1 半導体層の膜厚をいっそうでは、実行的電界移動度を向上させることができ、 2 ソースで配層、半導体層及びドレイン電極層を6回回転対称軸を有する構造とするので、素子に大きな電流を流すことができ、よって、入力信号に対する演算結果を高速で出力することが

できる。

[0051]

### 【実施例】

(実施例1)

( 1 ) ガラス基板上に密着膜としてCr膜を30nm幅に成膜し、続いて、このCr膜の上にAu膜を70nm幅に成膜した。

(2)前記Au膜上にアルカンチオールインクをインク付けした版を用いて転写し、この基板をよう素 / よう化アンモニウム水溶液よりなるエッチング液に浸漬して、Au膜をエッチングし、続いて、この基板を硝酸セリウムアンモニウムを含む硝酸水溶液に浸漬して Cr膜をエッチングすることによりT型電極(図8参照)を形成した。

(3)フォトレジスト(東京応化社製、OFPR800)を前記基板上にスピンコーティングしてレジスト膜を3μmの厚さに成膜し、続いて、このレジスト膜を6回回転対称軸を有する構造(正六角形)に露光、現像した後、ポストベーク及びUVキュアを施して、前記第1の電極層の右側壁に接するように垂直方向に立てたゲート電極層を形成した。その際、トランジスタ動作部としての活性層の幅は、200μmとした(図9参照)。

#### [0052]

(4) 導電性高分子溶液(ダイエル社製、 P E D O T )を用いてドレイン電極層をインクジェット法により形成した後、精製した p 型半導体材料のポリヘキシルチオフェン(市販品)をクロロホルムに溶解した溶液とし、この溶液をインクジェット法にて成膜して、 p 型半導体層を形成した。その際、ポリヘキシルチオフェンの濃度を 0 . 5 重量 % 以下にした結果、約 1 0 0 n m 以下の p 型半導体層の形成が可能になった。

(5) さらに、次の式

## 【化1】

に示されるn型半導体材料をポリスチレン中に分散させた後、これをTHF中に溶解し、 得られた溶液をインクジェット法にて成膜して、p型半導体層を形成した。

(6)引き続きソース電極層及びゲート電極をインクジェット法にて形成して縦型電界効果トランジスタ素子を作製した。

[ 0 0 5 3 ]

(比較例1)

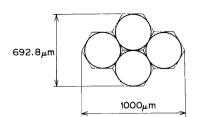

図12に示すように、パターニング形条を円形とした以外は、実施例1と同様にして縦型電界効果トランジスタ素子を作製した。このようにして得られた縦型電界効果トランジスタ素子のチャネル幅は、約10.5μmであった。

[0054]

## 【発明の効果】

(1)請求項1,8に記載された発明によれば、ソース電極層、半導体層及びドレイン電極層が順次積層され、そして、それらの層の一方の側壁に接するように垂直方向に立てて設けたゲート電気絶縁層及びゲート電極層を順次有する電界効果型トランジスタにおいて、前記ソース電極層、半導体層及びドレイン電極層を、6回回転対称軸を有する構造(正六角形)としたので、 1 半導体層の膜厚をいっそう薄くすることができ、そのために、フォトリソグラフィー加工を用いなくても、ゲート長Lを短くして飛躍的な短チャネル長を構造的に実現でき、よって、トランジスタ性能、即ち、実行的キャリア移動度を向上

10

20

30

50

20

30

40

50

させることができ、 2 縦型電界効果トランジスタが円柱形状となっているもの、又は、対称軸を有していないものと比較して、素子の集積化が容易となるなり、そして、 3 ゲート電気絶縁層を介して面で半導体層にゲート電圧を印加できることにより、チャネル幅を増加させることが可能となり、素子に大きな電流を流すことが可能となる。

[ 0 0 5 5 ]

(2)請求項2,3に記載された発明によれば、半導体層が有機半導体材料で構成されているので、高分子有機半導体材料では、その溶液を印刷法、インクジェット法等の手段により成膜することができ、また、低分子有機半導体材料では、これを真空蒸着法等の手段により成膜することができ、よって、極めて薄い有機半導体層を低コストで形成することができる。

[0056]

(3)請求項4,5に記載された発明によれば、半導体層が無機半導体材料で構成されているので、有機半導体材料を用いたものと比較し、高速応答の可能な縦型電界効果トランジスタが作製可能となる。

[0057]

(4)請求項6,7に記載された発明によれば、ゲート電気絶縁層が有機電気絶縁材料で構成されているので、真空真空蒸着法を用いることなく、印刷法、インクジェット法等の手段を用いて、ゲート電気絶縁層を形成することができ、そのために、装置コスト及び製造コストを低減することができる。

[0058]

(5)請求項9に記載された発明によれば、 1 半導体層の膜厚をいっそう薄くすることができるので、実行的電界移動度を向上させることができ、 2 ソース電極層、半導体層及びドレイン電極層を6回回転対称軸を有する構造(正六角形)とするので、素子の集積化が容易となり、また、 3 チャネル幅を増加させることが可能となり、素子に大きな電流を流すことができる。

[0059]

(6)請求項10に記載された発明によれば、 1 半導体層の膜厚をいっそう薄くすることができるので、実行的電界移動度を向上させることができ、 2 ソース電極層、半導体層及びドレイン電極層を6回回転対称軸を有する構造とするので、素子の集積化が容易となり、また、 3 チャネル幅を増加させることが可能となり、素子に大きな電流を流すことができ、よって、入力信号に対する演算結果を高速で出力することができる演算素子を低コストで提供することができる。

【図面の簡単な説明】

- 【図1】本発明の一実施の形態を示す縦型電界効果トランジスタの断面図である。

- 【図2】本発明の他の一実施の形態を示す半導体装置の断面図である。

- 【図3】本発明の他の一実施の形態を示す縦型電界効果トランジスタの断面図である。

- 【 図 4 】 本 発 明 の 縦 型 電 界 効 果 ト ラ ン ジ ス タ を 駆 動 さ せ る た め の 電 気 的 接 続 と 動 作 を 説 明 す る た め の 説 明 図 で あ る 。

- 【図5】演算素子が有する論理回路の説明図である。

- 【図 6 】、演算素子の論理演算回路における p c h 及び n c h が有する縦型電界効果トランジスタの説明図である。

- 【 図 7 】 本 発 明 の 一 実 施 の 形 態 を 示 す 縦 型 電 界 効 果 ト ラ ン ジ ス タ を 有 す る 演 算 素 子 の 説 明 図 で あ る 。

- 【図8】p-ch、n-ch及びVoutを接続するT型電極の説明図である。

- 【図9】本発明の一実施の形態を示す縦型電界効果トランジスタの製造工程を説明するための説明図である。

- 【図10】マイクロコンタクトプリンティングの工程を説明するための説明図である。

- 【図11】実施例1で得られた縦型電界効果トランジスタの平面図である。

- 【 図 1 2 】 比 較 例 1 で 得 ら れ た 縦 型 電 界 効 果 ト ラ ン ジ ス タ の 平 面 図 で あ る 。

- 【図13】従来の半導体層を無機半導体材料で構成した薄膜電界効果型トランジスタであ

る。

【図14】従来の半導体層を有機半導体材料で構成した薄膜電界効果型トランジスタである。

## 【符号の説明】

- 1 ソース電極層

- 2 半導体層

- 3 ドレイン電極層

- 4 ゲート電気絶縁層

- 5 ゲート電極層

- 6 , 7 素子間分離電気絶縁層

- 8 , 9 バッファー層

- 1 0 活性領域

- 1 1 基板

# 【図1】

# 【図2】

# 【図3】

# 【図4】

【図5】

# 【図6】

# 【図7】

# 【図8】

# 【図9】

# 【図10】

# 【図11】

【図12】

【図14】

【図13】

# フロントページの続き

(51) Int.CI.<sup>7</sup> F I テーマコード (参考)

H 0 1 L 29/78 H 0 1 L 27/08 3 2 1 G

H 0 1 L 51/00

F ターム(参考) 5F110 AA01 AA07 BB04 CC09 DD02 EE01 EE02 EE03 EE04 EE22

FF01 FF27 GG01 GG05 GG22 GG23 GG42 HK01 HK02 HK03

HK04 HK21 HK32 HK33 HM04 NN62 QQ06