# (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 108695239 B (45) 授权公告日 2021. 09. 21

(21) 申请号 201710224689.X

(22)申请日 2017.04.07

(65) 同一申请的已公布的文献号 申请公布号 CN 108695239 A

(43) 申请公布日 2018.10.23

(73) 专利权人 联华电子股份有限公司 地址 中国台湾新竹市 专利权人 福建省晋华集成电路有限公司

(72) 发明人 冯立伟 王嫈乔 何建廷 陈凯评

(74) **专利代理机构** 北京市柳沈律师事务所 11105

代理人 陈小雯

(51) Int.CI.

*H01L* 21/768 (2006.01) *H01L* 21/02 (2006.01)

#### (56) 对比文件

US 2004120179 A1,2004.06.24

KR 20010083349 A,2001.09.01

CN 1401139 A,2003.03.05

KR 20090128726 A,2009.12.16

审查员 廉海峰

权利要求书2页 说明书6页 附图10页

#### (54) 发明名称

具有接触插塞的半导体结构及其制作方法

#### (57) 摘要

本发明公开一种具有接触插塞的半导体结构及其制作方法,该具有接触插塞的半导体结构包含一基底,基底上定义有一存储器区以及一周边电路区,存储器区内包含有至少一存储单元,存储单元包含有一晶体管和一电容结构,一平坦化第一堆叠介电层包含二第一介电层和一第二介电层,第一介电层和第二介电层以第一介电层、第二介电层和第一介电层的顺序由下至上依序排列,其中在最下方的第一介电层延伸至存储器区并且覆盖电容结构,一接触插塞位于周边电路区并且贯穿平坦化第一堆叠介电层。

1.一种具有接触插塞的半导体结构,包含

基底,该基底上定义有一存储器区以及一周边电路区,该存储器区内包含有至少一存储单元,该存储单元包含有晶体管和电容结构;

平坦化第一堆叠介电层,覆盖该周边电路区,该平坦化第一堆叠介电层包含二第一介电层和一第二介电层,该二第一介电层和该第二介电层以该第一介电层、该第二介电层和该第一介电层的顺序由下至上依序排列,该第一介电层的材料和该第二介电层的材料不同,其中在最下方的该第一介电层延伸至该存储器区并且覆盖该电容结构;以及

接触插塞,位于该周边电路区并且贯穿整个该平坦化第一堆叠介电层。

- 2.如权利要求1所述的具有接触插塞的半导体结构,其中该第二介电层延伸至该存储器区并且覆盖该电容结构。

- 3.如权利要求1所述的具有接触插塞的半导体结构,其中该第二介电层的厚度是该平坦化第一堆叠介电层的厚度的十分之一至八分之一。

- 4.如权利要求1所述的具有接触插塞的半导体结构,其中该周边电路区内包含至少一栅极,该接触插塞电连结该栅极。

- 5.如权利要求1所述的具有接触插塞的半导体结构,其中该接触插塞的一末端位于该平坦化第一堆叠介电层中最下层的该第一介电层内。

- 6.如权利要求1所述的具有接触插塞的半导体结构,另包含一平坦化第二堆叠介电层位于该周边电路区并且覆盖该平坦化第一堆叠介电层,该平坦化第二堆叠介电层包含另一层该第二介电层和另一层该第一介电层由下至上排列。

- 7.如权利要求6所述的具有接触插塞的半导体结构,其中该接触插塞贯穿该平坦化第二堆叠介电层。

- 8.如权利要求1所述的具有接触插塞的半导体结构,其中该第二介电层未覆盖该电容结构。

- 9. 如权利要求1所述的具有接触插塞的半导体结构,其中该第二介电层包含氮化硅、氮氧化硅、氮碳化硅、或金属氧化物。

- 10.一种具有接触插塞的半导体结构的制作方法,包含:

提供一基底,该基底上定义有一存储器区以及一周边电路区,该存储器区内包含有至少一存储单元,该存储单元包含有晶体管和电容结构;

形成一第一堆叠介电层覆盖该周边电路区和该存储器区使该第一堆叠介电层在该周边电路区和该存储器区之间形成一高低差,其中该第一堆叠介电层包含二第一介电层和一第二介电层,该二个第一介电层和该第二介电层以该第一介电层、该第二介电层和该第一介电层的顺序由下至上依序排列,该第一介电层的材料和该第二介电层的材料不同;

进行一平坦化步骤,移除位于该第一堆叠介电层中最上层的该第一介电层直至曝露出该存储器区内该第一堆叠介电层中的该第二介电层,以形成一平坦化第一堆叠介电层;

在该平坦化步骤之后,形成一接触插塞位于该周边电路区并且贯穿整个该平坦化第一堆叠介电层。

11.如权利要求10所述的具有接触插塞的半导体结构的制作方法,在该平坦化步骤时, 移除位于该第一堆叠介电层中最上层的该第一介电层之后,接续移除该第一堆叠介电层中 的该第二介电层,直至曝露出存储器区内该第一堆叠介电层中最下层的该第一介电层。

- 12.如权利要求10所述的具有接触插塞的半导体结构的制作方法,另包含在该平坦化步骤之前,形成至少一第二堆叠介电层于该周边电路区和该存储器区,并且覆盖该第一堆叠介电层,该第二堆叠介电层包含另一层该第二介电层和另一层该第一介电层由下至上排列。

- 13. 如权利要求12所述的具有接触插塞的半导体结构的制作方法,另包含该平坦化步骤之时,先完全移除位于该存储器区内的该第二堆叠介电层,形成一平坦化第二堆叠介电层,再接续移除位该第一堆叠介电层直至曝露出存储器区内该第一堆叠介电层中的该第二介电层。

- 14. 如权利要求12所述的具有接触插塞的半导体结构的制作方法,另包含该平坦化步骤之时,先完全移除位于该存储器区内的该第二堆叠介电层,形成一平坦化第二堆叠介电层,再接续移除该第一堆叠介电层直至曝露出存储器区内该第一堆叠介电层中最下层的该第一介电层。

- 15.如权利要求13所述的具有接触插塞的半导体结构的制作方法,其中该接触插塞位于该周边电路区并且贯穿该平坦化第一堆叠介电层和该平坦化第二堆叠介电层。

- 16. 如权利要求10所述的具有接触插塞的半导体结构的制作方法,其中该接触插塞的一末端位于该平坦化第一堆叠介电层中最下层的该第一介电层内。

- 17. 如权利要求10所述的具有接触插塞的半导体结构的制作方法,其中该第二介电层包含氮化硅、氮氧化硅、氮碳化硅、或金属氧化物。

# 具有接触插塞的半导体结构及其制作方法

#### 技术领域

[0001] 本发明涉及一种具有接触插塞的半导体结构及其制作方法,特别是涉及一种于介电层中交替设置两种介电材料的制作方法。

## 背景技术

[0002] 动态随机存取存储器 (dynamic random access memory,以下简称为DRAM) 是一种主要的挥发性存储器,且是很多电子产品中不可或缺的关键元件。DRAM由数目庞大的存储单元 (memory cell) 聚集形成一阵列区,用来存储数据,而每一存储胞则由一金属氧化半导体晶体管与一电容串联组成。

[0003] 其中,电容位于存储器区内,而存储器区的旁边存在有周边电路区,周边电路区内包含有其他晶体管元件以及接触结构等。一般而言,位于存储器区内的电容有较大的高度,如此具有较好的存储电荷效能,但如此在形成介电层同时覆盖周边电路区和存储器区后,要在周边电路区内形成一接触插塞时,就需要蚀刻很厚的介电层以形成接触洞,在蚀刻的过程,由于介电层过厚而不好操控蚀刻条件,经常会造成接触洞过蚀刻的问题,使得在周边电路区内的元件受损。

### 发明内容

[0004] 有鉴于此,如何解决上述接触洞过蚀刻的问题,为本发明所欲解决的目标之一。

[0005] 根据本发明的第一优选实施例,一种具有接触插塞的半导体结构,包含一基底,基底上定义有一存储器区以及一周边电路区,存储器区内包含有至少一存储单元,存储单元包含有一晶体管和一电容结构,一平坦化第一堆叠介电层覆盖周边电路区,平坦化第一堆叠介电层包含二第一介电层和一第二介电层,第一介电层和第二介电层以第一介电层、第二介电层和第一介电层的顺序由下至上依序排列,其中在最下方的第一介电层延伸至存储器区并且覆盖电容结构,一接触插塞位于周边电路区并且贯穿平坦化第一堆叠介电层。

[0006] 根据本发明的第二优选实施例,一种具有接触插塞的半导体结构的制作方法,包含首先提供一基底,基底上定义有一存储器区以及一周边电路区,存储器区内包含有至少一存储单元,存储单元包含有一晶体管和一电容结构,然后形成一第一堆叠介电层覆盖周边电路区和存储器区,其中第一堆叠介电层包含二第一介电层和一第二介电层,各个第一介电层和第二介电层以第一介电层、第二介电层和第一介电层的顺序由下至上依序排列,接着进行一平坦化步骤,移除位于第一堆叠介电层中最上层的第一介电层直至曝露出存储器区内第一堆叠介电层中的第二介电层,以形成一平坦化第一堆叠介电层,在平坦化步骤之后,形成一接触插塞位于周边电路区并且贯穿平坦化第一堆叠介电层。

#### 附图说明

[0007] 图1至图5为本发明的第一优选实施例所绘示的具有接触插塞的半导体结构的制作方法的示意图:

[8000] 图6为第一优选实施例的制作方法的变化型的示意图:

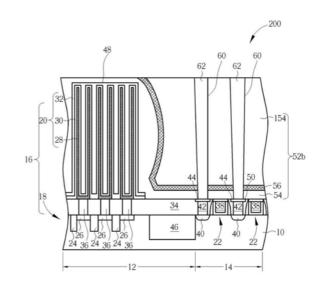

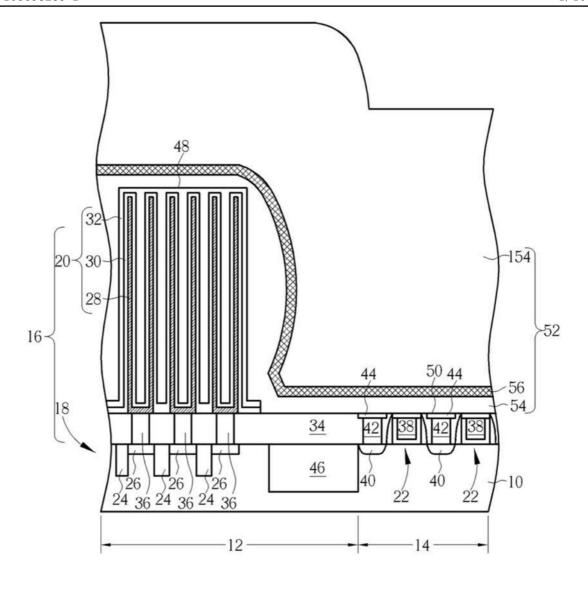

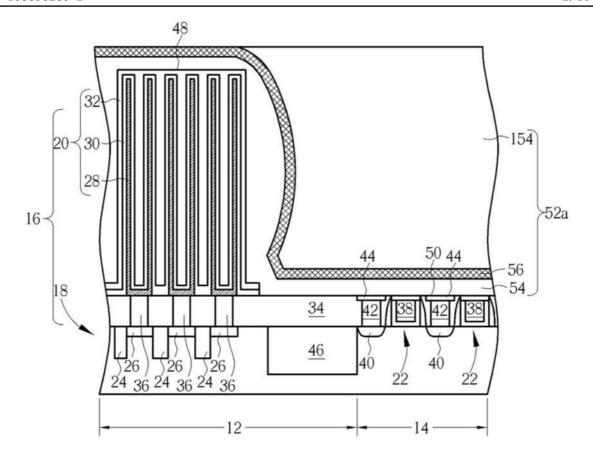

[0009] 图7至图9为本发明的第二优选实施例所绘示的具有接触插塞的半导体结构的制 作方法的示意图;

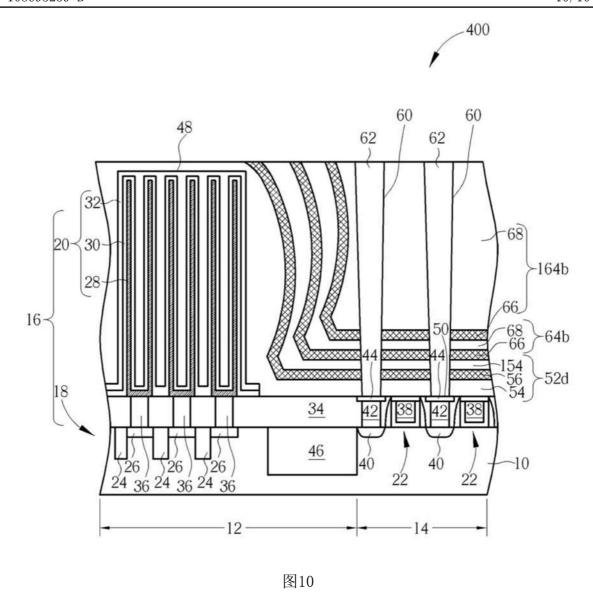

[0010] 图10为第二优选实施例的制作方法的变化型的示意图。

| [0011] | 主要元件符号说明 |    |    |   |      |

|--------|----------|----|----|---|------|

| [0012] | 10       | 基底 | 15 | 2 | 存储器区 |

| [0013] | 14 | 周边电路区 | 16 | 存储单元 |

|--------|----|-------|----|------|

|        |    |       |    |      |

| [0016] | 26 | 源极/漏极掺杂区 | 28 | 下电极 |

|--------|----|----------|----|-----|

|--------|----|----------|----|-----|

| [0019] | 38 | 栅极 | 40 | 源极/漏极掺杂区 |

|--------|----|----|----|----------|

|--------|----|----|----|----------|

[0031] 结构

[0032] 第二堆叠介电层 164a 平坦化第二堆叠介电层 164b 平坦化第二堆叠介电层 [0033] 200 具有接触插塞的半导体

[0034] 结构

[0035] 300 具有接触插塞的半导体 400 具有接触插塞的半导体

[0036] 结构 结构

#### 具体实施方式

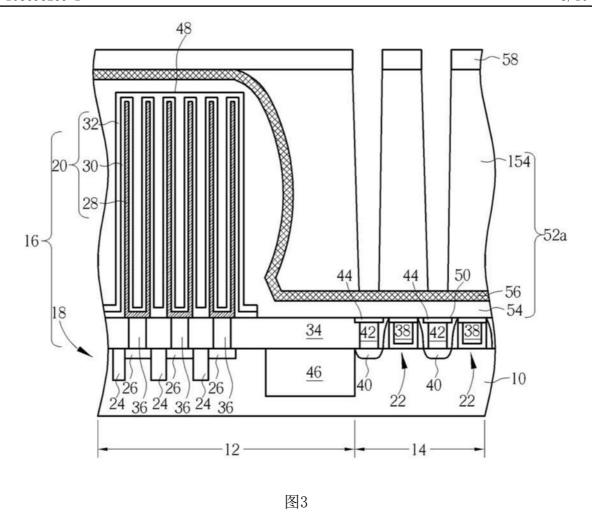

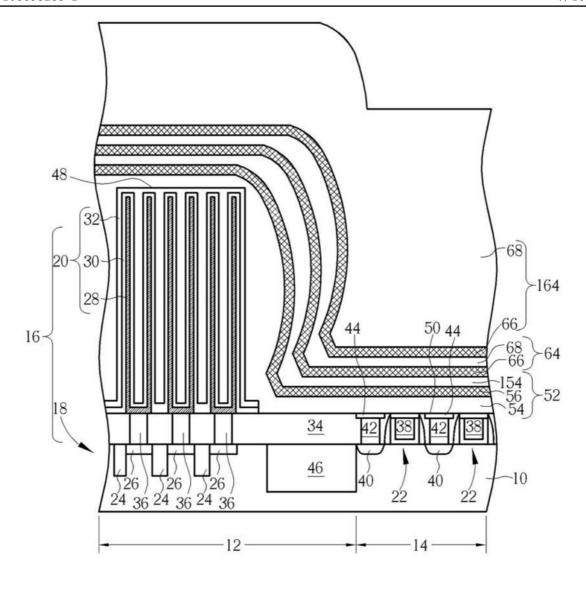

图1至图5为根据本发明的第一优选实施例所绘示的具有接触插塞的半导体结构 的制作方法。如图1所示,提供一基底10,基底10上至少定义有一存储器区12与一周边电路 区14,在存储器区12内包含有至少一存储单元16,例如一动态随机存取存储器的存储单元, 在图1中以多个存储单元为例,各个存储单元16包含有一第一晶体管18和一电容结构20,此 外在周边电路区14内的基底10上设置有至少一第二晶体管22。在本实施例中,存储器区12 内的各第一晶体管18包含埋藏式栅极24以及源极/漏极掺杂区26,埋藏式栅极24设置于基 底10中,而源极/漏极掺杂区26则位于埋藏式栅极24的两侧。电容结构20则包含有下电极 28、绝缘层30以及上电极32,另外,上电极32上方还可以选择性包含有掩模结构(图未示), 不过掩模结构通常仅覆盖于电容结构20的顶部以及侧壁,而不会覆盖至周边电路区14内。 在电容结构20以及第一晶体管18之间,可包含有单层或多层的介电层34以及接触插塞36, 接触插塞36电连接第一晶体管18的源极/漏极掺杂区26以及电容结构20,再者第二晶体管 22位于介电层34中,第二晶体管22包含一栅极38,栅极38两侧设置有源极/漏极掺杂区40, 接触插塞42位于介电层34中并且电连接源极/漏极掺杂区40,另外在接触插塞42上方可设 置有一导电垫44和接触插塞42相连。除此之外,在存储器区12以及周边电路区14的基底10 内,还包含至少一绝缘层46,例如一浅沟槽隔离或是一场氧化层,绝缘层46用来隔离存储器 区12和周边电路区14。此外,电容结构20的上表面48和导电垫44的上表面50构成一高低差。 [0038] 接着全面形成一第一堆叠介电层52顺应地覆盖周边电路区14和存储器区12,其中 第一堆叠介电层52包含二层第一介电层54/154和一第二介电层56,详细来说第一堆叠介电 层52的形成步骤包含先形成最下层的第一介电层54,再形成第二介电层56,最后再形成最 上层的第一介电层154,也就是说,第一堆叠介电层52中的两层第一介电层54/154和一层第 二介电层56系以第一介电层54、第二介电层56和第一介电层154的顺序由下至上依序排列, 第一介电层54和第一介电层154的材料相同,其厚度可以相同或相异。此外两层第一介电层 54/154都和第二介电层56接触。第一介电层54/154的材料和第二介电层56的材料不同,具 有不同的蚀刻速率。在一实施例中第一介电层和第二介电层的蚀刻选择比大于5,较佳大于 7。第一介电层54/154较佳为氧化硅,第二介电层56较佳为氮化硅、氮氧化硅、氮碳化硅或金 属氧化物,第一介电层54/154和第二介电层56可以利用化学气相沉积、物理气相沉积、等离 子体辅助化学气相沉积、旋转涂布、原子层沉积等方式形成。在第一堆叠介电层52中的第二 介电层56,通常较在第一堆叠介电层52中的任一层第一介电层54/154薄,而在一实施例中, 第一堆叠介电层52中最上层的第一介电层154的厚度较在第一堆叠介电层52中最下层的第 一介电层54来得厚。另外,由于电容结构20的上表面48和导电垫44的上表面50构成高低差, 因此第一堆叠介电层54在存储器区12和周边电路区14之间也形成一高低差。

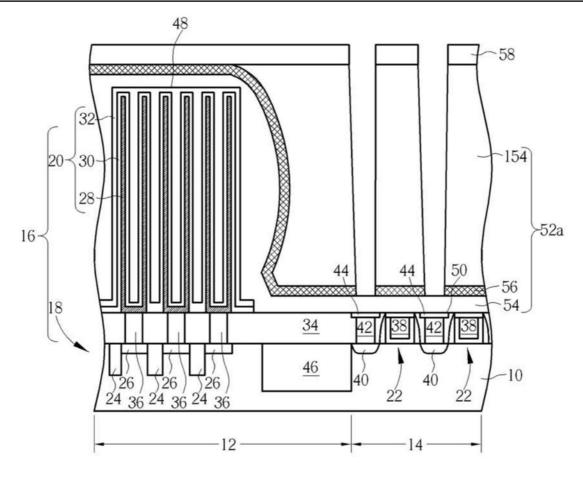

[0039] 如图2所示,以第二介电层56作为停止层,平坦化第一介电层154,详细来说,平坦化第一介电层154直至曝露出存储器区12内的第二介电层56时停止,此时在存储器区12内曝露的第二介电层56的上表面和剩余的第一介电层154的上表面切齐,并且第一堆叠介电层52转变为一平坦化第一堆叠介电层52a。如图3所示,形成一图案化掩模58覆盖第一介电层154、第二介电层56和第一介电层54,图案化掩模58在周边电路区14内定义出至少一接触洞的位置,接着以图案化掩模58为掩模蚀刻第一介电层154直至曝露出第二介电层56,之后如图4所示,继续以图案化掩模58为掩模蚀刻第二介电层56,直至第一介电层54曝露出来,然后如图5所示,蚀刻第一介电层54至曝露出导电垫44时立即停止,至此接触洞60已经完成,之后移除图案化掩模58,再形成接触插塞62于接触洞中,接触插塞62可以为金属材料,例如钛、氮化钛或钨等,接触插塞62位于周边电路区14并且贯穿平坦化第一堆叠介电层52a,至此本发明的具有接触插塞的半导体结构100业已完成,接触插塞62的一末端位于平坦化第一堆叠介电层52a中最下层的第一介电层54内。在本实施例中较佳使用干蚀刻来形成接触洞60,在形成接触洞60的过程,需经过蚀刻第一介电层154、第二介电层56和第一介电层54三个阶段,在蚀刻完第一介电层154接续蚀刻第二介电层56时,需转换蚀刻剂,例如将蚀刻氧化硅的蚀刻剂换成蚀刻氮化硅,同样地在蚀刻完第二介电层56接触蚀刻第一介电

层54时,也需转换蚀刻剂,例如将蚀刻氮化硅的蚀刻剂换成蚀刻氧化硅的蚀刻剂。

[0040] 以传统制作工艺制作接触洞时,本发明第一堆叠介电层52的位置会采用单层的介电层,例如为单层的氧化硅,因此在以传统制作工艺蚀刻接触洞时,需要在一个蚀刻步骤中就曝露出导电垫44,也就是说在一个蚀刻步骤中需要蚀刻很厚的介电层,但如此制作经常会过蚀刻(over etch),造成导电垫44被损坏或甚至蚀刻到导电垫44下方的元件。本发明将形成接触洞60的过程拆解成三个阶段,让最后曝露出导电垫44的蚀刻阶段所需蚀刻的第一介电层54的厚度相较于传统制作工艺的介电层的厚度小,如此就不容易发生过蚀刻的现象。

[0041] 此外,本发明使用第一堆叠介电层52还有另外一些优点,如前文所述在电容结构20的上表面48和导电垫44的上表面50构成高低差,若是以传统制作工艺来说,因为第一堆叠介电层52的位置传统上是采用单层的介电层,其单层的介电层在存储器区12和周边电路区14之间也形成一高底差,在平坦化的过程中,在存储器区12所需移除的介电层较厚,制作工艺控制不易,使得原来欲在电容结构20上保留部分的介电层也被完全移除,甚至损坏到上电极32。但本发明使用第一堆叠介电层52时,就能够利用研磨选择比的不同,将第二介电层56作为平坦化的停止层,保证电容结构20上的介电层能确实被留下,而且最后第一介电层54仍同时覆盖存储器区12和周边电路区14。

[0042] 另外,在电容结构中的绝缘层30和上电极32与周边电路区14中的介电层34之间的交界处容易产生额外应力,以传统制作工艺来说因为使用单层介电层,因此介电层的应力方向相同,所以此介电层的应力和交界处的应力加乘易在介电层中顺着某一方向形成裂缝。然而在本发明中特意使用第一介电层54/154和第二介电层56交替堆叠的方式,由于第一介电层54/154和第二介电层56的应力方向或大小不同,交界处的应力较不容易传递。

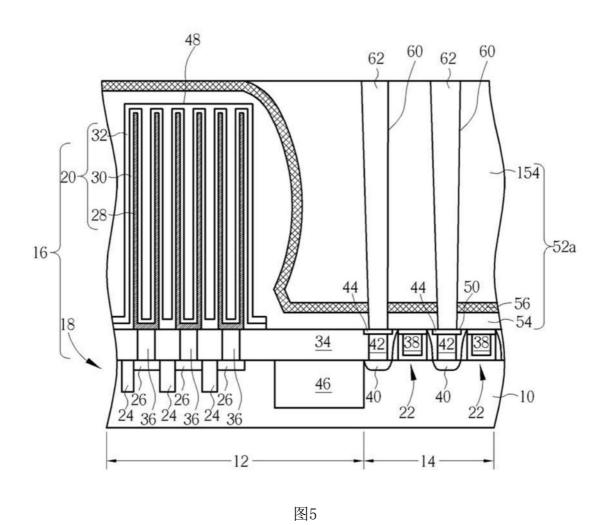

[0043] 根据本发明的另一优选实施例,如图6所示,在图2步骤中平坦化第一介电层154曝露出第二介电层56后,可以接续平坦化曝露出的第二介电层56,直至在电容结构20上表面48的第二介电层56完全被移除为止,此时在电容结构20上表面48只剩下第一介电层54,并且第一堆叠介电层52转变为一平坦化第一堆叠介电层52b,之后再如图2至图5中所述的步骤形成接触洞60和接触插塞62,至此具有接触插塞的半导体结构200业已完成。

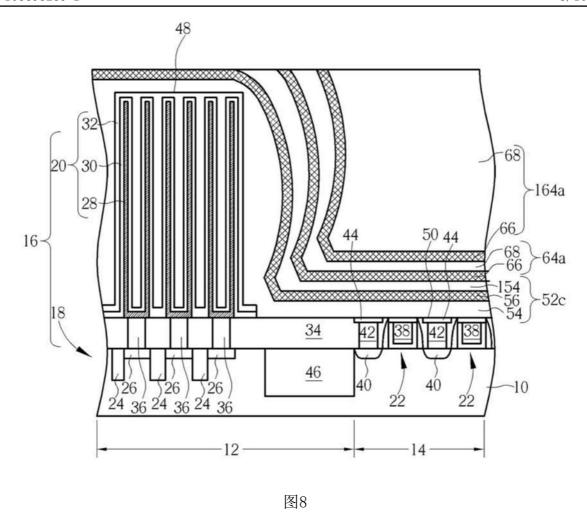

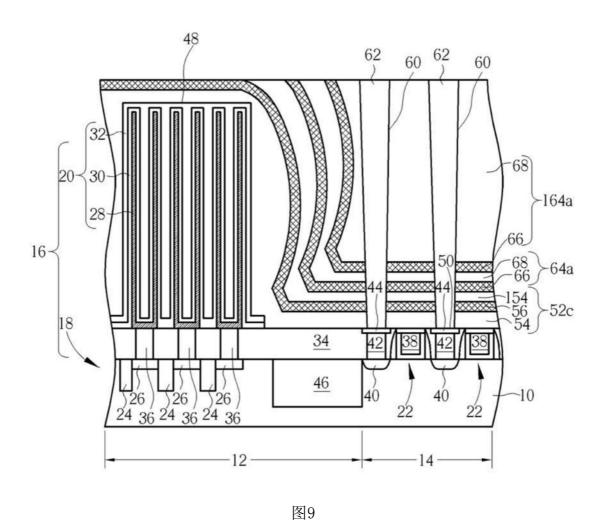

[0044] 图7至图9为根据本发明的第二优选实施例所绘示的具有接触插塞的半导体结构的制作方法,其中具有相同功能和位置的元件将使用和第一优选实施例中相同的标号。第二优选实施例和第一优选实施例的不同之处在于,在第二优选实施例中第一堆叠介电层上另外形成至少一第二堆叠介电层。其它在存储器区和周边电路区中的元件位置和功能,都和第一优选实施例中的相同,在此不再赘述。

[0045] 如图7所示,提供一基底10,基底上定义有一存储器区12与一周边电路区14,存储单元16、电容结构10、第二晶体管22、接触插塞62和导电垫44等元件都和第一优选实施例在相同的位置。然后,形成一第一堆叠介电层52顺应地覆盖周边电路区14和存储器区12,同样地第一堆叠介电层52包含二层第一介电层54/154和一第二介电层56,第一堆叠层52以第一介电层54、第二介电层56和第一介电层154的顺序由下至上依序排列,之后形成至少一第二堆叠介电层64于周边电路区14和存储器区12,并且覆盖第一堆叠介电层52,在本实施例中以形成二层第二堆叠介电层,例如一第二堆叠介电层64和一第二堆叠介电层164为例,第二堆叠介电层64和第二堆叠介电层164的组成相同,都是由一层第二介电层66和一层第一介

电层68由下至上排列,在此给予两种标号只是为了区分其上下位置的不同,视情况需要,可以有多层第二堆叠介电层64/164形成在第一堆叠介电层52上,第一介电层68和第一介电层54/154的材料相同,第二介电层66和第二介电层56的材料相同,也就是说在本发明中的所有的第一介电层其材料都相同,给予不同标号只是为了方便区分其设置的位置,而本发明中的所有的第二介电层56/66其材料都相同,给予不同标号只是为了方便区分其设置的位置。此时第一堆叠介电层52和第二堆叠介电层64/164中的第一介电层54/68/154、第二介电层56/66交替排列,在每层第二介电层56/66的上面和下面各有一层第一介电层54/68/154与其接触。第二堆叠介电层64的数量可视情况调整。另外,在所有的第一介电层54/68/154和第二介电层54/68/154中,通常是在最上层的第二堆叠介电层164中的第一介电层68的厚度最大。另外,第二介电层的材料可为氮化硅、氮氧化硅、氮碳化硅或金属氧化物,视情况需要,第二介电层66和第二介电层56也可选择不同材料,例如第二介电层66可为金属氧化物,第二介电层56可为氮化硅,只要第二介电层相对于第一介电层具有蚀刻选择比,可以作为蚀刻停止层即可。

[0046] 如图8所示,以第一堆叠介电层52中的第二介电层56作为停止层,平坦化第二堆叠介电层64、第二堆叠介电层164和第一堆叠介电层52,详细来说,平坦化制作工艺持续到曝露出第二介电层56时停止,此时第二堆叠介电层164转变为一平坦化第二堆叠介电层52转变为一平坦化第二堆叠介电层52转变为一平坦化第一堆叠介电层52c。此时在存储器区12中的第二介电层56的上表面和在周边电路区14中平坦化第二堆叠介电层52c。此时在存储器区12中的第二介电层56的上表面和在周边电路区14中平坦化第二堆叠介电层164a中的第一介电层68的上表面切齐,如图9所示,形成一接触洞60于平坦化第一堆叠介电层52c、平坦化第二堆叠介电层64a和平坦化第二堆叠介电层164a中,接触洞60的形成方式可以如第一优选实施例中的分成多个阶段蚀刻平坦化第二堆叠介电层164a、平坦化第二堆叠介电层52c,最后形成接触插塞62于接触洞60中,至此本发明的具有接触插塞的半导体结构300业已完成,接触插塞62位于周边电路区14并且贯穿平坦化第二堆叠介电层164a、平坦化第二堆叠介电层64a和平坦化第一堆叠介电层52c。

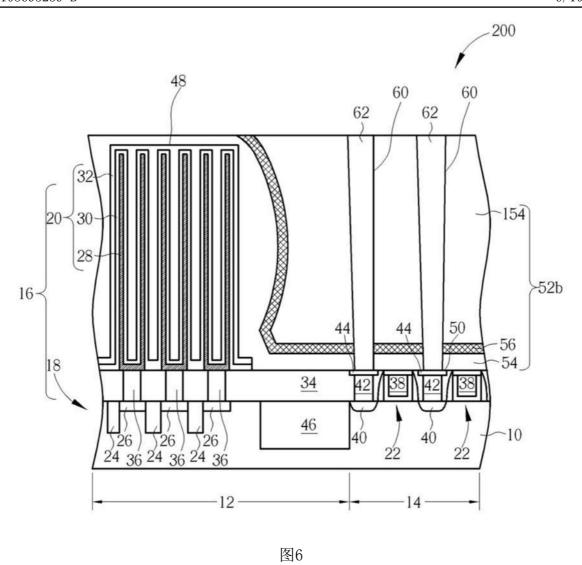

[0047] 根据本发明的另一优选实施例,如图10所示,在形成平坦化第一堆叠介电层52c之后,继续平坦化制作工艺接续移除位于平坦化第一堆叠介电层52c中的第二介电层56,直至曝露出存储器区12内的第一介电层54。此时在周边电路区14的平坦化第二堆叠介电层64a/164a各自转变为一平坦化第二堆叠介电层64b和一平坦化第二堆叠介电层164b,而平坦化第一堆叠介电层52c则转变为一平坦化第一堆叠介电层52d。之后如前文所述的方式形成接触洞60和接触插塞62,接触插塞60贯穿平坦化第二堆叠介电层164b、平坦化第二堆叠介电层64b和平坦化第一堆叠介电层52d,至此具有接触插塞的半导体结构400业已完成。

[0048] 如图5所示,本发明的一种具有接触插塞的半导体结构100,包含一基底10,基底10上定义有一存储器区12以及一周边电路区14,存储器区10内包含有至少一存储单元16,例如一动态随机存取存储器存储单元,包含有一第一晶体管18和一电容结构20,此外在周边电路区14内的基底10上设置有至少一第二晶体管22。一平坦化第一堆叠介电层52a覆盖周边电路区14,平坦化第一堆叠介电层52a包含二层第一介电层54/154和一层第二介电层56,第一介电层54/154和第二介电层56以第一介电层54、第二介电层56和第一介电层154的顺序由下至上依序排列,其中在最下方的第一介电层54和第二介电层56延伸至存储器区12并

且覆盖电容结构20,一接触插塞62位于周边电路区14并且贯穿平坦化第一堆叠介电层52a,此外接触插塞52的一末端位于平坦化第一堆叠介电层52a中最下层的第一介电层54内,第一介电层54/154的材料和第二介电层56的材料不同,第一介电层54和第一介电层154的材料相同,第一介电层54/154较佳为氧化硅,第二介电层56较佳为氮化硅或金属氧化物。此外,第二介电层56的厚度是平坦化第一堆叠介电层52a的厚度的十分之一至八分之一。

[0049] 根据本发明的另一优选实施例,如图6所示,具有接触插塞的半导体结构200其和图5中的具有接触插塞的半导体结构100的不同在于,图6中的第二介电层56未延伸至电容结构20上,其余部分都和图5中的具有接触插塞的半导体结构100相同,请参阅有关图5中的叙述。

[0050] 本发明的具有接触插塞的半导体结构还可以在周边电路区的平坦化第一堆叠介电层上另外设置至少一平坦化第二堆叠介电层,如图9中所示的具有接触插塞的半导体结构300,在一平坦化第一堆叠介电层52c上就另外设置了二层平坦化第二堆叠介电层64a/164a,当然平坦化第二堆叠介电层64a/164a的数量可视产品需求而改变,不限于图9中的二层,平坦化第二堆叠介电层64a/164a各自包含一层第二介电层66和一层第一介电层68由下至上排列,平坦化第一堆叠介电层52c包含了第一介电层54/154和第二介电层56以第一介电层54、第二介电层56和第一介电层154的顺序由下至上依序排列,其中在最下方的第一介电层54和第二介电层56延伸至存储器区12并且覆盖电容结构20,第一介电层54、第一介电层68、第一介电层56延伸至存储器区12并且覆盖电容结构20,第一介电层56和第二介电层68为相同材料,给予不同标号只是为了区别其位置不同,第二介电层56和第二介电层68为相同材料,给予不同标号只是为了区别其位置不同,接触插塞62位于周边电路区14并且贯穿平坦化第二堆叠介电层164a、平坦化第二堆叠介电层64a和平坦化第一堆叠介电层52c、平坦化第二堆叠介电层664a和平坦化第二堆叠介电层664a和平坦化第二堆叠介电层664a和平坦化第二堆叠介电层664。

[0051] 根据本发明的另一优选实施例,如图10所示,具有接触插塞的半导体结构400其和图9中的具有接触插塞的半导体结构300的不同在于,图10中存储器区12内只留有平坦化第一堆叠介电层52d中最下层的第一介电层54,第二介电层56未覆盖电容结构20,也就是说,平坦化第一堆叠介电层52c和平坦化第一堆叠介电层52d的不同之处在于平坦化第一堆叠介电层52d在电容结构20上没有第二介电层56。其余部分都和图9中的具有接触插塞的半导体结构相同,请参阅有关图9中的叙述。

[0052] 以上所述仅为本发明的优选实施例,凡依本发明权利要求所做的均等变化与修饰,都应属本发明的涵盖范围。

图1

图2

12

图4

14

15

图7

18