## (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(43) 공개일자

(51)Int. Cl.

> **G09G 3/36** (2006.01) **H03M 1/66** (2006.01) **G09G 3/20** (2006.01) **G02F 1/133** (2006.01)

(21) 출원번호

10-2008-0129115

(22) 출원일자

2008년12월18일

심사청구일자

없음

(71) 출원인

(11) 공개번호

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

조규형

충청남도 공주시 반포면 상신리 585-1 도예촌 밤

10-2010-0070535

2010년06월28일

전용준

대전광역시 유성구 전민동 청구나래아파트 108동 605호

(뒷면에 계속)

(74) 대리인

박영우

전체 청구항 수 : 총 10 항

#### (54) 디지털-아날로그 변환기, 이를 포함하는 소스 구동회로, 및소스 구동회로를 포함하는 표시 장치

#### (57) 요 약

드레인 전류 변조 방식을 사용한 디지털-아날로그 변환기 및 이를 포함하는 소스 구동회로가 개시된다. 디지털-아날로그 변환기는 전압-전류 변환기, 전류 모드 디지털-아날로그 변환기 및 연산증폭기를 포함한다. 전압-전류 변환기는 제 1 전압 레벨을 갖는 제 1 전압신호와 제 2 전압 레벨을 갖는 제 2 전압신호의 차이에 비례하는 제 1 전류신호를 발생시킨다. 전류 모드 디지털-아날로그 변환기는 디지털 입력신호 및 제 1 전류신호에 응답하여 디 지털 입력신호에 대응하는 제 2 전류신호를 발생시킨다. 연산증폭기는 제 2 전류신호 및 제 2 전압신호에 응답하 여 드레인 전류를 변조하고 옵셋을 갖는 출력전압을 발생시킨다. 따라서, 디지털-아날로그 변환기는 반도체 집적 회로에서 차지하는 면적이 적고, 디지털-아날로그 변환기를 포함하는 소스 구동회로는 제조비용이 적다.

#### 대 표 도 - 도1

## (72) 발명자

## 이형민

대구광역시 달서구 상인동 1516 우방아파트 203동 901호

### 이성우

경상남도 마산시 내서읍 중리 동신아파트 103동 103호

### 김형래

경기도 화성시 병점동 늘벗마을신창1차아파트 105 동 705호

#### 최윤경

경기도 용인시 기흥구 보정동 현대아이파크1차아파 트 210동 805호

#### 특허청구의 범위

#### 청구항 1

제 1 전압 레벨을 갖는 제 1 전압신호와 제 2 전압 레벨을 갖는 제 2 전압신호의 차이에 비례하는 제 1 전류신호를 발생시키는 전압-전류 변환기;

디지털 입력신호 및 상기 제 1 전류신호에 응답하여 상기 디지털 입력신호에 대응하는 제 2 전류신호를 발생시키는 전류 모드 디지털-아날로그 변환기; 및

상기 제 2 전류신호 및 상기 제 2 전압신호에 응답하여 드레인 전류를 변조하고 옵셋을 갖는 출력전압을 발생시키는 연산증폭기를 포함하는 디지털-아날로그 변환기.

#### 청구항 2

제 1 항에 있어서,

상기 디지털 입력신호가 M 비트의 데이터일 때, 상기 디지털-아날로그 변환기는 2<sup>™</sup> 개의 아날로그 전압신호를 발생시키는 것을 특징으로 하는 디지털-아날로그 변환기.

#### 청구항 3

제 2 항에 있어서, 상기 전류 모드 디지털-아날로그 변환기는

2<sup>N</sup> 개의 전류신호를 발생시키고, 상기 디지털 입력신호에 대응하는 전류신호를 출력하는 것을 특징으로 하는 디지털-아날로그 변환기.

#### 청구항 4

제 1 항에 있어서, 상기 전압-전류 변환기는

상기 연산증폭기의 차동입력부와 동일한 회로 구성을 갖는 증폭기인 것을 특징으로 하는 디지털-아날로그 변환기.

#### 청구항 5

제 1 항에 있어서, 상기 연산증폭기는

상기 제 2 전류신호를 사용하여 드레인 전류를 변조하고, 상기 제 2 전압신호와 상기 출력전압의 차이를 증폭하는 차동 입력부; 및

상기 차동 입력부의 출력신호를 증폭하여 상기 출력전압을 발생시키는 이득부를 포함하는 것을 특징으로 하는 디지털-아날로그 변환기.

#### 청구항 6

디지털 입력신호의 상위 비트들에 대해 디지털-아날로그 변환을 수행하여, 제 1 전압 레벨을 갖는 제 1 전압신호와 제 2 전압 레벨을 갖는 제 2 전압신호를 발생시키는 제 1 디지털-아날로그 변환기; 및

상기 제 1 전압신호와 상기 제 2 전압신호의 크기 차이에 비례하는 제 1 전류신호를 발생시키고, 상기 디지털 입력신호의 하위 비트들 및 상기 제 1 전류신호에 응답하여 상기 디지털 입력신호에 대응하는 제 2 전류신호를 발생시키고, 상기 제 2 전류신호 및 상기 제 2 전압신호에 응답하여 드레인 전류를 변조하고 옵셋을 갖는 출력 전압을 발생시키는 제 2 디지털-아날로그 변환기를 포함하는 디지털-아날로그 변환기.

#### 청구항 7

제 6 항에 있어서, 상기 제 1 디지털-아날로그 변환기는

상기 디지털 입력신호의 상위 비트들이 디코딩된 값들에 대응하는 전압신호들을 발생시키기 위한 저항 스트링을 포함하는 것을 특징으로 하는 디지털-아날로그 변환기.

#### 청구항 8

제 6 항에 있어서, 상기 제 2 디지털-아날로그 변환기는

상기 제 1 전류신호를 발생시키는 전압-전류 변환기;

상기 제 2 전류신호를 발생시키는 전류 모드 디지털-아날로그 변환기; 및

상기 제 2 전류신호 및 상기 제 2 전압신호에 응답하여 드레인 전류를 변조하고 옵셋을 갖는 출력전압을 발생시키는 연산 증폭기를 포함하는 것을 특징으로 하는 디지털-아날로그 변환기.

#### 청구항 9

클럭신호와 입출력 제어신호에 기초하여 펄스신호를 발생시키는 쉬프트 레지스터;

상기 쉬프트 레지스터의 쉬프트 순서에 따라 데이터를 래치하고, 로드신호에 응답하여 상기 데이터를 디지털 입력신호들로서 출력하는 데이터 래치 회로; 및

계조전압을 사용하여, 상기 디지털 입력신호들에 대응하는 소스 신호들을 발생시키는 디지털-아날로그 변환기를 포함하고,

상기 디지털-아날로그 변환기는

상기 디지털 입력신호의 상위 비트들에 대해 디지털-아날로그 변환을 수행하여, 제 1 전압 레벨을 갖는 제 1 전 압신호와 제 2 전압 레벨을 갖는 제 2 전압신호를 발생시키는 제 1 디지털-아날로그 변환기; 및

상기 제 1 전압신호와 상기 제 2 전압신호의 크기 차이에 비례하는 제 1 전류신호를 발생시키고, 상기 디지털 입력신호의 하위 비트들 및 상기 제 1 전류신호에 응답하여 상기 디지털 입력신호에 대응하는 제 2 전류신호를 발생시키고, 상기 제 2 전류신호 및 상기 제 2 전압신호에 응답하여 드레인 전류를 변조하고 옵셋을 갖는 상기 소스 신호들을 발생시키는 제 2 디지털-아날로그 변환기를 포함하는 것을 특징으로 하는 소스 구동 회로.

#### 청구항 10

클럭신호와 입출력 제어신호에 기초하여 펄스신호를 발생시키는 쉬프트 레지스터;

상기 쉬프트 레지스터의 쉬프트 순서에 따라 데이터를 래치하고, 로드신호에 응답하여 상기 데이터를 디지털 입력신호들로서 출력하는 데이터 래치 회로;

계조전압을 사용하여, 상기 디지털 입력신호들에 대응하는 소스 신호들을 발생시키는 디지털-아날로그 변환기; 및

상기 소스 신호들에 응답하여 구동되는 패널을 포함하고,

상기 디지털-아날로그 변환기는

상기 디지털 입력신호의 상위 비트들에 대해 디지털-아날로그 변환을 수행하여, 제 1 전압 레벨을 갖는 제 1 전 압신호와 제 2 전압 레벨을 갖는 제 2 전압신호를 발생시키는 제 1 디지털-아날로그 변환기; 및

상기 제 1 전압신호와 상기 제 2 전압신호의 크기 차이에 비례하는 제 1 전류신호를 발생시키고, 상기 디지털 입력신호의 하위 비트들 및 상기 제 1 전류신호에 응답하여 상기 디지털 입력신호에 대응하는 제 2 전류신호를 발생시키고, 상기 제 2 전류신호 및 상기 제 2 전압신호에 응답하여 드레인 전류를 변조하고 옵셋을 갖는 상기 소스 신호들을 발생시키는 제 2 디지털-아날로그 변환기를 포함하는 것을 특징으로 하는 표시 장치.

#### 명 세 서

[0001]

#### 발명의 상세한 설명

#### 기 술 분 야

본 발명은 디지털-아날로그 변환기에 관한 것으로, 특히 표시 장치의 소스 구동회로에 사용되는 디지털-아날로 그 변환기에 관한 것이다.

#### 배경기술

- [0002] LCD 장치는 음극선관(Cathode Ray Tube)에 비해 두께가 얇고 가벼우며 그 품질도 점차 개선되고 있기 때문에, 정보처리 기기로서 널리 사용되고 있다.

- [0003] 액티브 매트릭스형 LCD 장치는 매트릭스 내에 배열된 복수의 픽셀 전국 각각에 연결된 복수의 능동 소자를 가진다. 액티브 매트릭스형 LCD 장치는 단순 매트릭스형 LCD 장치에 비해 높은 콘트라스트 비(contrast ratio)를 가진다. 따라서, 액티브 매트릭스형 구동은 칼라 LCD 장치에 필수적으로 되고 있다. 액티브 매트릭스형 LCD 장치의 각 픽셀 전국에 연결되는 능동소자로는 박막 필름 트랜지스터(Thin Film Transistor; 이하 TFT라 함)가 널리사용되고 있다.

- [0004] 종래에는 64 계조 이상의 고 해상도의 LCD 장치에서는 집적회로 상에서 소스 구동 회로 전체의 면적에서 디지털 -아날로그 변환기가 차지하는 면적이 상당 부분을 차지한다. 종래의 디지털-아날로그 변환기는 직렬 연결된 저항들로 구성된 저항 스트링으로 구성되었으므로, 디지털 데이터의 비트 수가 증가하면 저항 스트링이 차지하는 면적이 크게 증가하였다. 따라서, 소스 구동 회로의 칩 사이즈가 증가하였다.

#### 발명의 내용

#### 해결 하고자하는 과제

- [0005] 본 발명의 목적은 반도체 집적회로 상에서 차지하는 면적이 적은 디지털-아날로그 변환기를 제공하는 것이다.

- [0006] 본 발명의 다른 목적은 상기 디지털-아날로그 변환기를 포함하는 소스 구동회로를 제공하는 것이다.

- [0007] 본 발명의 또 다른 목적은 상기 소스 구동회로를 포함하는 표시 장치를 제공하는 것이다.

### 과제 해결수단

- [0008] 상기 목적을 달성하기 위하여 본 발명의 하나의 실시형태에 따른 디지털-아날로그 변환기는 전압-전류 변환기, 전류 모드 디지털-아날로그 변환기 및 연산증폭기를 포함한다.

- [0009] 전압-전류 변환기는 제 1 전압 레벨을 갖는 제 1 전압신호와 제 2 전압 레벨을 갖는 제 2 전압신호의 차이에 비례하는 제 1 전류신호를 발생시킨다. 전류 모드 디지털-아날로그 변환기는 디지털 입력신호 및 상기 제 1 전류신호에 응답하여 상기 디지털 입력신호에 대응하는 제 2 전류신호를 발생시킨다. 연산증폭기는 상기 제 2 전류신호 및 상기 제 2 전압신호에 응답하여 드레인 전류를 변조하고 옵셋을 갖는 출력전압을 발생시킨다.

- [0010] 본 발명의 하나의 실시예에 의하면, 상기 디지털 입력신호가 M 비트의 데이터일 때, 상기 디지털-아날로그 변환 기는  $2^{^{\mathrm{M}}}$  개의 아날로그 전압신호를 발생시킬 수 있다.

- [0011] 본 발명의 하나의 실시예에 의하면, 상기 전류 모드 디지털-아날로그 변환기는 2<sup>™</sup> 개의 전류신호를 발생시키고, 상기 디지털 입력신호에 대응하는 전류신호를 출력할 수 있다.

- [0012] 본 발명의 하나의 실시예에 의하면, 상기 전압-전류 변환기는 상기 연산증폭기의 차동입력부와 동일한 회로 구성을 가질 수 있다.

- [0013] 본 발명의 하나의 실시예에 의하면, 상기 연산증폭기는 차동 입력부 및 이득부를 포함할 수 있다.

- [0014] 차동 입력부는 상기 제 2 전류신호를 사용하여 드레인 전류를 변조하고, 상기 제 2 전압신호와 상기 출력전압의 차이를 증폭한다. 이득부는 상기 차동 입력부의 출력신호를 증폭하여 상기 출력전압을 발생시킬 수 있다.

- [0015] 본 발명의 하나의 실시형태에 따른 디지털-아날로그 변환기는 제 1 디지털-아날로그 변환기 및 제 2 디지털-아날로그 변환기를 포함한다.

- [0016] 제 1 디지털-아날로그 변환기는 디지털 입력신호의 상위 비트들에 대해 디지털-아날로그 변환을 수행하여, 제 1 전압 레벨을 갖는 제 1 전압신호와 제 2 전압 레벨을 갖는 제 2 전압신호를 발생시킨다. 제 2 디지털-아날로그 변환기는 상기 제 1 전압신호와 상기 제 2 전압신호의 크기 차이에 비례하는 제 1 전류신호를 발생시키고, 상기 디지털 입력신호의 하위 비트들 및 상기 제 1 전류신호에 응답하여 상기 디지털 입력신호에 대응하는 제 2 전류신호를 발생시키고, 상기 제 2 전류신호 및 상기 제 2 전압신호에 응답하여 드레인 전류를 변조하고 옵셋을 갖는 출력전압을 발생시킨다.

- [0017] 본 발명의 하나의 실시예에 의하면, 상기 제 1 디지털-아날로그 변환기는 상기 디지털 입력신호의 상위 비트들이 디코딩된 값들에 대응하는 전압신호들을 발생시키기 위한 저항 스트링을 포함할 수 있다.

- [0018] 본 발명의 하나의 실시예에 의하면, 상기 제 2 디지털-아날로그 변환기는 전압-전류 변환기, 전류 모드 디지털-아날로그 변환기 및 연산 증폭기를 포함할 수 있다.

- [0019] 전압-전류 변환기는 상기 제 1 전류신호를 발생시키고, 전류 모드 디지털-아날로그 변환기는 상기 제 2 전류신호를 발생시킨다. 연산 증폭기는 상기 제 2 전류신호 및 상기 제 2 전압신호에 응답하여 드레인 전류를 변조하고 옵셋을 갖는 출력전압을 발생시킨다.

- [0020] 본 발명의 하나의 실시형태에 따른 소스 구동회로는 쉬프트 레지스터, 데이터 래치 회로 및 디지털-아날로그 변환기를 포함한다.

- [0021] 쉬프트 레지스터는 클럭신호와 입출력 제어신호에 기초하여 펄스신호를 발생시킨다. 데이터 래치 회로는 상기 쉬프트 레지스터의 쉬프트 순서에 따라 데이터를 래치하고, 로드신호에 응답하여 상기 데이터를 디지털 입력신 호들로서 출력한다. 디지털-아날로그 변환기는 계조전압을 사용하여, 상기 디지털 입력신호들에 대응하는 소스 신호들을 발생시킨다.

- [0022] 상기 디지털-아날로그 변환기는 제 1 디지털-아날로그 변환기 및 제 2 디지털-아날로그 변환기를 포함한다. 제 1 디지털-아날로그 변환기는 상기 디지털 입력신호의 상위 비트들에 대해 디지털-아날로그 변환을 수행하여, 제 1 전압 레벨을 갖는 제 1 전압신호와 제 2 전압 레벨을 갖는 제 2 전압신호를 발생시킨다. 제 2 디지털-아날로 그 변환기는 상기 제 1 전압신호와 상기 제 2 전압신호의 크기 차이에 비례하는 제 1 전류신호를 발생시키고, 상기 디지털 입력신호의 하위 비트들 및 상기 제 1 전류신호에 응답하여 상기 디지털 입력신호에 대응하는 제 2 전류신호를 발생시키고, 상기 제 2 전류신호 및 상기 제 2 전압신호에 응답하여 드레인 전류를 변조하고 옵셋을 갖는 상기 소스 신호들을 발생시킨다.

- [0023] 본 발명의 하나의 실시형태에 따른 표시 장치는 쉬프트 레지스터, 데이터 래치 회로, 디지털-아날로그 변환기 및 패널을 포함한다.

- [0024] 쉬프트 레지스터는 클럭신호와 입출력 제어신호에 기초하여 펄스신호를 발생시킨다. 데이터 래치 회로는 상기 쉬프트 레지스터의 쉬프트 순서에 따라 데이터를 래치하고, 로드신호에 응답하여 상기 데이터를 디지털 입력신 호들로서 출력한다. 디지털-아날로그 변환기는 계조전압을 사용하여, 상기 디지털 입력신호들에 대응하는 소스 신호들을 발생시킨다. 패널은 상기 소스 신호들에 응답하여 구동된다.

- [0025] 상기 디지털-아날로그 변환기는 상기의 디지털-아날로그 변환기의 구성을 갖는다.

#### 直 과

[0026] 본 발명에 따른 디지털-아날로그 변환기는 전류 모드 디지털-아날로그 변환기 및 연산증폭기를 사용하여 드레인 전류 변조를 수행함으로써 두 전압 값 사이의 전압들을 보간(interpolation)하였다. 드레인 전류의 변조는 종래의 소스 구동회로의 출력 버퍼 증폭기를 사용하기 때문에 디지털-아날로그 변환기가 칩 내에서 차지하는 면적이적다. 본 발명의 디지털-아날로그 변환기를 포함하는 소스 구동회로는 칩 면적을 적게 차지하므로 특히 8비트이상의 고 정밀도 고 계조 LCD 장치의 구동회로에 사용 가능하다. 따라서, 본 발명에 따른 디지털-아날로그 변환기를 포함하는 소스 구동회로 및 표시 장치는 제조단가를 낮출 수 있다.

#### 발명의 실시를 위한 구체적인 내용

- [0027] 본문에 개시되어 있는 본 발명의 실시예들에 대해서, 특정한 구조적 내지 기능적 설명들은 단지 본 발명의 실시예를 설명하기 위한 목적으로 예시된 것으로, 본 발명의 실시예들은 다양한 형태로 실시될 수 있으며 본문에 설명된 실시예들에 한정되는 것으로 해석되어서는 안 된다.

- [0028] 본 발명은 다양한 변경을 가할 수 있고 여러 가지 형태를 가질 수 있는 바, 특정 실시예들을 도면에 예시하고 본문에 상세하게 설명하고자 한다. 그러나, 이는 본 발명을 특정한 개시 형태에 대해 한정하려는 것이 아니며, 본 발명의 사상 및 기술 범위에 포함되는 모든 변경, 균등물 내지 대체물을 포함하는 것으로 이해되어야 한다.

- [0029] 제1, 제2 등의 용어는 다양한 구성요소들을 설명하는데 사용될 수 있지만, 상기 구성요소들은 상기 용어들에 의해 한정되어서는 안된다. 상기 용어들은 하나의 구성요소를 다른 구성요소로부터 구별하는 목적으로만 사용된다. 예를 들어, 본 발명의 권리 범위로부터 이탈되지 않은 채 제1 구성요소는 제2 구성요소로 명명될 수

있고, 유사하게 제2 구성요소도 제1 구성요소로 명명될 수 있다.

- [0030] 어떤 구성요소가 다른 구성요소에 "연결되어" 있다거나 "접속되어" 있다고 언급된 때에는, 그 다른 구성요소에 직접적으로 연결되어 있거나 또는 접속되어 있을 수도 있지만, 중간에 다른 구성요소가 존재할 수도 있다고 이해되어야 할 것이다. 반면에, 어떤 구성요소가 다른 구성요소에 "직접 연결되어" 있다거나 "직접 접속되어" 있다고 언급된 때에는, 중간에 다른 구성요소가 존재하지 않는 것으로 이해되어야 할 것이다. 구성요소들 간의 관계를 설명하는 다른 표현들, 즉 "~사이에"와 "바로 ~사이에" 또는 "~에 이웃하는"과 "~에 직접 이웃하는" 등도 마찬가지로 해석되어야 한다.

- [0031] 본 출원에서 사용한 용어는 단지 특정한 실시예를 설명하기 위해 사용된 것으로, 본 발명을 한정하려는 의도가 아니다. 단수의 표현은 문맥상 명백하게 다르게 뜻하지 않는 한, 복수의 표현을 포함한다. 본 출원에서, "포함하다" 또는 "가지다" 등의 용어는 설시된 특징, 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것이 존재함을 지정하려는 것이지, 하나 또는 그 이상의 다른 특징들이나 숫자, 단계, 동작, 구성요소, 부분품 또는 이들을 조합한 것들의 존재 또는 부가 가능성을 미리 배제하지 않는 것으로 이해되어야 한다.

- [0032] 다르게 정의되지 않는 한, 기술적이거나 과학적인 용어를 포함해서 여기서 사용되는 모든 용어들은 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에 의해 일반적으로 이해되는 것과 동일한 의미를 가지고 있다. 일 반적으로 사용되는 사전에 정의되어 있는 것과 같은 용어들은 관련 기술의 문맥 상 가지는 의미와 일치하는 의미를 가지는 것으로 해석되어야 하며, 본 출원에서 명백하게 정의하지 않는 한, 이상적이거나 과도하게 형식적인 의미로 해석되지 않는다.

- [0033] 한편, 어떤 실시예가 달리 구현 가능한 경우에 특정 블록 내에 명기된 기능 또는 동작이 순서도에 명기된 순서 와 다르게 일어날 수도 있다. 예를 들어, 연속하는 두 블록이 실제로는 실질적으로 동시에 수행될 수도 있고, 관련된 기능 또는 동작에 따라서는 상기 블록들이 거꾸로 수행될 수도 있다.

- [0034] 이하, 첨부된 도면을 참조하여 본 발명의 바람직한 실시예들을 설명한다.

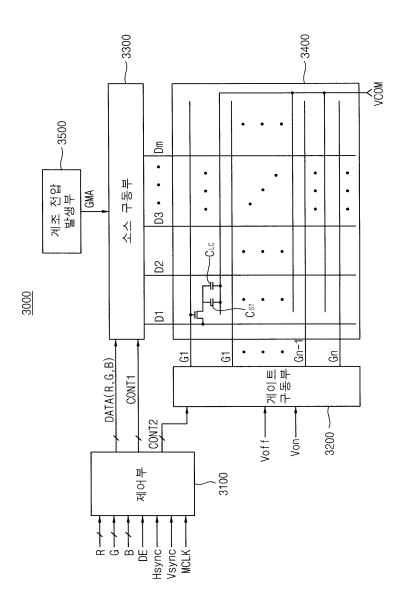

- [0035] 도 1은 본 발명의 제 1 실시예에 따른 디지털-아날로그 변환기(100)를 나타내는 블록도이다.

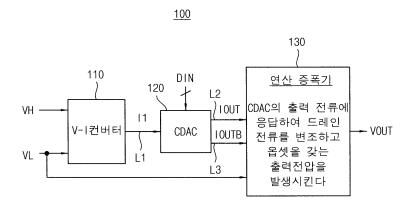

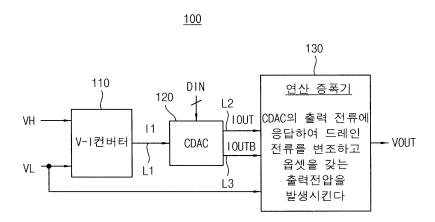

- [0036] 도 1을 참조하면, 디지털-아날로그 변환기(100)는 전압-전류 변환기(110), 전류 모드 디지털-아날로그 변환기 (current-mode digital-to-analog converter; CDAC)(120) 및 연산증폭기(130)를 포함한다.

- [0037] 전압-전류 변환기(110)는 제 1 전압 레벨을 갖는 제 1 전압신호(VH)와 제 2 전압 레벨을 갖는 제 2 전압신호 (VL)의 차이에 비례하는 제 1 전류신호(I1)를 발생시킨다. 전류 모드 디지털-아날로그 변환기(120)는 제 1 라인 (L1)으로부터 제 1 전류신호(I1)를 수신하고, 디지털 입력신호(DIN) 및 제 1 전류신호(I1)에 응답하여 디지털 입력신호(DIN)에 대응하는 제 2 전류신호(IOUT) 및 제 3 전류신호(IOUTB)를 발생시킨다. 제 3 전류신호(IOUTB)는 제 2 전류신호(IOUT)와 상보(complementary) 관계를 갖는 전류신호이다. 연산증폭기(130)는 제 2 라인(L2)및 제 3 라인(L3)으로부터 각각 제 2 전류신호(IOUT) 및 제 3 전류신호(IOUTB)를 수신하고, 제 2 전류신호(IOUT), 제 3 전류신호(IOUTB) 및 제 2 전압신호(VL)에 응답하여 드레인 전류를 변조하고 옵셋을 갖는 출력전압 (VOUT)을 발생시킨다.

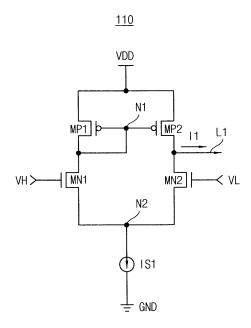

- [0038] 도 2는 도 1의 디지털-아날로그 변환기(100)에 포함된 전압-전류 변환기(110)의 하나의 예를 나타내는 회로도이다.

- [0039] 도 2를 참조하면, 전압-전류 변환기(110)는 제 1 PMOS 트랜지스터(MP1), 제 2 PMOS 트랜지스터(MP2), 제 1 NMOS 트랜지스터(MN1), 제 2 NMOS 트랜지스터(MN2) 및 제 1 전류원(IS1)을 포함한다.

- [0040] 제 1 PMOS 트랜지스터(MP1)는 전원전압(VDD)에 연결된 소스, 제 1 노드(N1)에 공통 연결된 게이트 및 드레인을 갖는다. 제 2 PMOS 트랜지스터(MP2)는 전원전압(VDD)에 연결된 소스, 제 1 노드(N1)에 연결된 게이트, 및 제 1 라인(L1)에 연결된 드레인을 갖는다. 제 1 NMOS 트랜지스터(MN1)는 제 1 노드(N1)에 연결된 드레인, 제 1 전압신호(VH)가 인가되는 게이트, 및 제 2 노드(N2)에 연결된 소스를 갖는다. 제 2 NMOS 트랜지스터(MN2)는 제 1 라인(L1)에 연결된 드레인, 제 2 전압신호(VL)가 인가되는 게이트, 및 제 2 노드(N2)에 연결된 소스를 갖는다. 제 1 전류원(IS1)은 제 2 노드(N2)와 접지전압(GND) 사이에 결합된다.

- [0041] 도 2에 도시된 전압-전류 변환기(110)는 제 1 전압신호(VH)와 제 2 전압신호(VL)의 차이를 증폭하여 제 1 전류 신호(I1)를 발생시켜 제 1 라인(L1)에 출력하는 차동증폭기이다. 후술하는 바와 같이, 전압-전류 변환기(110)는 연산증폭기(130)의 차동입력부와 동일한 구성을 가질 수 있다.

[0042] 제 1 NMOS 트랜지스터(MN1) 및 제 2 NMOS 트랜지스터(MN2)의 트랜스컨덕턴스(transconductance)가 gm1일 때, 제 1 전류신호(II)는 수학식 1과 같이 나타낼 수 있다.

#### 수학식 1

## $I1 = 2gm1 \times (VH - VL)$

[0043]

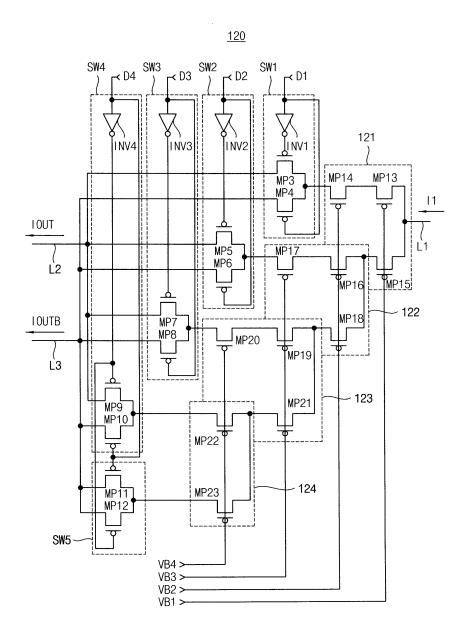

- [0044] 도 3은 도 1의 디지털-아날로그 변환기(100)에 포함된 전류 모드 디지털-아날로그 변환기(120)의 하나의 예를 나타내는 회로도이다.

- [0045] 도 3을 참조하면, 전류 모드 디지털-아날로그 변환기(120)는 제 1 전류 분배기(121), 제 2 전류 분배기(122), 제 3 전류 분배기(123), 제 4 전류 분배기(124), 제 1 스위칭부(SW1), 제 2 스위칭부(SW2), 제 3 스위칭부(SW3), 제 4 스위칭부(SW4) 및 제 5 스위칭부(SW5)를 포함한다.

- [0046] 제 1 전류 분배기(121)는 제 1 바이어스 전압(VB1)과 제 2 바이어스 전압(VB2)에 응답하여 동작하며, 제 1 전류 신호(도 1의 I1)를 2로 나눈다. 제 2 전류 분배기(122)는 제 2 바이어스 전압(VB2)과 제 3 바이어스 전압(VB3)에 응답하여 동작하며, 제 1 전류 분배기(121)의 출력 전류신호를 2로 나눈다. 제 3 전류 분배기(123)는 제 3 바이어스 전압(VB3)과 제 4 바이어스 전압(VB4)에 응답하여 동작하며, 제 2 전류 분배기(122)의 출력 전류신호를 2로 나눈다. 제 4 전류 분배기(124)는 제 4 바이어스 전압(VB4)에 응답하여 동작하며, 제 3 전류 분배기(123)의 출력 전류신호를 2로 나눈다.

- [0047] 제 1 스위칭부(SW1)는 디지털 입력신호(DIN)의 제 1 비트(D1)에 응답하여 동작하며, 제 1 전류 분배기(121)의 출력 전류신호를 제 2 라인(L2) 또는 제 3 라인(L3)에 출력한다. 제 2 스위칭부(SW2)는 디지털 입력신호(DIN)의 제 2 비트(D2)에 응답하여 동작하며, 제 2 전류 분배기(122)의 출력 전류신호를 제 2 라인(L2) 또는 제 3 라인(L3)에 출력한다. 제 3 스위칭부(SW3)는 디지털 입력신호(DIN)의 제 3 비트(D3)에 응답하여 동작하며, 제 3 전류 분배기(123)의 출력 전류신호를 제 2 라인(L2) 또는 제 3 라인(L3)에 출력한다. 제 4 스위칭부(SW4)는 디지털 입력신호(DIN)의 제 4 비트(D4)에 응답하여 동작하며, 제 4 전류 분배기(124)의 출력 전류신호를 제 2 라인(L2) 또는 제 3 라인(L3)에 출력한다. 제 5 스위칭부(SW5)는 디지털 입력신호(DIN)의 제 4 비트(D4)에 응답하여 동작한다. 그러나 제 5 스위칭부(SW5)는 디지털 입력신호(DIN)의 제 4 비트(D4)의 로직 상태에 관계없이 제 4 전류 분배기(124)의 출력 전류신호를 제 3 라인(L3)에 출력한다.

- [0048] 도 3의 전류 모드 디지털-아날로그 변환기(120)에서, 제 2 라인(L2)을 통해 IOUT가 흐르고 제 3 라인(L3)을 통해 IOUTB가 흐른다.

- [0049] 제 1 스위칭부(SW1)는 제 1 인버터(INV1), 제 3 PMOS 트랜지스터(MP3) 및 제 4 PMOS 트랜지스터(MP4)를 포함한다. 제 1 인버터(INV1)는 디지털 입력신호(DIN)의 제 1 비트(D1)의 위상을 반전시킨다. 제 3 PMOS 트랜지스터(MP3)는 제 1 인버터(INV1)의 출력신호에 응답하여 동작하고, 제 4 PMOS 트랜지스터(MP4)는 디지털 입력신호(DIN)의 제 1 비트(D1)에 응답하여 동작한다.

- [0050] 디지털 입력신호(DIN)의 제 1 비트(D1)가 로직 "하이"상태이면, 제 3 PMOS 트랜지스터(MP3)는 턴온되고 제 4 PMOS 트랜지스터(MP4)는 턴오프된다. 따라서, 제 1 스위칭부(SW1)는 제 1 전류 분배기(121)의 출력 전류신호를 제 2 전류신호(IOUT)로서 제 2 라인(L2)을 통해 출력한다. 디지털 입력신호(DIN)의 제 1 비트(D1)가 로직 "로우"상태이면, 제 3 PMOS 트랜지스터(MP3)는 턴오프되고 제 4 PMOS 트랜지스터(MP4)는 턴온된다. 따라서, 제 1 스위칭부(SW1)는 제 1 전류 분배기(121)의 출력 전류신호를 제 3 전류신호(IOUTB)로서 제 3 라인(L3)을 통해 출력한다.

- [0051] 제 2 스위칭부(SW2)는 제 2 인버터(INV2), 제 5 PMOS 트랜지스터(MP5) 및 제 6 PMOS 트랜지스터(MP6)를 포함한다. 제 2 인버터(INV2)는 디지털 입력신호(DIN)의 제 2 비트(D2)의 위상을 반전시킨다. 제 5 PMOS 트랜지스터(MP5)는 제 2 인버터(INV2)의 출력신호에 응답하여 동작하고, 제 6 PMOS 트랜지스터(MP6)는 디지털 입력신호(DIN)의 제 2 비트(D2)에 응답하여 동작한다.

- [0052] 디지털 입력신호(DIN)의 제 2 비트(D2)가 로직 "하이"상태이면, 제 5 PMOS 트랜지스터(MP5)는 턴온되고 제 6 PMOS 트랜지스터(MP6)는 턴오프된다. 따라서, 제 2 스위칭부(SW2)는 제 2 전류 분배기(122)의 출력 전류신호를 제 2 전류신호(IOUT)로서 제 2 라인(L2)을 통해 출력한다. 디지털 입력신호(DIN)의 제 2 비트(D2)가 로직 "로우"상태이면, 제 5 PMOS 트랜지스터(MP5)는 턴오프되고 제 6 PMOS 트랜지스터(MP6)는 턴온된다. 따라서, 제 2 스위칭부(SW2)는 제 2 전류 분배기(122)의 출력 전류신호를 제 3 전류신호(IOUTB)로서 제 3 라인(L3)을 통해

출력한다.

- [0053] 제 3 스위칭부(SW3)는 제 3 인버터(INV3), 제 7 PMOS 트랜지스터(MP7) 및 제 8 PMOS 트랜지스터(MP8)를 포함한다. 제 3 인버터(INV3)는 디지털 입력신호(DIN)의 제 3 비트(D3)의 위상을 반전시킨다. 제 7 PMOS 트랜지스터(MP7)는 제 3 인버터(INV3)의 출력신호에 응답하여 동작하고, 제 8 PMOS 트랜지스터(MP8)는 디지털 입력신호(DIN)의 제 3 비트(D3)에 응답하여 동작한다.

- [0054] 디지털 입력신호(DIN)의 제 3 비트(D3)가 로직 "하이"상태이면, 제 7 PMOS 트랜지스터(MP7)는 턴온되고 제 8 PMOS 트랜지스터(MP8)는 턴오프된다. 따라서, 제 3 스위칭부(SW3)는 제 3 전류 분배기(123)의 출력 전류신호를 제 2 전류신호(IOUT)로서 제 2 라인(L2)을 통해 출력한다. 디지털 입력신호(DIN)의 제 3 비트(D3)가 로직 "로우"상태이면, 제 7 PMOS 트랜지스터(MP7)는 턴오프되고 제 8 PMOS 트랜지스터(MP8)는 턴온된다. 따라서, 제 3 스위칭부(SW3)는 제 3 전류 분배기(123)의 출력 전류신호를 제 3 전류신호(IOUTB)로서 제 3 라인(L3)을 통해 출력한다.

- [0055] 제 4 스위칭부(SW4)는 제 4 인버터(INV4), 제 9 PMOS 트랜지스터(MP9) 및 제 10 PMOS 트랜지스터(MP10)를 포함한다. 제 4 인버터(INV4)는 디지털 입력신호(DIN)의 제 4 비트(D4)의 위상을 반전시킨다. 제 9 PMOS 트랜지스터 (MP9)는 제 4 인버터(INV4)의 출력신호에 응답하여 동작하고, 제 10 PMOS 트랜지스터(MP10)는 디지털 입력신호 (DIN)의 제 4 비트(D4)에 응답하여 동작한다.

- [0056] 디지털 입력신호(DIN)의 제 4 비트(D4)가 로직 "하이"상태이면, 제 9 PMOS 트랜지스터(MP9)는 턴온되고 제 10 PMOS 트랜지스터(MP10)는 턴오프된다. 따라서, 제 4 스위칭부(SW4)는 제 4 전류 분배기(124)의 출력 전류신호를 제 2 전류신호(IOUT)로서 제 2 라인(L2)을 통해 출력한다. 디지털 입력신호(DIN)의 제 4 비트(D4)가 로직 "로우"상태이면, 제 9 PMOS 트랜지스터(MP9)는 턴오프되고 제 10 PMOS 트랜지스터(MP10)는 턴온된다. 따라서, 제 4 스위칭부(SW4)는 제 4 전류 분배기(124)의 출력 전류신호를 제 3 전류신호(IOUTB)로서 제 3 라인(L3)을 통해 출력한다.

- [0057] 제 5 스위칭부(SW5)는 제 11 PMOS 트랜지스터(MP11) 및 제 12 PMOS 트랜지스터(MP12)를 포함한다. 제 11 PMOS 트랜지스터(MP11)는 디지털 입력신호(DIN)의 제 4 비트(D4)에 응답하여 동작하고, 제 12 PMOS 트랜지스터(MP1 2)는 제 4 인버터(INV4)의 출력신호에 응답하여 동작한다.

- [0058] 디지털 입력신호(DIN)의 제 4 비트(D4)가 로직 "하이"상태이면, 제 11 PMOS 트랜지스터(MP11)는 턴오프되고 제 12 PMOS 트랜지스터(MP12)는 턴온된다. 따라서, 제 5 스위칭부(SW5)는 제 4 전류 분배기(124)의 출력 전류신호를 제 3 전류신호(IOUTB)로서 제 3 라인(L3)을 통해 출력한다. 디지털 입력신호(DIN)의 제 4 비트(D4)가 로직 "로우"상태이면, 제 11 PMOS 트랜지스터(MP11)는 턴온되고 제 12 PMOS 트랜지스터(MP12)는 턴오프된다. 따라서, 제 5 스위칭부(SW5)는 제 4 전류 분배기(124)의 출력 전류신호를 제 3 전류신호(IOUTB)로서 제 3 라인(L3)을 통해 출력한다. 제 11 PMOS 트랜지스터(MP11)의 드레인과 제 12 PMOS 트랜지스터(MP12)의 드레인은 제 3 라인(L3)에 공통 연결되어 있으므로, 제 5 스위칭부(SW5)는 디지털 입력신호(DIN)의 제 4 비트(D4)의 로직 상태에 관계없이 제 4 전류 분배기(124)의 출력 전류신호를 제 3 전류신호(IOUTB)로서 제 3 라인(L3)을 통해 출력한다.

- [0059] 제 1 전류 분배기(121)는 제 13 PMOS 트랜지스터(MP13), 제 14 PMOS 트랜지스터(MP14) 및 제 15 PMOS 트랜지스터(MP15)를 포함한다. 제 13 PMOS 트랜지스터(MP13)와 제 14 PMOS 트랜지스터(MP14)는 전류미러 형태로 연결되어 있으며, 제 1 전류신호(I1)의 크기의 1/2인 전류가 제 13 PMOS 트랜지스터(MP13) 및 제 14 PMOS 트랜지스터(MP14) 각각을 통해 흐른다. 제 13 PMOS 트랜지스터(MP13)를 통해 흐르는 전류는 제 14 PMOS 트랜지스터(MP14)를 통해 흐르며, 제 14 PMOS 트랜지스터(MP14)의 드레인 전류가 제 1 전류 분배기(121)의 출력 전류신호이다.

- [0060] 제 2 전류 분배기(122)는 제 16 PMOS 트랜지스터(MP16), 제 17 PMOS 트랜지스터(MP17) 및 제 18 PMOS 트랜지스터(MP18)를 포함한다. 제 16 PMOS 트랜지스터(MP16)와 제 18 PMOS 트랜지스터(MP18)는 전류미러 형태로 연결되어 있으며, 제 16 PMOS 트랜지스터(MP16)의 게이트와 제 18 PMOS 트랜지스터(MP18)의 게이트는 제 14 PMOS 트랜지스터(MP14)의 게이트에 공통 연결되어 있다. 제 15 PMOS 트랜지스터(MP15)의 드레인 전류의 1/2인 전류가제 16 PMOS 트랜지스터(MP16) 및 제 18 PMOS 트랜지스터(MP18) 각각을 통해 흐른다. 제 16 PMOS 트랜지스터(MP16)를 통해 흐르는 전류는 제 17 PMOS 트랜지스터(MP17)를 통해 흐르며, 제 17 PMOS 트랜지스터(MP17)의 드레인 전류가 제 2 전류 분배기(122)의 출력 전류신호이다.

- [0061] 제 3 전류 분배기(123)는 제 19 PMOS 트랜지스터(MP19), 제 20 PMOS 트랜지스터(MP20) 및 제 21 PMOS 트랜지스터(MP19)를 포함한다. 제 19 PMOS 트랜지스터(MP19)와 제 21 PMOS 트랜지스터(MP21)는 전류미러 형태로 연결되

어 있으며, 제 19 PMOS 트랜지스터(MP19)의 게이트와 제 21 PMOS 트랜지스터(MP21)의 게이트는 제 17 PMOS 트랜지스터(MP17)의 게이트에 공통 연결되어 있다. 제 18 PMOS 트랜지스터(MP18)의 드레인 전류의 1/2인 전류가 제 19 PMOS 트랜지스터(MP19) 및 제 21 PMOS 트랜지스터(MP21) 각각을 통해 흐른다. 제 19 PMOS 트랜지스터(MP19)를 통해 흐르는 전류는 제 20 PMOS 트랜지스터(MP20)를 통해 흐르며, 제 20 PMOS 트랜지스터(MP20)의 드레인 전류가 제 3 전류 분배기(123)의 출력 전류신호이다.

- [0062] 제 4 전류 분배기(124)는 제 22 PMOS 트랜지스터(MP22) 및 제 23 PMOS 트랜지스터(MP23)를 포함한다. 제 22 PMOS 트랜지스터(MP22)와 제 23 PMOS 트랜지스터(MP23)는 전류미러 형태로 연결되어 있으며, 제 22 PMOS 트랜지스터(MP22)의 게이트와 제 23 PMOS 트랜지스터(MP23)의 게이트는 제 20 PMOS 트랜지스터(MP20)의 게이트에 공통 연결되어 있다. 제 21 PMOS 트랜지스터(MP21)의 드레인 전류의 1/2인 전류가 제 22 PMOS 트랜지스터(MP22) 및 제 23 PMOS 트랜지스터(MP23) 각각을 통해 흐른다. 제 22 PMOS 트랜지스터(MP22)의 드레인 전류 또는 제 23 PMOS 트랜지스터(MP23)의 드레인 전류가 제 4 전류 분배기(124)의 출력 전류신호이다.

- [0063] 도 3의 전류 모드 디지털-아날로그 변환기(120)에서 사용된 바이어스 전압들(VB1, VB2, VB3, VB4)은 제 1 내지 제 4 전류 분배기(121, 122, 123, 124) 내에 있는 PMOS 트랜지스터들을 포화 영역에서 동작시킬 수 있는 적당한 값으로 설정된다.

- [0064] 이하, 도 3에 도시된 전류 모드 디지털-아날로그 변환기(120)의 동작에 대해 설명한다.

- [0065] 도 3의 전류 모드 디지털-아날로그 변환기(120)는 PMOS 트랜지스터들로 구성되어 있으며, 4 비트(D1, D2, D3, D4)의 디지털 입력신호(DIN)를 16 개의 아날로그 전류신호로 변환하는 소스 형태(source type)의 디지털-아날로 그 변환기이다.

- [0066] 전류 모드 디지털-아날로그 변환기(120)는 디지털 입력신호(DIN)의 비트들(D1, D2, D3, D4) 및 제 1 전류신호 (I1)에 응답하여 수신된 디지털 입력신호(DIN)에 대응하는 제 2 전류신호(IOUT) 및 제 3 전류신호(IOUTB)를 발생시킨다. 제 3 전류신호(IOUTB)는 제 2 전류신호(IOUT)와 상보 관계를 갖는 전류신호이다. 제 1 전류신호(I1)는 전압-전류 변환기(도 1의 110)의 출력 전류신호로서, 제 1 전압신호(VH)와 제 2 전압신호(VL)의 차이가 전압 -전류 변환기(110)에 의해 증폭된 신호이다.

- [0067] 제 14 PMOS 트랜지스터(MP14)의 드레인 전류가 제 1 전류 분배기(121)의 출력 전류신호이며, 제 17 PMOS 트랜지스터(MP17)의 드레인 전류가 제 2 전류 분배기(122)의 출력 전류신호이며, 제 20 PMOS 트랜지스터(MP20)의 드레인 전류가 제 3 전류 분배기(123)의 출력 전류신호이며, 제 22 PMOS 트랜지스터(MP22) 또는 제 23 PMOS 트랜지스터(MP23)의 드레인 전류가 제 4 전류 분배기(124)의 출력 전류신호이다.

- [0068] 제 1 전류 분배기(121)의 출력 전류신호는 제 1 전류신호(I1)의 1/2의 크기를 가지며, 제 2 전류 분배기(122)의 출력 전류신호는 제 1 전류 분배기(121)의 출력 전류신호의 1/2의 크기를 가지며, 제 3 전류 분배기(123)의 출력 전류신호는 제 2 전류 분배기(122)의 출력 전류신호의 1/2의 크기를 가지며, 제 4 전류 분배기(124)의 출력 전류신호는 제 3 전류 분배기(123)의 출력 전류신호의 1/2의 크기를 갖는다.

- [0069] 따라서, 디지털 입력신호(DIN)의 비트들(D1, D2, D3, D4)의 로직 상태에 응답하여 제 1 내지 제 4 스위칭부 (SW1~SW4)에 포함된 PMOS 트랜지스터들을 턴온 또는 턴오프시킴으로써, 2<sup>4</sup>(=16) 개의 디지털 신호에 대응하는 전류를 제 2 전류신호(IOUT)로서 발생시킬 수 있다. 제 3 전류신호(IOUTB)는 제 2 전류신호(IOUT)와 상보 관계를 갖는 전류신호로서, 경우에 따라서 연상증폭기(도 1의 130)의 입력신호로서 사용할 수 있다.

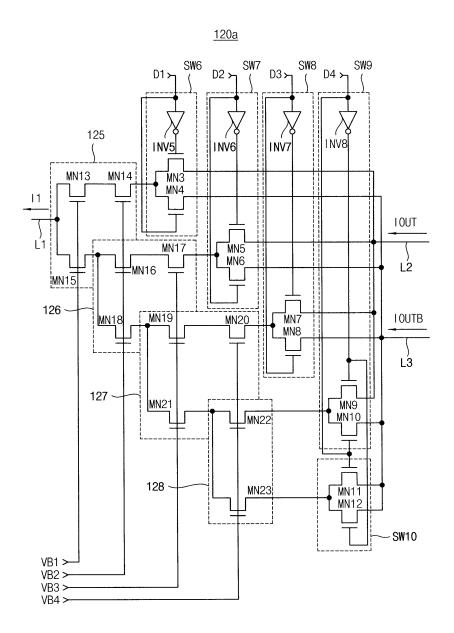

- [0070] 도 4는 도 1의 디지털-아날로그 변환기(100)에 포함된 전류 모드 디지털-아날로그 변환기(120)의 다른 하나의 예를 나타내는 회로도이다. 도 4의 전류 모드 디지털-아날로그 변환기(120a)는 NMOS 트랜지스터들로 구성되어 있으며, 4 비트(D1, D2, D3, D4)의 디지털 입력신호(DIN)를 16 개의 아날로그 전류신호로 변환하는 싱크 형태 (sink type)의 디지털-아날로그 변환기이다.

- [0071] 도 4를 참조하면, 전류 모드 디지털-아날로그 변환기(120a)는 제 5 전류 분배기(125), 제 6 전류 분배기(126), 제 7 전류 분배기(127), 제 8 전류 분배기(128), 제 6 스위칭부(SW6), 제 7 스위칭부(SW7), 제 8 스위칭부(SW8), 제 9 스위칭부(SW9) 및 제 10 스위칭부(SW10)를 포함한다.

- [0072] 제 5 전류 분배기(125)는 제 1 바이어스 전압(VB1)과 제 2 바이어스 전압(VB2)에 응답하여 동작하며, 제 1 전류 신호(I1)를 2로 나눈다. 제 6 전류 분배기(126)는 제 2 바이어스 전압(VB2)과 제 3 바이어스 전압(VB3)에 응답하여 동작하며, 제 5 전류 분배기(125)의 출력 전류신호를 2로 나눈다. 제 7 전류 분배기(127)는 제 3 바이어스 전압(VB3)과 제 4 바이어스 전압(VB4)에 응답하여 동작하며, 제 6 전류 분배기(126)의 출력 전류신호를 2로 나

눈다. 제 8 전류 분배기(128)는 제 4 바이어스 전압(VB4)에 응답하여 동작하며, 제 7 전류 분배기(127)의 출력 전류신호를 2로 나눈다.

- [0073] 도 4의 전류 모드 디지털-아날로그 변환기(120a)는 NMOS 트랜지스터들로 구성되고, 입력전류와 출력전류의 방향이 도 3의 전류 모드 디지털-아날로그 변환기(120)와 다르다. 그러나, 전류 모드 디지털-아날로그 변환기(120a)의 동작이 유사하다. 따라서, 도 4의 전류 모드 디지털-아날로그 변환기(120a)의 동작 설명은 생략한다.

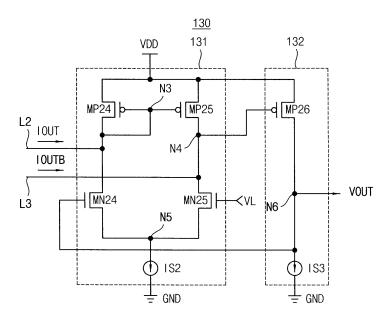

- [0074] 도 5는 도 1의 디지털-아날로그 변환기(100)에 포함된 연산 증폭기(130)의 하나의 예를 나타내는 회로도이다.

- [0075] 도 5를 참조하면, 연산 증폭기(130)는 차동 입력부(131) 및 부의 이득부(negative gain unit)(132)를 포함한다.

- [0076] 차동 입력부(131)는 제 2 전류신호(IOUT) 및 제 3 전류신호(IOUTB)를 사용하여 드레인 전류를 변조하고, 제 2 전압신호(VL)와 출력전압(VOUT)의 차이를 증폭한다. 부의 이득부(132)는 차동 입력부(131)의 출력신호를 증폭하여 출력전압(VOUT)을 발생시키며, 출력전압(VOUT)을 차동 입력부(131)에 피드백시킨다.

- [0077] 차동 입력부(131)는 제 24 PMOS 트랜지스터(MP24), 제 25 PMOS 트랜지스터(MP25), 제 24 NMOS 트랜지스터 (MN24), 제 25 NMOS 트랜지스터(MN25) 및 제 2 전류원(IS2)을 포함한다.

- [0078] 제 24 PMOS 트랜지스터(MP24)는 전원전압(VDD)에 연결된 소스, 제 3 노드(N3)에 공통 연결된 게이트 및 드레인을 갖는다. 제 25 PMOS 트랜지스터(MP25)는 전원전압(VDD)에 연결된 소스, 제 3 노드(N3)에 연결된 게이트 및 제 4 노드(N4)에 연결된 드레인을 갖는다. 제 24 NMOS 트랜지스터(MN24)는 제 3 노드(N3)에 연결된 드레인, 출력전압(VOUT)이 인가되는 게이트 및 제 5 노드(N5)에 연결된 소스를 갖는다. 제 25 NMOS 트랜지스터(MN25)는 제 4 노드(N4)에 연결된 드레인, 제 2 전압신호(VL)가 인가되는 게이트 및 제 5 노드(N5)에 연결된 소스를 갖는다. 제 2 전류원(IS2)은 제 5 노드(N5)와 접지전압(GND) 사이에 결합된다. 제 2 라인(L2)은 제 3 노드(N3)에 연결되고, 제 3 라인(L3)은 제 4 노드(N4)에 연결된다.

- [0079] 부의 이득부(132)는 제 26 PMOS 트랜지스터(MP26) 및 제 3 전류원(IS3)을 포함한다. 제 3 전류원(IS3)은 전류 미러 형태로 연결된 NMOS 트랜지스터일 수 있다. 제 26 PMOS 트랜지스터(MP26)는 전원전압(VDD)에 연결된 소스, 제 4 노드(N4)에 연결된 게이트 및 제 6노드(N6)에 연결된 드레인을 갖는다. 제 3 전류원(IS3)은 제 6 노드(N6)와 접지전압(GND) 사이에 결합된다. 제 6노드(N6)는 차동 입력부(131)를 구성하는 제 24 NMOS 트랜지스터 (MN24)의 게이트에 연결된다.

- [0080] 이하, 도 5의 연산 증폭기(130)의 동작에 대해 설명한다.

- [0081] 먼저, 제 2 전류신호(IOUT)와 제 3 전류신호(IOUTB)를 고려하지 않을 경우, 연산 증폭기(130)의 동작은 다음과 같다.

- [0082] 부의 이득부(132)는 피드백 회로로서 연산 증폭기(130)의 이득을 결정한다. 제 4 노드(N4)의 전압의 크기가 증가하면 제 6 노드(N6)의 전압, 즉 출력전압(VOUT)의 크기가 감소한다. 따라서, 부의 이득부(132)는 부 (negative)의 이득을 갖는다. 출력전압(VOUT)이 제 24 NMOS 트랜지스터(MN24)의 게이트에 피드백된다. 출력전압 (VOUT)의 크기가 감소하면, 제 24 NMOS 트랜지스터(MN24)를 통해 흐르는 전류의 크기는 감소하고, 제 25 NMOS 트랜지스터(MN25)를 통해 흐르는 전류의 크기는 증가한다. 따라서, 제 4 노드(N4)의 전압의 크기가 감소하고, 출력전압(VOUT)의 크기는 증가한다. 출력전압(VOUT)의 크기가 증가하면, 제 24 NMOS 트랜지스터(MN24)를 통해 흐르는 전류의 크기는 증가하고, 제 25 NMOS 트랜지스터(MN25)를 통해 흐르는 전류의 크기는 감소한다. 따라서, 제 4 노드(N4)의 전압의 크기가 증가하고, 출력전압(VOUT)의 크기는 감소한다.

- [0083] 따라서, 연산 증폭기(130)는 부궤환(negative feedback) 회로의 구성을 가지며, 제 2 전압신호(VL)의 크기를 갖는 안정된 출력전압(VOUT)을 발생시킨다.

- [0084] 제 2 전류신호(IOUT)와 제 3 전류신호(IOUTB)를 고려할 경우, 연산 증폭기(130)의 동작은 다음과 같다.

- [0085] 제 2 라인(L2)을 통해 수신된 제 2 전류신호(IOUT)는 제 24 NMOS 트랜지스터(MN24)의 드레인 전류를 변조시키고, 제 3 라인(L3)을 통해 수신된 제 3 전류신호(IOUTB)는 제 25 NMOS 트랜지스터(MN25)의 드레인 전류를 변조시킨다. 연산 증폭기(130)에 드레인 전류의 변조가 발생하면, 출력전압(VOUT)은 제 2 전압신호(VL)의 크기에 오프셋(offset) 전압(VOUT-OFFSET)이 더해진다.

[0086] 제 24 NMOS 트랜지스터(MN24) 및 제 25 NMOS 트랜지스터(MN25)의 트랜스컨덕턴스(transconductance)가 gm1일 때, 오프셋(offset) 전압(VOUT OFFSET)은 수학식 2와 같이 나타낼 수 있다.

#### 수학식 2

# $VOUTOFFSET = \frac{(IOUT-IOUTB)}{2gm1}$

- [0087]

- [0088] 수학식 1과 수학식 2를 비교하면, 오프셋(offset) 전압(VOUT OFFSET)의 최대값은 VH VL임을 알 수 있다. 따라서, 전류 모드 디지털-아날로그 변환기(120)를 사용하여 제 2 전류신호(IOUT)와 제 3 전류신호(IOUTB)의 양을 조절하고 도 5의 연산 증폭기(130)를 사용하여 증폭하면 디지털-아날로그 변환기(100)는 VH와 VL 사이의 전압을 보간(interpolation)할 수 있다.

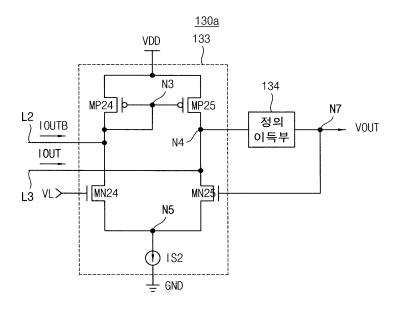

- [0089] 도 6은 도 1의 디지털-아날로그 변환기(100)에 포함된 연산 증폭기(130)의 다른 하나의 예를 나타내는 회로도이다.

- [0090] 도 6을 참조하면, 연산 증폭기(130a)는 차동 입력부(133) 및 정의 이득부(positive gain unit)(134)를 포함한다.

- [0091] 차동 입력부(133)는 제 2 전류신호(IOUT) 및 제 3 전류신호(IOUTB)를 사용하여 드레인 전류를 변조하고, 제 2 전압신호(VL)와 출력전압(VOUT)의 차이를 증폭한다. 정의 이득부(134)는 차동 입력부(133)의 출력신호를 증폭하여 출력전압(VOUT)을 발생시키며, 출력전압(VOUT)을 차동 입력부(133)에 피드백시킨다.

- [0092] 차동 입력부(133)의 회로 구성은 도 5에 있는 차동 입력부(131)의 회로 구성과 동일하다. 그러나, 도 6의 연산 증폭기(130a)에서는 출력전압(VOUT)이 제 25 NMOS 트랜지스터(MN25)의 게이트에 피드백되고, 제 2 라인(L2)을 통해 제 3 전류신호(IOUTB)가 수신되고, 제 3 라인(L3)을 통해 제 2 전류신호(IOUT)가 수신된다.

- [0093] 이하, 도 6의 연산 증폭기(130a)의 동작에 대해 설명한다.

- [0094] 먼저, 제 2 전류신호(IOUT)와 제 3 전류신호(IOUTB)를 고려하지 않을 경우, 연산 증폭기(130a)의 동작은 다음과 같다.

- [0095] 정의 이득부(134)는 피드백 회로로서 연산 증폭기(130a)의 이득을 결정한다. 제 4 노드(N4)의 전압의 크기가 증가하면 제 7 노드(N7)의 전압, 즉 출력전압(VOUT)의 크기가 증가한다. 따라서, 정의 이득부(134)는 정 (positive)의 이득을 갖는다. 출력전압(VOUT)이 제 25 NMOS 트랜지스터(MN25)의 게이트에 피드백된다. 출력전압 (VOUT)의 크기가 증가하면, 제 25 NMOS 트랜지스터(MN25)를 통해 흐르는 전류의 크기는 증가하고, 제 24 NMOS 트랜지스터(MN24)를 통해 흐르는 전류의 크기는 감소한다. 따라서, 제 4 노드(N4)의 전압의 크기가 감소하고, 출력전압(VOUT)의 크기는 감소한다. 출력전압(VOUT)의 크기가 감소하면, 제 25 NMOS 트랜지스터(MN25)를 통해 흐르는 전류의 크기는 감소하고, 제 24 NMOS 트랜지스터(MN24)를 통해 흐르는 전류의 크기는 증가한다. 따라서, 제 4 노드(N4)의 전압의 크기가 증가하고, 출력전압(VOUT)의 크기도 증가한다.

- [0096] 따라서, 연산 증폭기(130a)는 부궤환(negative feedback) 회로의 구성을 가지며, 제 2 전압신호(VL)의 크기를 갖는 안정된 출력전압(VOUT)을 발생시킨다.

- [0097] 제 2 전류신호(IOUT)와 제 3 전류신호(IOUTB)를 고려할 경우, 연산 증폭기(130a)의 동작은 다음과 같다.

- [0098] 제 2 라인(L2)을 통해 수신된 제 3 전류신호(IOUTB)는 제 24 NMOS 트랜지스터(MN24)의 드레인 전류를 변조시키고, 제 3 라인(L23을 통해 수신된 제 2 전류신호(IOUT)는 제 25 NMOS 트랜지스터(MN25)의 드레인 전류를 변조시킨다. 연산 증폭기(130a)에 드레인 전류의 변조가 발생하면, 출력전압(VOUT)은 제 2 전압신호(VL)의 크기에 오프셋(offset) 전압(VOUT-OFFSET)이 더해진다.

- [0099] 따라서, 전류 모드 디지털-아날로그 변환기(120)를 사용하여 제 2 전류신호(IOUT)와 제 3 전류신호(IOUTB)의 양을 조절하고 도 6의 연산 증폭기(130a)를 사용하여 증폭하면 디지털-아날로그 변환기(100)는 VH와 VL 사이의 전압을 보간(interpolation)할 수 있다.

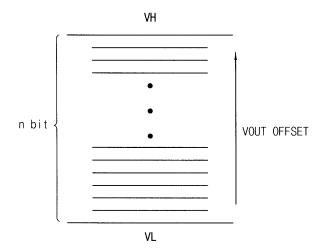

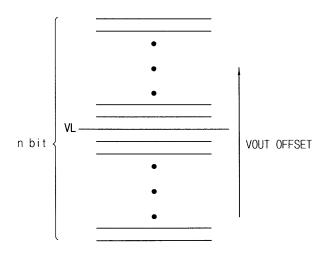

- [0100] 도 7 및 도 8은 도 1에 도시된 디지털-아날로그 변환기(100)의 출력 오프셋 전압(VOUT OFFSET)의 범위를 설명하기 위한 도면이다.

- [0101] 도 7은 제 3 전류신호(IOUTB)는 사용하지 않고 제 2 전류신호(IOUT)만 사용해서 드레인 전류를 변조하여 디지털

-아날로그 변환을 수행할 경우의 출력 오프셋 전압(VOUT OFFSET)의 범위를 나타내며, 도 8은 제 2 전류신호 (IOUT)와 제 3 전류신호(IOUTB)를 모두 사용해서 드레인 전류를 변조하여 디지털-아날로그 변환을 수행할 경우의 출력 오프셋 전압(VOUT OFFSET)의 범위를 나타낸다.

- [0102] 제 2 전류신호(IOUT)만 사용해서 디지털-아날로그 변환을 수행할 경우, 출력전압(VOUT)은 제 2 전압신호(VL)의 크기에 오프셋 전압(VOUT-OFFSET)이 더해져 VL에서 VH까지의 값을 갖는다. 제 2 전류신호(IOUT)와 제 3 전류신호(IOUTB)를 모두 사용해서 디지털-아날로그 변환을 수행할 경우, 출력전압(VOUT)은 제 2 전압신호(VL)에 위 방향과 아래 방향으로 오프셋 전압(VOUT-OFFSET)이 더해져, VL을 중심으로 대칭인 값을 갖는다.

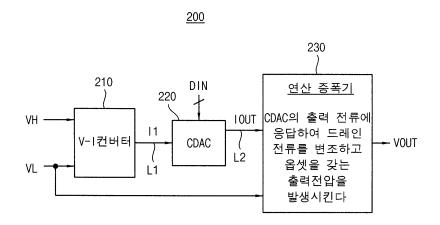

- [0103] 도 9는 본 발명의 제 2 실시예에 따른 디지털-아날로그 변환기(200)를 나타내는 블록도이다.

- [0104] 도 9를 참조하면, 디지털-아날로그 변환기(200)는 전압-전류 변환기(210), 전류 모드 디지털-아날로그 변환기 (CDAC)(220) 및 연산증폭기(230)를 포함한다.

- [0105] 전압-전류 변환기(210)는 제 1 전압 레벨을 갖는 제 1 전압신호(VH)와 제 2 전압 레벨을 갖는 제 2 전압신호 (VL)의 차이에 비례하는 제 1 전류신호(I1)를 발생시킨다. 전류 모드 디지털-아날로그 변환기(220)는 제 1 라인 (L1)으로부터 제 1 전류신호(I1)를 수신하고, 디지털 입력신호(DIN) 및 제 1 전류신호(I1)에 응답하여 디지털 입력신호(DIN)에 대응하는 제 2 전류신호(IOUT)를 발생시킨다. 연산증폭기(230)는 제 2 라인(L2)으로부터 제 2 전류신호(IOUT)를 수신하고, 제 2 전류신호(IOUT) 및 제 2 전압신호(VL)에 응답하여 드레인 전류를 변조하고 옵셋을 갖는 출력전압(VOUT)을 발생시킨다.

- [0106] 도 9에 도시된 디지털-아날로그 변환기(200)는 도 1에 도시된 디지털-아날로그 변환기(100)와 달리, 제 3 전류 신호(IOUTB)는 사용하지 않고 제 2 전류신호(IOUT)만 사용해서 드레인 전류를 변조하여 디지털-아날로그 변환을 수행한다.

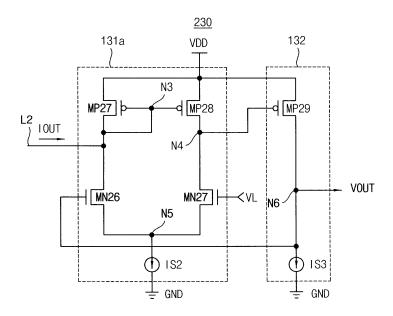

- [0107] 도 10은 도 9의 디지털-아날로그 변환기(200)에 포함된 연산 증폭기(230)의 하나의 예를 나타내는 회로도이다.

- [0108] 도 10을 참조하면, 연산 증폭기(230)는 차동 입력부(131a) 및 부의 이득부(negative gain unit)(132)를 포함한다. 차동 입력부(131a)의 제 3 노드(N3)에 제 2 라인(L2)이 결합되어 있으며, 제 2 전류신호(IOUT)가 제 2 라인(L2)을 통해 수신된다.

- [0109] 도 10의 연산 증폭기(230)는 도 5에 도시된 연산 증폭기(130)와 동작이 유사하므로 설명을 생략한다.

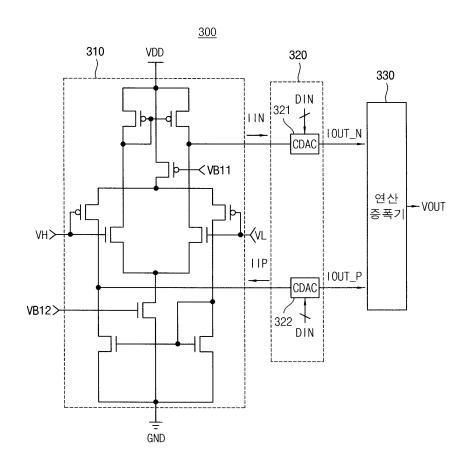

- [0110] 도 11은 본 발명의 제 3 실시예에 따른 디지털-아날로그 변환기(300)를 나타내는 회로도이고, 도 12는 도 11의 디지털-아날로그 변환기(300)에 포함된 연산 증폭기(330)의 하나의 예를 나타내는 회로도이다.

- [0111] 도 11 및 도 12를 참조하면, 디지털-아날로그 변환기(300)는 CMOS(Complementary Metal Oxide Semiconductor) 트랜지스터들을 사용한 레일-투-레일(rail-to-rail) 증폭기의 구조를 갖는다.

- [0112] 디지털-아날로그 변환기(300)는 전압-전류 변환기(310), 전류 모드 디지털-아날로그 변환기(320) 및 연산증폭기 (330)를 포함한다.

- [0113] 전압-전류 변환기(310)와 연산증폭기(330)는 모두 PMOS 트랜지스터들로 구성된 회로 부분과 NMOS 트랜지스터들 로 구성된 회로 부분이 결합된 구성을 갖는다. 전류 모드 디지털-아날로그 변환기(320)는 PMOS 트랜지스터들로 구성된 회로 부분과 NMOS 트랜지스터들로 구성된 회로 부분에 전류를 제공하기 위해 제 1 전류 모드 디지털-아날로그 변환부(321) 및 제 2 전류 모드 디지털-아날로그 변환부(322)를 포함한다.

- [0114] 도 11에 도시된 디지털-아날로그 변환기(300)는 레일-투-레일 증폭기 구조를 가지므로 동작 범위가 넓다.

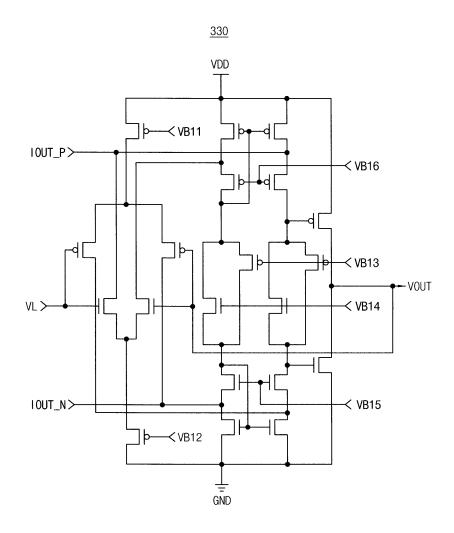

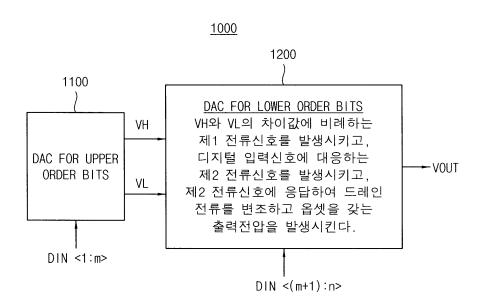

- [0115] 도 13은 본 발명의 제 4 실시예에 따른 디지털-아날로그 변환기를 나타내는 블록도이다.

- [0116] 도 13을 참조하면, 디지털-아날로그 변환기(1000)는 제 1 디지털-아날로그 변환기(1100) 및 제 2 디지털-아날로 그 변환기(1200)를 포함한다.

- [0117] 제 1 디지털-아날로그 변환기(1100)는 디지털 입력신호(DIN)의 상위 비트들(DIN<1:m)에 대해 디지털-아날로그 변환을 수행하여, 제 1 전압 레벨을 갖는 제 1 전압신호(VH)와 제 2 전압 레벨을 갖는 제 2 전압신호(VL)를 발생시킨다.

- [0118] 제 2 디지털-아날로그 변환기(1200)는 제 1 전압신호(VH)와 제 2 전압신호(VL)의 크기 차이에 비례하는 제 1 전 류신호를 발생시키고, 디지털 입력신호의 하위 비트들(DIN<(m+1):n) 및 상기 제 1 전류신호에 응답하여 디지털 입력신호(DIN)에 대응하는 제 2 전류신호를 발생시키고, 상기 제 2 전류신호 및 제 2 전압신호(VL)에 응답하여

드레인 전류를 변조하고 옵셋을 갖는 출력전압(VOUT)을 발생시킨다.

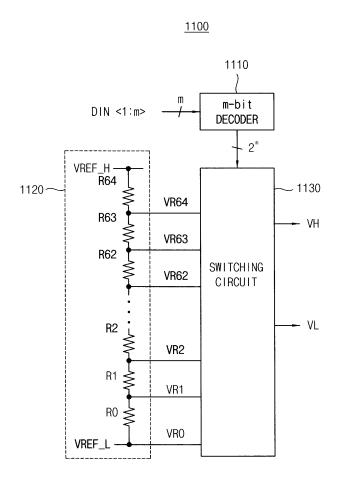

- [0119] 도 14는 도 13의 디지털-아날로그 변환기(1000)에 포함된 디지털 입력신호의 상위 비트들(DIN<1:m)에 대해 디지털-아날로그 변환을 수행하는 제 1 디지털-아날로그 변환기(1100)의 예를 나타내는 회로도이다.

- [0120] 도 14를 참조하면, 제 1 디지털-아날로그 변환기(1100)는 디코더(1110), 저항 스트링(1120) 및 스위칭 회로 (1130)를 포함한다.

- [0121] 디코더(1110)는 디지털 입력신호(DIN)의 상위 비트들(DIN<1:m)(m은 자연수)에 대해 디코딩을 수행하여 2<sup>m</sup> 개의 디지털 신호를 발생시킨다.

- [0122] 저항 스트링(1120)은 제 1 기준전압(VREF\_H)과 제 2 기준전압(VREF\_L) 사이에 결합되어 있고, 서로 직렬 연결된 저항들(R0~R64)을 포함하며, 기준전압들(VR0~VR64)을 출력한다. 디지털 입력신호(DIN)가 6 비트의 데이터라면, 저항 스트링(1120)은 직렬 연결된 65(64+1) 개의 저항을 포함하며, 65 개의 기준전압들(VR0~VR64)을 출력한다.

- [0123] 스위칭 회로(1130)는 2<sup>™</sup> 개의 디지털 신호에 응답하여 기준전압들(VRO~VR64) 중 인접한 두 개의 기준전압을 제 1 전압신호(VH) 및 제 1 전압신호(VH)로서 출력한다.

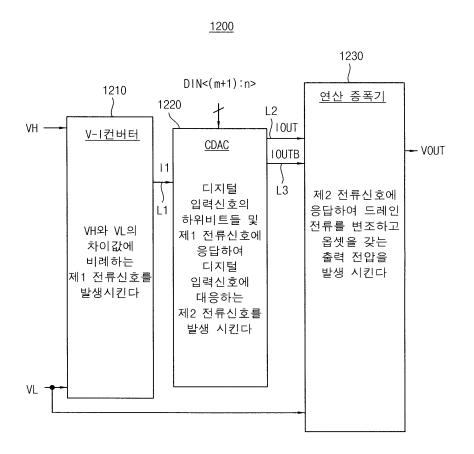

- [0124] 도 15는 도 13의 디지털-아날로그 변환기(1000)에 포함된 디지털 입력신호의 하위 비트들(DIN<(m+1):n)(m, n은 자연수)에 대해 디지털-아날로그 변환을 수행하는 제 2 디지털-아날로그 변환기(1200)의 예를 나타내는 블록도이다.

- [0125] 도 15를 참조하면, 제 2 디지털-아날로그 변환기(1200)는 전압-전류 변환기(1210), 전류 모드 디지털-아날로그 변환기(CDAC)(1220) 및 연산증폭기(1230)를 포함한다.

- [0126] 전압-전류 변환기(1210)는 제 1 전압 레벨을 갖는 제 1 전압신호(VH)와 제 2 전압 레벨을 갖는 제 2 전압신호 (VL)의 차이에 비례하는 제 1 전류신호(I1)를 발생시킨다. 전류 모드 디지털-아날로그 변환기(CDAC)(1220)는 제 1 라인(L1)으로부터 제 1 전류신호(I1)를 수신하고, 디지털 입력신호의 하위 비트들(DIN<(m+1):n) 및 상기 제 1 전류신호(I1)에 응답하여 디지털 입력신호(DIN)에 대응하는 제 2 전류신호(IOUT) 및 제 3 전류신호(IOUTB)를 발생시킨다. 제 3 전류신호(IOUTB)는 제 2 전류신호(IOUT)와 상보(complementary) 관계를 갖는 전류신호이다.

- [0127] 연산증폭기(1230)는 제 2 라인(L2) 및 제 3 라인(L3)으로부터 각각 제 2 전류신호(IOUT) 및 제 3 전류신호 (IOUTB)를 수신하고, 제 2 전류신호(IOUT), 제 3 전류신호(IOUTB) 및 제 2 전압신호(VL)에 응답하여 드레인 전류를 변조하고 옵셋을 갖는 출력전압(VOUT)을 발생시킨다.

- [0128] 전압-전류 변환기(1210), 전류 모드 디지털-아날로그 변환기(CDAC)(1220) 및 연산증폭기(1230)는 각각 도 1에 있는 전압-전류 변환기(110), 전류 모드 디지털-아날로그 변환기(CDAC)(120) 및 연산증폭기(130)의 구성과 동일 한 구성을 가질 수 있다.

- [0129] 도 15의 제 2 디지털-아날로그 변환기(1200)에서 디지털 입력신호(DIN)의 상위 비트들(DIN<1:m)은 저항 스트링을 포함하는 제 1 디지털-아날로그 변환기(1100)에 의해 디지털-아날로그 변환이 이루어지고, 디지털 입력신호의 하위 비트들(DIN<(m+1):n)은 드레인 전류 변조를 수행하는 제 2 디지털-아날로그 변환기(1200)에 의해 디지털-아날로그 변환이 이루어진다.

- [0130] 예를 들어 10비트의 디지털 입력신호(DIN)의 경우, 디지털 입력신호(DIN)의 상위 6 비트는 저항 스트링을 포함하는 제 1 디지털-아날로그 변환기(1100)에 의해 디지털-아날로그 변환이 이루어져 64 개의 아날로그 신호가 출력된다. 또한, 디지털 입력신호(DIN)의 하위 4 비트는 제 2 디지털-아날로그 변환기(1200)에 의해 디지털-아날로그 변환기(1200)에 의해 디지털-아날로그 변환이 이루어져 16 개의 아날로그 신호가 출력된다. 제 1 디지털-아날로그 변환기(1100)의 출력신호 및 디지털 입력신호(DIN)의 하위 4 비트에 응답하여 디지털-아날로그 변환을 수행하면, 1024 개의 아날로그 신호가 출력된다.

- [0131] 따라서, 디지털-아날로그 변환기(1000)는 제 1 디지털-아날로그 변환기(1100) 및 제 2 디지털-아날로그 변환기 (1100)를 사용하여 10비트의 디지털-아날로그 변환을 수행할 수 있다.

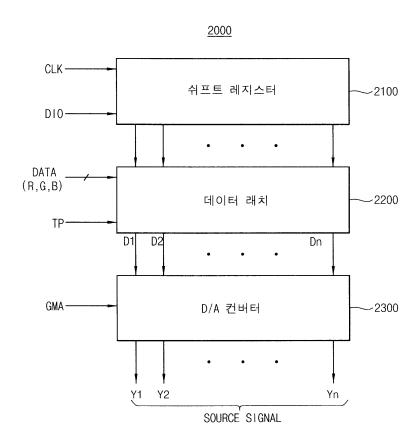

- [0132] 도 16은 본 발명의 실시예에 따른 디지털-아날로그 변환기를 포함하는 소스 구동 회로(2000)를 나타내는 블록도이다.

- [0133] 도 16을 참조하면, 소스 구동 회로(2000)는 쉬프트 레지스터(2100), 데이터 래치 회로(2200) 및 D/A 컨버터

(digital to analog converter)(2300)를 구비한다.

- [0134] 쉬프트 레지스터(2100)는 클럭신호(CLK)와 입출력 제어신호(DIO)를 수신하고, 일정 수의 클럭신호마다 펄스신호를 발생시킨다. 데이터 래치 회로(2200)는 데이터(DATA)와 로드신호(TP)를 수신한다. 데이터 래치 회로(2200)는 쉬프트 레지스터(2100)의 쉬프트 순서에 따라 데이터(DATA)를 래치하고, 로드신호(TP)가 인가되면 데이터(DATA)를 출력한다.

- [0135] D/A 컨버터(2300)는 계조전압(GMA)을 사용하여, 데이터 래치 회로(2200)의 출력신호들(D1 ~ Dn)에 대응하는 아날로그 신호인 소스 신호들(Y1 ~ Yn)을 발생시킨다. 소스 신호들(Y1 ~ Yn)은 데이터 래치 회로(2200)에 인가되는 데이터(DATA)의 순서에 따라서 각 소스라인들에 출력된다.

- [0136] 도 16의 소스 구동 회로(2000)는 상기 실시예들에 따른 디지털-아날로그 변환기의 구성을 갖는다. 소스 구동 회로(2000)에 포함된 디지털-아날로그 변환기는 드레인 전류를 변조하고 옵셋을 갖는 출력전압을 발생시켜 디지털-아날로그 변환을 수행할 수 있다. 또한, 소스 구동 회로(2000)에 포함된 디지털-아날로그 변환기는 저항 스트링을 갖는 제 1 아날로그-디지털 변환기를 사용하여 디지털 입력신호의 상위 비트들에 대한 디지털-아날로그 변환을 수행하고, 전류 모드 디지털-아날로그 변환기를 포함하는 제 2 아날로그-디지털 변환기를 사용하여 디지털 입력신호의 하위 비트들에 대한 디지털-아날로그 변환을 수행할 수 있다.

- [0137] 도 17은 본 발명의 실시예에 따른 소스 구동 회로를 포함하는 LCD(Lyquid Crystal Display) 장치(3000)를 나타 내는 블록도이다.

- [0138] 도 17을 참조하면, LCD 장치(3000)는 제어부(3100), 게이트 구동부(3200), 소스 구동부(3300), 액정 패널 (3400), 및 계조전압 발생부(3500)를 구비한다.

- [0139] 액정 패널(3400)은 매트릭스의 각 교차점에 있는 TFT(Thin Film Transistor)를 가진다. TFT의 소스는 소스 신호("데이터 신호"라고도 함)를 수신하고, TFT의 게이트는 게이트 신호("주사 신호"라고도 함)를 수신한다. TFT의 드레인 단자와 공통전압(VCOM) 사이에 스토리지 커패시터(storage capacitor)(CST)와 액정 커패시터(CLC)가 연결되어 있다. 액정 패널(3400)은 게이트 라인(G1 ~ Gn)을 통해 게이트 신호를 수신하고, 소스 라인(D1 ~ Dm)을 통해 소스 신호를 수신한다. 게이트 구동부(3200)는 온 전압(Von)과 오프 전압(Voff)의 조합으로 이루어진 게이트 신호들을 게이트 라인들(G1 ~ Gn)에 인가한다.

- [0140] 계조전압 발생부(3500)는 LCD 장치(3000)의 휘도와 관련된 정극성과 부극성의 계조전압들(GMA)을 발생시킨다.

- [0141] 소스 구동부(3300)는 계조전압 발생부(3500)의 출력인 계조전압들(GMA)을 이용하여 제어부(3100)로부터 수신되는 데이터(DATA)를 D/A 변환하고 소스 라인들(D1 ~ Dm)에 인가한다.

- [0142] 제어부(3100)는 RGB 영상신호(R, G, B), 및 수직동기 신호(Vsync), 수평동기 신호(Hsync), 메인 클럭신호 (MCLK), 데이터 인에이블 신호(DE) 등의 제어신호들을 수신한다. 제어부(100)는 이들 제어신호들에 기초하여 소스 제어신호(CONT1) 및 게이트 제어신호(CONT2)를 발생시키고 영상신호들(DATA(R, G, B))을 액정 패널(3400)의 동작조건에 맞게 적절히 처리한 후, 게이트 제어신호(CONT2)를 게이트 구동부(3200)에 전송하고, 소스 제어신호 (CONT1)와 영상신호(DATA(R, G, B))를 소스 구동부(3300)에 전송한다.

- [0143] 게이트 구동부(3200)와 소스 구동부(3300)는 각각 복수의 게이트 드라이브 IC(Integrated Circuit)와 복수의 소스 드라이브 IC를 구비할 수 있다(미도시). 데이터(DATA)는 각 픽셀에 대한 계조 레벨(gray level)을 결정한다. 소스 구동부(3300)는 소스 신호들을 액정 패널(liquid crystal panel)(3400) 상에 배열되어 있는 소스 라인에 인가하고, 게이트 구동부(3200)는 게이트 신호들을 액정 패널(3400)상에 배열되어 있는 게이트 라인에 인가한다.

- [0144] 도 17의 LCD 장치(3000)에 포함된 소스 구동부(3300)는 도 16의 소스 구동 회로(2000)와 같은 구성을 갖는다. 따라서, LCD 장치(3000)는 상기 실시예의 디지털-아날로그 변환기를 포함한다. LCD 장치(3000)에 포함된 디지털-아날로그 변환기는 드레인 전류를 변조하고 옵셋을 갖는 출력전압을 발생시켜 디지털-아날로그 변환을 수행할수 있다. 또한, LCD 장치(3000)에 포함된 디지털-아날로그 변환기는 저항 스트링을 갖는 제 1 아날로그-디지털 변환기를 사용하여 디지털 입력신호의 상위 비트들에 대한 디지털-아날로그 변환을 수행하고, 전류 모드 디지털-아날로그 변환기를 포함하는 제 2 아날로그-디지털 변환기를 사용하여 디지털 입력신호의 하위 비트들에 대한 디지털-아날로그 변환을 수행할수 있다.

- [0145] 상기에서는 디지털-아날로그 변환기, 이를 포함하는 소스 구동회로, 및 이를 포함하는 LCD 장치에 대해 기술하였지만, 본 발명은 LCD 장치뿐만 아니라 PDP(Plasma Display Panel), OLED(Organic Light Emitting Diode) 등

일반적인 표시 장치에 적용이 가능하다.

### 산업이용 가능성

- [0146] 본 발명은 디지털-아날로그 변환기 및 이를 포함하는 표시 장치에 적용이 가능하며, 특히 8 비트 이상의 고계조 (high gray scale) LCD 장치의 구동 회로에 적용이 가능하다.

- [0147] 상기에서는 본 발명의 바람직한 실시예를 참조하여 설명하였지만, 해당 기술 분야의 숙련된 당업자는 하기의 특 허 청구의 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

#### 도면의 간단한 설명

- [0148] 도 1은 본 발명의 제 1 실시예에 따른 디지털-아날로그 변환기를 나타내는 블록도이다.

- [0149] 도 2는 도 1의 디지털-아날로그 변환기에 포함된 전압-전류 변환기의 하나의 예를 나타내는 회로도이다.

- [0150] 도 3은 도 1의 디지털-아날로그 변환기에 포함된 전류 모드 디지털-아날로그 변환기의 하나의 예를 나타내는 회로도이다.

- [0151] 도 4는 도 1의 디지털-아날로그 변환기에 포함된 전류 모드 디지털-아날로그 변환기의 다른 하나의 예를 나타내는 회로도이다.

- [0152] 도 5는 도 1의 디지털-아날로그 변화기에 포함된 연산 증폭기의 하나의 예를 나타내는 회로도이다.

- [0153] 도 6은 도 1의 디지털-아날로그 변화기에 포함된 연산 증폭기의 다른 하나의 예를 나타내는 회로도이다.

- [0154] 도 7 및 도 8은 도 1에 도시된 디지털-아날로그 변환기의 출력 오프셋 전압의 범위를 설명하기 위한 도면이다.

- [0155] 도 9는 본 발명의 제 2 실시예에 따른 디지털-아날로그 변환기를 나타내는 블록도이다.

- [0156] 도 10은 도 9의 디지털-아날로그 변환기에 포함된 연산 증폭기의 하나의 예를 나타내는 회로도이다.

- [0157] 도 11은 본 발명의 제 3 실시예에 따른 디지털-아날로그 변환기를 나타내는 회로도이다.

- [0158] 도 12는 도 11의 디지털-아날로그 변환기에 포함된 연산 증폭기의 하나의 예를 나타내는 회로도이다.

- [0159] 도 13은 본 발명의 제 4 실시예에 따른 디지털-아날로그 변환기를 나타내는 블록도이다.

- [0160] 도 14는 도 13의 디지털-아날로그 변환기에 포함된 디지털 입력신호의 상위 비트들에 대해 디지털-아날로그 변환을 수행하는 제 1 디지털-아날로그 변환기의 예를 나타내는 회로도이다.

- [0161] 도 15는 도 13의 디지털-아날로그 변환기에 포함된 디지털 입력신호의 하위 비트들에 대해 디지털-아날로그 변환을 수행하는 제 2 디지털-아날로그 변환기의 예를 나타내는 블록도이다.

- [0162] 도 16은 본 발명의 실시예에 따른 디지털-아날로그 변환기를 포함하는 소스 구동 회로를 나타내는 블록도이다.

- [0163] 도 17은 본 발명의 실시예에 따른 소스 구동 회로를 포함하는 LCD 장치를 나타내는 블록도이다.

- [0164] <도면의 주요부분에 대한 부호의 설명>

- [0165] 100, 200, 300, 1000 : 디지털-아날로그 변환기

- [0166] 1100 : 제 1 디지털-아날로그 변환기

- [0167] 1200 : 제 2 디지털-아날로그 변환기

- [0168] 110, 210, 310, 1210 : 전압-전류 변환기

- [0169] 120, 220, 320, 1220 : 전류 모드 디지털-아날로그 변환기

- [0170] 130, 230, 330, 1230 : 연산증폭기

- [0171] 2000 : 소스 구동회로

- [0172] 3000 : LCD 장치

## 도면1

## 도면8

도면17