# (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 113594254 B (45) 授权公告日 2024. 01. 23

(21)申请号 202110862381.4

(22) 申请日 2021.07.29

(65) 同一申请的已公布的文献号 申请公布号 CN 113594254 A

(43) 申请公布日 2021.11.02

(73) 专利权人 上海华虹宏力半导体制造有限公司

地址 201203 上海市浦东新区张江高科技园区祖冲之路1399号

(72) 发明人 刘冬华 蔡晓晴 段文婷 令海阳

(74) 专利代理机构 上海浦一知识产权代理有限 公司 31211

专利代理师 戴广志

(51) Int.CI.

**H01L 29/78** (2006.01)

#### (56) 对比文件

CN 105789311 A,2016.07.20

H01L 29/06 (2006.01)

CN 107564965 A,2018.01.09

CN 110190110 A,2019.08.30

CN 104518023 A, 2015.04.15

CN 112382658 A, 2021.02.19

CN 108493248 A,2018.09.04

CN 101969074 A, 2011.02.09

US 2016181369 A1,2016.06.23

CN 108258051 A,2018.07.06

CN 106298935 A, 2017.01.04

CN 102569045 A,2012.07.11

审查员 戴丽娟

权利要求书1页 说明书4页 附图2页

## (54) 发明名称

改善跨导的LDMOS器件结构

#### (57) 摘要

本申请涉及半导体集成电路制造技术领域, 具体涉及一种改善跨导的LDMOS器件结构。改善 跨导的LDMOS器件结构包括:基底层,基底层中形 成横向相邻的沟道区和漂移区,沟道区和漂移区 均从基底层的上表面向下延伸;栅结构,栅结构 沿着基底层的表面,跨接在沟道区和漂移区之 间,其栅结构的第一端部和第二端部,分别与沟 道区和漂移区重叠;在漂移区中,远离沟道区的 一侧形成第一漏端掺杂区,在第一漏端掺杂区与 栅结构第二端部之间的漂移区位置处,形成第一 场氧层,第二端部与第一场氧层重叠;在靠近栅 结构第一端部位置处的沟道区中,形成源端掺杂 区;漂移区下方位置处的基底层中形成耐压提高 区,耐压提高区与漂移区纵向接触。

1.一种改善跨导的LDMOS器件结构,其特征在于,所述改善跨导的LDMOS器件结构包括: 基底层,所述基底层中形成横向相邻的沟道区和漂移区,所述沟道区和漂移区均从所述基底层的上表面向下延伸;

栅结构,所述栅结构沿着所述基底层的表面,跨接在所述沟道区和漂移区之间,其所述栅结构的第一端部和第二端部,分别与所述沟道区和漂移区重叠;

在所述漂移区中,远离所述沟道区的一侧形成第一漏端掺杂区,在所述第一漏端掺杂区与所述栅结构第二端部之间的所述漂移区位置处,形成第一场氧层,所述第二端部与所述第一场氧层重叠;

在靠近所述栅结构第一端部位置处的所述沟道区中,形成源端掺杂区;

所述漂移区下方位置处的基底层中形成耐压提高区,所述耐压提高区与所述漂移区纵向接触:

所述漂移区为第一导电类型,所述漂移区中的掺杂浓度范围为1e17cm<sup>-3</sup>~1e18cm<sup>-3</sup>; 所述耐压提高区为第二导电类型,所述耐压提高区中的掺杂浓度范围为5e17cm<sup>-3</sup>~ 5e18cm<sup>-3</sup>:

所述漂移区在所述基底层中,沿纵向延伸的第一深度为0.6微米至1.0微米; 所述耐压提高区在所述基底层中,沿纵向延伸的第二深度为1.4微米至3.0微米。

2.如权利要求1所述的改善跨导的LDMOS器件结构,其特征在于,所述基底层中还形成高压隔离区;

所述高压隔离区,位于所述漂移区相对于所述沟道区的另一侧,用于将所述LDMOS器件隔离。

- 3.如权利要求2所述的改善跨导的LDMOS器件结构,其特征在于,所述高压隔离区中形成第二漏端掺杂区。

- 4. 如权利要求3所述的改善跨导的LDMOS器件结构,其特征在于,所述第二漏端掺杂区与所述第一漏端掺杂区之间的基底层中,形成第二场氧层。

- 5. 如权利要求2所述的改善跨导的LDMOS器件结构,其特征在于,所述高压隔离区从所述基底层的上表面向下延伸,所述高压隔离区的下端连有第一导电类型埋层;

所述第一导电类型埋层在所述基底层中横向延伸;

横向延伸的所述第一导电类型埋层,与纵向延伸的所述高压隔离区,半包围所述LDMOS 器件结构。

6.如权利要求5所述的改善跨导的LDMOS器件结构,其特征在于,所述高压隔离区为第一导电类型。

# 改善跨导的LDMOS器件结构

## 技术领域

[0001] 本申请涉及半导体集成电路制造技术领域,具体涉及一种改善跨导的LDMOS器件结构。

#### 背景技术

[0002] 高压LDMOS(横向扩散MOS, Lateral Diffuse MOS)器件,既具有分立器件高压大电流特点,又汲取了低压集成电路高密度智能逻辑控制的优点,单芯片实现原来多个芯片才能完成的功能,大大缩小了面积,降低了成本,提高了能效,符合现代电力电子器件小型化,智能化,低能耗的发展方向。

[0003] 相关技术中,为了提高LDMOS器件的耐压,采用降低外延层掺杂浓度或增大漂移区长度、深度的方案,以提高器件击穿电压的同时增大器件的导通电阻。但是随着器件漂移区深度的增加,器件的跨导受到压缩,从而导致器件饱和电流不足的问题。

#### 发明内容

[0004] 本申请提供了一种改善跨导的LDMOS器件结构,可以解决相关技术中漂移区深度较大,使得器件的跨导受到压缩,从而导致器件饱和电流不足的问题。

[0005] 为了解决背景技术中所述的技术问题,本申请提供一种改善跨导的LDMOS器件结构,所述改善跨导的LDMOS器件结构包括:

[0006] 基底层,所述基底层中形成横向相邻的沟道区和漂移区,所述沟道区和漂移区均从所述基底层的上表面向下延伸;

[0007] 栅结构,所述栅结构沿着所述基底层的表面,跨接在所述沟道区和漂移区之间,其所述栅结构的第一端部和第二端部,分别与所述沟道区和漂移区重叠;

[0008] 在所述漂移区中,远离所述沟道区的一侧形成第一漏端掺杂区,在所述第一漏端掺杂区与所述栅结构第二端部之间的所述漂移区位置处,形成第一场氧层,所述第二端部与所述第一场氧层重叠;

[0009] 在靠近所述栅结构第一端部位置处的所述沟道区中,形成源端掺杂区;

[0010] 所述漂移区下方位置处的基底层中形成耐压提高区,所述耐压提高区与所述漂移区纵向接触。

[0011] 可选地,所述基底层中还形成高压隔离区;

[0012] 所述高压隔离区,位于所述漂移区相对于所述沟道区的另一侧,用于将所述LDMOS 器件隔离。

[0013] 可选地,所述高压隔离区中形成第二漏端掺杂区。

[0014] 可选地,所述第二漏端掺杂区与所述第一漏端掺杂区之间的基底层中,形成第二场氧层。

[0015] 可选地,所述高压隔离区从所述基底层的上表面向下延伸,所述高压隔离区的下端连有第一导电类型埋层:

[0016] 所述第一导电类型埋层在所述基底层中横向延伸;

[0017] 横向延伸的所述第一导电类型埋层,与纵向延伸的所述高压隔离区,半包围所述 LDMOS器件结构。

[0018] 可选地,所述高压隔离区为第一导电类型。

[0019] 可选地,所述漂移区为第一导电类型,所述漂移区中的掺杂浓度范围为1e17cm<sup>-3</sup>~1e18cm<sup>-3</sup>。

[0020] 可选地,所述耐压提高区为第二导电类型,所述耐压提高区中的掺杂浓度范围为 5e17cm<sup>-3</sup>~5e18cm<sup>-3</sup>。

[0021] 可选地,所述漂移区在所述基底层中,沿纵向延伸的第一深度为0.6微米至1.0微米。

[0022] 可选地,所述耐压提高区在所述基底层中,沿纵向延伸的第二深度为1.4微米至3.0微米。

[0023] 本申请技术方案,至少包括如下优点:通过在漂移区下方位置处的基底层中,形成耐压提高区,使得该耐压提高区与该漂移区在纵向上接触,从而能够使得不改变该漂移区横向长度、保证器件耐压性能的同时,在纵向上减薄该漂移区的深度,以提高该LDMOS器件的跨导,增大器件的饱和电流。

### 附图说明

[0024] 为了更清楚地说明本申请具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本申请的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

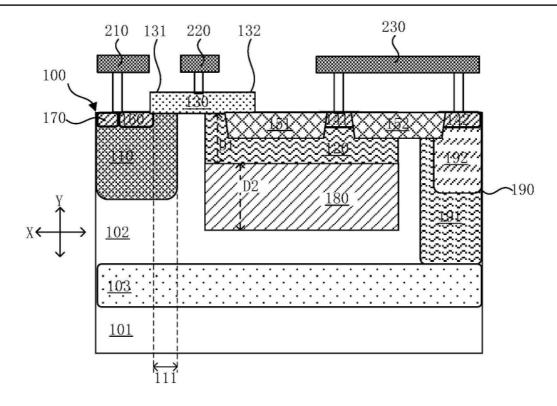

[0025] 图1示出了本申请一实施例提供的改善跨导的LDMOS器件结构;

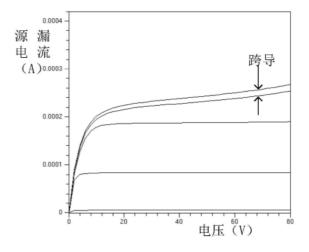

[0026] 图2示出了相关技术提供的LDMOS器件,其跨导变化曲线;

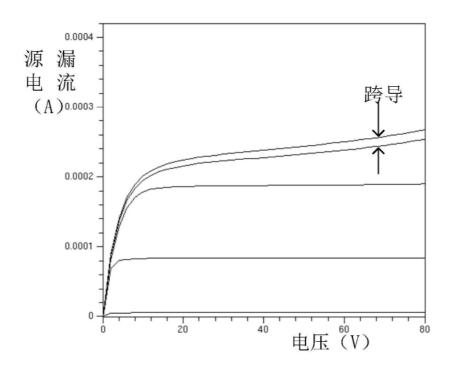

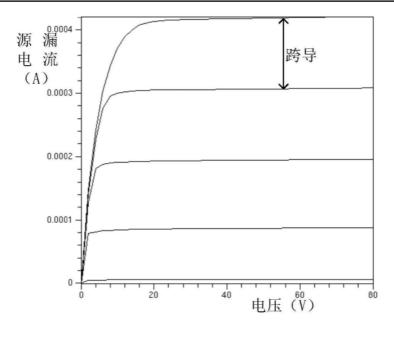

[0027] 图3示出了本申请提供的LDMOS器件,其跨导变化曲线。

#### 具体实施方式

[0028] 下面将结合附图,对本申请中的技术方案进行清楚、完整的描述,显然,所描述的实施例是本申请的一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在不做出创造性劳动的前提下所获得的所有其它实施例,都属于本申请保护的范围。

[0029] 在本申请的描述中,需要说明的是,术语"中心"、"上"、"下"、"左"、"右"、"竖直"、"水平"、"内"、"外"等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本申请和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本申请的限制。此外,术语"第一"、"第二"、"第三"仅用于描述目的,而不能理解为指示或暗示相对重要性。

[0030] 在本申请的描述中,需要说明的是,除非另有明确的规定和限定,术语"安装"、"相连"、"连接"应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电气连接;可以是直接相连,也可以通过中间媒介间接相连,还可

以是两个元件内部的连通,可以是无线连接,也可以是有线连接。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本申请中的具体含义。

[0031] 此外,下面所描述的本申请不同实施方式中所涉及的技术特征只要彼此之间未构成冲突就可以相互结合。

[0032] 图1示出了本申请一实施例提供的改善跨导的LDMOS器件结构,从图1中可以看出,该改善跨导的LDMOS器件结构包括:

[0033] 基底层100,该基底层100中形成横向相邻的沟道区110和漂移区120,该沟道区110和漂移区120均从该基底层100的上表面向下延伸。图1中所示的X向为横向,Y向为纵向,该沟道区110和漂移区120在该基底层100中,均沿Y向向下延伸特定深度。可选地,该沟道区110和漂移区120可以为间隔相连,即如图1所示,该沟道区110和漂移区120之间相间隔。

[0034] 栅结构130,该栅结构130沿着该基底层100的表面,跨接在所述沟道区110和漂移区120之间,且该栅结构130的第一端部131与该沟道区110重叠,该栅结构130的第二端部132与该漂移区120重叠。其中,该第一端部131与该沟道区110的第一重叠部分111用于形成LDMOS器件的导电沟道。该栅结构130引出该LDMOS器件的栅极230。

[0035] 在该漂移区120中,远离该沟道区110的一侧形成第一漏端掺杂区141,即如图1所示,该第一漏端掺杂区141形成于该漂移区120的右侧部分,该沟道区110位于该漂移区120的X向左侧的基底层100中。

[0036] 在该第一漏端掺杂区141与栅结构130第二端部132之间的漂移区120位置处形成第一场氧层151,该第二端部132与第一场氧层151之间重叠。本实施例中,该第一场氧层151位于该漂移区120中,且从漂移区120的上表面,沿Y向向下延伸,该第一场氧层151在该漂移区120中纵向延伸的深度,小于该漂移区120在基底层100中纵向延伸的深度。由于,该第二端部132与第一场氧层151之间部分重叠,从而使得该栅结构130的第二端部132通过该第一场氧层151与该第一漏端掺杂区141连接。

[0037] 在靠近该栅结构130第一端部131位置处的沟道区110中,形成源端掺杂区160,可选地,该第一端部131的边缘与该源端掺杂区160的边缘交叠,相交叠的边缘作为该第一端部131与该源端掺杂区160的分界位置。从而使得该源端掺杂区160,与该第一端部131和该沟道区110之间的第一重叠部分111,在该分界位置处横向邻接。本实施例中,该源端掺杂区160还邻接有体端掺杂区170,该体端掺杂区170与该第一重叠部分111分别位于该源端掺杂区160相对的两侧,且该体端掺杂区170也位于沟道区110中。该源端掺杂区160与体端掺杂区170引出LDMOS器件体端和源端相连的源极210。

[0038] 在该漂移区120下方位置处的基底层100中,形成耐压提高区180,该耐压提高区180与该漂移区120纵向接触。

[0039] 相关技术中的漂移区深度较深且掺杂浓度小,从而器件的跨导较小、饱和电流不足,若通过增大漂移区浓度或者减薄漂移区厚度,导致器件的击穿电压不够高,无法满足器件的工作耐压要求。

[0040] 本实施例,通过在漂移区下方位置处的基底层中,形成耐压提高区,使得该耐压提高区与该漂移区在纵向上接触,从而能够使得不改变该漂移区横向长度、保证器件耐压性能的同时,在纵向上减薄该漂移区的深度,耐压提高区,以提高该LDMOS器件的跨导,增大器件的饱和电流。

[0041] 可选地,该漂移区120从基底层100的上表面纵向向下延伸第一深度D1的范围为0.6微米至1.0微米,该耐压提高区180在纵向上延伸第二深度D2的范围为1.4微米至3.0微米。

[0042] 以N型LDMOS为例,即本申请中所述的第一导电类型为N型,第二导电类型为P型。从而图1中所示的基底层100的导电类型为P型,该沟道区110的导电类型为P型,该漂移区120的导电类型为N型,该耐压提高区180的导电类型为P型,该第一漏端掺杂区141的导电类型为N型,该源端掺杂区160的导电类型为N型,该体端掺杂区170的导电类型为P型。其中该漂移区120中的掺杂浓度范围为1e17cm<sup>-3</sup>~1e18cm<sup>-3</sup>,该耐压提高区中的掺杂浓度范围为5e17cm<sup>-3</sup>~5e18cm<sup>-3</sup>。对于P型LDMOS,图1所示的沟道区110、漂移区120、耐压提高区180、第一漏端掺杂区141、源端掺杂区160和体端掺杂区170,与N型LDMOS的导电类型相反。其中,P型和N型为互为相反的导电类型。

[0043] 继续参照图1,该基底层100在纵向上,即图1所示的Y向,可以包括由下至上依次层叠的底层101和外延层102,该底层101和外延层102交界位置处,可以通过掺杂工艺形成埋层103。以N型LDMOS为例,该埋层103的导电类型为N型。上述LDMOS器件位于该外延层102中,即沟道区110、漂移区120和耐压提高区180均位于该外延层102中。

[0044] 该外延层102中还形成高压隔离区190。该高压隔离区190,位于该漂移区120相对于所述沟道区110的另一侧,用于将所述LDMOS器件隔离。从图1中可以看出,该高压隔离区190和沟道区110分别位于漂移区120的X向右侧和左侧。该高压隔离区190在纵向上延伸,且与埋层103在纵向上相接触,使得该高压隔离区190与埋层103半包围该LDMOS器件结构,从而将该LDMOS器件结构与相邻的其他器件隔离。

[0045] 本实施例中,该高压隔离区190的导电类型为N型,可以包括第一N型阱区191和第二N型阱区192,该第一N型阱区191从基底层100的上表面向下延伸至于该埋层103接触相连。该第二N型阱区192,形成于该第一N型阱区191中,且从该第一N型阱区191的上表面向下延伸,且第二N型阱区192在纵向上的深度,小于该第一N型阱区191在纵向上的深度。第二N型阱区192中通过重掺杂N型杂质形成第二漏端掺杂区142,在该第二漏端掺杂区142与第一漏端掺杂区141之间的基底层200中,形成第二场氧层152。从图1可以看出,该第二场氧层152,由第一漏端掺杂区141位置处开始,依次穿过漂移区120、第一N型阱区191和第二N型阱区192,直至与第二漏端掺杂区142接触相连。

[0046] 该第一漏端掺杂区141和第二漏端掺杂区142共同引出该LDMOS器件的漏极230。

[0047] 图2示出了相关技术提供的LDMOS器件,其跨导变化曲线,从该图2中可以看出该LDMOS器件的跨导较小。

[0048] 图3示出了本申请提供的LDMOS器件,其跨导变化曲线,从图3中可以看出,本申请提供的LDMOS器件,其跨导较大,可以解决相关技术中漂移区深度较大,使得器件的跨导受到压缩,从而导致器件饱和电流不足的问题。

[0049] 显然,上述实施例仅仅是为清楚地说明所作的举例,而并非对实施方式的限定。对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动。这里无需也无法对所有的实施方式予以穷举。而由此所引伸出的显而易见的变化或变动仍处于本申请创造的保护范围之中。

图1

图2

图3