### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2011-90756 (P2011-90756A)

(43) 公開日 平成23年5月6日(2011.5.6)

| (51) Int.Cl. |         |           | FI   |       |       | テーマコー        | ド(参考)    |

|--------------|---------|-----------|------|-------|-------|--------------|----------|

| G11C         | 11/4076 | (2006.01) | G11C | 11/34 | 354C  | 5B079        |          |

| нозк         | 5/00    | (2006.01) | нозк | 5/00  | V     | 5MO24        |          |

| G11C         | 11/407  | (2006.01) | G11C | 11/34 | 362T  |              |          |

| G06F         | 1/10    | (2006.01) | GO6F | 1/04  | 330A  |              |          |

| G06F         | 1/12    | (2006.01) | GO6F | 1/04  | 340D  |              |          |

|              |         |           |      | 審査請   | 求 未請求 | 講求項の数 16 O L | (全 19 頁) |

|              |         |           |      |       |       |              |          |

(21) 出願番号 特願2010-25065 (P2010-25065) (22) 出願日 平成22年2月8日 (2010.2.8)

(31) 優先権主張番号 10-2009-0101950

(32) 優先日 平成21年10月26日 (2009.10.26)

(33) 優先権主張国 韓国 (KR)

(71) 出願人 591024111

株式会社ハイニックスセミコンダクター HYNIX SEMICONDUCTOR INC.

大韓民国京畿道利川市夫鉢邑牙美里山13

6 - 1

San 136-1, Ami-Ri, Bu bal-Eup, Ichon-Shi, K youngki-Do, Korea

(74)代理人 110000796

特許業務法人三枝国際特許事務所

(72) 発明者 崔 勳

大韓民国京畿道利川市夫鉢邑牙美里山13

6 - 1

最終頁に続く

## (54) 【発明の名称】半導体装置およびその動作方法

## (57)【要約】

【課題】外部から印加されるクロックをバッファリング して内部クロックを生成する回路を提供すること。

【解決手段】外部クロックを受信し、各々互いに異なる遅延量を反映する複数の同期化クロックを生成するクロック遅延部340と、複数の前記同期化クロックのうち、最も大きい遅延量が反映されたクロックから最も小さい遅延量が反映されたクロックの順にクロックイネーブル信号を各々同期させて同期化クロックイネーブル信号を生成するクロック同期化部300と、前記同期化クロックに対応する内部クロックを生成し、前記同期化クロックイネーブル信号に応じて、その動作がオン・オフ制御される内部クロック生成部320とを備えることを特徴とする。

### 【選択図】図3

#### 【特許請求の範囲】

### 【請求項1】

外部クロックを受信し、各々互いに異なる遅延量を反映する複数の同期化クロックを生成するクロック遅延部と、

複数の前記同期化クロックのうち、最も大きい遅延量が反映されたクロックから最も小さい遅延量が反映されたクロックの順に各前記同期化クロックにクロックイネーブル信号を同期させて同期化クロックイネーブル信号を生成するクロック同期化部と、

前記外部クロックに対応する内部クロックを生成し、前記同期化クロックイネーブル信号に応じて、その動作がオン・オフ制御される内部クロック生成部と、

を備えることを特徴とする半導体装置。

### 【請求項2】

前記クロック遅延部が、

前記外部クロックを受信し、予め設定された第1の遅延量の分だけ遅延して、複数の前記同期化クロックに含まれる第1の同期化クロックを生成する第1の遅延部と、

前記第1の同期化クロックを受信し、予め設定された第2の遅延量の分だけ遅延して、複数の前記同期化クロックに含まれる第2の同期化クロックを生成する第2の遅延部と、

前記第2の同期化クロックを受信し、予め設定された第3の遅延量の分だけ遅延して、 複数の前記同期化クロックに含まれる第3の同期化クロック(前記複数の同期化クロック に含まれる)を生成する第3の遅延部と、

を備えることを特徴とする請求項1に記載の半導体装置。

#### 【請求項3】

前記第1の遅延量~前記第3の遅延量が、同一の遅延量であることを特徴とする請求項 2に記載の半導体装置。

#### 【請求項4】

前記第1の遅延量~前記第3の遅延量が、互いに異なる遅延量であることを特徴とする請求項2に記載の半導体装置。

## 【請求項5】

前記クロック同期化部が、

前記クロックイネーブル信号を受信し、前記第3の同期化クロックを基準として同期させる第1の同期化部と、

前記第1の同期化部の出力信号を受信し、前記第2の同期化クロックを基準として同期させる第2の同期化部と、

前記第2の同期化部の出力信号を受信し、前記第1の同期化クロックを基準として同期させる第3の同期化部と、

を備えることを特徴とする請求項2に記載の半導体装置。

### 【請求項6】

前記内部クロック生成部が、

前記同期化クロックイネーブル信号の活性化期間では前記外部クロックのトグルに対応して前記内部クロックをトグルさせ、

前記同期化クロックイネーブル信号の非活性化期間では前記外部クロックのトグルとは関係なく、前記内部クロックを予め設定された論理レベルに固定することを特徴とする請求項1に記載の半導体装置。

### 【請求項7】

前記クロック遅延部が、

前記外部クロックを受信し、その位相を反転することによって、前記外部クロックに比べて予め設定された遅延量の分だけ遅延した、複数の前記同期化クロックに含まれる第 1 のクロックを生成する第 1 のインバータと、

前記第1のクロックを受信し、その位相を反転することによって、前記第1のクロックに比べて予め設定された遅延量の分だけ遅延した、複数の前記同期化クロックに含まれる第2のクロックを生成する第2のインバータと、

10

20

30

40

前記第2のクロックを受信し、その位相を反転することによって、前記第2のクロックに比べて予め設定された遅延量の分だけ遅延した、複数の前記同期化クロックに含まれる第3のクロックを生成する第3のインバータと、

前記第3のクロックを受信し、その位相を反転することによって、前記第3のクロックに比べて予め設定された遅延量の分だけ遅延した、複数の前記同期化クロックに含まれる第4のクロックを生成する第4のインバータと、

を備えることを特徴とする請求項1に記載の半導体装置。

### 【請求項8】

前記クロック同期化部が、

正制御入力端に印加される前記第3のクロックと負制御入力端に印加される前記第4のクロックとに応じて信号入力端に印加される前記クロックイネーブル信号の信号出力端への伝達を制御する第1の伝達制御ゲートと、

正制御入力端に印加される前記第2のクロックと負制御入力端に印加される前記第3のクロックとに応じて信号入力端に印加される前記第1の伝達制御ゲートの出力信号の信号出力端への伝達を制御する第2の伝達制御ゲートと、

正制御入力端に印加される前記第1のクロックと負制御入力端に印加される前記第2のクロックとに応じて信号入力端に印加される前記第2の伝達制御ゲートの出力信号を前記同期化クロックイネーブル信号として信号出力端に伝達することを制御する第3の伝達制御ゲートと、

を備えることを特徴とする請求項7に記載の半導体装置。

#### 【請求項9】

前記クロック同期化部が、

前記第1の伝達制御ゲート~前記第3の伝達制御ゲートの各々の信号出力端にそれぞれ接続されて出力される信号がフローティングされることを防止する第1のラッチ~第3のラッチをさらに備えることを特徴とする請求項8に記載の半導体装置。

### 【請求項10】

前記内部クロック生成部が、

前記第3の伝達制御ゲートの信号出力端に出力された前記同期化クロックイネーブル信号と前記外部クロックとの論理積演算を行い、前記内部クロックを生成することを特徴とする請求項9に記載の半導体装置。

#### 【請求項11】

外部クロックのトグルより第1期間の分だけ遅延した時点でトグルする第1の同期化クロックを生成するステップと、

前記外部クロックのトグルより前記第1期間よりも長い第2期間の分だけ遅延した時点でトグルする第2の同期化クロックを生成するステップと、

クロックイネーブル信号を前記第 2 の同期化クロックに同期させて第 1 の同期化クロックイネーブル信号を生成するステップと、

前記第1の同期化クロックイネーブル信号を前記第1の同期化クロックに同期させて第2の同期化クロックイネーブル信号を生成するステップと、

前記外部クロックに対応する内部クロックを生成し、前記第2の同期化クロックイネーブル信号に応じて、その動作をオン・オフ制御するステップと、

を含むことを特徴とする半導体装置の動作方法。

### 【請求項12】

前記動作をオン・オフ制御する前記ステップが、

前記第2の同期化クロックイネーブル信号が活性化状態であるときには、前記外部クロックのトグルに対応して前記内部クロックをトグルさせるステップと、

前記第2の同期化クロックイネーブル信号が非活性化状態であるときには、前記外部クロックのトグルとは関係なく、前記内部クロックを予め設定された論理レベルに固定させるステップと、

を含むことを特徴とする請求項11に記載の半導体装置の動作方法。

10

20

30

30

#### 【請求項13】

外部クロックを受信し、バッファリングして内部クロックとして出力し、クロックイネ ーブル信号に応じて、その動作がオン・オフ制御されるクロックバッファリング部と、 前 記 内 部 ク ロ ッ ク に 実 際 出 力 経 路 の 遅 延 時 間 を 反 映 し て 遅 延 複 製 ク ロ ッ ク と し て 出 力 す

る遅延複製モデル部と、

前記内部クロックと前記遅延複製クロックとの位相を比較し、比較結果に対応する時間 の分だけ前記内部クロックを遅延して遅延固定クロックとして出力する遅延固定部と、 を備え、

前記クロックバッファリング部が、

前 記 外 部 ク ロ ッ ク を 受 信 し 、 各 々 互 い に 異 な る 遅 延 量 を 反 映 す る 複 数 の 同 期 化 ク ロ ッ ク を生成するクロック遅延部と、

複数の前記同期化クロックのうち、最も大きい遅延量が反映されたクロックから最も小 さ N 遅 延 量 が 反 映 さ れ た ク ロ ッ ク の 順 に 各 前 記 同 期 化 ク ロ ッ ク に 前 記 ク ロ ッ ク イ ネ ー ブ ル 信号を同期させて同期化クロックイネーブル信号を生成するクロック同期化部と、

前 記 外 部 ク ロ ッ ク に 対 応 す る 前 記 内 部 ク ロ ッ ク を 生 成 し 、 前 記 同 期 化 ク ロ ッ ク イ ネ ー ブ ル信号に応じて、その動作がオン・オフ制御される内部クロック生成部と、

を備えることを特徴とする半導体装置。

#### 【 請 求 項 1 4 】

前記クロック遅延部が、

前 記 外 部 ク ロ ッ ク を 受 信 し 、 予 め 設 定 さ れ た 第 1 の 遅 延 量 の 分 だ け 遅 延 し て 、 複 数 の 前 記 同 期 化 ク ロ ッ ク に 含 ま れ る 第 1 の 同 期 化 ク ロ ッ ク を 生 成 す る 第 1 の 遅 延 部 と 、

前記第1の同期化クロックを受信し、予め設定された第2の遅延量の分だけ遅延して、

複 数 の 前 記 同 期 化 ク ロ ッ ク に 含 ま れ る 第 2 の 同 期 化 ク ロ ッ ク を 生 成 す る 第 2 の 遅 延 部 と 、

前記第2の同期化クロックを受信し、予め設定された第3の遅延量の分だけ遅延して、 複 数 の 前 記 同 期 化 ク ロ ッ ク に 含 ま れ る 第 3 の 同 期 化 ク ロ ッ ク を 生 成 す る 第 3 の 遅 延 部 と 、 を備えることを特徴とする請求項13に記載の半導体装置。

### 【請求項15】

前記クロック同期化部が、

前記クロックイネーブル信号を受信し、前記第3の同期化クロックを基準として同期さ せる第1の同期化部と、

前記第1の同期化部の出力信号を受信し、前記第2の同期化クロックを基準として同期 させる第2の同期化部と、

前記第2の同期化部の出力信号を受信し、前記第1の同期化クロックを基準として同期 させる第3の同期化部と、

を備えることを特徴とする請求項14に記載の半導体装置。

### 【請求項16】

前記内部クロック生成部が、

前 記 同 期 化 ク ロ ッ ク イ ネ ー ブ ル 信 号 の 活 性 化 区 間 で は 前 記 外 部 ク ロ ッ ク の ト グ ル に 対 応 して前記内部クロックをトグルさせ、

前 記 同 期 化 ク ロ ッ ク イ ネ ー ブ ル 信 号 の 非 活 性 化 区 間 で は 前 記 外 部 ク ロ ッ ク の ト グ ル と は 関係なく、前記内部クロックを予め設定された論理レベルに固定することを特徴とする請 求項13に記載の半導体装置。

【発明の詳細な説明】

### 【技術分野】

## [ 0 0 0 1 ]

本発明は、半導体設計技術に関し、特に、外部から印加されるクロックをバッファリン グして内部クロックを生成する回路に関する。

## 【背景技術】

### [00002]

一般に、SDRAM(Synchronous DRAM)をはじめとする同期式半導

10

20

30

40

体装置は、外部クロックをバッファリングして内部クロックを生成した後、生成された内部クロックを用いて予め設定された動作を行う。

[0003]

このとき、外部クロックをバッファリングして内部クロックを生成する過程では、クロックイネーブル信号に応じてバッファリング動作がオン・オフ制御されなければならないが、これは、ほとんどの半導体装置の場合、消費する電流を低減することが目的で、外部クロックに対応して内部クロックを生成する動作モード、例えば、パワーダウンモード(power down mode)を支援するためである。

[0004]

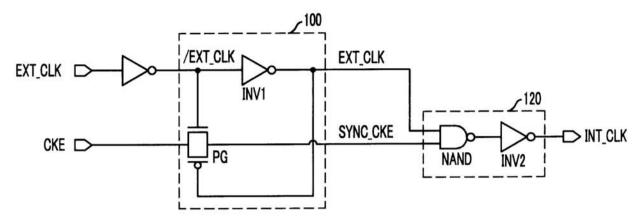

図 1 は、従来技術により外部クロックをバッファリングして内部クロックを生成する回路の構成を詳細に示した回路図である。

[0005]

図1に示すように、従来技術による外部クロックをバッファリングして内部クロックを生成する回路は、外部クロックEXT\_\_CLKに応じてクロックイネーブル信号CKEを同期させる同期化部100と、外部クロックEXT\_\_CLKに対応する内部クロックINT\_\_CLKを生成し、同期化部100を介して出力される同期したクロックイネーブル信号SYNC\_\_CKEに応じて、その動作がオン・オフ制御される内部クロック生成部120とを備える。

[0006]

ここで、同期化部100は、外部クロックEXT\_CLKを負入力端に受信し、外部クロックEXT\_CLKの位相を反転したクロック/EXT\_CLKを正入力端に受信して、信号入力端に印加されるクロックイネーブル信号CKEが信号出力端へSYNC\_CKEとして伝送することを制御するパスゲートPG、およびインバータINV1を備える。

[0007]

そして、内部クロック生成部120は、外部クロックEXT\_CLKを第1の入力端に受信し、同期化部100を介して出力される同期したクロックイネーブル信号SYNC\_ CKEを第2の入力端に受信して論理積演算を行い、内部クロックINT\_CLKとして 出力するNANDゲートNAND、およびインバータINV2を備える。

[ 0 0 0 8 ]

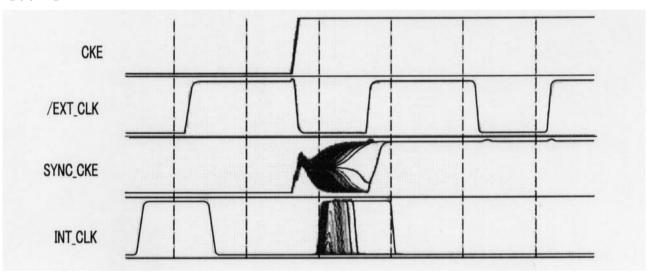

図 2 は、図 1 に示された従来技術による、外部クロックをバッファリングして内部クロックを生成する回路の動作を説明するためのタイミング図である。

[0009]

図 2 に示すように、外部クロック E X T \_ C L K は、所定の周期を有する状態でトグル(toggling)しており、クロックイネーブル信号 C K E は、ロジック「ロー」(Low)の非活性化状態から瞬時的に論理レベルが遷移してロジック「ハイ」(High)の活性化状態になることが分かる。

[0010]

ところが、クロックイネーブル信号 CKE がロジック「ロー」からロジック「ハイ」に遷移する時点が外部クロック EXT\_CLKのエッジ(図2では、立ち下りエッジが示されているが、立ち上りエッジでもあり得る)の近くにある場合、同期化部 100を介して出力される同期したクロックイネーブル信号 SYNC\_CKEには、図2に示されたように、グリッチ(glitch)が発生するという問題がある。

[0011]

このようにグリッチが発生した、同期したクロックイネーブル信号SYNC\_CKEをそのまま用いて内部クロック生成部120を動作させる場合、図2に示されたように、生成された内部クロックINT\_CLKにもグリッチが発生する。

[0012]

上述した問題は、外部クロックEXT\_CLKの周波数が高周波数になればなるほど、 半導体装置の全体動作に大きな影響を及ぼす恐れがある。

【発明の概要】

40

10

20

30

#### 【発明が解決しようとする課題】

### [ 0 0 1 3 ]

本発明は、上記のような従来技術の問題を解決するために提案されたものであって、その目的は、外部クロックをバッファリングして内部クロックを生成するとき、外部クロックとは非同期のクロックイネーブル信号を用いて、バッファリング動作をオン・オフ制御する過程でグリッチが発生することを防止することができる半導体装置のクロックバッファリング回路を提供することにある。

## 【課題を解決するための手段】

## [0014]

そこで、上記の目的を達成するための本発明に係る半導体装置は、外部クロックを受信し、各々互いに異なる遅延量を反映して複数の同期化クロックを生成するクロック遅延部と、複数の前記同期化クロックのうち、最も大きい遅延量が反映されたクロックから最も小さい遅延量が反映されたクロックの順に前記同期化クロックにクロックイネーブル信号を同期させて同期化クロックイネーブル信号を生成するクロック同期化部と、前記外部クロックに対応する内部クロックを生成し、前記同期化クロックイネーブル信号に応じて、その動作がオン・オフ制御される内部クロック生成部とを備えることを特徴とする。

### [0015]

また、上記の目的を達成するための本発明に係る半導体装置の動作方法は、外部クロックのトグルより第1期間の分だけ遅延した時点でトグルする第1の同期化クロックを生成するステップと、前記外部クロックのトグルより前記第1期間よりも長い第2期間の分だけ遅延した時点でトグルする第2の同期化クロックを生成するステップと、クロックイネーブル信号を前記第2の同期化クロックに同期させて第1の同期化クロックイネーブル信号を前記第1の同期化クロックイネーブル信号を生成するステップと、前記外部クロックに対応する内部クロックを生成し、前記第2の同期化クロックイネーブル信号に応じて、その動作をオン・オフ制御するステップとを含むことを特徴とする。

### [0016]

## 【発明の効果】

#### [0017]

本発明は、外部クロックをバッファリングして内部クロックを生成するとき、外部クロックとは非同期のクロックイネーブル信号を用いてバッファリング動作をオン・オフ制御する過程で外部クロックを段階的に遅延させた複数の同期化クロックに、クロックイネーブル信号を設定された順にそれぞれ同期させることにより、グリッチが発生することを防止できるという効果がある。

### 【図面の簡単な説明】

#### [ 0 0 1 8 ]

【図1】従来技術による外部クロックをバッファリングして内部クロックを生成する回路

10

20

30

40

の構成を詳細に示した回路図である。

【図2】図1に示された従来技術による外部クロックをバッファリングして内部クロックを生成する回路の動作を説明するためのタイミング図である。

【図3】本発明の実施形態による、外部クロックをバッファリングして内部クロックを生成する回路の構成を詳細に示した回路図である。

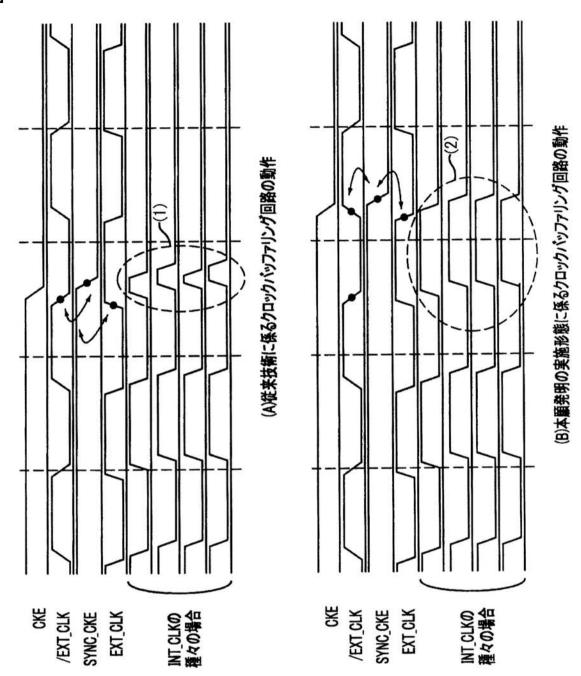

【図4】図1に示された従来技術に係るクロックバッファリング回路の動作と図3に示された本発明の実施形態に係るクロックバッファリング回路の動作とを比較して示したタイミング図である。

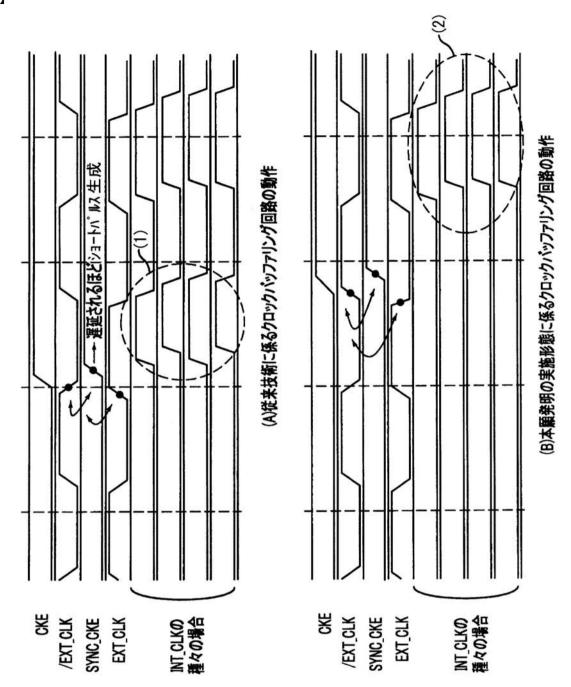

【図 5 】図 1 に示された従来技術に係るクロックバッファリング回路の動作と図 3 に示された本発明の実施形態に係るクロックバッファリング回路の動作とを比較して示したタイミング図である。

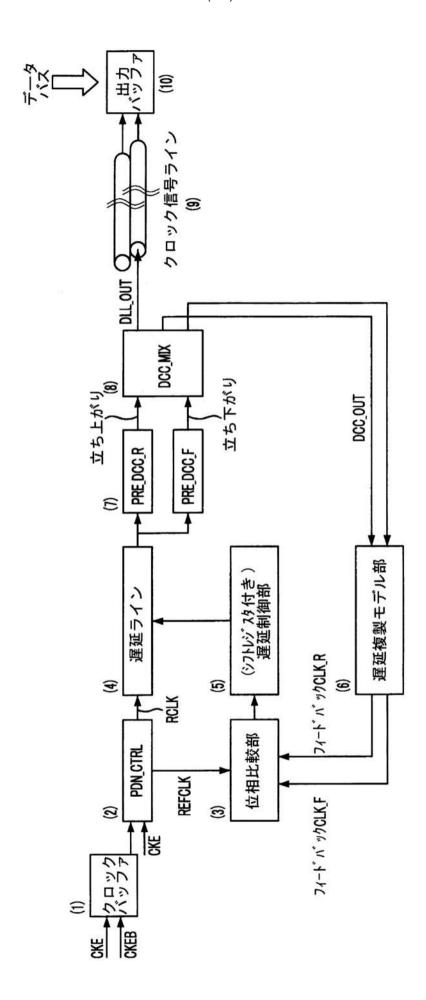

【図 6 】本発明の実施形態に係るクロックバッファリング回路が適用された遅延固定ループ回路の構成を示したブロック図である。

【発明を実施するための形態】

### [0019]

以下、添付した図面を参照して、本発明の好ましい実施形態を説明する。しかし、本発明は、以下で開示される実施形態に限定されるものではなく、互いに異なる様々な形態で構成されることができる。本実施形態は、単に、本発明の開示が完全となり、当技術分野で通常の知識を有する者に本発明の範疇を完全に知らせるために提供されるものである。

## [0020]

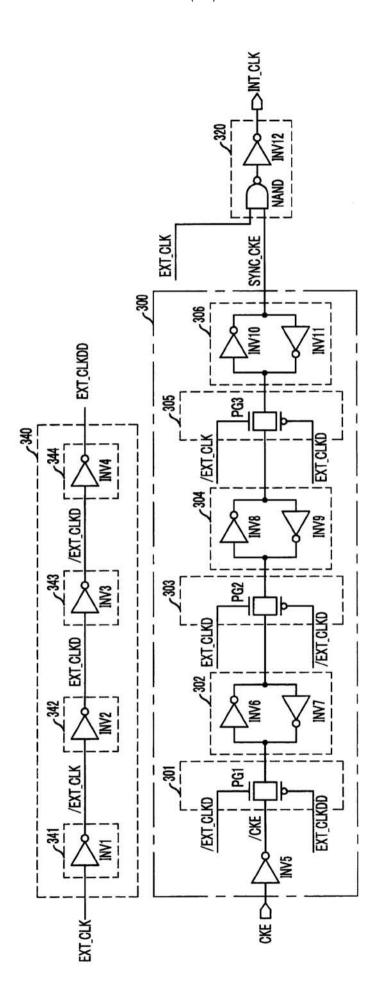

図 3 は、本発明の実施形態による、外部クロックをバッファリングして内部クロックを 生成する回路を詳細に示した回路図である。

### [0021]

図3に示すように、外部クロックをバッファリングして内部クロックを生成する回路は、外部クロックEXT\_\_CLKを受信し、互いに異なる遅延量を反映する複数の同期化クロック/EXT\_\_CLKD、EXT\_\_CLKDDを生成するクロック遅延部340と、

複数の同期化クロック/EXT\_CLK、EXT\_CLKD、/EXT\_CLKD、EXTCLKDDのうち、最も大きい遅延量が反映されたクロックEXT\_CLKDDから最も小さい遅延量が反映されたクロック/EXT\_CLKの順に、それらの同期化クロックにクロックイネーブル信号CKEを各々同期させて同期化クロックイネーブル信号SYNC\_CKEを生成するクロック同期化部300と、

外部クロックEXT\_CLKに対応する内部クロックINT\_CLKを生成し、同期化クロックイネーブル信号SYNC\_CKEに応じて、その動作がオン・オフ制御される内部クロック生成部320と

を備える。

#### [0022]

ここで、クロック遅延部340は、

外部クロックEXT\_CLKを受信し、予め設定された第1の遅延量の分だけ遅延して、 第1の同期化クロック/EXT\_CLK、EXT\_CLKD(複数の同期化クロック/E XT\_CLK、EXT\_CLKD、/EXT\_CLKD、EXTCLKDDに含まれる) を生成する第1の遅延部341、342と、

第1の同期化クロック/EXT\_CLK、EXT\_CLKDを受信し、予め設定された第 2の遅延量の分だけ遅延して、第2の同期化クロックEXT\_CLKD、/EXT\_CL KD(複数の同期化クロック/EXT\_CLK、EXT\_CLKD、/EXT\_CLKD 、EXTCLKDDに含まれる)を生成する第2の遅延部342、343と、

第 2 の同期化クロック E X T \_\_ C L K D、 / E X T \_\_ C L K Dを受信し、予め設定された第 3 の遅延量の分だけ遅延して、第 3 の同期化クロック / E X T \_\_ C L K D、 E X T \_\_ C L K D、 / E X T \_\_ C L K D、 / E X T \_\_ C L K D、 / E X T \_\_ C L K D、 / E X T \_\_ C L K D、 / E X T \_\_ C L K D、 / E X T \_\_ C L K D、 / E X T \_\_ C L K D D に含まれる)を生成する第 3 の遅延部 3 4 3 、 3 4 4 と

10

20

30

40

を備える。

### [0023]

参考までに、図3のクロック遅延部340に備えられる第1の遅延部341、342、第2の遅延部342、343、および第3の遅延部343、344は、内部に含まれた構成要素INV2、INV3が互いに重複していることが分かるが、これは、本発明の実施形態に係るクロック遅延部340で複数のインバータINV1、INV2、INV3、INV4を用いてクロックを遅延させるという回路的な特徴のためにそのように具現されただけであり、図3に示された構成と異なる方式で具現される回路では、もちろん内部に含まれた構成要素が互いに重複しないように構成することもできる。

#### [0024]

すなわち、図3に示されたようなクロック遅延部340は、1つの実施形態であり、図3に示された構成と異なる形態で構成される回路である場合も本願発明の範疇に含まれる

## [0025]

また、図3に示されたようなクロック遅延部340は、次のとおりにさらに具体的に構成要素を分けることができる。

### [0026]

クロック遅延部340は、

外 部 ク ロ ッ ク E X T \_\_ C L K を 受 信 し 、 そ の 位 相 を 反 転 す る こ と に よ っ て 外 部 ク ロ ッ ク E X T \_\_ C L K に比べて予め設定された遅延量の分だけ遅延した第1のクロック/EXT\_ CLK(複数の同期化クロック/EXT CLK、EXT CLKD、/EXT CLK D、EXTCLKDDに含まれる)を生成する第1のインバータINV1と、 第 1 のクロック / EXT \_ CLKを受信し、その位相を反転することによって第 1 のクロ ック/EXT\_\_ C LKに比べて予め設定された遅延量の分だけ遅延した第2のクロックE X T \_\_ C L K D ( 複数の同期化クロック / E X T \_\_ C L K 、 E X T \_\_ C L K D 、 / E X T \_\_ CLKD、EXTCLKDDに含まれる)を生成する第2のインバータINV2と、 第 2 のクロックEXT \_\_ CLKDを受信し、その位相を反転することによって第 2 のクロ ックEXT \_\_ CLKDに比べて予め設定された遅延量の分だけ遅延した第3のクロック / EXT\_\_CLKD(複数の同期化クロック/EXT\_\_CLK、EXT\_\_CLKD、/EX T\_CLKD、EXTCLKDDに含まれる)を生成する第3のインバータINV3と、 第 3 のクロック / EXT \_\_ CLKDを受信し、その位相を反転することによって第 3 のク ロック / E X T \_\_ C L K D に比べて予め設定された遅延量の分だけ遅延した第 4 のクロッ ク E X T \_\_ C L K D D (複数の同期化クロック / E X T \_\_ C L K 、 E X T \_\_ C L K D 、 / E X T \_\_ C L K D 、 E X T C L K D D に含まれる)を生成する第 4 のインバータ I N V 4 とを備える。

### [0027]

そして、図3に示されたようなクロック遅延部340では、第1の遅延部341、342に入力されるクロックEXT\_\_CLK、/EXT\_\_CLKを遅延させて/EXT\_\_CLK、EXT\_\_CLKを遅延させて/EXT\_\_CLK、EXT\_\_CLKを遅延させて/EXT\_\_CLKの力されるクロック/EXT\_\_CLK、EXT\_\_CLK Dを遅延させてEXT\_\_CLK D、/EXT\_\_CLK Dを出力する第2の遅延量と、第3の遅延部343、344に入力されるクロックEXT\_\_CLK D、/EXT\_\_CLK Dを遅延させて/EXT\_\_CLK D、EXT\_\_CLK D Dを出力する第3の遅延量とは、互いに同一の遅延量を有する状態になる。

# [ 0 0 2 8 ]

すなわち、第1のインバータINV1~第4のインバータINV4は、全て同じサイズを有し、入力されるクロックを全て同一の遅延量の分だけ遅延させて出力する。

### [ 0 0 2 9 ]

しかし、図3に示されたものと異に構成された回路では、第1の遅延量~第3の遅延量が各々互いに異なる遅延量を有するか、または、一部は同一の遅延量を有し、残りは異なる遅延量を有するように構成されることもできる。

10

20

30

40

#### [0030]

そして、クロック同期化部300は、クロックイネーブル信号 C K E を受信し、第3の同期化クロック / E X T \_ C L K D 、 E X T \_ C L K D D を基準として同期させる第1の同期化部301と、該第1の同期化部301の出力信号を受信し、第2の同期化クロック E X T \_ C L K D を基準として同期させる第2の同期化部303と、第2の同期化部303の出力信号を受信し、第1の同期化クロック / E X T \_ C L K D を基準として同期させる第3の同期化部305とを備える。

### [0031]

参考までに、図3に示されたクロック同期化部300には、クロック同期化動作を行う複数の伝達ゲートPG1、PG2、PG3だけでなく、クロックの論理レベルがフローティング(f1oating)されることを防止する複数のインバータINV5、INV9、INV10、INV11も備えられている。これらのインバータを第1の同期化部~第3の同期化部301、303、305で具現した理のは、本発明の実施形態に係るクロック同期化部300で最も重要な動作は、入力されるしい、クイネーブル信号CKEを複数の同期化クロック/EXT\_CLKDDに同期させて出力し、複数の同期化クロック/EXT\_CLKDDに同期でせて出力し、複数の同期化クロック/EXT\_CLKDDのうち順をスT\_CLKDD / EXT\_CLKDD E X T \_CLKDDのの側下であるため、これを最もにには、クロックイネーブル信号CKEを各々同期させるという動作であるため、これを最も単純化して具現しただけである。図3に示された回路に忠実に表現してみれば、次のように説明されることができる。

## [0032]

クロック同期化部300は、正制御入力端に印加される第3のクロック/EXT\_CLKDと負制御入力端に印加される第4のクロックEXT\_CLKDDとに応じて信号入力端に印加される位相が反転されたクロックイネーブル信号/CKEの信号出力端への伝達を制御する第1の伝達制御ゲートPG1と、正制御入力端に印加される第2のクロックEXT\_CLKDとに応じて信号入力端に印加される第1の伝達制御ゲートPG1の出力信号の信号出力端への伝達を制御する第2の伝達制御ゲートPG2と、正制御入力端に印加される第1のクロック/EXT\_CLKDとに応じて信号入力端に印加される第2の伝達制御ゲートPG2の出力信号を同期化クロックイネーブル信号SYNC\_CKEとして信号出力端に伝達することを制御する第3の伝達制御ゲートPG3とを備える。

## [0033]

また、第1の伝達制御ゲートPG1、第2の伝達制御ゲートPG2、および第3の伝達制御ゲートPG3の信号出力端に各々接続されて出力される信号がフローティングされることを防止する第1のラッチ302、第2のラッチ304、および第3のラッチ306がさらに備えられている。

## [0034]

そして、内部クロック生成部320は、同期化クロックイネーブル信号SYNC\_CKEの活性化期間では外部クロックEXT\_CLKのトグルに対応して内部クロックINT\_CLKをトグルさせ、同期化クロックイネーブル信号SYNC\_CKEの非活性化期間では外部クロックEXT\_CLKのトグルと関係なく、内部クロックINT\_CLKを予め設定された論理レベルに固定させる動作を行う。

## [0035]

したがって、内部クロック生成部320は、第3の伝達制御ゲートPG3の信号出力端に出力された同期化クロックイネーブル信号SYNC\_CKEと外部クロックEXT\_CLKとの否定論理積の演算を行って内部クロックINT\_CLKを生成するNANDゲートNAND、およびインバータINV12を備える。

10

20

30

40

10

20

30

40

50

[0036]

図 4 は、図 1 に示された従来技術に係るクロックバッファリング回路の動作と図 3 に示された本発明の実施形態に係るクロックバッファリング回路の動作とを比較して示したタイミング図である。

[0037]

図4に示すように、従来技術に係るクロックバッファリング回路の動作(A)と本発明の実施形態に係るクロックバッファリング回路の動作(B)とが別々に図示されており、クロックイネーブル信号CKEがロジック「ハイ」の活性化状態からロジック「ロー」の非活性化状態に遷移する過程でのバッファリング動作を示していることが分かる。

[0038]

まず、従来技術に係るクロックバッファリング回路の動作 A を説明すれば、次のとおりである。

(A)図4に示されたように、外部クロックEXT\_CLKがロジック「ロー」の非活性化状態からロジック「ハイ」の活性化状態に遷移(立ち上りエッジ)する時点とほとんど同時に、クロックイネーブル信号CKEがロジック「ハイ」の活性化状態からロジック「ロー」の非活性化状態に遷移(立ち下りエッジ)するような現象が発生するとき、クロックイネーブル信号CKEを外部クロックEXT\_CLKの位相を反転したクロック/EXT\_CLKに同期させて同期したクロックイネーブル信号SYNC\_CKEを生成する過程で発生するグリッチと、同期したクロックイネーブル信号SYNC\_CKEと外部クロックEXT\_CLKとの間に論理積演算を行い、内部クロックINT\_CLKの正確なる過程で発生するグリッチとによって、生成された内部クロックINT\_CLKの正確な計理レベルが分からない問題点(図4(A)の(1)で示した波線部分参照)を生じることが分かる。

[0039]

すなわち、グリッチによって外部クロックEXT\_CLKがロジック「ロー」の非活性化状態からロジック「ハイ」の活性化状態に遷移(立ち上りエッジ)される時点よりも、同期したクロックイネーブル信号SYNC\_CKEがロジック「ハイ」の活性化状態からロジック「ロー」の非活性化状態に遷移(立ち下りエッジ)される時点が後に位置(どのくらい後であるか予め知ることができない)し、このため、外部クロックEXT\_CLK に対応して内部クロックINT\_CLKがロジック「ロー」の非活性化状態からロジック「ハイ」の活性化状態に遷移(立ち上りエッジ)した後、まもなく(どのくらい後であるか予め知ることができない)ロジック「ハイ」の活性化状態からロジック「ロー」の非活性化状態に遷移(立ち下りエッジ)し、内部クロックINT\_CLKが正常なトグル期間を維持できなくなる可能性がある。

[0040]

このように、従来技術に係るクロックバッファリング回路では、外部クロックEXT\_ CLKの論理レベルが遷移する時点とクロックイネーブル信号CKEがトグルする時点とが互いに近接すると、内部クロックINT\_CLKが正常なクロック信号として認識されないパルスとして発生する可能性があり、このため、半導体装置が全体的に誤動作する恐れがある。

[0041]

それに対し、本発明の実施形態に係るクロックバッファリング回路の動作( B )を説明 すれば、次のとおりである。

(B)図4に示されたように、外部クロックEXT\_CLKがロジック「ハイ」の活性化状態からロジック「ロー」の非活性化状態に遷移(立ち下りエッジ)する時点とほとんど同時に、クロックイネーブル信号CKEがロジック「ハイ」の活性化状態からロジック「ロー」の非活性化状態に遷移するような現象が発生しても、クロックイネーブル信号CKEを複数の同期化クロック/EXT\_CLK、EXT\_CLKD、/EXT\_CLKD、 EXTCLKDDに同期させて同期したクロックイネーブル信号SYNC\_CKEを生成する過程で各同期化クロック/EXT\_CLK、EXT\_CLKD、/EXT\_CLKD

10

20

30

40

50

、 E X T C L K D D にクロックイネーブル信号 C K E が同期するため、同期する過程でグリッチがほとんど発生しなくなる。

## [0042]

同時に、複数の同期化クロック/EXT\_CLK、EXT\_CLKD、/EXT\_CLKD、/EXT\_CLKD、/EXT\_CLKD、/EXT\_CLKDDのうち、最も大きい遅延量が反映されたクロックから最も小さい遅延量が反映されたクロックの順序(EXT\_CLKDD /EXT\_CLKD EXT\_CLKD /EXT\_CLKD 「EXT」 C LKD 「E X T 」 C LKDO 「E X T 」 C LKの位相を反転したクロック/EXT\_ C LKがロジック「ロー」の非活性化状態に遷移(立ち上りエッジ)する動作が発生した後、同期したクロックイネーブル信号SYNC\_ C KEがロジック「ハイ」の活性化状態からロジック「ロー」の非活性化状態に遷移(立ち下りエッジ)する動作が発生し、これにより、外部クロックEXT\_ C LKと同期したクロックイネーブル信号SYNC\_ C KEとの論理積演算を行い、内部クロックINT\_ C LKを生成する過程で内部クロックINT\_ C LKは、常に正確な論理レベルを有する状態(図4の(2)で示した破線部分参照)になることが分かる。

### [0043]

すなわち、本願発明の実施形態に係るクロックバッファリング回路では、常に外部クロックEXT\_\_CLKがロジック「ハイ」の活性化状態からロジック「ロー」の非活性化状態に遷移(立ち下りエッジ)された後、同期したクロックイネーブル信号SYNC\_\_CKEがロジック「ハイ」の活性化状態からロジック「ロー」の非活性化状態に遷移(立ち下りエッジ)するので、それに対応して発生する内部クロックINT\_\_CLKが常に正常なトグル期間を有することができるようになる。

#### [0044]

このように、本発明の実施形態に係るクロックバッファリング回路では、外部クロックEXT\_CLKの論理レベルが遷移する時点とクロックイネーブル信号CKEがトグルする時点とが互いに近接しても、内部クロックINT\_CLKが常に正常なトグル期間を有することができ、これにより、半導体装置が誤動作することを防止することができる。

### [0045]

図 5 は、図 1 に示された従来技術に係るクロックバッファリング回路の動作と図 3 に示された本発明の実施形態に係るクロックバッファリング回路の動作とを比較して示したタイミング図である。

#### [0046]

図 5 に示すように、従来技術に係るクロックバッファリング回路の動作(A)と本発明の実施形態に係るクロックバッファリング回路の動作(B)とが別々に図示されており、クロックイネーブル信号 CKEがロジック「ロー」の非活性化状態からロジック「ハイ」の活性化状態に遷移する過程でのバッファリング動作を示していることが分かる。

### [0047]

まず、従来技術に係るクロックバッファリング回路の動作Aを説明すれば、次のとおりである。

( A ) 図 5 に示されたように、外部クロック E X T \_ C L K がロジック「ロー」の非活性化状態からロジック「ハイ」の活性化状態に遷移(立ち上りエッジ)する時点とほとんど同時に、クロックイネーブル信号 C K E がロジック「ロー」の非活性化状態からロジック「ハイ」の活性化状態に遷移(立ち上りエッジ)する現象が発生するとき、クロックイネーブル信号 C K E を外部クロック E X T \_ C L K の位相を反転したクロック / E X T \_ C L K に同期させて同期したクロックイネーブル信号 S Y N C \_ C K E を生成する過程で発生するグリッチと、同期したクロックイネーブル信号 S Y N C \_ C K E と外部クロック E X T \_ C L K との否定論理積の演算を行い、内部クロック I N T \_ C L K を発生させる過程で発生するグリッチとによって、生成された内部クロック I N T \_ C L K が、正常な活性化期間を有することができないという問題点(図 5 の(1)で示した破線部分参照)を

10

20

30

40

50

生じることが分かる。

[0048]

すなわち、グリッチによって外部クロックEXT\_CLKがロジック「ロー」の非活性化状態からロジック「ハイ」の活性化状態に遷移(立ち上りエッジ)される時点よりも、同期したクロックイネーブル信号SYNC\_CKEがロジック「ロー」の非活性化状態からロジック「ハイ」の活性化状態に遷移(立ち上りエッジ)される時点が、後に位置(どのくらい後であるか予め知ることができない)し、このため、外部クロックEXT\_CLKに対応して内部クロックINT\_CLKがロジック「ロー」の非活性化状態からロジック「ハイ」の活性化状態に遷移(立ち上りエッジ)する時点が遅延(どのくらい後であるか予め知ることができない)され、内部クロックINT\_CLKが正常なトグル期間を維持できなくなる可能性がある。

[0049]

このように、従来技術に係るクロックバッファリング回路では、外部クロックEXT\_ CLKの論理レベルが遷移する時点とクロックイネーブル信号CKEがトグルする時点とが互いに近接すると、内部クロックINT\_CLKが正常なクロック信号として認識されないパルスとして発生する可能性があり、このため、半導体装置が全体的に誤動作する恐れがある。

[0050]

それに対し、本発明の実施形態に係るクロックバッファリング回路の動作 B を説明すれば、次のとおりである。

(B)図5に示されたように、外部クロックEXT\_CLKがロジック「ハイ」の活性化状態からロジック「ロー」の非活性化状態に遷移(立ち下りエッジ)する時点とほとんど同時に、クロックイネーブル信号CKEがロジック「ロー」の非活性化状態からロジック「ハイ」の活性化状態に遷移(立ち上りエッジ)するような現象が発生しても、クロックイネーブル信号CKEを複数の同期化クロック/EXT\_CLK、EXT\_CLKD、/EXT\_CLKD、EXTCLKDDに同期させて同期したクロックイネーブル信号SYNC\_CKEを生成する過程で各同期化クロック/EXT\_CLK、EXT\_CLKD、/EXT\_CLKD、EXTCLKDDにクロックイネーブル信号CKEが同期するため、同期する過程でグリッチがほとんど発生しなくなる。

[0051]

同時に、複数の同期化クロック/EXT\_CLK、EXT\_CLKD、/EXT\_CLKD、/EXT\_CLKD、/EXT\_CLKDL。 / EXT\_CLKDDのうち、最も大きい遅延量が反映されたクロックから最も小さい遅延量が反映されたクロックの順序(EXT\_CLKDD / EXT\_CLKD E X T \_ C L K D D / E X T \_ C L K D E E X T \_ C L K D D / E X T \_ C L K D D / E X T \_ C L K D D / E X T \_ C L K D D / E X T \_ C L K D D / E X T \_ C L K D D / E X T \_ C L K D D / E X T \_ C L K がロジック「即立の非活性化状態に置移(立ち上りエッジ)する動作が発生した後、同期によりによりに対したクロックイネーブル信号 S Y N C \_ C K E とのが分しまる T \_ C L K と同期化したクロックイネーブル信号 S Y N C \_ C K E との論理積演算を行い、内部クロック I N T \_ C L K を生成する過程で内部クロック I N T \_ C L K に正確な論理レベルを有する状態(図 5 の(2)で示した破線部分参照)になることが分かる。

[ 0 0 5 2 ]

すなわち、本願発明の実施形態に係るクロックバッファリング回路では、常に外部クロックEXT\_\_CLKがロジック「ハイ」の活性化状態からロジック「ロー」の非活性化状態に遷移(立ち下りエッジ)した後、同期したクロックイネーブル信号SYNC\_\_CKEがロジック「ロー」の非活性化状態からロジック「ハイ」の活性化状態に遷移(立ち上りエッジ)するので、それに対応して発生する内部クロックINT\_\_CLKが常に正常なトグル期間を有することができるようになる。

#### [ 0 0 5 3 ]

このように、本発明の実施形態に係るクロックバッファリング回路では、外部クロック EXT CLKの論理レベルが遷移する時点とクロックイネーブル信号CKEがトグルす る時点とが互いに近接しても、内部クロックINT\_CLKが常に正常なトグル期間を有 することができ、これにより、半導体装置が誤動作することが防止できる。

#### [0054]

以上で説明したように、本発明の実施形態を適用すれば、外部クロックEXT CLK をバッファリングして内部クロックINT\_CLKを生成するとき、外部クロックEXT \_ CLKとは非同期のクロックイネーブル信号CKEを用いてバッファリング動作をオン ・オフ制御する過程で外部クロックEXT\_CLKを段階的に遅延させた複数の同期化ク ロック/EXT\_CLK、EXT\_CLKD、/EXT\_CLKD、EXTCLKDDに クロックイネーブル信号を設定された順序(最も大きい遅延量が反映されたクロックから 最も小さい遅延量が反映されたクロックの順序(EXTCLKDD /EXT\_CLKD EXT\_CLKD /EXT\_CLK))でそれぞれ同期させることにより、グリッチ が発生することが防止でき、これにより、クロックイネーブル信号CKEの論理レベルが 遷移する時点と関係なく、外部クロックEXT\_CLKのトグル期間に正確に対応するト グル期間を有する内部クロックINT CLKを発生させることが可能である。

#### [0055]

参考までに、前述した本発明の実施形態に係るクロックバッファリング回路は、単に外 部クロックをバッファリングして内部クロックを生成する動作を制御するための回路のみ に適用されるものではなく、図6に示すような遅延固定ループ回路でパワーダウンモード 進入を制御するための構成要素PDN CTRL(2)に適用することもできる。

#### [0056]

すなわち、本発明の実施形態に係るクロックバッファリング回路は、所定の周期でトグ ルするクロックを伝達する過程で特定の制御信号(クロックの周期に同期していない信号 である)に対応して、その伝達をオン・オフ制御する回路であれば、どんな回路にも適用 することができる。

# [0057]

以上で説明した本発明は、前述した実施形態及び添付図面によって限定されるものでは なく、本発明の技術的思想を逸脱しない範囲内で様々な置換、変形、及び変更が可能であ ることが本発明の属する技術分野における通常の知識を有する者にとって明白であろう。

## [0058]

例えば、前述した実施形態で例示した論理ゲートおよびトランジスタは、入力される信 号の極性に応じて、その位置および種類が異なるように実現されるべきであろう。

### 【符号の説明】

## [0059]

100、300 クロック同期化部

3 0 1 、 3 0 3 、 3 0 5 第 1 ~ 第 3 の 同期 化部

302、304、306 第1~第3のラッチ

クロック遅延部 3 4 0

1 2 0 、 3 2 0 内部クロック生成部 10

20

30

【図1】

【図2】

【図4】

【図5】

【図6】

# フロントページの続き

# (72)発明者 羅 光振

大韓民国京畿道利川市夫鉢邑牙美里山136-1

Fターム(参考) 5B079 AA07 BC03 CC14 DD05

5M024 AA36 AA40 BB27 DD82 JJ03 JJ32 JJ38 KK18 PP01 PP02 PP07