(19) **日本国特許庁(JP)**

(51) Int. Cl.

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4258411号 (P4258411)

(45) 発行日 平成21年4月30日 (2009. 4.30)

(24) 登録日 平成21年2月20日(2009.2.20)

HO1L 23/48 (2006.01)

HO1L 23/48

FL

J

請求項の数 7 (全 17 頁)

(21) 出願番号 特願2004-89165 (P2004-89165) (22) 出願日 平成16年3月25日 (2004.3.25) (65) 公開番号 特開2005-277150 (P2005-277150A)

(65) **公開番号** 特 (43) **公開日** 平

審查請求日

平成17年10月6日 (2005.10.6) 平成18年5月15日 (2006.5.15)

(73) 特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

|(74)代理人 100100022

弁理士 伊藤 洋二

|(74)代理人 100108198

弁理士 三浦 高広

(74)代理人 100111578

弁理士 水野 史博

(72) 発明者 平野 尚彦

愛知県刈谷市昭和町1丁目1番地 株式会

社デンソー内

審査官 宮本 靖史

最終頁に続く

## (54) 【発明の名称】半導体装置

### (57)【特許請求の範囲】

## 【請求項1】

半導体素子(10)と、

前記半導体素子(10)の一面側に設けられ、電極と放熱体とを兼ねる第1の金属体(20)と、

前記半導体素子(10)の他面側に設けられ、電極と放熱体とを兼ねる第2の金属体(30)と、

前記半導体素子(10)と外部とを電気的に接続するための端子(60)と、

前記半導体素子(10)、前記第1の金属体(20)、前記第2の金属体(30)および前記端子(60)の一部を包み込むように封止するモールド樹脂(80)とを備える半導体装置において、

前記半導体素子(10)としてゲート酸化膜デバイス(10)が用いられており、

前記ゲート酸化膜デバイス(10)は、2個以上設けられており、

個々の前記ゲート酸化膜デバイス(10)は、複数種類の信号用パッド(10a、10 b、10c、10d、10e)を有するとともに、1個の前記ゲート酸化膜デバイス(1 0)について同種の前記信号用パッド(10a~10e)が2個以上設けられており、

前記ゲート酸化膜デバイス(10)の間にて、同種の前記信号用パッド(10a、10c)同士が電気的に接続されており、

個々の前記ゲート酸化膜デバイス(10)は、前記信号用パッドとして2個以上のゲートセンス用パッド(10c)および2個以上のケルビンセンス用パッド(10a)を備え

20

#### ており、

前記ゲート酸化膜デバイス(10)の間にて、前記ゲートセンス用パッド(10c)同 士および前記ケルビンセンス用パッド(10a)同士が電気的に接続されていることを特 徴とする半導体装置。

### 【請求項2】

個々の前記ゲート酸化膜デバイス(10)は矩形板状をなすものであり、

前記複数種類の信号用パッド(10a~10e)が配列されてなるパッドの配列ユニット(12)が、個々の前記ゲート酸化膜デバイス(10)における少なくとも2辺以上に設けられていることを特徴とする請求項1に記載の半導体装置。

#### 【請求項3】

前記パッドの配列ユニット(12)は、個々の前記ゲート酸化膜デバイス(10)における少なくとも3辺以上に設けられていることを特徴とする請求項1に記載の半導体装置

## 【請求項4】

個々の前記ゲート酸化膜デバイス(10)において、前記パッドの配列ユニット(12)が設けられる辺は、少なくとも互いに対向する2辺であることを特徴とする請求項2または3に記載の半導体装置。

### 【請求項5】

前記2個以上の前記ゲート酸化膜デバイスは、隣り合って配置されている2個以上のIGBT素子(10)であることを特徴とする請求項1ないし4のいずれか1つに記載の半導体装置。

#### 【請求項6】

前記IGBT素子(10)は2個であることを特徴とする請求項5に記載の半導体装置

### 【請求項7】

前記2個以上のゲート酸化膜デバイス(10)のうちの1個のゲート酸化膜デバイス(10)の前記信号用パッド(10a~10e)と、前記端子(60)とがボンディングワイヤ(70)により電気的に接続されていることを特徴とする請求項1ないし6のいずれか1つに記載の半導体装置。

## 【発明の詳細な説明】

### 【技術分野】

## [0001]

本発明は、半導体素子の両側を一対の金属体で挟んでなり、装置のほぼ全体が樹脂でモールドされてなる半導体装置に関する。

## 【背景技術】

#### [0002]

従来より、この種の半導体装置としては、半導体素子と、半導体素子の一面側に設けられ電極と放熱体とを兼ねる第1の金属体と、半導体素子の他面側に設けられ電極と放熱体とを兼ねる第2の金属体と、半導体素子と外部とを電気的に接続するための端子と、半導体素子、第1の金属体、第2の金属体および端子の一部を包み込むように封止するモールド樹脂とを備えた半導体装置が提案されている(たとえば、特許文献1参照)。

### [0003]

このような半導体装置において、半導体素子としては、たとえば、IGBT(絶縁ゲート型バイポーラトランジスタ)やMOSFET素子などのゲート酸化膜デバイス、あるいはFWD(フリーホイールダイオード)などの縦型パワー素子が採用される。

## [0004]

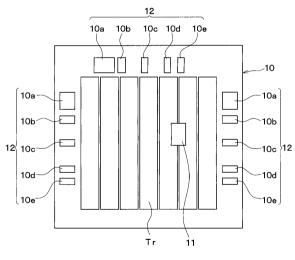

図 6 は、この種の半導体装置の一般的な概略構成を示す図であって(a)は各部の平面的な配置を示す図、(b)は、(a)に示される半導体装置の概略断面構成を示す図である。

## [0005]

10

20

30

10

20

30

40

50

図6において、半導体素子としてのゲート酸化膜デバイス10は、IGBT素子10であり、また、もう一つの半導体素子18はFWDである。そして、これら半導体素子10、18のうち、図6において現れている面が素子形成面である主表面、これと反対側の面が主裏面である。

### [0006]

ここで、IGBT素子10の主表面には、温度センスダイオード11が設けられている。この温度センスダイオード11は、一般的に設けられているもので、半導体製造技術を用いて形成されたポリシリコン等からなるダイオード素子である。

### [0007]

この温度センスダイオード11は温度によって電圧が変化するので、IGBT素子10 の温度を検出するのに用いられている。

#### [0008]

これら半導体素子10、18の主裏面側には、電極と放熱体とを兼ねる第1の金属体2 0が、はんだなどの導電性接合部材を介して電気的・熱的に接合されている。また、半導体素子10、18の主表面側には、電極と放熱体とを兼ねる第2の金属体30が、はんだなどの導電性接合部材を介して電気的・熱的に接合されている。

#### [0009]

また、ゲート酸化膜デバイスであるIGBT素子10の周囲には、各種の信号端子60が設けられており、IGBT素子10の主表面と信号端子60とは、ボンディングワイヤ70を介して電気的に接続されている。そして、装置のほぼ全体が樹脂80によりモールドされ封止されている。

#### [0010]

ここにおいて、図6中の5本の信号端子60のうち、下側から1番目と2番目の2本が温度センスダイオード11用の端子すなわち温度センス用端子A、Kである。これら温度センス用端子A、Kは、アノード用端子Aとカソード用端子Kであり、それぞれ、IGBT素子10に設けられた素子の温度検出を行うための温度センス用パッドに接続されている。

### [0011]

また、図6中の5本の信号端子60のうち、下側から3番目の端子は、IGBT素子10の信号電極用パッドであるゲートセンス用パッドと接続されるゲートセンス用端子Gである。

## [0012]

また、図6中の5本の信号端子60のうち、下側から4番目の端子は、IGBT素子10に流れる電流を検出するための電流センス用パッドと接続される電流センス用端子SEであり、一番上側の端子は、IGBT素子10の基準電位用パッドであるケルビンセンス用パッドと接続される基準端子としてのケルビンセンス用端子KEである。

#### [0013]

ここで、図6に示されるように、IGBT素子10は、その主表面に複数個のセルブロックTrが配列されたものであり、個々のセルブロックTrは、たとえば複数個のトランジスタ等の素子の集合体として構成されている。

## [0014]

そして、多数のトランジスタセルのうちの1個のセルTrが、電流センス用セルとして用いられ、電流センス用端子SEから出力される電流の異常を検出するようになっている。電流の異常が検出された場合には、ゲート電流を止めてIGBT素子10の作動を停止するようになっている。

【特許文献1】特開2003-110064号公報

#### 【発明の開示】

【発明が解決しようとする課題】

#### [0015]

ところで、上記した従来の半導体装置においては、両金属体20、30に挟まれた半導

体素子としてのゲート酸化膜デバイス10は、比較的大型(たとえば13mm 程度)の ものであり、コストが高く、半導体装置につき1個しか設けられていなかった。

### [0016]

そこで、本発明は上記問題に鑑み、半導体素子の両側を一対の金属体で挟んでなり、装置のほぼ全体がモールド樹脂でモールドされてなる半導体装置において、より安価な構成を実現することを目的とする。

【課題を解決するための手段】

### [0017]

上記目的を達成するため、請求項1に記載の発明では、半導体素子(10)と、半導体素子(10)の一面側に設けられ、電極と放熱体とを兼ねる第1の金属体(20)と、半導体素子(10)の他面側に設けられ、電極と放熱体とを兼ねる第2の金属体(30)と、半導体素子(10)と外部とを電気的に接続するための端子(60)と、半導体素子(10)、第1の金属体(20)、第2の金属体(30)および端子(60)の一部を包み込むように封止するモールド樹脂(80)とを備える半導体装置において、次のような点を特徴としている。

#### [0018]

すなわち、本発明は、半導体素子(10)としてゲート酸化膜デバイス(10)が用いられており、ゲート酸化膜デバイス(10)は、2個以上設けられており、個々のゲート酸化膜デバイス(10)は、複数種類の信号用パッド(10a、10b、10c、10d、10e)を有するとともに、1個のゲート酸化膜デバイス(10)について同種の信号用パッド(10a~10e)が2個以上設けられており、ゲート酸化膜デバイス(10)の間にて、同種の信号用パッド(10a、10c)同士が電気的に接続されており、個々のゲート酸化膜デバイス(10)は、信号用パッドとして2個以上のゲートセンス用パッド(10c)および2個以上のケルビンセンス用パッド(10a)を備えており、ゲート酸化膜デバイス(10)の間にて、ゲートセンス用パッド(10c)同士およびケルビンセンス用パッド(10a)同士およびケルビンセンス用パッド(10a)同士が電気的に接続されていることを特徴としている。

#### [0019]

IGBT素子やMOSFET素子などのようなゲート酸化膜デバイス(10)の素子性能は、通常その素子面積に比例する。本発明によれば、ゲート酸化膜デバイス(10)を2個以上設けることにより、個々のゲート酸化膜デバイス(10)の素子面積を従来よりも小さなものにできるため、コストダウンを実現することができる。

## [0020]

そして、素子面積の小さなゲート酸化膜デバイス(10)を2個以上設けることにより、2個以上のゲート酸化膜デバイス(10)を合わせた素子性能を、従来の比較的素子面積の大きなゲート酸化膜デバイスと同程度のものにできるため、素子性能については確保することができる。

## [0021]

また、本発明では、個々のゲート酸化膜デバイス(10)は、複数種類の信号用パッド(10a~10e)を有するとともに、同種の信号用パッド(10a~10e)が2個以上設けられており、さらに、異なるゲート酸化膜デバイス(10)の間にて、同種の信号用パッド(10a、10c)同士が電気的に接続されている。

#### [0022]

このことは、具体的には、次のようなことである。たとえば、2個のゲート酸化膜デバイスのそれぞれが、P1、P2、P3の3種類の信号用パッドを有し、1個のゲート酸化膜デバイスについて、P1のパッドが2個、P2のパッドが2個、P3のパッドが2個備えられているとする。

### [0023]

そして、たとえば、第1のゲート酸化膜デバイスにおける P 1 のパッド、および、第 2 のゲート酸化膜デバイスにおける P 1 のパッド同士が、電気的に接続されているということである。

10

20

30

40

#### [0024]

それにより、2個以上のゲート酸化膜デバイス(10)は、2個以上のものが合わさったもの全体として適切に機能することができるとともに、1個のゲート酸化膜デバイス(10)について外部接続用の端子(60)を用意すればよいため、当該端子(60)の数を増加させることがなくなる。

### [0025]

したがって、本発明によれば、半導体素子(10)の両側を一対の金属体(20、30)で挟んでなり、装置のほぼ全体がモールド樹脂(80)でモールドされてなる半導体装置において、より安価な構成を適切に実現することができる。また、請求項1に記載の発明では、個々のゲート酸化膜デバイス(10)は、信号用パッドとして2個以上のゲートセンス用パッド(10c)および2個以上のケルビンセンス用パッド(10a)を備えており、ゲート酸化膜デバイス(10)の間にて、ゲートセンス用パッド(10c)同士およびケルビンセンス用パッド(10a)同士が電気的に接続されているため、半導体装置における2個以上のゲート酸化膜デバイス(10)のそれぞれにおいて、基本的な作動を適切に確保できることから、それぞれの誤作動を極力防止することができ、好ましい。

#### [0026]

また、請求項 2 に記載の発明では、請求項 1 に記載の半導体装置において、個々のゲート酸化膜デバイス(10)は矩形板状をなすものであり、複数種類の信号用パッド(10  $a\sim10e$ )が配列されてなるパッドの配列ユニット(12)が、個々のゲート酸化膜デバイス(10)における少なくとも 2 辺以上に設けられていることを特徴としている。

#### [0027]

このように、矩形板状をなす個々のゲート酸化膜デバイス(10)の少なくとも2辺以上に、パッドの配列ユニット(12)を設けることにより、個々のゲート酸化膜デバイス(10)において、同種のものが2個以上である複数種類の信号用パッド(10a~10e)を適切に形成することができ、さらに、異なるゲート酸化膜デバイス(10)の間にて、同種の信号用パッド(10a、10c)同士の電気的な接続を適切に行うことができる。

## [0028]

また、請求項3に記載の発明では、請求項1に記載の半導体装置において、パッドの配列ユニット(12)は、個々のゲート酸化膜デバイス(10)における少なくとも3辺以上に設けられていることを特徴としている。

## [0029]

パッドの配列ユニット(12)を、個々のゲート酸化膜デバイス(10)における3辺以上に設ければ、2辺に設ける場合に比べて、異なるゲート酸化膜デバイス(10)の間の信号用パッド(10a~10e)同士の電気的な接続を行うにあたって、ゲート酸化膜デバイス(10)の配置位置や配置個数などの配置形態の自由度が大きくなる。

## [0030]

ここで、請求項4に記載の発明のように、請求項2または請求項3に記載の半導体装置においては、個々のゲート酸化膜デバイス(10)において、パッドの配列ユニット(12)が設けられる辺は、少なくとも互いに対向する2辺であることが好ましい。

## [0031]

また、請求項5に記載の発明のように、請求項1~請求項4に記載の半導体装置においては、2個以上のゲート酸化膜デバイスとしては、隣り合って配置されている2個以上のIGBT素子(10)とすることができる。

#### [0032]

また、請求項 6 に記載の発明では、請求項 5 に記載の半導体装置において、 I G B T 素子( 1 0 ) は 2 個であることを特徴としている。

### [0033]

また、請求項7に記載の発明のように、請求項1~請求項6に記載の半導体装置においては、2個以上のゲート酸化膜デバイス(10)のうちの1個のゲート酸化膜デバイス(

10

20

30

40

10)の信号用パッド(10a~10e)と、端子(60)とがボンディングワイヤ(70)により電気的に接続されているものにできる。

#### [0036]

なお、上記各手段の括弧内の符号は、後述する実施形態に記載の具体的手段との対応関係を示す一例である。

【発明を実施するための最良の形態】

#### [0037]

以下、本発明の実施形態について図に基づいて説明する。なお、以下の各実施形態相互において、互いに同一もしくは均等である部分には、説明の簡略化を図るべく、図中、同一符号を付してある。

10

### [0038]

#### (第1実施形態)

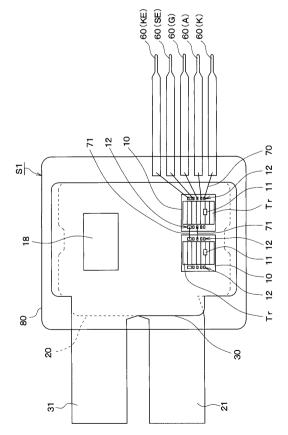

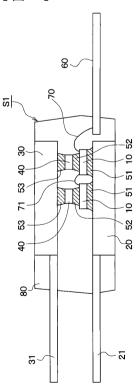

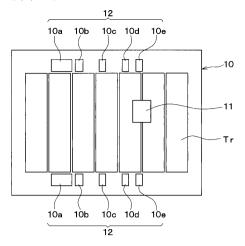

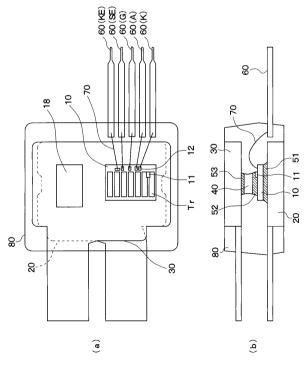

図1は本発明の第1実施形態に係る半導体装置S1の概略構成を示す図であって、モールド樹脂80内の各部の平面的な配置を示す図、図2は図1の概略断面構成を示す図である。また、図3は、図1中の半導体素子としてのゲート酸化膜デバイス10をその主表面側から見たときの構成を模式的に示す平面図である。

### [0039]

図1、図2に示されるように、本実施形態における半導体装置S1は、第1の半導体素子としての2個のゲート酸化膜デバイス10、第2の半導体素子としてのFWD(フリーホイールダイオード)18と、第1の金属体としての下側ヒートシンク20と、第2の金属体としての上側ヒートシンク30と、ヒートシンクブロック40と、これらの間に介在する各導電性接合部材51、52、53と、ゲート酸化膜デバイス10と外部とを電気的に接続するための信号端子60と、さらにモールド樹脂80とを備えて構成されている。

20

### [0040]

この構成の場合、図2に示されるように、両半導体素子10、18の下面と下側ヒートシンク20の上面との間は、第1の導電性接合部材51によって接合されている。

#### [0.041]

また、両半導体素子10、18の上面とヒートシンクブロック40の下面との間は、第2の導電性接合部材52によって接合されている。

[0042]

30

さらに、ヒートシンクブロック40の上面と上側ヒートシンク30の下面との間は、第3の導電性接合部材53によって接合されている。

#### [0043]

ここで、これら第1、第2、第3の導電性接合部材51、52、53としては、はんだや導電性接着剤等を採用することができる。具体的に本例の半導体装置においては、これら第1、第2、第3の導電性接合部材51、52、53として、Sn(すず)系はんだを用いている。

### [0044]

これにより、上記した構成においては、第1および第2の半導体素子10、18の上面では、第2の導電性接合部材52、ヒートシンクブロック40、第3の導電性接合部材53および上側ヒートシンク30を介して放熱が行われ、第1および第2の半導体素子10、18の下面では、第1の導電性接合部材51から下側ヒートシンク20を介して放熱が行われる構成となっている。

40

## [0045]

本実施形態では、半導体素子としてゲート酸化膜デバイス10が用いられており、このゲート酸化膜デバイス10は、2個以上設けられている。このゲート酸化膜デバイス10としては、IGBT(絶縁ゲート型バイポーラトランジスタ)やMOSFET素子などを採用することができる。

## [0046]

本例では、ゲート酸化膜デバイス10は、IGBT素子10であり、図1に示されるよ

10

20

30

40

50

うに、2個のIGBT素子が隣り合って配置されている。具体的には、各IGBT素子10の形状は、たとえば矩形状の薄板状とすることができる。そして、図2において、IGBT素子10の上面側が素子形成面である主表面、下面側が主裏面である。

#### [0047]

また、本実施形態のIGBT素子10の主表面には、図3に示されるように、複数個のセルブロックTrが配列された形となっている。図示例では7個のセルブロックTrが配列している。個々のセルブロックTrは、たとえば複数個のトランジスタ等の素子の集合体として構成されている。

#### [0048]

そして、図示しないが、各セルブロックTrの上には、主表面側における主電極が形成されている。また、図示しないが、IGBT素子10の主裏面側にも主電極が形成されている。ここで、IGBT素子10の主電極としては、たとえば主表面側の主電極がエミッタ電極、主裏面側の主電極がコレクタ電極とすることができる。

### [0049]

また、図3に示されるように、各IGBT素子10の主表面には、温度センスダイオード11が設けられている。

### [0050]

この温度センスダイオード11は、上述したように、一般的に設けられているもので、 半導体製造技術を用いて形成されたポリシリコン等からなるダイオード素子であり、温度 によって電圧が変化するので、各IGBT素子10の温度を検出する目的で用いられてい る。

#### [0051]

また、図3に示されるように、各IGBT素子10の主表面の外周部には、複数種類の信号用パッド10a、10b、10c、10d、10eが設けられている。これら各信号用パッド10a~10eはアルミニウムなどをスパッタリングなどによって成膜してなるものである。

## [0052]

そして、1個のIGBT素子10について同種の信号用パッド10a~10eが2個以上、本例では2個ずつ設けられている。また、本例では、矩形板状をなす個々のIGBT素子10の外周部において対向する2辺に、それぞれ、複数種類の信号用パッド10a、10b、10c、10d、10eが配列されてなるパッドの配列ユニット12が設けられている。

#### [0053]

そして、図1に示されるように、2個のIGBT素子10は、上記したパッドの配列ユニット12が設けられている辺1つのにおいて対向するように、互いに隣り合って配置されている。本例では、後述する各信号端子60の配列方向とは直交する方向(つまり、信号端子60の長手方向)に沿って2個のIGBT素子10が配列されている。

### [0054]

ここにおいて、図3中の5個の信号用パッド10a~10eからなる1つのパッドの配列ユニット12をみた場合、右側から1番目と2番目の2個のパッド10d、10eが温度センスダイオード11用の端子すなわち温度センス用パッド10d、10eである。これら温度センス用パッド10d、10eは、アノード用パッド10dとカソード用パッド10eである。

## [0055]

また、図3中の1つのパッドの配列ユニット12における5個の信号用パッド10a~10eのうち、右側から3番目のパッド10cは、IGBT素子10の信号電極用パッドであるゲートセンス用パッド10cであり、右側から4番目のパッド10bは、IGBT素子10に流れる電流を検出するための電流センス用パッド10bであり、一番左側のパッド10aは、IGBT素子10の基準電位用パッドであるケルビンセンス用パッド10aである。

#### [0056]

そして、本実施形態においては、図2に示されるように、IGBT素子10の主裏面側の主電極は、第1の金属体である下側ヒートシンク20に対して、第1の導電性接合部材51を介して電気的に接続され、IGBT素子10の主表面側の主電極およびFWD18の上面は、第2の導電性接合部材52を介してヒートシンクブロック40に対して、電気的および熱的に接続されている。

#### [0057]

ここで、ヒートシンクブロック 40 は、 2 個の I G B T 素子 10 および F W D 18 のそれぞれについて設けられている。なお、 F W D 18 に対応して設けられているヒートシンクブロックは図示せずに省略してある。

[0058]

さらに、図2に示されるように、ヒートシンクブロック40における半導体素子10、18側の面とは反対側の面にて、第2の金属体である上側ヒートシンク30とヒートシンクブロック40とが、第3の導電性接合部材53を介して電気的および熱的に接続されている。

[0059]

ここで、下側ヒートシンク20、上側ヒートシンク30およびヒートシンクブロック40は、たとえば、銅合金もしくはアルミ合金等の熱伝導性および電気伝導性の良い金属で構成されている。また、ヒートシンクブロック40としては、一般的な鉄合金を用いてもよい。

[0060]

また、図1に示されるように、下側ヒートシンク20は、たとえば、全体としてほぼ長方形状の板材とすることができる。また、この下側ヒートシンク20には、端子部21が突設されているが、この端子部21は、IGBT素子10の主裏面側の主電極であるたとえばコレクタ電極の取り出し電極となっている。

[0061]

また、ヒートシンクブロック40は、たとえば、IGBT素子10よりも1回り小さい 程度の大きさの矩形状の板材とすることができる。

[0062]

このヒートシンクブロック40は、半導体素子10、18と上側ヒートシンク30との間に介在し、それぞれの半導体素子10、18と上側ヒートシンク30とを熱的および電気的に接続するとともに、各IGBT素子10から後述するボンディングワイヤ70、71を引き出す際の当該ワイヤの高さを確保する等のために、IGBT素子10と上側ヒートシンク30との間の高さを確保する役割を有している。

[0063]

さらに、図1に示されるように、上側ヒートシンク30も、たとえば、全体としてほぼ長方形状の板材で構成することができる。また、この上側ヒートシンク30にも、端子部31が突設されているが、この端子部31は、IGBT素子10の主表面側の主電極であるたとえばエミッタ電極の取り出し電極となっている。

[0064]

ここで、下側ヒートシンク20の端子部21および上側ヒートシンク30の端子部31は、それぞれ上述したように、IGBT素子10の主電極の取り出し電極であり、これら端子部21、31は、半導体装置S1において外部配線部材等との接続を行うために設けられているものである。

[0065]

このように、下側ヒートシンク20および上側ヒートシンク30は、それぞれ、電極と放熱体とを兼ねる第1の金属体および第2の金属体として構成されており、半導体装置S1において半導体素子10、18からの放熱を行う機能を有するとともに半導体素子10の電極としての機能も有する。

[0066]

10

20

30

40

また、IGBT素子10の周囲には、リードフレーム等からなる信号端子60が設けられている。この信号端子60は、IGBT素子10の主表面に設けられている信号電極(たとえばゲート電極)や上記した温度センスダイオード11などと導通する端子や基準端子となるものである。

## [0067]

図 1、図 2 に示されるように、信号端子 6 0 は、 2 個の I G B T 素子 1 0 うちの図中の右側に位置する一方の I G B T 素子 1 0 の外周部に設けられている各信号用パッド 1 0 a ~ 1 0 e に対して、ボンディングワイヤ 7 0 によって結線され、電気的に接続されている。このワイヤ 7 0 はワイヤボンディング等により形成され、金やアルミニウム等からなるものである。

[0068]

図 1 中の 5 本の信号端子 6 0 のうち、下側から 1 番目と 2 番目の 2 本が温度センスダイオード 1 1 用の端子すなわち温度センス用端子 A 、 K である。

[0069]

これら温度センス用端子A、Kは、アノード用端子Aとカソード用端子Kであり、それぞれ、IGBT素子10に設けられた温度センス用パッドとしてのアノード用パッド10dとカソード用パッド10e(図3参照)に接続されている。

[0070]

また、図1中の5本の信号端子60のうち、下側から3番目の端子はゲートセンス用端子Gであり、このゲートセンス用端子GはIGBT素子10の信号電極用パッドであるゲートセンス用パッド10cと接続されている。

[0071]

また、図1中の5本の信号端子60のうち、下側から4番目の端子は電流センス用端子SEであり、この電流センス用端子SEは、IGBT素子10の電流センス用パッド10 bと接続されている。また、一番上側の端子はケルビンセンス用端子KEであり、このケルビンセンス用端子KEは、IGBT素子10ケルビンセンス用パッド10aと接続されている。

[0072]

また、本半導体装置 S 1 においては、 2 個の I G B T 素子 1 0 の間にて、同種の信号用パッド 1 0 a 、 1 0 c 同士が電気的に接続されている。

[0073]

本例では、図1、図2に示されるように、2個のIGBT素子10の間にて、ゲートセンス用パッド10c同士およびケルビンセンス用パッド10a同士が、ボンディングワイヤ71を介して結線され、電気的に接続されている。このワイヤ71も、ワイヤボンディング等により形成され、金やアルミニウム等からなるものである。

[0074]

なお、2個のIGBT素子10の間にて、ゲートセンス用パッド10c同士およびケルビンセンス用パッド10a同士だけでなく、すべての同種の信号用パッド10a~10e同士をボンディングワイヤを介して結線し、電気的に接続するようにしてもよい。

[0075]

ただし、本例では、ボンディングワイヤ71の本数を低減して構成を簡略化するために、IGBT素子10の作動に必要な最低限のパッド同士、すなわち、ゲートセンス用パッド10c同士およびケルビンセンス用パッド10a同士を電気的に接続している。それにより、2個のIGBT素子10の基本的な作動を確保している。

[0076]

さらに、本実施形態の半導体装置 S 1 においては、装置 S 1 のほぼ全体がモールド樹脂 8 0 によりモールドされ封止されている。具体的には、図 1、図 2 に示されるように、一対のヒートシンク 2 0、3 0 の隙間、並びに、半導体素子 1 0、 1 8 およびヒートシンク ブロック 4 0 の周囲部分には、モールド樹脂 8 0 が充填封止されている。

[0077]

10

20

30

40

10

20

30

40

50

また、複数本の信号端子60は、上述したように一方のIGBT素子10とボンディングワイヤ70を介して結線されているが、各信号端子60におけるボンディングワイヤ70との接続部は、モールド樹脂80にて封止されている。そして、各信号端子60の先端部は、モールド樹脂80から突出しており、外部の基板や配線部材などと接続可能となっている。

## [0078]

このモールド樹脂 8 0 は、たとえばエポキシ樹脂等の通常のモールド材料を採用することができる。また、ヒートシンク 2 0 、 3 0 等を樹脂 8 0 でモールドするにあたっては、上下型からなる成形型(図示しない)を使用し、トランスファーモールド法によって容易に行うことができる。

[0079]

このように、本実施形態の半導体装置 S 1 は、基本的には、縦型パワー素子であるゲート酸化膜デバイス 1 0 の表裏の主面に金属体 2 0 、 3 0 、 4 0 を導電性接着剤 5 1 ~ 5 3 を介して電気的・熱的に接続してなる樹脂モールドタイプの半導体装置として構成されている。

[0800]

次に、上記した構成の半導体装置 S 1 の製造方法について、図 1 、図 2 を参照して、簡単に説明する。まず、下側ヒートシンク 2 0 の上面に、両半導体素子 1 0 、 1 8 とヒートシンクブロック 4 0 をはんだ付けする工程を実行する。

[0081]

この場合、下側ヒートシンク20の上面に、たとえばSn系はんだからなるはんだ箔を介して両半導体素子10、18を積層するとともに、これら両半導体素子10、18の上に、同じはんだ箔を介して、それぞれヒートシンクブロック40を積層する。

[0082]

この後、加熱装置(リフロー装置)によって、はんだの融点以上に昇温することにより 、上記はんだ箔を溶融させてから、硬化させる。

[0083]

続いて、一方のIGBT素子10と信号端子60とをワイヤボンディングする工程を実行する。これにより、ワイヤ70によって一方のIGBT素子10と信号端子60とが結線され電気的に接続される。

[0084]

また、2個のIGBT素子10間において、同種の信号用パッド10a、10c同士の間でワイヤボンディングを行う。本例では、2個のIGBT素子10間において、ゲートセンス用パッド10c同士およびケルビンセンス用パッド10a同士の間でワイヤボンディングを行う。これにより、2個のIGBT素子10の間にて、同種の信号用パッド10a、10c同士がボンディングワイヤ71を介して結線され、電気的に接続される。

[0085]

次いで、各ヒートシンクブロック40の上に上側ヒートシンク30をはんだ付けする工程を実行する。この場合、ヒートシンクブロック40の上にはんだ箔を介して上側ヒートシンク30を載せる。そして、加熱装置によって上記はんだ箔を溶融させてから、硬化させる。

[0086]

こうして、溶融した各々のはんだ箔が硬化すれば、硬化したはんだが、第1、第2、第3の導電性接合部材51、52、53として構成されることになる。

[0087]

そして、これら導電性接合部材 5 1 ~ 5 3 を介して、下側ヒートシンク 2 0 、両半導体素子 1 0 、 1 8 、ヒートシンクブロック 4 0 、上側ヒートシンク 3 0 間の接合および電気的・熱的接続を実現することができる。

[0088]

なお、第1、第2および第3の導電性接合部材51、52、53として導電性接着剤を

(11)

用いた場合にも、上記工程において、はんだを導電性接着剤に置き換え、導電性接着剤の塗布や硬化を行うことにより、下側ヒートシンク20、両半導体素子10、18、ヒートシンクプロック40、上側ヒートシンク30間の接合および電気的・熱的接続を実現することができる。

### [0089]

しかる後、図示しない成形型を使用して、ヒートシンク20、30の隙間および外周部等にモールド樹脂80を充填する工程を実行する。これにより、図1、図2に示されるように、ヒートシンク20、30の隙間および外周部等に、モールド樹脂80が充填封止される。

### [0090]

そして、モールド樹脂80が硬化した後、成形型内から半導体装置S1を取り出せば、 半導体装置S1が完成する。この半導体装置S1は、たとえば、プリント基板などの外部 の実装基板に対して、モールド樹脂80から突出する信号端子60の部分を介して電気的 に接続された状態で実装される。

### [0091]

なお、半導体装置 S 1 においては、上記構成の場合、下側ヒートシンク 2 0 の下面および上側ヒートシンク 3 0 の上面が、それぞれ露出するように樹脂モールドされている。これにより、ヒートシンク 2 0 、 3 0 の放熱性が高められている。

#### [0092]

ところで、本実施形態によれば、半導体素子10と、半導体素子10の一面側に設けられ電極と放熱体とを兼ねる第1の金属体としての下側ヒートシンク20と、半導体素子10の他面側に設けられ電極と放熱体とを兼ねる第2の金属体としての上側ヒートシンク30と、半導体素子10と外部とを電気的に接続するための信号端子60と、半導体素子10、両ヒートシンク20、30および信号端子60の一部を包み込むように封止するモールド樹脂80とを備える半導体装置S1において、次のような点を特徴としている。

### [0093]

1つ目の点として、半導体素子10としてIGBT素子やMOSFET素子などのゲート酸化膜デバイス10が用いられており、ゲート酸化膜デバイス10は2個以上設けられていること。本例では、IGBT素子10が2個用いられている。

## [0094]

2つ目の点として、個々のゲート酸化膜デバイス10は、複数種類の信号用パッド10a、10b、10c、10d、10eを有するとともに、1個のゲート酸化膜デバイス10について同種の信号用パッド10a~10eが2個以上設けられており、異なるゲート酸化膜デバイス10の間にて、同種の信号用パッド10a、10c同士が電気的に接続されていること。本実施形態の半導体装置S1は、主としてこれらの2つの点を特徴としている。

## [0095]

上述したように、IGBT素子やMOSFET素子などのようなゲート酸化膜デバイス 10の素子性能は、通常その素子面積に比例する。つまり、通常、素子面積が大きいほど 、素子性能は高くなる。

## [0096]

本実施形態によれば、ゲート酸化膜デバイス10を2個以上設けることにより、個々のゲート酸化膜デバイス10の素子面積を従来よりも小さなものにできるため、コストダウンを実現することができる。

#### [0097]

そして、素子面積の小さなゲート酸化膜デバイス10を2個以上設けることにより、2個以上のゲート酸化膜デバイス10を合わせた素子性能を、従来の比較的素子面積の大きなゲート酸化膜デバイスと同程度のものにできるため、素子性能については確保することができる。

## [0098]

10

20

30

また、上記した2つ目の特徴点によれば、2個以上のゲート酸化膜デバイス10は、2個以上のものが合わさったもの全体として適切に機能することができる。それとともに、2個以上のゲート酸化膜デバイス10のすべてではなく、1個のゲート酸化膜デバイス10について信号端子60を用意すればよいため、信号端子60の数を増加させることがなくなる。

## [0099]

具体的には、図1に示されるように、2個のIGBT素子10が設けられていても、一方のIGBT素子10について信号用パッド10a~10eと各信号端子60とをワイヤ70を介して電気的に接続すればよい。

## [0100]

そして、他方のIGBT素子10については、一方のIGBT素子10に対して同種の信号用パッド10a、10cが、ワイヤ71を介して電気的に接続されている。そのため、結果的に、他方のIGBT素子10も信号端子60と導通し、素子として作動することができる。

### [0101]

したがって、本実施形態によれば、半導体素子10の両側を一対の金属体20、30で挟んでなり、装置のほぼ全体がモールド樹脂80でモールドされてなる半導体装置において、より安価な構成を適切に実現することができる。

### [0102]

また、本実施形態では、半導体装置 S 1 において、個々のゲート酸化膜デバイスとしての I G B T 素子 1 0 は矩形板状をなすものであり、複数種類の信号用パッド 1 0 a ~ 1 0 e が配列されてなるパッドの配列ユニット 1 2 が、個々の I G B T 素子 1 0 における外周部の 2 辺に設けられている。

#### [0103]

特に、上記図1、図3に示される例では、個々のIGBT素子10において、パッドの配列ユニット12が設けられる辺は、矩形状のIGBT素子10において互いに対向する 2辺としている。

#### [0104]

このように、矩形板状をなす個々のIGBT素子10の2辺に、パッドの配列ユニット12を設けることにより、個々のIGBT素子10において、同種のものが2個ある複数種類の信号用パッド10a~10eを適切に形成することができ、さらに、異なるIGBT素子10の間にて、同種の信号用パッド10a、10c同士の電気的な接続を適切に行うことができる。

## [0105]

また、本実施形態では、半導体装置S1においては、2個のIGBT素子10のうちの一方のIGBT素子10の信号用パッド10a~10eと、信号端子60とがボンディングワイヤ70により電気的に接続されているものとしている。ただし、信号用パッド10a~10eと信号端子60との電気的な接続はボンディングワイヤに限定されるものではなく、種々の形態が可能である。

### [0106]

また、本実施形態では、半導体装置S1において、個々のIGBT素子10は、信号用パッドとして2個のゲートセンス用パッド10cおよび2個のケルビンセンス用パッド10aを備えており、異なるIGBT素子10の間にて、ゲートセンス用パッド10c同士およびケルビンセンス用パッド10a同士がボンディングワイヤ71を介して電気的に接続されている。

## [0107]

それによれば、半導体装置における2個のIGBT素子10のそれぞれにおいて、基本的な作動を適切に確保できることから、それぞれの誤作動を極力防止することができ、好ましい。

## [0108]

40

10

20

30

また、異なるIGBT素子10の間にて、ゲートセンス用パッド10c同士およびケルビンセンス用パッド10a同士などの同種の信号用パッドを電気的に接続するにあたっても、ボンディングワイヤ71に限定されるものではなく、種々の形態が可能である。

#### [0109]

なお、本実施形態においては、主としてゲート酸化膜デバイス10としてIGBT素子10を例にして述べてきたが、ゲート酸化膜デバイス10であるならば、それ以外のたとえばMOSFET素子であっても同様のものとできることはもちろんである。

### [0110]

つまり、本実施形態でいうゲート酸化膜デバイスとは、ゲート酸化膜を有するデバイス であって、IGBT素子およびMOSFET素子を意味するものである。

10

### [0111]

#### (第2実施形態)

上記第1実施形態では、主として、ゲート酸化膜デバイス10が2個である場合について説明したが、もちろんゲート酸化膜デバイスは2個以上であるならばよく、3個でも、あるいは4個以上でもよい。

#### [0112]

また、上記第1実施形態では、主として、個々のゲート酸化膜デバイス10は、複数種類の信号用パッド10a、10b、10c、10d、10eを有するとともに、1個のゲート酸化膜デバイス10について同種の信号用パッド10a~10eが2個である場合を示しているが、1個のゲート酸化膜デバイス10について同種の信号用パッド10a~10eが3個以上であってもよいことはもちろんである。

20

#### [0113]

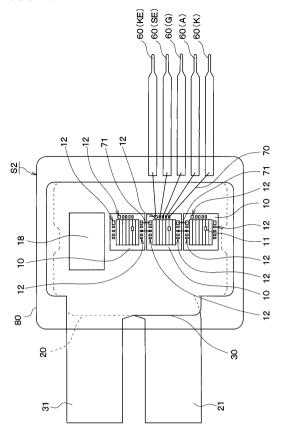

図4は、本発明の第2実施形態に係る半導体装置S2の概略構成を示す図であって、モールド樹脂80内の各部の平面的な配置を示す図である。また、図5は、図4中の半導体素子としてのゲート酸化膜デバイス10をその主表面側から見たときの構成を模式的に示す平面図である。上記実施形態との相違点を中心に述べる。

### [0114]

図 4 に示される半導体装置 S 2 では、ゲート酸化膜デバイスとしての I G B T 素子 1 0 が 3 個配列されており、 1 個の I G B T 素子 1 0 について同種の信号用パッド 1 0 a ~ 1 0 e が 3 個である場合が示されている。

30

## [0115]

### [0116]

### [0117]

そして、本半導体装置S2においても、配列された3個のIGBT素子10のうち隣り合うIGBT素子10の間にて、同種の信号用パッド10a、10c同士が電気的に接続されている。

40

### [0118]

本例では、図4に示されるように、隣り合うIGBT素子10の間にて、ゲートセンス用パッド10c同士およびケルビンセンス用パッド10a同士が、ボンディングワイヤ71を介して結線され、電気的に接続されている。

#### [0119]

また、本例では、信号端子60は、配列された3個のIGBT素子10のうち中央の1個のIGBT素子10に設けられた各信号用パッド10a~10eに対して、ボンディングワイヤ70によって結線され、電気的に接続されている。

#### [0120]

本実施形態のように、パッドの配列ユニット 12 を、個々の 1 G B T 素子 10 における 3 辺以上に設ければ、2 辺に設ける場合に比べて、異なる 1 G B T 素子 10 の間の信号用パッド 10 a  $\sim 10$  e 同士の電気的な接続を行うにあたって、1 G B T 素子 10 の配置位置や配置個数などの配置形態の自由度が大きくなる。

#### [0121]

たとえば、上記図1や図3に示されるようなIGBT素子10における対向する2辺のみに、パッドの配列ユニット12を設けた場合、複数個のIGBT素子10は、1列に直線状に配置せざるを得ない。

### [0122]

それに対して、本実施形態のように、当該配列ユニット12を、IGBT素子10の3 辺以上に設ければ、複数個のIGBT素子10を2列に配置したり、曲がった形で配列し たりすることもできる。

## [0123]

たとえば、図4に示される例では、各信号端子60の配列方向に沿って、3個のIGBT素子10が配列されているが、IGBT素子10の上記3辺を用いれば、たとえば3個のIGBT素子10をL字形状に配列することも可能である。もちろん、本実施形態においても、各信号端子60の配列方向とは直交する方向へ3個のIGBT素子10を直線状に配列することも可能である。

## [0124]

また、本例では、信号端子 6 0 は、 3 個のうちの中央の 1 個の I G B T 素子 1 0 に設けられた各信号用パッド 1 0 a ~ 1 0 e に対してワイヤボンディングワイヤされているが、両外側の 2 個のどちらか一方の I G B T 素子 1 0 にワイヤボンディングするようにしてもよい。

### [0125]

ここで、上記図4、図5に示される例では、パッドの配列ユニット12は、矩形板状をなす個々のIGBT素子10における3辺に設けられていたが、4辺、つまりすべての辺にパッドの配列ユニット12が設けられていてもよい。

### [0126]

#### (他の実施形態)

なお、上述したように、ヒートシンクブロック40は、半導体素子10、18と上側ヒートシンク30との間に介在し、第1の半導体素子10と上側ヒートシンク30との間の高さを確保する役割を有するものであるが、可能であるならば、上記各実施形態において、ヒートシンクブロック40は存在しないものであってもよい。

# [0127]

要するに、本発明は、半導体素子と、半導体素子の一面側に設けられ電極と放熱体とを 兼ねる第1の金属体と、半導体素子の他面側に設けられ電極と放熱体とを兼ねる第2の金 属体と、半導体素子と外部とを電気的に接続するための信号端子と、半導体素子、第1の 金属体、第2の金属体および信号端子の一部を包み込むように封止するモールド樹脂とを 備える半導体装置において、半導体素子としてゲート酸化膜デバイスを用い、ゲート酸化 膜デバイスを2個以上設けるとともに、個々のゲート酸化膜デバイスは、複数種類の信号 用パッドを有し、1個のゲート酸化膜デバイスについて同種の信号用パッドを2個以上設 け、異なるゲート酸化膜デバイスの間にて同種の信号用パッド同士を電気的に接続したこ とを要部とするものであり、その他の部分については適宜設計変更が可能である。

### 【図面の簡単な説明】

## [0128]

【図1】本発明の第1実施形態に係る半導体装置におけるモールド樹脂内の各部の平面的な配置構成を示す図である。

【図2】図1に示される半導体装置の概略断面構成を示す図である。

【図3】図1中の半導体素子としてのゲート酸化膜デバイスをその主表面側から見たとき

10

20

30

40

の構成を模式的に示す平面図である。

【図4】本発明の第2実施形態に係る半導体装置におけるモールド樹脂内の各部の平面的な配置構成を示す図である。

【図5】図4中の半導体素子としてのゲート酸化膜デバイスをその主表面側から見たときの構成を模式的に示す平面図である。

【図6】従来の半導体装置の一般的な概略構成を示す図であって(a)は各部の平面的な配置を示す図、(b)は、(a)に示される半導体装置の概略断面構成を示す図である。 【符号の説明】

## [0129]

10…半導体素子であるゲート酸化膜デバイスとしてのIGBT素子、

10a…ケルビンセンス用パッド、10b…電流センス用パッド、

- 10c…ゲートセンス用パッド、10d、10e…温度センス用パッド、

- 12…パッドの配列ユニット、20…第1の金属体としての下側ヒートシンク、

- 30…第2の金属体としての上側ヒートシンク、60…信号端子、

- 70…ボンディングワイヤ、80…モールド樹脂。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

# フロントページの続き

(56)参考文献 特開平10-056131(JP,A)

特開平05-291485(JP,A)

特開2001-156219(JP,A)

特開2005-032736(JP,A)

特開2001-237369(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 23/48