# (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 108933116 B (45) 授权公告日 2023. 12. 05

(21)申请号 201810506948.2

(22)申请日 2018.05.24

(65) 同一申请的已公布的文献号 申请公布号 CN 108933116 A

(43)申请公布日 2018.12.04

(30)优先权数据

15/603476 2017.05.24 US

(73) **专利权人** 英飞凌科技股份有限公司 地址 德国瑙伊比贝尔格市坎芘昂1-12号

(72) **发明人** D.阿勒斯 G.德拉洛泽 D.施赖泽 C.施皮尔曼 T.施特克

(74) **专利代理机构** 中国专利代理(香港)有限公司 72001

专利代理师 胡莉莉 申屠伟进

(51) Int.CI.

H01L 23/495 (2006.01)

(56) 对比文件

CN 104009013 A,2014.08.27

US 2014240945 A1,2014.08.28

US 2015092375 A1,2015.04.02

US 2016247751 A1,2016.08.25

US 2005133902 A1,2005.06.23

US 9496208 B1,2016.11.15

US 2014306332 A1,2014.10.16

CN 102931182 A,2013.02.13

US 2005121777 A1,2005.06.09

审查员 穆晓龄

权利要求书2页 说明书11页 附图9页

#### (54) 发明名称

具有引线框的半导体封装

#### (57) 摘要

公开了具有引线框的半导体封装。半导体封装包括:引线框;第一晶体管芯片,在漏极向下配置中被连接到引线框的第一岛状部;以及第二晶体管芯片,在与第一晶体管芯片相同的漏极向下配置中被连接到引线框的第二岛状部。引线框的第一岛状部包括在朝向第二岛状部的方向上延伸超过第一晶体管芯片的外周并且重叠于第二晶体管芯片的延伸部。第一晶体管芯片和第二晶体管芯片被经由第一岛状部的延伸部和将延伸部电连接到第二晶体管芯片的第一电连接元件彼此电互连以形成半桥电路。

1.一种半导体封装,包括:

引线框;

第一晶体管芯片,在漏极向下配置中被连接到引线框的第一岛状部;以及

第二晶体管芯片,在与第一晶体管芯片相同的漏极向下配置中被连接到引线框的第二岛状部,

其中引线框的第一岛状部和第二岛状部彼此相互电隔离,

其中第一岛状部包括从第一岛状部的与第二岛状部相邻的边沿的端部悬置在外的延伸部,延伸部以保留第一岛状部和第二岛状部之间的间隙的方式延伸到第二岛状部的与第一岛状部的所述端部相邻的边沿区域外侧,

其中第一晶体管芯片和第二晶体管芯片被经由第一岛状部的延伸部和将延伸部电连接到第二晶体管芯片的第一电连接元件彼此电互连以形成半桥电路。

- 2.根据权利要求1所述的半导体封装,其中第一晶体管芯片包括面对并且连接到引线框的第一岛状部的漏极端子,其中第二晶体管芯片包括面对并且连接到引线框的第二岛状部的漏极端子,其中第二晶体管芯片包括在第二晶体管芯片的背对第二岛状部的一侧处的源极端子,并且其中第一晶体管芯片的漏极端子被通过第一岛状部的延伸部和第一电连接元件电耦合到第二晶体管芯片的源极端子。

- 3.根据权利要求2所述的半导体封装,其中第一电连接元件是在第一端部处连接到第一岛状部的延伸部并且在第二端部处连接到第二晶体管芯片的源极端子的金属夹片。

- 4.根据权利要求2所述的半导体封装,其中第一岛状部包括每个从延伸部向外突出的相邻的第一引脚和第二引脚,其中第一引脚对应于第一晶体管芯片的漏极端子,并且其中第二引脚对应于第二晶体管芯片的源极端子。

- 5.根据权利要求4所述的半导体封装,其中第一岛状部包括从延伸部向外突出的至少 一个附加的引脚。

- 6.根据权利要求2所述的半导体封装,其中第一晶体管芯片的漏极端子被直接导电地 胶粘、焊接或烧结在引线框的第一岛状部的上主表面上,并且其中第二晶体管芯片的漏极 端子被直接导电地胶粘、焊接或烧结在引线框的第二岛状部的上主表面上。

- 7.根据权利要求2所述的半导体封装,其中第一晶体管芯片包括在第一晶体管芯片的 背对第一岛状部的一侧处的源极端子和控制端子,并且其中第二晶体管芯片包括在第二晶 体管芯片的背对第二岛状部的一侧处的控制端子。

- 8.根据权利要求7所述的半导体封装,进一步包括:

- 第二电连接元件,将第一晶体管芯片的源极端子连接到引线框的至少一个第一源极引脚;

- 第三电连接元件,将第一晶体管芯片的控制端子连接到引线框的第一栅极引脚;以及第四电连接元件,将第二晶体管芯片的控制端子连接到引线框的第二栅极引脚。

- 9.根据权利要求8所述的半导体封装,其中第二电连接元件将第一晶体管芯片的源极端子连接到引线框的多个第一源极引脚。

- 10.根据权利要求9所述的半导体封装,其中第二电连接元件是金属夹片。

- 11.根据权利要求10所述的半导体封装,其中金属夹片在面对引线框的所述多个第一源极引脚的夹片端部处加宽。

- 12.根据权利要求9所述的半导体封装,其中第一栅极引脚和第二栅极引脚在相同的方向上并且从引线框的同一侧突出。

- 13.根据权利要求12所述的半导体封装,其中第一岛状部的延伸部插入在第一栅极引脚和第二栅极引脚之间。

- 14.根据权利要求9所述的半导体封装,其中第一栅极引脚和第二栅极引脚在相反的方向上突出并且从引线框的相对的侧突出。

- 15.根据权利要求1所述的半导体封装,其中引线框的第一岛状部的延伸部包括在半导体封装的第一侧处从延伸部向外突出的多个引脚,并且其中引线框的第二岛状部包括从引线框的与第一侧相对的第二侧突出的多个引脚。

- 16.根据权利要求1所述的半导体封装,其中第一晶体管芯片具有在第一晶体管芯片的 背对第一岛状部的一侧并且电连接到引线框的第一栅极引脚的控制端子,并且其中第二晶 体管芯片具有在第二晶体管芯片的背对第二岛状部的一侧并且电连接到引线框的第二栅 极引脚的控制端子。

- 17.根据权利要求1所述的半导体封装,其中第一晶体管芯片和第二晶体管芯片是在大小和形状上实质相同的半导体芯片。

- 18.根据权利要求1所述的半导体封装,其中第一晶体管芯片以第一定向连接到引线框的第一岛状部,并且其中第二晶体管芯片以被相对于第一定向旋转90度或180度的第二定向连接到引线框的第二岛状部。

- 19.根据权利要求1所述的半导体封装,其中半导体封装具有PQFN或HSOF封装架构。

# 具有引线框的半导体封装

#### 技术领域

[0001] 本发明涉及封装、电子器件、使用方法和制造方法。

## 背景技术

[0002] 例如用于汽车应用的封装为包括一个或多个集成电路元件的一个或多个电子芯片提供物理容置。封装的集成电路元件的示例是场效应晶体管、绝缘栅双极晶体管(IGBT)和二极管。

[0003] 潜在地仍然存在简化封装的可制造性同时高效地减少空间消耗并保持电流路径 短的空间。

## 发明内容

[0004] 可能存在针对具有高效布局的晶体管或集成电路封装的需要。

[0005] 根据示例性实施例,提供了一种封装,其包括:至少部分导电的芯片载体;包括第一连接端子、第二连接端子和控制端子的第一晶体管芯片,其中第一晶体管芯片和第二晶体管芯片被连接以形成半桥,并且其中第一晶体管芯片的第二连接端子通过芯片载体的在第一晶体管芯片的外部边沿区域和第二晶体管芯片的外部边沿区域之间延伸并且保持将第一晶体管芯片关于第二晶体管芯片横向地间隔开的间隙的条形部区段来与第二晶体管芯片的第一连接端子电耦合。

[0006] 根据另一个示例性实施例,提供了一种封装,其包括:引线框类型芯片载体;包括源极端子、漏极端子和栅极端子的第一场效应晶体管芯片;以及包括源极端子、漏极端子和栅极端子的第二场效应晶体管芯片,其中第一场效应晶体管芯片的漏极端子通过芯片载体与第二场效应晶体管芯片的源极端子电耦合,从而在第一场效应晶体管芯片和第二场效应晶体管芯片之间保留电绝缘的间隙。

[0007] 根据另一个示例性实施例,提供了一种电子器件,其包括具有上面提到的特征的多个电互连的封装。

[0008] 根据又一个示例性实施例,提供了一种制造封装的方法,其中该方法包括:提供至少部分导电的芯片载体;在芯片载体上安装第一晶体管芯片,第一晶体管芯片包括第一连接端子、第二连接端子和控制端子;在芯片载体上安装第二晶体管芯片,第二晶体管芯片包括第一连接端子、第二连接端子和控制端子;将第一晶体管芯片和第二晶体管芯片连接以形成半桥,并且通过芯片载体的在第一晶体管芯片的外部边沿区域和第二晶体管芯片的外部边沿区域之间延伸并且保持将第一晶体管芯片关于第二晶体管芯片横向地间隔开的间隙的条形部区段来将第一晶体管芯片的第二连接端子与第二晶体管芯片的第一连接端子电耦合。

[0009] 根据又一示例性实施例,提供了一种制造封装的方法,其中方法包括:提供引线框类型芯片载体:在芯片载体上安装第一场效应晶体管芯片,第一场效应晶体管包括源极端

子、漏极端子和栅极端子;在芯片载体上安装第二场效应晶体管芯片,第二场效应晶体管包括源极端子、漏极端子和栅极端子;以及通过芯片载体将第一场效应晶体管芯片的漏极端子与第二场效应晶体管芯片的源极端子电耦合,从而在第一场效应晶体管芯片和第二场效应晶体管芯片之间保留电绝缘的间隙。

[0010] 根据又一示例性实施例,具有上面提到的特征的封装被用于汽车应用,特别是用于控制车辆中的电马达。

[0011] 根据示例性实施例,提供了一种封装,其中,两个晶体管芯片(其特别地可以是场效应晶体管芯片)被互连在(特别是引线框类型)芯片载体上,从而晶体管芯片中的一个的第二连接端子经由芯片载体(优选地经由芯片载体的外部条形部)与另一个晶体管芯片的第一连接端子连接,同时在晶体管芯片之间保留间隙。这样的设计允许以低的技术耗费进行制造并且节省相当大量的空间。在更具体的实施例中,第一场效应晶体管芯片的漏极端子可以经由芯片载体与另一场效应晶体管芯片的源极端子连接。通过采取这种措施,可以获得在封装的空间消耗和电流路径长度方面的有利布局。换言之,第一晶体管芯片的第二连接端子和第二晶体管芯片的第一连接端子可以经由芯片载体准直接地彼此耦合的事实允许保持提到的两个端子之间的电路径短。这造成半桥类型封装的低损耗和小的空间要求。作为结果,可以获得非常简单的封装,其能够以紧凑、成本有效并且简单的方式制造。通过这样的电路架构可以避免涉及附加阻抗的复杂的电流路径。

[0012] 下面将解释封装、电子器件、使用方法和制造方法的进一步的示例性实施例。

[0013] 在本申请的上下文中,术语"晶体管芯片"可以特别地表示可以以半导体技术体现并且可以具有至少一个集成晶体管的电子芯片。所提到的晶体管可以是场效应晶体管、绝缘栅双极晶体管或另外种类的双极晶体管。可能的是只有晶体管被实现在晶体管芯片上作为唯有的集成电路元件。然而还可能的是,二极管(其可以例如是通过像这样制造场效应晶体管而被内在地提供的,或者其可以是与晶体管分离地制造的)形成晶体管芯片的一部分。在又一个实施例中,至少一个进一步的有源的或无源的集成电路元件可以被形成在晶体管芯片上。

[0014] 在本申请的上下文中,术语"连接端子"可以特别地表示晶体管的使用信号可以在操作期间沿着其传播的典型地两个的端子中的一个。在场效应晶体管的示例中,所提到的连接端子是源极端子和漏极端子。在另一晶体管类型中,该两个连接端子可以是发射极和集电极。

[0015] 在本申请的上下文中,术语"控制端子"可以特别地表示晶体管的在其处可以施加控制信号——通过该控制信号可以控制、影响或启用/禁用在两个连接端子之间传播的电信号的特性——的端子。在场效应晶体管或IGBT的示例中,控制端子可以是栅极端子。在另外的双极晶体管配置中,控制端子可以是基极端子。

[0016] 在本申请的上下文中,术语"半桥"可以特别地表示由上部晶体管开关("高侧")和下部晶体管开关("低侧")构成的电路。例如,晶体管可以是MOSFET,即金属氧化物半导体场效应晶体管。晶体管可以是以共源共栅布置连接的。可以通过在控制端子中的每个处施加对应的电压波形来使两个晶体管开关彼此互补地(特别是具有非重叠的死区时间)接通和关断。想要的结果可以是在第一电势(诸如DC总线电压)和第二电势(诸如地)之间切换的在中点处的方波电压。两个晶体管可以是利用它们的连接端子的相互连接来互连的,从而可

以获得具有所实现的二极管特性的基于两个晶体管的开关。所提到的半桥配置可以被像这样使用或者被单独使用,或者可以与一个或多个进一步的半桥(或其它电路)组合以实现更复杂的电功能。例如,两个这样的半桥可以形成全桥。

[0017] 在本申请的上下文中,术语"芯片载体"可以特别地表示至少部分导电的结构,该至少部分导电的结构同时用作为用于晶体管芯片的安装基座并且还贡献于晶体管芯片之间的电互连。换句话说,芯片载体可以满足机械支承功能和电连接功能。

[0018] 在实施例中,芯片载体是引线框。这样的引线框可以是类似片状的金属结构,其可以被图案化以便形成:安装区段,用于安装晶体管芯片;一个或多个条形部区段,用于晶体管芯片的端子之间的电互连;以及引脚区段,用于当晶体管芯片被安装在引线框上时将封装电连接到电子环境。在实施例中,引线框可以是金属板(特别是由铜制成),其可以例如通过冲压或蚀刻而被图案化。将芯片载体形成为引线框是成本有效的并且是其中晶体管芯片的低欧姆连接可以与引线框的鲁棒支承能力组合的在机械上和在电气上高度地有利的配置。更进一步地,引线框可以贡献于封装的导热性,并且作为引线框的金属(特别是铜)材料的高导热性的结果而可以去除在晶体管芯片的在操作期间生成的热。

[0019] 在实施例中,第一晶体管芯片和第二晶体管芯片中的至少一个是从由场效应晶体管芯片和绝缘栅双极晶体管芯片组成的组中选择的。场效应晶体管配置以及绝缘栅双极晶体管配置这两者与高切换性能兼容,并且可以使封装呈现为针对诸如汽车应用的鲁棒的并且要求高的应用是高度地适合的。然而,一般地还有其它晶体管几何结构是可能的,例如任何其它类型的双极晶体管。

[0020] 在实施例中,第一晶体管芯片和第二晶体管芯片中的至少一个被配置用于利用竖向电流流动(特别是垂直于芯片载体在其中延伸的平面的电流流动)进行操作。对应地,源极端子和栅极端子可以例如位于场效应晶体管芯片的背对芯片载体的表面上,并且漏极端子可以位于场效应晶体管芯片的面对芯片载体的表面上。晶体管芯片被配置用于竖向电流流动可以使晶体管端子分别处在晶体管芯片的上主表面和下主表面这两者处。特别是在这样的竖向流动配置中,第一晶体管芯片的第二连接端子(特别是漏极端子)与第二晶体管芯片的第一连接端子(特别是源极端子)之间的准直接耦合是高度地有利的并且可以是利用极其短的电流路径实现的,并且因此具有非常简单的布局。当对应的晶体管芯片被安装在芯片载体上时,其下主表面处的一个或多个芯片端子可以直接地与导电芯片载体的安装表面机械地和电气地连接。相应的晶体管芯片的相对的上主表面上的一个或多个端子于是可以通过诸如夹片或接合布线的一个或多个连接元件与芯片载体电连接。由此,可能的是把来自对应于晶体管芯片的上主表面的平面的信号引导至芯片载体的位于下部的平面。

[0021] 在实施例中,第一晶体管芯片被配置为低侧开关并且第二晶体管芯片被配置为高侧开关。术语"低侧"晶体管芯片和"高侧"晶体管芯片涉及半桥应用的情形中的相应的晶体管芯片的功能。更具体地,低侧场效应晶体管芯片的漏极端子可以经由芯片载体与高侧场效应晶体管芯片的源极端子直接连接。

[0022] 在实施例中,第一晶体管芯片的第二连接端子对应于芯片载体的第一引脚,该第一引脚被定位为相邻于或者挨着与芯片载体的第二引脚,第二晶体管芯片的第一连接端子对应于该第二引脚。当芯片载体的上面提到的两个引脚——这两个引脚被分配给第一晶体管芯片的第二连接端子和第二晶体管芯片的第一连接端子——被直接彼此并置或者被并

排地定位而在它们之间没有附加的引脚时,可以获得在半桥配置的所提到的两个端子之间的极其短的电流路径。作为结果,可以由此获得具有高的电性能的非常低的欧姆的配置和非常紧凑的配置。

[0023] 在实施例中,条形部区段在第一引脚和第二引脚之间延伸。可能的是条形部区段实质上垂直于第一引脚和第二引脚的延伸而延伸。由此,高效地将第一晶体管芯片的第二连接端子与第二晶体管芯片的第一连接端子短路变得可能。条形部区段可以平行于并且沿着晶体管芯片被沿着其对准的方向延伸。这提供了非常短的电流路径,并且因此提供了紧凑的设计。水平地桥接晶体管芯片之间的间隙的耗费空间的连接元件可能变得可省却。

[0024] 在实施例中,第一晶体管芯片的第二连接端子与第二晶体管芯片的第一连接端子位于封装的不同的高度水平处。作为结果,第一晶体管芯片的第二连接端子与第二晶体管芯片的第一连接端子之间的电耦合可以竖向地桥接高度间隙并且因此可以部分地沿着竖向方向延伸。

[0025] 在实施例中,第一晶体管芯片和第二晶体管芯片被布置在芯片载体的两个分离的岛状部上。这两个金属岛状部之间的电连接可以是通过诸如夹片或接合布线的一个或多个附加的电连接元件来可靠地实现的。

[0026] 在实施例中,第一晶体管芯片和第二晶体管芯片之间的间隙没有连接元件(并且可以可选地也没有芯片载体材料)。作为省略对水平的芯片间间隙进行桥接的电连接元件的结果,非常大的芯片面积是可能的并且可以生产紧凑的封装。

[0027] 在实施例中,控制端子(特别是栅极端子)被布置为背对芯片载体。因此,控制端子可以竖向地突出超过芯片载体的安装表面。由此可以省略更复杂的设计,诸如倒装芯片配置或源极向下架构。

[0028] 在实施例中,连接端子中的两个(特别是源极端子)被布置为背对芯片载体并且连接端子中的另外两个(特别是漏极端子)被布置为面对芯片载体。

[0029] 在实施例中,第一晶体管芯片的第二连接端子与第二晶体管芯片的第二连接端子中的至少一个被直接电连接到芯片载体。换句话说,至少一个所提到的连接端子中的每个可以被连接到芯片载体而在它们之间没有附加的电路。例如,所提到的芯片端子可以被直接焊接或烧结或胶粘在芯片载体上。这保持整个封装小并且电流路径短。

[0030] 在实施例中,第一晶体管芯片的第一连接端子、第一晶体管芯片的控制端子、第二晶体管芯片的第一连接端子和第二晶体管芯片的控制端子中的至少一个被经由电连接元件间接地电连接到芯片载体。当芯片端子中的一部分被直接接合在芯片载体上时,并且当所提到的晶体管芯片是竖向电流流动组件时,剩余的其它芯片端子位于如下的平面中:该平面被关于芯片载体的安装平面竖向地移位或间隔开。在这样的状况下,用于把电信号从晶体管芯片的顶部主表面上的升高的平面引导回芯片载体的安装平面的一个或多个连接元件的实现是有利的。

[0031] 在实施例中,相应的电连接元件被配置为把在晶体管芯片中的一个的顶侧处的相应的端子与在同一晶体管芯片或晶体管芯片中的另一个的底侧处的相应的另一端子、和/或与芯片载体的引脚电连接。这样的实施例在具有竖向流动晶体管芯片——竖向流动晶体管芯片进而是用于高功率半导体应用的优选选择——的封装的配置中是有利的。

[0032] 在实施例中,电连接元件包括由夹片、接合布线和接合带组成的组中的一个。夹片

可以是三维地弯曲的板类型的连接元件,其具有要被连接到相应的晶体管芯片的上主表面和芯片载体的上主表面的两个平面区段,其中,所提到的两个平面区段是通过倾斜的连接区段互连的。作为这样的夹片的替换,可能的是使用接合布线或接合带,该接合布线或接合带是具有连接到相应的晶体管芯片的上主表面的一个端部部分并且具有被电连接到芯片载体的相对的另一端部部分的柔性导电布线或被构形成带的主体。

[0033] 在实施例中,第一晶体管芯片和第二晶体管芯片是实质上相同的半导体芯片。当半桥类型封装的两个晶体管芯片在形状、尺寸和电性能上相同时,提供仅一种类型的晶体管芯片以用于制造封装就足够了。这保持耗费低。然而,在替换的实施例中,可能的是两个晶体管芯片具有不同的大小和电性能,例如以考虑晶体管芯片的不同的占空比。

[0034] 在实施例中,封装包括部分地包封芯片载体、并且至少部分地包封第一晶体管芯片和第二晶体管芯片的包封物。所提到的包封物可以提供对所包封的晶体管芯片和芯片载体的被包封部分的机械保护和电隔离。例如,可能的是包封物被体现为覆盖全部所提到的元件的单个包封主体。替换地,可能的是为不同的晶体管芯片提供分离的包封主体。

[0035] 在实施例中,包封物是从由模制化合物和层压材料组成的组中选择的。对于通过模制进行包封而言,可以使用塑料材料或陶瓷材料。包封物可以包括环氧树脂材料。例如用于改进导热性的填充物颗粒(例如Si $0_2$ 、Al $_2$ 0 $_3$ 、Si $_3$ N $_4$ 、BN、AlN、金刚石等)可以被嵌入在包封物的基于环氧树脂的基质中。

[0036] 在实施例中,封装被配置为由引线封装和无引线封装组成的组中的一个。无引线封装例如在图9中示出。无引线封装实质上不包括超出包封物而从芯片载体延伸出来的引线。与此相反,引线封装(参见图10)包括芯片载体的延伸超出包封物并且例如被构形有鸥翼类型几何结构的引线。

[0037] 可以利用许多不同的封装类型来实现具有被连接以形成半桥的两个晶体管芯片——其中所提到的两个连接端子被经由芯片载体彼此耦合——的所述描述的电路架构。 更具体地,各种不同的封装架构与具有紧凑的布局和短的电路径的所描述的连接架构兼容。例如,PQFN封装类型与所描述的连接技术兼容,HS0F封装技术也与所描述的连接技术兼容。因此,所提到的布局设计可以被容易地适配于各种不同的封装技术。

[0038] 在实施例中,至少一个源极端子被分配到芯片载体的至少两个引脚。其中晶体管芯片中的一个的源极端子连接到多个分配的引脚的这样的配置允许增加封装的电流承载能力。因此,所描述的配置特别是对于高功率应用而言是高度地有利的。

[0039] 在实施例中,晶体管芯片被配置为功率半导体芯片。因此,晶体管芯片(诸如半导体芯片)可以被用于例如汽车领域中的功率应用,并且可以例如具有至少一个集成的绝缘栅双极晶体管(IGBT)和/或另外的类型(诸如MOSFET、JFET等)的至少一个晶体管和/或至少一个集成的二极管。这样的集成电路元件可以是例如采用硅技术制成的或者是基于宽带隙半导体(诸如碳化硅、氮化镓或硅上氮化镓)制成的。半导体功率芯片可以包括一个或多个场效应晶体管、二极管、逆变器电路、半桥、全桥、驱动器、逻辑电路、进一步的器件等。

[0040] 在实施例中,晶体管芯片可以形成电路功能而作为半桥、共源共栅电路、由彼此并联连接的场效应晶体管和双极晶体管构成的电路、或者功率半导体电路。因此,根据示例性实施例的封装架构与非常不同的电路构思的要求兼容。

[0041] 在实施例中,功率模块或封装被配置为由引线框连接的功率模块、晶体管外形

(T0) 电子组件、四方扁平无引线封装(QFN) 电子组件、小外形(S0) 电子组件、小外形晶体管(S0T) 电子组件和薄型更小尺寸封装(TS0P) 电子组件组成的组中的一个。因此,根据示例性实施例的模块或封装与标准封装构思完全兼容(特别是与标准T0封装构思完全兼容),这是高度地对用户方便的。在实施例中,封装被配置为功率模块,例如模制的功率模块。

[0042] 作为形成(多个)晶体管芯片或(多个)电子芯片的基础的衬底或晶片,可以使用半导体衬底,优选地硅衬底。替换地,可以提供氧化硅或另外的绝缘体衬底。还可能的是实现锗衬底或III-V族半导体材料。例如,可以采用GaN或SiC技术来实现示例性实施例。

[0043] 更进一步地,示例性实施例可以利用标准半导体处理技术,诸如适当的蚀刻技术(包括各向同性蚀刻技术和各向异性蚀刻技术,特别是等离子蚀刻、干法蚀刻、湿法蚀刻)、图案化技术(其可能涉及平版印刷掩模)、沉积技术(诸如化学气相沉积(CVD)、等离子增强化学气相沉积(PECVD)、原子层沉积(ALD)、溅射等)。

[0044] 从结合其中通过同样的参考标号表示同样的部分或元件的随附附图所作的随后的描述和所附权利要求,本发明的以上的和其它的目的、特征和优点将变得明显。

# 附图说明

[0045] 被包括以提供对示例性实施例的进一步的理解并且构成说明书的一部分的随附 附图图示示例性实施例。

[0046] 在附图中:

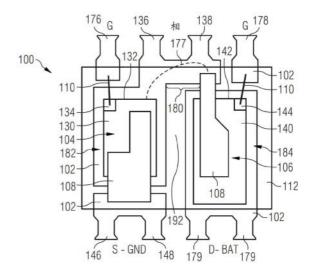

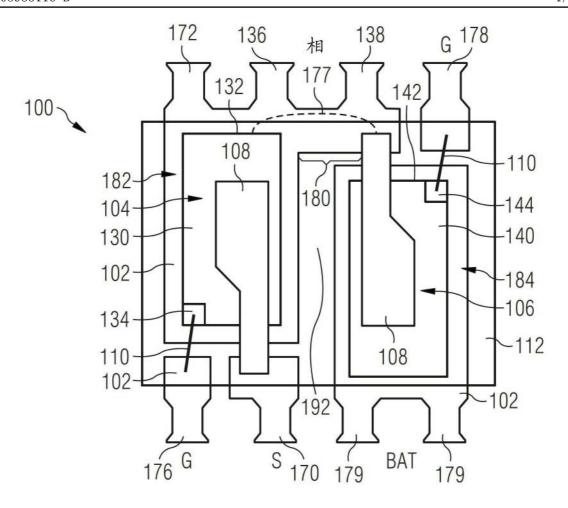

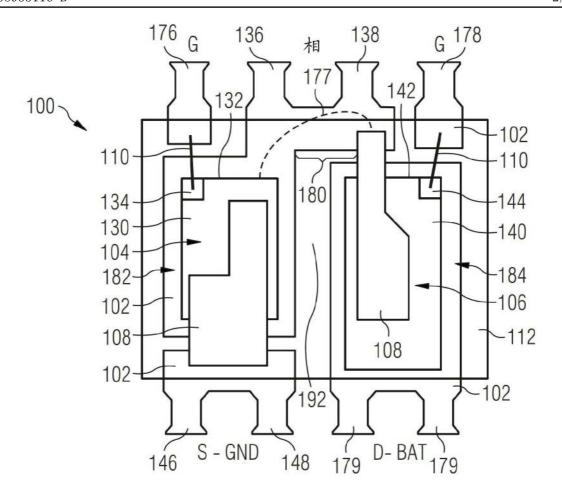

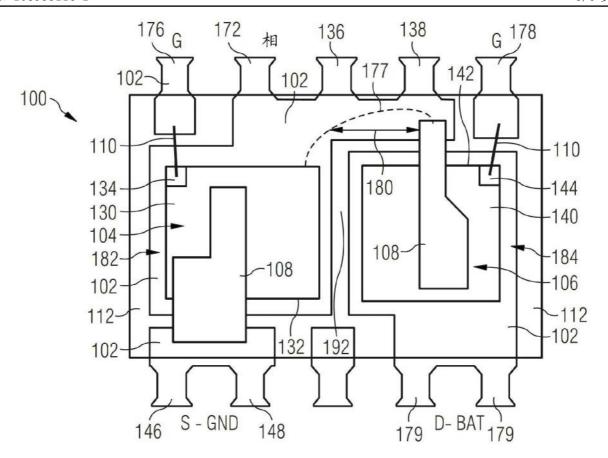

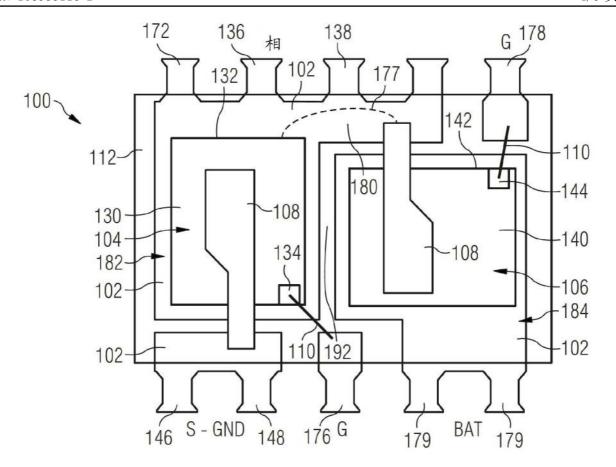

[0047] 图1到图4示出根据示例性实施例的封装的横截面视图。

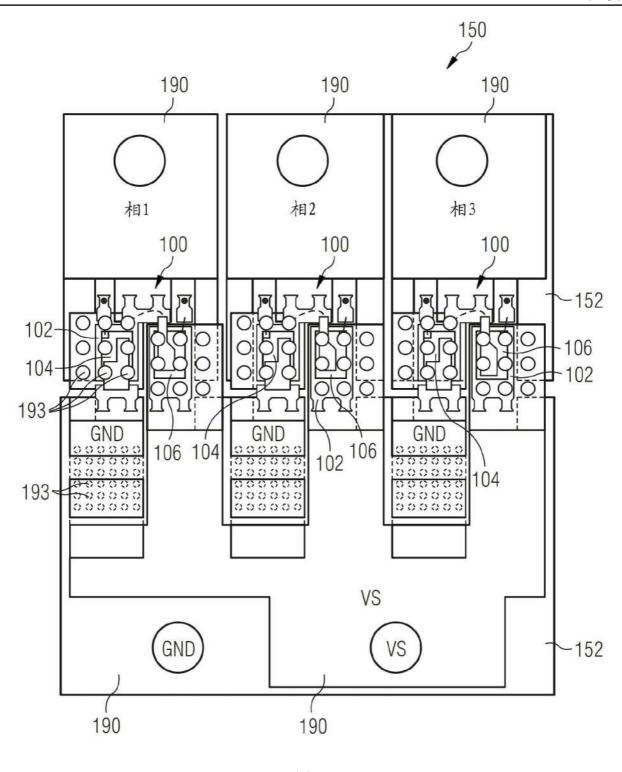

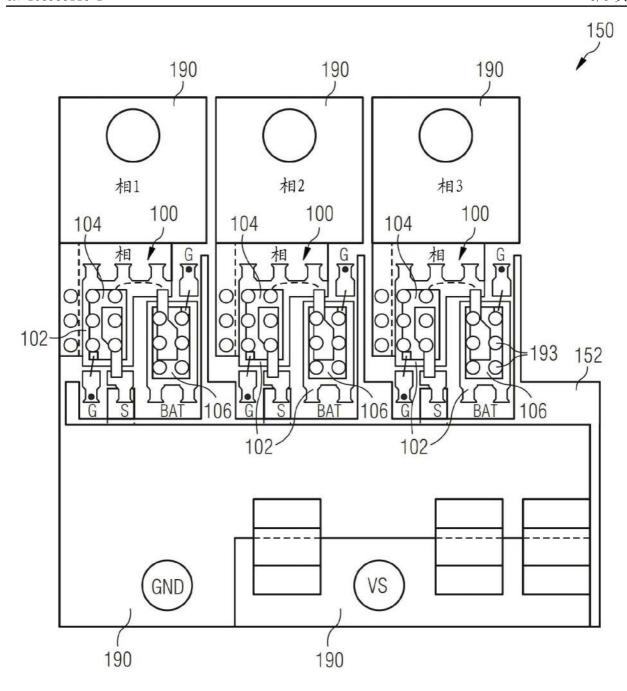

[0048] 图5和图6示出包括组装在板上的根据示例性实施例的多个封装的电子器件的横截面视图。

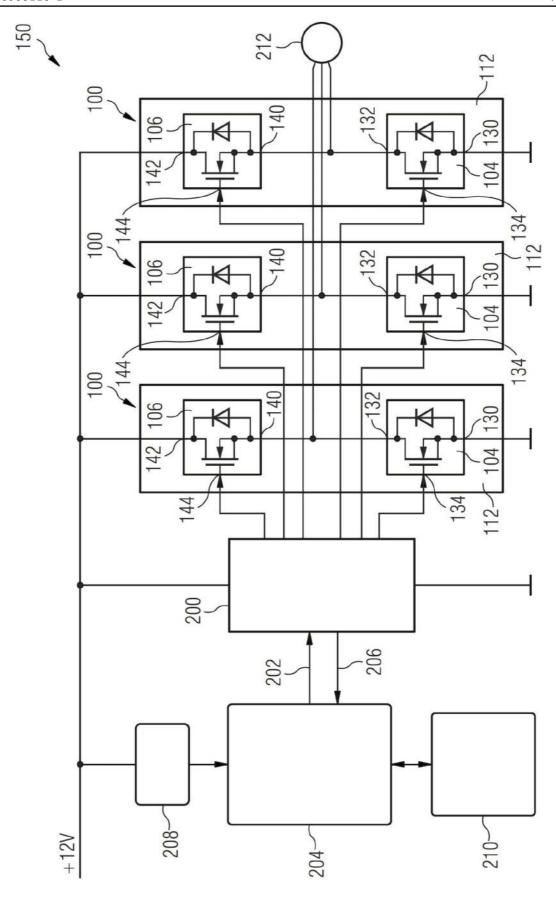

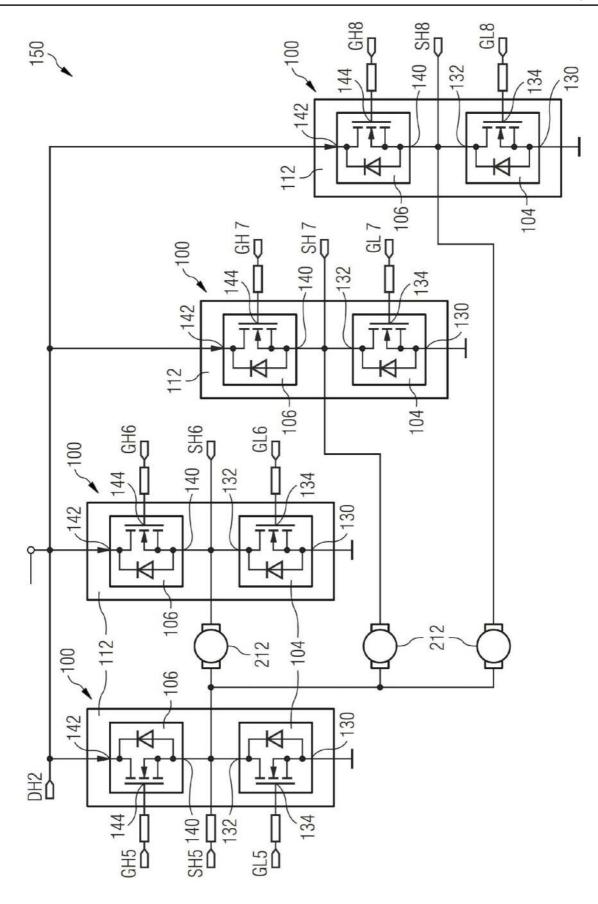

[0049] 图7示出根据示例性实施例的被配置为包括多个封装的三相马达桥的电子器件的电路图。

[0050] 图8示出根据示例性实施例的被配置为包括多个封装的级联多马达控制的电子器件的电路图。

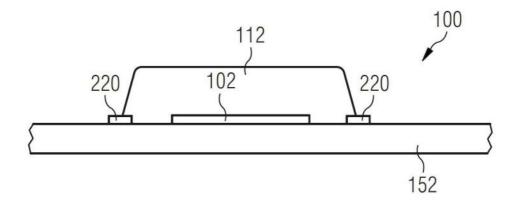

[0051] 图9示出根据示例性实施例的无引线封装的横截面视图。

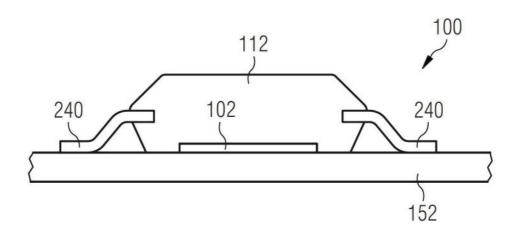

[0052] 图10示出根据示例性实施例的引线封装的横截面视图。

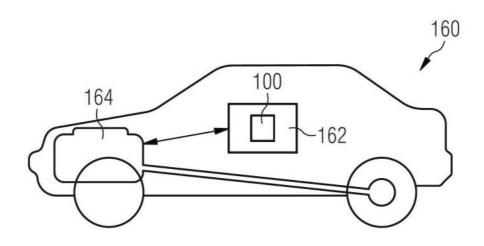

[0053] 图11示意性地图示根据示例性实施例的包括功率封装的车辆。

## 具体实施方式

[0054] 附图中示出的图示是示意性的。

[0055] 在进一步详细地描述进一步的示例性实施例之前,将基于已开发的示例性实施例 对本发明的一些基本的考虑进行概述。

[0056] 汽车中越来越多的马达被转换为所谓的无刷DC(直流)拓扑。这种拓扑简化了马达构造但是增加了电子控制耗费。然而,这种耗费也以改进的马达精度和效率的方式得益。

[0057] 常规的挑战是为用于上面的和其它的电子应用的半桥晶体管(诸如 MOSFET)寻求成本和空间高效的解决方案。

[0058] 常规地,典型地通过使用两个分立的MOSFET来设计半桥。这在板设计中并且针对 MOS的来源提供了高的灵活性。然而,在成本非常敏感的应用中,因为封装成本是占首要地

位的,所以分立的MOS可能不是最便宜的解决方案。另外在使用多于典型数量的三个相的应用(例如未能省却电子转向)中,分立的MOS可能不是恰当的解决方案,因为所要求的MOSFET的数量可能容易地超过12个或更多。

[0059] 常规的双MOS封装对于所描述的应用而言不是现实的选项,因为就对于高效率而言有利的低杂散电感来说在板水平上的布线不能使得呈现为是高效的。

[0060] 鉴于前述,示例性实施例提供了一种在封装内的晶体管芯片(特别是MOSFET芯片)的配置。在这种情形下,芯片载体(特别是引线框)可以被设计以使得以允许有利的板布局的方式布置三个电流承载引脚。示例性实施例的要点是半桥是通过特定的引线框设计形成的。这样的设计的优点是其简明性。不需要改变晶片技术,例如可以使用与常规的夹片封装中相同的技术。另外原则上可以通过对应的芯片载体(特别是引线框)设计来覆盖封装水平上的修改。因此,示例性实施例提供了支持小型化的在系统水平上的设计和效率改进。

[0061] 示例性实施例的有利特征是支持高效的适配于板的半桥设计的特定引线框设计。 对应的设计保持晶体管芯片和芯片载体之间的电路径短,由此改进电性能。同时,这种设计 使获得封装的紧凑配置是可能的。

[0062] 在参照各图的对示例性实施例的以下描述中,场效应晶体管被实现为第一晶体管芯片104和第二晶体管芯片106。因此,这些晶体管芯片104,106在下面将被表示为场效应晶体管芯片104,106。然而,本领域技术人员将理解的是,在下面描述的所有实施例也可以是利用其它晶体管类型(诸如绝缘栅双极晶体管)实现的。换句话说,所提到的场效应晶体管芯片104,106也可以被实现为不同技术的晶体管芯片。对应地,第一连接端子130,140在下面将被表示为源极端子130,140,并且第二连接端子132,142将被表示为漏极端子132,142,相应地,控制端子134,144将在下面被表示为栅极端子134,144,虽然它们可以被配置为诸如基极端子的其它类型的控制端子。

[0063] 图1至图4示出根据示例性实施例的封装100的横截面视图。

[0064] 图1和图2示出具有半桥配置的封装100的两个实施例,其中芯片载体102被体现为基于PQFN封装设计的占用面积的引线框。图1的实施例提供实现大的管芯大小的机会。图2的实施例提供非凡的高电流能力,因为两个引脚146,148可用于电流承载。

[0065] 图3和图4示出基于HS0F占用面积或封装设计的两个实施例。在高数量的引脚被提供在那里的情况下,电流可以总是由两个引脚来承载的。

[0066] 现在详细参照图1,示出了包括导电芯片载体102的封装100,导电芯片载体102在此被体现为由铜构成的引线框。作为对铜的替换,还可以使用铁作为用于引线框类型芯片载体102的材料。

[0067] 第一场效应晶体管芯片104(更具体地为MOSFET(即金属氧化物半导体场效应晶体管)芯片)被安装在芯片载体102上,并且在上侧上包括源极端子130,在下侧上包括漏极端子132并且在上侧上包括栅极端子 134。分离的第二场效应晶体管芯片106(在此也被体现为MOSFET芯片)也被安装在芯片载体102上,并且在上侧上包括源极端子140、在下侧上包括漏极端子142并且在上侧上包括栅极端子144。如可以从图1取得的那样,第一晶体管芯片104和第二晶体管芯片106被布置在芯片载体102的两个分离的岛状部上(参见参考标号182,184)。彼此相互电隔离的岛状部仅通过夹片108中的一个和芯片载体102连接。

[0068] 第一场效应晶体管芯片104和第二场效应晶体管芯片106彼此电互连以形成半桥

电路。就这种半桥布置来说,第一场效应晶体管芯片104被配置为低侧开关并且第二场效应晶体管芯片106被配置为高侧开关。

[0069] 有利地,第一场效应晶体管芯片104的漏极端子132通过或者经由芯片载体102并且附加地通过夹片108或另外的电连接元件而与第二场效应晶体管芯片106的源极端子140电耦合。经由芯片载体102的耦合是通过芯片载体102的在第一场效应晶体管芯片104的外部边沿区域和第二场效应晶体管芯片106的外部边沿区域之间延伸的条形部区段180来实现的。因为条形部区段180沿着外部边沿区域延伸而不是在芯片104,106之间延伸,所以保留了将第一场效应晶体管芯片104关于第二场效应晶体管芯片106横向地间隔开的非桥接间隙192。作为结果,在第一场效应晶体管芯片104和第二场效应晶体管芯片106之间保留电绝缘间隙192。第一场效应晶体管芯片104和第二场效应晶体管芯片106之间的间隙192没有诸如夹片108和接合布线110的连接元件。

[0070] 如可以从图1取得的那样,第一场效应晶体管芯片104的漏极端子132对应于芯片载体102的第一引脚136,第一引脚136被定位为直接相邻于(即在它们之间没有其它引脚)芯片载体102的第二引脚138,第二场效应晶体管芯片106的源极端子140对应于该第二引脚138。

[0071] 第一场效应晶体管芯片104和第二场效应晶体管芯片106这两者都被配置用于利 用竖向电流流动,即利用垂直于图1的纸面的电流传播方向进行操作。第一场效应晶体管芯 片104的漏极端子132和第二场效应晶体管芯片106 的漏极端子142这两者都被电连接到芯 片载体102。与晶体管芯片104,106的下主表面对应的漏极端子132,142被直接导电地安装 (特别是被导电地胶粘、焊接或烧结)在芯片载体102的上主表面上(即,在其之间没有任何 进一步的连接元件,诸如夹片、接合布线等)。与此相反,第一场效应晶体管芯片104的源极 端子 130、第一场效应晶体管芯片104的栅极端子134、第二场效应晶体管芯片106的源极端 子140和第二场效应晶体管芯片106的栅极端子144被布置在相应的晶体管芯片104,106的 上主表面上,并且经由电连接元件108,110电连接到芯片载体102。栅极端子134,144被布置 为背对芯片载体102的安装表面。另外,两个源极端子130,140被布置为背对芯片载体102。 与此相反,两个漏极端子132,142被布置为面对芯片载体102。经由电连接元件108,110来桥 接在一方面的端子130,134,140,144的平面与芯片载体102的上主表面之间的竖向间隙。因 此,电连接元件108,110中的每个被配置为把在晶体管芯片104,106之一的顶侧处的端子 130,134,140,144中的相应的一个与芯片载体102电连接。换句话说,源极端子130,140和栅 极端子134,144位于场效应晶体管芯片104,106的背对芯片载体102和漏极端子132,142的 表面上。后者位于场效应晶体管芯片104,106的面对芯片载体102的表面上。第一场效应晶 体管芯片104 的漏极端子132和第二场效应晶体管芯片106的源极端子140位于封装100的 不同的高度水平上。

[0072] 有利地,第一场效应晶体管芯片104和第二场效应晶体管芯片106在大小和形状方面是实质上相同的半导体芯片。这允许以低的耗费制造封装100。根据图1,晶体管芯片104,106可以被制造为相同的管芯,由此获得对称的配置。通过利用相同的芯片面积大小来体现晶体管芯片104,106,获得了可以附加地以低的耗费来制造的具有高度对称的电性能的组件封装100。

[0073] 包封物112,特别是模制化合物,被提供用于包封芯片载体102的一部分、整个第一

场效应晶体管芯片104和整个第二场效应晶体管芯片106。

[0074] 在根据图1的实施例中,示出了引线框类型芯片载体102的附加引脚。布置在第一场效应晶体管芯片104的顶侧上的源极端子130经由作为连接元件的夹片108与芯片载体102的源极引脚170连接。布置在第一场效应晶体管芯片104的底表面上的漏极端子132被直接安装(例如焊接或烧结)在引线框类型芯片载体102上并且因此被电连接到所提到的第一引脚136并且与进一步的相引脚 172电连接。第一场效应晶体管芯片104的栅极端子134被布置在其顶表面上并且利用进一步的连接元件(在此被体现为接合布线110)与栅极引脚176连接。利用"BAT"表示的引脚179指示电池连接。

[0075] 第二场效应晶体管芯片106的源极端子140被布置在所提到的该后者芯片的顶表面上,并且经由又一连接元件(在此还被体现为进一步的夹片 108)与第二引脚138电连接。第二场效应晶体管芯片106的漏极端子142被布置在第二场效应晶体管芯片106的下主表面上,并且被通过焊接或烧结连接直接接合在引线框类型芯片载体102上。第二场效应晶体管芯片106 的栅极端子144利用再一连接元件(在此被体现为进一步的接合布线110)与芯片载体102的进一步的栅极引脚178连接。因此,电连接元件108,110中的一些被体现为夹片108,电连接元件108,110中的另外一些被体现为接合布线110。

[0076] 在所示出的实施例中,芯片载体102 包括上面提到的条形部区段180,其在第一引脚136和第二引脚138之间并且与第一引脚136 和第二引脚138垂直地延伸,以由此将第一晶体管芯片104的漏极端子132与第二晶体管芯片106的源极端子140短路。高度有利地,芯片载体102的条形部区段180从芯片载体102的承载第一场效应晶体管芯片104的岛状部或安装区段182朝向芯片载体102 的其上安装有第二场效应晶体管芯片106 的另一个岛状部或安装区段184之上的夹片108延伸。这造成紧凑的设计和短的电连接路径(在图1中示意性地图示为虚线177)。如从图1可以取得的那样,与安装区段182,184相比,可以实现高的芯片容纳面积。

[0077] 参照图2中示出的优选实施例,源极端子130被分配到芯片载体102的两个引脚146,148,由此允许获得高的电流承载能力。更具体地,将源极端子130与芯片载体102电连接的夹片108被直接连接到芯片载体的引脚146,148这两者。为了进一步提升该区域中的电流承载能力并且使得电流流动均匀,所提到的夹片108在面对引脚146,148的夹片端部处被加宽。因此,根据图2的实施例与根据图1的实施例不同之处在于图2的实施例包括两个源极引脚146,148而不是如根据图1可用那样的一个源极引脚170。因此,在根据图2的实施例的情况下可以处理更大的电流。在低侧第一场效应晶体管芯片104上提供多个源极引脚146,148因此提供封装100作为整体的更高的电流承载能力的优点。

[0078] 图1的实施例和图2的实施例这两者可以例如以 $5\times6$   $mm^2$ 的尺寸来制造,例如采用 PQFN封装架构。

[0079] 与此相反,图3和图4的实施例涉及另一种封装技术,其可以被表示为HS0F封装构思。根据图3和图4的封装100的尺寸可以是7×8 mm²。如图2那样,作为在低侧晶体管芯片上提供两个源极引脚146,148的结果,根据图3和图4的实施例也具有高的电流承载能力。除此之外,如在图1和图2中那样,芯片载体102的在两个场效应晶体管芯片104,106之间的悬臂类型条形部区段180在上面在空间上并且在功能上确保紧密连接的漏极端子132和源极端子140的短的和对称的电流路径。

[0080] 替换的解决方案或者要求采用针对高侧MOS的源极向下配置的形式的复杂的前端技术——这对于技术开发而言意味着相当大的耗费。或者它们要求在封装水平上的倒装芯片方法,这增加制造复杂性和风险。由于可以在没有这些复杂性增加措施的情况下形成所描述的实施例,所以示例性实施例提供了简单和高效的布局。

[0081] 图5示出根据示例性实施例的包括多个封装100 的电子器件150的横截面视图。在所示出的实施例中,各封装100被电互连以提供引擎控制功能并且是在图2中示出的类型。电子器件150还可以包括支承各封装100的公共的安装基座152(诸如印刷电路板)。在图5中示出的电子器件150实现如上面所描述的三个半桥类型封装100。还可能的是将各封装 100容纳在公共的壳体中。这样的壳体可以具有中空的容纳体积或者可以是进一步的包封物,诸如模制化合物。根据图5的封装类型电子器件150中的系统因此允许提供复杂的电功能并且可以由用户处理为单个器件并且因此被以简单的方式处理。用户只须将用于连接根据图5 的电子器件150的外部连接焊盘190与电子外围设备连接。图5是用于PQFN半桥的示例的布局示例。在所示出的印刷电路板(PCB)布局中的小圆圈是过孔193,其可以被用于连接板中的不同的金属平面或者被用于增强热阻。

[0082] 图6示出根据另一示例性实施例的包括多个封装100的电子器件150的横截面视图。所示出的实施例不同于图5中示出的实施例之处在于,根据图6,封装100为图1中所示出类型。

[0083] 图7示出根据示例性实施例的被配置为包括多个封装100的三相马达桥的电子器件150的电路图。

[0084] 图7示出三相马达控制的电路。针对马达212的每个相,实现具有由在供给电压和相之间的高侧MOS(参见参考标号106)与在相和地之间的低侧MOS(参见参考标记104)构成的半桥MOS配置的封装100。图7因此示出具有连接到电池的三个高侧MOSFET芯片和连接到地的三个低侧MOSFET芯片的三相马达桥的配置。

[0085] 根据图7,供给电压(在此为+12V)可以被从电池供给到以三个封装100的形式实现的各个半桥。封装100可以例如被体现为图1至图4中所示那样。此外,预见如下的驱动器芯片200:其可以经由连接202从微控制器204接收脉冲宽度调制(PMW)信号。微控制器204可以经由连接206从驱动器芯片200接收诊断信号。此外,可以提供一个或多个供给芯片208以及收发器210(例如根据CAN/LIN通信技术而被体现)。

[0086] 图7中示出的三个封装100还可以被体现为如在图5或图6中示出的电子器件150。

[0087] 图8示出根据示例性实施例的被配置为包括多个封装100的级联多马达控制的电子器件150的电路图。

[0088] 因此,图8示出使用如可以在汽车动力座椅控制中使用或者可以针对折叶控制而在汽车加热、通风和空调(HVAC)系统中使用的级联桥拓扑的多个马达控制。每个马达212是通过两个半桥(其可以被表示为H 桥配置)来操作的。左手侧半桥是针对所有马达212独有的,而在右手侧上存在用于每一马达212的分离的半桥。对于低功率至中等功率的电马达212而言,具有被体现为图1至图4中所示那样的封装100的图8的电路是非常高效的解决方案。图8因此示出级联多马达控制的示例,其中左侧半桥被针对所有马达212一起来使用,同时在右手侧上每个马达212具有其自己的半桥。

[0089] 根据图8的级联多引擎控制架构实现了四个封装100,其中的每个可以是如参照图

1至图4所示出和描述那样而体现的。可以由根据图8的电路架构来控制三个马达212或引擎。

[0090] 图9示出根据示例性实施例的无引线封装100的横截面视图。

[0091] 在根据图9的无引线配置中,实质上没有引线延伸超出包封物112。仅提供了将封装100与诸如印刷电路板(PCB)的安装基座152连接的小的连接结构220。连接结构220可以例如通过焊接或烧结与安装基座152的焊盘连接。场效应晶体管芯片104,106被嵌入在包封物112内,并且因此根据图9是不可见的。

[0092] 图10示出根据另一示例性实施例的引线封装100的横截面视图。

[0093] 根据图10的引线封装100不同于根据图9的无引线封装100之处在于,根据图10,芯片载体102的引线240延伸超出包封物112。引线240用于使封装100与安装基座152电接触。在所示出的实施例中,暴露的引线240被以鸥翼配置进行配置,鸥翼配置具有使得能够例如在热负载的情况下进行弹性平衡的一定的弹性。

[0094] 图11示意性地图示根据示例性实施例的包括功率封装100的车辆160。更具体地,功率封装100可以形成对电马达/电池块164的操作进行控制的控制块162的一部分。因此,根据示例性实施例的封装100或功率模块可以被用于汽车应用。

[0095] 应当注意的是,术语"包括"不排除其它的元件或特征,并且"一"或"一个"也不排除多个。另外,与不同的实施例关联地描述的元件可以被组合。还应当注意的是,参考标记不应当被解释为对权利要求的范围进行限制。此外,本申请的范围不意图被限制于说明书中所描述的处理、机器、制造、物质组成、手段、方法和步骤的特定实施例。相应地,所附权利要求意图将这样的处理、机器、制造、物质组成、手段、方法或步骤包括在其范围内。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 9

图 10

图 11