## (19)**日本国特許庁(JP)**

# (12) 公開特許公報(A)

(11)公開番号

特開2023-22141 (P2023-22141A)

(43)公開日 令和5年2月14日(2023.2.14)

|                                       | 類                | FΙ            |                    |                    |       |        |

|---------------------------------------|------------------|---------------|--------------------|--------------------|-------|--------|

| H 0 1 L                               | 29/78 (2006.01)  | H 0 1 L       | 29/78              | 6 5 7 D            |       |        |

| H 0 1 L                               | 29/872 (2006.01) | H 0 1 L       | 29/78              | 6 5 3 A            |       |        |

| H 0 1 L                               | 29/12 (2006.01)  | H 0 1 L       | 29/78              | 6 5 2 J            |       |        |

| H 0 1 L                               | 29/06 (2006.01)  | H 0 1 L       | 29/78              | 6 5 2 M            |       |        |

| H 0 1 L                               | 29/861 (2006.01) | H 0 1 L       | 29/86              | 3 0 1 F            |       |        |

|                                       |                  | 審査請求有         | 請求項の数              | 21 OL (            | 全70頁) | 最終頁に続く |

| (21)出願番号                              | 特願2022-185920(l  | P2022-185920) | (71)出願人            | 000116024          |       |        |

| (22)出願日                               | 令和4年11月21日(2     | 022.11.21)    | ローム株式会社            |                    |       |        |

| (62)分割の表示 特願2020-502079(P2020-502079  |                  |               | 京都府京都市右京区西院溝崎町21番地 |                    |       |        |

|                                       | )の分割             |               | (74)代理人            | 100105957          |       |        |

| 原出願日                                  | 平成31年1月17日(2     | 019.1.17)     |                    | 弁理士 恩田             | 誠     |        |

| (31)優先権主張番号 特願2018-31148(P2018-31148) |                  |               | (74)代理人            | 100068755          |       |        |

| (32)優先日                               | 平成30年2月23日(2     | 018.2.23)     |                    | 弁理士 恩田             | 博宣    |        |

| (33)優先権主張国・地域又は機関                     |                  |               | (72)発明者            | 大嶽 浩隆              |       |        |

| 日本国(JP)                               |                  |               |                    | 京都府京都市右京区西院溝崎町21番地 |       |        |

|                                       |                  |               | ローム株式会社内           |                    |       |        |

|                                       |                  |               |                    |                    |       |        |

|                                       |                  |               |                    |                    |       |        |

|                                       |                  |               |                    |                    |       |        |

|                                       |                  |               |                    |                    |       |        |

|                                       |                  |               |                    |                    |       |        |

|                                       |                  |               |                    |                    |       |        |

## (54)【発明の名称】 半導体装置及びパワーモジュール

## (57)【要約】

【課題】ゲート・ソース間電圧の変動を低減すること。 【解決手段】半導体装置は、ワイドギャップ半導体からなり、ドレイン端子11d、ソース端子11g、及びゲート端子11gを有する上側スイッチング素子11と、ドレイン端子11dがカソードに接続されるように設けられたワイドギャップ半導体からなる上側ダイオード71と、ソース端子11gにアノードが接続され、ドレイン端子11dにカソードが接続されているボディダイオード11aと、を備える。上側ダイオード71の順方向しきい値電圧がボディダイオード11aの順方向しきい値電圧よりも低い。

【選択図】図17

## 【特許請求の範囲】

### 【請求項1】

ワイドギャップ半導体からなり、第1端子、第2端子、及び制御端子を有するスイッチング素子と、

前記第1端子と前記第2端子との間において前記第1端子がカソードに接続されるように設けられたワイドギャップ半導体からなるショットキーバリアダイオードと、

前記第2端子にアノードが接続され、前記第1端子にカソードが接続されているダイオードと、

を備え、

前記ショットキーバリアダイオードの順方向しきい値電圧が前記ダイオードの順方向しきい値電圧よりも低い、半導体装置。

【請求項2】

前記ダイオードは、前記スイッチング素子のボディダイオードであり、

前記ショットキーバリアダイオード及び前記スイッチング素子は、同一チップに形成されている

請求項1に記載の半導体装置。

### 【請求項3】

前記ショットキーバリアダイオードは、複数設けられており、

前記複数のショットキーバリアダイオードは、平面視で所定間隔ごとに配置されている 請求項 2 に記載の半導体装置。

【請求項4】

前記スイッチング素子は、複数設けられており、

前記複数のショットキーバリアダイオードの配列方向において、前記ショットキーバリアダイオードと前記スイッチング素子とは交互に配置されている

請求項3に記載の半導体装置。

## 【請求項5】

前記ショットキーバリアダイオードと前記スイッチング素子との配列方向において、前記ショットキーバリアダイオードの大きさは、前記スイッチング素子の大きさよりも大きい

請求項4に記載の半導体装置。

## 【請求項6】

前記ダイオードは、前記スイッチング素子のボディダイオードであり、

前記ショットキーバリアダイオード及び前記スイッチング素子は、別体として設けられている

請求項1に記載の半導体装置。

## 【請求項7】

前記スイッチング素子は、プレーナゲート型VDMOSETである

請求項1~6のいずれか一項に記載の半導体装置。

## 【請求項8】

前記ショットキーバリアダイオード及び前記スイッチング素子の前記ワイドギャップ半 導体は、SiCを用いた半導体である

請求項1~7のいずれか一項に記載の半導体装置。

### 【請求項9】

前記スイッチング素子は、

前記第1端子としての第1上側端子、前記第2端子としての第2上側端子、及び前記制御端子としての上側制御端子を有する上側スイッチング素子と、

前記第1端子としての第1下側端子、前記第2端子としての第2下側端子、及び前記制御端子としての下側制御端子を有する下側スイッチング素子と、

を含み、

前記ショットキーバリアダイオードは、

10

20

30

40

前記第1上側端子と前記第2上側端子との間において前記第1上側端子がカソードに接続されるように設けられた上側ショットキーバリアダイオードと、

前記第1下側端子と前記第2下側端子との間において前記第1下側端子がカソードに接続されるように設けられた下側ショットキーバリアダイオードと、

を含み、

前記ダイオードは、

前記第2上側端子にアノードが接続され、前記第1上側端子にカソードが接続されている上側ボディダイオードと、

前記第2下側端子にアノードが接続され、前記第1下側端子にカソードが接続されている下側ボディダイオードと、

を含み、

前記上側ショットキーバリアダイオード及び前記下側ショットキーバリアダイオードの順方向しきい値電圧が前記上側ボディダイオード及び前記下側ボディダイオードの順方向しきい値電圧よりも低い、請求項1に記載の半導体装置。

### 【 請 求 項 1 0 】

前記上側ショットキーバリアダイオード及び前記上側スイッチング素子の前記ワイドギャップ半導体は、SiCを用いた半導体であり、

前記下側ショットキーバリアダイオード及び前記下側スイッチング素子の前記ワイドギャップ半導体は、SiCを用いた半導体である

請求項9に記載の半導体装置。

### 【請求項11】

ワイドギャップ半導体からなり、第1端子、第2端子、及び制御端子を有するスイッチング素子と、

前記第1端子と前記第2端子との間において前記第1端子がカソードに接続されるように設けられたワイドギャップ半導体からなるショットキーバリアダイオードと、

前記第2端子にアノードが接続され、前記第1端子にカソードが接続されているダイオードと、

前記スイッチング素子及び前記ショットキーバリアダイオードが実装されている基板と

前記基板の少なくとも一部と前記スイッチング素子と前記ショットキーバリアダイオードと前記ダイオードとを封止する封止樹脂と、

を備え、

前記ショットキーバリアダイオードの順方向しきい値電圧が前記ダイオードの順方向し きい値電圧よりも低い、パワーモジュール。

## 【請求項12】

前記ショットキーバリアダイオード及び前記スイッチング素子は、それぞれ複数設けられ、かつ前記基板上に一列に並ぶように配置され、

前記複数のショットキーバリアダイオードは並列に接続されており、

前記複数のスイッチング素子は並列に接続されている

請求項11に記載のパワーモジュール。

### 【請求項13】

前記ダイオードは、前記スイッチング素子のボディダイオードであり、

前記ショットキーバリアダイオード及び前記スイッチング素子は、交互に配列されてい 3

請求項11又は12に記載のパワーモジュール。

### 【請求項14】

ワイドギャップ半導体からなり、第1上側端子、第2上側端子、及び上側制御端子を有するとともに、前記第2上側端子にアノードが接続され、前記第1上側端子にカソードが接続されている上側ボディダイオードを有し、互いに並列に接続された複数の上側スイッチング素子と、

20

10

30

ワイドギャップ半導体からなり、第1下側端子、第2下側端子、及び下側制御端子を有 するとともに、前記第2下側端子にアノードが接続され、前記第1下側端子にカソードが 接続されている下側ボディダイオードを有し、互いに並列に接続された複数の下側スイッ チング素子と、

ワイドギャップ半導体からなり、アノードが前記第2上側端子に接続され、カソードが 前記第1上側端子に接続され、互いに並列に接続された複数の上側ショットキーバリアダ

ワイドギャップ半導体からなり、アノードが前記第2下側端子に接続され、カソードが 前 記 第 1 下 側 端 子 に 接 続 さ れ 、 互 い に 並 列 に 接 続 さ れ た 複 数 の 下 側 ショ ッ ト キ ー バ リ ア ダ イオードと、

前記上側スイッチング素子、前記下側スイッチング素子、前記上側ショットキーバリア ダイオード、及び前記下側ショットキーバリアダイオードが実装された基板と、

前 記 基 板 の 少 な く と も 一 部 と 前 記 上 側 ス イ ッ チ ン グ 素 子 と 前 記 下 側 ス イ ッ チ ン グ 素 子 と 前記上側ショットキーバリアダイオードと前記下側ショットキーバリアダイオードとを封 止する封止樹脂と、

を備え、

前 記 上 側 ショットキーバリアダイオード及び前記下 側 ショットキーバリアダイオードの それぞれの順方向しきい値電圧は、前記上側ボディダイオード及び前記下側ボディダイオ ードのそれぞれの順方向しきい値電圧よりも低い、パワーモジュール。

### 【請求項15】

前記基板は、前記上側スイッチング素子及び前記上側ショットキーバリアダイオードが 表 面 に 実 装 さ れ た 第 1 基 板 と 、 前 記 下 側 ス イ ッ チ ン グ 素 子 及 び 前 記 下 側 シ ョ ッ ト キ ー バ リ アダイオードが表面に実装された第2基板とを有し、

前 記 パ ワ ー モ ジ ュ ー ル の 平 面 視 に お け る 第 1 方 向 に お い て 前 記 第 1 基 板 と 前 記 第 2 基 板 とが並べられ、

前 記 第 1 基 板 及 び 前 記 第 2 基 板 は 、 前 記 パ ワ ー モ ジ ュ ー ル の 平 面 視 に お い て 前 記 第 1 方 向と直交する第2方向が長手方向となる長方形状に形成され、

前 記 複 数 の 上 側 ス イ ッ チ ン グ 素 子 及 び 前 記 複 数 の 上 側 シ ョ ッ ト キ ー バ リ ア ダ イ オ ー ド は 、前記第2方向において互いに離間して前記第1基板に実装されており、

前 記 複 数 の 下 側 ス イ ッ チ ン グ 素 子 及 び 前 記 複 数 の 下 側 シ ョ ッ ト キ ー バ リ ア ダ イ オ ー ド は 、前記第2方向において互いに離間して前記第2基板に実装されており、

前 記 複 数 の 上 側 ス イ ッ チ ン グ 素 子 及 び 前 記 複 数 の 下 側 ス イ ッ チ ン グ 素 子 は 前 記 第 2 方 向 において交互に配置されており、

前 記 パ ワ ー モ ジ ュ ー ル は 、 そ の 厚 さ 方 向 に お い て 前 記 第 1 基 板 と 間 隔 を 空 け て 対 向 す る 入力端子部材を有し、

前記入力端子部材は、複数の接続部を有し、

前記複数の接続部は、前記複数の上側スイッチング素子の前記第2方向の間に配置され 、前記第1方向において前記複数の下側スイッチング素子と対向しており、

前記複数の上側スイッチング素子の前記第2上側端子はそれぞれ、上側電力用接続部材 により前記第2基板に電気的に接続されており、

前 記 複 数 の 下 側 ス イ ッ チ ン グ 素 子 の 前 記 第 2 下 側 端 子 は そ れ ぞ れ 、 前 記 第 1 方 向 に お い て前記下側スイッチング素子と対向する接続部に下側電力用接続部材により電気的に接続 されている

請求項14に記載のパワーモジュール。

## 【請求項16】

前 記 複 数 の 上 側 シ ョ ッ ト キ ー バ リ ア ダ イ オ ー ド 及 び 前 記 複 数 の 下 側 シ ョ ッ ト キ ー バ リ ア ダイオードは前記第2方向において1つずつ交互に配置されており、

前 記 複 数 の 接 続 部 は 、 前 記 複 数 の 上 側 ショット キー バ リ ア ダ イ オー ド の 前 記 第 2 方 向 の 間に配置され、前記第1方向において前記複数の下側ショットキーバリアダイオードと対 向しており、

10

20

30

40

前記複数の上側ショットキーバリアダイオードのアノードはそれぞれ、上側ダイオード 用接続部材により前記第2基板に電気的に接続されており、

前記複数の下側ショットキーバリアダイオードのアノードはそれぞれ、前記第1方向において前記下側ショットキーバリアダイオードと対向する接続部に下側ダイオード用接続部材により電気的に接続されている

請求項15に記載のパワーモジュール。

#### 【請求項17】

前記第1基板は、上側制御配線部を有し、

前記第2基板は、下側制御配線部を有し、

前記上側スイッチング素子は、上側制御部材により前記上側制御端子と前記上側制御配線部とが接続されるものであり、

前記下側スイッチング素子は、下側制御部材により前記下側制御端子と前記下側制御配線部とが接続されるものであり、

前記上側スイッチング素子、前記上側ショットキーバリアダイオード、前記下側スイッチング素子、及び前記下側ショットキーバリアダイオードのそれぞれは、前記上側制御配線部と前記下側制御配線部との前記第1方向の間に配置されており、

前記上側制御配線部及び前記下側制御配線部は、前記第2方向に延びている請求項16に記載のパワーモジュール。

## 【請求項18】

前記第1基板及び前記第2基板のそれぞれは、グラファイト基板を有する請求項15~17のいずれか一項に記載のパワーモジュール。

### 【請求項19】

前記第1基板は、前記第2方向における前記第1基板の熱伝導性が前記第1方向における前記第1基板の熱伝導性よりも低くなるように構成されており、

前記第2基板は、前記第2方向における前記第2基板の熱伝導性が前記第1方向における前記第2基板の熱伝導性よりも低くなるように構成されている

請求項18に記載のパワーモジュール。

### 【請求項20】

前記上側ショットキーバリアダイオードは前記上側スイッチング素子に内蔵されており

前記下側ショットキーバリアダイオードは前記下側スイッチング素子に内蔵されており

前記上側スイッチング素子及び前記下側スイッチング素子はそれぞれ、複数個設けられ

前記基板は、グラファイト基板を有し、

前記グラファイト基板は、前記複数の上側スイッチング素子が表面に実装された第1基板と、前記複数の下側スイッチング素子が表面に実装された第2基板とを有し、

前記パワーモジュールの第1方向において前記第1基板と前記第2基板とが並べられ、前記第1基板及び前記第2基板は、前記パワーモジュールの平面視において前記第1方向と直交する第2方向が長手方向となる長方形状に形成されており、

前記複数の上側スイッチング素子及び前記複数の下側スイッチング素子は前記第2方向において交互に配置されており、

前記パワーモジュールは、その厚さ方向において前記第1基板と間隔を空けて対向する 入力端子部材を有し、

前記入力端子部材は、複数の接続部を有し、

前記複数の接続部は、前記複数の上側スイッチング素子の前記第2方向の間に配置され、前記第1方向において前記複数の下側スイッチング素子と対向しており、

前記複数の上側スイッチング素子の前記第2上側端子はそれぞれ、上側電力用接続部材により前記第2基板に電気的に接続されており、

前記複数の下側スイッチング素子の前記第2下側端子はそれぞれ、前記第1方向におい

20

10

30

40

て前記下側スイッチング素子と対向する接続部に下側電力用接続部材により電気的に接続されている

請求項14に記載のパワーモジュール。

#### 【請求項21】

前記第1基板において前記複数の上側スイッチング素子及び前記複数の上側ショットキーバリアダイオードが配置される表面には第1表面側金属層が設けられており、

前記第1基板において前記第1基板の表面とは反対側の裏面には第1裏面側金属層が設けられており、

前記第2基板において前記複数の下側スイッチング素子及び前記複数の下側ショットキーバリアダイオードが配置される表面には第2表面側金属層が設けられており、

前記第2基板において前記第2基板の表面とは反対側の裏面には第2裏面側金属層が設けられている

請求項20に記載のパワーモジュール。

【発明の詳細な説明】

【技術分野】

$[0 \ 0 \ 0 \ 1]$

本発明は、半導体装置及びパワーモジュールに関する。

【背景技術】

[0002]

スイッチング素子からなるハーフブリッジ回路において、デッドタイム状態から例えば下側スイッチング素子がオンするとき、下側スイッチング素子のドレイン・ソース間電圧 V d s に起因する上側スイッチング素子のドレイン・ソース間電圧 V d s に伴い上側スイッチング素子のゲート・ソース間電圧 V g s が変動してゲート誤オンが生じる場合がある (例えば、特許文献 1 参照)。

【先行技術文献】

【特許文献】

[0003]

【特許文献1】特開2013-99133号公報

【発明の概要】

【発明が解決しようとする課題】

[0004]

近年、シリコン(Si)を用いた半導体よりも高耐圧、低オン抵抗、高速スイッチング、及び高温動作に対応したシリコンカーバイド(SiC:Silicon Carbide)等を用いたワイドギャップ半導体の研究、及び製造販売が進められている。このようなワイドギャップ半導体は、低電流領域におけるプラトー電圧(ミラー効果領域におけるゲート・ソース間電圧)が低く、ゲート・ドレイン間容量 C g d に対するゲート・ソース間容量 C g d に対するゲート・ソース間容量 C g d に対するゲート・ソース間電圧 V d s の時間変化 d V d s / d t が、ゲート・ドレイン間容量 C g d を介してゲート・ソース間電圧 V g s に及ぼす影響が大きい。このため、ゲート・ソース間電圧 V g s の変動が大きくなるので、その電圧サージが正方向に掛かれば、スイッチング素子がオフ状態にもかかわらずオンしてしまう、所謂セルフターンオンし易くなり、ハーフブリッジの上下に貫通電流が流れる。またその電圧サージが負方向に掛かれば、負側のゲート電圧定格を超過するおそれがある。SiC M O S F E T (Metal-Oxide-Semiconductor Field Effect Transistor)では、ゲートしきい値シフトの関係から負側のゲート電圧定格が小さく設定されていることが多く、この現象は特に問題になり易い。

[0005]

本発明の目的は、ゲート・ソース間電圧の変動を低減することができる半導体装置及びパワーモジュールを提供することにある。

【課題を解決するための手段】

[0006]

20

10

30

40

上記課題を解決する半導体装置は、ワイドギャップ半導体からなり、第1端子、第2端子、及び制御端子を有するスイッチング素子と、前記第1端子と前記第2端子との間において前記第1端子がカソードに接続されるように設けられたワイドギャップ半導体からなるショットキーバリアダイオードと、前記第2端子にアノードが接続され、前記第1端子にカソードが接続されているダイオードと、を備え、前記ショットキーバリアダイオードの順方向しきい値電圧が前記ダイオードの順方向しきい値電圧よりも低い。

### [0007]

また、上記課題を解決するパワーモジュールは、ワイドギャップ半導体からなり、第1端子、第2端子、及び制御端子を有するスイッチング素子と、前記第1端子と前記第2端子との間において前記第1端子がカソードに接続されるように設けられたワイドギャップ半導体からなるショットキーバリアダイオードと、前記第2端子にアノードが接続され、前記第1端子にカソードが接続されているダイオードと、前記スイッチング素子及び前記ショットキーバリアダイオードと前記ダイオードとを封止するお上樹脂と、を備え、前記ショットキーバリアダイオードの順方向しきい値電圧が前記ダイオードの順方向しきい値電圧よりも低い。

### [00008]

また、上記課題を解決するパワーモジュールは、ワイドギャップ半導体からなり、第1 上側端子、第2上側端子、及び上側制御端子を有するとともに、前記第2上側端子にアノ ードが接続され、前記第1上側端子にカソードが接続されている上側ボディダイオードを 有し、互いに並列接続された複数の上側スイッチング素子と、ワイドギャップ半導体から なり、第1下側端子、第2下側端子、及び下側制御端子を有するとともに、前記第2下側 端子にアノードが接続され、前記第1下側端子にカソードが接続されている下側ボディダ イオードを有し、互いに並列接続された複数の下側スイッチング素子と、ワイドギャップ 半 導 体 か ら な り 、 ア ノ ー ド が 前 記 第 2 上 側 端 子 に 接 続 さ れ 、 カ ソ ー ド が 前 記 第 1 上 側 端 子 に接続され、互いに並列接続された複数の上側ショットキーバリアダイオードと、ワイド ギャップ半導体からなり、アノードが前記第2下側端子に接続され、カソードが前記第1 下側端子に接続され、互いに並列接続された複数の下側ショットキーバリアダイオードと 、 前 記 上 側 ス イ ッ チ ン グ 素 子 、 前 記 下 側 ス イ ッ チ ン グ 素 子 、 前 記 上 側 シ ョ ッ ト キ ー バ リ ア ダイオード、及び前記下側ショットキーバリアダイオードが実装された基板と、前記基板 の少なくとも一部と前記上側スイッチング素子と前記下側スイッチング素子と前記上側シ ョットキーバリアダイオードと前記下側ショットキーバリアダイオードとを封止する封止 樹脂と、を備え、前記上側ショットキーバリアダイオード及び前記下側ショットキーバリ アダイオードのそれぞれの順方向しきい値電圧は、前記上側ボディダイオード及び前記下 側ボディダイオードのそれぞれの順方向しきい値電圧よりも低い。

## 【発明の効果】

[0009]

上記半導体装置及びパワーモジュールによれば、ゲート・ソース間電圧の変動を低減することができる。

【図面の簡単な説明】

[ 0 0 1 0 ]

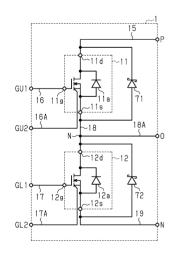

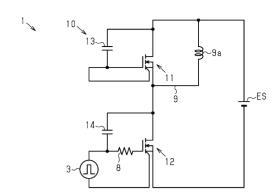

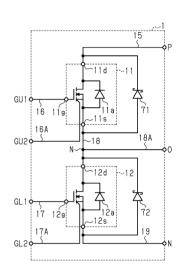

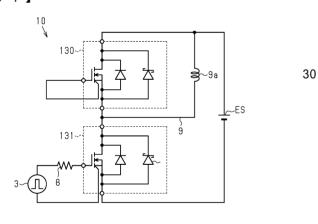

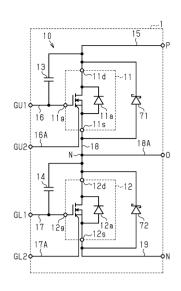

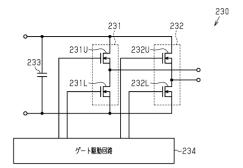

【図1】第1実施形態の半導体装置を有するパワーモジュール及びその駆動回路を示す模式回路図。

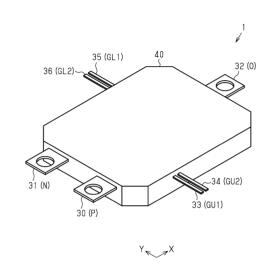

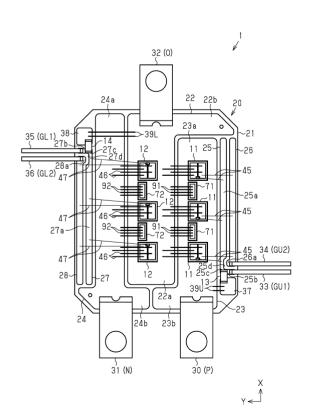

- 【図2】パワーモジュールの斜視図。

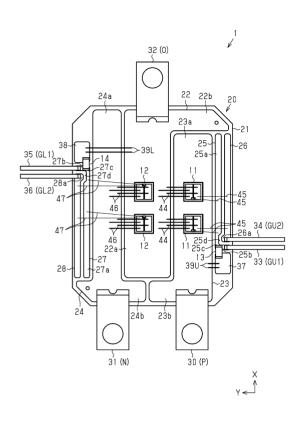

- 【図3】パワーモジュールの内部構成を示す平面図。

- 【図4】パワーモジュールの底面図。

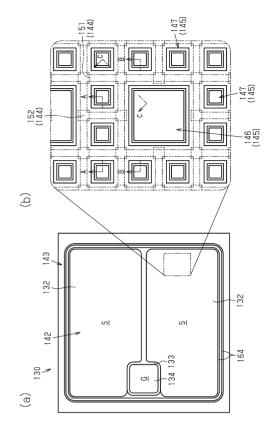

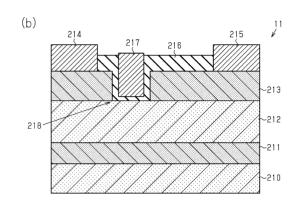

- 【図5】(a)はスイッチング素子の平面図、(b)は(a)の一部の内部拡大図。

- 【図6】スイッチング素子の断面図。

- 【図7】比較例のパワーモジュールの応用を示す模式回路図。

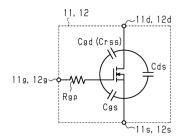

- 【 図 8 】 上 側 ス イ ッ チ ン グ 素 子 及 び 下 側 ス イ ッ チ ン グ 素 子 の 寄 生 容 量 及 び 寄 生 抵 抗 を 示 す

10

20

30

模式図。

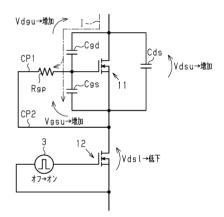

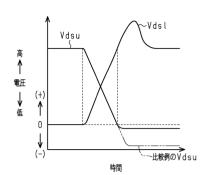

【図9】下側スイッチング素子をオフ状態からオン状態に変化させたときの下側スイッチ ング素子のドレイン・ソース間電圧の変化と、上側スイッチング素子のドレイン・ソース 間電圧、ドレイン・ゲート間電圧、及びゲート・ソース間電圧の変化とを示す模式回路図

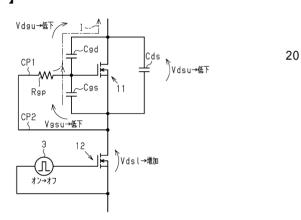

【 図 1 0 】 下 側 ス イ ッ チ ン グ 素 子 を オ ン 状 態 か ら オ フ 状 態 に 変 化 さ せ た と き の 下 側 ス イ ッ チング素子のドレイン・ソース間電圧の変化と、上側スイッチング素子のドレイン・ソー ス間電圧、ドレイン・ゲート間電圧、及びゲート・ソース間電圧の変化とを示す模式回路 図。

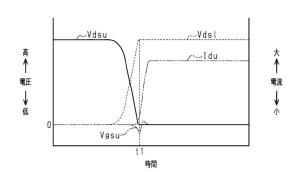

【 図 1 1 】 下 側 ス イ ッ チ ン グ 素 子 を オ ン 状 態 か ら オ フ 状 態 に 変 化 さ せ た と き の 下 側 ス イ ッ チング素子のドレイン・ソース間電圧、上側スイッチング素子のドレイン・ソース間電圧 、及びゲート・ソース間電圧の推移示すグラフ。

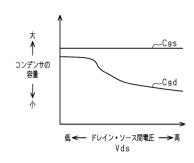

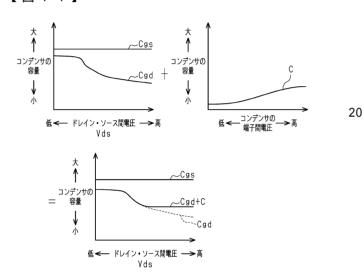

【 図 1 2 】 上 側 ス イ ッ チ ン グ 素 子 及 び 下 側 ス イ ッ チ ン グ 素 子 の ゲ ー ト ・ ソ ー ス 間 容 量 及 び ゲート・ドレイン間容量について、ドレイン・ソース間電圧と容量との関係を示すグラフ

【 図 1 3 】 上 側 コン デン サ 及 び 下 側 コン デン サ に お け る コン デン サ の 端 子 間 電 圧 と 容 量 と の関係を示すグラフ。

【図14】パワーモジュールにおいて、上側スイッチング素子及び下側スイッチング素子 のゲート・ソース間容量及びゲート・ドレイン間容量と、上側コンデンサ及び下側コンデ ンサとを含めたコンデンサ容量を示すグラフ。

【図15】第1実施形態のパワーモジュールのシミュレーションを行うための回路図。

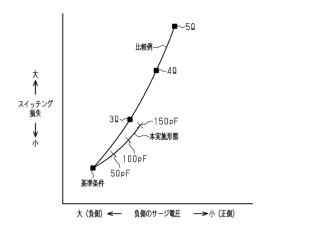

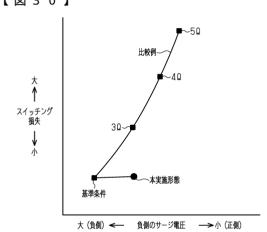

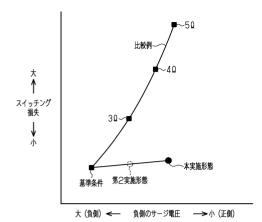

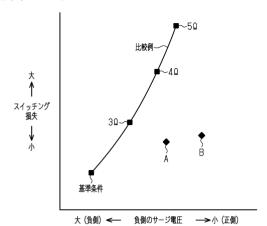

【図16】図7の比較例のパワーモジュールと、図15のパワーモジュールとのシミュレ ーション結果であって、負側のサージ電圧とスイッチング損失との関係を示すグラフ。

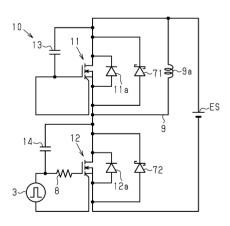

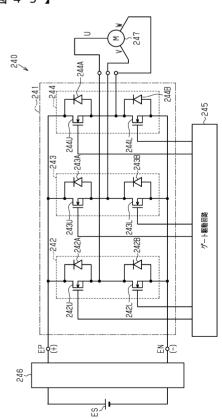

【図17】第2実施形態のパワーモジュールの模式回路図。

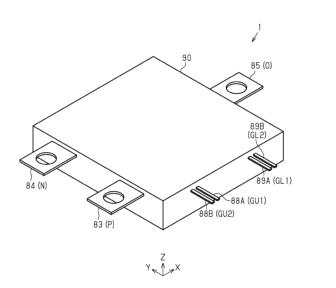

【図18】パワーモジュールの斜視図。

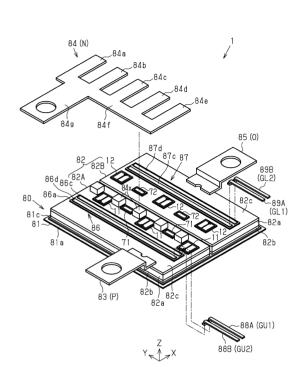

【 図 1 9 】 パ ワ ー モ ジ ュ ー ル の 内 部 構 成 を 示 す 分 解 斜 視 図 。

【図20】パワーモジュールの内部構成を示す平面図。

【図21】パワーモジュールの底面図。

【 図 2 2 】 図 2 0 の パ ワ ー モ ジ ュ ー ル の 第 2 基 板 の 一 部 を 第 2 方 向 及 び 第 3 方 向 に 沿 う 平 面で切った断面図。

【図23】図20のパワーモジュールの第1基板の一部を第1方向及び第3方向に沿う平 面で切った断面図。

【 図 2 4 】図 2 0 のパワーモジュールの一部を第 1 方向及び第 3 方向に沿う平面で切った 断面図。

【図25】ダイオードの平面図。

【図26】ダイオードの一部の断面図。

【図27】比較例のパワーモジュールにおいて、下側スイッチング素子をオン状態からオ フ 状 態 に 変 化 さ せ た と き の 上 側 ス イ ッ チ ン グ 素 子 及 び 下 側 ス イ ッ チ ン グ 素 子 の そ れ ぞ れ の ドレイン・ソース間電圧の推移を示すグラフ。

【図28】第2実施形態のパワーモジュールにおいて、下側スイッチング素子をオン状態 からオフ状態に変化させたときの上側スイッチング素子及び下側スイッチング素子のそれ ぞれのドレイン・ソース間電圧の推移を示すグラフ。

【図29】第2実施形態のパワーモジュールのシミュレーションを行うための回路図。

【 図 3 0 】図 7 の比較 例のパワーモジュールと、 図 2 9 のパワーモジュールとのシミュレ ーション結果であって、負側のサージ電圧とスイッチング損失との関係を示すグラフ。

【 図 3 1 】 第 3 実 施 形 態 の パ ワ ー モ ジ ュ ー ル に つ い て 、 ( a ) は M I S ト ラ ン ジ ス タ の 平 面図、(b)は(a)の一部の内部拡大図。

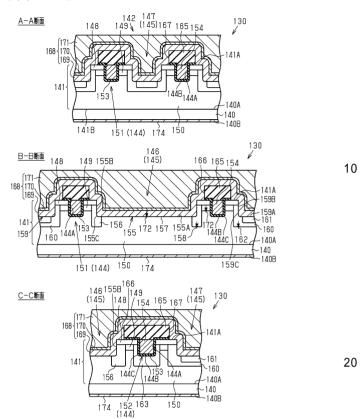

【図32】図31のA-A断面、B-B断面、及びC-C断面の各断面図。

【 図 3 3 】 パ ワ ー モ ジ ュ ー ル の 内 部 構 成 を 示 す 平 面 図 。

【図34】第3実施形態のパワーモジュールのシミュレーションを行うための回路図。

10

20

30

40

【 図 3 5 】図 7 の比較 例のパワーモジュールと、図 3 4 のパワーモジュールとのシミュレーション 結果であって、 負側のサージ電圧とスイッチング損失との関係を示すグラフ。

- 【図36】第4実施形態のパワーモジュールの模式回路図。

- 【図37】パワーモジュールの内部構成を示す平面図。

- 【図38】第4実施形態のパワーモジュールのシミュレーションを行うための回路図。

- 【図39】図7の比較例のパワーモジュールと、図38のパワーモジュールとのシミュレーション結果であって、負側のサージ電圧とスイッチング損失との関係を示すグラフ。

- 【図40】変形例のパワーモジュールの下側アイランド部及びその周辺の平面図。

- 【図41】変形例のパワーモジュールの下側アイランド部及びその周辺の平面図。

- 【図42】変形例のパワーモジュールの内部構成を示す平面図。

- 【 図 4 3 】 ( a ) ( b ) は変形例のスイッチング素子の断面図。

- 【図44】パワーモジュールを適用するフルブリッジ型インバータの模式回路図。

- 【図45】パワーモジュールを適用する3相交流インバータの模式回路図。

- 【発明を実施するための形態】

- [0011]

以下、半導体装置及びパワーモジュールの各実施形態について図面を参照して説明する。以下に示す各実施形態は、技術的思想を具体化するための構成や方法を例示するものであって、各構成部品の材質、形状、構造、配置、寸法等を下記のものに限定するものではない。以下の各実施形態は、種々の変更を加えることができる。

[ 0 0 1 2 ]

本明細書において、「部材 A が部材 B と接続された状態」とは、部材 A と部材 B とが物理的に直接的に接続される場合、並びに、部材 A 及び部材 B が、電気的な接続状態に影響を及ぼさない他の部材を介して間接的に接続される場合を含む。

[0013]

同様に、「部材 C が部材 A と部材 B との間に設けられた状態」とは、部材 A と部材 C 、あるいは部材 B と部材 C とが直接的に接続される場合、並びに、部材 A と部材 C 、あるいは部材 B と部材 C とが、電気的な接続状態に影響を及ぼさない他の部材を介して間接的に接続される場合を含む。

[0014]

(第1実施形態)

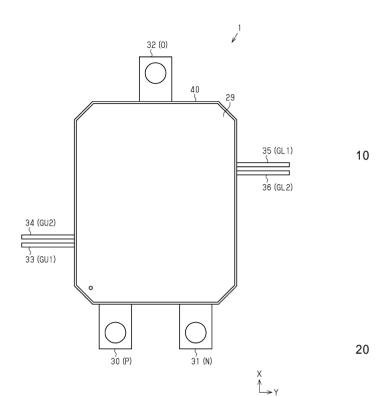

図1に示すように、パワーモジュール1とその駆動回路において、パワーモジュール1は、複数の端子を有する。パワーモジュール1は、複数の端子として図1に示されるとおり、正側となる第1入力端子P、負側となる第2入力端子N、出力端子O、第1上側制御端子GU1、第2上側制御端子GU2、第1下側制御端子GL1、及び第2下側制御端子GL2を有する。第1入力端子Pは、電源電圧VDDを生成する電源(図示略)と電気的に接続可能である。第2入力端子Nは、グランドに電気的に接続可能である。

[0015]

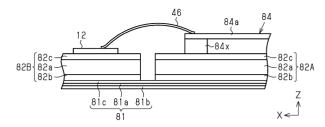

半導体装置10は、上側スイッチング素子11及び下側スイッチング素子12が直列に接続されたハーフブリッジ回路を備える。上側スイッチング素子11及び下側スイッチング素子12は、4H‐SiC(絶縁破壊電界が約2.8MV/cmであり、バンドギャップの幅が約3.26eVのワイドバンドギャップ半導体)が用いられている。なお、上側スイッチング素子11及び下側スイッチング素子12に用いられるワイドバンドギャップ半導体は、シリコンカーバイド(SiC)に限られず、窒化ガリウム(GaN)、酸化ガリウム(Ga203)、ダイヤモンド等であってもよい。窒化ガリウム(GaN)は、その絶縁破壊電界が約3MV/cmであり、バンドギャップの幅が約3.42eVである。酸化ガリウム(Ga203)は、その絶縁破壊電界が約8MV/cmであり、バンドギャップの幅が約4.8eVである。ダイヤモンドは、その絶縁破壊電界が約8MV/cmであり、バンドギャップの幅が約4.8eVである。ダイヤモンドは、その絶縁破壊電界が約8MV/cmであり、バンドギャップの幅が約5.47eVである。上側スイッチング素子11及び下側スイッチング素子12の一例は、SiC MOSFET(metal-oxide-semiconductor field-effect transistor)である。

10

20

30

40

## [0016]

上側スイッチング素子11は、第1上側端子の一例であるドレイン端子11d、第2上側端子の一例であるソース端子11s、及び上側制御端子の一例であるゲート端子11gを有する。下側スイッチング素子12は、第1下側端子の一例であるドレイン端子12d、第2下側端子の一例であるソース端子12s、及び下側制御端子の一例であるゲート端子12gを有する。

## [0017]

上側スイッチング素子11及び下側スイッチング素子12のそれぞれの個数は任意に変更可能である。例えば、上側スイッチング素子11及び下側スイッチング素子12のそれぞれの個数は、予め設定されたオン抵抗となるように設定される。上側スイッチング素子11は互いに並列に接続される。すなわち、複数の上側スイッチング素子11のドレイン端子11dが互いに接続され、複数の上側スイッチング素子11gが互いに接続され、複数の上側スイッチング素子11gが互いに接続され、複数の上側スイッチング素子11gが互いに接続される。また下側スイッチング素子11のゲート端子11gが互いに接続される。また下側スイッチング素子12が複数個設けられる場合、複数の下側スイッチング素子12dが互いに接続される。すなわち、複数の下側スイッチング素子12のゲート端子12gが互いに接続される。本実施形態では、上側スイッチング素子11は2個設けられ、下側スイッチング素子12は2個設けられている。

### [0018]

上側スイッチング素子11のドレイン端子11dは、第1配線15を介して第1入力端子Pに電気的に接続されている。これにより、上側スイッチング素子11のドレイン端子11dには、電源電圧VDDが供給される。上側スイッチング素子11のソース端子11gは、第4配線18を介して下側スイッチング素子12のドレイン端子12dに接続スイッチング素子12のドレイン端子11gと下側スイッチング素子11のソース端子11gと下側スイッチング素子11のケート端子11gと下側スイッチング素子11のゲート端子11gはスイッチング素子11のゲート端子11gは、第2配線16を介して第1上側制御端子GU1と電気的に接続されている。第1上側制御端子GU1は、第1上側配線4を介して上側ゲート駆動回路2に電気的に接続されている。上側スイッチング素子11のソースは、図示しない制御回路からの指令に応じて上側スイッチング素子11のソースは、上側センス配線16Aを介して第2上側制御端子GU2と電気的に接続されている。第2上側制御端子GU2は、第2上側配線5により上側ゲート駆動回路2に接続されている。

## [0019]

下側スイッチング素子12のソース端子12sは、第5配線19を介して第2入力端子 N に電気的に接続されている。これにより、下側スイッチング素子12のソース端子12gは、第3配線17を介して第1下側制御端子GL1に電気的に接続されている。第1下側制御端子GL1は、第1下側配線6を介して下側ゲート駆動回路3に電気的に接続されている。第1下側制る。下側ゲート駆動回路3は、図示しない制御回路からの指令に応じて下側ズイッチング素子12を動作させるためのゲート駆動信号をゲート端子12gに出力する。上側ゲート駆動回路2及び下側ゲート駆動回路3は、上側スイッチング素子11及び下側スイッチング素子12を制御する。下側スイッチング素子11及び下側スイッチング素子12を制御する。下側スイッチング素子11及び下側スイッチング素子12を制御する。下側スイッチング素子12を制御端子GL2と電気的に接続されている。第2下側制御端子GL2は、第2下側配線7により下側ゲート駆動回路3に接続されている。

### [0020]

図1に示すとおり、上側ゲート駆動回路2、下側ゲート駆動回路3、第1上側配線4、 第2上側配線5、第1下側配線6、及び第2下側配線7は、パワーモジュール1の外部に 10

20

30

40

20

30

40

50

設けられている。なお、上側ゲート駆動回路2及び下側ゲート駆動回路3の少なくとも一方は、パワーモジュール1の内部に設けられてもよい。また、パワーモジュール1は上下2つのパワーモジュールを組み合せて構成されてもよい。

#### [0021]

半導体装置10は、上側コンデンサ13及び下側コンデンサ14を有する。図1及び図3に示すとおり、上側コンデンサ13は、上側スイッチング素子11とは別体として設けられている。下側コンデンサ14は、下側スイッチング素子12とは別体として設けれている。上側コンデンサ13及び下側コンデンサ14の一例は、セラミックコンデンサ、フィルムコンデンサ13及び下側コンデンサキであるが、パワーモジュール1内のの容量によって作り込まれていてもよい。上側コンデンサ13及び下側コンデンサ14のの量によって作り込まれていてもよい。上側コンデンサ13は、上側スイッチング素子11のドレイン・ソース間電圧であるドレイン・ソース間電圧との間の電圧であるドレイン・ソース間電圧との間の電圧であるドレイン・ソース間電圧とはまままで、その容量が増加するように構成されることが好ましい。この間の電圧であるドレイン・ソース間電圧とはままで、その容量が増加する場合、その容量が増加する特性を有する。反強誘電性のコンデンサは、正の電圧が印加されると容量が増加する特性を有する。

## [0022]

上側コンデンサ13は、上側スイッチング素子11のドレイン端子11dとゲート端子11gとの間に設けられている。詳述すると、上側コンデンサ13の第1端子は、ドレイン端子11dと第1入力端子Pとを繋ぐ第1配線15に接続されている。上側コンデンサ13の第2端子は、ゲート端子11gと第1上側制御端子GU1とを繋ぐ第2配線16に接続されている。

### [0023]

下側コンデンサ14は、下側スイッチング素子12のドレイン端子12dとゲート端子12gとの間に設けられている。詳述すると、下側コンデンサ14の第1端子は、ドレイン端子12dと上側スイッチング素子11のソース端子11sとの間に接続されている。より詳細には、下側コンデンサ14の第1端子は、第4配線18においてノードNと下側スイッチング素子12のドレイン端子12dとの間の部分に接続されている。下側コンデンサ14の第2端子は、ゲート端子12gと第1下側制御端子GL1とを繋ぐ第3配線17に接続されている。

## [0024]

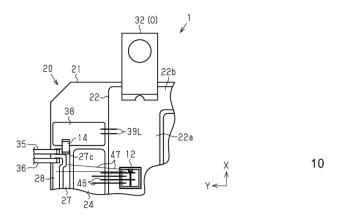

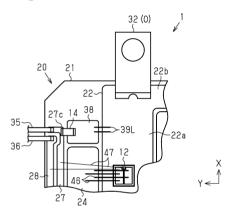

図 2 ~ 図 4 は、パワーモジュール 1 の構成の一例を示している。パワーモジュール 1 の構成は、図 2 ~ 図 4 に示す構成に限られず、種々の変更が可能である。

図2~図4に示すように、パワーモジュール1は、上側スイッチング素子11、下側スイッチング素子12、上側コンデンサ13、及び下側コンデンサ14が実装された基板20と、上側スイッチング素子11、下側スイッチング素子12、上側コンデンサ13、下側コンデンサ14、及び基板20の一部を封止する封止樹脂40と、を有する。またパワーモジュール1は、端子部材の一例として、第1入力端子Pを構成する第1入力端子部材30、第2入力端子Nを構成する第2入力端子部材31、出力端子Oを構成する出力端子部材32、第1上側制御端子GU1を構成する第1上側制御端子部材33、第2上側制御端子GU2を構成する第2下側制御端子GH制御端子部材35、及び第2下側制御端子GL2を構成する第2下側制御端子部材36を有する。

## [0025]

基板 2 0 は、支持基板の一例である平板状のセラミック基板 2 1 を有する。セラミック基板 2 1 の表面側には、出力配線部 2 2、正側となる第 1 入力配線部 2 3、負側となる第 2 入力配線部 2 4、第 1 上側制御配線部 2 5、第 2 上側制御配線部 2 6、第 1 下側制御配線部 2 7、及び第 2 下側制御配線部 2 8 が設けられている。各配線部 2 2 ~ 2 8 はそれぞ

20

30

40

れ、銅(Cu)からなる。以降の説明において、基板20の縦方向を「第1方向X」と規定し、基板20の横方向を「第2方向Y」と規定する。第2方向Yは、パワーモジュール 1の平面視において第1方向Xと直交する方向となる。

### [0026]

出力配線部22は、第2方向Yにおけるセラミック基板21の中央に設けられている。出力配線部22は、平面視において略L字状に形成されている。出力配線部22は、第1方向Xに延びる第1部分22aと、第2方向Yに延びる第2部分22bとを有する。第2部分22bは、第1部分22aの第1方向Xの端部に設けられている。第1部分22aの幅寸法(第2方向Yにおける第1部分22aの長さ)は、第2部分22bの幅寸法(第1方向Xにおける第2部分22bの長さ)よりも大きい。第1部分22aは、セラミック基板21における第2方向Yの中央に位置している。第2部分22bは、セラミック基板21における第1方向Xの端部に位置している。第2部分22bには、出力端子部材32が接続されている。出力端子部材32は、セラミック基板21の第2方向Yの中央に位置している。

## [0027]

第1入力配線部23は、出力配線部22と隣り合うように設けられている。第1入力配線部23は、 第1方向Xに延びる第1部分23aと、第2方向Yに延びる第2部分23bとを有する。第1部分23aは、出力配線部22の第1部分22aに対して各上側制御端子部材33,34が位置する側に、第2方向Yにおいて第1部分22aと隙間を介して隣り合うように配置されている。第1部分23aにおける出力端子部材32側の端部は、第1方向Xにおいて出力配線部22の第2部分23bは、第1方向Xの端部に設けられている。第2部分23bは、第1部分23aの第1方向Xの端部に設けられている。第2部分23bは、出力配線部22の第1部分23aの長さ)は、第1和分23aの長さ)は5記録が表記の一部を第1方向Xから覆っている。第2部分23bには、第1入力端子部材30が接続されている。第1部分23aの長さ)よりも大きい。第1部分23aの幅寸法は、出力配線部22の第1部分22aの幅寸法よりも小さい。第1部分23aの幅寸法は、出力配線部22の第1部分22aの幅寸法よりも小さい。

## [0028]

第2入力配線部24は、出力配線部22と隣り合うように設けられている。第2入力配 線部24は、平面視において略T字状に形成されている。第2入力配線部24は、第1方 向Xに伸びる第1部分24aと、第2方向Yに延びる第2部分24bとを有する。第1部 分 2 4 a は、出力配線部 2 2 の第 1 部分 2 2 a に対して各下側制御端子部材 3 5 , 3 6 が 位置する側に、第2方向Yにおいて第1部分22aと隙間を介して隣り合うように配置さ れている。図3に示すとおり、第2方向Yにおいて、出力配線部22の第1部分22aは 、 第 1 入力配線部 2 3 の第 1 部分 2 3 a と第 2 入力配線部 2 4 の第 1 部分 2 4 a とに挟ま れるように配置されている。 第 2 部 分 2 4 b は、 第 1 部 分 2 4 a の 第 1 方向 X の 端 部 に 設 けられている。第2部分24bは、第2方向Yにおいて第1部分24aの両側から突出し ている。第1部分24aの幅寸法(第2方向Yにおける第1部分24aの長さ)は、第2 部 分 2 4 b の 幅 寸法 ( 第 1 方 向 X に お け る 第 2 部 分 2 4 b の 長 さ ) よ り も 大 き い 。 第 1 部 分24aの幅寸法は、出力配線部22の第1部分22aの幅寸法及び第1入力配線部23 の第1部分23aの幅寸法よりも小さい。第1部分24aの第1方向Xの長さは、出力配 線部22の第1部分22aの第1方向Xの長さ及び第1入力配線部23の第1部分23a の第1方向Xの長さよりも長い。第2部分24bの第1方向Xの位置は、第1入力配線部 2 3 の 第 2 部 分 2 3 b の 第 1 方 向 X の 位 置 と 等 し い 。 第 2 部 分 2 4 b に お い て 第 1 部 分 2 4 a よりも第 1 入力配線部 2 3 側に突出する部分は、出力配線部 2 2 の第 1 部分 2 2 a に おける出力端子部材32が配置される側とは反対側の端部の一部を第1方向Xから覆って いる。

## [0029]

20

30

40

50

第1上側制御配線部25は、セラミック基板21における各上側制御端子部材33,34が配置される側の端部に設けられている。第1上側制御配線部25は、第1入力配線部23の第1部分23aに対して各上側制御端子部材33,34が配置される側に、第1部分23aと第2方向Yにおいて隣り合うように設けられている。第1上側制御配線部25は、第1方向Xに延びる第1部分25aに設けられている。第1上側制御配線部25は、第1方向Xに延びる第1部分25aにおいて第1入力配線部23側に凹む凹部25はが形成されている。すなわち第1部分25aにおいて凹部25はが形成される部分の幅寸法(第2方向Yにおける第1部分25aの長さ)よりも小さい。第1部分25aの第1方向Xの長さは、第1分和配線部23の第1部分25aの第1方向Xの長さは、第1入力配線部23の第1方向Xの長さは、第1上側制御端子部材33が接続されている。第1上側制御端子部材33は、第2方向Yに延びている。

[0030]

第2上側制御配線部26は、セラミック基板21における各上側制御端子部材33,34が配置される側の端部に設けられている。第2上側制御配線部26は、第1上側制御配線部25に対して各上側制御端子部材33,34が配置される側に、第1上側制御配線部25と第2方向Yにおいて隣り合うように設けられている。第2上側制御配線部26において第1上側制御配線部25の凹部25dと第2方向Yに対向する部分には、凹部25dに向けて延びる接続部26aが設けられている。接続部26aには、第1方向Xにおいて第1上側制御配線部25の第2部分25bに覆われている。接続部26aには、第2上側制御端子部材34が接続されている。第2上側制御端子部材34は、第2方向Yに延びている。

[0031]

第1下側制御配線部27は、セラミック基板21における各下側制御端子部材35,36が配置される側の端部に設けられている。第1下側制御配線部27は、第2入力配線部24の第1部分24aに対して各下側制御端子部材35,36が配置される側に、第1部分24aと第2方向Yにおいて隣り合うように設けられている。第1下側制御配線部27は、第1方向Xに延びる第1部分27a、第2方向Yに延びる第2部分27b、及び第1部分27aと第2部分27bとを接続する屈曲部27cを有する。第1部分27aにおける屈曲部27c側の端部には、第2方向Yにおいて第2入力配線部24側に凹む凹部27dが形成されている。すなわち第1部分27aにおいて凹部27dが形成される部分の幅寸法(第2方向Yにおける第1部分27aの長さ)は、第1部分27aの他の部分の幅寸法(第2方向Yにおける第1部分27aの長さ)は、第1部分27aの第1方向Xの長さは、第2入力配線部24の第1部分24aの第1方向Xの長さは、第2入力配線部24の第1方向Xの長さは、第2方向Yにおける第1方向Xの長さよりも短い。第2部分27bの先端部には、第1下側制御端子部材35が接続されている。第1下側制御端子部材35は、第2方向Yに延びている。

[0032]

第2下側制御配線部28は、セラミック基板21における各下側制御端子部材35,36が配置される側の端部に設けられている。第2下側制御配線部28は、第1下側制御配線部27に対して各下側制御端子部材35,36が配置される側に、第1下側制御配線部27と第2方向Yにおいて隣り合うように設けられている。第2下側制御配線部28において第1下側制御配線部27の凹部27dと第2方向Yに対向する部分には、凹部27dに向けて延びる接続部28aが設けられている。接続部28aには、第1方向Xにおいて第1下側制御配線部27の第2部分27bに覆われている。接続部28aには、第2下側制御端子部材36が接続されている。第2下側制御端子部材36は、第2方向Yに延びている。

[0033]

セラミック基板 2 1 の表面側には、上側アイランド部 3 7 及び下側アイランド部 3 8 が

設けられている。上側アイランド部37及び下側アイランド部38のそれぞれの形状は、 第1方向×が長手方向となる長方形である。上側アイランド部37及び下側アイランド部 38は、例えば銅(Cu)からなる。

#### [0034]

上側アイランド部37は、セラミック基板21における各上側制御端子部材33,34が配置される側の端部に設けられている。上側アイランド部37は、第1方向Xにおいて各上側制御配線部25,26よりも第1入力端子部材30側に設けられている。詳述すると、上側アイランド部37は、第1方向Xにおいて第1上側制御配線部25の第2部分25b及び屈曲部25cと隙間を空けて隣り合い、第2方向Yにおいて第1入力配線部23の第1部分23aと隙間を空けて隣り合うように設けられている。上側アイランド部37と第1入力配線部23とは、1本又は複数本の上側接続用ワイヤ39Uにより電気的に接続されている。本実施形態では、2本の上側接続用ワイヤ39Uにより、上側アイランド部37と第1入力配線部23とが電気的に接続されている。上側接続用ワイヤ39Uにより、上側アイランド部37と第1入力配線部23とが電気的に接続されている。上側接続用ワイヤ39Uによりイヤ45(下側制御用ワイヤ47)の線径よりも大きいことが好ましく、例えば上側電力用ワイヤ(下側電力用ワイヤ46)の線径と等しい。

### [0035]

下側アイランド部38は、セラミック基板21における各下側制御端子部材35,36が配置される側の端部に設けられている。下側アイランド部38は、第1方向Xにおいて第1下側制御配線部27の第2部分27b及び屈曲部27cと隙間を空けて隣り合い、第2方向Yにおいて第2入力配線部24の第1部分24aと隙間を空けて隣り合うように設けられている。下側アイランド部38と出力配線部22とは、1本又は複数本の下側接続用ワイヤ39Lにより電気的に接続されている。本実施形態では、2本の下側接続用ワイヤ39Lにより、下側アイランド部38と出力配線部22とが電気的に接続されている。下側接続用ワイヤ39Lは、第2入力配線部24の第1部分24aを第2方向Yに跨ぐように設けられている。下側接続用ワイヤ39Lは、第2入力配線部24の第1部分24aを第2方向Yに跨ぐように設けられている。下側接続用ワイヤ39Lの線径は、上側電力用ワイヤ45(下側制御用ワイヤ47)の線径よりも大きいことが好ましく、例えば上側電力用ワイヤ44(下側電力用ワイヤ46)の線径と等しい。

## [0036]

2個の上側スイッチング素子11はそれぞれ、チップ状に形成され、第1入力配線部23の第1部分23aに実装されている。2個の上側スイッチング素子11は、第1方向×に沿って互いに隙間を空けて位置している。すなわち、2個の上側スイッチング素子11は、第1方向×において互いに離間して第1入力配線部23に実装されている。各上側スイッチング素子11は、第1入力配線部23の第1部分23aの第2方向Yの中央に位置している。また各上側スイッチング素子11は、第1方向×において各上側制御端子部材33,34よりも出力端子部材32側に位置している。より詳細には、各上側スイッチング素子11は、第1方向×において第1上側制御配線部25の凹部25dよりも出力端子部材32側に位置している。

### [ 0 0 3 7 ]

各上側スイッチング素子11は、第1上側端子(ドレイン端子)を構成するドレイン電極(図示略)、第2上側端子(ソース端子)を構成するソース電極41、及び上側制御端子(ゲート端子)を構成するゲート電極42を有する(ともに図5(a)参照)。ドレイン電極は、上側スイッチング素子11における第1入力配線部23に実装される裏面に設けられている。ソース電極41及びゲート電極42は、上側スイッチング素子11における裏面とは反対側の表面に設けられている。図5(a)に示すとおり、上側スイッチング素子11の表面の外周部には、ガードリング43が設けられている。ソース電極41及びゲート電極42は、ガードリング43の内部に設けられている。ソース電極41は、ガードリング43内の面積の殆どを占めている。ソース電極41は、2つの電極に分離されて

10

20

30

20

30

40

50

いる。ソース電極 4 1 は、ガードリング 4 3 から離間するように凹む凹部 4 1 a を有する。凹部 4 1 a とガードリング 4 3 とにより囲まれた領域には、ゲート電極 4 2 が設けられている。

#### [0038]

図3に示すとおり、各上側スイッチング素子11のソース電極41(図5(a)参照) は、上側電力用接続部材の一例として複数本の上側電力用ワイヤ44により出力配線部2 2の第1部分22aと電気的に接続されている。本実施形態では、4本の上側電力用ワイ ヤ 4 4 により、上側スイッチング素子 1 1 のソース電極 4 1 と出力配線部 2 2 とが電気的 に接続されている。上側電力用ワイヤ44は、例えばアルミニウム(A1)からなる。ま た 各 上 側 ス イ ッ チ ン グ 素 子 1 1 の ソ ー ス 電 極 4 1 は 、 上 側 制 御 用 接 続 部 材 の 一 例 と し て 1 本又は複数本の上側制御用ワイヤ45により第2上側制御配線部26と電気的に接続され ている。上側制御用ワイヤ45は、第1上側制御配線部25の第1部分25aを第2方向 Yに跨ぐように設けられている。上側制御用ワイヤ45は、例えばアルミニウム(A1) からなる。上側電力用ワイヤ44の線径は、上側制御用ワイヤ45の線径よりも大きい。 上側電力用ワイヤ44の線径の一例は 400μmであり、上側制御用ワイヤ45の線径 の一例は 1 5 0 μ m である。各上側スイッチング素子 1 1 のゲート電極 4 2 は、 1 本又 は複数本の上側制御用ワイヤ45により第1上側制御配線部25の第1部分25aと電気 的に接続されている。このように、2個の上側スイッチング素子11のドレインが共通の 第 1 入 力 配 線 部 2 3 に 電 気 的 に 接 続 さ れ 、 2 個 の 上 側 ス イ ッ チ ン グ 素 子 1 1 の ソ ー ス 電 極 41が共通の出力配線部22に電気的に接続されているため、2個の上側スイッチング素 子11は互いに並列に接続されることになる。なお、上側電力用接続部材は、例えばCI C (Cu/Inver/Cu)のリードフレームなどであってもよい。

## [0039]

2個の下側スイッチング素子12はそれぞれ、チップ状に形成され、出力配線部22の第1部分22aに実装されている。2個の下側スイッチング素子12は、第1方向×に沿って互いに隙間を空けて位置している。すなわち2個の下側スイッチング素子12は、第1方向×において互いに離間して出力配線部22に実装されている。2個の下側スイッチング素子12は、第1方向×において2個の上側スイッチング素子11と同じ位置となるように実装されている。各下側スイッチング素子12は、第2方向×において出力配線部22の第1部分22aのうちの第2入力配線部24側に位置している。これにより、出力配線部22の第1部分22aにおいて、複数本の上側電力用ワイヤ44が接続される領域を確保することができる。

## [0040]

2個の下側スイッチング素子12は、上側スイッチング素子11と同様の構造である。 すなわち各下側スイッチング素子12は、ドレイン電極(図示略)、ソース電極41、ゲート電極42、及びガードリング43を有する。

## [0041]

図3に示すとおり、各下側スイッチング素子12のソース電極41は、下側電力用接続部材の一例として複数本の下側電力用ワイヤ46により第2入力配線部24の第1部分24aと電気的に接続されている。本実施形態では、4本の下側電力用ワイヤ46に接続されている。下側スイッチング素子12のソース電極41と第2入力配線部24とが電気的に接続されている。下側電力用ワイヤ46は、例えばアルミニウム(A1)からなる。下側電力用ワイヤ46は、例えばアルミニウム(A1)からなる。下側電力用ワイヤ47の線径と等しい。また各下側スイッチング素のサース電極41は、下側制御配線部28と電気的に接続されている。下側制御用ワイヤ47の線径は、上側電力用ワイヤ47の線径は、下側制御用ワイヤ47の線径は、下側制御用ワイヤ47の線径と等しい。各下側スイッチング素子12のソース電極41に接続配れた下側制御用ワイヤ47は、第2入力配線部24の第1部分24a及び第1下側制線部27の第1部分27aを第2方向Yに跨ぐように設けられている。各下側スイッチング素子12のゲート電極42は、1本又は複数本の下側制御用ワイヤ47により第1下側

20

30

40

50

制御配線部27の第1部分27aと電気的に接続されている。ゲート電極42に接続された下側制御用ワイヤ47は、第2入力配線部24の第1部分24aを跨ぐように設けられている。このように、2個の下側スイッチング素子12のドレインが共通の出力配線部22に電気的に接続され、2個の下側スイッチング素子12のソース電極41が共通の第2入力配線部24に電気的に接続されているため、2個の下側スイッチング素子12は互いに並列に接続されることになる。なお、下側電力用接続部材は、例えばCIC(Cu/Inver/Cu)のリードフレームなどであってもよい。

### [0042]

上側コンデンサ13は、第1上側制御配線部25の屈曲部25cと上側アイランド部37とに実装されている。詳述すると、上側コンデンサ13の第1端子は第1上側制御配線部25の屈曲部25cに実装され、上側コンデンサ13の第2端子は上側アイランド部37に実装されている。図3に示すとおり、上側コンデンサ13の第2端子は、上側アイランド部37における第1入力配線部23の第1部分23a側の端部に位置している。このように、上側コンデンサ13は、複数の上側スイッチング素子11の共通のドレイン端子11d(ドレイン)と、複数の上側スイッチング素子11の共通のゲート端子11g(ゲート)とを電気的に接続している。

## [0043]

下側コンデンサ14は、第1下側制御配線部27の屈曲部27cと下側アイランド部38とに実装されている。詳述すると、下側コンデンサ14の第1端子は第1下側制御配線部27の屈曲部27cに実装され、下側コンデンサ14の第2端子は下側アイランド部38に実装されている。図3に示すとおり、下側コンデンサ14の第2端子は、下側アイランド部38における第2入力配線部24の第1部分24a側の端部に位置している。このように、下側コンデンサ14は、複数の下側スイッチング素子12の共通のドレイン端子12d(ドレイン)と、複数の下側スイッチング素子12の共通のゲート端子12g(ゲート)とを電気的に接続している。

## [0044]

図4に示すように、セラミック基板21の裏面側には、封止樹脂40から露出する放熱板29が設けられている。放熱板29は、銅(Cu)からなる。放熱板29の板厚は、セラミック基板21の形状と相似形状となるように形成されている。放熱板29の外周縁は、セラミック基板21の外周縁よりも内側に位置している。これにより、封止樹脂40がセラミック基板21の裏面側に回り込むため、セラミック基板21と封止樹脂40との密着性が向上する。なお、放熱板29は、冷却器等に接続されることを想定して、表面がニッケル(Ni)又は銀(Ag)でメッキされていてもよい。

## [ 0 0 4 5 ]

(上側スイッチング素子及び下側スイッチング素子の構造)

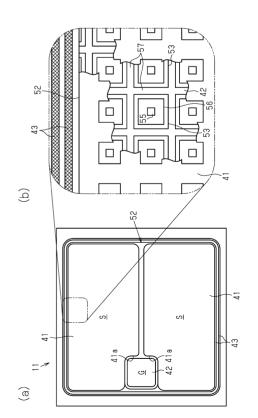

次に、上側スイッチング素子11及び下側スイッチング素子12の構造について説明する。図5及び図6は、上側スイッチング素子11の構造の一例を示している。なお、上側スイッチング素子11及び下側スイッチング素子12は同一構造である。このため、図5及び図6は、下側スイッチング素子12の構造の一例を示しているとも言える。また以降では、上側スイッチング素子11の構造を説明し、下側スイッチング素子12の構造の説明を省略する。なお、上側スイッチング素子11及び下側スイッチング素子12の構造は、図5及び図6に示す構造に限られず、種々の変更が可能である。

### [0046]

上側スイッチング素子11は、シリコンカーバイド(SiC)を用いたプレーナゲート型 V D M O S F E T (Vertical Double implanted MOSFET)であり、図 5 ( a ) に示すとおりの平面視で正方形のチップ状である。

## [0047]

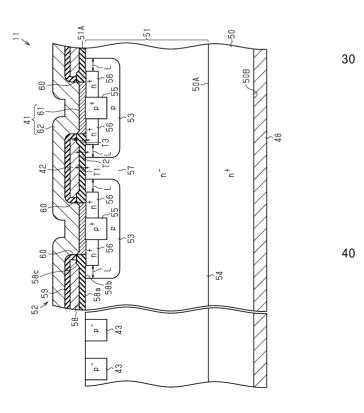

図 6 に示すように、 n <sup>+</sup>型の S i C 基板 5 0 を有する。本実施形態では、 S i C 基板 5 0 は、上側スイッチング素子 1 1 のドレインとして機能し、その表面 5 0 A (上面) がシ

リコン面(Si面)であり、その裏面50B(下面)がカーボン面(C面)である。

### [0048]

SiC基板50上には、SiC基板50よりも低濃度のn <sup>-</sup>型のSiCからなるエピタキシャル層51が積層されている。半導体層としてのエピタキシャル層51は、Si面を成長主面として成長させられる。したがって、エピタキシャル成長により形成されるエピタキシャル層51の表面51Aは、SiC基板50の表面50Aと同様にSi面である。

## [0049]

図 5 ( a ) に示すように、上側スイッチング素子11には、平面視においてエピタキシャル層 5 1 (図 6 参照)上の中央部に配置され、電界効果トランジスタとして機能する活性領域 5 2 が形成されている。エピタキシャル層 5 1 には、活性領域 5 2 を取り囲むように、活性領域 5 2 から間隔を空けてガードリング 4 3 (図 5 ( b ) においてクロスハッチングを付して示す)が複数本形成されている。本実施形態では、ガードリング 4 3 は、 2 本形成されている。

## [0050]

図 6 に示すように、活性領域 5 2 とガードリング 4 3 との間隔は、全周に亘ってほぼ一定である。ガードリング 4 3 は、エピタキシャル層 5 1 に p 型不純物をインプランテーションすることにより形成された p 型の低濃度領域である。

## [ 0 0 5 1 ]

活性領域 5 2 において、エピタキシャル層 5 1 の表面 5 1 A 側(Si面側)には、p型のボディ領域 5 3 が、行方向及び列方向に一定のピッチで行列状(マトリクス状)に配列されて多数形成されている。各ボディ領域 5 3 の形状は、例えば、平面視で正方形である。p型不純物は、例えばアルミニウム(A1)であってもよい。一方、エピタキシャル層 5 1 におけるボディ領域 5 3 よりもSiC基板 5 0 側(C面側)の領域は、エピタキシャル成長後のままの状態が維持された、n゚型のドリフト領域 5 4 となっている。

#### [0052]

各ボディ領域 5 3 の表層部には、その中央部に p + 型のボディコンタクト領域 5 5 が形成されており、このボディコンタクト領域 5 5 を取り囲むように n + 型のソース領域 5 6 が形成されている。ボディコンタクト領域 5 5 の形状は、例えば、平面視で正方形である。ソース領域 5 6 の形状は、例えば、平面視で正方形環状である。 n 型不純物濃度の一例は、燐 ( P ) である。

## [ 0 0 5 3 ]

また活性領域 5 2 において、一定のピッチで行列状に配列されたボディ領域 5 3 の各間の領域(隣り合うボディ領域 5 3 の側面により挟まれるボディ間領域 5 7 )は、一定幅を有する格子状である。

## [ 0 0 5 4 ]

ボディ間領域57上には、このボディ間領域57に沿って、格子状のゲート絶縁膜58(図5(b)では図示略)が形成されている。ゲート絶縁膜58は、隣り合うボディ領域53の間に跨っており、ボディ領域53におけるソース領域56を取り囲む部分(ボディ領域53の周縁部)及びソース領域56の外周縁を覆っている。本実施形態では、ゲート絶縁膜58は、窒素(N)を含有する酸化膜、例えば、窒素及び酸素を含有するガスを用いた熱酸化により形成される窒化酸化シリコン膜からなる。

## [0055]

ゲート絶縁膜58は、ボディ領域53の外部のエピタキシャル層51に接する第1部分58a、ボディ領域53に接する第2部分58b、及びソース領域56に接する第3部分58cを含む。図6に示されるように、第3部分58cの膜厚T3は、第1部分58aの膜厚T1及び第2部分58bの膜厚T2よりも大きい。詳述すると、第3部分58cの下側界面(ソース領域56との界面)は、第1部分58aの下側界面(エピタキシャル層51との界面)及び第2部分58bの下側界面(ボディ領域53との界面)よりも下側、すなわちSiC基板50側であり、エピタキシャル層51の表面51Aからより深い位置に位置している。また第3部分58cの上側界面(ゲート電極42との界面)は、第1部分

20

10

30

40

5 8 a の上側界面(ゲート電極 4 2 との界面)及び第 2 部分 5 8 b の上側界面(ゲート電極 4 2 との界面)よりも上側、すなわちゲート電極 4 2 側であり、エピタキシャル層 5 1 の表面 5 1 A からより遠い位置に位置している。

#### [0056]

ゲート絶縁膜58上には、ゲート電極42が形成されている。ゲート電極42は、格子状のゲート絶縁膜58に沿って格子状に形成されており、ゲート絶縁膜58を挟んで各ボディ領域53の周縁部に対向している。詳述すると、ゲート電極42は、ゲート絶縁膜58を挟んで、ボディ領域53の外部のエピタキシャル層51、ボディ領域53、及びソース領域56に跨る領域に対向している。したがって、ゲート電極42は、平面視においてソース領域56とオーバーラップしている。例えば、ゲート電極42は、平面視において、ボディ領域53とソース領域56との境界線からソース領域56に向けて僅かにはみ出している。これにより、ソース領域56とエピタキシャル層51との間のボディ領域53に対してゲート電極42を確実に対向させることができるため、ボディ領域53におけるチャネルの形成を確実に制御できる。ゲート電極42は、例えばポリシリコンからなる。ゲート電極42は、例えばp型不純物が高濃度に導入されて低抵抗化されている。

#### [0057]

上側スイッチング素子11では、ボディ間領域57の幅方向中央に単位セル間の境界が設定されている。各単位セルでは、ゲート電極42に印加する電圧を制御することにより (例えば6V以上の電圧を印加することにより)、各単位セルのボディ領域53の周縁部に環状のチャネルが形成される。この環状のチャネルを介して、ドリフト領域54において各ボディ領域53の4つの側面に沿ってエピタキシャル層51の表面51A側へ流れるドレイン電流を、ソース領域56に流すことができる。チャネル長Lは、ゲート電極42の直下のボディ領域53の幅によって規定される。

### [0058]

エピタキシャル層 5 1 上には、ゲート電極 4 2 を被覆するように、例えば酸化シリコン(SiO2)からなる層間絶縁膜 5 9 が積層されている。層間絶縁膜 5 9 は、コンタクトホール 6 0 が形成されている。コンタクトホール 6 0 内には、ソース領域 5 6 の中央部及びボディコンタクト領域 5 5 の全体が露出している。

## [0059]

エピタキシャル層 5 1 上には、ソース電極 4 1 が形成されている。ソース電極 4 1 は、各コンタクトホール 6 0 を介して一括して接触している。つまり、ソース電極 4 1 は、全ての単位セルに対して共通の配線になっている。ソース電極 4 1 上には層間絶縁膜(図示略)が形成されている。ソース電極 4 1 は、層間絶縁膜を除く領域を形成することにより、すなわちソース電極 4 1 が露出する領域が形成され、ソース電極パッドを構成する。

## [0060]

ソース電極41は、エピタキシャル層51との接触側から順にTi/TiN層61と、A1層62とが積層された構造を有する。Ti/TiN層61は、密着層としてのTi層をエピタキシャル層51側に有し、このTi層にバリア層としてのTiN層を積層した積層膜である。バリア層は、A1層62の構成原子(A1原子)がエピタキシャル層51側へと拡散することを抑制する。

## [ 0 0 6 1 ]

SiC基板50の裏面50Bには、その全域を覆うようにドレイン電極48が形成されている。ドレイン電極48は、全ての単位セルに対して共通の電極になっている。ドレイン電極48としては、例えばSiC基板50側から順にチタン(Ti)、ニッケル(Ni)、金(Au)、及び銀(Ag)が積層された積層構造(Ti/Ni/Au/Ag)を適用することができる。

## [0062]

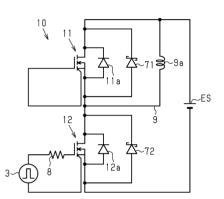

(比較例)

図 7 は、比較例のパワーモジュールの回路構成を示す。比較例のパワーモジュールの回路では、上側スイッチング素子 1 1 をオフし、下側スイッチング素子 1 2 をオンオフする

10

20

30

40

場合を示す。

### [0063]

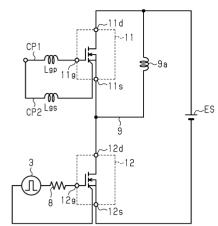

比較例のパワーモジュールは、図1に示す本実施形態のパワーモジュール1の回路構成から上側コンデンサ13及び下側コンデンサ14を省略し、ボディダイオード11a,12aの記載を省略したものである。また比較例のパワーモジュールにおいて、電源ESの正側端子は上側スイッチング素子11のドレイン端子11dに接続されている。また、上側スイッチング素子11のドレイン端子11gと接続されている。また、上側スイッチング素子11のドレイン端子11gとサース端子11sとを繋ぐ配線9を有する。配線9は、インダクタ負荷9aを有する。比較例のパワーモジュールの回路構成では、上側スイッチング素子11のゲート端子11gとソース端子11sとが第1上側制御配線部25に基づく寄生インダクタンスLgpを有する第1接続配線CP1と、第2上側制御配線部26に基づく寄生インダクタンスLgsを有する第2接続配線CP2とを短絡している。ゲート端子12gと下側ゲート駆動回路3に接続されている。ゲート端子12gと下側ゲート駆動回路3との間には、ゲート抵抗8が設けられている。

## [0064]

このような構成の上側スイッチング素子11及び下側スイッチング素子12はそれぞれ、SiC MOSFETが用いられることにより絶縁破壊電界が高い。このため、各スイッチング素子11,12のドリフト領域54の薄型化及び高濃度化を図ることにより、低いオン抵抗を実現することができる。一方、各スイッチング素子11,12のドリフト領域54を高濃度化した分、空乏層の拡張幅が制限されるため、ゲート・ドレイン間容量Cgdが低下し難い。これにより、図8に示すように、ゲート・ソース間容量をCgsとした場合、Cgs / Cgdの値が小さくなりやすい。

### [0065]

[0066]

図9及び図10は、図7及び図8に基づく回路図であり、下側スイッチング素子12を状態変化させたときの下側スイッチング素子12のドレイン・ソース間電圧 Vdslの変化と、上側スイッチング素子11のドレイン・ソース間電圧 Vdsu、ドレイン・ゲート間電圧 Vdgu、及びゲート・ソース間電圧 Vgsuの変化とを示す模式回路図を示す。

比較例のパワーモジュールにおいて、下側スイッチング素子12をオフ状態からオン状態に変更した場合、図9に示すように、下側スイッチング素子12のドレイン・ソース間電圧Vdslが低下するとともに上側スイッチング素子11のドレイン・ソース間電圧Vdsu及びドレイン・ゲート間電圧Vdguが増加する。このような過渡応答において、上側スイッチング素子11のゲート・ソース間は各接続配線CP1,CP2で短絡されているため、本来ならゲート・ソース間電圧Vgsuが変化することはない。しかし、上側スイッチング素子11のゲート・ソース間には上記インダクタンス成分(Lgp+Lgs)及び寄生ゲート抵抗Rgpが存在するため、瞬間的にゲート・ソース間容量Cgsに分圧が発生する。すなわち瞬間的にゲート・ソース間に正側のサージ電圧が発生する。その結果、ドレイン・ソース間電圧Vdsの変化dVds/dtに起因してゲート・ソース間電圧Vgsuが急激に増加して、しきい値電圧を越えることにより、セルフターンオンが生じるおそれがある。

## [0067]

このようなセルフターンオンの発生を抑制するため、上側スイッチング素子11のゲートに負バイアスを印加する対策が知られている。すなわち、ゲート・ソース間電圧Vgsuを予め負側に維持することによりゲート・ソース間電圧Vgsuとゲートしきい値電圧との差を大きくする。これにより、正側のサージ電圧がゲートに印加されたとしても、ゲートしきい値電圧を越えにくくなる。

## [0068]

ところで、各スイッチング素子11,12は、SiC MOSFETの特性上、ゲート・ソース間電圧Vgsの負側絶対最大定格値がゲート・ソース間電圧Vgsの正側絶対最

10

20

30

40

20

30

40

50

大定格値よりも小さい。一例では、各スイッチング素子11,12のゲート・ソース間電圧 Vgsの負側絶対最大定格値は・10 Vであり、ゲート・ソース間電圧 Vgsの正側絶対最大定格値は26 Vである。このため、ゲート負バイアスを印加すると、ゲート・ソース間電圧 Vgsの負側絶対最大定格値との差が小さくなり、許容可能なゲート・ソース間電圧 Vgsの負側の範囲が狭くなる。

## [0069]

ここで、下側スイッチング素子12をオン状態からオフ状態に変更した場合、図10に示すように、下側スイッチング素子12のドレイン・ソース間電圧Vds1が増加するとともに上側スイッチング素子11のドレイン・ソース間電圧Vdsu及びドレイン・ゲート間電圧Vdguが低下する。このような過渡応答においても同様に、上記インダクタンス成分(Lgp+Lgs)及び寄生ゲート抵抗Rgpに起因して、瞬間的にゲート・ソース間容量Cgsに分圧が発生する。すなわち瞬間的にゲート・ソース間に負側のサージ電圧が発生する。その結果、ドレイン・ソース間電圧Vdsの変化dVds/dtに起因してゲート・ソース間電圧Vgsuが急激に低下することにより、負側絶対最大定格値を下回るおそれがある。特に、上側スイッチング素子11のゲートに負バイアスを印加する場合、ゲート・ソース間電圧Vgsuと負側絶対最大定格値との差が小さくなるため、負側のサージ電圧に起因して、ゲート・ソース間電圧Vgsuが負側絶対最大定格値を下回り易くなる。

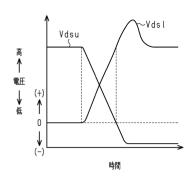

## [0070]

図 1 1 は、比較例のパワーモジュールにおける下側スイッチング素子 1 2 をオン状態からオフ状態に変更した場合の上側スイッチング素子 1 1 のドレイン・ソース間電圧 V d s u、ゲート・ソース間電圧 V g s u、及びドレイン電流 I d u の推移と、下側スイッチング素子 1 2 のドレイン・ソース間電圧 V d s 1 の推移を示している。

### [0071]

図11から分かるとおり、ゲート・ソース間容量 Сgsの分圧であるゲート・ソース間電圧 Vgsuは、上側スイッチング素子11のドレイン・ソース間電圧 Vdsuが最も低下する時刻t1において、負側に最も大きくなる。言い換えれば、ゲート・ソース間電圧 Vgsuは、下側スイッチング素子12のドレイン・ソース間電圧 Vdslが最も高くなったときに負側に最も大きくなる。このように、下側スイッチング素子12が駆動し、上側スイッチング素子11が駆動しない場合には、下側スイッチング素子12のドレイン・ソース間電圧 Vdslによって上側スイッチング素子11のドレイン・ソース間電圧 Vdsuが決められる。

## [0072]

またゲート・ソース間容量 C g s の分圧は、 C g s / C g d の逆比によって決められる。すなわちゲート・ソース間容量 C g s の分圧は、 C g s / C g d が小さくなるにつれて大きくなる。言い換えれば、ゲート・ソース間容量 C g s の分圧は、 C g s / C g d が大きくなるにつれて小さくなる。ところで、各スイッチング素子11,12では、SiCMOSFETの特性上、ゲート・ソース間容量 C g s 及びゲート・ドレイン間容量 C g d とドレイン・ソース間電圧 V d s u との関係は、図12に示すグラフのようになる。詳述すると、ゲート・ソース間容量 C g s は、ドレイン・ソース間電圧 V d s u が変化しない。一方、ゲート・ドレイン間容量 C g d は、ドレイン・ソース間電圧 V d s u が増加するにつれて小さくなる傾向を有する。このため、ドレイン・ソース間電圧 V d s u が比較的低い領域では C g s / C g d が大きくなる。 C g s / C g d は、ドレイン・ソース間電圧 V d s u が高くなるにつれて大きくなる。

## [0073]

上側スイッチング素子11のゲート・ソース間電圧Vgsuは、瞬間的には上側スイッチング素子11のドレイン・ソース間電圧Vdsuの変化に伴い変化するため、ドレイン・ソース間電圧Vdsuの変化速度を低減する必要がある。また、上側スイッチング素子11のドレイン・ソース間電圧Vdsuが下側スイッチング素子12のドレイン・ソース

20

30

40

50

間電圧 V d s l に伴い変化するため、上側スイッチング素子 1 1 のゲート・ソース間電圧 V g s u のサージ電圧を低減するためには、下側スイッチング素子 1 2 のドレイン・ソース間電圧 V d s l の変化速度を低減すればよい。下側スイッチング素子 1 2 のドレイン・ソース間電圧 V d s l の変化速度は、ゲート・ドレイン間容量 C g d によって概ね決められる。詳述すると、ドレイン・ソース間電圧 V d s l の変化速度は、ゲート・ドレイン間容量 C g d が大きくなるにつれて遅くなる。

### [0074]

そこで、本実施形態のパワーモジュール1は、上側スイッチング素子11のゲート端子11g及びドレイン端子11dに電気的に接続された上側コンデンサ13と、下側スイッチング素子12のゲート端子12g及びドレイン端子12dに電気的に接続された下側コンデンサ14とを有する。

### [0075]

こ の 構 成 に よ れ ば 、 例 え ば 下 側 ス イ ッ チ ン グ 素 子 1 2 が オ フ 状 態 か ら オ ン 状 態 に 変 更 す る場合、ゲート電流が下側コンデンサ14を充電することによりドレイン・ソース間電圧 Vdslの変化速度が遅くなる。これに伴い、上側スイッチング素子11のドレイン・ソ ース間電圧Vdsuの変化速度が遅くなる。したがって、上側スイッチング素子11のゲ ート・ソース間電圧 V g s u の変化が抑制されるため、セルフターンオンの発生を抑制す ることができる。また、例えば下側スイッチング素子12がオン状態からオフ状態に変更 する場合、ゲート端子12gに下側コンデンサ14が放電することにより下側スイッチン グ素子12のドレイン・ソース間電圧Vdslの変化速度が遅くなる。これに伴い、上側 スイッチング素子11のドレイン・ソース間電圧Vdsuの変化速度が遅くなることによ り、ゲート・ソース間電圧Vgsuの変化が抑制される。したがって、ゲート・ソース間 電圧Vgsuが負側絶対最大定格値を下回ることが抑制される。なお、上側スイッチング 素 子 1 1 が オン 状 態 と オ フ 状 態 と を 切 り 替 え る 場 合 を 想 定 し て 、 上 側 ス イ ッ チ ン グ 素 子 1 1にも上側コンデンサ13が接続されているが、上側コンデンサ13は、上側スイッチン グ素子11の寄生ゲート抵抗Rgpよりも外側に接続されているため、下側スイッチング 素子12のスイッチング時の瞬間的な挙動に対してCgs/Cgdを小さくさせる効果は 薄く、ゲート・ソース間容量Cgsへの分圧増加が抑制されるため、効果的に上側スイッ チング素子11のゲート・ソース間電圧Vgsuのサージ電圧を抑制することができる。

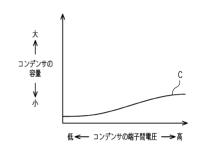

## [0076]

また、上側コンデンサ 1 3 及び下側コンデンサ 1 4 は、図 1 3 に示すような端子間電圧と容量との関係を有することが好ましい。詳述すると、上側コンデンサ 1 3 及び下側コンデンサ 1 4 の端子間電圧がそれぞれ大きくなるにつれて上側コンデンサ 1 3 及び下側コンデンサ 1 4 の容量がそれぞれ増加する。本実施形態では、上側コンデンサ 1 3 及び下側コンデンサ 1 4 の端子間電圧が高い領域における容量は、ドレイン・ソース間電圧 V d s u が高い領域におけるゲート・ドレイン間容量 C g d と同等レベルである。

### [0077]

この構成によれば、例えば下側スイッチング素子12がオン状態からオフ状態に変更する場合、下側スイッチング素子12のドレイン・ソース間電圧Vdslが高くなることにより、下側コンデンサ14の電圧変化に必要な電荷量が増加するため、下側スイッチング素子12のドレイン・ソース間電圧Vdslの変化速度がより遅くなる。これに伴い、上側スイッチング素子11のドレイン・ソース間電圧Vdsuの変化速度がより遅くなることにより、ゲート・ソース間電圧Vgsuの変化が一層抑制される。

## [0078]

また、例えば下側スイッチング素子12がオン状態からオフ状態に変更する場合、上側スイッチング素子11のドレイン・ソース間電圧Vdsuが低くなることにより、上側コンデンサ13の端子間電圧が低くなり、上側コンデンサ13の容量が小さくなる。ここで、上述のとおり、上側コンデンサ13は上側スイッチング素子11の寄生ゲート抵抗Rgpの外側に接続されているため、下側スイッチング素子12のスイッチング時の瞬間的な

挙動に対してCgs/Cgdを小さくさせる効果は薄いが、寄生ゲート抵抗Rgpが極端に小さい場合などは影響が全く無いわけではないため、上側コンデンサ13の低電圧印加時の容量が大きいと、上側スイッチング素子11のドレイン・ソース間電圧Vdsuに対する上側スイッチング素子11のゲート・ソース間電圧Vgsuの分圧が大きくなり、ゲート・ソース間電圧Vgsuの変化が大きくなってしまう。しかし、図14に示すように、上側スイッチング素子11のドレイン・ソース間電圧Vdsuが低い場合は上側コンデンサ13の容量が小さいため、Cgs/Cgdを小さくする影響を抑制することができる

### [0079]

(シミュレーション結果)

比較例及び本実施形態のパワーモジュール1において、上側スイッチング素子11をオフし、下側スイッチング素子12をオンオフする場合における負側のサージ電圧の発生とスイッチング損失との関係について、図7及び図15に示す模式的な回路構成に基づいてシミュレーションを行った。図7は比較例のパワーモジュールの模式的な回路構成を示し、図15は本実施形態のパワーモジュール1において図7と同様の外部接続を行った場合の模式的な回路構成を示す。

## [0800]

図15の回路構成では、上側スイッチング素子11のソースとゲートとが短絡され、下側スイッチング素子12のゲートに下側ゲート駆動回路3が電気的に接続されている。ゲートと下側ゲート駆動回路3との間には、ゲート抵抗8が設けられている。ゲート抵抗8の第1端子は下側スイッチング素子12のゲートに接続され、ゲート抵抗8の第2端子は下側ゲート駆動回路3に接続されている。下側コンデンサ14の第1端子は下側スイッチング素子12のドレインに接続され、下側コンデンサ14の第2端子はケート抵抗8の第2端子に接続されている。上側スイッチング素子11のドレインには電源ESの正側端子が電気的に接続され、下側スイッチング素子11のドレインには電源ESの負側端子が電気的に接続されている。図15の回路構成は、電源ESの正側端子と上側スイッチング素子11のドレインとの間と、上側スイッチング素子11のソースと下側スイッチング素子12のドレインとの間とを繋ぐ配線9を有する。配線9は、インダクタ負荷9aを有する。

[0081]

比較例のパワーモジュールでは、ゲート抵抗 8 を 2 、 3 、 4 、 及び 5 と変化させた場合のシミュレーションを行った。ここで、比較例及び本実施形態のパワーモジュールの回路構成であってゲート抵抗 8 が 2 の場合を基準条件と規定する。

[0082]

図16に示すように、比較例のパワーモジュールでは、ゲート抵抗8を大きくすることにより、下側スイッチング素子12のスイッチング速度(ドレイン・ソース間電圧Vds 1の変化速度)が遅くなることにより負側のサージ電圧の絶対値が小さくなる一方、ゲート抵抗8を大きくすることにより、スイッチング損失が急激に大きくなる。

[0083]

本実施形態のパワーモジュール 1 では、上側コンデンサ 1 3 及び下側コンデンサ 1 4 の容量を 5 0 p F 、 1 0 0 p F 、 及び 1 5 0 p F と変化させた場合のシミュレーションを行った。

[0084]

図16に示すように、本実施形態のパワーモジュール1では、上側コンデンサ13及び下側コンデンサ14により、基準条件よりも負側のサージ電圧の絶対値が小さくなる。そして上側コンデンサ13及び下側コンデンサ14の容量が大きくなるにつれて負側のサージ電圧の絶対値が小さくなる。一方、上側コンデンサ13及び下側コンデンサ14の容量が大きくなるにつれてスイッチング損失が大きくなるが、比較例のパワーモジュールのようにゲート抵抗8を大きくする場合に比べ、スイッチング損失が小さくなる。

### [0085]

本実施形態によれば、以下の効果が得られる。

10

20

30

20

30

40

50

(1-1)パワーモジュール1は、上側スイッチング素子11のドレイン端子11d及 びゲート端子11gに電気的に接続される上側コンデンサ13と、下側スイッチング素子 1 2 のドレイン端子 1 2 d 及びゲート端子 1 2 g に電気的に接続される下側コンデンサ 1 4とを有する。この構成によれば、例えば下側スイッチング素子12がオン状態からオフ 状態に変化するとき、下側コンデンサ14によって下側スイッチング素子12のドレイン ・ソース間電圧Vdslの変化速度が遅くなる。これにより、上側スイッチング素子11 のドレイン・ソース間電圧 V d s u の変化速度が遅くなるため、上側スイッチング素子 1 1のゲート・ソース間電圧Vgsuの変化速度が遅くなる。したがって、上側スイッチン グ素子11のゲート・ソース間電圧 V g s u のサージ電圧の増加が抑制されるため、上側 スイッチング素子11のゲート・ソース間電圧Vgsuの変動を低減することができる。 また例えば上側スイッチング素子11がオン状態からオフ状態に変化するとき、上側コン デンサ 1 3 によって上側スイッチング素子 1 1 のドレイン・ソース間電圧 V d s u の変化 速度が遅くなる。これにより、下側スイッチング素子12のドレイン・ソース間電圧Vd slの変化速度が遅くなるため、下側スイッチング素子12のゲート・ソース間電圧Vg s 1 の変化速度が遅くなる。これにより、下側スイッチング素子 1 2 のゲート・ソース間 電圧Vgslのサージ電圧の増加が抑制されるため、下側スイッチング素子12のゲート ・ソース間電圧Vgslの変動を低減することができる。

[0086]

(1 - 2)上側コンデンサ13は、上側スイッチング素子11のドレイン・ソース間電圧 V d s u が正の値の場合に容量が増加するように構成されている。下側コンデンサ14は、下側スイッチング素子12のドレイン・ソース間電圧 V d s l が正の値の場合に容量が増加するように構成されている。この構成によれば、ドレイン・ソース間電圧 V d s が高い領域においてゲート・ドレイン間容量 C g d をより増加させることができ、ゲート・ソース間電圧 V g s の変動を好適に抑制することができる。

[0087]

(1-3)パワーモジュール1は、複数個(2個)の上側スイッチング素子11が互いに並列に接続され、複数個(2個)の下側スイッチング素子12が互いに並列に接続されているため、複数個の上側スイッチング素子11のオン抵抗及び複数個の下側スイッチング素子12のオン抵抗が小さくなる。したがって、パワーモジュール1の導通損失を低減することができる。

[0088]

(1-4)上側スイッチング素子11のドレイン・ゲート間電圧Vdgu及び下側スイッチング素子12のドレイン・ゲート間電圧Vdglはそれぞれ高電圧が印加されるため、上側コンデンサ13及び下側コンデンサ14に対して十分な耐圧及び絶縁距離が必要となる。このような実情に対して、本実施形態のパワーモジュール1は、基板20に実装された上側スイッチング素子11、下側スイッチング素子12、上側コンデンサ13、及び下側コンデンサ14を封止する封止樹脂40を有する。この封止樹脂40によって沿面放電を抑制することができるため、上側コンデンサ13及び下側コンデンサ14の耐圧及び絶縁距離を確保することができる。

[0089]

(1-5)第2方向Yにおいて、出力配線部22の一方側に第1入力配線部23が配置され、出力配線部22の他方側に第2入力配線部24が配置されている。上側スイッチング素子11は第1入力配線部23に実装され、下側スイッチング素子12は出力配線部22に実装されている。この構成によれば、上側スイッチング素子11のソース電極41と出力配線部22とを繋ぐ上側電力用ワイヤ44の長さを短くすることができ、下側スイッチング素子12のソース電極41と第2入力配線部24とを繋ぐ下側電力用ワイヤ46の長さを短くすることができる。

[0090]

(1-6)上側コンデンサ13が上側アイランド部37に電気的に接続され、上側アイ

20

30

40

50

ランド部 3 7 が上側接続用ワイヤ 3 9 Uにより第 1 入力配線部 2 3 に電気的に接続されている。これにより、上側コンデンサ 1 3 が第 1 上側制御配線部 2 5 の屈曲部 2 5 c に対して、上側コンデンサ 1 3 の第 1 端子及び第 2 端子の配列方向が第 1 方向 X となる状態で接続することができる。したがって、第 1 上側制御配線部 2 5 において上側スイッチング素子 1 1 のゲート電極 4 2 に接続された上側制御用ワイヤ 4 5 が接続された部分から第 1 上側制御端子部材 3 3 が接続される部分までの範囲において、上側コンデンサ 1 3 が第 1 上側制御配線部 2 5 の凹部 2 5 d 以外の部分で接続することができる。

### [0091]

また下側コンデンサ14が下側アイランド部38に電気的に接続され、下側アイランド部38が下側接続用ワイヤ39Lにより出力配線部22に電気的に接続されている。これにより、下側コンデンサ14が第1下側制御配線部27の屈曲部27cに対して、下側コンデンサ14の第1端子及び第2端子の配列方向が第1方向Xとなる状態で接続することができる。したがって、第1下側制御配線部27において下側スイッチング素子12のゲート電極42に接続された下側制御用ワイヤ47が接続された部分から第1下側制御配線・コンデンサ14が第1下側制御配線・コンデンサ14が第1下側制御配線・コンデンサ14が第1下側制御配線・コンデンサ14が第1下側制御配線・コンデンサ14が第1下側制御配線・コンデンサ14が第1下側制御配線・15が下側接続用ワイヤ39Lによって出力配線部22と電気的に接続されるため、下側アイランド部38と出力配線部22との間に他の部材(例えば第2入力配線部24)が存在しても、その他の部材を跨いで電気的に接続することができる。

### [0092]

(1-7)下側スイッチング素子12は、出力配線部22の第1部分22aにおいて第2方向Yの第2入力配線部24寄りに配置されている。このため、出力配線部22の第1部分22aにおいて、上側スイッチング素子11に接続された上側電力用ワイヤ44を出力配線部22に接続するためのスペースを確保することができる。したがって、上側電力用ワイヤ44を出力配線部22に容易に接続することができる。

## [0093]

(1-8)出力配線部22の第1方向Xの長さは、下側スイッチング素子12が1~5個配置可能な長さに設定されている。第1入力配線部23の第1方向Xの長さは、上側スイッチング素子11が1~5個配置可能な長さに設定されている。この構成によれば、パワーモジュール1の同一サイズにおいて、オン抵抗が異なるパワーモジュール1のバリエーションを提供することができる。

### [0094]

(1-9)上側スイッチング素子11と上側コンデンサ13とが個別のチップとして設けられ、下側スイッチング素子12と下側コンデンサ14とが個別のチップとして設けられている。この構成によれば、上側コンデンサ13及び下側コンデンサ14の個数及び容量を任意に設定可能となるため、サージ電圧抑制のために適切な上側コンデンサ13及び下側コンデンサ14を用いることができる。

## [0095]

## (第2実施形態)

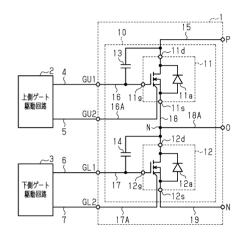

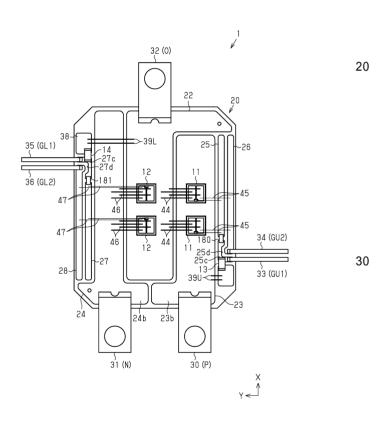

図17~図30を参照して、第2実施形態のパワーモジュール1について説明する。本実施形態のパワーモジュール1は、第1実施形態のパワーモジュール1と比較して、上側コンデンサ13及び下側コンデンサ14を省略した点と、上側ダイオード71及び下側ダイオード72を追加した点とが異なる。以下の説明において、第1実施形態のパワーモジュール1と共通の構成については同一符号を付し、その説明を省略する。また、図18~図24は、本実施形態のパワーモジュール1の構成の一例を示している。なお、本実施形態のパワーモジュール1の構成に限られず、種々の変更が可能である。

## [0096]

図17及び図19に示すように、上側ダイオード71は上側スイッチング素子11とは 別体として設けられ、下側ダイオード72は下側スイッチング素子12とは別体として設

20

30

40

50

けられている。図17に示すとおり、上側ダイオード71のカソードは、上側スイッチング素子11のドレイン端子11dと第1入力端子Pとを繋ぐ第1配線15に電気的に接続されている。上側ダイオード71のアノードは、上側スイッチング素子11のソース端子11gと下側スイッチング素子12のドレイン端子12dとを繋ぐ第4配線18においてノードNよりも上側スイッチング素子11側の部分に電気的に接続されている。下側ダイオード72のカソードは、第4配線18においてノードNよりも下側スイッチング素子12側の部分に電気的に接続されている。下側ダイオード72のアノードは、下側スイッチング素子12のソース端子12sと第2入力端子Nとを繋ぐ第5配線19に電気的に接続されている。本実施形態では、上側ダイオード71及び下側ダイオード72はそれぞれ、ショットキーバリアダイオードが用いられている。上側ダイオード71及び下側ダイオード72のそれぞれの順方向しきい値電圧は、上側スイッチング素子11のボディダイオード11a及び下側スイッチング素子12のボディダイオード11a及び下側スイッチング素子12のボディダイオード11a及び下側スイッチング素子12のボディダイオード11a

## [0097]

上側スイッチング素子11及び下側スイッチング素子12のそれぞれの個数は任意に変更可能である。例えば、上側スイッチング素子11及び下側スイッチング素子12のそれぞれの個数は、予め設定されたオン抵抗となるように設定される。上側スイッチング素子11は互いに並列に接続される。すなわち、複数の上側スイッチング素子11のドレイン端子11dが互いに接続され、複数の上側スイッチング素子11gが互いに接続され、複数の上側スイッチング素子11gが互いに接続され、複数の上側スイッチング素子11gが互いに接続される。また下側スイッチング素子11のゲート端子11gが互いに接続される。また下側スイッチング素子12が複数個設けられる場合、複数の下側スイッチング素子12dが互いに接続される。すなわち、複数の下側スイッチング素子12のゲート端子12gが互いに接続される。本実施形態では、上側スイッチング素子11は3個設けられ、下側スイッチング素子12は3個設けられている。

## [0098]

また上側ダイオード71及び下側ダイオード72のそれぞれの個数は任意に変更可能である。例えば、上側ダイオード71及び下側ダイオード72のそれぞれの個数は任意に変更可能でイッチング素子11及び下側スイッチング素子12を避けて流す還流電流の大きさに基基でいて設定される。上側ダイオード71が複数個設けられる場合、複数の上側ダイオード71のアノードが互いに接続される。複数の上側ダイオード71のカソードが互いに接続される。複数の上側ダイオード71のアノードが互いに接続される。複数の上側ダイオード71のアノードが多の上側ダイオード71のアノードが多の上側ダイオード71のアノードが多に接続される。また下側ダイオード72が複数の下側ダイオード72のアノードが互いに接続される。複数の下側ダイオード72のカソードが互いに接続される。複数の下側ダイオード72のカソードは第4配線18におけるノードNよりも下側スイッチング素子12側の部分に接続なれ、複数の下側ダイオード72のアノードは第5配線19に接続される。本実施形態では、上側ダイオード71は2個設けられ、下側ダイオード72は2個設けられている。

### [0099]

パワーモジュール 1 は、上側ダイオード 7 1 が許容可能な D C 定格電流が、上側スイッチング素子 1 1 が許容可能な D C 定格電流未満となり、かつ下側ダイオード 7 2 が許容可能な D C 定格電流が、下側スイッチング素子 1 2 が許容可能な D C 定格電流未満となるように構成されている。ここで、 D C 定格電流は、絶対最大定格の直流電流である。上側ダイオード 7 1 及び上側スイッチング素子 1 1 がそれぞれ複数個設けられる場合、パワーモジュール 1 は、複数の上側ダイオード 7 1 の D C 定格電流の合計が、複数の上側スイッチング素子 1 1 の D C 定格電流の合計未満となるように構成されている。また下側ダイオード 7 2 及び下側スイッチング素子 1 2 がそれぞれ複数個設けられる場合、パワーモジュー

20

30

40

50

ル1は、複数の下側ダイオード72のDC定格電流の合計が、複数の下側スイッチング素子12のDC定格電流の合計未満となるように構成されている。

## [0100]

一例では、パワーモジュール1は、上側ダイオード71の個数が上側スイッチング素子11の個数よりも少なく、かつ下側ダイオード72の個数が下側スイッチング素子12の個数よりも少なくなるように構成されている。上述したとおり、本実施形態では、図19に示すとおり、パワーモジュール1は、3個の上側スイッチング素子11、3個の下側スイッチング素子12、2個の上側ダイオード71、及び2個の下側ダイオード72を有する。また例えば、1つの上側ダイオード71が許容可能なDC定格電流が、1つの上側スイッチング素子11が許容可能なDC定格電流未満としてもよい。また1つの下側ダイオード72が許容可能なDC定格電流が、1つの下側スイッチング素子12が許容可能なDC定格電流が、1つの下側スイッチング素子12の個数と上側ダイオード71の個数とが互いに等しくてもよい。また下側スイッチング素子12の個数と下側ダイオード72の個数とが互いに等しくてもよい。

### [ 0 1 0 1 ]

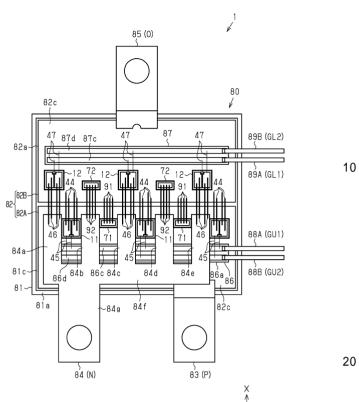

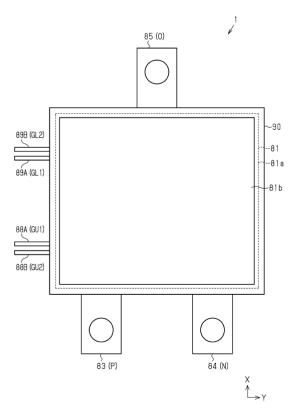

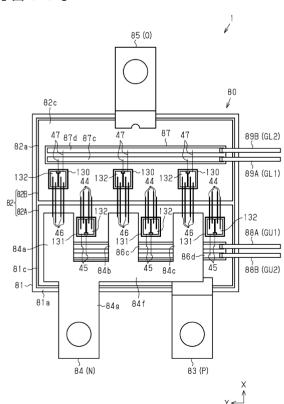

図18~図20に示すように、パワーモジュール1は、平面視において矩形状の基板80と、各スイッチング素子11,12及び各ダイオード71,72を封止する封止樹脂90とを備える。以降の説明では、基板80の縦方向を「第1方向X」と規定し、基板80の横方向(長手方向)を「第2方向Y」と規定し、基板80の板厚方向を「第3方向Z」と規定する。

### [ 0 1 0 2 ]

基板 8 0 は、セラミック基板 8 1 とグラファイト基板 8 2 とが積層された構成を有する。グラファイト基板 8 2 は、第 1 基板 8 2 A 及び第 2 基板 8 2 B を有する。第 1 基板 8 2 A と第 2 基板 8 2 B は、第 1 方向 X において隙間を空けて並べて配置されている。第 1 基板 8 2 A 及び第 2 基板 8 2 B はそれぞれ、第 2 方向 Y が長手方向となる矩形状に形成されている。

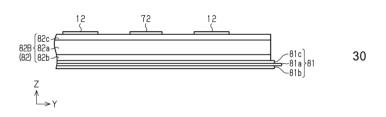

## [0103]

図19、図21、及び図22に示すように、セラミック基板81は、セラミック材料か らなる本体部81aと、本体部81aの裏面側に設けられた裏面金属層81bと、本体部 81aの表面側に設けられた表面金属層81cとを有する。裏面金属層81bは、例えば 銅( C u )からなり、 本体部 8 1 a の裏面に接着剤等により取り付けられている。 表面金 属 層 8 1 c は、 例 え ば 銅 ( C u ) か ら な り 、 本 体 部 8 1 a の 表 面 に 接 着 剤 等 に よ り 取 り 付 けられている。図20~図22に示すとおり、平面視における本体部81aの面積は、平 面視における表面金属層81cの面積及び裏面金属層81bの面積のそれぞれよりも大き い。すなわち、表面金属層81cの外周縁は、本体部81aの外周縁よりも内側に形成さ れ、裏面金属層81bの外周縁は、本体部81aの外周縁よりも内側に形成されている。 また例えば、本体部81aの厚さは、裏面金属層81b及び表面金属層81cの厚さのそ れぞれよりも薄い。裏面金属層81bの厚さと表面金属層81cの厚さとは互いに等しい 。裏面金属層81bの平面視における形状と表面金属層81cの平面視における形状とは 互いに等しい。このように、裏面金属層 8 1 b の体積と表面金属層 8 1 c の体積とは互い に等しい。本実施形態では、本体部81aの厚さが0.32mmであり、裏面金属層81 b の厚さが 0 . 4 mmであり、表面金属層 8 1cの厚さが 0 . 4 mmである。なお、本体 部81a、裏面金属層81b、及び表面金属層81cの厚さはそれぞれ、任意に変更可能 である。一例では、本体部81aの厚さ、裏面金属層81bの厚さ、及び表面金属層81 c の厚さが互いに等しくてもよい。図21に示すように、裏面金属層81bは封止樹脂9 0から露出する一方、本体部81aは封止樹脂90から露出していない。すなわち、封止 樹 脂 9 0 は、 本 体 部 8 1 a の 裏 面 金 属 層 8 1 b 側 の 部 分 を 覆 っ て い る 。 こ れ に よ り 、 セ ラ ミック基板81が封止樹脂90から剥離することを抑制することができる。

### [0104]

図19に示すように、第1基板82A及び第2基板82Bはそれぞれ、セラミック基板

20

30

40

50

8 1 の表面金属層 8 1 c に積層されている。第 1 基板 8 2 A は、グラファイトからなる本 体部82aと、本体部82aの裏面側に設けられた裏面金属層82bと、本体部82aの 表面側に設けられた表面金属層82cとを有する。裏面金属層82bは、例えば銅(Cu )からなる。 裏面金属層 8 2 b は、セラミック基板 8 1 の表面金属層 8 1 c と半田等によ って貼り合わせられている。表面金属層82cは、例えば銅(Cu)からなる。図19及 び図20に示すとおり、平面視における本体部82aの面積は、平面視における表面金属 層 8 2 c の面 積 及 び 裏 面 金 属 層 8 2 b の 面 積 の そ れ ぞ れ と 等 し い 。 第 1 基 板 8 2 A の 外 周 縁は、セラミック基板81の表面金属層81cの外周縁よりも内側に形成されている。ま た例えば、本体部82aの厚さは、裏面金属層82bの厚さ及び表面金属層82cの厚さ のそれぞれよりも厚い。一例では、本体部82aは、裏面金属層82bの厚さ及び表面金 属層82cの厚さのそれぞれの2倍以上の厚さを有する。また裏面金属層82bの厚さと 表面金属層82cの厚さは互いに等しい。すなわち裏面金属層82bの体積と表面金属層 82cの体積とは互いに等しい。また裏面金属層82bの厚さ及び表面金属層82cの厚 さ は そ れ ぞ れ 、 セ ラ ミ ッ ク 基 板 8 1 の 裏 面 金 属 層 8 1 b の 厚 さ 及 び 表 面 金 属 層 8 1 c の 厚 さよりも厚い。一例では、裏面金属層82bの厚さ及び表面金属層82cの厚さはそれぞ れ、セラミック基板81の裏面金属層81bの厚さ及び表面金属層81cの厚さの2倍程 度である。本実施形態では、本体部82aの厚さが2.0mmであり、裏面金属層82b の厚さが0.8mmであり、表面金属層82cの厚さが0.8mmである。

[ 0 1 0 5 ]

第1基板82Aの本体部82aは、異方性となる熱伝導性を有する。詳述すると、第1基板82Aの本体部82aは、第2方向Yにおける本体部82aの熱伝導性が第1方向Xにおける本体部82aの熱伝導性よりも低くなるように構成されている。言い換えれば、第1基板82Aの本体部82aの熱伝導率よりも低くなるように構成されている。第1基板82Aの本体部82aの熱伝導率よりも低くなるように構成されている。第1基板82Aの本体部82aの熱伝導性が第1方向Xにおける本体部82aの熱伝導性と等しくなるように構成されている。なお、第1基板82Aの本体部82aは、第1方向Xの熱伝導性と第3方向2の熱伝導性とが互いに異なってもよい。この場合においても第1基板82Aの本体部82aの第2方向Yの熱伝導性が、第1方向Xの熱伝導性及び第3方向2の熱伝導性よりも低いことが好ましい。

[0106]

第2基板82Bの構造は、第1基板82Aの構造と同じであり、本体部82a、裏面金属層82b、及び表面金属層82cを有する。第2基板82Bの裏面金属層82bは、セラミック基板81の表面金属層81cに貼り合わせられている。第2基板82Bの外周縁は、セラミック基板81の表面金属層81cの外周縁よりも内側に形成されている。

[0107]

第2基板82Bの本体部82aは、異方性となる熱伝導性を有する。詳述すると、第2基板82Bの本体部82aは、第2方向Yにおける本体部82aの熱伝導性が第1方向Xにおける本体部82aの熱伝導性よりも低くなるように構成されている。言い換えれば、第2基板82Bの本体部82aは、第2方向Yにおける本体部82aの熱伝導率が第1方向Xにおける本体部82aの熱伝導率よりも低くなるように構成されている。第2基板82Bの本体部82aは、第3方向Zの熱伝導性が第1方向Xにおける本体部82aの熱伝導性と第1方向Xの熱伝導性と第3方向Zの熱伝導性とが互いに異なってもよい。この場合においても第2基板82Bの本体部82aの第2方向Yの熱伝導性が、第1方向Xの熱伝導性及び第3方向Zの熱伝導性よりも低いことが好ましい。

[0108]

図19及び図20に示すように、パワーモジュール1は、第1入力端子部材83、第2入力端子部材84、出力端子部材85、上側信号基板86、下側信号基板87、第1上側制御端子部材88A、第2上側制御端子部材88B、第1下側制御端子部材89A、及び第2下側制御端子部材89Bを有する。第1入力端子部材83はパワーモジュール1の第

20

30

40

50

1 入力端子 P を構成し、第 2 入力端子部材 8 4 はパワーモジュール 1 の第 2 入力端子 N を構成し、出力端子部材 8 5 はパワーモジュール 1 の出力端子 O を構成する。また第 1 上側制御端子部材 8 8 A は第 1 上側制御端子 G U 1 を構成し、第 2 上側制御端子部材 8 8 B は第 2 上側制御端子 G U 2 を構成し、第 1 下側制御端子部材 8 9 A は第 1 下側制御端子 G L 1 を構成し、第 2 下側制御端子部材 8 9 B は第 2 下側制御端子 G L 2 を構成する。第 1 入力端子部材 8 3 、第 2 入力端子部材 8 4 、出力端子部材 8 5 、第 1 上側制御端子部材 8 8 A 、第 2 上側制御端子部材 8 8 B 、第 1 下側制御端子部材 8 9 A 、及び第 2 下側制御端子部材 8 9 B はそれぞれ、銅(C u)からなる。

#### [0109]

第1基板82Aには、第1入力端子部材83、第2入力端子部材84、上側信号基板86、3個の上側スイッチング素子11、及び2個の上側ダイオード71が実装されている。第1基板82Aの表面金属層82cは、上側スイッチング素子11と第1入力端子Pとを繋ぐ第1配線15(ともに図17参照)を構成している。

#### [0110]

第1入力端子部材83は、第1方向Xにおいて第1基板82Aのうちの第2基板82B とは反対側の端部、かつ第2方向Yにおいて第1基板82Aのうちの各上側制御端子部材88A,88B側の部分に位置している。

## [0111]

第2入力端子部材84は、第3方向とにおいて第1基板82Aに対して隙間を空けて対向するように設けられている。第2入力端子部材84は、第1接続部84a、第2接続部84b、第3接続部84c、第4接続部84d、第5接続部84e、連結部84f、及び端子部84gを有する。第1接続部84a、第2接続部84b、第3接続部84c、第4接続部84d、第5接続部84d、第5接続部84d、第5在100元

### [0112]

連 結 部 8 4 f は 、 第 1 方 向 X に お い て 第 1 基 板 8 2 A の う ち の 第 2 基 板 8 2 B 側 と は 反 対側の端部に対して第3方向2に隙間を空けて対向した状態で配置されている。連結部8 4 f は、第 2 方向 Y に延びている。連結部 8 4 f の一部は、第 1 入力端子部材 8 3 の一部 を 第 3 方 向 Z か ら 覆 っ て い る 。 各 接 続 部 8 4 a ~ 8 4 b は 、 連 結 部 8 4 f か ら 第 2 基 板 8 2 B 側に向けて第 1 方向 X に沿って延びている。各接続部 8 4 a ~ 8 4 b は同一形状であ り、第1方向Xが長手方向となる長方形状に形成されている。第2方向Yにおいて各上側 制御端子部材88A,88B側とは反対側の端部から順に、第1接続部84a、第2接続 部 8 4 b 、 第 3 接 続 部 8 4 c 、 第 4 接 続 部 8 4 d 、 及 び 第 5 接 続 部 8 4 e が 互 い に 第 2 方 向Yに間隔を空けて位置している。各接続部84a~84eは、第2方向Yにおいて等間 隔に配置されている。各接続部84a~84eの第1方向Xの長さは互いに等しい。各接 続 部 8 4 a ~ 8 4 e の 先 端 部 の 第 1 方 向 X の 位 置 は 互 い に 等 し い 。 連 結 部 8 4 f は 、 第 2 方向Yに延びており、各接続部84a~84eの接続されている。端子部84gは、第1 方向 X において連結部 8 4 f から各接続部 8 4 a ~ 8 4 e とは反対側に延びている。端子 部 8 4 g は、第 2 方 向 Y において第 1 接続部 8 4 a 及び第 2 接続部 8 4 b に対応する位置 に設けられている。端子部84gの幅寸法(端子部84gの第2方向Yの長さ)は、各接 続 部 8 4 a ~ 8 4 e の 幅 寸 法 ( 各 接 続 部 8 4 a ~ 8 4 e の 第 2 方 向 Y の 長 さ ) よ り も 大 き い。端子部 8 4 g の幅寸法は、出力端子部材 8 5 の幅寸法(出力端子部材 8 5 の第 2 方向 Yの長さ)及び第1入力端子部材83の幅寸法(第1入力端子部材83の第2方向Yの長 さ)と等しい。

## [0113]

図19及び図24に示すとおり、各接続部84a~84eの先端部は、絶縁支持部84 ×を介して第1基板82Aに取り付けられている。絶縁支持部84×は、電気的絶縁性を 有する材料により形成されている。絶縁支持部84×によって第2入力端子部材84が支 持されることにより、第2入力端子部材84が第1基板82Aに対して第3方向Zに隙間 を介して対向することができる。絶縁支持部84×の厚さは、第2入力端子部材84が上 側信号基板86に対して第3方向2に隙間を形成可能となるように設定されている。

## [0114]

3個の上側スイッチング素子11及び2個の上側ダイオード71は、第1基板82Aのうちの第2基板82B側の端部に位置している。3個の上側スイッチング素子11及び2個の上側ダイオード71は、第1基板82Aにおいて熱伝導率(熱伝導性)が低い第2方向Yにおいて互いに隙間を空けて配置されている。詳述すると、上側スイッチング素子11と上側ダイオード71とが第2方向Yにおいて交互に配置されている。すなわち第2方向Yにおいて上側ダイオード71の両側には、上側スイッチング素子11が位置している。第1方向Xにおける上側スイッチング素子11の位置と上側ダイオード71の位置とは互いに等しい。具体的には、第1方向Xにおいて上側スイッチング素子11における第2基板82B側の端縁の位置とが互いに等しい。

## [0115]

3個の上側スイッチング素子11のうちの1個の上側スイッチング素子11は、第2方向Yにおいて第1接続部84aと第2接続部84bとの間に配置されている。3個の上側スイッチング素子11のうちの別の1個の上側スイッチング素子11は、第2方向Yにおいて第3接続部84cと第4接続部84dとの間に配置されている。3個の上側スイッチング素子11の残りの1個の上側スイッチング素子11は、第2方向Yにおいて第2入力端子部材84とは異なる位置に配置されている。

### [0116]

2個の上側ダイオード71のうちの1個の上側ダイオード71は、第2方向Yにおいて第2接続部84bと第3接続部84cとの間に配置されている。2個の上側ダイオード71のうちの残りの1個の上側ダイオード71は、第4接続部84dと第5接続部84eとの間に配置されている。

### [0117]

3個の上側スイッチング素子11及び2個の上側ダイオード71は、第1方向×において各接続部84a~84eの先端縁よりも第2基板82Bとは反対側に位置している。3個の上側スイッチング素子11は、第1方向×において、第1基板82Aのうちの第2基板82B側の端縁と、上側信号基板86のうちの第2基板82B側の端縁との間における上側信号基板86寄りに配置されている。一方、2個の上側ダイオード71は、第1方向×において、第1基板82Aのうちの第2基板82B側の端縁と、上側信号基板86のうちの第2基板82B側の端縁と、上側信号基板86のうちの第2基板82B側の端縁との間における第1基板82Aのうちの第2基板82B側の端縁寄りに配置されている。

## [0118]

上側信号基板 8 6 は、第 1 基板 8 2 A における第 1 入力端子部材 8 3 が配置される領域と 3 個の上側スイッチング素子 1 1 及び 2 個の上側ダイオード 7 1 が配置される領域との間の領域に位置している。上側信号基板 8 6 は、第 2 方向 Y が長手方向となる長方形状に形成されている。

## [0119]

図23に示すように、上側信号基板86は、絶縁基板86a、裏面金属層86b、第1上側制御配線部86c、及び第2上側制御配線部86dを有する。第1上側制御配線部86cは第2配線16の一部を構成し、第2上側制御配線部86dは上側センス配線16Aの一部を構成している。

### [0120]

絶縁基板86aは、電気的絶縁性を有する材料により形成されている。裏面金属層86bは、例えば銅(Cu)からなり、絶縁基板86aの裏面に接着剤等により取り付けられている。各上側制御配線部86c,86dは、絶縁基板86aの表面に接着剤等により取り付けられている。なお、裏面金属層86b及び各上側制御配線部86c,86dは、絶縁基板86aに形成された銅箔のパターンとして構成されてもよい。図23に示すとおり、裏面金属層86bの外周縁は、絶縁基板86aの外周縁よりも内側に形成されている。

10

20

30

40

これにより、封止樹脂 9 0 が絶縁基板 8 6 a の裏面側を覆うため、第 1 基板 8 2 A から上側信号基板 8 6 が剥離することを抑制することができる。

### [0121]

第1上側制御配線部86cと第2上側制御配線部86dとは、第1方向Xにおいて間隔を空けて並べて配置されている。各上側制御配線部86c,86dは、第2方向Yに沿って延びている。第1方向Xにおいて第1上側制御配線部86cは、第2上側制御配線部86dよりも3個の上側スイッチング素子11及び2個の上側ダイオード71側に配置されている。第2方向Yにおいて第1上側制御配線部86cの一方側の端部には、第1上側制御端子部材88Aが取り付けられ、第2上側制御配線部86dの一方側の端部には、第2上側制御端子部材88Bが取り付けられている。各上側制御端子部材88A,88Bは、封止樹脂90から第2方向Yに突出している。

[0122]

第2基板82Bには、出力端子部材85、下側信号基板87、3個の下側スイッチング素子12、及び2個の下側ダイオード72が実装されている。第2基板82Bの表面金属層82cは、上側スイッチング素子11のソース端子11sと下側スイッチング素子12のドレイン端子12dとを繋ぐ第4配線18の一部を構成している。

[0123]

出力端子部材 8 5 は、第 2 基板 8 2 B の表面金属層 8 2 c に取り付けられている。出力端子部材 8 5 は、第 1 方向 X において第 2 基板 8 2 B のうちの第 1 基板 8 2 A 側とは反対側の端部、かつ第 2 方向 Y において第 2 基板 8 2 B の中央部に位置している。出力端子部材 8 5 は、第 1 方向 X に延び、封止樹脂 9 0 から外部に突出している(図 1 7 参照)。

[0124]

3個の下側スイッチング素子12及び2個の下側ダイオード72は、第2基板82Bのうちの第1基板82A側の端部に位置している。3個の下側スイッチング素子12及び2個の下側ダイオード72は、第2基板82Bにおいて熱伝導率(熱伝導性)が低い第2方向Yにおいて互いに隙間を空けて配置されている。詳述すると、下側スイッチング素子12と下側ダイオード72とが第2方向Yにおいて交互に配置されている。すなわち第2方向Yにおいて下側ダイオード72の両側には、下側スイッチング素子12が位置している。第1方向Xにおける下側スイッチング素子12の位置と下側ダイオード72の位置とは互いに等しい。具体的には、第1方向Xにおいて下側スイッチング素子12における第1基板82A側の端縁の位置とが互いに等しい。

[0125]

3個の下側スイッチング素子12は、第1方向Xにおいて、第2基板82Bのうちの第1基板82A側の端縁と、下側信号基板87のうちの第1基板82A側の端縁との間における下側信号基板87寄りに配置されている。一方、2個の下側ダイオード72は、第1方向Xにおいて、第2基板82Bのうちの第1基板82A側の端縁と、下側信号基板87のうちの第1基板82A側の端縁寄りに配置されている。

[0126]

下側信号基板 8 7 は、第 2 基板 8 2 B における出力端子部材 8 5 が配置される領域と 3 個の下側スイッチング素子 1 2 及び 2 個の下側ダイオード 7 2 が配置される領域との間の領域に位置している。下側信号基板 8 7 は、第 2 方向 Y が長手方向となる長方形状に形成されている。

[0127]

次に、各スイッチング素子11,12及び各ダイオード71,72の電気的な接続構成について説明する。

3個の上側スイッチング素子11はそれぞれ、ゲート電極42(図5(a)参照)が上側信号基板86側となるように配置されている。ゲート電極42は、1本の上側制御用ワイヤ45により第1上側制御配線部86cに電気的に接続されている。ソース電極41(

10

20

30

20

30

40

50

図5(a)参照)は、1本の上側制御用ワイヤ45により第2上側制御配線部86dに電気的に接続されている。またソース電極41は、4本の上側電力用ワイヤ44により第2基板82Bの表面金属層82cに電気的に接続されている。3個の上側スイッチング素子11のドレイン電極48(図6参照)はそれぞれ、半田等により第1基板82Aの表面金属層81cに電気的に接続されている。

## [0128]

2個の上側ダイオード 7 1 のカソードはそれぞれ、半田等により第 1 基板 8 2 A の表面 金属層 8 1 c に電気的に接続されている。 2 個の上側ダイオード 7 1 のアノードはそれぞれ、上側ダイオード用接続部材の一例として 4 本の上側ダイオード用ワイヤ 9 1 により第 2 基板 8 2 B の表面金属層 8 2 c に電気的に接続されている。本実施形態の上側ダイオード用ワイヤ 9 1 の線径は、上側電力用ワイヤ 4 4 の線径と等しい。 4 本の上側ダイオード用ワイヤ 9 1 は、そのインダクタンスが 4 本の上側電力用ワイヤ 4 4 のインダクタンスよりも小さくなるように構成されることが好ましい。一例では、 4 本の上側ダイオード用ワイヤ 9 1 の長さはそれぞれ、 4 本の上側電力用ワイヤ 4 4 の長さよりも短い。なお、上側ダイオード用ワイヤ 9 1 のインダクタンスが上側電力用ワイヤ 4 4 のインダクタンスよりも小さくなる構成の一例として、上側ダイオード用ワイヤ 9 1 の線径が上側電力用ワイヤ 4 4 の線径よりも大きくなるように構成されてもよい。

### [0129]

3個の下側スイッチング素子12はそれぞれ、ゲート電極42が下側信号基板87側となるように配置されている。ゲート電極42は、1本の下側制御用ワイヤ47により第1下側制御配線部87cに電気的に接続されている。ソース電極41は、1本の下側制御用ワイヤ47により第2下側制御配線部87dに電気的に接続されている。またソース電極41は、4本の下側電力用ワイヤ46により第1基板82Aの表面金属層81cに電気的に接続されている。3個の下側スイッチング素子12のドレイン電極48はそれぞれ、半田等により第2基板82Bの表面金属層82cに電気的に接続されている。

## [0130]

2個の下側ダイオード72のカソードはそれぞれ、半田等により第2基板82Bの表面金属層82cに電気的に接続されている。2個の下側ダイオード72のアノードはそれぞれ、下側ダイオード用接続部材の一例として4本の下側ダイオード用ワイヤ92により第1基板82Aの表面金属層81cに電気的に接続されている。下側ダイオード用ワイヤ92の線径は、下側電力用ワイヤ46の線径と等しい。また下側ダイオード用ワイヤ92の線径は、上側ダイオード用ワイヤ91の線径と等しい。4本の下側ダイオード用ワイヤ92のは、そのインダクタンスが4本の下側電力用ワイヤ46のインダクタンスよりも小さくなるように構成されることが好ましい。一例では、4本の下側ダイオード用ワイヤ92の長さはそれぞれ、4本の下側電力用ワイヤ46の長さよりも短い。なお、下側ダイオード用ワイヤ92のはそれぞれ、4本の下側電力用ワイヤ46の行ンダクタンスよりも小さくなる構成の一例として、下側ダイオード用ワイヤ92の線径が下側電力用ワイヤ46の線径よりも大きくなるように構成されてもよい。

## [0131]

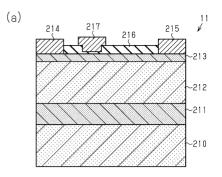

(上側ダイオード及び下側ダイオードの構成)

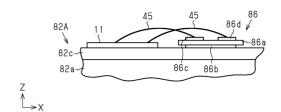

図 2 5 及び図 2 6 を参照して、上側ダイオード 7 1 及び下側ダイオード 7 2 の構成について説明する。なお、上側ダイオード 7 1 及び下側ダイオード 7 2 は同じ構成であるため、以下の説明では、上側ダイオード 7 1 の構成を説明し、下側ダイオード 7 2 の構成の説明を省略する。また、上側ダイオード 7 1 及び下側ダイオード 7 2 の構成は、図 2 5 及び図 2 6 に示す構成に限れず、種々の変更が可能である。

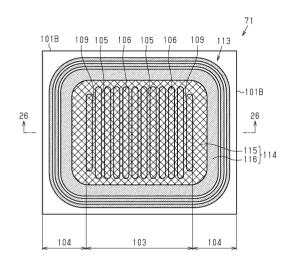

## [0132]

図 2 5 は、上側ダイオード 7 1 の構成の一例を示している。上側ダイオード 7 1 は、ワイドギャップ半導体からなる。上側ダイオード 7 1 は、4 H - S i C (絶縁破壊電界が約2 . 8 M V / c m であり、バンドギャップの幅が約3 . 2 6 e V のワイドバンドギャップ半導体)が用いられている。なお、上側ダイオード 7 1 に用いられるワイドバンドギャッ

20

30

40

50

プ半導体は、シリコンカーバイド(SiC)に限られず、窒化ガリウム(GaN)、酸化ガリウム(Ga2〇3)、ダイヤモンド等であってもよい。窒化ガリウム(GaN)は、その絶縁破壊電界が約3 M V / c mであり、バンドギャップの幅が約3 . 4 2 e V である。酸化ガリウム(Ga2〇3)は、その絶縁破壊電界が約8 M V / c mであり、バンドギャップの幅が約4 . 8 e V である。ダイヤモンドは、その絶縁破壊電界が約8 M V / c mであり、バンドギャップの幅が約5 . 4 7 e V である。

[ 0 1 3 3 ]

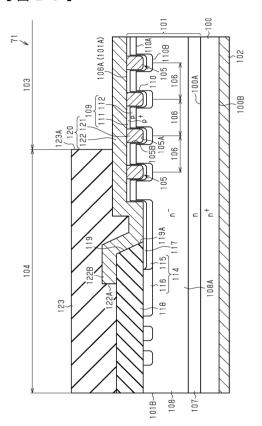

図 2 6 に示すように、上側ダイオード 7 1 は、 n <sup>+</sup>型の S i C 基板 1 0 0 と、 n <sup>+</sup>型の S i C 基板 1 0 0 の表面 1 0 0 A に積層されたエピタキシャル層 1 0 1 とを有する。

SiC基板100の裏面100Bには、その全域を覆うようにカソード電極102が配置されている。カソード電極102は、SiC基板100との間にオーミック接合を形成している。カソード電極102は、例えばSiC基板50側から順にチタン(Ti)、ニッケル(Ni)、金(Au)、及び銀(Ag)が積層された積層構造(Ti/Ni/Au/Ag)を適用することができる。

[0134]

SiC基板100は、例えば(0001)面(Si面)を主面とする基板である。したがって、SiC基板100の表面100A(主面)にエピタキシャル成長によって積層されるエピタキシャル層101は、(0001)面を主面として積層される。この場合、SiC基板100の裏面100Bは、(000-1)面(C面)である。なお、SiC基板100は、その表面100Aが(000-1)面で、裏面100Bが(0001)面であってもよい。また、SiC基板100は、0~10度のオフ角を有することが好ましい。

[0135]

エピタキシャル層 1 0 1 には、活性領域 1 0 3 と、活性領域 1 0 3 を取り囲む外周領域 1 0 4 とが設定されている。

活性領域103においてエピタキシャル層101は、トレンチ105が形成された表面101Aを有する。トレンチ105は、互いに間隔を空けて複数個形成されている。これにより、トレンチ105は、活性領域103に複数の単位セル106を区画している。本実施形態では、図25に示すように、ストライプパターンのトレンチ105が、活性領域103に複数の直線状の単位セル106を区画している。したがって、エピタキシャル層101の表面部には、複数の単位セル106の表面106A並びにそれらの間のトレンチ105の底面105A及び側面105Bが断面視で葛折状に連続した表面(エピタキシャル層101の表面101A)が形成されている。なお、トレンチ105のパターンは、ストライプパターンに限られず、例えば格子パターンであってもよい。この場合、格子パターンのトレンチ105の各窓部分にメサ状の単位セル106が複数区画され、全体として単位セル106が行列状(マトリクス状)に配列される。

[0136]

エピタキシャル層 1 0 1 は、 S i C 基板 1 0 0 側から順に成長させられた n 型のバッファ層 1 0 7 と、 n  $^-$ 型のドリフト層 1 0 8 と、 p 型層 1 0 9 とを有する。

p型層109は、活性領域103の全域に亘って連続した領域である(図25においてクロスハッチングが付された領域(後述するp型のJTE構造114の領域を除く))。p型層109は、ドリフト層108との界面110がエピタキシャル層101の表面101Aに沿っように、かつこの界面110の反対側の部分が表面101Aから露出するように、エピタキシャル層101の表面101Aに沿って形成されている。これにより、単位セル106では、トレンチ105の底面105Aに対して上方位置及び下方位置のそれぞれに、p型層109とドリフト層108との界面110が設定されている。具体的には、界面110は、単位セル106の表面106Aの直下に位置する相対的に上側に形成された第1界面110Aと、トレンチ105の底面105Aの直下に位置する相対的に下側に形成された第2界面110Bとを有する。したがって、ドリフト層108は、エピタキシャル層101において互いに隣り合うトレンチ105によって挟まれた部分に選択的に入り込んでいる。

## [0137]

また、 p 型層 1 0 9 は、エピタキシャル層 1 0 1 の表面 1 0 1 A から露出する高濃度領域である p  $^+$ 型領域 1 1 1 と、 p  $^+$ 型領域 1 1 1 よりも深い部分に形成され、 p  $^+$ 型領域 1 1 1 に比べて低濃度領域である p 型領域 1 1 2 とを有する。本実施形態では、 p  $^+$ 型領域 1 1 1 及び p 型領域 1 1 2 は、その界面がエピタキシャル層 1 0 1 の表面 1 0 1 A に層ように形成されており、 p 型層 1 0 9 は、 p  $^+$ 型領域 1 1 1 及び p 型領域 1 1 2 の積層構造を有する。なお、 p  $^+$ 型領域 1 1 1 は、活性領域 1 0 3 の全域に亘って形成されている必要は無く、活性領域 1 0 3 の一部に選択的に形成されてもよい。例えば、単位セル 1 0 6 の表面 1 0 6 A、 トレンチ 1 0 5 の底面 1 0 5 A、 及びトレンチ 1 0 5 の側面 1 0 5 B の少なくとも一つに選択的に形成されてもよい。

[ 0 1 3 8 ]

また、 p 型層 1 0 9 は、トレンチ 1 0 5 の底面 1 0 5 A と側面 1 0 5 B との間において互いに異なる厚さを有する。詳述すると、 p 型層 1 0 9 における底面 1 0 5 A 上の部分が側面 1 0 5 B 上の部分に比べて厚い。これにより、トレンチ 1 0 5 の底面 1 0 5 A と側面 1 0 5 B との間で p 型層 1 0 9 の厚さに差が設けられている。

[0139]

外周領域104においてエピタキシャル層101には、ドリフト層108が露出する深さまでエピタキシャル層101がエッチングされることによって除去領域113が形成されている。本実施形態では、除去領域113は、ストライプパターンのトレンチ105の長手方向の両端部を横切るように、活性領域103を取り囲む環状に形成されている。これにより、除去領域113は、ストライプパターンのトレンチ105に連なっている。つまり、除去領域113は、ストライプパターンの延長部で構成されている。また除去領域113の外周縁は、図25に示すように、エピタキシャル層101の端面101Bに一致してもよいし、エピタキシャル層101の端面101Bから内側に設定されてもよい(図示略)。除去領域113の深さは、トレンチ105の深さと同じであってもよい。

[0140]

除去領域113の形成によって、ドリフト層108は、活性領域103の周囲からSiС基板100の表面100Aに沿う横方向にエピタキシャル層101の端面101Bまで引き出された引き出し部108Aを有する。引き出し部108Aは、単位セル106の表面106Aに対して一段低くなった低段部となっている。

[0141]

また、外周領域104においてドリフト層108には、p型のJTE(Junction Termination Extension)構造114が形成されている。本実施形態では、JTE構造114は、活性領域103を取り囲む環状に形成されている。詳述すると、単位セル106及び引き出し部108Aを跨るように、p型層109と一体的に形成されている。JTE構造114は、エピタキシャル層101の端面101Bに向かって外側に広がる複数のリングによって構成されてもよい。この場合、複数のリング間において、互いに不純物濃度が等しくてもよいし、外側に向かって不純物濃度が減少してもよい。

[0142]

本実施形態では、JTE構造114は、不純物濃度の違いによって周方向に沿って分割されている。すなわちJTE構造114は、相対的に高濃度となる第1部分115(図25においてクロスハッチングが付された領域(p型層109の領域を除く))と、第1部分115に比べて低濃度となる第2部分116(図25においてドットが付された領域)とを有する。

[0143]

第 1 部 分 1 1 5 は、第 2 部 分 1 1 6 に対して活性領域 1 0 3 に近い側に配置されている。第 1 部 分 1 1 5 において、JTE構造 1 1 4 は、第 1 部 分 1 1 5 の他の部分に比べて高濃度となる p <sup>+</sup>型領域 1 1 7 を有する。 p <sup>+</sup>型領域 1 1 7 は、JTE構造 1 1 4 とドリフト層 1 0 8 との境界から間隔を空けた内側において、この境界に沿って p <sup>+</sup>型領域 1 1 1 と一体的に形成されている。

10

20

30

40

20

30

## [0144]

第2部分116は、複数のリングによって構成されている。第2部分116の最内周のリングは、図25及び図26に示すように第1部分115に接している。なお、第2部分116の最内周のリングは、第1部分115と接していなくてもよい。

### [0145]

エピタキシャル層 1 0 1 上には、フィールド絶縁膜 1 1 8 が形成されている。フィールド絶縁膜 1 1 8 の材料としては、例えば酸化シリコン( $SiO_2$ )等を用いることができる。フィールド絶縁膜 1 1 8 は、例えば、プラズマ CVD (chemical vapor deposition)によって形成することができる。

## [0146]

フィールド絶縁膜118には、活性領域103の全域及び外周領域104の一部を選択的に露出させるコンタクトホール119が形成されている。本実施形態では、コンタクトホール119の外周縁119Aは、第1部分115と第2部分116との境界に対して活性領域103に近い側に設定されている。これにより、フィールド絶縁膜118は、第2部分116の全体及び第1部分115の一部(例えば、周端部)を覆っている。またコンタクトホール119は、その幅が開口端に向かって広くなるテーパ形状に形成されていることが好ましい。

### [0147]

フィールド絶縁膜118上には、アノード電極120が形成されている。アノード電極120は、コンタクトホール119から露出する活性領域103の全域を覆うように形成されており、トレンチ105に埋め込まされた埋め込み部121と、埋め込み部121を覆うようにエピタキシャル層101の最表面に沿って形成された平面部122とを有する

### [0148]

埋め込み部121は、トレンチ105の底面105A及び側面105Bにおいてp型層109に接しており、p型層109との間にオーミック接合を形成している。埋め込み部121の材料としては、例えば、ポリシリコン、タングステン(W)、チタン(Ti)、又はそれらの合金等を用いることができる。これらのうち、好ましくは、p型のポリシリコンを用いることができる。これらの材料は、良好な埋め込み性を有するため、埋め込み部121のステップカバレッジを向上することができる。このため、トレンチ105のアスペクト比が高い場合でも、アノード電極120の埋め込み時におけるボイドの発生を抑制することができる。

## [0149]

平面部 1 2 2 は、単位セル 1 0 6 の表面 1 0 6 A において p 型層 1 0 9 に接しており、 p 型層 1 0 9 との間にオーミック接合を形成している。平面部 1 2 2 の材料としては、例えば T i / N i 等の積層構造を用いることができる。また平面部 1 2 2 は、コンタクトホール 1 1 9 の外方へフランジ状に張り出している。本実施形態では、アノード電極 1 2 0 の平面部 1 2 2 の外周縁 1 2 2 A は、JTE構造 1 1 4 の第 1 部分 1 1 5 と第 2 部分 1 1 6 との境界に対して活性領域 1 0 3 から遠い側に位置している。つまり、アノード電極 1 2 0 の平面部 1 2 2 は、この境界よりも第 2 部分 1 1 6 側にはみ出すオーバーラップ部 1 2 2 Bを有する。

## [0150]

上側スイッチング素子11の最表面には、表面保護膜123が形成されている。表面保護膜123の材料としては、例えば酸化シリコン(SiO2)、窒化シリコン(SiN)、ポリイミド等を用いることができる。また表面保護膜123は、例えばプラズマCVDによって形成することができる。表面保護膜123の膜厚の一例は、8000 程度である。表面保護膜123には、アノード電極120の一部をパッドとして選択的に露出させるパッド開口123Aが形成されている。上側ダイオード用ワイヤ91(図20参照)は、パッド開口123Aを介してアノード電極120に接合される。

## [0151]

50

このような上側ダイオード71の構成によれば、エピタキシャル層101にトレンチ105が形成されており、トレンチ105が形成されたエピタキシャル層101の表面101Aに沿うようにp型層109が形成され、p型層109とドリフト層108とのpn接合部を含むpnダイオードが形成されている。トレンチ105の側面105Bにもp型層109が形成されるため、p型層109の表面積は、エピタキシャル層101の主面に垂直な平面視(図24)における見かけ上の表面積よりも大きくなる。それに応じて、p型層109に対するアノード電極120の接触面積が増加するため、p型層109とアノード電極120との接触抵抗を低減することができる。このため、イオン注入によってp型層109を形成した上側ダイオード71でも低抵抗化を図ることができる。これにより、エピタキシャル成長によってp型層109を形成する場合に比べて簡単に製造でき、オン抵抗が低いpnダイオードを備える上側ダイオード71を提供することができる。

[0152]

また、p型層109におけるアノード電極120との接触部分が高濃度なp \* 型領域111であるため、p \* 型領域111においてアノード電極120との間に良好なオーミック接合を形成することができる。一方、p \* 型領域111を覆うように低濃度となるp型領域112が形成されているため、トレンチ105の底部への電界集中を良好に緩和することができる。これにより、順方向電圧及び逆方向リーク電流を低減することができる。

[ 0 1 5 3 ]

また、上側ダイオード71では、外周領域104にJTE構造114が形成されていることにより、JTE構造114とドリフト層108との界面のpn接合部から発生する空乏層によってトレンチ105の底部(特に、最も外側に配置されたトレンチ105)における電界集中を緩和することができる。これにより、トレンチ105の底部における逆方向リーク電流の発生を低減することができる。

[ 0 1 5 4 ]

(作用)

次に、本実施形態の作用について、比較例のパワーモジュールとの比較に基づいて説明する。比較例のパワーモジュールは、本実施形態のパワーモジュール 1 から上側ダイオード 7 1 及び下側ダイオード 7 2 を省略した構成である。

[0155]

比較例のパワーモジュールでは、例えば下側スイッチング素子12がオン状態からオフ状態に変更するとき、図27に示すように、下側スイッチング素子12のドレイン・ソース間電圧Vdsuが増加する一方、上側スイッチング素子11のドレイン・ソース間電圧Vdsuが低下する。このドレイン・ソース間電圧Vdsuは、負側まで落ち込み、上側スイッチング素子11のボディダイオードの順方向しきい値電圧に達したときに低下が近まる。このようにドレイン・ソース間電圧Vds1が変動することに伴い上側スイッチング素子11のゲート・ソース間電圧Vgsuも変動する。このため、このゲート・ソース間電圧Vgsuに発生するサージ電圧が増加してしまう。なお、例えば上側スイッチング素子11がオン状態からオフ状態に変更するときも同様に、下側スイッチング素子12のボディダイオードの順方ドレイン・ソース間電圧Vds1が下側スイッチング素子12のゲート・ソース間電圧Vds1に発生するサージ電圧が増加する。

[0156]

このような比較例のパワーモジュールに対して、本実施形態のパワーモジュール1は、上側スイッチング素子11のボディダイオード11aの順方向しきい値電圧よりも低い順方向しきい値電圧を有する上側ダイオード71と、下側スイッチング素子12のボディダイオード12aの順方向しきい値電圧よりも低い順方向しきい値電圧を有する下側ダイオード72とを有する。このため、例えば下側スイッチング素子12がオン状態からオフ状態に変更するとき、図28に示すように、上側スイッチング素子11のドレイン・ソース間電圧Vdsuが低下して負側に落ち込んだとしても、上側ダイオード71の順方向しきい値電圧に達すると、ドレイン・ソース間電圧Vdsuの低下が止まる。このため、比較

10

20

30

40

例のパワーモジュールに比べて、ゲート・ソース間電圧 Vgslが変動する期間が短くなるため、ゲート・ソース間電圧 Vgslに発生するサージ電圧が低減される。

### [0157]

(シミュレーション結果)

比較例及び本実施形態のパワーモジュール1において、上側スイッチング素子11をオフ状態に維持し、下側スイッチング素子12を駆動した場合における負側のサージ電圧の発生とスイッチング損失との関係について、図7及び図29に示す模式的な回路構成に基づいてシミュレーションを行った。図7は比較例のパワーモジュールの模式的な回路構成を示し、図29は本実施形態のパワーモジュール1の模式的な回路構成を示す。

#### [0158]

図29の回路構成では、上側スイッチング素子11のドレインに上側ダイオード71のカソードが電気的に接続され、上側スイッチング素子12のドレインに下側ダイオード71のアノードが電気的に接続されている。下側スイッチング素子12のソースに下側ダイオード72のカソードが電気的に接続されている。また、上側スイッチング素子11のソースに下側ダイオード72のアノードが電気的に接続されている。また、上側スイッチング素子11のソースとゲートとが短絡され、下側スイッチング素子12のゲートと下側ゲート駆動回路3が電気的に接続されている。上側スイッチング素子11のドレイト駆動回路は、ゲート抵抗8が設けられている。上側スイッチング素子11のドレインに源と5の負側端子が電気的に接続されている。図29の回路構成は、電源ESの正側端子には源と上側スイッチング素子11のドレインとの間と、上側スイッチング素子11のソースと下側スイッチング素子11のドレインとの間とを繋ぐ配線9を有する。配線9は、インダクタ負荷9aを有する。

## [0159]

比較例のパワーモジュールでは、ゲート抵抗 8 を 2 、 3 、 4 、 及び 5 と変化させた場合のシミュレーションを行った。ここで、比較例のパワーモジュールの回路構成であってゲート抵抗 8 が 2 の場合を基準条件と規定する。

## [0160]

図30に示すように、比較例のパワーモジュールでは、ゲート抵抗8を大きくすることにより、下側スイッチング素子12のスイッチング速度(ドレイン・ソース間電圧Vds1の変化速度)が遅くなることにより負側のサージ電圧の絶対値が小さくなる一方、ゲート抵抗8を大きくすることにより、スイッチング損失が急激に大きくなる。

## [0161]

これに対して、本実施形態のパワーモジュール1では、上側ダイオード71により、基準条件よりも負側のサージ電圧の絶対値が小さくなる。一方、本実施形態のパワーモジュール1では、基準条件と比較して、スイッチング損失が大きくなるが、比較例のパワーモジュールのようにゲート抵抗8を大きくする場合に比べ、スイッチング損失が小さくなる

## [0162]

本実施形態によれば、以下の効果が得られる。

(2-1)パワーモジュール1は、上側スイッチング素子11のボディダイオード11 aの順方向しきい値電圧よりも低い順方向しきい値電圧を有する上側ダイオード71と、下側スイッチング素子12のボディダイオード12aの順方向しきい値電圧よりも低い順方向しきい値電圧よりも低い順方向しきい値電圧を有する下側ダイオード72とを有する。この構成によれば、例えば下側スイッチング素子12がオン状態からオフ状態に変化するとき、上側スイッチング素子11のドレイン・ソース間電圧Vdsuが負側に低下しても上側ダイオード71の順方向しきい値電圧で上側スイッチング素子11のドレイン・ソース間電圧Vdsuの低下が止まる。また例えば上側スイッチング素子11がオン状態からオフ状態に変化するとき、下側スイッチング素子12のドレイン・ソース間電圧Vdslでに低下しても下側ダイオード72の順方向しきい値電圧で下側スイッチング素子12のドレイン・ソース間電圧

10

20

30

50

40

Vdslの低下が止まる。このように、ドレイン・ソース間電圧Vdsの変動期間が短くなるため、ゲート・ソース間電圧Vgsの変動期間が短くなる。したがって、ゲート・ソース間電圧Vgsの変動を低減することができる。

#### [ 0 1 6 3 ]

さらに、上側ダイオード71の許容可能なDC定格電流が上側スイッチング素子11の 許容可能なDC定格電流未満であり、下側ダイオード72の許容可能なDC定格電流が下 側スイッチング素子12の許容可能なDC定格電流未満である。このため、上側ダイオー ド71のチップ面積及び下側ダイオード72のチップ面積をそれぞれ小さくすることがで きる。したがって、パワーモジュール1の小型化を図ることができる。

#### [0164]

(2 - 2)上側ダイオード 7 1 の個数が上側スイッチング素子 1 1 の個数よりも少なく、下側ダイオード 7 2 の個数が下側スイッチング素子 1 2 の個数よりも少ない。この構成によれば、上側ダイオード 7 1 の個数が上側スイッチング素子 1 1 の個数以上の場合、及び下側ダイオード 7 2 の個数が下側スイッチング素子 1 2 の個数以上の場合と比較して、パワーモジュール 1 の素子数を減らすことができ、パワーモジュール 1 の小型化を図ることができる。

### [0165]

(2-3)パワーモジュール1の基板80は、グラファイト基板82を有する。グラファイト基板82は、複数の上側スイッチング素子11及び複数の上側ダイオード71が第2方向Yに間隔を空けて配置された第1基板82Aと、複数の下側スイッチング素子12及び複数の下側ダイオード72が第2方向Yに間隔を空けて配置された第2基板82Bとを有する。第1基板82Aは、第2方向Yにおける第1基板82Aの熱伝導性が第1方向Xにおける第1基板82Aの熱伝導性よりも低くなるように構成されている。第2基板82Bの熱伝導性よりも低くなるように構成されている。この構成によれば、複数の上側スイッチング素子11の熱が複数の上側ダイオード71に伝わり難くなり、複数の下側スイッチング素子12の熱が複数の下側ダイオード72に伝わり難くなる。このため、上側ダイオード71及び下側ダイオード72の温度変化にともなう順方向しきい値の変化を抑制することができる。

### [0166]

(2-4)第1基板82Aの裏面に裏面金属層82bが設けられ、第1基板82Aの表面に表面金属層82cが設けられている。裏面金属層82b及び表面金属層82cは、同一の材料により形成されている。この構成によれば、第1基板82Aの表面の熱伝導率とが同じになる。これにより、第1基板82Aが加熱されたときに第1基板82Aの表面の伸び量と第1基板82Aの裏面の伸び量とが概ね同一となる。したがって、第1基板82Aの表面の熱伝導率と第1基板82Aの裏面の熱伝導率と第1基板82Aの裏面の熱伝導率と第1基板82Aの裏面の熱伝導率との違いに起因して第1基板82Aが反ることを抑制することができる。また、第2基板82Bの裏面に裏面金属層82bが設けられ、第2基板82Bの表面に表面金属層82cが設けられている。この構成によれば、第1基板82Aと同様に、第2基板82Bの表面の熱伝導率と裏面の熱伝導率との違いに起因する第2基板82Bの反りを抑制することができる。

## [0167]

(2-5)上側ダイオード 7 1 は、上側スイッチング素子 1 1 とは別チップとして設けられ、かつ上側スイッチング素子 1 1 とは間隔を空けて配置されている。下側ダイオード 7 2 は、下側スイッチング素子 1 2 とは別チップとして設けられ、かつ下側スイッチング素子 1 2 とは間隔を空けて配置されている。この構成によれば、上側ダイオード 7 1 が上側スイッチング素子 1 1 による熱影響を受けることを抑制することができ、下側ダイオード 7 2 が下側スイッチング素子 1 2 による熱影響を受けることを抑制することができる。

#### [0168]

(2-6)上側ダイオード用ワイヤ91のインダクタンスが上側電力用ワイヤ44のイ

10

20

30

ンダクタンスよりも小さくなるように構成されている。下側ダイオード用ワイヤ92のインダクタンスが下側電力用ワイヤ46のインダクタンスよりも小さくなるように構成されている。このような構成によれば、上側電力用ワイヤ44よりもインダクタンスが低い上側ダイオード用ワイヤ91に電流が流れ易くなるため、上側スイッチング素子11のボディダイオード11aよりも上側ダイオード71に電流が流れ易くなる。下側電力用ワイヤ46よりもインダクタンスが低い下側ダイオード用ワイヤ92に電流が流れ易くなるため、下側スイッチング素子12のボディダイオード12aよりも下側ダイオード72に電流が流れ易くなる。

#### [0169]

#### [0170]

特に、上側電力用ワイヤ44と下側電力用ワイヤ46とが互いに平行となるため、上側電力用ワイヤ44に発生する磁界と下側電力用ワイヤ46に発生する磁界とを効果的に打ち消し合うことができる。また上側ダイオード用ワイヤ91と下側ダイオード用ワイヤ92とが互いに平行となるため、上側ダイオード用ワイヤ91に発生する磁界と下側ダイオード用ワイヤ92に発生する磁界とを効果的に打ち消し合うことができる。

# [0171]

(2-8)セラミック基板81の本体部81aの裏面に裏面金属層81bが設けられ、本体部81aの表面に表面金属層81cが設けられている。裏面金属層81b及び表面金属層81cは、同一の材料により形成されている。この構成によれば、セラミック基板81の本体部81aの裏面の熱伝導率とが同じになる。これにより、セラミック基板81が加熱されたときにセラミック基板81の表面の伸び量とが概ね同一となる。したがって、セラミック基板81の表面の熱伝導率とセラミック基板81の裏面の熱伝導率との違いに起因してセラミック基板81が反ることを抑制することができる。

### [0172]

## (第3実施形態)

図31~図35を参照して、第3実施形態のパワーモジュール1について説明する。本実施形態のパワーモジュール1は、第2実施形態のパワーモジュール1と比較して、上側スイッチング素子及び上側ダイオードが同一チップに形成された点、及び下側スイッチング素子及び下側ダイオードが同一チップに形成された点が異なる。

# [0173]

パワーモジュール1は、上側スイッチング素子及び上側ダイオードが同一チップに形成された上側MISトランジスタ130、及び下側スイッチング素子及び下側ダイオードが同一チップに形成された下側MISトランジスタ131を有する。各MISトランジスタ130、131は、シリコンカーバイド(SiC)が採用されたトレンチゲート型DMI

10

20

30

40

SFET (Double Implanted Metal Insulator Semiconductor Field Effect T ransistor) である。上側MISトランジスタ130と下側MISトランジスタ131 は、同一構造である。このため、以降の説明では、上側MISトランジスタ130の構造について説明し、下側MISトランジスタ131の構造の説明を省略する。なお、上側MISトランジスタ131の構成は、図31及び図32に示す構成に限られず、種々の変更が可能である。

[0174]

上側 M I S トランジスタ 1 3 0 は、例えば図 3 1 ( a )に示すような平面視で正方形のチップ状である。上側 M I S トランジスタ 1 3 0 は、図 3 1 ( a )の紙面における上下左右方向の長さがそれぞれ数 m m 程度である。

[0175]

上側MISトランジスタ130の表面には、ソースパッド132が形成されている。ソースパッド132は、上側MISトランジスタ130の表面のほぼ全域を覆うように形成されている。このソースパッド132の一辺の中央付近には、除去領域133が形成されている。除去領域133は、ソースパッド132が形成されていない領域である。

[0176]

除去領域133には、ゲートパッド134が配置されている。ゲートパッド134とソースパッド132との間には、間隔が設けられている。ゲートパッド134とソースパッド132とは互いに電気的に絶縁されている。

[0177]

図32に示すように、上側MISトランジスタ130は、n<sup>+</sup>型のSiC基板140を 有する。SiC基板140は、上側MISトランジスタ130のドレインとして機能し、 その表面140A(上面)がSi面であり、その裏面140B(下面)がC面である。

[ 0 1 7 8 ]

SiC基板140の表面140Aには、SiC基板140よりも低濃度のn‐型のエピタキシャル層141が積層されている。半導体層としてのエピタキシャル層141は、SiC基板140上に、所謂エピタキシャル成長によって形成されている。Si面である表面140A上に形成されるエピタキシャル層141は、Si面を成長主面として成長させられる。したがって、成長により形成されるエピタキシャル層141の表面141Aは、SiC基板140の表面140Aと同様に、Si面である。

[0179]

図31(a)に示すように、上側MISトランジスタ130には、平面視でエピタキシャル層141の中央部に配置され、上側MISトランジスタ130として機能する活性領域142と、この活性領域142を取り囲む外周領域143とが形成されている。

[0180]

活性領域142において、エピタキシャル層141にはゲートトレンチ144が格子状に形成されている(図31(b)参照)。これらゲートトレンチ144によりエピタキシャル層141はそれぞれ、四角状(正方形状)の複数のセル145に区画されている。

[0181]

複数のセル 1 4 5 は、ショットキーセル 1 4 6 と、ショットキーセル 1 4 6 よりも相対的に平面面積の小さい p n ダイオードセル 1 4 7 とを含む。例えば、ショットキーセル 1 4 6 は、 p n ダイオードセル 1 4 7 の 4 つ分に相当する面積を有しており、ショットキーセル 1 4 6 の一辺の長さは p n ダイオードセル 1 4 7 の一辺の長さの 2 倍に相当する。

[ 0 1 8 2 ]

そして、1つのショットキーセル146と、そのショットキーセル146を取り囲む複数のpnダイオードセル147(本実施形態では、12個のpnダイオードセル147)とにより1つのセル群が構成されている。そしてこのようなセル群がさらに行列状に配置されている。ここで、互いに隣り合うセル群のpnダイオードセル147が共有されている。つまり、所定のセル群のショットキーセル146を取り囲むpnダイオードセル14

10

20

30

40

ル147としても用いられている。

#### [ 0 1 8 3 ]

図32に示すように、ショットキーセル146及びpnダイオードセル147に共通する要素として、エピタキシャル層141には、その表面141Aから裏面141B側に向かって順に、n<sup>+</sup>型のソース領域148、p型のボディ領域149、及びドリフト領域150を有する。

#### [ 0 1 8 4 ]

ドリフト領域150は、エピタキシャル成長後のままの状態が維持された n ・型の領域であり、全てのセル145の底部で一体的に繋がっており、それらの間で共有されている。つまり、ゲートトレンチ144は、ソース領域148及びボディ領域149を側面144Aに露出させ、その最深部がドリフト領域150の途中部に位置するように各セル145を区画している。ゲートトレンチ144は、隣り合うセル145の各間を、各セル145の4つの側面に沿って行方向及び列方向のそれぞれに直線状に延びる線状部151と、行方向に延びる線状部151と列方向に延びる線状部151とが交差する交差部152とを含む。

#### [0185]

ゲートトレンチ 1 4 4 の内面には、酸化膜 S i O  $_2$  、もしくは H i g h - k 材料 ( S i N 、 A l  $_2$  O  $_3$  、 A l O N 等 ) からなるゲート絶縁膜 1 5 3 が、その全域を覆うように形成されている。ゲート絶縁膜 1 5 3 は、ゲートトレンチ 1 4 4 の底面 1 4 4 B 上の部分が、ゲートトレンチ 1 4 4 の側面 1 4 4 A 上の部分よりも厚くなっている。そして、ゲートトレンチ 1 4 4 におけるゲート絶縁膜 1 5 3 の内側がポリシリコンで埋め尽くされることにより、ゲートトレンチ 1 4 4 内にゲート電極 1 5 4 が埋設されている。

### [0186]

このように、各ショットキーセル146及びpnダイオードセル147には、ソース領域148とドリフト領域150とが、エピタキシャル層141の表面141Aに垂直な縦方向にボディ領域149を介して離間して配置された、縦型MISトランジスタ構造が構成されている。

#### [ 0 1 8 7 ]

ショットキーセル 1 4 6 の中央部には、エピタキシャル層 1 4 1 の表面 1 4 1 A からソース領域 1 4 8 及びボディ領域 1 4 9 を貫通してドリフト領域 1 5 0 に達する、平面視で正方形状の第 1 ソーストレンチ 1 5 5 が形成されている。第 1 ソーストレンチ 1 5 5 の深さは、ゲートトレンチ 1 4 4 の深さと同じである。

### [0188]

第1ソーストレンチ155には、p型の第1耐圧保持領域156が形成されている。第1耐圧保持領域156は、第1ソーストレンチ155の底面155Aと側面155Bとが交わって形成され、底面155Aの周囲を取り囲む環状のエッジ部155C及びこのエッジ部155Cから第1ソーストレンチ155の側面155Bに露出するボディ領域149に至る環状に形成されている。これにより、第1耐圧保持領域156に取り囲まれる第1ソーストレンチ155の底面155Aの中央部には、ドリフト領域150の一部からなる平面視で正方形状のショットキー領域157が形成されている。

## [ 0 1 8 9 ]

ショットキー領域 1 5 7 は、ショットキー領域 1 5 7 と第 1 耐圧保持領域 1 5 6 との p n 接合部(ボディダイオード 1 5 8 ) から発生する空乏層が繋がらない面積が形成されている。

## [0190]

一方、 p n ダイオードセル 1 4 7 の中央部には、エピタキシャル層 1 4 1 の表面 1 4 1 A からソース領域 1 4 8 及びボディ領域 1 4 9 を貫通してドリフト領域 1 5 0 に達する第 2 ソーストレンチ 1 5 9 が形成されている。第 2 ソーストレンチ 1 5 9 の 面積 は、 ショットキー領域 1 5 7 の 面積よりも小さい。

10

20

30

40

### [0191]

第2ソーストレンチ159には、p型の第2耐圧保持領域160が形成されている。第2耐圧保持領域160は、第2ソーストレンチ159の底面159Aの全面に亘り形成され、かつ、第2ソーストレンチ159の底面159Aと側面159Bとが交わって形成されて底面159Aの周囲を取り囲む環状のエッジ部159C及びこのエッジ部159Cから第2ソーストレンチ159の側面159Bに露出するボディ領域149に至る器状に形成されている。

## [0192]

第2ソーストレンチ159には、その底面159Aの中央部における第2耐圧保持領域160の表層部にp<sup>+</sup>型の底部ボディコンタクト領域161が形成されている。底部ボディコンタクト領域161をオーミック接触させることにより、第2耐圧保持領域160を介してpnダイオードセル147のボディ領域149に対してコンタクトすることができる(電気的に接続することができる)。

#### [0193]

そして第 2 ソーストレンチ 1 5 9 に第 2 耐圧保持領域 1 6 0 が形成されていることにより、 p n ダイオードセル 1 4 7 は、第 2 耐圧保持領域 1 6 0 とドリフト領域 1 5 0 との p n 接合により構成され、アノード側のコンタクトとして底部ボディコンタクト領域 1 6 1 を有し、カソード側のコンタクトとして S i C 基板 1 4 0 を有するボディダイオード 1 6 2 を内蔵している。

#### [0194]

また、複数のセル145を区画するゲートトレンチ144の各交差部152には、第3耐圧保持領域163(中継領域)が形成されている。第3耐圧保持領域163は、交差部152におけるゲートトレンチ144の底面144Bの全面に亘り形成され、かつ、底面144Bから交差部152に臨む各セル145の各角部の下部に形成されたゲートトレンチ144のエッジ部144C及びエッジ部144C直上のボディ領域149に至るように形成されている。すなわち、第3耐圧保持領域163は、平面視でゲートトレンチ144の交差部152よりもやや大きい正方形状に形成されており、その各角が、交差部152に臨む各セル145の各角部にそれぞれ入り込んでいる。また第3耐圧保持領域163の不純物濃度は、ボディ領域149の不純物濃度及びドリフト領域150の不純物濃度よりも高い。

## [0195]

第3耐圧保持領域163の中継により、底部ボディコンタクト領域161 第2耐圧保持領域160 pnダイオードセル147のボディ領域149 第3耐圧保持領域163 ショットキーセル146のボディ領域149を介して、ショットキーセル146の第1耐圧保持領域156に対してコンタクトすることができる(電気的に接続することができる)。

#### [0196]

図31(a)に示すように、外周領域143において、エピタキシャル層141の表層部には、活性領域142を取り囲むように、活性領域142から間隔を空けてp型のガードリング164が複数本(本実施形態では、4本)形成されている。これらガードリング164は、p型のボディ領域149を形成する工程と同一のイオン注入工程で形成することができる。各ガードリング164は、平面視において上側MISトランジスタ130の外周に沿う四角環状に形成されている。

#### [0197]

# [0198]

40

30

10

20

層間絶縁膜165上には、ソース電極168が形成されている。ソース電極168は、 各コンタクトホール166,167を介して、全ての第1ソーストレンチ155及び第2 ソーストレンチ159に一括して入り込んでいる。

#### [0199]

ソース電極 1 6 8 は、ショットキーセル 1 4 6 において、第 1 ソーストレンチ 1 5 5 の底側から順にショットキー領域 1 5 7、第 1 耐圧保持領域 1 5 6、及びソース領域 1 4 8 に接触している。またソース電極 1 6 8 は、 p n ダイオードセル 1 4 7 において、第 2 ソーストレンチ 1 5 9 の底側から順に底部ボディコンタクト領域 1 6 1、第 2 耐圧保持領域 1 6 0、及びソース領域 1 4 8 に接触している。すなわち、ソース電極 1 6 8 は、全てのセル 1 4 5 に対して共通の配線となっている。

[ 0 2 0 0 ]

ソース電極168上には、層間絶縁膜165が形成されており、この層間絶縁膜165を介してソース電極168がソースパッド132に電気的に接続されている。一方、ゲートパッド134は、層間絶縁膜165上に引き回されたゲート配線(図示略)を介してゲート電極154に電気的に接続されている。

[ 0 2 0 1 ]

ソース電極 1 6 8 は、エピタキシャル層 1 4 1 の接触側から順に、ポリシリコン層 1 6 9、中間層 1 7 0、及びメタル層 1 7 1 を有する。

ポリシリコン層 1 6 9 は、不純物がドーピングされたドープドポリシリコンが用いられる。ポリシリコン層 1 6 9 の不純物としては、窒素( N )、燐( P )、砒素( A s )等の n 型の不純物、アルミニウム( A l )、ホウ素( B )等の p 型の不純物を用いることができる。

[0202]

ポリシリコン層 1 6 9 は、コンタクトホール 1 6 6 , 1 6 7 内に露出するセル 1 4 5 の表面全域を覆うように形成されている。ポリシリコン層 1 6 9 は、第 1 ソーストレンチ 1 5 5 内でショットキー領域 1 5 7 、第 1 耐圧保持領域 1 5 6、及びソース領域 1 4 8 の全て、第 2 ソーストレンチ 1 5 9 内で底部ボディコンタクト領域 1 6 1、第 2 耐圧保持領域 1 6 0、及びソース領域 1 4 8 の全てに接触している。

[0203]

ポリシリコン層169は、ショットキーセル146においてソース領域148との間にショットキー接合を形成している。これにより、ポリシリコン層169は、ショットキー領域157との間に、ショットキーセル146及びpnダイオードセル147にそれぞれ内蔵されたボディダイオード172(ボディ領域149とドリフト領域150とのpn接合により形成されるダイオード)の拡散電位(例えば、2.8~3.2eV)よりも接合障壁の小さいへテロ接合(例えば、接合障壁の高さが1~1.5eV)を形成している。これにより、ショットキーセル146においては、ソース電極168とショットキー領域157との間にヘテロ接合ダイオード172が形成されている。また、ポリシリコン層169は、pnダイオードセル147において底部ボディコンタクト領域161及びソース領域148との間にオーミック接触を形成している。

[0204]

中間層 1 7 0 は、ポリシリコン層 1 6 9 上に積層されたメタル層である。メタル層 1 7 1 は、ソース電極 1 6 8 の最表層をなしている。

このようなポリシリコン層169、中間層170、及びメタル層171の組合せとしては、ポリシリコン(ポリシリコン層169)、チタン(中間層170)、及びアルミニウム(メタル層171)が順に積層される積層構造(ポリシリコン/Ti/Al)である。また、これらに加えて、メタル層171がモリブデン層(Mo層)を有することが好ましい。モリブデンは融点が高いため、メタル層171にモリブデン層を含まれることにより、ソース電極168に大電流が流れたときに生じる熱によるメタル層171の溶損を抑制することができる。

[0205]

10

20

30

20

30

40

50

SiC基板140の裏面140Bには、その全域を覆うようにドレイン電極174が形成されている。ドレイン電極174は、全てのセル145に対して共通の電極となる。ドレイン電極174としては、例えばSiC基板140側から順に、チタン(Ti)、ニッケル(Ni)、金(Au)、及び銀(Ag)が積層された積層構造(Ti/Ni/Au/Ag)を用いることができる。

# [0206]

図33に示すように、パワーモジュール1では、複数個の上側MISトランジスタ13 0(本実施形態では、3個の上側MISトランジスタ130)が第1基板82Aに実装され、複数個の下側MISトランジスタ131(本実施形態では、3個の下側MISトランジスタ131)が第2基板82Bに実装されている。

#### [ 0 2 0 7 ]