# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

| (51) Int. CI. <sup>5</sup><br>HO1L 29/94 | (11) 공개번호 특1992-0010974<br>(43) 공개일자 1992년06월27일                 |

|------------------------------------------|------------------------------------------------------------------|

| (21) 출원번호<br>(22) 출원일자                   | 특 1991-0018670<br>1991년 10월 23일                                  |

| (30) 우선권주장<br>(71) 출원인                   | 90-314542 1990년11월19일 일본(JP)<br>미쓰비시 뎅끼 가부시끼가이샤  시기 모리야          |

| (72) 발명자                                 | 일본국 도오교도 지요다구 마루노우찌 2쪼메 2-3<br>고나가와 가꼬                           |

|                                          | 일본국 효고겡 이다미시 미즈하라 4쪼메 1번지 미쓰비시뎅끼 가부시끼가이<br>샤 기다이단세이샤꾸쇼 나이        |

|                                          | 고야마 도오루                                                          |

|                                          | 일본국 효고겡 이다미시 미즈하라 4쪼메 1번지 미쓰비시뎅끼 가부시끼가이<br>샤 기다이단세이샤꾸쇼 나이        |

|                                          | 히사부 겐지                                                           |

|                                          | 일본국 효고겡 이다미시 미즈하라 4쪼메 1번지 미쓰비시뎅끼 가부시끼가이<br>샤 기다이단세이샤꾸쇼 나이        |

|                                          | 다무라 가쓰히꼬                                                         |

|                                          | 일본국 효고겡 이다미시 미즈하라 4쪼메 1번지 미쓰비시뎅끼 가부시끼가이<br>샤 기다이단세이샤꾸쇼 나이        |

|                                          | 나까무라 세나                                                          |

| (74) 대리인                                 | 일본국 효고겡 이다미시 미즈하라 4쪼메 1번지 미쓰비시뎅끼 가부시끼가이<br>샤 기다이단세이샤꾸쇼 나이<br>김영길 |

|                                          |                                                                  |

| 시시처그 ㆍ 이으                                |                                                                  |

#### 심사정구 : 있음

## (54) 반도체장치 및 그의 제조방법

## 요약

내용 없음

## 대표도

#### 도1

### 명세서

[발명의 명칭]

반도체장치 및 그의 제조방법

[도면의 간단한 설명]

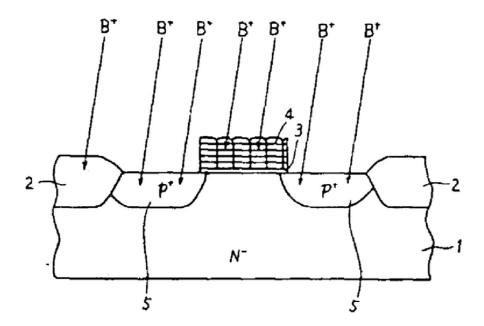

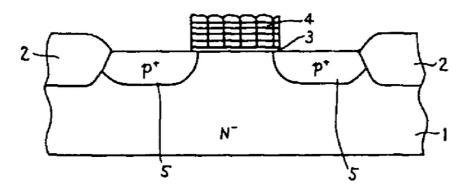

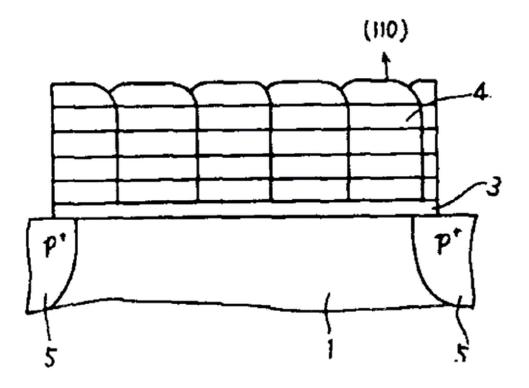

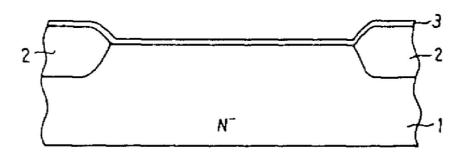

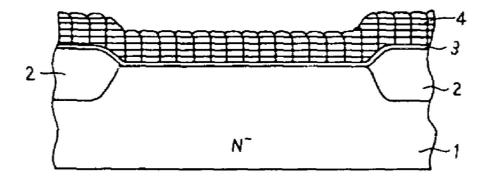

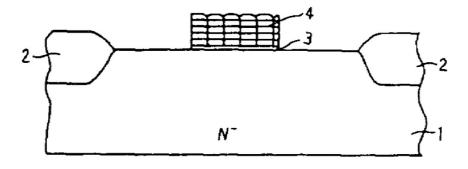

제1도는 본 발명의 1실시예에 의한 게이트전극을 구비한 P채널 MOS트랜지스터를 표시한 단면도, 제2도는 제1도에 표시한 게이트전극의 결정구조를 설명하기 위해서의 확대단면도, 제3A도 내지 제3D도는 제1도에 표시한 P채널 MOS트랜지스터의 제조프로세스를 설명하기 위해서의 단면도.

본 내용은 요부공개 건이므로 전문내용을 수록하지 않았음

#### (57) 청구의 범위

### 청구항 1

제1도전형의 반도체기판의 상기 제1도전형의 반도체 기판상에 소정의 간격을 두고 형성되어 제2도전형을 가지는 1쌍의 불순물영역과 상기 1쌍의 불순물영역간의 상기 반도체기판상에 절연막을 끼워서 형성되어 그의 결정립의 결정방위가 소정의 방위에 갖추어진 다결정체층을 가지는 게이트전극을 구비하는 반도체 장치.

## 청구항 2

반도체기판상에 그의 결정립의 결정방위가 소정의 방위에 갖추어지게 다결정체층을 형성하는 공정과 상기 다결정체층을 패터닝하는 공정과 상기 패터닝된 다결정체층을 마스크로서 상기 다결정체층의 결정방위에 대해 소정의 각도기울인 방향에 이온주입하는 것에 의해 상기 반도체 기판상에 불순물영역을 형성하는 공정을 구비하는 반도체장치의 제조방법.

#### 청구항 3

다결정 실리콘층의 제조방법이고 하지로되는 기재상에 반응가스로서 시란계가스를 사용하여 분위기압력 0.1~1.0Torr, 분위기온도 550℃~620℃의 조건하에서 화학기상성장법에 의해 그의 결정립의 결정방위가 소정의 방위에 갖추어 지도록 다결정 실리콘층을 형성하는 다결정 실리콘층의 제조방법.

※ 참고사항:최초출원 내용에 의하여 공개하는 것임.

#### 도면

#### 도면1

도면2

# 도면3a

# 도면3b

도면3c

# 도면3d