# (19) 国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 107026642 B (45) 授权公告日 2022. 06. 07

(21)申请号 201710061169.1

(22) 申请日 2017.01.25

(65) 同一申请的已公布的文献号 申请公布号 CN 107026642 A

(43) 申请公布日 2017.08.08

(30) 优先权数据

10-2016-0012766 2016.02.02 KR 10-2016-0062282 2016.05.20 KR

(73) **专利权人** 三星电子株式会社 地址 韩国京畿道

(72) 发明人 具京会 朴相勋 崔珍镐

(74) **专利代理机构** 北京市柳沈律师事务所 11105

专利代理师 钱大勇 王新宇

(51) Int.CI.

**HO3K** 19/0185 (2006.01)

(56) 对比文件

US 7786760 B2,2010.08.31

US 7990175 B2,2011.08.02

US 2005212552 A1,2005.09.29

US 8837231 B2,2014.09.16

US 8837231 B2,2014.09.16

CN 101317232 A.2008.12.03

CN 104867475 A, 2015.08.26

CN 102769442 A,2012.11.07

US 2015130511 A1,2015.05.14

CN 101017704 A,2007.08.15

熊军等.一种新型的用于高速串行接口的发送器.《电路与系统学报》.2004,(第05期),

#### 审查员 曹焯

权利要求书5页 说明书10页 附图11页

#### (54) 发明名称

用于在低电压下操作的发射器电路和接收 器电路

## (57) 摘要

可以提供一种发射器电路,其包括:预驱动器电路,其被配置为从逻辑电路接收逻辑信号并且生成由第一电压驱动的第一信号,所述预驱动器电路包括晶体管,所述晶体管具有等于或低于所述逻辑电路中所包括的晶体管的阈值电压的阈值电压;以及主驱动器电路,其被配置为接收所述第一信号并且生成由第二电压驱动的第二信号,所述主驱动器电路被配置为将所述第二信号输出到输入/输出垫,所述主驱动器电路包括晶体管,所述晶体管具有等于或低于所述逻辑电路中所包括的所述晶体管的所述阈值电压的阈值电压。

1.一种发射器电路,其包括:

预驱动器电路,其被配置为从逻辑电路接收逻辑信号并且生成由第一电压驱动的第一信号,所述预驱动器电路包括晶体管,所述晶体管具有等于或低于所述逻辑电路中所包括的晶体管的阈值电压的阈值电压;

主驱动器电路,其被配置为接收所述第一信号并且生成由第二电压驱动的第二信号, 所述主驱动器电路被配置为将所述第二信号输出到输入/输出垫,所述主驱动器电路包括 晶体管,所述晶体管具有等于或低于所述逻辑电路中所包括的所述晶体管的阈值电压的阈 值电压:

电平移位器,其被配置为将所述逻辑信号的电压电平转换成第一电压电平;以及

多路复用器电路,在所述电平移位器和所述预驱动器电路之间,其被配置为接收所述逻辑信号和具有所述第一电压电平的所转换的逻辑信号并且根据模式控制信号将所述逻辑信号或所转换的逻辑信号之一提供给所述预驱动器电路,所述模式控制信号是根据向所述输入/输出垫发送或从其接收的数据的传输频率而确定的。

2. 如权利要求1所述的发射器电路,其中所述主驱动器电路包括:

PMOS晶体管,其被配置为通过所述第一信号将所述输入/输出垫的电压上拉到所述第二电压;

第一电阻器,其连接在所述PMOS晶体管与所述输入/输出垫之间;

NMOS晶体管,其被配置为通过所述第一信号将所述输入/输出垫的电压下拉到第三电压;以及

第二电阻器,其连接在所述NMOS晶体管与所述输入/输出垫之间。

3. 如权利要求1所述的发射器电路,其中所述主驱动器电路包括:

第一NMOS晶体管,其被配置为通过所述第一信号将所述输入/输出垫的电压上拉到第二电压;

第一电阻器,其连接在所述第一NMOS晶体管与所述输入/输出垫之间:

反相器,其被配置为通过对所述第一信号进行反相来生成反相信号;

第二NMOS晶体管,其被配置为通过所述反相信号将所述输入/输出垫的电压下拉到第三电压:以及

第二电阻器,其连接在所述第二NMOS晶体管与所述输入/输出垫之间。

4.一种发射器电路,其包括:

预驱动器电路,其被配置为从逻辑电路接收逻辑信号并且生成由第一电压驱动的第一信号,所述预驱动器电路包括晶体管,所述晶体管具有等于或低于所述逻辑电路中所包括的晶体管的阈值电压的阈值电压;

主驱动器电路,其被配置为接收所述第一信号并且生成由第二电压驱动的第二信号, 所述主驱动器电路被配置为将所述第二信号输出到输入/输出垫,所述主驱动器电路包括 晶体管,所述晶体管具有等于或低于所述逻辑电路中所包括的所述晶体管的阈值电压的阈 值电压:

电平移位器,其被配置为将所述第一信号的电压电平转换成第二电压;以及

多路复用器电路,在所述电平移位器和所述主驱动器电路之间,其被配置为接收所述 第一信号和具有所述第二电压电平的所转换的第一信号并且根据模式控制信号将所述第

- 一信号或所转换的第一信号之一提供给所述主驱动器电路,所述模式控制信号是根据向所述输入/输出垫发送或从其接收的数据的传输频率而确定的。

- 5. 如权利要求4所述的发射器电路,其中所述主驱动器电路包括:

PMOS晶体管,其被配置为通过所述第一信号将所述输入/输出垫的电压上拉到所述第二电压;

第一电阻器,其连接在所述PMOS晶体管与所述输入/输出垫之间;

NMOS晶体管,其被配置为通过所述第一信号将所述输入/输出垫的电压下拉到第三电压;以及

- 第二电阻器,其连接在所述NMOS晶体管与所述输入/输出垫之间。

- 6. 如权利要求4所述的发射器电路,其中所述主驱动器电路包括:

- 第一NMOS晶体管,其被配置为通过所述第一信号将所述输入/输出垫的电压上拉到第二电压:

第一电阻器,其连接在所述第一NMOS晶体管与所述输入/输出垫之间;

反相器,其被配置为通过对所述第一信号进行反相来生成反相信号;

第二NMOS晶体管,其被配置为通过所述反相信号将所述输入/输出垫的电压下拉到第三电压:以及

第二电阻器,其连接在所述第二NMOS晶体管与所述输入/输出垫之间。

7.一种接口电路,包括:

发射器,其包括,

预驱动器电路,其被配置为从逻辑电路接收逻辑信号并且生成由第一电压驱动的第一信号,所述预驱动器电路包括晶体管,所述晶体管具有等于或低于所述逻辑电路中所包括的晶体管的阈值电压的阈值电压,主驱动器电路,其被配置为接收所述第一信号并且生成由第二电压驱动的第二信号,所述主驱动器电路被配置为将所述第二信号输出到输入/输出垫,所述主驱动器电路包括晶体管,所述晶体管具有等于或低于所述逻辑电路中所包括的所述晶体管的所述阈值电压的阈值电压,

电平移位器,其被配置为将所述逻辑信号的电压电平转换成第一电压电平或者将所述第一信号的电压电平转换成第二电压电平,以及

多路复用器电路,其被配置为接收所述逻辑信号和所述电平移位器的输出或者接收所述第一信号和所述电平移位器的输出,所述多路复用器电路被配置为基于模式控制信号向所述预驱动器电路提供所述逻辑信号和所述电平移位器的输出中的一个或者向所述主驱动器电路提供所述第一信号和所述电平移位器的输出中的一个,所述模式控制信号是根据向所述输入/输出垫发射或从其接收的数据的传输频率而确定的;以及

接收器,其包括,

第一输入缓冲器,其被配置为由所述第一电压驱动以从所述输入/输出垫接收低频带的输入数据,以及

第二输入缓冲器,其被配置为由第三电压驱动以从所述输入/输出垫接收高频带的输入数据。

- 8. 如权利要求7所述的接口电路,所述第一电压和所述第二电压具有相同的电压电平。

- 9. 如权利要求7所述的接口电路,所述第三电压的电平与所述逻辑信号的高电平相同。

10.一种控制器的发射器电路,包括:

预驱动器电路,其被配置为接收逻辑信号并且生成由第一电压驱动的第一信号,所述 预驱动器电路包括第一晶体管,所述第一晶体管具有等于或低于参考电压的阈值电压;以 及

主驱动器电路,其被配置为接收所述第一信号并且生成由第二电压驱动的第二信号,所述主驱动器电路包括第二晶体管,所述第二晶体管具有等于或低于所述参考电压的阈值电压:

电平移位器,其被配置为将所述逻辑信号的电压电平转换成第一电压电平或者将所述 第一信号的电压电平转换成第二电压;以及

多路复用器电路,其被配置为接收所述逻辑信号和所述电平移位器的输出或者接收所述第一信号和所述电平移位器的输出信号,所述多路复用器电路被配置为基于模式控制信号向所述预驱动器电路提供所述逻辑信号和所述电平移位器的输出中的一个或者向所述主驱动器电路提供所述第一信号和所述电平移位器的输出信号中的一个。

- 11.如权利要求10所述的发射器电路,其中所述参考电压是逻辑电路中包括的第三晶体管的阈值电压,所述逻辑电路将逻辑信号发送到所述预驱动器电路。

- 12.如权利要求10所述的发射器电路,其中基于所述控制器的操作频率确定所述模式控制信号。

- 13. 如权利要求10所述的发射器电路,其中所述主驱动器电路包括:

PMOS晶体管,其被配置为通过所述第一信号将输入/输出垫的电压上拉到所述第二电压;以及

NMOS晶体管,其被配置为通过所述第一信号将所述输入/输出垫的电压下拉到第三电压。

14. 如权利要求10所述的发射器电路,其中所述主驱动器电路包括:

第一NMOS晶体管,其被配置为通过所述第一信号将输入/输出垫的电压上拉到所述第二电压;

反相器,其被配置为通过对所述第一信号进行反相来生成反相信号:以及

第二NMOS晶体管,其被配置为通过所述反相信号将所述输入/输出垫的电压下拉到第三电压。

15.一种片上系统(SoC),包括:

逻辑电路,被配置为输出逻辑信号并且包括第一晶体管;和

发射器电路,包括:

预驱动器电路,被配置为从所述逻辑电路接收逻辑信号并且生成由第一电压驱动的第一信号,所述预驱动器电路包括第二晶体管;

主驱动器电路,被配置为接收所述第一信号,配置为生成由第二电压驱动的第二信号,所述主驱动器电路包括第三晶体管;

电平移位器,被配置为将所述逻辑信号的电压电平转换成第一电压电平或者将所述第一信号的电压电平转换成第二电压:以及

多路复用器电路,被配置为接收所述逻辑信号和所述电平移位器的输出或者接收所述 第一信号和所述电平移位器的输出信号,所述多路复用器电路被配置为基于模式控制信号 向所述预驱动器电路提供所述逻辑信号和所述电平移位器的输出中的一个或者向所述主 驱动器电路提供所述第一信号和所述电平移位器的输出信号中的一个,

其中所述第二晶体管的阈值电压等于或低于第一晶体管的阈值电压,并且

所述第三晶体管的阈值电压等于或低于第一晶体管的阈值电压。

- 16. 如权利要求15所述的片上系统,其中所述逻辑电路的电源电压等于或小于1.0V。

- 17. 如权利要求15所述的片上系统,其中所述主驱动器电路包括:

PMOS晶体管,被配置为通过所述第一信号将输入/输出垫的电压上拉到所述第二电压;

第一电阻器,连接到所述PMOS晶体管和所述输入/输出垫;

NMOS晶体管,被配置为通过所述第一信号将所述输入/输出垫的电压下拉到第三电压; 以及

第二电阻器,连接到所述NMOS晶体管和所述输入/输出垫。

18. 如权利要求15所述的片上系统,其中所述主驱动器电路包括:

第一NMOS晶体管,被配置为通过所述第一信号将输入/输出垫的电压上拉到所述第二电压;

第一电阻器,连接到所述第一NMOS晶体管很所述输入/输出垫;

反相器,被配置为通过对所述第一信号进行反相来生成反相信号;

第二NMOS晶体管,被配置为通过所述反相信号将所述输入/输出垫的所述电压下拉到第三电压:以及

第二电阻器,连接到所述第二NMOS晶体管和所述输入/输出垫。

19.如权利要求15所述的片上系统,还包括接收器,配置为基于根据动态电压缩放频率 (DVFS) 操作而发生的电压变化来操作。

20.一种片上系统(SoC),包括:

逻辑电路,被配置为输出逻辑信号并且包括第一晶体管;

输入/输出垫:

预驱动器电路,被配置为从所述逻辑电路接收逻辑信号并且生成由第一电压驱动的第一信号,所述预驱动器电路包括第二晶体管:

主驱动器电路,被配置为接收所述第一信号,配置为生成由第二电压驱动的第二信号,并且被配置为向所述输入/输出垫输出所述第二信号,所述主驱动器电路包括第三晶体管;以及

接收器电路,被配置为基于根据动态电压缩放频率DVFS操作而发生的电压变化来操作,所述接收器电路包括第一缓冲器和第二缓冲器,

其中所述第二晶体管的阈值电压等于或低于第一晶体管的阈值电压,

所述第三晶体管的阈值电压等于或低于第一晶体管的阈值电压,以及

所述第一缓冲器的操作电压不同于所述第二缓冲器的操作电压。

- 21. 如权利要求20所述的片上系统,其中DVFS操作基于所述片上系统的操作频率来执行。

- 22. 如权利要求20所述的片上系统,还包括电平移位器,被配置为将所述逻辑信号的电压电平转换成第一电压电平或者将所述第一信号的电压电平转换成第二电压。

- 23. 如权利要求22所述的片上系统,还包括多路复用器电路,被配置为接收所述逻辑信

号和所述电平移位器的输出或者接收所述第一信号和所述电平移位器的输出信号,所述多路复用器电路被配置为基于模式控制信号向所述预驱动器电路提供所述逻辑信号和所述电平移位器的输出中的一个或者向所述主驱动器电路提供所述第一信号和所述电平移位器的输出信号中的一个。

24.如权利要求20所述的片上系统,其中所述接收器电路包括第一缓冲器、第二缓冲器和多路复用器。

25.一种片上系统(SoC),包括:

逻辑电路,被配置为输出逻辑信号并且包括第一晶体管:

发射器,被配置为从所述逻辑电路接收逻辑信号,并且包括具有与所述第一晶体管相同的特性的低电压晶体管,所述发射器被配置为由逻辑电压和接口电压驱动,以及被配置为将从所述逻辑电路接收的数据经过输入/输出垫发送到外部设备;和

包括第一缓冲器和第二缓冲器的接收器,

其中所述第一缓冲器由第一电压驱动,以从所述输入/输出垫接收低频带的输入数据, 所述第二缓冲器由第二电压驱动,以从所述输入/输出垫接收高频带的输入数据,

所述逻辑电路的电源电压等于或小于1.0V,以及

所述接口电压被设置为高于,等于或低于动态电压缩放频率(DVFS)操作的逻辑电压。

26. 如权利要求25所述的片上系统,其中所述发射器包括:

预驱动器电路,被配置为接收所述逻辑信号并且生成由第三电压驱动的第一信号;

主驱动器电路,被配置为接收所述第一信号,配置为生成由第四电压驱动的第二信号, 并且被配置为输出所述第二信号;

电平移位器,被配置为将所述逻辑信号的电压电平转换成第三电压电平或者将所述第一信号的电压电平转换成第四电压;以及

多路复用器电路,被配置为接收所述逻辑信号和所述电平移位器的输出或者接收所述 第一信号和所述电平移位器的输出信号,所述多路复用器电路被配置为基于模式控制信号 向所述预驱动器电路提供所述逻辑信号和所述电平移位器的输出中的一个或者向所述主 驱动器电路提供所述第一信号和所述电平移位器的输出信号中的一个。

27. 如权利要求26所述的片上系统,其中基于所述片上系统的操作频率确定所述模式控制信号。

28. 如权利要求25所述的片上系统,其中所述第一电压和所述第二电压具有相同的电压电平。

29. 如权利要求25所述的片上系统,其中所述发射器不包括电平移位器。

# 用于在低电压下操作的发射器电路和接收器电路

[0001] 相关申请的交叉引用

[0002] 本申请要求2016年2月2日提交的韩国专利申请号10-2016-0012766和2016年5月20日提交的韩国专利申请号10-2016-0062282的优先权,所述申请的全部内容以引用的方式并入。

#### 背景技术

[0003] 本发明构思的示例性实施例涉及半导体器件,具体地涉及用于低电压操作的发射器电路和接收器电路。

[0004] 根据移动设备的最近趋势,期望高集成、高性能和/或低功率半导体集成电路。半导体集成电路的低功耗可按照各种方式来实现。例如,半导体集成电路的低功耗可被设计为降低半导体集成电路的操作电压。具体地,接口电路消耗用于发射和接收数据的总功耗的大部分。为了降低功耗,最近的片上系统中的逻辑电路的电源电压倾向于减小至例如1.0V或更低。

[0005] 动态电压缩放频率 (DVFS) 技术被用作用于降低半导体集成电路的功耗的另一种方式。DVFS是指用于通过基于半导体集成电路的工作负荷改变半导体集成电路的操作速度和驱动电压来降低功耗的技术。半导体集成电路可以能够基于DVFS操作改变逻辑电路和接口电路的驱动电压。

[0006] 尽管电源电压可以根据移动半导体器件的低电压趋势而减小,并且电源电压可以由于根据DVFS操作的驱动电压的变化而减小,但是发射器电路和接收器电路(其操作得更有效)期望进一步降低半导体器件的功耗。

### 发明内容

[0007] 本发明构思的一些示例性实施例提供用低电压晶体管实现并且在低电压下操作的发射器电路。本发明构思的一些其他示例性实施例提供接收器电路,所述接收器电路包括操作不同操作电压的多个专用缓冲器,并且根据依据动态电压缩放频率 (DVFS) 操作发生的电压改变有效地操作。

[0008] 根据本发明构思的示例性实施例,发射器电路可以包括预驱动器电路和主驱动器电路。预驱动器电路可以从逻辑电路接收逻辑信号以生成由第一电压驱动的第一信号。主驱动器电路可以接收所述第一信号以生成由第二电压驱动的第二信号,以便将第二信号输出到输入/输出垫。预驱动器电路和主驱动器电路中的每一个可以包括晶体管,所述晶体管具有等于或低于逻辑电路中所包括的晶体管的阈值电压的阈值电压。

[0009] 根据本发明构思的示例性实施例,接收电路可以包括:第一输入缓冲器,其被配置为由第一电压驱动以从输入/输出垫接收低频带的输入数据;以及第二输入缓冲器,其被配置为由第二电压驱动以从输入/输出垫接收高频带的输入数据。

[0010] 根据本发明构思的示例性实施例,接口电路可以包括发射器和接收器。发射器可以包括预驱动器电路和主驱动器电路。预驱动器电路可以被配置为从逻辑电路接收逻辑信

号并且生成由第一电压驱动的第一信号,并且可以包括晶体管,所述晶体管具有等于或低于所述逻辑电路中所包括的晶体管的阈值电压的阈值电压。主驱动器电路可以被配置为接收第一信号并且生成由第二电压驱动的第二信号,以便将第二信号输出到输入/输出垫,并且可以包括晶体管,所述晶体管具有等于或低于逻辑电路中所包括的晶体管的阈值电压的阈值电压。接收器可以包括第一输入缓冲器和第二输入缓冲器。第一输入缓冲器可以被配置为由第一电压驱动以从输入/输出垫接收低频带的输入数据。第二输入缓冲器可以被配置为由第三电压驱动以从所述输入/输出垫接收高频带的输入数据。

[0011] 附图简述

[0012] 图1是示出根据本发明构思的示例性实施例的包括发射器电路和接收器电路的片上系统的方框图;

[0013] 图2是示出图1所例示的发射器电路的电路图;

[0014] 图3是示出图2所例示的主驱动器的输出信号的图;

[0015] 图4是示出图2所例示的主驱动器的另一个示例性实施例的电路图:

[0016] 图5是示出图4所例示的主驱动器的输出信号的图;

[0017] 图6是示出图2所例示的电平移位器的电路图;

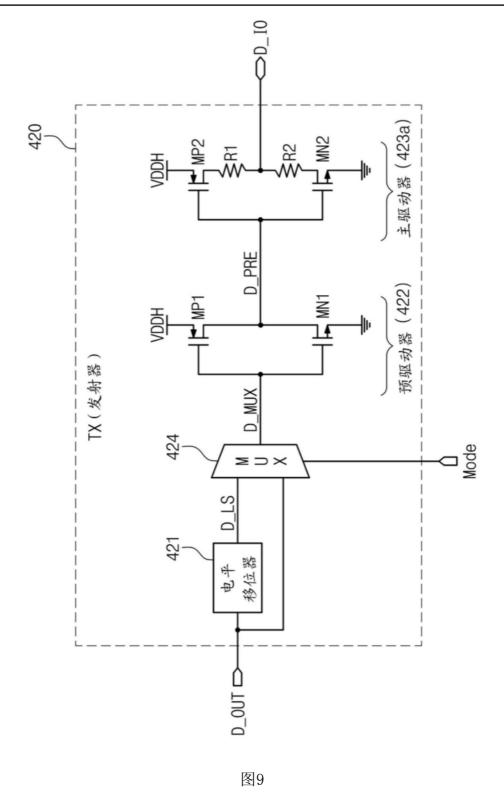

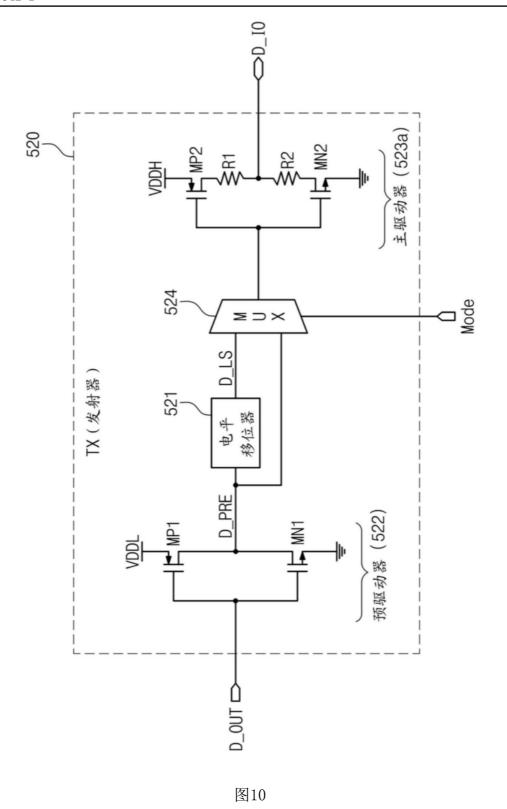

[0018] 图7至图10是根据一些示例性实施例的图1所例示的发射器电路的电路图;

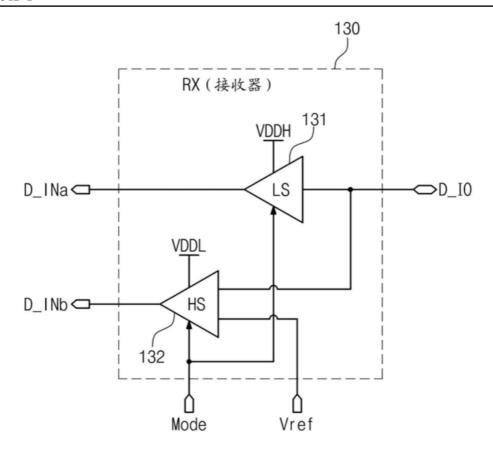

[0019] 图11是示出图1所例示的接收器电路的方框图;

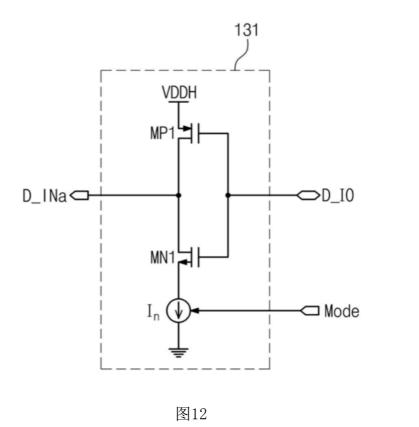

[0020] 图12是示出图11所例示的LS缓冲器的电路图;

[0021] 图13是示出图11所例示的HS缓冲器的电路图;

[0022] 图14是示出图1所例示的接收器电路的另一个示例性实施例的方框图;以及

[0023] 图15是示出根据本发明构思的示例性实施例的移动电子设备的方框图。

## 具体实施方式

[0024] 下面,将更全面地描述本发明构思的一些示例性实施例,使得本领域技术人员可以容易地理解本发明构思。此外,术语"高电压"意指驱动片上系统(SoC)的不同电平的电源电压中的相对高的电压,并且术语"低电压"意指作为通用逻辑电路的驱动电压提供给SoC的电压电平。限定"高电压"和"低电压"的参考可以根据低功率技术的发展而改变。

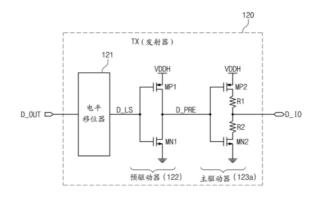

[0025] 图1是示出根据本发明构思的示例性实施例的包括发射器电路和接收器电路的片上系统的方框图。参考图1,片上系统100可包括逻辑电路110、发射器电路120、接收器电路130、静电放电(ESD)电路140、以及输入/输出垫150。

[0026] 逻辑电路110可以与发射器电路120和接收器电路130连接。逻辑电路110可以由逻辑电压VDDL驱动。逻辑电路110可以处理通过接收器电路130从外部接收到的数据并且将经处理的数据发送到外部。例如,在片上系统100是应用处理器 (AP) 或调制解调器应用处理器 (ModAP) 的情况下,逻辑电路110可以包括被配置为处理数据并且与存储器交换经处理的数据的电路、用户接口和/或与片上系统100连接的音频处理器。在片上系统100是存储器芯片的情况下,逻辑电路110可以包括诸如延迟锁定环 (DLL)、单元阵列、解码器和/或读出放大器的元件。逻辑电路110还可以包括基于片上系统100的功能的任何电路。因为逻辑电路110的操作特性与本发明构思的示例性实施例不密切相关,因此在此将不再重复其详细描述。

[0027] 片上系统100可支持范围从1.2V至3.3V的各种电压电平的所有输入/输出信号以

与各种外部芯片对接,而片上系统100中的逻辑电路110的电源电压可以是例如1.0V或更低。在一些示例性实施例中,片上系统100可以通过DVFS操作支持高电压或低电压的各种电压电平的驱动电压,以降低功耗。

[0028] 片上系统100可以通过执行DVFS操作来调整逻辑电路110、发射器电路120和接收器电路130的驱动电压,以便有效地管理片上系统100的功耗和/或性能。例如,在片上系统100的工作负载增加的情况下,片上系统100可以增加逻辑电路110、发射器电路120和/或接收器电路130的驱动电压,以便增加处理数据的速度。在一些示例性实施例中,即使当片上系统100发送和接收数据的数据传送速度增加时,片上系统100可以增加至少一些驱动电压。当片上系统100的工作负载减小时或者当片上系统100以较低的传送速度发送和接收数据时,片上系统100可以减小至少一些驱动电压以降低功耗。

[0029] 此外,为了容易地管理上述片上系统100的功耗和/或性能,可以划分逻辑电路110、发射器电路120和/或接收器电路130的供电电压。然而,如果在片上系统100中划分的供电电压的数量增加,则片上系统100的设计效率和集成度可能劣化。

[0030] 根据本发明构思的示例性实施例,发射器电路120和接收器电路130可以使用具有与逻辑电路110中所使用的晶体管相同的特性的低电压晶体管。例如,低电压晶体管的阈值电压可以低于接口电路中所使用的晶体管的阈值电压。因此,在低电压下可以确保发射器电路120和接收器电路130的性能。因为发射器电路120和接收器电路130在低电压下操作,所以其功耗可能减小。此外,在发射器电路120和接收器电路130使用与逻辑电路110中所使用的晶体管相同的低电压晶体管的情况下,不期望专用于接口电路(未示出)的多个电压源确保发射器电路120和接收器电路130的性能。因此,发射器电路120和接收器电路130可以在专用于接口电路的电压源处操作。

[0031] 因为逻辑电压VDDL和接口电路的电压电平根据片上系统100的性能和功耗特性而变化,所以发射器电路120和接收器电路130可以包括被配置为改变电压域中的数据的附加电路。

[0032] 根据本发明构思的示例性实施例的发射器电路120可以通过输入/输出垫150将通过逻辑电路110接收到的数据传输到外部。发射器电路120可以由逻辑电压VDDL和接口电压 VDDH驱动。因此,发射器电路120可以包括电平移位器,所述电平移位器将数据的逻辑电压 VDDL的电平转换成接口电压 VDDH的电平。将参考图2至图10详细描述发射器电路120的配置和操作。

[0033] 根据本发明构思的示例性实施例的接收器电路130可以通过输入/输出垫150接收数据,并且可以将接收到的数据提供给逻辑电路110。接收器电路130可以包括接收低频带数据的输入缓冲器(以下称为"LS缓冲器")和接收高频带数据的输入缓冲器(以下称为"HS缓冲器")。由于LS和HS缓冲器分别由单独的供电电压驱动,所以接收器电路130可能不需要单独提供用于转换数据的电压电平的移位寄存器。将参考图11至图14更详细地描述接收器电路130的结构和操作。

[0034] ESD电路140可以减轻或防止内部电路受到从外部产生的瞬时高电压的损坏。例如,ESD电路可以用二极管和电阻器的组合来实现。输入/输出垫150可以连接到外部通道,并且片上系统100可以通过输入/输出垫150向外部发送数据/从外部接收数据。发射器电路120、接收器电路130、ESD电路和输入/输出垫150可以通过节点D I0彼此连接。因为ESD电路

140和输入/输出垫150的操作特性与本发明构思的示例性实施例不密切相关,因此在此不再重复其详细描述。

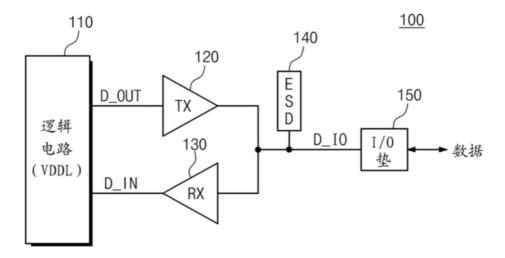

[0035] 图2是示出图1所例示的发射器电路的电路图。参考图2,发射器电路120可以包括电平移位器121、预驱动器122和主驱动器123a。将参考图1描述图2。接口电压VDDH可以被设置为高于、等于或低于用于DVFS操作的逻辑电压VDDL。

[0036] 电平移位器121可以连接在逻辑电路110与预驱动器122之间。电平移位器121可以将从逻辑电路110传输的数据的电压电平转换成预驱动器122和主驱动器123a可以处理的电压电平。也就是说,电平移位器121可以将在逻辑电压VDDL与地(GND)电压之间摆动的数据电平转换成在接口电压VDDH与GND电压之间摆动的信号电平。因此,可以减轻或防止当将低电压电平的信号提供给由高电压驱动的电路的输入时所生成的短路电流。

[0037] 预驱动器122可以连接在电平移位器121与主驱动器123a之间。预驱动器122可以作为主驱动器123a的缓冲器操作。也就是说,预驱动器122可以被提供有来自电平移位器121的数据,并且可以将所提供的数据传输到主驱动器123a的输入节点。预驱动器122可以用包括第一PMOS晶体管MP1和第一NMOS晶体管MN1的反相器来实现。在图2中,预驱动器122可以用一级反相器来实现。在一些示例性实施例中,预驱动器122可以利用包括多个级的反相器电路来实现。此外,例如,预驱动器122可以被配置为分别提供关于构成主驱动器123a的第二PMOS晶体管MP2和第二NMOS晶体管MN2的分类信号路径。

[0038] 主驱动器123a可以将从预驱动器122提供的数据传输到输入/输出垫150。主驱动器123a可以具有"A"型结构,其是指由第二PMOS晶体管MP2和第二NMOS晶体管MN2组成的结构。第二PMOS晶体管MP2和第一电阻器R1可以串联连接在接口电压VDDH与节点D\_I0之间。第二NMOS晶体管MN2和第二电阻器R2可以串联连接在节点D\_I0与GND之间。第二PMOS晶体管MP2和第二NMOS晶体管MN2的栅极可以构成主驱动器123a的输入节点,并且主驱动器123a的输入节点可以与节点D\_PRE连接,所述节点D\_PRE是预驱动器123a的输出节点。

[0039] 当主驱动器123a向外部传输数据时,主驱动器123a可以与外部通道连接。因此,为了防止在传输数据时通道的反射波,主驱动器123a可以执行对与通道匹配的阻抗的操作。因此,发射器电路120还可以包括调整主驱动器123a的输出阻抗的ZQ校准电路(未示出)。在图2中,仅示出第二PMOS晶体管MP2和第二NMOS晶体管MN2以及电阻器R1和R2。然而,示例性实施例不限于此。图2的每个元件可以利用彼此并联连接的两个或更多个器件来实现。此外,在一些情况下,当片上系统100接收数据时,主驱动器123a可以作为片内终结器(ODT)操作。

[0040] 在用于移动设备的片上系统100的情况下,片上系统100可以降低由主驱动器123a 传输的数据的信号电平,以降低其功耗。这样,片上系统100可以减小接口电压VDDH。当传输低频率的数据时,不期望高性能操作,并且因此发射器电路120可以通过DVFS操作来减小接口电压VDDH。如参考图1所述,根据本发明构思的示例性实施例的发射器电路120可以利用低电压晶体管来实现,以便支持低电压的输入/输出信号。因此,发射器电路120可以由诸如逻辑电压VDDL的低电压驱动。然而,为了独立地控制发射器电路120和接收器电路130的驱动电压电平,可以使用不同于逻辑电压VDDL的接口电压VDDH。此外,可以在低电平的接口电压VDDH下确保发射器电路120和接收器电路130的传输质量。

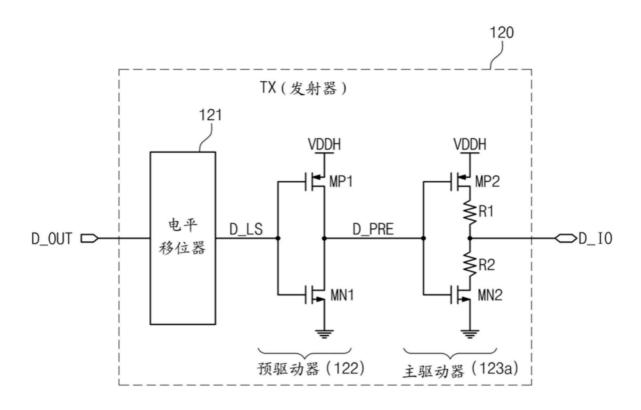

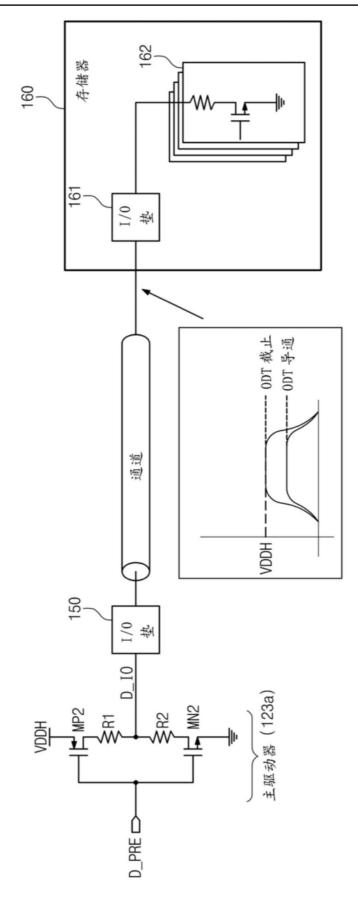

[0041] 图3是示出图2所例示的主驱动器的输出信号的图。参考图3,图2的主驱动器123a

可以通过通道将数据发送到存储器160。将参考图1描述图3。

[0042] 由片上系统100的主驱动器123a开发的数据可以通过输入/输出垫150提供给通道。所提供的数据可以通过通道来传输到存储器160的输入/输出垫161。存储器160的输入/输出垫161处的数据的电压电平可以根据是否使用ODT 162而变化。

[0043] 在图3中,示出通过通道的数据的电压电平。当传输的数据是逻辑"0"时,存储器 160的输入/输出垫161可以通过第二电阻器R2和第二NMOS晶体管MN2连接到GND。因此,不管 0DT 162是否导通,通过通道的数据的电压电平可以是GND电压。当传输的数据是逻辑"1"时,存储器160的输入/输出垫161可以通过第一电阻器R1和第二PMOS晶体管MP2连接到接口电压VDDH。在这种情况下,传输的数据的电压电平可以根据0DT 162是否导通而变化。当0DT 162关闭时,传输的数据可以具有接口电压VDDH的电平。相反,当0DT 162导通时,传输的数据信号可以具有在第二PMOS晶体管MP2、第一电阻器R1和0DT 162之间划分的电压电平。划分的电压电平可以低于接口电压VDDH的电平。

[0044] 例如,存储器160可以包括具有任何形式的0DT 162。在这种情况下,传输的数据的摆动电平可以根据0DT 162的形式而变化。在一些示例性实施例中,存储器160可以不包括0DT 162。

[0045] 例如,存储器160可以包括具有动态随机存取存储器 (DRAM) 和静态随机存取存储器 (SRAM) 的易失性存储器或非易失性存储器。

[0046] 易失性存储器可以包括诸如低功率DDR4 (LPDDR4) 或LPDDR4X存储器的DRAM、SRAM、晶闸管RAM (TRAM)、零电容器RAM (Z-RAM)、双晶体管RAM (TTRAM) MRAM。

[0047] 非易失性存储器可以是电可擦除可编程只读存储器(EEPROM)、闪存、磁性RAM (MRAM)、自旋转移力矩MRAM (STT-MRAM)、导电桥接RAM (CBRAM)、铁电RAM (FeRAM)、相变RAM (PRAM)、电阻RAM (RRAM)、纳米管RRAM (RRAM)、聚合物RAM (PoRAM)、纳米浮栅存储器 (NFGM)、全息存储器、分子电子存储器设备或绝缘体电阻变化存储器。一个或多个位可以存储在非易失性存储器的单元中。

[0048] 在图3中,存储器160被示为连接到片上系统100的外部芯片之一。这只是一个实例。例如,片上系统100可以连接到包括各种功能的芯片,诸如音频处理器、图像处理器、控制器和应用专用集成电路(ASIC)。因为存储器160的操作特性与本发明构思的示例性实施例不密切相关,因此在此不再重复其详细描述。

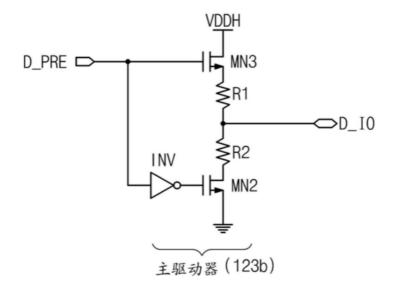

[0049] 图4是示出图2所例示的主驱动器的另一个示例性实施例的电路图。参考图4,主驱动器123b可以包括第二NMOS晶体管MN2和第三NMOS晶体管MN3、第一电阻器R1和第二电阻器R2、以及反相器INV。图4的主驱动器123b可以具有"B"型结构,其是指由第二NMOS晶体管MN2和第三NMOS晶体管MN3组成的结构。将参考图2描述图4。

[0050] 第三NMOS晶体管MP3和第一电阻器R1可以串联连接在接口电压VDDH与节点D\_IO之间。第二电阻器R2和第二NMOS晶体管MN2可以连接在节点D\_IO与GND之间。第二NMOS晶体管MN2和第三NMOS晶体管MN3的栅极可以构成主驱动器123b的输入节点。主驱动器123b的输入节点可以被提供有来自预驱动器122的数据。图4的主驱动器123b可以不同于图2的主驱动器123a,不同之处在于:第二NMOS晶体管MN2被提供有由反相器INV反相的数据。这样,第二NMOS晶体管MN2和第三NMOS晶体管MN3之一可以根据节点D\_PRE的数据而导通。例如,第三NMOS晶体管MN3的栅极可以由反相器INV提供反相的数据,并且第二NMOS晶体管MN2的栅极

可以直接从预驱动器122提供数据(例如,未反相数据)。将参考图5描述主驱动器123b的发射操作和传输的数据的电压电平。

[0051] 图5是示出图4所例示的主驱动器的输出信号的图。在图5中,主驱动器123b可以基本上与图3的主驱动器123a相同,不同的是主驱动器123b具有B型结构,并且因此,在此将不再重复其详细描述。

[0052] 在图5中,示出通过通道传输的数据的电压电平。当传输的数据是逻辑"0"时,如在图3中,通过通道的数据可以具有GND电压的电平,而不管ODT 162是否导通。当传输的数据是逻辑"1"时,传输的数据的电压电平可以根据ODT 162是否接通而变化。当ODT 162关闭时,可以根据第三NMOS晶体管MN3的阈值电压值来确定传输数据的电压电平。也就是说,传输的数据的电压电平可以是"Vgs-Vth"的电压电平。在此,"Vgs"是第三NMOS晶体管MN3的栅极输入电压,并且"Vth"是第三NMOS晶体管MN3的阈值电压。原因是节点D\_IO的电压电平增加,直到第三NMOS晶体管MN3截止。当ODT 162导通时,传输的数据的电压电平可以是在第三NMOS晶体管MN3、第一电阻器R1和ODT 162之间划分的电压电平。

[0053] 与图3的A型主驱动器123a相比,B型主驱动器123b可以传输低于接口电压VDDH的电压的信号。这样,与A型主驱动器123a相比,B型主驱动器123b可以传输比A型主驱动器123a的摆动电平小的摆动电平的信号。因此,可以通过主驱动器123b减少功耗。此外,由于使用NMOS晶体管代替PMOS晶体管,可以减小主驱动器123b的物理尺寸。此外,因为上拉和下拉驱动器由相同的NMOS晶体管实现,所以可以提高上拉和下拉驱动器的对称特性。因为主驱动器123b的摆动电平由第三NMOS晶体管MN3的阈值电压确定,所以信号的传输质量可能受阈值电压分布影响。

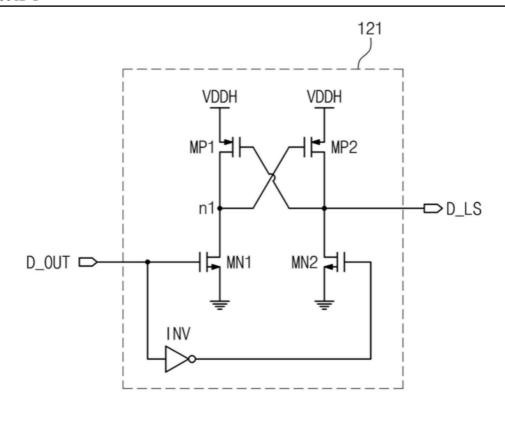

[0054] 图6是示出图2所例示的电平移位器的电路图。参考图6,电平移位器121可以包括第一输入晶体管MN1和第二输入晶体管MN2、第一锁存晶体管MP1和第二锁存晶体管MP2以及反相器INV。电平移位器121将输入信号的电压电平转换成作为电平移位器的驱动电压的接口电压VDDH的电平。将参考图1和图2描述图6。

[0055] 第一输入晶体管MN1和第二输入晶体管MN2可以通过节点D\_0UT从逻辑电路110提供数据。所提供的数据可以逻辑电压VDDL的电平摆动。第一输入晶体管MN1可以直接提供有输入数据,并且第二输入晶体管MN2可以提供有通过反相器INV反相的数据。第一输入晶体管MN1和第二输入晶体管MN2可以对所提供的数据进行反相和放大,并且可以将经反相和放大的数据提供给节点n1和D LS。

[0056] 第一锁存晶体管MP1和第二锁存晶体管MP2可以构成锁存器。第一锁存晶体管MP1和第二锁存晶体管MP2可以将根据输入数据而变化的节点n1和D\_LS的电压上拉或下拉到接口电压VDDH或GND电压。例如,当节点D\_OUT的数据是逻辑"0"时,节点n1可以通过第一锁存晶体管MP1和第二锁存晶体管MP2被上拉到接口电压VDDH,并且节点D\_LS可以变为GND电压。当节点D\_OUT的数据是逻辑"1"时,节点n1可以被下拉到GND电压,并且节点D\_LS可以被上拉到接口电压VDDH。

[0057] 图6所示的电平移位器121的结构仅仅是实例,并且电平移位器121可以具有任何形式的电平移位器结构。例如,电平移位器121可以具有其中仅提供一个输入的单输入电平移位器结构。

[0058] 图7至图10是根据一些示例性实施例的图1所例示的发射器电路的电路图。图7至

图10所示的发射器电路220至520中所包括的元件(例如,预驱动器、主驱动器和/或电平移位器)的配置和操作可以与图2至图6中所示的那些元件相同。因此,在此不再重复其详细描述。此外,主驱动器可以包括A型配置、B型配置或两种类型的配置。

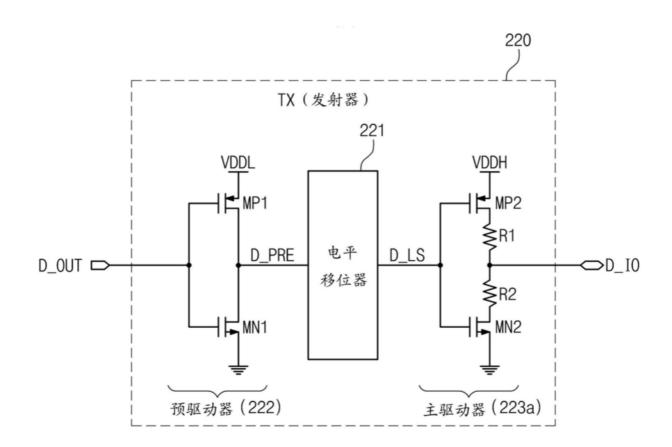

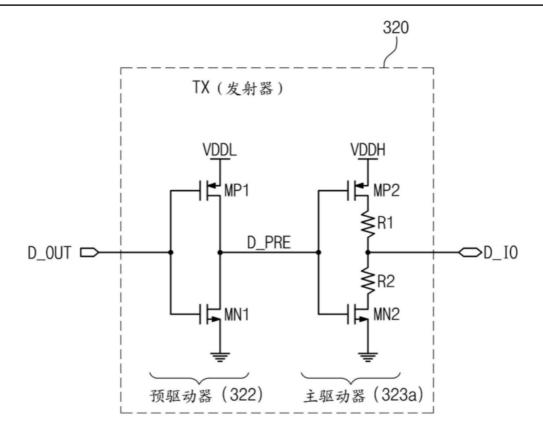

[0059] 参考图7,发射器电路220可以包括电平移位器221、预驱动器222和主驱动器223a。图7的发射器电路220可以不同于图2的发射器电路120,不同之处在于预驱动器222由逻辑电压VDDL驱动,并且电平移位器221连接在预驱动器222与主驱动器223a之间。除了上述差别之外,因为图7的发射器电路220的元件和操作与图2中所示的发射器电路的那些相同,在此不再重复其详细描述。

[0060] 参考图8,发射器电路320可以包括预驱动器322和主驱动器323a。图8的预驱动器322和主驱动器323a可以不同于图2的预驱动器122和主驱动器123a,不同之处在于因为预驱动器322和主驱动器323a由逻辑电压VDDL驱动,所以不使用电平移位器221。原因是预驱动器322和主驱动器323a由具有低阈值电压的低电压晶体管实现。在这种情况下,因为包括图8的发射器电路320的片上系统100不使用单独的接口电压,但是可以降低设计片上系统100的难度,并且可以降低用于设计片上系统100的成本。

[0061] 图2、图7和图8的发射器电路120、220和320可以包括基本上相同的配置。设计者可以基于设计考虑来选择图2、图7和图8的发射器电路120、220和320的配置之一。例如,设计考虑可以包括设计中的困难、发射器电路的控制信号的数量和/或数据传输质量。

[0062] 参考图9,发射器电路420可以包括电平移位器421、预驱动器422、主驱动器423a和多路复用器424。发射器电路420可以通过多路复用器424选择将要通过节点D\_0UT提供的数据的传输路径。以下,数据通过电平移位器421的路径可以被称为"第一路径",并且数据不通过(例如,旁路)电平移位器421的路径可以被称为"第二路径"。

[0063] 当接口电压VDDH的电压电平大于逻辑电压VDDL的电压电平时,发射器电路420可以选择第一路径以减轻或防止由于短路电流引起的功耗。也就是说,为了通过低于接口电压VDDH的输入电压来防止预驱动器422的短路电流的发生,输入电压的电平可以通过第一路径转换成接口电压VDDH的电平。

[0064] 当接口电压VDDH的电压电平等于或低于逻辑电压VDDL的电压电平时,发射器电路420可以选择第二路径。也就是说,当接口电压VDDH低于逻辑电压VDDL时,在预驱动器422中可能不发生短路电流,因此,可不需要转换数据的电压电平(意味着数据可能不通过电平移位器421)。因此,当使用不需要通过DVFS操作的电平移位器的驱动电压的组合时,图9的发射器电路420可以选择第二路径,从而减少数据信号的传播延迟时间。可以由多路复用器424基于模式控制信号Mode来选择第一路径或第二路径,并且下面将描述确定模式控制信号Mode的方法。

[0065] 多路复用器424可以由模式控制信号Mode控制,并且可以确定通过节点D\_0UT提供的数据的传输路径。可以将通过多路复用器424选择的通过第一路径和第二路径之一的数据提供给预驱动器422。

[0066] 模式控制信号Mode可以根据图1的片上系统100的操作频率来确定。也就是说,可以根据将要发射/接收的数据的频率来确定片上系统100的操作频率,并且可以基于操作频率来执行DVFS操作。也就是说,片上系统100可以基于操作频率来调整接口电压VDDH的电压电平。

[0067] 例如,当片上系统100的操作频率高于参考频率时,为了保持数据传输质量,片上系统100可以操作以设置为使得接口电压VDDH高于逻辑电压VDDL。在这种情况下,可以选择第一路径。当片上系统100的操作频率低于参考频率时,为了降低功耗,片上系统100可以使接口电压VDDH等于或低于逻辑电压VDDL。在这种情况下,可以选择第二路径。

[0068] 在本说明书中,描述确定模式控制信号Mode的一个实例。然而,模式控制信号Mode可以由根据DVFS操作的任何算法确定。例如,模式控制信号Mode可以由图1的逻辑电路110或外部控制器确定。

[0069] 参考图10,发射器电路520可以包括电平移位器521、预驱动器522、主驱动器523a和多路复用器524。图10的发射器电路520的配置和操作与图9基本上相同,不同的是电平移位器521和多路复用器524连接在预驱动器522与主驱动器523a之间。因此,在此不再重复其详细描述。

[0070] 图11是示出图1所例示的接收器电路的电路图。参考图11,接收器电路130可以包括LS缓冲器131和HS缓冲器132。将参考图1描述图11。接收器电路130可以基于模式控制信号Mode选择性地使用LS缓冲器131和HS缓冲器132之一。图11的模式控制信号Mode可以是与图9的控制信号相同的控制信号,并且因此,在此不再重复其详细描述。

[0071] LS缓冲器131可以接收通过节点D\_I0传输的数据,并且可以通过输出节点D\_Ina将接收到的数据提供给逻辑电路110。LS缓冲器131可以由接口电压VDDH驱动,并且可以被实现为接收低频率的数据。在图11中,LS缓冲器131被示为不使用参考电压。这只是一个实例。例如,LS缓冲器131可以被实现为使用参考电压。将参考图12描述LS缓冲器131的示例性配置。

[0072] HS缓冲器132可以接收通过节点D\_IO传输的数据,并且可以通过输出节点D\_INb将接收到的数据提供给逻辑电路110。HS缓冲器132可以由逻辑电压VDDL驱动,并且可以被实现为接收高频率的数据。将参考图13描述HS缓冲器132的示例性配置。

[0073] 如图11所示,LS缓冲器131和HS缓冲器132的输出节点D\_INa和D\_INb可以彼此分离,以使逻辑电路110基于输出节点D\_INa和D\_INb的电压电平单独处理传输的数据。

[0074] 例如,当逻辑电压VDDL的电平高于接口电压VDDH的电平时,由于通过输出节点D\_INa提供的数据的低电压,可以在逻辑电路110中生成短路电流。在这种情况下,逻辑电路110还可以包括用于通过单独的输出节点D\_INa提供的数据的电平移位器。因为通过输出节点D\_INb提供的数据的电压摆动电平以与逻辑电路110中相同的逻辑电压VDDL的电平摆动,所以逻辑电路110可以直接接收通过输出节点D\_INb提供的数据。

[0075] 然而,当逻辑电压VDDL等于或低于接口电压VDDH时,逻辑电路110可以不需要电平移位器,并且因此输出节点D INa和D INb可以被集成。

[0076] 如上所述,根据DVFS操作,图1的片上系统100可以改变逻辑电路110和接收器电路130的操作电压。在这种情况下,可以根据逻辑电路110和/或接收器电路130的性能来确定片上系统100的操作性能。因此,根据本发明构思的示例性实施例的接收器电路130可以包括操作电压和电路配置彼此分开的LS缓冲器131和HS缓冲器132,以有效地接收数据,即使当逻辑电压VDDL或接口电压VDDH根据DVFS操作而改变。

[0077] 当根据操作电压和电路配置来分开各缓冲器时,可以根据DVFS操作容易地管理各缓冲器的特性。例如,当在同一操作频率的数据上使用高电平的逻辑电压VDDL时,LS缓冲器

131可以由相对低电平的接口电压VDDH驱动。因此,接收器电路130可以在不受逻辑电压 VDDL影响的情况下操作,从而降低功耗。在一些示例性实施例中,为了提高在相同的情况下的传输质量,接收器电路130可以选择并使用由相对高电平的逻辑电压VDDL驱动的具有高性能的HS缓冲器132。

[0078] 此外,使用如上所述的单独的缓冲器可以具有额外的益处。与多目的电路相比,用于一个目的的专用电路可以具有高操作效率并且可以有利于设计优化。例如,因为LS缓冲器131接收低频率的数据,所以LS缓冲器131可以被设计为以低性能操作,以减轻功耗。也就是说,LS缓冲器131可以被设计为低性能缓冲器,以便仅接收低频率的低摆动电平的数据信号。HS缓冲器132可以被设计为接收高摆动电平的数据信号的高性能缓冲器。因此,LS缓冲器131和HS缓冲器132可以被设计为具有优化或改进的特性,和/或可以减少专用电路的缓冲器所占用的面积。

[0079] 图12是示出图11所例示的LS缓冲器的电路图。参考图12,LS缓冲器131可以包括第一PMOS晶体管MP1、第一NMOS晶体管MN1和电流源In。图12的LS缓冲器131可以作为反相器操作。

[0080] 第一PMOS晶体管PM1和NMOS晶体管MN1构成反相器并分别通过其栅极接收数据。电流源In串联连接在第一NMOS晶体管MN1的源极节点与地GND之间。电流源In可以向LS缓冲器131提供恒定电流,并且可以由模式控制信号Mode控制。LS缓冲器131可以根据电流源In是否导通/截止而导通/截止。

[0081] 图12的LS缓冲器131可以基于反相器的逻辑阈值电压来区分通过节点D\_I0接收的数据的信号电平。在图12中,反相器结构被示为LS缓冲器131的实例。这只是一个实例。例如,LS缓冲器131可以不限于图12并且可以用具有缓冲功能的任何电路来实现。

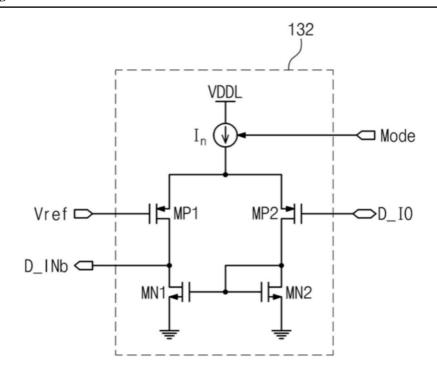

[0082] 图13是示出图11所例示的HS缓冲器的电路图。参考图13,HS缓冲器132可以包括第一输入晶体管MP1和第二输入晶体管MP2、第一负载晶体管MN1和第二负载晶体管MN2、以及电流源Ip。图13的HS缓冲器132可以作为差分放大器操作。

[0083] 第一输入晶体管MP1可以用PMOS晶体管来实现,并且可以被提供有参考电压Vref作为输入。例如,参考电压Vref的电平可以是"VDDL/2"的电压电平。第二输入晶体管MP2可以用PMOS晶体管实现,并且可以通过节点D\_IO接收数据。图13的HS缓冲器132可以通过PMOS晶体管接收数据,以通过低电压摆动端接逻辑(LVSTL)技术接收具有低电压电平的数据摆动。这只是一个实例。例如,第一输入晶体管MP1和第二输入晶体管MP2中的每一个可以基于数据摆动电平利用NMOS晶体管来实现。

[0084] 第一负载晶体管MN1和第二负载晶体管MN2构成电流镜。第一负载晶体管MN1和第二负载晶体管MN2中的每一个可以用NMOS晶体管实现,并且可以作为关于HS缓冲器132的输出数据信号的负载操作。因此,输出信号可以通过第一负载晶体管MN1的漏极节点提供给输出节点D INb。

[0085] 电流源Ip可以连接在逻辑电压VDDL与第一输入晶体管MP1和第二输入晶体管MP2的源极节点之间。电流源Ip可以由模式控制信号Mode控制。LS缓冲器131可以根据电流源Ip是否导通/截止而导通/截止。

[0086] 图13的HS缓冲器132可以基于参考电压Vref来区分通过节点D\_I0接收的数据的信号电平。例如,当通过节点D\_I0接收的数据的电压电平高于参考电压Vref的电压电平时,流

过第二输入晶体管MP2的电流量可能减小;相反,流过第一输入晶体管MP1的电流量可以增加。这样,因为第一负载晶体管MN1的电流量增加,所以输出节点D\_INb的电压可以增加。因此,HS缓冲器132可接收逻辑"1",并可将接收到的逻辑"1"输出到输出节点D\_INb。

[0087] 在图13中,差分放大器被示为HS缓冲器132的示例性实施例。这只是一个实例。例如,HS缓冲器132可以不限于图13并且可以被实现为具有缓冲功能的任何电路。尽管在图12和13中未示出,LS缓冲器131和HS缓冲器132中的每一个还可以包括用于使接收到的数据与时钟信号同步的触发器。

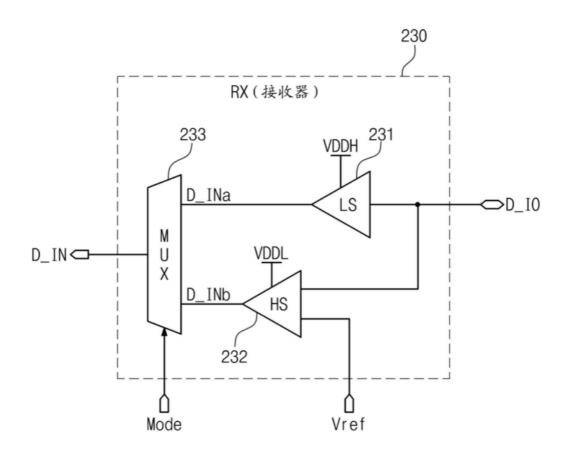

[0088] 图14是示出图1所例示的接收器电路的另一个示例性实施例的方框图。参考图14,接收器电路230可以包括LS缓冲器231、HS缓冲器232和复用器233。LS缓冲器231和HS缓冲器232的配置和操作可以基本上与图11的那些相同或相似地操作,不同的是LS缓冲器231和HS缓冲器232不由模式控制信号Mode控制。因此,在此不再重复其详细描述。

[0089] 多路复用器233可以被提供有LS缓冲器231和HS缓冲器232中的每一个的输出数据,并且可以向节点D\_IN提供由模式控制信号Mode选择的输出数据。尽管在图14中未示出,多路复用器233还可以包括用于HS缓冲器232的输出数据信号的电平移位器的功能。当多路复用器233接收模式控制信号Mode时,LS和HS缓冲器231和232可以不由模式控制信号Mode控制。因此,与图11的LS缓冲器131和HS缓冲器132相比,LS缓冲器231和HS缓冲器232可以按照改进的方式设计。

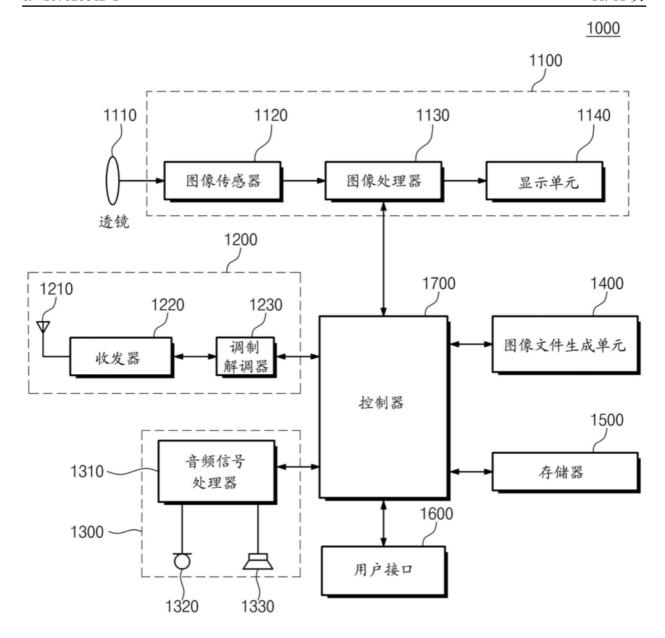

[0090] 图15是示出根据本发明构思的示例性实施例的移动电子设备的方框图。参考图 15,移动电子设备1000可以包括透镜1110、图像处理单元1100、无线收发器单元1200、音频 处理单元1300、图像文件生成单元1400、存储器1500、用户接口1600和控制器1700。

[0091] 图像处理单元1100可以包括图像传感器1120、图像处理器1130和显示单元1140。 无线收发器单元1200可以包括天线1210、收发器1220和调制解调器1230。音频处理单元 1300可以包括音频处理器1310、麦克风1320和扬声器1330。

[0092] 存储器1500可以是诸如多媒体卡(MMC)、嵌入式多媒体卡(eMMC)、安全数字(SD) 卡、微型SD卡等的存储卡。此外,控制器1700可以是驱动应用程序、操作系统等的片上系统。 控制器1700可以被配置为与图像处理器1130和调制解调器1230通信。

[0093] 存储器1500可以用包括参考图1至图14描述的发射器电路和接收器电路的存储器来实现。在一些示例性实施例中,控制器1700可以用包括参考图1至图14描述的发射器电路和接收器电路的片上系统来实现。因此,即使当电源电压根据DVFS而变化时,存储器1500或控制器1700也可以有效地发射和接收数据。

[0094] 根据示例性实施例,因为发射器电路和接收器电路在低驱动电压下操作,所以其功耗可能降低。另外,因为接收器电路根据操作电压具有专用缓冲器,所以接收器电路可以被设计为减小接收器电路所占据的设计面积,从而可以提高其性能。

[0095] 如上所述,在附图和说明书中公开了最佳示例性实施例。在此,本文中所使用的术语仅仅是为了描述具体示例性实施例,并且不意图限制本发明构思。这里,本文所使用的术语仅用于描述特定示例性实施例的目的,并且不旨在限制本发明构思。本发明构思的技术保护范围将由所附权利要求的技术精神限定。

图1

图2

图3

图4

图5

图6

图7

图8

图11

图13

图14

图15