## (19) 日本国特許庁(JP)

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2009-195602 (P2009-195602A)

(43) 公開日 平成21年9月3日(2009.9.3)

| (51) Int.Cl. |       |           | F I     |       |      | テーマコード (参考) |

|--------------|-------|-----------|---------|-------|------|-------------|

| A61B         | 1/04  | (2006.01) | A 6 1 B | 1/04  | 362J | 2HO4O       |

| G02B         | 23/24 | (2006.01) | A 6 1 B | 1/04  | 370  | 40061       |

| HO4N         | 7/18  | (2006.01) | GO2B    | 23/24 | В    | 5CO54       |

|              |       |           | HO4N    | 7/18  | M    |             |

審査請求 未請求 請求項の数 6 OL (全 14 頁)

|                       |                                                        | 田旦明小     | 小明小 明小頃の数 0 0 0 1 (主 14 貝/                   |  |

|-----------------------|--------------------------------------------------------|----------|----------------------------------------------|--|

| (21) 出願番号<br>(22) 出願日 | 特願2008-42885 (P2008-42885)<br>平成20年2月25日 (2008. 2. 25) | (71) 出願人 | 000005430<br>フジノン株式会社<br>埼玉県さいたま市北区植竹町1丁目324 |  |

|                       |                                                        |          | 番地                                           |  |

|                       |                                                        | (74) 代理人 | — <del>-</del>                               |  |

|                       |                                                        |          | 弁理士 小林 和憲                                    |  |

|                       |                                                        | (74) 代理人 | 100095234                                    |  |

|                       |                                                        |          | 弁理士 飯嶋 茂                                     |  |

|                       |                                                        | (72) 発明者 | 中村 和彦                                        |  |

|                       |                                                        |          | 埼玉県さいたま市北区植竹町1丁目324<br>番地 フジノン株式会社内          |  |

|                       |                                                        |          |                                              |  |

|                       |                                                        | Fターム (参  | 考) 2H040 DA12 DA22 GA02 GA10 GA11            |  |

|                       |                                                        |          | 4C061 AA01 BB01 CC06 DD03 GG01               |  |

|                       |                                                        |          | LL02 NN05 NN07 SS30 YY14                     |  |

|                       |                                                        |          | 5C054 CC07 HA12                              |  |

|                       |                                                        |          |                                              |  |

(54) 【発明の名称】電子通信システム及び内視鏡システム

## (57)【要約】

【課題】外部装置から電子装置にデータを高速にかつ安定してシリアル伝送する。

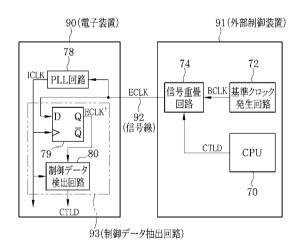

【解決手段】制御データCTLDを送信する送信側の外部制御装置(外部装置)91は、基準クロック信号BLCKを発生する基準クロック発生回路72と、制御データCTLDを発生するCPU70と、基準クロック信号に制御データCTLDを重畳させたものを外部クロック信号ECLKとして、信号線92を介して電子装置90にシリアル伝送させる信号重畳回路74とを備える。受信側の電子装置90は、外部制御装置91からシリアル伝送される外部クロック信号BLCKの周波数と同期した内部クロック信号ICLKを生成するPLL回路78と、内部クロック信号ICLKに基づき、外部クロック信号ECLKに重畳された制御データCTLDを抽出する制御データ抽出回路93とを備える。

【選択図】図9

### 【特許請求の範囲】

### 【請求項1】

電子装置と外部装置とが信号線を介して接続された電子通信システムにおいて、

前記外部装置は、基準クロック信号を発生する基準クロック発生回路と、データを発生 す る デ ー 夕 発 生 回 路 と 、 前 記 基 準 ク ロ ッ ク 信 号 に 前 記 デ ー タ を 重 畳 さ せ た も の を 外 部 ク ロ ック信号として、前記信号線を介して前記電子装置にシリアル伝送させる信号重畳回路と を備え、

前記電子装置は、前記外部装置からシリアル伝送される前記外部クロック信号の周波数 と同期した内部クロック信号を生成する内部クロック生成回路と、前記内部クロック信号 に基づき、前記外部クロック信号に重畳された前記データを抽出するデータ抽出回路とを 備えたことを特徴とする電子通信システム。

### 【請求項2】

前 記 外 部 装 置 は 、 前 記 デ ー タ の ビ ッ ト 数 を 増 や し 、 同 じ デ ー タ が 所 定 ビ ッ ト 以 上 連 続 し ないように前記データをエンコードするエンコーダを備えることを特徴とする請求項1に 記載の電子通信システム。

### 【請求項3】

前記信号重畳回路は、前記データ発生回路からデータが発生されない場合には、前記基 準 ク ロ ッ ク 信 号 を そ の ま ま 外 部 ク ロ ッ ク 信 号 と し て 前 記 電 子 装 置 に シ リ ア ル 伝 送 さ せ る こ とを特徴とする請求項1または2に記載の電子通信システム。

## 【請求項4】

前記データは、前記電子装置を制御するための制御データであることを特徴とする請求 項1から3いずれか1項に記載の電子通信システム。

### 【請求項5】

固体撮像素子を有する撮像装置を内蔵した内視鏡と、前記固体撮像素子を制御するプロ セッサ装置とが信号線を介して接続され、前記撮像装置は、前記プロセッサ装置から前記 信号線を介して伝送されたデータに基づいて前記固体撮像素子の撮像動作及び前記固体撮 像 素 子 か ら 出 力 さ れ た 撮 像 信 号 の 信 号 処 理 を 行 う 内 視 鏡 シ ス テ ム に お い て 、

前 記 プロ セ ッ サ 装 置 は 、 基 準 ク ロ ッ ク 信 号 を 発 生 す る 基 準 ク ロ ッ ク 発 生 回 路 と 、 前 記 デ ータを発生するデータ発生回路と、前記基準クロック信号に前記データを重畳させたもの を外部クロック信号として、前記信号線を介して前記撮像装置にシリアル伝送させる信号 重畳回路とを備え、

前 記 撮 像 装 置 は 、 前 記 プ ロ セ ッ サ 装 置 か ら シ リ ア ル 伝 送 さ れ る 前 記 外 部 ク ロ ッ ク 信 号 の 周波数と同期した内部クロック信号を生成する内部クロック生成回路と、前記内部クロッ ク 信 号 に 基 づ き 、 前 記 外 部 ク ロ ッ ク 信 号 に 重 畳 さ れ た 前 記 デ ー タ を 抽 出 す る デ ー タ 抽 出 回 路とを備えたことを特徴とする内視鏡システム。

## 【請求項6】

前記固体撮像素子は、CMOS型の固体撮像素子であることを特徴とする請求項4に記 載の内視鏡システム。

## 【発明の詳細な説明】

# 【技術分野】

[ 0 0 0 1 ]

本発明は、撮像装置等の電子装置と外部装置とが信号線を介して電気的に接続された電 子通信システム及び内視鏡システムに関するものである。

# 【背景技術】

## [0002]

C C D (Charge Coupled Device) 型 や C M O S (Complementary Metal Oxide Semicon ductor )型 の 固 体 撮 像 素 子 の 小 型 化 が 進 め ら れ て お り 、 医 療 分 野 に お け る 内 視 鏡 シ ス テ ム に適用されている。内視鏡システムは、被検体内に挿入され、固体撮像素子により被検体 内を撮像する撮像装置を備えた内視鏡と、撮像装置の動作を制御するとともに、撮像装置 から送られてきた画像をモニタに表示させる外部装置(プロセッサ装置)とが信号線を介 20

10

30

40

して相互に接続されてなる一種の電子通信システムである。

### [0003]

CMOS型固体撮像素子は、CCD型固体撮像素子とは異なり、固体撮像素子の駆動や信号処理を行う周辺回路とともに、半導体により形成された一体の撮像装置として1チップ化(SoC(System On a Chip)化)が可能であるため、撮像動作により得た撮像信号を1チップ化された撮像装置内で処理することができ、外部装置に接続されるモニタに適合したフォーマットの映像信号として出力することができる。

### [0004]

CMOS型固体撮像素子を備えた撮像装置において実行される撮像信号の処理としては、ホワイトバランス調整、ゲイン補正、ガンマ補正、映像信号へのフォーマット変換等がある。これらの処理内容は、外部装置に接続されるモニタの種類や、撮像装置の使用環境(例えば、照明光の明るさや波長)等によって異なるため、CMOS型固体撮像素子を撮像装置内に備えた内視鏡システムでは、撮像装置における処理の実行のために、撮像装置に対して、処理内容に対応した制御データを外部装置から伝送する必要がある(例えば、特許文献 1 , 2 参照)。

### [00005]

特許文献 1 , 2 に記載の内視鏡システムでは、信号線の本数を削減するために、 1 本の信号線を用いて外部装置から撮像装置へ制御データを伝送(シリアル伝送)させており、撮像装置内では、伝送された制御データをビット単位で時系列的に検出するために、クロック発生器により発生した内部クロック信号に基づいて、制御データの検出が行われている。

【特許文献 1 】特開 2 0 0 2 - 1 8 5 8 5 3 号公報

【特許文献 2 】特開 2 0 0 2 - 1 8 5 8 7 3 号公報

【発明の開示】

【発明が解決しようとする課題】

### [0006]

特許文献 1 , 2 に記載の内視鏡システムのように、受信側の電子装置(撮像装置)内で発生した内部クロック信号を用いて、外部から伝送される制御データを検出する電子通信システムでは、制御データの伝送周波数が低い場合には特に問題はないが、制御データの伝送周波数が高い場合(例えば、1 G H z を超える場合)には、制御データの伝送周波数と内部クロック信号の周波数との間にずれが生じ、制御データの誤検出が生じることが問題となる。

### [0007]

かかる問題を解決するために、送信側の外部装置と受信側の電子装置との間に、制御データ伝送用の信号線(データ線)に加えてクロック信号伝送用の信号線(クロック線)を配し、送信側から制御データとともにそれに同期したクロック信号を伝送し、受信側では伝送されたクロック信号を用いて制御データの検出を行う高速シリアル伝送技術を用いることが考えられる。

## [0008]

しかしながら、この高速シリアル伝送技術を用いたとしても、内視鏡システムのように送受信間に距離があり、長い信号線を有する電子通信システムでは、各信号線に付随する寄生容量や配線抵抗の差により、データ線とクロック線との間でタイミングスキュー(データ信号とクロック信号との位相差)が生じて制御データの伝送が不安定化し、その結果、受信側では、制御データの誤検出が生じるといった問題がある。

# [0009]

本発明は、上記課題を鑑みてなされたものであり、外部装置から電子装置に制御データ 等のデータを高速にかつ安定してシリアル伝送することができる電子通信システム及び内 視鏡システムを提供することを目的とする。

【課題を解決するための手段】

## [0010]

10

20

30

上記目的を達成するために、本発明の電子システムは、電子装置と外部装置とが信号線を介して接続された電子通信システムにおいて、前記外部装置は、基準クロック信号を発生する基準クロック発生回路と、データを発生するデータ発生回路と、前記基準クロック信号に前記データを重畳させたものを外部クロック信号として、前記信号線を介して前記電子装置にシリアル伝送させる信号重畳回路とを備え、前記電子装置は、前記外部装置からシリアル伝送される前記外部クロック信号の周波数と同期した内部クロック信号を生成する内部クロック生成回路と、前記内部クロック信号に基づき、前記外部クロック信号に重置された前記データを抽出するデータ抽出回路とを備えたことを特徴とする。

[0011]

なお、前記外部装置は、前記データのビット数を増やし、同じデータが所定ビット以上連続しないように前記データをエンコードするエンコーダを備えることが好ましい。

[0012]

また、前記信号重畳回路は、前記データ発生回路からデータが発生されない場合には、前記基準クロック信号をそのまま外部クロック信号として前記電子装置にシリアル伝送させることが好ましい。

[ 0 0 1 3 ]

また、前記データは、前記電子装置を制御するための制御データであることが好ましい -

[0014]

また、本発明の内視鏡システムは、固体撮像素子を有する撮像装置を内蔵した内視鏡と、前記固体撮像素子を制御するプロセッサ装置とが信号線を介して接続され、前記撮像装置は、前記プロセッサ装置から前記信号線を介して伝送されたデータに基づいて前記固体撮像素子の撮像動作及び前記固体撮像素子から出力された撮像信号の信号処理を行う内視鏡システムにおいて、前記プロセッサ装置は、基準クロック信号を発生する基準クロック信号を発生するがロック信号として、前記信号線を介して前記撮像装置にシリアル伝送させる信号重畳回路とを備え、前記撮像装置は、前記プロセッサ装置からシリアル伝送される前記外部クロック信号の周波数と同期した内部クロック信号に重畳された可能である。前記内部クロック信号に基づき、前記外部クロック信号に重畳された前記データを抽出するデータ抽出回路とを備えたことを特徴とする。

[0015]

なお、前記固体撮像素子は、CMOS型の固体撮像素子であることが好ましい。

【発明の効果】

[0016]

本発明の電子通信システムによれば、外部装置は、内部で発生した基準クロック信号にデータを重畳させたものを外部クロック信号として、信号線を介して電子装置にシリアル伝送させるので、伝送されるクロック信号とデータとの間にタイミングスキューが生じるといった問題は生じず、データの伝送の高速化及び安定化を図ることができる。また、1本の信号線を用いてクロック信号とデータとを伝送することができるため、電子装置と外部装置との間を接続する信号線の本数を削減することができる。

[0017]

また、本発明の内視鏡システムでは、1本の信号線を用いてクロック信号とデータとをシリアル伝送することができることから、信号線が挿通されるケーブルを細線化し、電子内視鏡を細径化するすることができる。これにより、電子内視鏡が挿入される患者の負担が軽減される。

【発明を実施するための最良の形態】

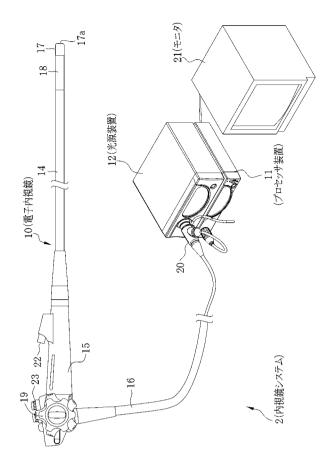

[0018]

図1において、内視鏡システム2は、電子内視鏡10、プロセッサ装置11、光源装置12などから構成されている。電子内視鏡10は、体腔内に挿入される可撓性の挿入部14と、挿入部14の基端部分に連設された操作部15と、プロセッサ装置11及び光源装

10

20

30

40

置12に接続されるユニバーサルコード16とを備えている。

### [0019]

挿入部14の先端には、体腔内撮影用の撮像チップ(撮像装置)42(図3参照)や照明部などが内蔵された先端部17が連設されている。先端部17の後方には、複数の湾曲駒を連結した湾曲部18が設けられている。湾曲部18は、操作部15に設けられたアングルノブ19が操作されて、挿入部14内に挿設されたワイヤが押し引きされることにより、上下左右方向に湾曲動作する。これにより、先端部17が体腔内の所望の方向に向けられる。

### [0020]

ユニバーサルコード16の基端は、コネクタ20に連結されている。コネクタ20は、 複合タイプのものであり、コネクタ20にはプロセッサ装置11が接続される他、光源装 置12が接続される。

### [0021]

プロセッサ装置11は、ユニバーサルコード16内に挿通されたケーブル50(図3参照)を介して電子内視鏡10に給電を行い、撮像チップ42の駆動を制御するとともに、撮像チップ42からケーブル50を介して伝送された映像信号を受信し、受信した映像信号を、プロセッサ装置11にケーブル接続されたモニタ21に内視鏡画像として表示させる。また、プロセッサ装置11は、コネクタ20を介して光源装置12と電気的に接続され、内視鏡システム2の動作を統括的に制御する。

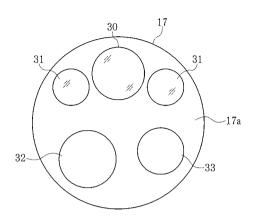

# [0022]

図2において、先端部17の前面17aには、観察窓30、照明窓31、鉗子出口32、及び送気・送水用ノズル33が設けられている。観察窓30は、先端部17の片側中央に配置されている。照明窓31は、観察窓30に関して対称な位置に2個配され、体腔内の被観察部位に光源装置12からの照明光を照射する。鉗子出口32は、挿入部14内に配設された鉗子チャンネル51(図3参照)に接続され、操作部15に設けられた鉗子口22(図1参照)に連通している。鉗子口22には、注射針や高周波メスなどが先端に配された各種処置具が挿通され、各種処置具の先端が鉗子出口32から露呈される。送気・送水用ノズル33は、操作部15に設けられた送気・送水ボタン23(図1参照)の操作に応じて、光源装置12に内蔵された送気・送水装置から供給される洗浄水や空気を、観察窓30や体腔内に向けて噴射する。

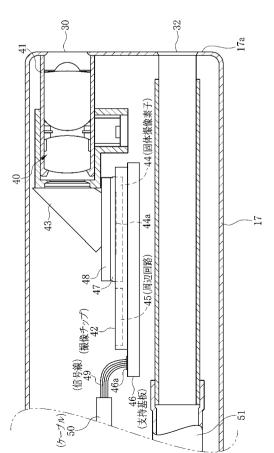

### [0023]

図3において、観察窓30の奥には、体腔内の被観察部位の像光を取り込むための対物 光学系40を保持する鏡筒41が配設されている。鏡筒41は、挿入部14の中心軸に対 物光学系40の光軸が平行となるように取り付けられている。鏡筒41の後端には、対物 光学系40を経由した被観察部位の像光を、略直角に曲げて撮像チップ42に向けて導光 するプリズム43が接続されている。

# [0024]

撮像チップ42は、CMOS型の固体撮像素子44と、固体撮像素子44の駆動及び信号処理を行う周辺回路45とが一体形成(SoC化)されたモノリシック半導体(いわゆるCMOSセンサチップ)であり、支持基板46上に実装されている。固体撮像素子44の撮像面44aは、プリズム43の出射面と対向するように配置されている。撮像面44a上には、矩形枠状のスペーサ47を介して矩形板状のカバーガラス48が取り付けられている。撮像チップ42、スペーサ47、及びカバーガラス48は、接着剤を介して組み付けられている。これにより、塵埃などの侵入から撮像面44aが保護されている。

### [0025]

挿入部14の後端に向けて延設された支持基板46の後端部には、複数の入出力端子46aが支持基板46の幅方向に並べて設けられている。入出力端子46aには、ユニバーサルコード16を介してプロセッサ装置11との各種信号の遣り取りを媒介するための信号線49(図5の信号線49a~49e)が接合されており、入出力端子46aは、支持基板46に形成された配線やボンディングパッド等(図示せず)を介して撮像チップ42

10

20

30

40

内の周辺回路45と電気的に接続されている。信号線49は、可撓性の管状のケーブル5 0内にまとめて挿通されている。ケーブル50は、挿入部14、操作部15、及びユニバーサルコード16の各内部を挿通し、コネクタ20に接続されている。

## [0026]

また、図示は省略したが、照明窓31の奥には、照明部が設けられている。照明部には、光源装置12からの照明光を導くライトガイドの出射端が配されている。ライトガイドは、ケーブル50と同様に、挿入部14、操作部15、及びユニバーサルコード16の各内部を挿通し、コネクタ20に入射端が接続されている。

## [0027]

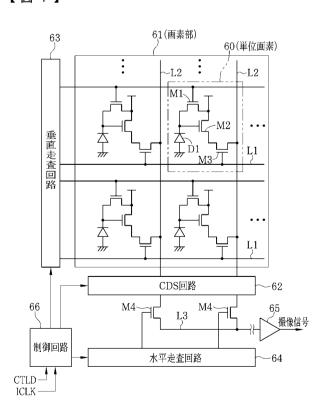

図4において、固体撮像素子44は、単位画素60がマトリクス状に配置された画素部61と、画素部61からの出力信号(画素データ)の処理(ノイズ抑制処理)を行なう相関二重サンプリング(CDS)回路62と、画素部61の垂直方向の走査を制御するとともに画素部61のリセット動作を制御する垂直走査回路63と、水平方向の走査を制御する水平走査回路64と、画素データの出力を行う出力回路65と、各回路62~64に制御信号を与え、垂直・水平走査及びサンプリングのためのタイミング等を制御する制御回路66とから構成されている。

### [0028]

単位画素 6 0 は、 1 個のフォトダイオード D 1 、 リセット用トランジスタ M 1 、 ドライブ用(増幅用)トランジスタ M 2 、 及び画素選択用トランジスタ M 3 とからなる。各単位画素 6 0 は、垂直走査線(行選択線) L 1 及び水平走査線(列信号線) L 2 に接続されており、垂直走査回路 6 3 と水平走査回路 6 4 によって順次に走査される。

#### [0029]

制御回路66は、画素部61の行及び列を走査するために垂直走査回路63及び水平走査回路64に入力する制御信号、フォトダイオードD1に蓄積された信号電荷をリセットするために垂直走査回路63に入力する制御信号、及び画素部61とCDS回路62との接続を制御するためにCDS回路62に入力する制御信号をそれぞれ生成する。

### [0030]

CDS回路62は、列信号線L2ごとに区分して設けられており、垂直走査回路63によって選択された行選択線L1に接続された各単位画素60の画素データを、水平走査回路64が出力する水平走査信号に従って順次に出力する。水平走査回路64は、CDS回路62と、出力回路65に接続された出力バスラインL3との間に設けられた列選択用トランジスタM4のオン/オフを水平走査信号により制御する。出力回路65は、CDS回路62から出力バスラインL3に順次に転送される画素データを増幅して出力する。以下では、出力回路65から出力される一連の画素データをまとめて撮像信号と称する。

# [0031]

なお、図示は省略するが、固体撮像素子44は、複数の色セグメントからなるカラーフィルタ(例えば、ベイヤー配列の原色カラーフィルタ)を備えた単板カラー撮像方式の固体撮像素子である。

## [0032]

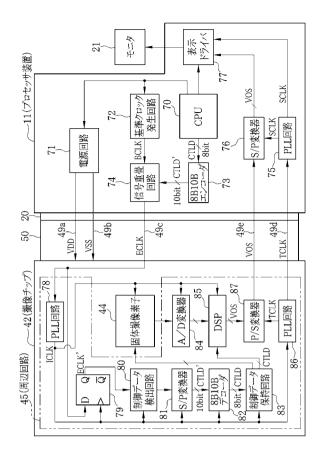

図 5 において、プロセッサ装置 1 1 は、 C P U (データ発生回路) 7 0 、電源回路 7 1 、基準クロック発生回路 7 2 、 8 B 1 0 B エンコーダ 7 3 、信号重畳回路 7 4 、 P L L (Phase-Locked Loop) 回路 7 5 、シリアル / パラレル (S / P) 変換器 7 6 、及び表示ドライバ 7 7 によって構成されている。

# [ 0 0 3 3 ]

CPU70は、プロセッサ装置11内の各部を制御するとともに、撮像チップ42の動作を制御するために、例えば8ビットのパラレル信号からなる制御データCTLDを出力し、8B10Bエンコーダ73を介して信号重畳回路74に入力する。

### [0034]

電源回路71は、電源電圧VDD及び接地電圧VSSを生成し、生成した電源電圧VDD及び接地電圧VSSを、プロセッサ装置11内の各部に供給するとともに、信号線49

10

20

30

40

(7)

a , 4 9 b を介して撮像チップ 4 2 内の各部に供給する。基準クロック発生回路 7 2 は、周波数が安定した基準クロック信号 B C L K を発生し、発生した基準クロック信号 B C L K を信号重畳回路 7 4 に入力する。

### [0035]

8 B 1 0 B エンコーダ 7 3 は、 C P U 7 0 から入力された 8 ビットの制御データ C T L D に対し、冗長な 2 ビットのデータを付加して 1 0 ビットの制御データ C T L D 'に変換する 8 B 1 0 B 方式のエンコーダであり、 8 ビットから 1 0 ビットへの変換は、規格で定められた変換表を用いて行う。この変換は、信号線 4 9 c を介して行うシリアル伝送の際に同じ信号レベル("0"または"1")が所定期間以上連続しないようにするためのものであり、例えば、元の 8 ビットの制御データ C T L Dが"0001111"のときには、"010111000"の10ビットの制御データ C T L D'に変換を行う。

[0036]

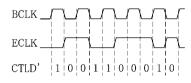

信号重畳回路74は、基準クロック発生回路72から入力された基準クロック信号BCLKに、8B10Bエンコーダ73から入力された制御データCTLD′を重畳することにより外部クロック信号ECLKを生成し、生成した外部クロック信号ECLKを、信号線49cを介して撮像チップ42ヘシリアル伝送させる。

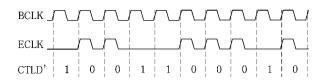

### [0037]

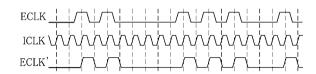

具体的には、信号重畳回路74は、図6に示すように、基準クロック信号BCLKの立ち上がリエッジを検出し、制御データCTLD'が"1"に対応する1周期(立ち上がリエッジから次の立ち上がリエッジまでの期間)をLowレベルに固定するように変換を行うことにより、制御データCTLD'が重畳された外部クロック信号ECLKを生成する。同図では、8B10Bエンコーダ73により変換された制御データCTLD'が"1001100010"の場合を示している。この制御データCTLD'は、負論理で表現したものであり、"1"はLowレベルに対応し、"0"はHighレベルに対応する。

[0038]

[0039]

PLL回路 7 5 は、位相比較器、ループフィルタ、電圧制御発信器、及び分周器を備える位相同期回路であり、撮像チップ 4 2 から信号線 4 9 dを介して伝送されるシリアル伝送用クロック信号 TCLKを受信し、このシリアル伝送用クロック信号 TCLKの周波数を所定倍(例えば 1 / 1 0 倍)に逓倍して、撮像チップ 4 2 内の内部クロック信号 ICLKと同一の周波数を有するクロック信号 SCLKを生成する。このクロック信号 SCLKは、S/P変換器 7 6 及び表示ドライバ 7 7 に供給される。

[0040]

S / P変換器 7 6 は、撮像チップ 4 2 から信号線 4 9 e を介してシリアル伝送される映像信号 V O S を受信し、 P L L 回路 7 5 が生成したクロック信号 S C L K に応じて、受信した映像信号 V O S をパラレル信号に変換して表示ドライバ 7 7 に順次に入力する。表示ドライバ 7 7 は、クロック信号 S C L K に基づき、映像信号 V O S を画像としてモニタ 2 1 に表示させる。

### [0041]

撮像チップ 4 2 内の周辺回路 4 5 は、 P L L 回路 7 8 、 D 型フリップフロップ 7 9 、制御データ検出回路 8 0 、 S / P 変換器 8 1 、 8 B 1 0 B デコーダ 8 2 、制御データ保持回路 8 3 、アナログ / デジタル ( A / D ) 変換器 8 4 、デジタル信号処理回路 ( D S P ) 8

10

20

30

40

5、 P L L 回路 8 6、 及びパラレル / シリアル ( P / S ) 変換器 8 7 によって構成されている。なお、本実施形態では、 D 型フリップフロップ 7 9、 制御データ検出回路 8 0 、 S / P 変換器 8 1、 及び 8 B 1 0 B デコーダ 8 2 が特許請求の範囲に記載の制御データ抽出回路に含まれる。

### [0042]

PLL回路78は、前述のPLL回路75と同様な構成であり、信号重畳回路74から信号線49cを介して入力される外部クロック信号ECLKの位相を検出して、この外部クロック信号ECLKの周波数を所定倍(例えば2倍)に逓倍した内部クロック信号ICLKを生成する。この内部クロック信号ICLKは、周辺回路45内の各部、及び固体撮像素子44の制御回路66(図4参照)に供給される。

[0043]

D型フリップフロップ79は、データ入力端子Dに外部クロック信号ECLKが入力され、クロック入力端子に内部クロック信号ICLKが入力される。D型フリップフロップ79は、図7に示すように、データ入力端子Dに入力された外部クロック信号ECLKを、内部クロック信号ICLKの立ち上がリエッジでサンプリングして保持することで、内部クロック信号ICLKに位相同期したリタイミングデータとして外部クロック信号ECLK で再生する。このリタイミングされた外部クロック信号ECLK は、データ出力端子Qから出力され、制御データ検出回路80に入力される。なお、PLL回路78とD型フリップフロップ79とは、いわゆるクロックデータリカバリ(Clock & Data Recovery:CDR)回路を構成している。

[0044]

制御データ検出回路80は、D型フリップフロップ79から入力される外部クロック信号ECLK'の遷移(立ち上がりエッジ、立ち下がりエッジ、または両エッジ)を、内部クロック信号ICLKに基づいて監視し、外部クロック信号ECLK'が周期的であるか否かを判定することで、外部クロック信号ECLK'に重畳された前述の制御データCTLD'が含まれる期間のみをS/P変換器81に入力する。具体的には、制御データ検出回路80は、図6に示す外部クロック信号ECLKのような非周期的な波形を検出した場合に、この波形部分をS/P変換器81に入力する。一方、制御データ検出回路80は、図6に示す基準クロック信号BCLKのような周期的な波形を検出した場合には、この波形部分はS/P変換器81に入力せずに破棄する。

[0045]

S/Р変換器81は、内部クロック信号ICLKに基づいて、制御データ検出回路80から部分的に入力される外部クロック信号ECLK'をパラレル信号に変換する。これにより、プロセッサ装置11内で8B10Bエンコーダ73により生成された10ビットの制御データCTLD'が復元される。復元された制御データCTLD'は、8B10Bデコーダ82に入力される。

[0046]

8 B 1 0 B デコーダ 8 2 は、 8 B 1 0 B 方式の規格で定められた変換表を用い、前述の 8 B 1 0 B エンコーダ 7 3 とは逆の変換を行い、入力された制御データ C T L D 'を 1 0 ビットから元の 8 ビットに復元する。 8 B 1 0 B デコーダ 8 2 により復元された 8 ビットの制御データ C T L D は、制御データ保持回路 8 3 に入力される。

[0047]

制御データ保持回路83は、データを一時的に保持するレジスタ回路からなり、入力された制御データCTLDを保持するとともに、制御データCTLDを、その種類に応じて固体撮像素子44内の制御回路66とDSP85とにそれぞれ入力する。固体撮像素子44の制御回路66に入力される制御データCTLDの種類としては、画素の走査方式(全画素走査/インターレース走査)、走査する画素領域(走査開始・終了する単位画素60の位置)、シャッタ速度(露光時間)などの駆動条件が挙げられる。また、DSP85に入力される制御データCTLDの種類としては、ホワイトバランス補正、ゲイン補正、色補間、輪郭強調補正、ガンマ補正、映像信号へのフォーマット変換等の実行のオン/オフ

10

20

30

40

10

20

30

40

50

や、ホワイトバランス補正やゲイン補正の補正係数、映像信号への変換フォーマット等の信号処理条件が挙げられる。固体撮像素子 4 4 内の制御回路 6 6 は、制御データ保持回路 8 3 から入力された制御データ C T L D 及び内部クロック信号 I C L K に基づいて、撮像動作を実行する。

## [0048]

A / D変換器 8 4 は、固体撮像素子 4 4 から出力される撮像信号について、アナログ信号である各画素データを量子化して、例えば、 8 ビット( 2 5 6 階調)のデジタル信号に変換し、デジタル化された撮像信号を D S P 8 5 に入力する。 D S P 8 5 は、ホワイトバランス補正、ゲイン補正、色補間、輪郭強調補正、ガンマ補正、映像信号へのフォーマット変換等の処理機能を備え、制御データ保持回路 8 3 から供給された制御データ C T L D により指定される処理を、指定された設定条件に基づいて実行し、映像信号 V O S を出力する。

### [0049]

PLL回路86は、前述のPLL回路75と同様な構成であり、内部クロック信号ICLKの周波数を所定倍(例えば10倍)に逓倍したシリアル伝送用クロック信号TCLKを生成し、生成したシリアル伝送用クロック信号TCLKを、P/S変換器87に供給するとともに、信号線49dを介してプロセッサ装置11内のPLL回路75へ伝送させる

### [0050]

P/S変換器87は、PLL回路86が生成したシリアル伝送用クロック信号TCLKに応じて、DSP85から入力される映像信号VOSをシリアル信号に変換し、信号線49eを介してプロセッサ装置11内のS/P変換器76へ伝送させる。

### [0051]

上記のように構成された内視鏡システム2で体腔内を観察する際には、電子内視鏡10、プロセッサ装置11、光源装置12、及びモニタ21の電源をオンにして、電子内視鏡10の挿入部14を体腔内に挿入し、光源装置12からの照明光で体腔内を照明しながら、挿入部14の先端部17に内蔵される撮像チップ42により撮像される体腔内の画像をモニタ21に表示して観察する。

## [0052]

プロセッサ装置11内のCPU70は、撮像チップ42の駆動に際して、制御データCTLDを発生する。制御データCTLDは、モニタ21の種類や光源装置12の種類(照明光の明るさや波長)に応じて決定されたものであり、固体撮像素子44の駆動条件(画素の走査方式、画素の走査領域、シャッタ速度等)や、DSP85による撮像信号の信号処理条件(各種処理のオン/オフ、ホワイトバランス補正やゲイン補正の補正係数、映像信号への変換フォーマット等)の制御を行うためのものである。

## [0053]

CPU70から出力された制御データCTLDは、8B10Bエンコーダ73を介して10ビットのパラレル信号に変換され、制御データCTLD'として信号重畳回路74に入力される。信号重畳回路74には、基準クロック発生回路72から基準クロック信号BCLKが入力されており、制御データCTLD'が入力されると、この制御データCTLD'を基準クロック信号BCLKに重畳させることにより外部クロック信号ECLKを生成し、信号線49cを介して撮像チップ42に伝送させる。信号重畳回路74は、制御データCTLD'がゼロ固定の場合)には、入力された基準クロック信号BCLKをそのまま外部クロック信号ECLKとして、信号線49cを介して撮像チップ42に伝送させる。

# [0054]

撮像チップ42は、シリアル伝送された外部クロック信号ECLKを、周辺回路45内のPLL回路78及びD型フリップフロップ79で受け、PLL回路78により内部クロック信号ICLKを生成するとともに、D型フリップフロップ79により、内部クロック信号ICLKに位相同期した外部クロック信号ECLK^を生成する。この外部クロック

信号ECLK'は、制御データ検出回路80により、外部クロック信号ECLK'に重畳された制御データCTLD'を含む期間が検出され、その期間(波形部分)のみが抽出される。

[0055]

制御データ検出回路80により抽出された外部クロック信号ECLK'の部分波形は、S/P変換器81及び8B10Bデコーダ82を介して、元の8ビットの制御データCTLDに復元される。復元された制御データCTLDは、制御データ保持回路83により保持され、その種類に応じて、固体撮像素子44内の制御回路66かDSP85に入力される。この制御データCTLDに基づいて固体撮像素子44により撮像動作が行われ、A/D変換器84によりA/D変換が行われ、DSP85により信号処理が行われた結果、映像信号VOSが生成される。

[0056]

DSP85により生成された映像信号VOSは、P/S変換器87によりシリアル信号に変換され、PLL回路86によって生成されたシリアル伝送用クロック信号TCLKに同期して、プロセッサ装置11に伝送された映像信号VOSは、S/P変換器76によってパラレル信号に変換され、表示ドライバ77を介してモニタ21に画像表示される。

[0057]

以上説明したように、内視鏡システム2では、基準クロック信号BCLKに制御データCTLD'を重畳させることにより、1本の信号線49cを介して伝送を行っているので、伝送されるデータ信号とクロック信号との間にタイミングスキューが生じるといった問題は生じず、伝送の高速化及び安定化が図られる。

[0058]

また、内視鏡システム 2 では、上記のように 1 本の信号線 4 9 c を介して基準クロック信号 B C L K 及び制御データ C T L D 'を伝送することができるため、ケーブル 5 0 を細線化して、電子内視鏡 1 0 の細径化を図ることができる。これにより、電子内視鏡 1 0 が挿入される患者の負担が軽減される。

[0059]

また、内視鏡システム2では、8B10Bエンコーダ73により、制御データCTLDを、同じデータが所定期間以上連続しないように制御データCTLD'に変換してから基準クロック信号BCLKに重畳してシリアル伝送を行っているため、受信側の撮像チップ42内のPLL回路78では、信号の遷移情報(立ち上がりエッジ)を高頻度に検出することができ、基準クロック信号BCLKの周波数に同期した内部クロック信号ICLKを常に正確に生成することができる。

[0060]

なお、上記実施形態では、CPU70は、撮像チップ42の制御を行わない場合に、8B10Bエンコーダ73を介して、信号重畳回路74にゼロ固定の制御データCTLD′を入力することによって、信号重畳回路74の重畳処理を実質的に停止させているが、CPU70が信号重畳回路74を直接制御することにより重畳処理を停止させても良い。

[0061]

また、上記実施形態では、信号重畳回路74は、制御データCTLD'を基準クロック信号BCLKに重畳させることにより外部クロック信号ECLKを生成しているが、さらに、制御データCTLD'にチェックサム(check sum)を付加してから重畳を行うことも好ましい。チェックサムとは、制御データCTLD'を所定ビット数ごとに分割し、それぞれのブロック内のデータを数値とみなして合計を取った値である。受信側の撮像チップ42内に、外部クロック信号ECLKから復元した制御データCTLD'から同様にチェックサムを計算し、送信側から送られてきたチェックサムと一致するか否かを検査する検査回路を設けることにより、通信経路上で生じたデータの誤りを検出することができる

[0062]

50

30

10

20

また、上記実施形態では、制御データCTLD'を負論理で表現しているため、信号重畳回路74は、図6に示すように、基準クロック信号BCLKの立ち上がりエッジを検出し、制御データCTLD'が"1"に対応する1周期をLowレベルに固定するように外部クロック信号ECLKへの変換を行っているが、制御データCTLD'を正論理で表現する場合には、上記とは逆に、制御データCTLD'が"0"に対応する一周期の期間をLowレベルに固定することが好ましい。また、信号重畳回路74は、基準クロック信号BCLKの立ち下がりエッジを検出するものであっても良く、さらに、制御データCTLD'が"1"または"0"に対応する1周期(立ち下がりエッジから次の立ち下がりエッジまでの期間)をHighレベルに固定するものであっても良い。

## [0063]

また、上記実施形態では、信号重畳回路74は、基準クロック信号BCLKの1周期に対して、制御データCTLD'の1ビットを割り当てて変換を行っているが、基準クロック信号BCLKの立ち上がり及び立ち下がりの両エッジを検出することにより、図8に示すように、基準クロック信号BCLKの半周期に対して、制御データCTLD'の1ビットを割り当てて変換を行っても良い。これにより、いわゆるダブルデータレートの転送が可能となり、データ転送速度が2倍に向上する。

### [0064]

また、上記実施形態では、プロセッサ装置11から撮像チップ42に入力された制御データCTLDを固体撮像素子44内の制御回路66及びDSP85に設定しているが、この制御データCTLDを、映像信号VOSとともに信号線49eを介してプロセッサ装置11に入力するように構成しても良い。この場合、制御データCTLDを、映像信号VOSのブランキング期間(水平ブランキング期間または垂直ブランキング期間)に重畳させて伝送することが好ましい。これにより、プロセッサ装置11では、撮像チップ42に制御データCTLDが正しく入力されたか否かを確認することができる。

### [0065]

また、上記実施形態では、電子通信システムとして内視鏡システムを例示して説明したが、本発明はこれに限定されず、超音波振動子を用いて撮像を行う超音波内視鏡システム、撮像機能を備える鏡筒が本体に着脱可能なデジタルカメラ、カメラとパソコンとからなるWebカメラシステム等の撮像システムの他、撮像機能を備えない電子通信システムにも適用可能である。

### [0066]

すなわち、本発明は、図9に示すように、電子装置90とこれを制御する外部制御装置91とが信号線92を介して接続された電子通信システムに適用可能である。外部制御装置91は、制御データCTLDを発生するCPU(データ発生回路)70と、基準クロック信号BCLKを発生する基準クロック発生回路72と、基準クロック信号BCLKを外部クロック信号ECLKを生成し、生成した外部クロック信号ECLKを生成し、生成した外部クロック信号ECLKを生成するPLL回路74とを備えるCLKの周波数に同期した内部クロック信号ICLKを生成するPLL回路(内部クロック生成回路)78と、生成された内部クロック信号ICLKに基づき、外部クロック信号 ECLKに重量された制御データCTLDを抽出する制御データ抽出回路93とを備えるものであれば良い。制御データ抽出回路93は、前述したD型フリップフロップ79と制御データ検出回路80とによって構成可能であるが、この構成は適宜変更して良い。

# [0067]

また、上記実施形態では、制御データを送信する場合について例示しているが、本発明はこれに限定されず、制御データ以外のデータ(動作状況を示すステータスデータ等)を送信する場合においても適用可能である。

## 【図面の簡単な説明】

## [0068]

【図1】内視鏡システムの概略構成を示す図である。

10

20

30

40

- 【図2】電子内視鏡の先端部の前面を示す図である。

- 【図3】電子内視鏡の先端部の構成を示す拡大部分断面図である。

- 【図4】固体撮像素子の構成を示す回路図である。

- 【図5】撮像チップ及びプロセッサ装置の構成を示すブロック図である。

- 【図6】信号重畳回路の動作を説明するタイミングチャートである。

- 【図7】D型フリップフロップの動作を説明するタイミングチャートである。

- 【図8】信号重畳回路の動作の別の例を説明するタイミングチャートである。

- 【図9】本発明を適用した電子通信システムを示すブロック図である。

### 【符号の説明】

[0069]

- 2 内視鏡システム

- 10 電子内視鏡

- 11 プロセッサ装置

- 42 撮像チップ(撮像装置)

- 4 4 固体撮像素子

- 4 9 信号線

- 49a~49e 信号線

- 70 СРU(データ発生回路)

- 72 基準クロック発生回路

- 7 3 8 B 1 0 B エンコーダ

- 7 4 信号重畳回路

- 78 PLL回路(内部クロック生成回路)

- 79 D型フリップフロップ

- 80 制御データ検出回路

- 8 1 シリアル/パラレル変換器

- 8 2 8 B 1 0 B デコーダ

- 83 制御データ保持回路

- 8 5 デジタル信号処理回路

- 90 電子装置

- 9 1 外部制御装置(外部装置)

- 9 2 信号線

- 93 制御データ抽出回路(データ抽出回路)

10

20

【図1】 【図2】

【図3】

【図4】

# 【図5】

# 【図6】

# 【図7】

# 【図8】

# 【図9】