## (12) UK Patent Application (19) GB (11) 2062878 A

- (21) Application No 8031968

- (22) Date of filing 3 Oct 1980

- (30) Priority data

- (31) 54/127730

- (32) 3 Oct 1979

- (33) Japan (JP)

- (43) Application published 28 May 1981

- (51) INT CL3 GO1R 19/04

- (52) Domestic classification G1U BV1C

- (56) Documents cited

None

- (58) Field of search G1U

- (71) Applicant

Victor Company of

Japan Ltd

No 12

3-Chome

Moriya-Cho

Kanagawa-Ku

Yokohama-City

Kanagawa-Ken

Japan

(72) Inventor

Tomohiro Mouri

(74) Agents Marks & Clerk 57-60 Lincoln's Inn

London WC2A 3LS

## (54) Level detection circuit

(57) A peak value detection and holding circuit 14, 15, D, C, R includes a capacitor for holding the peak value of a detected input signal, which is supplied to the input for a predetermined time *via* control means 12, after which a discharge circuit 16, 17 discharges the capacitor C. The level of the input signal is detected by measuring the time taken for the capacitor C to be discharged to a predetermined voltage. Thus, the level detection circuit is substantially insensitive to

fluctuations in the input signal level caused, by drop-outs and unstable magnetic tape-tape head contact when detecting the level of a signal reproduced from magnetic tape.

UD 7 U U O / O F

## **SPECIFICATION**

## Level detection circuit

5 The present invention provides a level detection circuit comprising a peak value detection and holding circuit having a capacitor mum peak value of an input signal and accordingly detects the maximum value of the 10 level of the input signal.

Recently, in cassette type tape recorders, for example, a circuit which automatically adjusts and establishes the most suitable recording bias current, recording equalizer characteristic recording and/or reproducing sensitivity and the like according to the kind of tape has been used, by employing a micro-computer to perform the measurements. Upon this type of automatic measurement, there is a need to record a specific signal on a part of the tape, and reproducing this signal to detect the level. Therefore, it is necessary to employ a level detection circuit which is capable of accurately

detecting the signal level.

The conventional level detection circuit which employs a micro-computer to detect the level was organized so that an input signal is applied to the integrating circuit to perform an integration operation by charging a capacitor

in the integrating circuit during a specific time controlled by the micro-computer, the charged electric charge in the above capacitor is discharged after the above specific charging time is elapsed, and the discharging interval during

the voltage of the capacitor reaches a specific voltage (for example, zero volts) is measured by the micro-computer, to detect the input signal level by using the above time.

However, when the contact between the 40 magnetic tape and the magnetic head is instable due to instability of the magnetic tape travelling in the tape recorder, fluctuation is introduced in the reproduced signal level. Therefore, the integrated voltage varied due to

45 the fluctuation in the signal level, and suffered a disadvantage in that accurate level detection could not be performed. Furthermore, upon partial drop-out of the reproduced signal, the integrated voltage varied, and also suffered a 50 disadvantage in that accurate level detection

could not be performed.

Hence, the inventor of the present invention perceived on the point that the level fluctuation of the reproduced signal in the tape recorder is generated symmetrically up-and-down as in the regular amplitude modulation, and that even upon the above fluctuation in the reproduced signal level, its maximum value is substantially equal to the maximum value of the reproduced signal upon normal contact between the magnetic tape and head.

value of the reproduced signal upon normal contact between the magnetic tape and head, and level upon level fluctuation in other parts is lower than the normal reproduced signal level. Accordingly, in the conventional circuits the whole reproduced signal level was inte-

grated, thus not being able to perform accurate level detection. However, in the present invention, level detection is performed by holding the peak level of the reproduced level 70 for a specific period of time sufficient for time interval during the maximum value appears.

Accordingly, it is a general object of the present invention to provide a novel and use-

ful level detection circuit.

The present invention provides a level detection circuit comprosing a peak value detection and holding circuit having a capacitor which detects and holds the peak value of an input signal by charging said capacitor, opera-

80 tion control means for supplying said input signal to said peak value detection and holding circuit during a specific time interval to perform maximum value detection and holding operation, a discharge circuit for perform-

85 ing constant current discharge of a charged electric charge in said capacitor of said peak value detection and holding circuit after said specific time interval, and detection means for detecting the level of said input signal by

90 measuring the time interval between a time point the constant current discharge of said capacitor by said discharge circuit is initiated and a time point the terminal voltage of said capacitor reaches a specific voltage.

95 Another and specific object of the invention is to provide a level detection circuit which detects the signal level by holding the peak value of the input signal in a capacitor for a specific period of time, afterwards discharging 00 the charged electric charge in the capacitor

100 the charged electric charge in the capacitor, and measuring the discharging time by use of a micro-computer.

Other objects and further features of the invention will be apparent from the following 105 detailed description when read in conjunction with the accompanying drawings.

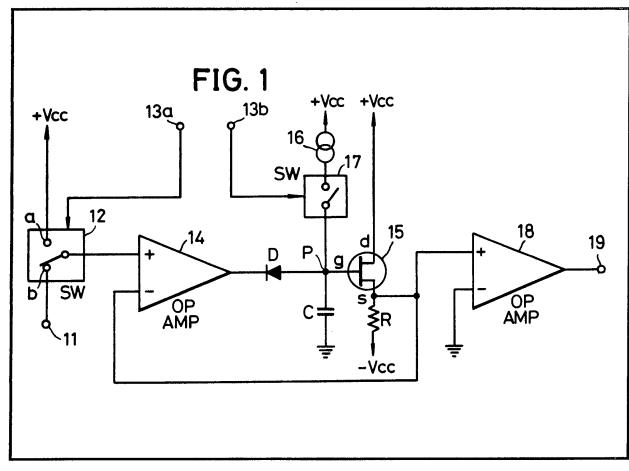

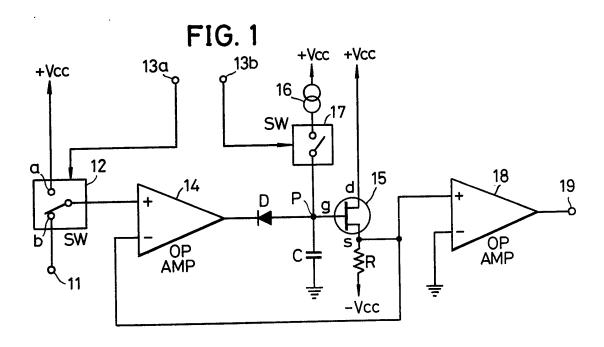

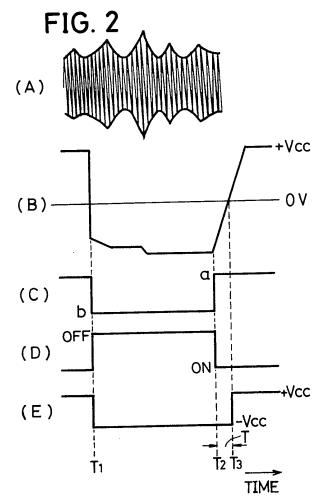

Figure 1 is a circuit diagram of one embodiment of a level detection circuit of the present invention; and

110 Figures 2(A) through 2(E) are respectively graphs showing the signal waveforms at respective parts of the circuit of Fig. 1.

In Fig. 1, the reproduced signal from the magnetic tape in the tape recorder, is applied 115 to an input terminal 11 as an input signal. An electronic switching circuit 12 is shown for explanation as a type in which a movable contact changes over between fixed contact points a and b. The contact point a is con-

120 nected to a direct current (DC) voltage source of a positive voltage + Vcc, and the contact point b is connected to the input terminal 11. The switch of the electronic switching circuit 12 is connected to a non-inverting input ter-

125 minal of an operational amplifier 14.

The output side of the operational amplifier 14 is connected to a gate g of a field-effect-transistor (FET) 15 through a diode D connected with its polarity reversed. A capacitor

130 C for charging and discharging is connected

between the ground and a connection point P between the diode D and gate g of the FET 15. A constant current source 16 and an electronic switching circuit 17 are connected between the connection point P and the DC voltage source of the voltage + Vcc. The electronic switching circuit 17 is shown for explanation as an opening-and-closing switch.

The electronic switching circuits 12 and 17 are respectively controlled by a switching control signal supplied by a micro-computer (not shown) through terminals 13a and 13b.

A drain terminal *d* of the FET 15 is connected to the DC voltage source of the voltage 15 + Vcc, and a source *s* is connected to the DC voltage source of the negative voltage - Vcc through a resistor *R*. Furthermore, the source terminal *s* of the FET 15 is connected to an inverting input terminal of the operational 20 amplifier 14 and also to a non-inverting input terminal of an operational amplifier 18. An inverting input terminal of the operational amplifier 18 is grounded.

Here, the operational amplifier 14, diode *D*, 25 capacitor *C*, FET 15, and resistor *R* construct a circuit which detects and holds the peak value of the reverse polarity characteristic. In addition, the operational amplifier 18 operates as a so-called zero-cross detector.

30 In the electronic switching circuit 12, the switch is changed over and connected to the contact b side at a time point t1, as shown in Fig. 2(A), by the control signal from the microcomputer applied through the terminal 13a. Accordingly, the input signal (the reproduced signal from the magnetic tape in the tape recorder) of the waveform shown in Fig. 2(C) applied to the input terminal 11, is supplied to the non-inverting input terminal of 40 the operational amplifier 14 through the electronic switching circuit 12 beyond the time point t<sub>1</sub>. The above input signal is usually a sinusoidal wave with constant peak level, however, in Fig. 2(A), the input signal is

magnetic tape, and level variation.

The electronic switching circuit 12 is turned off at the time point t<sub>1</sub> as shown in Fig. 2(D), by the control signal from the micro-computer applied through the terminal 13b. The connection of the switch to the contact b side within the electronic switching circuit 12, and the OFF state of the electronic switching circuit 17 is maintained until a time point t<sub>2</sub>. The time interval between the time points t<sub>1</sub> and t<sub>2</sub> is predetermined to a constant time interval (for example, 40 msec) in which time interval

45 shown as having unstable movement of the

(for example, 40 msec) in which time interval the maximum value of the input signal will appear beyond the time point t<sub>1</sub>.

When the electronic switching circuit 17 is in an OFF state (between the time points t<sub>1</sub> and t<sub>2</sub>), the FET 15 is in a non-conductive state, and the signal which has undergone reverse polarity wave detection, of the output 65 signals of the operational amplifier 14 which

has passed through the diode *D*, is charged in the capacitor *C*. The terminal voltage of the capacitor *C* is obtained from the FET 15 of a source-follower, and then applied to the in-

70 verting terminal of the operational amplifier

14. As a result, the reverse polarity peak

value of the input signal is held in the capacitor C, during the time interval between the

time points t<sub>1</sub> and t<sub>2</sub>. The waveform of the

75 source output of the FET 15 is shown in Fig.

2(B).

The source output signal of the FET 15 is

compared with the ground level at the operational amplifier 18. During the time interval 80 between the time points t<sub>1</sub> and t<sub>2</sub>, the source output of the FET 15 is negative, and thus the output signal obtained from the operational amplifier 18 through an output terminal 19 is of a negative saturated value — Vcc, as

85 shown in Fig. 2(E).

Furthermore, even when the contact between the magnetic tape and magnetic head is unstable and there exist fluctuation in the input signal as shown in Fig. 2(A), the capaci-90 tor C keeps holding the peak value by the above constructed peak holding circuit, and the terminal voltage of the capacitor C obtained from the source terminal of the FET 15 is always a voltage corresponding to the maximum value of the input signal level to that particular point in time, as shown in Fig. 2(B). Accordingly, the maximum peak value of the input signal can constantly be detected, with-

Next, at a time point t<sub>2</sub> after a specific time lapse from the time point t<sub>1</sub>, the switch of the electronic switching circuit 12 is changed over to the contact a side as shown in Fig. 2(C), by 105 the control signal applied from the microcomputer through the terminal 13a. Therefore, the supply of the input signal to the operational amplifier 14 is interrupted, and a

out being effected by the above level fluctua-

100 tion.

positive voltage + Vcc of the DC voltage 110 source is applied to the non-inverting terminal of the operational amplifier 14 through he electronic switching circuit 12. Hence, the diode D is turned OFF, and the input signal peak value detection operation is stopped.

At the time point t<sub>2</sub>, the electronic switching circuit 17 becomes ON as shown in Fig. 2(D), by the control signal applied from the microcomputer through the terminal 13b. Therefore, the constant current from the constant

120 current source 16 flows through the capacitor C through the electronic switching circuit 17, and the charged electric charge in the capacitor C is discharged under constant current discharge.

125 By the constant current discharge of the capacitor *C* after the time point t<sub>2</sub>, the terminal voltage of the capacitor *C* rises, and the output voltage of the source terminal of the FET 15 also rises as shown in Fig. 2(B). The 130 output voltage of the source terminal of the

FET 15 is constantly applied to the noninverting terminal of the operational amplifier 18.

The operational amplifier 18 having its inverting terminal grounded operates as a zerocross detector, and the moment (a time point t<sub>3</sub>) the output voltage of the source terminal of the FET 15 rises above the ground level (zero volt), the output signal of the operational amplifier 18 reverses to a positive saturated voltage + Vcc, as shown in Fig. 2(E). The output signal of the above operational amplifier 18 is supplied to the micro-computer from the output terminal 19. The micro-computer measures a time interval *T* between the time points t<sub>2</sub> and t<sub>3</sub>.

The time interval *T* for the terminal voltage of the capacitor *C* to reach a specific voltage (ground level in this case), from the constant 20 current discharge starting time point t<sub>2</sub> to the time point t<sub>3</sub> to reach the specific voltage, is proportional to the negative peak value charged in the capacitor *C*. Accordingly since the constant current value of the constant current value of the constant current value of the capacitor *C* are previously known, by measuring the time interval *T* by the above micro-computer, the maximum peak value of the input signal between the time points t<sub>1</sub> and t<sub>2</sub> can be accurately measured and detected.

The detection circuit according to the present invention applied to a bias current establishing apparatus of a tape recorder for exam-35 ple, will be briefly described. Preceding the recording of the audio signal on the magnetic tape, the medium frequency range signal and high frequency range signal within the audible frequency domain, are mutually recorded ev-40 ery time period slightly longer than that between the time points t<sub>1</sub> and t<sub>3</sub>, by successively varying the bias current. This signal is then reproduced, by detecting the respective levels of the medium frequency range signal 45 and high frequency range signal during reproduction, and a bias current recorded so that the level of the two become identical by use of the micro-computer, is established. Upon the above level detection, relatively high accu-50 racy is demanded, and thus the detection circuit of the present invention is most suitable for this type of detection. In addition, the detection circuit of the present invention cannot only be applied for level detection upon 55 establishing of the recording bias current, but can also be applied for level detection upon adjusting and setting of the recording equalizer, upon recording and/or reproducing sen-

sitivity, and the like.

Further, this invention is not limited to these embodiments but various variations and modifications may be made without departing from the scope of the invention.

A level detection circuit comprising:

a peak value detection and holding circuit

having a capacitor which detects and holds

the peak value of an input signal by charging

said capacitor;

operation control means for supplying said input signal to said peak value detection and holding circuit during a specific time interval to perform maximum value detection and 75 holding operation;

a discharge circuit for performing constant current discharge of a charged electric charge in said capacitor of said peak value detection and holding circuit after said specific time 80 interval; and

detection means for detecting the level of said input signal by measuring the time interval between a time point the constant current discharge of said capacitor by said discharge 5 circuit is initiated and a time point the terminal voltage of said capacitor reaches a specific voltage.

A level detection circuit as described in claim 1 in which said peak value detection

and holding circuit comprises an operational amplifier supplied with said input signal to its non-inverting terminal, a diode connected in reverse polarity to an output side of said operational amplifier, a transistor element connected to said diode and having its output side connected to an inverting terminal of said operational amplifier, and a capacitor connected between ground and a connection point between said diode and said transistor

diode and said transistor

A level detection circuit as described in claim 2, in which said discharge circuit comprises a constant current source connected between a positive voltage terminal of an 105 voltage source and the connection point between said diode and said transistor element, and a first switching circuit connected in series with said constant current source, said first switching circuit being open for a specific 110 time interval and closed after lapse of said specific time interval.

4. A level detection circuit as described in claim 3 in which said operation control means comprises a second switching circuit con-

115 nected to the non-inverting input terminal of said operational amplifier, and means for opening said first switching circuit for said specific time interval and controlling the connection state of said second switching circuit 120 so that said input signal is led to said opera-

tional amplifier.

5. A level detection circuit as described in claim 2 in which said detection means comprises a second operational amplifier having

125 its non-inverting input terminal connected to the output side of said transistor element, its inverting input terminal connected to ground, said second operational amplifier reversing the output polarity when the applied voltage to 130 said non-inverting input terminal reaches

ground level, and means for measuring the time interval between the constant current discharge initiation time point and the time point when the output of said second operational amplifier reverses its polarity.

6. A level detection circuit substantially as described with reference to the accompanying drawings.

Printed for Her Majesty's Stationery Office by Burgess & Son (Abingdon) Ltd.—1981. Published at The Patent Office, 25 Southampton Buildings, London, WC2A 1AY, from which copies may be obtained.