심사관 :

석상문

# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) Int. Cl.

**G11C 8/00** (2006.01)

(21) 출원번호 10-2006-0129582

(22) 출원일자 **2006년12월18일** 심사청구일자 **2006년12월18일**

(65) 공개번호 **10-2008-0056544**

(43) 공개일자 **2008년06월23일**

(56) 선행기술조사문헌 KR1020040091975 A KR1020040095965 A

전체 청구항 수 : 총 20 항

(45) 공고일자 2008년09월09일

(11) 등록번호 10-0857429

(24) 등록일자 2008년09월02일

(73) 특허권자

#### 주식회사 하이닉스반도체

경기 이천시 부발읍 아미리 산136-1

(72) 발명자

#### 심석보

서울 서초구 서초동 1359-1 현대리츠빌 101동 50 2호

(74) 대리인

김성남

#### (54) 반도체 메모리 장치의 지연 고정 루프 회로

## (57) 요 약

본 발명은 내부 클럭의 듀티 싸이클을 보정하여 출력하는 듀티 싸이클 보정수단, 외부 클럭의 클럭 펄스폭을 검출하여 펄스폭 검출신호를 출력하는 클럭 펄스폭 검출수단, 및 상기 듀티 싸이클 보정수단의 출력의 위상을 분리하고, 상기 펄스폭 검출신호에 상응하도록 상기 위상 분리된 두 신호 중 적어도 하나의 펄스폭을 조절하여 지연고정 루프 클럭으로서 출력하는 드라이빙 수단을 구비한다.

#### 대표도

#### 특허청구의 범위

#### 청구항 1

내부 클럭의 듀티 싸이클을 보정하여 출력하는 듀티 싸이클 보정수단;

외부 클럭의 클럭 펄스폭을 검출하여 펄스폭 검출신호를 출력하는 클럭 펄스폭 검출수단; 및

상기 듀티 싸이클 보정수단의 출력의 위상을 분리하고, 상기 펼스폭 검출신호에 상응하도록 상기 위상 분리된 두 신호 중 적어도 하나의 펄스폭을 조절하여 지연 고정 루프 클럭으로서 출력하는 드라이빙 수단을 구비하는 반도체 메모리 장치의 지연 고정 루프 회로.

#### 청구항 2

제 1 항에 있어서,

상기 클럭 펄스폭 검출수단은

상기 외부 클럭의 주파수를 분할하는 분주부,

상기 분주부의 출력을 지연시키는 지연부,

상기 분주부의 출력과 상기 지연부의 출력을 입력 받는 제 1 논리회로, 및

상기 제 1 논리회로의 출력을 입력받아 상기 펄스폭 검출신호를 출력하는 래치를 구비하는 것을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

#### 청구항 3

제 2 항에 있어서,

상기 제 1 논리회로는 논리곱 연산을 수행하도록 구성됨을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

#### 청구항 4

제 2 항에 있어서,

상기 래치는

제 1 입력단에 전원이 인가되고 출력단을 통해 상기 펄스폭 검출신호를 출력하는 제 1 논리소자,

상기 제 1 논리회로의 출력을 입력받는 반전소자, 및

제 1 입력단에 상기 제 1 논리소자의 출력을 입력받고 제 2 입력단에 상기 반전소자의 출력을 입력받으며 출력 단이 상기 제 1 논리소자의 제 2 입력단과 연결된 제 2 논리소자를 구비하는 것을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

#### 청구항 5

제 1 항에 있어서,

상기 드라이빙 수단은

상기 듀티 싸이클 보정부의 출력을 제 1 및 제 2 위상 신호로 분리하여 출력하는 위상 분리부, 및

상기 제 1 및 제 2 위상 신호 중 적어도 하나의 펄스폭을 상기 펄스폭 검출신호에 따라 조절하여 출력하는 펄스폭 조절부를 구비하는 것을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

#### 청구항 6

제 5 항에 있어서,

상기 펄스폭 조절부는

상기 제 1 위상 신호의 펄스폭을 상기 펄스폭 검출신호에 해당하는 폭만큼 감소시켜 출력하는 제 1 펄스폭 조절부, 및

상기 제 2 위상 신호의 펄스폭을 상기 펄스폭 검출신호에 해당하는 폭만큼 감소시켜 출력하는 제 2 펄스폭 조절 부를 구비하는 것을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

## 청구항 7

제 6 항에 있어서,

상기 제 1 펄스폭 조절부는

상기 제 1 위상 신호를 상기 펄스폭 검출신호에 상응하는 시간만큼 지연시켜 출력하는 가변 지연부,

상기 제 1 위상 신호와 상기 가변 지연부의 출력을 연산하는 논리소자, 및

상기 논리소자의 출력과 상기 제 1 위상신호를 연산하는 제 2 논리회로를 구비하는 것을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

#### 청구항 8

제 7 항에 있어서,

상기 가변 지연부는

상기 펄스폭 검출신호에 따라 상기 제 1 위상 신호를 통과시키는 복수개의 스위칭 소자,

상기 복수개의 스위칭 소자의 출력을 서로 다른 시간만큼 지연시키는 복수개의 지연소자, 및

상기 복수개의 지연소자의 출력을 연산하는 제 3 논리회로를 구비하는 것을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

## 청구항 9

제 8 항에 있어서,

상기 복수개의 스위칭 소자는 패스 게이트인 것을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

#### 청구항 10

제 8 항에 있어서,

상기 제 3 논리회로는 상기 복수개의 지연소자의 출력을 논리합하도록 구성됨을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

#### 청구항 11

제 7 항에 있어서,

상기 제 2 논리회로는 상기 논리소자의 출력과 상기 제 1 위상신호를 논리곱하도록 구성됨을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

#### 청구항 12

제 6 항에 있어서,

상기 제 2 펄스폭 조절부는 상기 제 1 펄스폭 조절부와 동일하게 구성됨을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

#### 청구항 13

제 5 항에 있어서,

상기 펄스폭 조절부의 출력과 상기 위상 분리부의 출력을 드라이빙하기 위한 제 1 및 제 2 드라이버를 더 구비하는 것을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

#### 청구항 14

내부 클럭의 듀티 싸이클을 보정하여 출력하는 듀티 싸이클 보정수단; 및

상기 듀티 싸이클 보정부의 출력의 위상을 분리하고, 상기 위상 분리된 두 신호 중 적어도 하나의 펄스폭을 조절하여 지연 고정 루프 클럭으로 출력하는 드라이빙 수단을 구비하는 반도체 메모리 장치의 지연 고정 루프 회로.

#### 청구항 15

제 14 항에 있어서,

상기 드라이빙 수단은

상기 듀티 싸이클 보정부의 출력을 제 1 및 제 2 위상 신호로 분리하여 출력하는 위상 분리부, 및

상기 제 1 및 제 2 위상 신호 중 적어도 하나의 펄스폭을 조절하여 출력하는 펄스폭 조절부를 구비하는 것을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

## 청구항 16

제 15 항에 있어서,

상기 펄스폭 조절부는

상기 제 1 위상 신호의 펄스폭을 원래의 펄스폭에 비해 감소시켜 출력하는 제 1 펄스폭 조절부, 및

상기 제 2 위상 신호의 펄스폭을 원래의 펄스폭에 비해 감소시켜 출력하는 제 2 펄스폭 조절부를 구비하는 것을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

#### 청구항 17

제 16 항에 있어서,

상기 제 1 펄스폭 조절부는

상기 제 1 위상 신호를 정해진 시간만큼 지연시켜 출력하는 지연부,

상기 제 1 위상 신호와 상기 지연부의 출력을 연산하는 논리소자, 및

상기 논리소자의 출력과 상기 제 1 위상신호를 연산하는 제 4 논리회로를 구비하는 것을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

## 청구항 18

제 17 항에 있어서,

상기 제 4 논리회로는 상기 논리소자의 출력과 상기 제 1 위상신호를 논리곱하도록 구성됨을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

#### 청구항 19

제 16 항에 있어서,

상기 제 1 펄스폭 조절부는 상기 제 2 펄스폭 조절부와 동일하게 구성됨을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

#### 청구항 20

제 15 항에 있어서,

상기 펄스폭 조절부의 출력과 상기 위상 분리부의 출력을 드라이빙하기 위한 제 1 및 제 2 드라이버를 더 구비

하는 것을 특징으로 하는 반도체 메모리 장치의 지연 고정 루프 회로.

### 명세서

#### 발명의 상세한 설명

#### 발명의 목적

### 발명이 속하는 기술 및 그 분야의 종래기술

- <19> 본 발명은 반도체 메모리 장치에 관한 것으로서, 특히 지연 고정 루프 클럭의 전송경로에 기인하여 발생되는 오 류를 해결하기 위한 반도체 메모리 장치의 지연 고정 루프 회로에 관한 것이다.

- <20> 지연 고정 루프(Delay Locked Loop: DLL) 회로는 반도체 메모리 장치 외부에서 공급되는 외부 클럭(CLK)과 반도 체 메모리 장치 내부에서 사용되는 내부 클럭(iclk)의 위상을 동기시키기 위한 지연 고정 루프 클럭(RCLKDLL, FCLKDLL)을 생성하는 회로이다.

- <21> 상기 지연 고정 루프 클럭(RCLKDLL)은 상기 외부 클럭(CLK)의 라이징 엣지(Rising Edge)에 동기된 클럭이며, 상기 지연 고정 루프 클럭(FCLKDLL)은 상기 외부 클럭(CLK)의 폴링 엣지(Falling Edge)에 동기된 클럭이다.

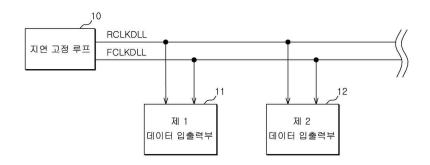

- <22> 도 1에 도시된 바와 같이, 상기 반도체 메모리 장치의 지연 고정 루프 회로(10)에서 출력된 지연 고정 루프 클럭(RCLKDLL, FCLKDLL)은 신호라인을 통과하여 제 1 데이터 입출력부(11) 및 제 2 데이터 입출력부(12)에 공급된다.

- <23> 상기 제 1 및 제 2 데이터 입출력부(11, 12)는 상기 지연 고정 루프 클럭(RCLKDLL, FCLKDLL)을 이용하여 전체 입출력 데이터를 반으로 나누어 처리하기 위한 구성이다. 예를 들어, 한 번의 입력 또는 출력 명령에 따라 출력 되는 전체 데이터가 16 비트라면 제 1 데이터 입출력부(11)가 0 ~ 7번에 해당하는 8개의 데이터를 처리하고, 나 머지 데이터를 제 2 데이터 입출력부(12)에서 처리한다.

- <24> 반도체 메모리 장치가 더욱 고속화되고 데이터 처리량이 증가함에 따라 원활한 데이터 입출력을 위해 상기와 같이 데이터 입출력부를 복수개로 사용하는 방식이 많이 사용되고 있다.

- <25> 상기 제 1 및 제 2 데이터 입출력부(11, 12)는 지연 고정 루프 클럭(RCLKDLL, FCLKDLL)의 스큐(Skew)를 고려하여 상기 tAC(클럭으로부터 데이터를 억세스하는데 소요되는 시간)와 카스 레이턴시(Column Access Strobe Latency)에 맞도록 상기 지연 고정 루프 클럭(RCLKDLL, FCLKDLL)에 대한 지연 및 타이밍 조정을 수행한다.

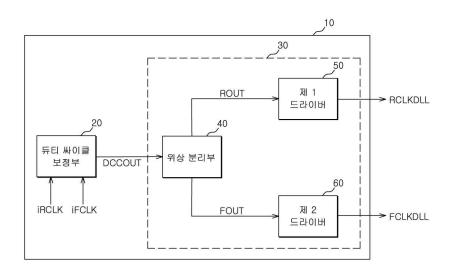

- <26> 종래의 기술에 따른 지연 고정 루프 회로(10)는 도 2에 도시된 바와 같이, 듀티 싸이클 보정부(20), 및 지연 고 정 루프 클럭 드라이버(30)를 구비한다.

- <27> 상기 지연 고정 루프 클럭 드라이버(30)는 위상 분리부(40), 제 1 드라이버(50), 및 제 2 드라이버(60)를 구비한다.

- <28> 이와 같이 구성된 종래 기술에 따른 지연 고정 루프 회로의 동작을 설명하면 다음과 같다.

- <29> 상기 듀티 싸이클 보정부(20)가 지연 고정 루프(10) 내부의 지연 루프(도시 생략)를 통해 지연 고정된 내부 클릭(iRCLK, iFCLK)의 듀티 싸이클을 보정하여 출력한다.

- <30> 상기 지연 고정 루프 클럭 드라이버(30)의 위상 분리부(40)가 상기 듀티 싸이클 보정부(20)의 출력(DCCOUT)의 위상을 분리하여 ROUT와 FOUT를 출력한다.

- <31> 상기 지연 고정 루프 클럭 드라이버(30)의 제 1 드라이버(50)가 상기 ROUT를 상기 RCLKDLL로 드라이빙하여 지연 고정 루프(10) 외부의 신호라인으로 출력하고, 상기 제 2 드라이버(60)가 상기 FOUT를 상기 FCLKDLL로 드라이빙 하여 지연 고정 루프(10) 외부의 신호라인으로 출력한다.

- <32> 종래의 기술에 따른 반도체 메모리 장치는 상기 지연 고정 루프 클럭(RCLKDLL, FCLKDLL)이 상기 도 1에 도시된 바와 같이 긴 신호라인을 통해 전송되면서 상술한 스큐를 갖게 되는데, 상기 도 1의 제 1 및 제 2 데이터 입출 력부(11, 12)에서 상기 지연 고정 루프 클럭(RCLKDLL, FCLKDLL)의 스큐를 보상하도록 되어 있다.

- <33> 그러나 종래의 기술에 따른 반도체 메모리 장치는 도 1과 같이, 제 1 및 제 2 데이터 입출력부(11, 12)와 연결 된 신호라인이 비대칭하므로 상술한 지연 고정 루프 클럭(RCLKDLL, FCLKDLL)의 스큐 보상이 이루어지지 못함은

물론이며, 오히려 스큐를 더욱 심화시킬 수 있다.

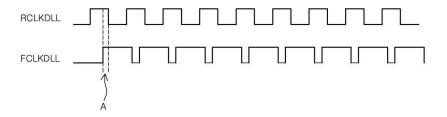

- <34> 이와 같이 종래의 기술에 따른 반도체 메모리 장치는 상술한 지연 고정 루프 클럭(RCLKDLL, FCLKDLL)의 스큐로 인하여 정상적인 경우 중첩되는 구간이 존재해서는 안 되는 RCLKDLL과 FCLKDLL간에 도 3의 A 구간과 같이 중첩되는 구간이 존재하는 타이밍 오류를 유발하게 된다. DDR DRAM(Double Data Rate Dynamic RAM)의 경우 클럭의라이징 엣지와 폴링 엣지 각각의 타이밍에 데이터를 입력받거나 출력하므로 상기와 같이 RCLKDLL과 FCLKDLL간에도 3의 A 구간과 같이 중첩되는 구간이 존재하게 되면 이를 사용하는 데이터 입출력 구성의 오동작으로 인해 심각한 데이터 입출력 오류를 유발할 수 있는 문제점이 있다.

- <35> 또한 상술한 종래기술의 문제는 도 3과 같이, 지연 고정 루프 클릭(RCLKDLL, FCLKDLL)의 하이 레벨 구간의 폭이 달라 발생된 것이다. 따라서 단순히 지연 고정 루프 클릭(RCLKDLL, FCLKDLL) 중 어느 하나를 지연시키는 것 만으로는 상술한 종래의 문제를 해결하기 매우 어려우며, 지연 고정 루프 클릭(RCLKDLL, FCLKDLL)을 지연시키는 것은 상기 제 1 및 제 2 데이터 입출력부에서 tAC 조정을 어렵게 하는 새로운 문제를 발생시킨다.

#### 발명이 이루고자 하는 기술적 과제

<36> 본 발명은 지연 고정 루프 클럭이 전송되는 과정에서 발생되는 타이밍 오류를 미연에 방지할 수 있도록 한 반도 체 메모리 장치의 지연 고정 루프 회로를 제공함에 그 목적이 있다.

#### 발명의 구성 및 작용

- <37> 본 발명에 따른 반도체 메모리 장치의 지연 고정 루프 회로는 내부 클릭의 듀티 싸이클을 보정하여 출력하는 듀티 싸이클 보정수단; 외부 클릭의 클릭 펄스폭을 검출하여 펄스폭 검출신호를 출력하는 클릭 펄스폭 검출수단; 및 상기 듀티 싸이클 보정수단의 출력의 위상을 분리하고, 상기 펄스폭 검출신호에 상응하도록 상기 위상 분리된 두 신호 중 적어도 하나의 펄스폭을 조절하여 지연 고정 루프 클릭으로 출력하는 드라이빙 수단을 구비함을 특징으로 한다.

- <38> 본 발명에 따른 반도체 메모리 장치의 지연 고정 루프 회로는 내부 클럭의 듀티 싸이클을 보정하여 출력하는 듀티 싸이클 보정수단; 및 상기 듀티 싸이클 보정부의 출력의 위상을 분리하고, 상기 위상 분리된 두 신호 중 적어도 하나의 펄스폭을 조절하여 지연 고정 루프 클럭으로 출력하는 드라이빙 수단을 구비함을 또 다른 특징으로한다.

- <39> 이하, 첨부된 도면을 참조하여 본 발명에 따른 반도체 메모리 장치의 지연 고정 루프 회로의 바람직한 실시예를 설명하면 다음과 같다.

#### <40> - 제 1 실시예 -

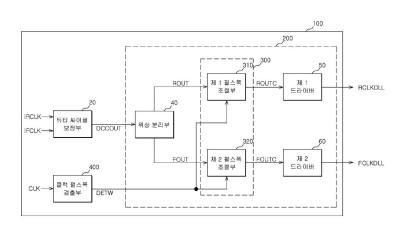

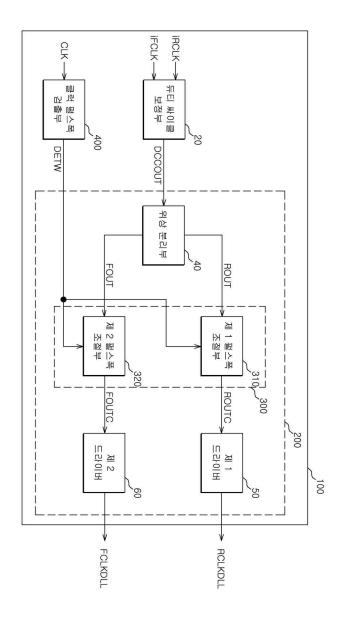

- <41> 본 발명에 따른 반도체 메모리 장치의 지연 고정 루프 회로(100)는 도 4에 도시된 바와 같이, 내부 클릭(iRCLK, iFCLK)의 듀티 싸이클을 보정하여 출력하는 듀티 싸이클 보정부(20), 외부 클릭(CLK)의 클릭 펄스폭을 검출하여 펄스폭 검출신호(DETW)를 출력하는 클릭 펄스폭 검출부(400), 및 상기 듀티 싸이클 보정부(20)의 출력의 위상을 분리하고, 상기 펄스폭 검출신호(DETW)에 상응하도록 상기 위상 분리된 두 신호(ROUT, FOUT) 중 적어도 하나의 펄스폭을 조절하여 지연 고정 루프 클릭(RCLKDLL, FCLKDLL)으로 출력하는 지연 고정 루프 클릭 드라이버(200)를 구비한다.

- <42> 상기 지연 고정 루프 클럭 드라이버(200)는 상기 듀티 싸이클 보정부(20)의 출력을 제 1 및 제 2 위상 신호 (ROUT, FOUT)로 분리하여 출력하는 위상 분리부(40), 상기 제 1 및 제 2 위상 신호(ROUT, FOUT) 중 적어도 하나의 펄스폭을 상기 펄스폭 검출신호(DETW)에 따라 조절하여 출력하는 펄스폭 조절부(300), 및 상기 펄스폭 조절부(300)의 출력을 드라이빙하기 위한 제 1 및 제 2 드라이버(50, 60)를 구비한다. 상기 펄스폭 조절부(300)가 상기 제 1 위상신호(ROUT)의 펄스폭을 조절하는 경우, 도 4의 제 2 펄스폭 조절부(320)가 삭제되고 제 2 위상신호(FOUT)가 직접 제 2 드라이버(60)에 인가된다. 한편, 상기 펄스폭 조절부(300)가 상기 제 2 위상신호(FOUT)의 펄스폭을 조절하는 경우, 도 4의 제 1 펄스폭 조절부(310)가 삭제되고 제 1 위상신호(ROUT)가 직접 제 1 드라이버(50)에 인가된다.

- <43> 상기 펄스폭 조절부(300)가 상기 제 1 및 제 2 위상신호(ROUT, FOUT)의 펄스폭을 조절하는 경우, 그 구성은 도 4에 도시된 바와 같이, 상기 제 1 위상 신호(ROUT)의 펄스폭을 상기 펄스폭 검출신호(DETW)에 해당하는 폭만큼 감소시켜 출력하는 제 1 펄스폭 조절부(310), 및 상기 제 2 위상 신호(FOUT)의 펄스폭을 상기 펄스폭 검출신호 (DETW)에 해당하는 폭만큼 감소시켜 출력하는 제 2 펄스폭 조절부(320)를 구비한다.

- <44> 상기 제 1 펄스폭 조절부(310)는 도 5에 도시된 바와 같이, 상기 제 1 위상 신호(ROUT)를 상기 펄스폭 검출신호 (DETW)에 상응하는 시간만큼 지연시켜 출력하는 가변 지연부(311), 상기 제 1 위상 신호(ROUT)와 상기 가변 지연부(311)의 출력을 연산하는 제 1 낸드 게이트(ND31), 및 상기 제 1 낸드 게이트(ND31)의 출력과 상기 제 1 위 상신호(ROUT)를 논리곱 연산하는 제 2 낸드 게이트(ND32)와 인버터(IV31)를 구비한다.

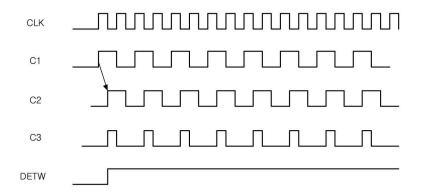

- <45> 상기 가변 지연부(311)는 도 6에 도시된 바와 같이, 상기 펄스폭 검출신호(DETW)를 입력받는 제 1 인버터 (IV41), 상기 펄스폭 검출신호(DETW)와 상기 제 1 인버터(IV41)의 출력에 따라 상기 제 1 위상 신호(ROUT)를 통과시키는 제 1 패스 게이트(PG41), 상기 제 1 인버터(IV41)의 출력과 상기 펄스폭 검출신호(DETW)에 따라 상기 제 2 위상 신호(FOUT)를 통과시키는 제 2 패스 게이트(PG42), 상기 제 1 패스 게이트(PG41)의 출력을 제 1 지연시간 만큼 지연시켜 출력하는 제 1 딜레이(312), 상기 제 2 패스 게이트(PG42)의 출력을 제 2 지연시간 만큼 지연시켜 출력하는 제 2 딜레이(313) 및 상기 제 1 및 제 2 패스 게이트(PG41, PG42)의 출력을 논리합 연산하는 노아 게이트(NR41)와 제 2 인버터(IV42)를 구비한다. 상기 제 1 딜레이(312)에 비해 제 2 딜레이(313)의 지연시간이 더 크게 설정된다.

- <46> 상기 도 4의 제 2 펄스폭 조절부(320)는 상기 제 1 펄스폭 조절부(310)와 동일하게 구성된다.

- <47> 상기 클럭 펄스폭 검출부(400)는 도 7에 도시된 바와 같이, 상기 외부 클럭(CLK)의 주파수를 분할하는 분주부 (410), 상기 분주부(410)의 출력을 지연시키는 지연부(420), 상기 분주부(410)의 출력과 상기 지연부(420)의 출 력을 입력 받는 제 1 낸드 게이트(ND51), 상기 제 1 낸드 게이트(ND51)의 출력을 입력받는 제 1 인버터(IV51), 상기 제 1 인버터(IV51)의 출력을 입력받는 래치(430)를 구비한다. 상기 클럭 펄스폭 검출부(400)는 분주부 (410)가 외부 클럭(CLK)의 주파수를 소정 배율(예를 들어, 1/2)로 나누어 출력한다. 상기 지연부(420)는 상기 분주부(410)의 출력을 정해진 시간만큼 지연시켜 출력한다. 상기 제 1 낸드 게이트(ND51)와 제 1 인버터(IV51) 가 상기 분주부(410)의 출력과 상기 지연부(420)의 출력을 논리곱 연산하여 그 연산결과를 출력한다. 상기 래치 (430)는 제 1 입력단에 전원(VDD)이 인가되고 출력단을 통해 상기 펄스폭 검출신호(DETW)를 출력하는 제 2 낸드 게이트(ND52), 상기 제 1 인버터(IV51)의 출력을 입력받는 제 2 인버터(IV52), 및 제 1 입력단에 상기 제 2 낸 드 게이트(ND52)의 출력을 입력받고 제 2 입력단에 상기 제 2 인버터(IV52)의 출력을 입력받으며 출력단이 상기 제 2 낸드 게이트(ND52)의 제 2 입력단과 연결된 제 3 낸드 게이트(ND53)를 구비한다. 상기 래치(430)는 초기 동작시부터 상기 제 1 인버터(IV51)의 출력이 로우 레벨인 구간동안 상기 펄스폭 검출신호(DETW)를 로우 레벨로 출력하다가, 상기 제 1 인버터(IV51)의 출력이 하이 레벨로 천이되면 상기 펄스폭 검출신호(DETW)를 하이 레벨 로 출력한다. 예를 들어, 외부 클럭(CLK)의 주파수가 높아 클럭 펄스폭이 좁은 경우 도 8a와 같이, 상기 분주부 (410)의 출력(C1)과 상기 지연부(420)의 출력(C2)을 논리곱하면 제 1 인버터(IV51)의 출력(C3)은 로우 레벨을 유지하므로 래치(430)를 통해 펄스폭 검출신호(DETW)가 로우 레벨로 출력된다. 따라서 펄스폭 검출신호(DETW)가 로우 레벨인 경우 클럭 펄스폭이 좁은 것을 검출할 수 있다. 한편, 외부 클럭(CLK)의 주파수가 낮아 클럭 펄스 폭이 넓은 경우 도 8b와 같이. 상기 분주부(410)의 출력(C1)과 상기 지연부(420)의 출력(C2)을 논리곱하면 제 1 인버터(IV51)의 출력(C3)은 하이 레벨 구간이 반복되는 펄스 형태를 나타내므로 래치(430)를 통해 펄스폭 검출 신호(DETW)가 하이 레벨로 출력된다. 따라서 펄스폭 검출신호(DETW)가 하이 레벨인 경우 클릭 펄스폭이 넓은 것 을 검출할 수 있다.

- <48> 이와 같이 구성된 본 발명의 제 1 실시예에 따른 반도체 메모리 장치의 지연 고정 루프 회로의 동작을 설명하면 다음과 같다.

- <49> 상기 듀티 싸이클 보정부(20)가 내부 클럭(iRCLK, iFCLK)의 듀티 싸이클을 보정하여 DCDCOUT를 출력한다.

- <50> 상기 클럭 펄스폭 검출부(400)가 도 8a 및 도 8b와 같이 외부 클럭(CLK)의 펄스폭에 따른 펄스폭 검출신호 (DETW)를 출력한다.

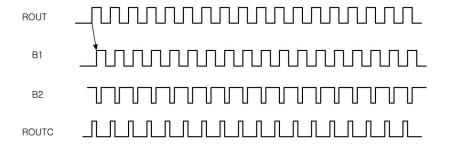

- <51> 상기 위상 분리부(40)가 상기 DCDCOUT의 위상을 분리하여 제 1 및 제 2 위상 신호(ROUT, FOUT)를 출력한다.

- <52> 상기 필스폭 조절부(300)가 상기 필스폭 검출신호(DETW)에 따라 제 1 및 제 2 위상 신호(ROUT, FOUT)의 필스폭을 조절하여 출력한다.

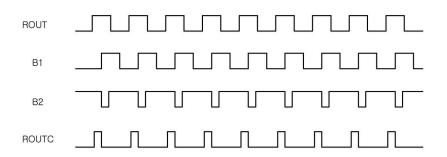

- <53> 상기 제 1 및 제 2 펄스폭 조절부(310, 320)의 펄스폭 조절동작은 동일하므로 제 1 펄스폭 조절부(310)의 동작을 설명하면 다음과 같다. 상기 도 6의 가변 지연부(311)는 상기 펄스폭 검출신호(DETW)가 하이 레벨인 경우즉, 외부 클럭(CLK)의 주파수가 낮아 외부 클럭(CLK)의 펄스폭이 넓은 경우 도 9a와 같이 상기 제 1 위상신호(ROUT)를 제 2 패스 게이트(PG42)를 통해 제 2 딜레이(313)로 입력시키므로 상기 제 1 위상신호(ROUT)가 상기제 1 딜레이(312)의 지연시간에 비해 긴 제 2 딜레이(313)의 지연시간 만큼 지연되고, 노아 게이트(NR41)와 인

버터(IV42)를 통해 B1이 출력된다. 상기 도 5의 제 1 낸드 게이트(ND31)가 상기 가변 지연부(311)의 출력 B1과 상기 제 1 위상신호(ROUT)를 연산하여 B2를 출력한다. 상기 제 2 낸드 게이트(ND32)와 인버터(IV31)가 상기 B2와 상기 제 1 위상신호(ROUT)를 논리곱하여 상기 제 1 위상신호(ROUT)의 펄스폭을 상기 제 2 딜레이(313)의 지연시간 만큼 감소시켜 생성한 ROUTC를 출력한다.

- <54> 한편, 상기 도 6의 가변 지연부(311)는 상기 펄스폭 검출신호(DETW)가 로우 레벨인 경우 즉, 외부 클럭(CLK)의 주파수가 높아 외부 클럭(CLK)의 펄스폭이 좁은 경우 도 9b와 같이 상기 제 1 위상신호(ROUT)를 제 1 패스 게이트(PG41)를 통해 제 1 딜레이(312)로 입력시키므로 상기 제 1 위상신호(ROUT)가 상기 제 1 딜레이(312)의 지연시간 만큼 지연되고, 노아 게이트(NR41)와 인버터(IV42)를 통해 B1이 출력된다. 상기 도 5의 제 1 낸드 게이트(ND31)가 상기 가변 지연부(311)의 출력 B1과 상기 제 1 위상신호(ROUT)를 연산하여 B2를 출력한다. 상기 제 2 낸드 게이트(ND32)와 인버터(IV31)가 상기 B2와 상기 제 1 위상신호(ROUT)를 논리곱하여 상기 제 1 위상신호(ROUT)의 펄스폭을 상기 제 1 딜레이(312)의 지연시간 만큼 감소시켜 생성한 ROUTC를 출력한다.

- <55> 결국, 제 1 펄스폭 조절부(310) 및 제 2 펄스폭 조절부(320)는 외부 클럭(CLK)의 펄스폭을 검출하여 펄스폭 조절량을 달리 함으로써, 외부 클럭(CLK)의 펄스폭이 달라지더라도 ROUTC 및 FOUTC의 펄스폭이 일정하게 되도록 한다.

- <56> 상기 제 1 및 제 2 드라이버(50, 60)는 상기 ROUTC와 FOUTC를 각각 드라이빙하여 지연 고정 루프 클럭(RCLKDLL, FCLKDLL)을 출력한다.

- <57> 상기 출력된 지연 고정 루프 클럭(RCLKDLL, FCLKDLL)은 상기 펄스폭 조절부(300)를 거치지 않고 생성된 경우에 비해, 하이 구간의 폭이 감소되었으며 주파수가 달라짐에 따라 외부 클럭(CLK)의 펄스폭이 가변되더라도 일정하게 유지된다. 따라서 상기 지연 고정 루프 클럭(RCLKDLL, FCLKDLL)이 지연 고정 루프 회로 외부로 출력되어 비대칭 신호라인을 거쳐 스큐가 발생되더라도 서로 중첩되는 구간이 존재하지 않게 된다.

- <58> 제 2 실시예 -

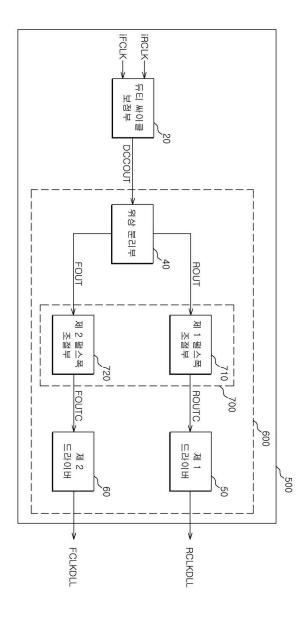

- <59> 본 발명의 제 2 실시예에 따른 반도체 메모리 장치의 지연 고정 루프 회로(500)는 도 10에 도시된 바와 같이, 내부 클럭(iRCLK, iFCLK)의 듀티 싸이클을 보정하여 출력하는 듀티 싸이클 보정부(20), 및 상기 듀티 싸이클 보 정부(20)의 출력의 위상을 분리하고, 상기 위상 분리된 두 신호(ROUT, FOUT) 중 적어도 하나의 펄스폭을 조절하 여 지연 고정 루프 클럭(RCLKDLL, FCLKDLL)으로 출력하는 지연 고정 루프 클럭 드라이버(600)를 구비한다.

- <60> 상기 지연 고정 루프 클럭 드라이버(600)는 상기 듀티 싸이클 보정부(20)의 출력을 제 1 및 제 2 위상 신호 (ROUT, FOUT)로 분리하여 출력하는 위상 분리부(40), 상기 제 1 및 제 2 위상 신호(ROUT, FOUT) 중 적어도 하나의 펄스폭을 조절하여 출력하는 펄스폭 조절부(700), 및 상기 펄스폭 조절부(700)의 출력을 드라이빙하기 위한 제 1 및 제 2 드라이버(50, 60)를 구비한다. 상기 펄스폭 조절부(700)가 상기 제 1 위상신호(ROUT)의 펄스폭을 조절하는 경우, 도 10의 제 2 펄스폭 조절부(720)가 삭제되고 제 2 위상신호(FOUT)가 직접 제 2 드라이버(60)에 인가된다. 한편, 상기 펄스폭 조절부(700)가 상기 제 2 위상신호(FOUT)의 펄스폭을 조절하는 경우, 도 10의 제 1 펄스폭 조절부(710)가 삭제되고 제 1 위상신호(ROUT)가 직접 제 1 드라이버(50)에 인가된다.

- <61> 상기 펄스폭 조절부(700)가 상기 제 1 및 제 2 위상신호(ROUT, FOUT)의 펄스폭을 조절하는 경우, 그 구성은 도 10에 도시된 바와 같이, 상기 제 1 위상 신호(ROUT)의 펄스폭을 정해진 폭만큼 감소시켜 출력하는 제 1 펄스폭 조절부(710), 및 상기 제 2 위상 신호(FOUT)의 펄스폭을 정해진 폭만큼 감소시켜 출력하는 제 2 펄스폭 조절부 (720)를 구비한다.

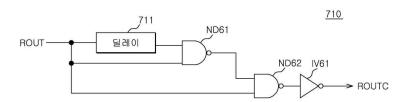

- <62> 상기 제 1 펄스폭 조절부(710)는 도 11에 도시된 바와 같이, 상기 제 1 위상 신호(ROUT)를 정해진 시간만큼 지연시켜 출력하는 딜레이(711), 상기 제 1 위상 신호(ROUT)와 상기 딜레이(711)의 출력을 연산하는 제 1 낸드 게이트(ND61), 및 상기 제 1 낸드 게이트(ND61)의 출력과 상기 제 1 위상신호(ROUT)를 논리곱 연산하는 제 2 낸드 게이트(ND62)와 인버터(IV61)를 구비한다.

- <63> 상기 도 10의 제 2 펄스폭 조절부(720)는 상기 제 1 펄스폭 조절부(710)와 동일하게 구성된다. 단, 제 1 펄스폭 조절부(710)의 딜레이(711)와 제 2 펄스폭 조절부(720)의 딜레이의 지연시간은 회로설계에 따라 동일하거나 다 를 수 있다.

- <64> 이와 같이 구성된 본 발명의 제 2 실시예에 따른 반도체 메모리 장치의 지연 고정 루프 회로의 동작을 설명하면 다음과 같다.

- <65> 상기 듀티 싸이클 보정부(20)가 내부 클럭(iRCLK, iFCLK)의 듀티 싸이클을 보정하여 DCDCOUT를 출력한다.

- <66> 상기 위상 분리부(40)가 상기 DCDCOUT의 위상을 분리하여 제 1 및 제 2 위상 신호(ROUT, FOUT)를 출력한다.

- <67> 상기 펄스폭 조절부(700)가 상기 제 1 및 제 2 위상 신호(ROUT, FOUT)의 펄스폭을 조절하여 출력한다.

- <68> 상기 제 1 및 제 2 펄스폭 조절부(710, 720)의 펄스폭 조절동작은 동일하므로 제 1 펄스폭 조절부(710)의 동작을 설명하면 다음과 같다. 상기 도 11과 같이, 딜레이(711)가 상기 제 1 위상신호(ROUT)를 기설정된 지연시간 만큼 지연시켜 출력한다. 상기 제 1 낸드 게이트(ND61)가 상기 딜레이(711)의 출력과 상기 제 1 위상신호(ROUT)를 연산하여 출력한다. 상기 제 2 낸드 게이트(ND62)와 인버터(IV61)가 상기 제 1 낸드 게이트(ND61)의 출력과 상기 제 1 위상신호(ROUT)를 논리곱하여 상기 제 1 위상신호(ROUT)의 펄스폭을 상기 딜레이(711)의 지연시간 만큼 감소시켜 생성한 ROUTC를 출력한다.

- <69> 결국, 제 1 펄스폭 조절부(310) 및 제 2 펄스폭 조절부(320)는 ROUT 및 FOUT의 펄스폭을 각각 일정량 만큼 감소 시켜 생성한 ROUTC 및 FOUTC출력한다.

- <70> 상기 제 1 및 제 2 드라이버(50, 60)는 상기 ROUTC와 FOUTC를 각각 드라이빙하여 지연 고정 루프 클럭(RCLKDLL, FCLKDLL)을 출력한다.

- <71> 상기 출력된 지연 고정 루프 클럭(RCLKDLL, FCLKDLL)은 상기 펄스폭 조절부(300)를 거치지 않고 생성된 경우에 비해, 하이 구간의 폭이 감소되었다. 따라서 상기 지연 고정 루프 클럭(RCLKDLL, FCLKDLL)이 지연 고정 루프 회로 외부로 출력되어 비대칭 신호라인을 거쳐 스큐가 발생되더라도 서로 중첩되는 구간이 존재하지 않게 된다.

- <72> 본 발명이 속하는 기술분야의 당업자는 본 발명이 그 기술적 사상이나 필수적 특징을 변경하지 않고서 다른 구체적인 형태로 실시될 수 있으므로, 이상에서 기술한 실시예들은 모든 면에서 예시적인 것이며 한정적인 것이 아닌 것으로서 이해해야만 한다. 본 발명의 범위는 상기 상세한 설명보다는 후술하는 특허청구범위에 의하여 나타내어지며, 특허청구범위의 의미 및 범위 그리고 그 등가개념으로부터 도출되는 모든 변경 또는 변형된 형태가 본 발명의 범위에 포함되는 것으로 해석되어야 한다.

#### 발명의 효과

- <73> 본 발명에 따른 반도체 메모리 장치의 지연 고정 루프 회로는 지연 고정 루프 회로 외부로 출력되어 비대칭 신호라인을 거칠 경우를 대비하여 지연 고정 루프 클럭의 필스폭을 조절하여 출력하므로 전송경로 상에 발생될 수있는 지연 고정 루프 클럭의 타이밍 오류 문제를 미연에 방지하여 반도체 메모리 장치의 성능을 향상시킬 수 있는 효과가 있다.

- <74> 또한 본 발명에 따른 반도체 메모리 장치의 지연 고정 루프 회로는 외부 클럭의 필스폭 가변에 대응하여 지연 고정 루프 클럭의 필스폭을 조절하므로 반도체 메모리 장치의 동작 주파수 변동에도 완벽하게 대응할 수 있는 효과가 있다.

### 도면의 간단한 설명

- <!> 도 1은 종래의 기술에 따른 반도체 메모리 장치에서 지연 고정 루프 클럭의 전송경로를 보여주는 블록도,

- <2> 도 2는 종래의 기술에 따른 반도체 메모리 장치의 지연 고정 루프 회로의 블록도,

- <3> 도 3은 종래의 기술에 따른 반도체 메모리 장치의 지연 고정 루프 클럭의 오류 발생을 보여주는 타이밍도,

- <4> 도 4는 본 발명의 제 1 실시예에 따른 반도체 메모리 장치의 지연 고정 루프 회로의 블록도,

- <5> 도 5는 도 4의 제 1 펄스폭 조절부의 회로도,

- <6> 도 6은 도 5의 가변 지연부의 회로도,

- <7> 도 7은 도 4의 클럭 펄스폭 검출부의 회로도,

- <8> 도 8a 및 도 8b는 도 7의 클럭 펄스폭 검출부의 동작 타이밍도,

- <9> 도 9a 및 도 9b는 도 5의 제 1 펄스폭 조절부의 동작 타이밍도,

- <10> 도 10은 본 발명의 제 2 실시예에 따른 반도체 메모리 장치의 지연 고정 루프 회로의 블록도,

<11> 도 11은 도 10의 제 1 펄스폭 조절부의 회로도이다.

<12> < 도면의 주요 부분에 대한 부호의 설명 >

<13> 100, 500: 지연 고정 루프 회로 20: 듀티 싸이클 보정부

<14> 40: 위상 분리부 50: 제 1 드라이버

<15> 60: 제 2 드라이버

<16>

200, 600: 지연 고정 루프 클럭 드라이버

<17> 300, 700: 펄스폭 조절부 710: 제 1 펄스폭 조절부

<18> 320, 720: 제 2 펄스폭 조절부 400: 클럭 펄스폭 검출부

## 도면

## 도면1

# 도면3

## 도면5

# 도면6

## 도면8a

#### 도면8b

## 도면9a

## 도면9b