## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2005-93531 (P2005-93531A)

(43) 公開日 平成17年4月7日 (2005.4.7)

| (51) Int.C1. <sup>7</sup> | F I        |   | テーマコード(参考) |

|---------------------------|------------|---|------------|

| HO1L 21/822               | HO1L 27/04 | C | 5F033      |

| HO1L 21/768               | HO1L 21/90 | Α | 5F038      |

| HO1L 27/04                |            |   |            |

#### 審査請求 有 請求項の数 9 OL (全 11 頁)

|           |                              |                        | THAT IT HAT SAY                   |

|-----------|------------------------------|------------------------|-----------------------------------|

| (21) 出願番号 | 特願2003-321633 (P2003-321633) | (71) 出願人               | 000000295                         |

| (22) 出願日  | 平成15年9月12日 (2003.9.12)       |                        | 沖電気工業株式会社                         |

|           |                              |                        | 東京都港区虎ノ門1丁目7番12号                  |

|           |                              | (71) 出願人               | 591048162                         |

|           |                              |                        | 宮城沖電気株式会社                         |

|           |                              |                        | 宮城県黒川郡大衡村沖の平1番                    |

|           |                              | (74)代理人                |                                   |

|           |                              |                        | 弁理士 佐藤 幸男                         |

|           |                              | (72) 発明者               | 谷島司                               |

|           |                              | ( - / / 2 / 1 -        | 宮城県黒川郡大衡村沖の平1番 宮城沖電               |

|           |                              |                        | 気株式会社内                            |

|           |                              | <br> F <i>ター た (</i> 参 | 考) 5F033 HH09 JJ19 KK09 PP06 PP15 |

|           |                              |                        | QQ08 QQ09 QQ10 QQ11 QQ37          |

|           |                              |                        |                                   |

|           |                              |                        | QQ48 RR04 RR06 RR08 SS11          |

|           |                              |                        | VV10 XX01 XX03                    |

|           |                              | 最終頁に続く                 |                                   |

(54) 【発明の名称】半導体素子の構造とその製造方法

## (57)【要約】

【課題】 垂直構造のキャパシタとすることで、飛躍的な容量の増大と微細化を可能とする。

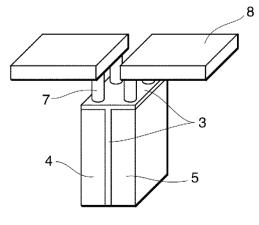

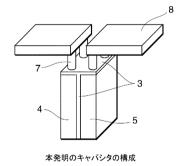

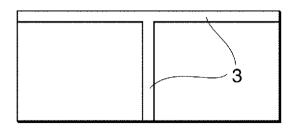

【解決手段】 基板に対し厚く形成された電極材料膜と、当該電極材料膜に対し、その厚さに対して狭く形成された隙間と、当該隙間内に埋め込まれた絶縁膜3とからなる構造をつくり、この構造体から、一組の対向電極4、5を形成して、プラグ7を介して配線8を接続し、キャパシタを構成する。

【選択図】 図1

本発明のキャパシタの構成

#### 【特許請求の範囲】

## 【請求項1】

基板に対して対向面を基板面と垂直にして立てた状態に形成された一組の対向電極と、 当該垂直な一組の対向電極の両対向面間の隙間に埋め込まれた絶縁膜とからなることを 特徴とする半導体素子の構造。

#### 【請求項2】

請求項1に記載の構造上に形成された層間膜と、

当該層間膜を貫通し、前記一組の対向電極にそれぞれ接続されたプラグと、

当該プラグに接続された配線とから成ることを特徴とする請求項1記載の半導体素子の構造。

#### 【請求項3】

前記絶縁膜は、前記一組の対向電極間の隙間に埋め込まれるとともに、前記垂直な一組の対向電極の上面にも形成されることを特徴とする請求項1記載の半導体素子の構造。

#### 【請求項4】

請求項3に記載の構造上に形成された層間膜と、

当該層間膜および前記上部絶縁膜を貫通し、前記一組の対向電極にそれぞれ接続されたプラグと、

当該プラグに接続された配線とから成ることを特徴とする請求項3記載の半導体素子の構造。

#### 【請求項5】

請求項1に記載の構造を、その長手方向に引き延ばし、複数回の折り返しを行って、所定の面積に納めたことを特徴とする請求項1記載の半導体素子の構造。

### 【請求項6】

基板に対して対向面を基板面と垂直にして立てた状態に形成された一組の対向電極と、 当該垂直な一組の対向電極の両対向面間の隙間に埋め込まれるとともに、垂直な一組の 対向電極上面およびそれらの対向電極の外側の側面に形成された絶縁膜とからなることを 特徴とする半導体素子の構造。

#### 【請求項7】

請求項6に記載の構造上に形成された層間膜と、

当該層間膜および前記上部絶縁膜を貫通し、前記一組の対向電極にそれぞれ接続されたプラグと、

当該プラグに接続された配線とから成ることを特徴とする請求項6記載の半導体素子の構造。

## 【請求項8】

基板に対し対向面を基板面と垂直にして一組の対向電極を垂直に立てた場合の高さに相当する厚さに電極材料膜を形成する工程と、

当該電極材料膜に対し、前記垂直な一組の対向電極の対向面の位置に電極板間隔に相当する幅の隙間を形成する工程と、

当該隙間内に絶縁膜を埋め込む工程と、

当該電極材料膜をエッチングして垂直な一組の対向電極を形成する工程とからなることを特徴とする半導体素子の製造方法。

#### 【請求項9】

基板に対し対向面を基板面と垂直にして一組の対向電極を垂直に立てた場合の高さに相当する厚さに電極材料膜を形成する工程と、

当該電極材料膜をエッチングして垂直な一組の対向電極を形成するとともに、当該電極材料膜に対し、前記垂直な一組の対向電極の対向面の位置に電極板間隔に相当する幅の隙間を形成する工程と、

当該隙間内に絶縁膜を埋め込むとともに、垂直な一組の対向電極上面およびそれらの外側の側面に絶縁膜を形成する工程とからなることを特徴とする半導体素子の製造方法。

### 【発明の詳細な説明】

50

40

10

20

#### 【技術分野】

## [0001]

本発明は、RF回路およびアナログ回路で使用されるMIM(金属・絶縁体・金属)キャパシタであって、基板に対し垂直方向の並行平板キャパシタ構造を有する半導体素子の構造とその製造方法に関するものである。

#### 【背景技術】

#### [0002]

近年、携帯電話を始めとする無線通信分野の進歩は目覚ましいものがあるが、さらに、その通信速度の向上および装置の小型化が求められている。このような時代の要請により、そのRF回路用のICの高集積化および低コスト化が求められている。

従来、RF回路用のICとしては、GaAs半導体やバイポーラ技術が用いられていたが、 コストが高く、ベースバンド部等の集積には、適していなかった。

#### [0003]

このような状況下において、近年、CMOSの微細化技術が進歩し、その動作周波数も高くなってきた。このため、CMOSを使ってベースバンド部の集積化を行うことが可能となってきた。

このCMOS技術は、特に、高集積化と低コスト化の面で優れており、これを使って、RF回路部とベースバンド部とをワンチップ化する技術が開発されつつある。

## [0004]

ところが、RF回路をCMOSへ集積させるためには、無線通信を取り扱うRF回路と、人間とのインターフェースを取り扱うアナログ回路とを同一基板に集積する必要がある。そして、このような基板に搭載される受動素子として、キャパシタ、インダクタ、バラクタなどがある。

これらのうち、キャパシタとしては、プロセス上の作りやすさや、電圧依存性の小ささなどの利点から、一般的に、MIM構造が採用される。そして、このMIMキャパシタ構造を微細化する必要がある。

### [0005]

しかしながら、従来の水平な構造のキャパシタ、すなわち、水平な 2 枚の電極板の間に 絶縁膜を挟んだキャパシタ構造では、微細化に限界があった。

ところで、従来のキャパシタとして、DRAMでは、蓄積電極を2重の円筒状にして蓄積容量を増大させたものがある(例えば、特許文献1参照)。

また、従来の他のキャパシタとして、上下の2枚の水平な電極板にそれぞれ内向きの柱を設けて電極の面積を増加させ、蓄積容量を増大させたものがある(例えば、特許文献2参照)。

## [0006]

しかし、これらの従来技術では、2重の円筒および内向きの柱といういずれも補助的な手段を使ったものに過ぎないため、キャパシタの微細化を飛躍的に進歩させることはできないという欠点があった。

### [0007]

【特許文献1】特開平6-77430号公報

【特許文献2】特開2002-299555号公報

#### 【発明の開示】

【発明が解決しようとする課題】

## [0008]

解決しようとする点は、キャパシタの微細化を飛躍的に進歩させる点である。

## 【課題を解決するための手段】

### [0009]

本発明の半導体素子の構造は、基板に対して対向面を基板面と垂直にして立てた状態に形成された一組の対向電極と、当該垂直な一組の対向電極の両対向面間の隙間に埋め込まれた絶縁膜とからなることを最も主要な特徴とする。

10

20

30

40

10

20

30

40

50

#### [0010]

また、本発明の半導体素子の製造方法は、基板に対し対向面を基板面と垂直にして一組の対向電極を垂直に立てた場合の高さに相当する厚さに電極材料膜を形成する工程と、当該電極材料膜に対し、前記垂直な一組の対向電極の対向面の位置に電極板間隔に相当する幅の隙間を形成する工程と、当該隙間内に絶縁膜を埋め込む工程と、当該電極材料膜をエッチングして一組の対向電極を形成する工程とからなることを最も主要な特徴とする。

#### 【発明の効果】

## [0011]

本発明の半導体素子の構造とその製造方法は、MIMキャパシタにおいて、単位面積当たりの容量を増加させることができる。その結果、RF回路の高集積化を図ることができるという利点がある。

【発明を実施するための最良の形態】

#### [0012]

垂直構造のキャパシタを構成するという目的を、通常のリソグラフィーおよびエッチング技術で実現した。

#### 【実施例1】

#### [0013]

図1は、本発明の半導体素子の構造の要部を示す斜視図である。

図示の構造は、垂直に形成されたMIMキャパシタ構造である。この構造において、3が絶縁膜、4と5が一組の対向電極である。また、7がプラグで、8が配線である。絶縁膜3は、一組の対向電極4、5の間に垂直に挟み込まれている。これによって、垂直なキャパシタ構造が構成されている。

#### [0014]

一組の対向電極4、5は、基板に対して垂直にして立てた状態に形成されている。

また、当該垂直な一組の対向電極 4 、 5 の両対向面を両側面とするように隙間が形成されている。そして、当該隙間内に絶縁膜 3 が埋め込まれている。

一組の対向電極 4 、 5 と、配線 8 とは、プラグ 7 によって接続されている。この場合、プラグ 7 は、一組の対向電極 4 、 5 の図中上面すなわち垂直に立てられた一組の対向電極 4 、 5 の端の部分に結合されている。この際、この端の部分すなわち一組の対向電極 4 、 5 の図中上面にも、絶縁膜 3 が存在している。

#### [0015]

一組の対向電極 4 、 5 は、図示しない基板に対し厚く(例えば、 1 0 0 0 0 )形成された金属膜を材料として形成される。そして、この金属膜に対しては、その高さに対して狭い幅の隙間を形成してある。そのようにしておいて、その隙間の中に絶縁膜 3 を埋め込んである。

### [0016]

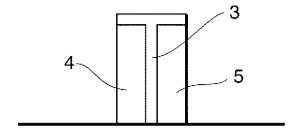

次に、図2ないし図7を参照して上述した図1のキャパシタ構造を形成する方法すなわち本発明の半導体素子の構造の製造方法を説明する。

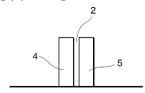

#### [ 0 0 1 7 ]

まず、基板に対し金属膜からなる電極材料膜1を厚く形成する工程を行う(図2)。これにより、基板に対し一組の対向電極4、5を垂直に立てた場合の高さに相当する厚さに電極材料膜1を形成する。これは、図示しない基板に対し、例えば、Ai-Cuをスパッタ法により堆積させることにより行う。具体的な厚さは、例えば、10000 である。

その後、当該電極材料膜1に対し、その高さに対して狭い幅の隙間2を形成する工程を行う(図3)。これにより、当該電極材料膜1に対し、前記垂直な一組の対向電極4、5の対向面の位置に電極板間隔に相当する幅の隙間2を形成する。これは、図示しないレジストを電極材料膜1に塗布し、これをパターニングし、そのパターニングに従って電極材料膜1をドライエッチングすることにより行う。

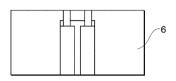

### [0018]

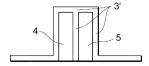

次に、当該隙間2内に絶縁膜3を埋め込む工程を行う(図4)。これは、CVD等によ

10

20

30

40

50

り絶縁膜3を堆積させることにより行う。絶縁膜3の種類は、回路上で必要とされる容量に応じて、酸窒化膜、酸化膜、窒化膜のいずれかを選択する。膜厚は、隙間2の幅に対して埋め込みが可能な厚さとする。

### [0019]

ここで、絶縁膜3は、隙間2内に埋め込まれるとともに、電極材料膜1の上面にも形成される。絶縁膜3は、後に形成される左右の電極を完全に絶縁するために隙間2内に十分に充填させる必要がある。このため、隙間2の開口からあふれるように絶縁膜3を堆積するようにされる。この結果、電極材料膜1の上面にも絶縁膜3が形成される。

しかしながら、この電極材料膜1の上面の絶縁膜3は、キャパシタの端部で漏洩する電界を低減させるのに役立つ。また、後に形成される電極に結合されるプラグ間の絶縁性を良好とするためにも役立つ(図7参照)。

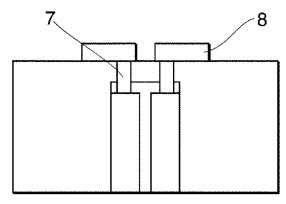

[ 0 0 2 0 ]

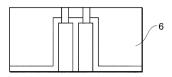

その後、当該電極材料膜1をエッチングして垂直な一組の対向電極4、5を形成する工程を行う(図5)。これは、図示は省略するが、電極材料膜1に塗布したレジストをパターニングし、そのパターニングに従って絶縁膜3と電極材料膜1をエッチングすることにより行う。

#### [0021]

次に、上述のように形成した構造上に層間膜 6 を形成する(図 6 )。これは、 C V D 法により例えば 1 5 0 0 0 堆積させる。そして、 C M P 法により表面を研磨し、平坦化させる。

その後、当該層間膜6および上部の絶縁膜3を貫通し、コンタクトを開口する。

[ 0 0 2 2 ]

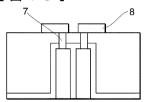

そして、一組の対向電極4、5にプラグ7を接続する(図7)。これは、CVD法によりタングステンを堆積させ、CMP法により全面を研磨することにより行う。

[0023]

最後に、当該プラグ 7 に配線 8 を接続する。すなわち、スパッタ法により AI-Cuを例えば 5 0 0 0 堆積させる。そして、通常のフォトリソグラフィーによりパターニングを行い、ドライエッチングにより配線を形成する。

[0024]

以上のようにして、本発明に係る垂直なMIMキャパシタ構造が完成する。このような構造により、MIMキャパシタにおいて、単位面積当たりの容量を増加させることができる。その結果、RF回路の高集積化を図ることができる。

[0025]

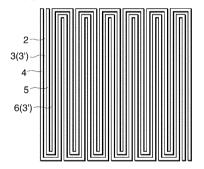

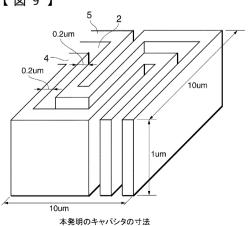

ここで、図を参照して本発明の半導体素子の全体構造を説明する。

図8は、本発明に係るキャパシタの全体構造を示す平面図である。また、図9は、図8の構造の一部分を詳細に示す斜視図である。

図8に示すように、図1のキャパシタ構造が複数回折り返されて所定の面積に納められる。この場合、図3の工程により隙間2が先に形成され、図4の工程でキャパシタ用の所定の誘電率の絶縁膜3が埋め込まれる。その後、図5の工程で一組の対向電極4、5が形成され、図6の工程で層間膜6が埋め込まれる。

[0026]

一組の対向電極 4 、 5 の幅は、 0 . 2  $\mu$ mであり、高さは、1 $\mu$ mである。長さは、約 1 3 0  $\mu$ mである。これを 1 3 回折り返して、図 8 に示すように、 1 0  $\mu$ m× 1 0  $\mu$ mの正方形内に納めている。

よって、キャパシタの電極の総面積は、 1 3 0  $\mu$  m2となる。これは、 1 0  $\mu$  m× 1 0  $\mu$  m の正方形の電極の水平型キャパシタの場合の 1 . 3 倍となる。

さらに、両電極の幅と隙間幅を小さくすることで、容量増加が期待でき、高集積化が可能となる。

[0027]

ところで、一般に、RF回路では、キャパシタの比精度が重要であり、製造ばらつきを

抑えることが望まれる。しかしながら、従来の水平方向のMIMキャパシタでは、絶縁膜の厚さのばらつきが容量のばらつきにつながる。これに対し、本発明に係る垂直方向のキャパシタでは、フォトリソグラフィーおよびエッチングの寸法変換差で容量が決定される。このため、寸法ばらつきが小さく抑えられる。その結果、比精度が向上する。

### 【実施例2】

## [0028]

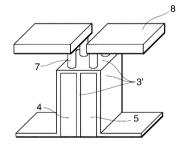

図10は、本発明の半導体素子の他の構造の要部を示す斜視図である。

図示の構造は、垂直に形成されたMIMキャパシタ構造である。この構造において、3'が絶縁膜、4と5が垂直な一組の対向電極である。また、7がプラグで、8が配線である。絶縁膜3'は、一組の対向電極4、5との間に垂直に挟み込まれている。これによって、垂直なキャパシタ構造が構成されている。

#### [0029]

一組の対向電極4、5と、配線8とは、プラグ7によって接続されている。この場合、プラグ7は、一組の対向電極4、5の図中上面すなわち垂直に立てられた一組の対向電極4、5の端の部分に結合されている。この際、この端の部分すなわち一組の対向電極4、5の図中上面にも、絶縁膜3′が存在している。さらに、一組の対向電極4、5の側面にも絶縁膜3′が存在している。

#### [0030]

一組の対向電極 4 、 5 は、図示しない基板に対し厚く(例えば、 1 0 0 0 0 )形成された金属膜を材料として形成される。そして、この金属膜に対しては、その高さに対して狭い幅の隙間を形成してある。そのようにしておいて、その隙間の中に絶縁膜 3 'を埋め込んである。

## [0031]

次に、図11ないし図15を参照して上述した図10のキャパシタ構造を形成する方法すなわち本発明の半導体素子の構造の製造方法を説明する。

#### [0032]

まず、図示しない基板に対し電極材料膜1を厚く形成する工程を行う(図11)。これは、基板に対し、例えば、Ai-Cuをスパッタ法により堆積させることにより行う。具体的な厚さは、例えば、10000 である。

その後、電極材料膜1から一組の対向電極4、5を形成するとともに、当該電極材料膜 1から形成される一組の対向電極4、5の間に、その高さに対して狭い幅の隙間2を形成する工程を行う(図12)。これは、図示は省略するが、レジストを電極材料膜1に塗布し、これをパターニングし、一組の対向電極4、5と、隙間2のパターンをつくる。そして、そのパターニングに従って電極材料膜1をドライエッチングすることにより、これらの形成を行う。

### [0033]

次に、当該隙間 2 内に絶縁膜 3 ′を埋め込む工程を行う(図 1 3 )。これは、 C V D 等により絶縁膜 3 ′を堆積させることにより行う。絶縁膜 3 ′の種類は、回路上で必要とされる容量に応じて、酸窒化膜、酸化膜、窒化膜のいずれかを選択する。膜厚は、隙間の幅に対して埋め込みが可能な厚さとする。例えば、 0 . 2 μmである。

## [ 0 0 3 4 ]

ここで、絶縁膜3 'は、隙間2内に埋め込まれるとともに、一組の対向電極4、5の上面および側面にも形成される。絶縁膜3 'は、左右の電極を完全に絶縁するために隙間2内に十分に充填させる必要がある。このため、隙間2の開口からあふれるように絶縁膜3 'を堆積するようにされる。この結果、一組の対向電極4、5の上面および側面にも絶縁膜3 'が形成される。

しかしながら、この一組の対向電極 4 、 5 の上面および側面の絶縁膜は、キャパシタの端部で漏洩する電界を低減させるのに役立つ。また、後に電極に結合されるプラグ間の絶縁性を良好とするためにも役立つ。

## [0035]

50

40

10

20

次に、上述のように形成した構造上に層間膜 6 を形成する(図 1 4 )。これは、 C V D 法により例えば 1 5 0 0 0 堆積させる。そして、 C M P 法により表面を研磨し、平坦化させる。

その後、当該層間膜6および上部絶縁膜3~を貫通し、コンタクトを開口する。

[0036]

そして、一組の対向電極 4 、 5 にプラグ 7 を接続する(図 1 5 )。これは、 C V D 法によりタングステンを堆積させ、 C M P 法により全面を研磨することにより行う。

[0037]

最後に、当該プラグ7に配線8を接続する。すなわち、スパッタ法によりAI-Cuを例えば5000 堆積させる。そして、通常のフォトリソグラフィーによりパターニングを行い、ドライエッチングにより配線8を形成する。

[0038]

以上のようにして、本発明に係る垂直なMIMキャパシタ構造が完成する。このような構造により、MIMキャパシタにおいて、単位面積当たりの容量を増加させることができる。その結果、RF回路の高集積化を図ることができる。

[0039]

また、実施例2の特有の効果として、電極材料膜1から一組の対向電極4、5と隙間2とを同時に形成することで、2回のフォトリソグラフィーおよびエッチング工程を1回にすることができる。このような工程の簡略化により、製造コストを低減することができる

実施例2でも、図8に示すように、図10のキャパシタ構造が複数回折り返されて所定の面積に納められる。この場合、図12の工程により隙間2、一組の対向電極4、5が同時に形成され、図13の工程でキャパシタ用の所定の誘電率の絶縁膜3′が埋め込まれる

【産業上の利用可能性】

[0040]

小型のMIMキャパシタ構造を、例えば、携帯電話機等のRF回路に適用でき、その小型化に貢献できる。

【図面の簡単な説明】

[0041]

- 【図1】本発明の半導体素子の構造を示した説明図である。(実施例1)

- 【図2】本発明の半導体素子の製造方法の第1工程を示した説明図である。(実施例1)

- 【図3】本発明の半導体素子の製造方法の第2工程を示した説明図である。(実施例1)

- 【図4】本発明の半導体素子の製造方法の第3工程を示した説明図である。(実施例1)

- 【図5】本発明の半導体素子の製造方法の第4工程を示した説明図である。(実施例1)

- 【図6】本発明の半導体素子の製造方法の第5工程を示した説明図である。(実施例1)

- 【図7】本発明の半導体素子の製造方法の第6工程を示した説明図である。(実施例1)

- 【図8】本発明の半導体素子の実体構造を示した説明図である。(実施例1、実施例2も 共通)

- 【 図 9 】 本 発 明 の 半 導 体 素 子 の 実 体 構 造 の 寸 法 を 示 し た 説 明 図 で あ る 。 ( 実 施 例 1 、 実 施 例 2 も 共 通 )

- 【 図 1 0 】 本 発 明 の 半 導 体 素 子 の 他 の 構 造 を 示 し た 説 明 図 で あ る 。 ( 実 施 例 2 )

- 【図11】本発明の半導体素子の他の製造方法の第1工程を示した説明図である。(実施例2)

- 【図12】本発明の半導体素子の他の製造方法の第2工程を示した説明図である。(実施例2)

- 【図13】本発明の半導体素子の他の製造方法の第3工程を示した説明図である。(実施例2)

- 【図14】本発明の半導体素子の他の製造方法の第4工程を示した説明図である。(実施例2)

20

10

30

•

40

【図15】本発明の半導体素子の他の製造方法の第5工程を示した説明図である。(実施例2)

# 【符号の説明】

# [0042]

1 電極材料膜

2隙間3、3、締線膜

4、5 一組の対向電極

6 層間膜 7 プラグ

8 配線

# 【図1】

## 【図2】

本発明のキャパシタの製造工程(その1)

# 【図3】

本発明のキャパシタの製造工程(その2)

# 【図4】

本発明のキャパシタの製造工程(その3)

【図5】

本発明のキャパシタの製造工程(その4)

【図6】

本発明のキャパシタの製造工程(その5)

# 【図7】

本発明のキャパシタの製造工程(その6)

# 【図8】

S=10um×1um×13=130um<sup>2</sup> 本発明のキャパシタの実体構造

## 【図9】

# 【図10】

本発明のキャパシタの他の構成

## 【図11】

本発明のキャパシタの他の製造工程(その1)

## 【図12】

本発明のキャパシタの他の製造工程(その2)

# 【図13】

本発明のキャパシタの他の製造工程(その3)

# 【図14】

本発明のキャパシタの他の製造工程(その4)

# 【図15】

本発明のキャパシタの他の製造工程(その5)

# フロントページの続き

F ターム(参考) 5F038 AC02 AC04 AC05 AC15 AC20 DF02 EZ14 EZ15 EZ20