(19) **日本国特許庁(JP)**

# (12)特 許 公 報(B2)

(11)特許番号

特許第4304198号 (P4304198)

(45) 発行日 平成21年7月29日(2009.7.29)

(24) 登録日 平成21年5月1日(2009.5.1)

(51) Int.Cl. F 1

HO1L 21/338 (2006.01) HO1L 29/812 (2006.01)

HO1L 29/06 (2006.01)

HO1L 29/80 B HO1L 29/06 3O1F

請求項の数 5 (全 6 頁)

(21) 出願番号 特願2006-250516 (P2006-250516)

(22) 出願日 平成18年9月15日 (2006. 9.15) (65) 公開番号 特開2008-71998 (P2008-71998A)

(43) 公開日 平成20年3月27日 (2008.3.27) 審査請求日 平成20年2月4日 (2008.2.4) |(73)特許権者 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

|(74)代理人 110000235

特許業務法人 天城国際特許事務所

|(72)発明者 川崎 久夫

東京都港区芝浦一丁目1番1号 株式会社

東芝内

審査官 村岡 一磨

最終頁に続く

### (54) 【発明の名称】半導体装置

### (57)【特許請求の範囲】

### 【請求項1】

上面に動作層を有する半導体基板と、

この半導体基板の前記動作層の上に設けられたソース電極、ドレイン電極、及びこれらのソース電極とドレイン電極の間に設けられたゲート電極と、このゲート電極と前記ドレイン電極の間に堆積された絶縁膜上に設けられるフィールドプレート電極を備え、

前記ゲート電極は少なくともその一部<u>が</u>前記動作層中に設けられたゲートリセス内で<u>そ</u>の側面部分で絶縁膜に直接接して設けられ、前記フィールドプレート電極は<u>少なくともその一部が</u>、前記ゲート<u>リセス</u>から所定距離離れ<u>て前</u>記動作層に設けられたフィールドプレートリセス内で<u>その側面部分で絶縁膜に直接接して</u>設けられたことを特徴とする半導体装置。

10

### 【請求項2】

前記フィールドプレートリセスの深さは、前記ゲートリセスの深さと略同じことを特徴 とする請求項1記載の半導体装置。

#### 【請求項3】

前記フィールドプレートリセスの深さは、前記ゲートリセスの深さより浅いことを特徴とする請求項 1 記載の半導体装置。

### 【請求項4】

前記ゲート電極は、前記ゲートリセスを覆うように形成されてなることを特徴する請求 項1万至3のいずれか一項に記載の半導体装置。

### 【請求項5】

前記フィールドプレート電極は、前記フィールドプレートリセスを覆うように形成されてなることを特徴する請求項1乃至3のいずれか一項に記載の半導体装置。

【発明の詳細な説明】

【技術分野】

[00001]

本発明は、半導体装置に係わり、特にフィールドプレート電極を有する半導体装置の改良に関する。

【背景技術】

[00002]

10

20

30

40

50

ゲート電極の電界集中を緩和するためにフィールドプレート電極を用いる半導体装置が 最近実用化されている(例えば特許文献 1 参照)。

[0003]

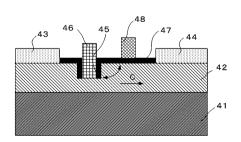

そのような従来の半導体装置一例の構造を図4に示す。同図において、半導体基板41の上に動作層42が形成され、その上にオーム性接触のソース電極43とドレイン電極44が設けられる。ソース電極43とドレイン電極44の間の半導体層にリセス45が設けられ、リセス45内にショットキ接合のゲート電極46と、絶縁物で構成された表面保護膜47上にフィールドプレート電極48がそれぞれ形成されている。

[0.004]

リセス 4 5 内にゲート電極 4 6 を形成するのは、動作層 4 2 の表面に形成される表面準位からゲート電極 4 6 のショットキ接合面を遠ざけ半導体装置を安定に動作させるためである。フィールドプレート電極 4 8 は、ゲート電極 4 6 に電界が集中することを緩和するためであり、半導体装置の高出力化を図る上で重要な役割を果たしている。

[0005]

電界集中緩和の効果を高めるには、ゲート電極 4 6 と動作層 4 2 とのショットキ接合面の近くにフィールドプレート電極 4 8 を配置すること、及びこの電極をチャネル方向に長くすることが望ましい。

[0006]

しかしながら、図4に示すような従来の半導体装置では、ゲート電極46がリセス45内に形成され、フィールドプレート電極48は動作層42の表面に形成され、ゲート電極46とは空間距離的に大きく離れているので、ゲート電極46への電界集中に対して十分な緩和がなされない。更に、フィールドプレート電極48をチャネル方向(C方向)に長くすると、ゲート・ドレイン間の帰還容量が増大するため半導体装置の安定動作が難しくなり、発振を引き起こしてしまうおそれがあった。

[0007]

上述のように、図4に示すような従来のフィールドプレート電極を有する半導体装置は、この電極とゲート電極とが空間距離的に大きく離れているので、ゲート電極における電界集中の緩和に対して十分な効果が得られず安定動作が損なわれる、という問題点があった。

【特許文献 1 】特開 2 0 0 0 - 3 1 5 8 0 4 号公報

【発明の開示】

【発明が解決しようとする課題】

[0008]

本発明は、上記のような従来の問題点にかんがみてなされたもので、ゲート電極への電界集中を十分緩和でき、安定動作をさせることが可能な、フィールドプレート電極を有する半導体装置を提供することを目的とする。

【課題を解決するための手段】

[0009]

本発明の請求項 1 によれば、上面に動作層を有する半導体基板と、この半導体基板の前記動作層の上に設けられたソース電極、ドレイン電極、及びこれらのソース電極とドレイ

ン電極の間に設けられたゲート電極と、このゲート電極と前記ドレイン電極の間に堆積された絶縁膜上に設けられるフィールドプレート電極を備え、前記ゲート電極は少なくともその一部が前記動作層中に設けられたゲートリセス内で<u>その側面部分で絶縁膜に直接接して</u>設けられ、前記フィールドプレート電極は<u>少なくともその一部が</u>、前記ゲート<u>リセス</u>から所定距離離れ<u>て前</u>記動作層に設けられたフィールドプレートリセス内で<u>その側面部分で</u>絶縁膜に直接接して設けられたことを特徴とする半導体装置を提供する。

#### 【発明の効果】

### [0010]

本発明によれば、ゲート電極への電界集中を十分緩和でき、しかも発振を生ずることなく安定動作を可能とする、フィールドプレート電極を有する半導体装置が得られる。

【発明を実施するための最良の形態】

#### [0011]

以下、本発明の実施形態について図面を用いて説明する。

### [0012]

#### < 実施形態 1 >

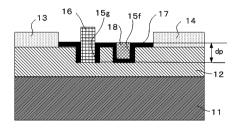

図1に本発明一実施形態の全体構成例を示す。図1に示す半導体装置は、半導体基板11の上に動作層12が形成される。この動作層12の上には、オーム性接触のソース電極13とドレイン電極14が所定距離離して設けられており、両電極の間にゲートリセス15gと、フィールドプレートリセス15fが設けられる。ゲートリセス15gはその少なくとも一部が動作層12中に設けられており、フィールドプレートリセス15fの少なくともその一部が動作層12中に設けられている。フィールドプレートリセス15fは、動作層12中に絶縁物を堆積して設けられる表面保護膜17の上に設けられる。

### [0013]

ゲートリセス 15g 内には、ショットキ接合のゲート電極 16 が形成される。フィールドプレート電極 18 は、フィールドプレートリセス 15f 上の絶縁物により構成された表面保護膜 170 上に形成されている。フィールドプレート電極 18 はゲート電極 16 と接続されており同電位である。表面保護膜 17 としては、例えば膜厚 100 n mの 100 が用いられる。ゲート電極 16 としては例えば 100 以 1

### [0014]

ゲートリセス15gの深さ(底のレベル)とフィールドプレートリセス15fの深さ(表面保護膜17の下面)が同じ(レベルdp)になるように形成すると、ゲート電極16の下端とフィールドプレート電極の下端が最も近い距離となり、ゲート電極の電界集中を緩和するフィールドプレート電極の効果が最も有効となる。また、このようにゲートリセス15gとフィールドプレートリセス15fの深さを同じ程度にする場合、このような半導体装置の製造は最も容易である。

### [0015]

### <実施形態2>

ところで、本発明の上記実施形態では、ゲートリセス15gの深さとフィールドプレートリセス15fの深さを同じ程度にした。フィールドプレートリセス15fの深さをゲートリセス15gの深さより深くすると、チャネルCHにおける寄生抵抗が増大するおそれがあるので、フィールドプレートリセス15fの深さはゲートリセス15gの深さと同じかそれより浅くすることが望ましい。

### [0016]

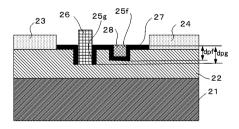

図 2 に、フィールドプレートリセスの深さをゲートリセスの深さより浅くした、本発明の実施形態 2 の半導体装置の構造を示す。図 2 に示す半導体装置は、半導体基板 2 1 の上に動作層 2 2 が形成され、この動作層 2 2 の上には、オーム性接触のソース電極 2 3 とドレイン電極 2 4 が所定距離離して設けられており、両電極の間に、深さdpgのゲートリセス 2 5 gと、深さdpfのフィールドプレートリセス 2 5 fが設けられる。深さdpgと深さdpfは、dpg>dpfの関係にある。

20

10

30

40

50

### [0017]

ゲートリセス 2 5 g内には、ショットキ接合のゲート電極 2 6 が形成される。フィールドプレート電極 2 8 は、フィールドプレートリセス 2 5 f 上の絶縁物により構成された表面保護膜 2 7 の上に形成されている。

### [0018]

この実施形態においては、フィールドプレートリセス15fの深さdpfがゲートリセス15gの深さより浅くなっているので、ゲート電極26への電界集中の緩和の効果は若干落ちるが、ドレイン電極24の抵抗を小さくすることができる効果が得られる。

### [0019]

<実施形態3>

10

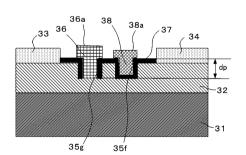

本発明のこの実施形態では、ゲート電極及びフィールドプレート電極の露出する上部が 各リセスを覆うように大きく形成される。

#### [0020]

すなわち、図3に示す半導体装置は、半導体基板31の上に動作層32が形成される。この動作層32の上には、オーム性接触のソース電極33とドレイン電極34が所定距離離して設けられており、両電極の間にゲートリセス35gと、フィールドプレートリセス35fが設けられる。

#### [0021]

ゲートリセス35g内には、ショットキ接合のゲート電極36が形成される。フィールドプレート電極38は、フィールドプレートリセス35f上の絶縁物により構成された表面保護膜37の上に形成されている。ゲート電極36の上部36aはゲートリセス35gを覆うように、その下の部分より大きく形成されており、またフィールドプレート電極38の上部38aもフィールドリセス35fを覆うように、その下の部分より大きく形成されている。

### [0022]

ゲートリセス35gの深さとフィールドプレートリセス35fの深さは同程度とされる

### [0023]

本発明のこの実施形態では、ゲート電極36及びフィールドプレート電極38の両方の上部が各リセスを覆うように大きく形成していた。しかし、ゲート電極36あるいはフィールドプレート電極の一方のみを、リセスを覆うように大きく形成してもよい。

30

20

### [0024]

このようにリセスを覆うように、電極の上部を大きくすると、ゲート電極やフィールド プレート電極の抵抗を小さくすることができ、また製造が容易となる利点がある。

## [0025]

本発明は上記実施形態に限定されるものではなく、本発明の技術思想の範囲内で種々変形して実施可能である。

【図面の簡単な説明】

### [0026]

【図1】本発明の実施形態1による半導体装置の構造を示す図。

40

- 【図2】本発明の実施形態2による半導体装置の構造を示す図。

- 【図3】本発明一実施形態3による半導体装置の構造を示す図。

- 【図4】従来の半導体装置一例の構造を示す図。

### 【符号の説明】

#### [0027]

- 11,21,41・・・半導体基板、

- 12,22,42・・・動作層、

- 13,23,43・・・ソース電極、

- 14,24,44・・・ドレイン電極、

- 15g・・・ゲートリセス、

50

- 15f・・・フィールドプレートリセス、

- 16,26,46・・・ゲート電極、

- 17,27,47・・・表面保護膜、

- 18,28,48・・・フィールドプレート電極、

- 45・・・リセス。

# 【図1】

# 【図2】

# 【図3】

【図4】

## フロントページの続き

(56)参考文献 特開2000-315804(JP,A)

特開2000-003919(JP,A)

特開2003-218130(JP,A)

特開2005-191022(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 21/338

H01L 29/06

H01L 29/812