(19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2007-193867 (P2007-193867A)

(43) 公開日 平成19年8月2日(2007.8.2)

(51) Int.C1.

FI

テーマコード (参考)

G 1 1 C 16/02

(2006, 01)

G11C 17/00 611A G11C 17/00 612C 5B125

審査請求 未請求 請求項の数 30 OL (全 32 頁)

(21) 出願番号 (22) 出願日 特願2006-9216 (P2006-9216)

平成18年1月17日 (2006.1.17)

(71) 出願人 000005821

松下電器産業株式会社

大阪府門真市大字門真1006番地

(74)代理人 100077931

弁理士 前田 弘

(74)代理人 100110939

弁理士 竹内 宏

(74)代理人 100110940

弁理士 嶋田 高久

(74)代理人 100113262

弁理士 竹内 祐二

(74)代理人 100115059

弁理士 今江 克実

弁理士 藤田 篤史

(74)代理人 100115691

最終頁に続く

(54) 【発明の名称】不揮発性半導体記憶装置及びその書き換え方法

# (57)【要約】

【課題】トラップ層を有する不揮発性メモリセルのデータ保持特性の劣化を抑制する。

【解決手段】トラップ層を有する不揮発性メモリセルにおいて、任意の待ち時間を確保した第1の電荷注入12 1と、書き換えシーケンスにおいて、第1の電荷注入後に実施する第2の電荷注入122とを有することにより、書き込み直後の初期変動(ごく短時間での周辺電荷との結合による電荷ロス現象)を利用して、データ保持特性を劣化させる周辺電荷を低減させたうえで、更に初期変動による電荷ロス分を補うことで、その後のデータ保持特性を向上させる。ただし、所定の判定レベルに達している時のみ第2の電荷注入を実施する。

# 【選択図】図1

### 【特許請求の範囲】

# 【請求項1】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施される第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の判定レベルに達している時のみ任意の閾値電圧まで電荷注入を実施することを特徴とする不揮発性半導体記憶装置の書き換え方法。

### 【請求項2】

請求項1記載の不揮発性半導体記憶装置の書き換え方法において、

前記第2の電荷注入ステップを任意の回数実施することを特徴とする不揮発性半導体記憶装置の書き換え方法。

# 【請求項3】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

消去前書き込み時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施される第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施することを特徴とする不揮発性半導体記憶装置の書き換え方法。

#### 【請求項4】

請求項3記載の不揮発性半導体記憶装置の書き換え方法において、

データ書き込み時には、前記消去前書き込み時とは条件を変更して第1の電荷注入と第 2の電荷注入とを実施することを特徴とする不揮発性半導体記憶装置の書き換え方法。

### 【請求項5】

請求項4記載の不揮発性半導体記憶装置の書き換え方法において、

前記消去前書き込み時に前記第1の電荷注入ステップのみを実施することを特徴とする揮発性半導体記憶装置の書き換え方法。

### 【請求項6】

請求項3~5のいずれか1項に記載の不揮発性半導体記憶装置の書き換え方法において

前記消去前書き込み時の第1の電荷注入ステップでは、データ書き込み時以上の書き込みレベルまで電荷注入を実施することを特徴とする不揮発性半導体記憶装置の書き換え方法。

## 【請求項7】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施される第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施し、

前記第1の電荷注入及び前記第2の電荷注入の条件を製造単位により変更することを特徴とする不揮発性半導体記憶装置の書き換え方法。

### 【請求項8】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施される第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意の待ち時間を確保し、

10

20

30

40

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施し、

前記第1の電荷注入ステップ及び前記第2の電荷注入ステップの条件を書き換え単位により変更することを特徴とする不揮発性半導体記憶装置の書き換え方法。

### 【請求項9】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施される第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施し、

前記第1の電荷注入ステップ及び前記第2の電荷注入ステップの条件を検査工程において製造単位で設定することを特徴とする不揮発性半導体記憶装置の書き換え方法。

### 【請求項10】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施される第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施し、

前記第1の電荷注入ステップ及び前記第2の電荷注入ステップの条件を検査工程において書き換え単位で設定することを特徴とする不揮発性半導体記憶装置の書き換え方法。

#### 【請求項11】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施される第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施し、

前記第1の電荷注入ステップ及び前記第2の電荷注入ステップの条件を、それ以前の書き換え時の特性から、書き換え単位で設定することを特徴とする不揮発性半導体記憶装置の書き換え方法。

# 【請求項12】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施される第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施し、

前記待ち時間は、前回のデータ書き込みから書き換えまでの放置時間の長さに応じて変化することを特徴とする不揮発性半導体記憶装置の書き換え方法。

# 【請求項13】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施される第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施し、

前回のデータ書き込みから書き換えまでの放置時間の長さに応じて、前記第1の電荷注入ステップのみを実施することを特徴とする不揮発性半導体記憶装置の書き換え方法。

## 【請求項14】

40

10

20

30

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施さ れる第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意 の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施し、

前 記 第 2 の 電 荷 注 入 ス テ ッ プ の 電 荷 注 入 条 件 は 、 前 回 の デ ー タ 書 き 込 み か ら 書 き 換 え ま での放置時間の長さに応じて変化することを特徴とする不揮発性半導体記憶装置の書き換 え方法。

### 【請求項15】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施さ れる第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意 の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施し、

前記待ち時間は、データ書き込み時の周辺温度の高さに応じて変化することを特徴とす る不揮発性半導体記憶装置の書き換え方法。

#### 【請求項16】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き 換 え 時 に 、 第 1 の 電 荷 注 入 ス テ ッ プ と 、 前 記 第 1 の 電 荷 注 入 ス テ ッ プ の 後 に 実 施 さ れる第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意 の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施し、

デ - 夕 書 き 込 み 時 の 周 辺 温 度 の 高 さ に 応 じ て 、 前 記 第 1 の 電 荷 注 入 ス テ ッ プ の み を 実 施 することを特徴とする不揮発性半導体記憶装置の書き換え方法。

## 【請求項17】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施さ れる第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意 の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施し、

前記第2の電荷注入ステップの電荷注入条件は、データ書き込み時の周辺温度の高さに 応じて変化することを特徴とする不揮発性半導体記憶装置の書き換え方法。

### 【請求項18】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き 換 え 時 に 、 第 1 の 電 荷 注 入 ス テ ッ プ と 、 前 記 第 1 の 電 荷 注 入 ス テ ッ プ の 後 に 実 施 さ れる第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施し、

前記待ち時間は、データ書き換え回数に応じて変化することを特徴とする不揮発性半導 体記憶装置の書き換え方法。

# 【請求項19】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き 換 え 時 に 、 第 1 の 電 荷 注 入 ス テ ッ プ と 、 前 記 第 1 の 電 荷 注 入 ス テ ッ プ の 後 に 実 施 さ れる第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意

10

20

30

40

の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施し、

データ書き換え回数に応じて、前記第1の電荷注入ステップのみを実施することを特徴とする不揮発性半導体記憶装置の書き換え方法。

### 【請求項20】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施される第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施し、

前記第2の電荷注入ステップの電荷注入条件は、データ書き換え回数に応じて変化することを特徴とする不揮発性半導体記憶装置の書き換え方法。

# 【請求項21】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施される第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施し、

前記待ち時間は、書き換え直前のデータ値に応じて変化することを特徴とする不揮発性半導体記憶装置の書き換え方法。

### 【請求項22】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施される第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施し、

書き換え直前のデータ値に応じて、前記第1の電荷注入ステップのみを実施することを特徴とする不揮発性半導体記憶装置の書き換え方法。

# 【請求項23】

トラップ層を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施される第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施し、

前記第2の電荷注入ステップの電荷注入条件は、書き換え直前のデータ値に応じて変化することを特徴とする不揮発性半導体記憶装置の書き換え方法。

# 【請求項24】

トラップ層を有し、かつ 3 値以上の複数のメモリセル閾値電圧を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施される第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施することとし、まず低い閾値電圧を設定するメモリセルに対して電荷注入を実施し、次に別のより高い閾値電圧を設定するメモリセルの電荷注入を実施し、前記低い閾値電圧を設定するメモリ

10

20

30

40

セルの第 1 の電荷注入後の待ち時間を確保し、その後、前記低い閾値電圧を設定するメモリセルに対して第 2 の電荷注入を実施することを特徴とする不揮発性半導体記憶装置の書き換え方法。

# 【請求項25】

トラップ層を有し、かつ3値以上の複数のメモリセル閾値電圧を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施される第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施することとし、まず高い閾値電圧を設定するメモリセルに対して電荷注入を実施し、次に別のより低い閾値電圧を設定するメモリセルの電荷注入を実施し、前記高い閾値電圧を設定するメモリセルの第1の電荷注入後の待ち時間を確保し、その後、前記高い閾値電圧を設定するメモリセルに対して第2の電荷注入を実施することを特徴とする不揮発性半導体記憶装置の書き換え方法。

## 【請求項26】

トラップ層を有し、かつ3値以上の複数のメモリセル閾値電圧を有する不揮発性半導体記憶装置の書き換え方法であって、

書き換え時に、第1の電荷注入ステップと、前記第1の電荷注入ステップの後に実施される第2の電荷注入ステップとを有し、

前記第1の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施した後に、任意の待ち時間を確保し、

前記第2の電荷注入ステップでは、任意の閾値電圧まで電荷注入を実施することとし、メモリセルの閾値電圧レベルに応じて、データ書き込み時に前記第1の電荷注入と前記第2の電荷注入とを実施するか、消去前書き込み時に前記第1の電荷注入と前記第2の電荷注入との双方又は前記第1の電荷注入のみを実施するかを変更することを特徴とする不揮発性半導体記憶装置の書き換え方法。

# 【請求項27】

請求項26記載の不揮発性半導体記憶装置の書き換え方法において、

特に書き換え時において、書き換え前に低い閾値電圧に設定されていたメモリセルに対しては、前記第1の電荷注入を消去前書き込み時に実施し、消去後のデータ書き込み時には前記第1の電荷注入と前記第2の電荷注入とをまず高い閾値電圧を設定するメモリセルに対して実施し、前記第1の電荷注入後の待ち時間を、別のより低い閾値電圧を設定するメモリセルの書き込み時間で確保し、その後、前記高い閾値電圧を設定するメモリセルに対して前記第2の電荷注入を実施することを特徴とする不揮発性半導体記憶装置の書き換え方法。

### 【請求項28】

トラップ層を有する不揮発性メモリアレイと、

書き換え時に第1の電荷注入と、第2の電荷注入とを実施するように、前記第1の電荷注入において、任意のメモリセル閾値電圧まで電荷注入を実施した後に任意の待ち時間を制御すると共に、前記任意の待ち時間以降に、前記第2の電荷注入を制御する書き換え順序制御回路と、

前記不揮発性メモリアレイの消去単位領域毎に前記第1の電荷注入の実施時刻を記憶する領域を有する時間管理領域とを備えたことを特徴とする不揮発性半導体記憶装置。

# 【請求項29】

トラップ層を有する不揮発性メモリアレイと、

書き換え時に第1の電荷注入と、第2の電荷注入とを実施するように、前記第1の電荷注入において、任意のメモリセル閾値電圧まで電荷注入を実施した後に任意の待ち時間を制御すると共に、前記任意の待ち時間以降に、前記第2の電荷注入を制御する書き換え順

10

20

30

40

30

40

50

序制御回路と、

前記不揮発性メモリアレイの消去単位領域毎に前記第1の電荷注入後であるか又は前記第2の電荷注入後であるかの状態を記憶する領域を有する状態管理領域とを備えたことを特徴とする不揮発性半導体記憶装置。

### 【請求項30】

トラップ層を有し、かつ書き換え時に第1の電荷注入と、第2の電荷注入とを実施するように、前記第1の電荷注入において、任意のメモリセル閾値電圧まで電荷注入を実施した後に任意の待ち時間を制御すると共に、前記任意の待ち時間以降に、前記第2の電荷注入を制御する書き換え順序制御回路を備えた不揮発性半導体記憶装置と、

前記第1の電荷注入における任意の待ち時間の制御終了後、前記第1の電荷注入と、前記第2の電荷注入とを切り換え選択可能な書き換え動作選択回路とを備えたことを特徴とする電子機器。

【発明の詳細な説明】

# 【技術分野】

### [0001]

本発明は、メモリセルトランジスタのチャネル領域とゲート電極との間のゲート絶縁膜の内部にトラップ層を有し、電気的に書き込みと消去が可能な不揮発性半導体記憶装置及びその書き換え方法に関するものである。

#### 【背景技術】

### [0002]

従来のトラップ層を有する不揮発性メモリでは、メモリセルのチャネル領域とゲート電極との間の絶縁膜(SiO₂)内に存在する離散化されたトラップ層(SiN膜又はSiN膜/トップSiO₂膜界面の遷移領域)に電気的な電荷(電子及びホール)注入により電荷がトラップされ、そのメモリセル閾値電圧によってデータ " 0 "、データ " 1 "を判定し、情報を記憶する。

### [0003]

以下、電子注入を書き込みとして、またホール注入を消去として、書き込み動作における注入電荷を電子とし、書き込み動作における周辺電荷をホールとして説明する。

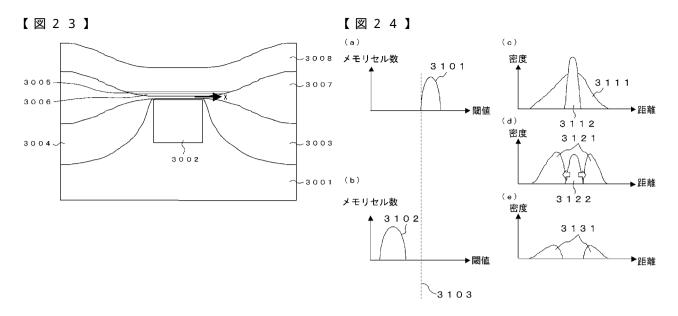

# [0004]

図23は、横軸をチャネル方向とした、トラップ層を有する不揮発性メモリの断面構造 図である。図23を用いて従来のトラップ層を有する不揮発性メモリの構成と動作につい て説明する。

### [0005]

## [0006]

書き込みは、ゲート電極3008に約9Vを、第1の不純物領域3003に約5Vを、第2の不純物領域3004に約1Vを、半導体基板3001に0Vをそれぞれ印加する。これにより、第2の不純物領域3004から第1の不純物領域3003に向かう電子の一部が第1の不純物領域3003の近傍の高電界によってホットとなり、トラップ層3006に局所的に注入され、メモリセル閾値電圧は高い状態となる。

## [0007]

消去は、ゲート電極3008に約-3Vを、第1の不純物領域3003に約5Vを、半

20

30

40

50

導体基板3001に0Vをそれぞれ印加し、第2の不純物領域3004をフローティングとする。これにより、第1の不純物領域3003内のバンド間トンネルにより生じるホールの一部が第1の不純物領域3003の近傍の高電界によってホットとなり、トラップ層3006に局所的に注入され、メモリセル閾値電圧は低い状態となる。

[0008]

読み出しは、ゲート電極 3 0 0 8 に約 4 V を、第 1 の不純物領域 3 0 0 3 に 0 V を、第 2 の不純物領域 3 0 0 4 に約 1 . 5 V を、半導体基板 3 0 0 1 に 0 V をそれぞれ印加する。これにより、トラップ層 3 0 0 6 中の電荷の有無により、データ " 0 "又は " 1 "が得られる。

[0009]

次に、図24を用いて従来のトラップ層を有する不揮発性メモリの、書き込み後の無バイアス状態におけるトラップされた電荷の挙動について説明する。

[0010]

図24(a)及び(b)は横軸をメモリセル閾値電圧、縦軸を書き込み対象のメモリセル数としたメモリセル閾値電圧の分布である。図24(c)から(e)は横軸を図23の矢印X方向の距離、縦軸を電荷密度とした第1の不純物領域3003の近傍の確率密度分布である。

[0011]

図24(a)において、3101は書き込み直後のメモリセル閾値電圧の分布である。図24(b)において、3102は寿命末期のメモリセル閾値電圧の分布であり、3103はベリファイレベルである。図24(c)において、3111は書き込みにより注入した電子の確率密度分布、3112は書き込み以前の消去により注入したホールの確率密度分布である。図24(d)において、3121はホールと結合した後の電子の確率密度分布、3122は電子と結合した後のホールの確率密度分布である。図24(e)において、3131は寿命末期の電子の確率密度分布である。

[0012]

上記のように局所的に2種類の電荷がトラップされた状態では、書き込み直後のメモリセル閾値電圧の分布3101において、図24(c)のように電子の確率密度分布3111とホールの確率密度分布3112はそれぞれ異なる確率密度分布を示し、電子の確率密度分布3112の重なった部分は瞬時に結合し、図24(d)のような電子の確率密度分布3121とホールの確率密度分布3122となる。その後、電荷の横方向拡散により電子とホールの結合が進み、メモリセル閾値電圧に変化が生じる。

[0013]

従来の寿命末期のメモリセル閾値電圧の分布 3 1 0 2 において、書き込み状態はホールよりも電子の総数が多いため、ホールが無くなり、図 2 4 ( e ) のような電子の確率密度分布 3 1 3 1 のみとなる。これにより、書き込み後のホールの総数を少なくすることで、メモリセルのデータ保持特性の向上を図ることができる。

[0014]

なお、ディスターブ(擾乱)によりメモリセル閾値電圧が低下し、ベリファイレベルを満たさないメモリセルに対して、再度書き込みを実施することで、ベリファイレベルを満たし、メモリセル閾値電圧の変化の抑制を図っているものもある(特許文献1参照)。

【特許文献 1 】特開平 7 - 3 7 3 9 7 号公報

【発明の開示】

【発明が解決しようとする課題】

[0015]

従来のトラップ層を有する不揮発性メモリにおいて、局所的に電荷をトラップ層に注入すると、トラップされた電荷が無バイアス状態にて横方向拡散し、周辺電荷と結合しメモリセル閾値電圧の変化が生じる。このメモリセル閾値電圧の変化によるデータ保持特性劣化が市場でのアクセススピードの低下やデータの誤読み出しの原因となる。

#### [0016]

また、データ保持特性には書き換え回数の依存性があり、書き換え回数が多いほどデータ保持特性の劣化が大きく、製品の書き換え保証回数の向上の妨げとなっている。

# [0017]

本発明は、上記従来の問題点を解決するためのもので、トラップ層を有する不揮発性メモリセルのデータ保持特性の劣化の抑制を実現することを目的とする。

### 【課題を解決するための手段】

# [0018]

上記目的を達成するため、本発明では、トラップ層を有する不揮発性半導体記憶装置の書き換えにあたり、任意の閾値電圧まで電荷注入を実施した後、任意の待ち時間を確保したうえ、更に任意の閾値電圧まで電荷注入を実施することとしたものである。ただし、一定の条件下で、待ち時間後の電荷注入を省略する。

### 【発明の効果】

# [0019]

本発明によれば、書き換えシーケンスにおいて、任意の待ち時間を確保した第1の電荷注入と、当該第1の電荷注入後の第2の電荷注入とを実施することにより、電荷注入動作直後の初期変動(ごく短時間での周辺電荷との結合による電荷ロス現象)を利用して、データ保持特性を劣化させる周辺電荷を低減させたうえで、更に、初期変動による電荷ロス分を補うことで、その後のデータ保持特性が向上する。しかも、第2の電荷注入が不要である場合には、これを省略することで高速書き換えを実現できる。

#### 【発明を実施するための最良の形態】

### [0020]

以下、本発明の実施形態について、図面を参照しながら説明する。なお、以下で述べる全ての実施形態における不揮発性半導体記憶装置のメモリセルは、トラップ層を有するものである。

# [0021]

以下、第1の電荷注入を第1の書き込み及び待ち時間とし、かつ第2の電荷注入を第2の書き込みとして説明する。

# [0022]

《第1の実施形態》

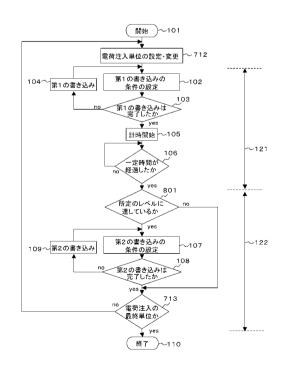

図 1 は、本発明の第 1 の実施形態における不揮発性半導体記憶装置の書き換え方法を示したフローチャートである。所定の不揮発性メモリセルに書き込みを行う場合の方法を説明する。

# [0023]

図 1 のフローチャートにおいて、 1 0 1 は開始端子、 1 1 0 は終了端子であり、また 1 0 2、 1 0 4、 1 0 5、 1 0 7、 1 0 9 は処理を示し、 1 0 3、 1 0 6、 1 0 8 は判断を示し、 1 2 1、 1 2 2 は範囲を示す。処理 7 1 2 及び判断 8 0 1 , 7 1 3 については後述する。

## [0024]

102は第1の書き込みを実施するための条件を設定する処理であり、104は第1の書き込みを実施する処理であり、105は時間計測を開始する処理であり、107は第2の書き込みを実施するための条件を設定する処理であり、109は第2の書き込みを実施する処理である。また103は第1の書き込みが完了したかを判断する処理であり、106は一定時間が経過しているかを判断する処理であり、108は第2の書き込みが完了したかを判断する処理である。121は第1の電荷注入の範囲であり、122は第2の電荷注入の範囲である。

### [0025]

所定のメモリセルに対する書き込みフローは開始端子101から開始し、所望の第1の書き込み条件を設定する処理102を経て第1の書き込みが完了したかの判断103に進む。処理102は例えば、書き込みにおける電圧条件・パルス幅条件などの設定である。

20

10

30

50

20

30

40

50

また判断103は例えば、所定の閾値電圧まで書き込みが行われていることを確認する書き込みベリファイである。

### [0026]

判断 1 0 3 において、第 1 の書き込みが完了していないと判断した場合は、第 1 の書き込み処理 1 0 4 へ進む。第 1 の書き込み処理 1 0 4 を実施した後は、所望の第 1 の書き込み条件を設定する処理 1 0 2 を経て第 1 の書き込みが完了したかの判断 1 0 3 に戻る。判断 1 0 3 で第 1 の書き込み完了を確認するまで、処理 1 0 4 、 1 0 2 を繰り返す。

## [0027]

判断103で第1の書き込み完了と判断した場合、時間計測を開始する処理105を実施し判断106に進む。判断106において、時間計測を開始する処理105から、計測した時間が一定時間以上経過しているかを確認し、経過している場合、第2の書き込みを実施するための条件を設定する処理107へ進む。判断106において、一定時間以上経過していない場合は、判断106の条件を満たすまで判断106を繰り返す。判断106での一定時間とは長時間であるほど望ましい。以上が第1の電荷注入の範囲121であり、第1の書き込みと一定時間で決定される待ち時間から構成されている。以後は第2の電荷注入122となる。

### [0028]

第2の書き込みを実施するための条件を設定する処理107は第2の書き込みが完了したかの判断108に進む。処理107は例えば、書き込みにおける電圧条件・パルス幅条件などの設定である。また判断108は例えば、所定の回数書き込みパルス印加をしたかを確認するものである。

### [0029]

判断108において、第2の書き込みが完了していないと判断した場合は、第2の書き込み処理109へ進む。第2の書き込み処理109を実施した後は、所望の第2の書き込み条件を設定する処理107を経て第2の書き込みが完了したかの判断108に戻る。判断108で書き込み完了を確認するまで、処理109、107を繰り返す。判断108で書き込み完了と判断した場合、終了端子110へ進み一連の書き込みフローが終了する。

### [0030]

本書き込みフローはメモリセルアレイの書き込みにおいても、各処理をアドレスなどの書き込み単位で実施することにより同様に適用できる。

## [0031]

図1のフローチャートにおいて、713はメモリセルアレイの所定の書き込みエリアにおける書き込み単位の最終であるかの判断、712は書き込み単位の設定又は変更処理を示す。

# [0032]

第1の書き込みを実施する前に、書き込みを実施する書き込み単位を設定712し、前記のとおり第1、第2の書き込みを実施し、第2の書き込みが完了したかの判断108において書き込み完了を確認した場合、メモリセルアレイの所定の書き込みエリアにおける書き込み単位の最終であるかの判断713を行う。判断713で最終でないと判断した場合書き込み単位の変更処理712を行った後、第1の書き込みを行う。判断713で最終と判断した場合、終了端子110へ進み一連の書き込みフローを終了する。ここで書き込み単位とは例えばアドレスであり、書き込み単位の変更とは例えばアドレスインクリメントである。なお、第2の書き込みを任意の回数実施することとしてもよい。

# [0033]

図 1 のフローチャートにおいて、 8 0 1 は所定の判定レベルに達しているかの判断を示す。ここで、所定の判定レベルとは例えば第 1 の書き込み時のベリファイレベルや、そのベリファイレベルから待ち時間における変動期待分を追加したレベルなどである。

### [0034]

所定のレベルに達している場合は、第2の書き込みの条件設定107に進み前記のとおり第2の電荷注入を実施する。所定のレベルに達していない場合は、電荷注入の最終単位

30

40

50

かの判断 7 1 3 に進み、他の書き込み単位の第 1 の書き込みに進むか、最終単位であれば終了 1 1 0 に進む。

### [0035]

所定のレベルに達しているかの判断801によって、例えば第1の書き込み及び待ち時間によって電子とホールの結合によるメモリセル閾値電圧の変化量が少ない場合は第2の電荷注入を実施しないこととなる。所定の判定レベルを例えば読み出しレベルからの必要なマージンを確保した書き込みレベルなどとすれば、判定レベルに達したもののみ第2の書き込みを実施すればよく、本発明の効果をより最適な時間で適用できる。

#### [0036]

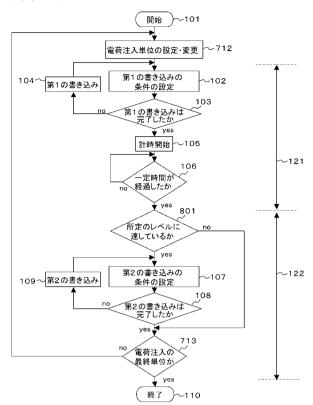

次に、図2を使って本発明の第1の実施形態における電荷の挙動を説明する。図2は、トラップ層を有する不揮発性メモリにおけるトラップされた電荷の挙動を、上記図1にて説明した書き込みフローをメモリセルアレイに対して実施した場合について示すものである。

# [0037]

図 2 において図 2 ( a ) から図 2 ( d ) は横軸をメモリセル閾値電圧、縦軸を書き込み対象のメモリセル数としたメモリセル閾値電圧の分布である。図 2 ( e ) から図 2 ( h ) は横軸を図 2 3 のメモリセルにおける矢印 X 方向の距離、縦軸を電荷密度とした第 1 の不純物領域 3 0 0 3 の近傍の確率密度分布である。

#### [0038]

図 2 ( a )において、 2 0 1 は第 1 の書き込み直後のメモリセル閾値電圧の分布である。図 2 ( b )において、 2 0 2 は一定時間経過後のメモリセル閾値電圧の分布である。図 2 ( c )において、 2 0 3 は一定時間経過後第 2 の書き込みを実施した直後のメモリセル閾値電圧の分布である。図 2 ( d )において、 2 0 4 は寿命末期のメモリセル閾値電圧の分布である。図 2 ( a )から( d )において、 2 0 5 は書き込みベリファイレベルである

### [0039]

図 2 ( e ) において、 2 1 1 は第 1 の書き込みにより注入した電子の確率密度分布、 2 1 2 はそれ以前の消去により注入したホールの確率密度分布である。図 2 ( f ) において、 2 2 1 はホールと結合した後の電子の確率密度分布、 2 2 2 は電子と結合した後のホールの確率密度分布である。図 2 ( g ) において、 2 3 1 はホールと結合した後に第 2 の書き込みにより注入した電子の確率密度分布、 2 3 2 は電子と結合した後のホールの確率密度分布である。図 2 ( h ) において、 2 4 1 は寿命末期の電子の確率密度分布である。

### [0040]

第1の書き込み完了直後のメモリセル閾値電圧の分布201において、図2(e)のように電子とホールはそれぞれ異なる確率密度分布を示し、電子とホールの重なった部分は瞬時に結合し、第1の書き込み完了から一定時間経過後、図2(f)のような電子の確率密度分布221とホールの確率密度分布222となり、メモリセル閾値電圧の分布は201から低下し202となる。

# [0041]

この後第2の書き込みを実施すると、メモリセル閾値電圧の分布は202から上昇し、図2(c)のような第2の書き込み完了直後のメモリセル閾値電圧の分布203となる。そしてその完了直後の電子、ホールの確率密度分布は、図2(g)のような電子の確率密度分布231、ホールの確率密度分布232となり、メモリセルのデータ保持特性を劣化させるホールの確率密度が減少し、電子の確率密度が増加することとなる。

### [0042]

これによって、本発明の効果としてその後の電荷の横方向拡散による電子とホールの結合は図24に示した従来例に比べ抑制され、メモリセル閾値電圧の経時変化量も低減し、メモリセルのデータ保持特性が向上する。すなわち、図2(d)のような寿命末期のメモリセル閾値電圧の分布241においては、図2(h)のように電子の確率密度分布241が図24(e)の従来の電子の確率密度分布3131に比べ高くなる。

20

30

40

50

#### [0043]

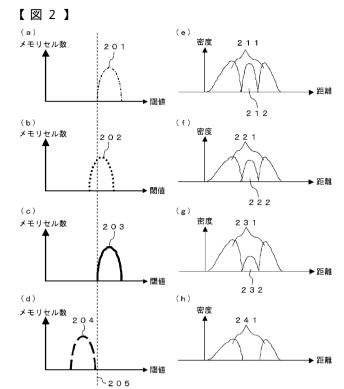

図3に、本発明を適用した場合のメモリセル閾値電圧の変化を示す。図3(a)は、横軸は保存時間、縦軸はメモリセル閾値電圧であり、301は従来のメモリセル閾値電圧の変動、302は読み出しレベルである。どの保存時間においても、本発明におけるメモリセル閾値電圧302は従来のメモリセル閾値電圧301に比べて高く、データ読み出しのマージンがより多く確保できるため、データ保持特性が向上する。

# [0044]

図3(b)は、横軸は書き換え回数、縦軸はメモリセル閾値電圧の変動量であり、31 1は従来の閾値変動量の書き換え回数依存性、312は本発明における閾値変動量の書き 換え回数依存性である。本発明によって、メモリセル閾値電圧の変動量が同じになる書き 換え回数が、従来に比べ増加する。

### [0045]

なお、本実施形態において第2の書き込みを、例えば電圧やパルス幅をより細かな単位 で実施することで、本実施形態の更なる効果を得られる。

#### 【0046】

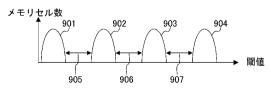

図4の多値メモリのメモリセル閾値電圧分布の図を用いて本実施形態の効果を説明する。901は多値メモリにおける1番目のレベルのデータのメモリセル閾値電圧の分布、902は多値メモリにおける2番目のレベルのデータのメモリセル閾値電圧の分布、903は多値メモリにおける3番目のレベルのデータのメモリセル閾値電圧の分布、904は多値メモリにおける4番目のレベルのデータのメモリセル閾値電圧の分布、905は1番目と2番目のデータの判定に必要な閾値電圧マージン、906は2番目と3番目のデータの判定に必要な閾値電圧マージンである。

# [0047]

特に閾値電圧レベルが中間的なレベルのものについて、例えば2番目のレベルのデータのメモリセル閾値電圧の分布902について効果を説明する。第1の書き込み後に所定のレベルに達した場合には第2の書き込みを行い、所定のレベルまで書き込みを行うが、その際例えば電圧やパルス幅をより細かな単位で実施することで、2番目のレベルのデータのメモリセル閾値電圧の分布902の上側の上昇を最小限にとどめることができる。これにより、2番目と3番目のデータの判定に必要な閾値電圧マージン906をより少なくできる。これによって、より多くのレベルを持った多値メモリ、あるいは全体の閾値レベルの低下による昇圧回路の縮小化などを図ることが可能となる。

# [0048]

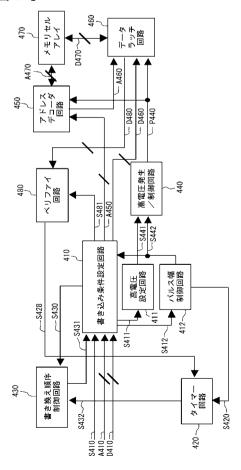

本実施形態は、図5の構成によって実現できる。図5は、本発明の第1の実施形態における不揮発性半導体記憶装置を示している。所定のアドレスの不揮発性メモリセルに書き込みを行う場合の方法を説明する。

### [0049]

図 5 の 4 1 0 は書き込み条件設定回路、 4 1 1 は高電圧設定回路、 4 1 2 はパルス幅制御回路、 4 2 0 はタイマー回路、 4 3 0 は書き換え順序制御回路、 4 4 0 は高電圧発生/制御回路、 4 5 0 はアドレスデコーダ回路、 4 6 0 はデータラッチ回路、 4 7 0 はメモリセルアレイ、 4 8 0 はベリファイ回路である。

## [0050]

また、S410~S481は制御信号、A410~A470はアドレスバス、D410~D480はデータバス、440は高電圧信号を示している。

# [0051]

まず、第1の書き込み動作について説明する。書き込み条件設定回路410は、外部から入力される制御信号S410、書き込みアドレスA410、書き込みデータD410を受けて、第1の書き込み条件の設定を行う。ここでの制御信号は書き込みコマンドなどである。また、書き込み条件は例えば、書き込みにおける電圧条件・パルス幅条件などの設

定である。入力された設定条件に従い、電圧条件は高電圧設定回路411に、パルス幅条件はパルス幅制御回路412に設定又は制御される。書き込みに必要な高電圧は、高電圧設定回路411の設定値に基づき高電圧発生/制御回路440で制御され、高電圧信号 P 4 4 0 として出力される。この高電圧信号 P 4 4 0 は、アドレスデコーダ回路450及びデータラッチ回路460に入力され、アドレスデコーダ回路450によって選択されたメモリセルアレイ470内のメモリセルを対象としてデータラッチ回路460のデータに基づきパルス幅制御回路412に設定された時間だけ印加される。

## [0052]

書き込み終了の判断は例えば、ベリファイ回路480を用いて、所定の閾値レベルまで 書き込みが行われていることを確認する書き込みベリファイによって行われる。

[0053]

書き込みベリファイにおいて、第1の書き込みが完了していないと判断した場合は、第 1の書き込みパルスを印加する。第1の書き込みパルス印加後は、所望の第1の書き込み 条件の設定を経て第1の書き込みが完了したかの書き込みベリファイを行う。書き込みベ リファイによって、書き込み完了を判断するまで、繰り返し行う。

[0054]

書き込みベリファイによって、書き込み完了と判断した場合、ベリファイ回路480の出力信号S428をタイマー回路420に入力することで時間計測を開始する。一定時間経過後、制御信号S432を書き換え順序制御回路430に入力し、第2の書き込み動作に進む。

[0055]

あるいは、例えば、ベリファイを実施しない書き込みフローの場合には、パルス幅制御回路412の出力信号S420からパルス印加終了のタイミングをタイマー回路420に入力することで時間計測を開始する。一定時間経過後、制御信号S432を書き換え順序制御回路430に入力し、第2の書き込み動作に進む。

[0056]

次に、第2の書き込み動作について説明する。書き込み条件設定回路410は、書き換え順序制御回路430からの制御信号S431によって、第2の書き込み動作を開始する。また、第2の書き込み条件の設定を行う。書き込み条件は例えば、書き込みにおける電圧条件・パルス幅条件などの設定である。入力された設定条件に従い、電圧条件は高電圧設定回路411に、パルス幅条件はパルス幅制御回路412にそれぞれ設定又は制御される。書き込みに必要な高電圧は、高電圧設定回路411の設定値に基づき高電圧発生1制のは、アドレスデコーダ回路450及びデータラッチ回路460に入力され、アドレスデコーダ回路450及びデータラッチ回路460に入力され、アドレスデータラッチ回路450のデータに基づきパルス幅制御回路412に設定された時間にでデータラッチ回路460のデータに基づきパルス幅制御回路412に設定された時間に対印加される。また、書き込み終了の判断は例えば、ベリファイによって行われる。

[0057]

書き込みベリファイにおいて、第2の書き込みが完了していないと判断した場合は、第2の書き込みパルスを印加する。第2の書き込みパルス印加後は、所望の第2の書き込み条件の設定を経て第2の書き込みが完了したかの書き込みベリファイを行う。書き込みベリファイによって、書き込み完了を判断するまで、繰り返し行う。

[0058]

書き込みベリファイによって、書き込み完了と判断した場合、一連の書き込み動作が終 了する。

[0059]

以上より本発明によれば、電荷注入動作直後のごく短時間での周辺電荷との結合による電荷ロス現象である初期変動を利用して、データ保持特性を劣化させる周辺電荷を低減さ

20

10

30

40

20

30

40

50

せたうえで、初期変動による電荷ロス分を補うことで、その後のデータ保持特性が向上する。

[0060]

なお、第1の書き込み(第1の電荷注入)を所定の回数実行することとしてもよい。第 1の書き込みと一定時間の放置による電子とホールの結合を繰り返すことで、データ保持 特性が更に向上し、更にメモリセル閾値電圧の分布の範囲が狭くなる利点がある。

[0061]

《第2の実施形態》

一般的な不揮発性メモリの書き換えでは、消去前に書き換えエリアのデータを全て"0"データにした後、消去を実施するものが多くある。これは、"1"データのセルを消去することで、セルがより深い消去レベルとなり、特性を悪化させるリークなどが発生することを防ぐものである。

[0062]

本発明は、この消去前書き込みにおいても適用することができ、第 2 の実施形態として 説明する。

[0063]

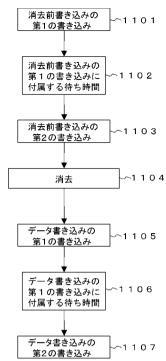

図6は、一般的な不揮発性メモリの書き換えに本発明を適用した場合のフローチャートである。1101から1103までは消去前書き込みでのフローであり、1105から1107まではデータ書き込みでのフローである。1104はデータの消去である。1101、1105は前記第1の書き込みであり、1102、1106は前記第1の書き込みに付属する待ち時間であり、1103、1107は前記第2の書き込みである。なお、データ消去1104の前の第2の書き込み1103は省略可能である。

[0064]

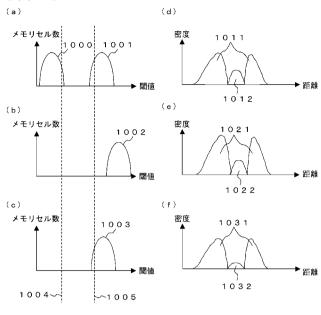

図7は、本発明の第2の実施形態における不揮発性半導体記憶装置の書き換え方法をメモリセル閾値電圧の分布及び確率密度分布で示した図である。所定の不揮発性メモリセルに消去前書き込みを行う場合を説明する。

[0065]

図 7 ( a ) から( c ) は横軸をメモリセル閾値電圧、縦軸を書き込み対象のメモリセル数としたメモリセル閾値電圧の分布である。ここに、 1 0 0 4 は消去ベリファイレベル、1 0 0 5 は書き込みベリファイレベルである。図 7 ( d ) から( f ) は横軸を図 2 3 の矢印 X 方向の距離、縦軸を密度とした第 1 の不純物領域 3 0 0 3 近傍の確率密度分布である

[0066]

図7(a)において、1000は消去前書き込み直前のデータ"1"側のメモリセル閾値の分布であり、1001は消去前書き込み直前のデータ"0"側のメモリセル閾値の分布である。図7(b)において、1002は消去前書き込みにおける第1の書き込み直後のメモリセル閾値電圧の分布である。図7(c)において、1003は第1の書き込みにおける一定時間経過後のメモリセル閾値電圧の分布である。図7(d)において、1011は消去前書き込み直前のデータ"0"側の電子の確率密度分布、1012は同じくホールの確率密度分布である。図7(e)において、1021は消去前書き込みにおける第1の書き込み直後の電子の確率密度分布、1022は同じくホールの確率密度分布である。図7(f)において、1031は第1の書き込みにおける一定時間経過後の電子の確率密度分布、1032は同じくホールの確率密度分布である。

[0067]

本発明の第2の実施形態は、消去前書き込みの第1の書き込み1101で、データ書き込み時の書き込みレベルよりも高い閾値電圧まで書き込みを行うことと、消去前書き込みの第2の書き込み1103を実施しないこととを特徴とするものである。

[0068]

消去前書き込みにおいて、第1の電荷注入1101をデータ書き込み時の書き込みレベルよりも高い閾値電圧まで実施することで、電子の確率密度分布1021が増加する。こ

れによって、電子とホールの結合によりメモリセルのデータ保持特性を劣化させるホールの確率密度 1 0 3 2 が減少し、電子の確率密度 1 0 3 1 が増加する。消去前書き込みでは、その後に必ず消去ステップ 1 1 0 4 があるので、データ保持に懸念される書き込みレベルが高いことによる問題もなく、また電子とホールの結合によって低下したレベルを上昇させる必要もないので、消去前書き込みの第 2 の書き込み 1 1 0 3 は省くことができる。

#### [0069]

書き換え毎にホールの確率密度分布を低下させておくことで、多数回の書き換えによって蓄積されるホールの増加を最小限にとどめることができ、不揮発性メモリの電荷保持特性の書き換え回数依存性の向上が図れ、高エンデュランスを実現できる。

## [0070]

なお、第1の書き込み及び第2の書き込みの条件を製造単位又は書き換え単位で変更することとしてもよい。ここで製造単位とは、例えば製造工場、製造時期、又はロットやウェハなど製造上のバラツキにより特性のバラツキが生ずる単位などである。また書き換え単位とは、例えば個々のチップやエリア、アドレス、個々のメモリセルなど、位置や回路的な違いなどにより特性差を生ずる単位である。

#### [0071]

これによって、製造や回路、位置などによる特性のバラツキが存在しても最適な第1及び第2の書き込みを実施できる。

#### [0072]

書き換えの最小単位で最適化することで、本発明の最大の効果を得ることができ、製造単位や大きな又は中間的な書き換え単位で最適化することで、書き換え時間の増加を最小限にとどめたうえで各種バラツキにも対応した本発明の効果向上を図ることができる。

### [0073]

《第3の実施形態》

第3の実施形態は、検査時に各チップの書き込み特性などを測定し、測定結果に応じて書き換えにおける第1及び第2の書き込みの条件を決定し、書き込み条件の設定値を記憶し、実使用においてその設定値により書き換えを実施するものである。

### [0074]

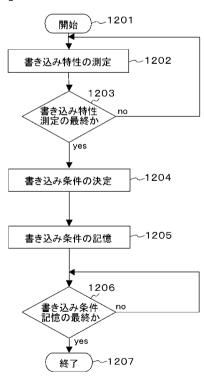

図 8 は、本実施形態を検査工程の中で実施する場合のフローチャートである。図 8 のフローチャートにおいて、1 2 0 1 は開始端子、1 2 0 7 は終了端子であり、また1 2 0 2 、1 2 0 4 、1 2 0 5 は処理を示し、1 2 0 3 、1 2 0 6 は判断を示す。

# [0075]

開始端子1201は書き込み特性の測定1202につながる。ここで測定する特性とは例えば所定の回数書き込みパルス印加をした後の書き込み閾値電圧レベルや、所定の書き込みベリファイレベルに達するまで印加したパルス数又は時間などである。1202は書き込み特性測定の最終かの判断1203につながる。測定が最終である場合書き込み条件の決定1204につながり、最終でない場合書き込み特性の測定1202に戻る。ここで書き込み条件の決定1204とは、例えば測定を行った範囲の特性の平均値又は最大値、最小値などから、過去の評価の結果などを踏まえて書き込み条件を算出するものである。

### [0076]

書き込み条件の決定1204後、書き込み条件の記憶1205につながる。書き込み条件の記憶1205は、例えば不揮発性メモリなどに行われる。書き込み条件の記憶1205は書き込み条件記憶の最終かの判断1206につながる。記憶の完了を待って端子1207につながる。

### [0077]

書き込み条件を実際のチップの特性測定結果を反映した値とすることで、各チップの特性を踏まえた最適な第1及び第2の書き込みが実現でき、実際の書き換えにおいて書き換え時間の増加なく本発明の効果をより上げることができる。

## [0078]

《第4の実施形態》

10

20

30

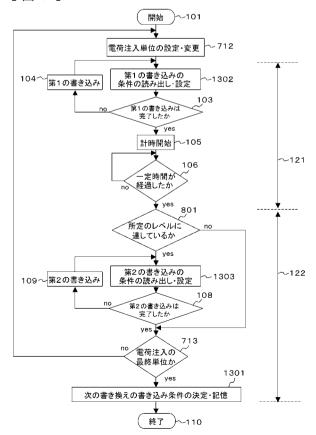

図9は、本発明の第4の実施形態における不揮発性半導体記憶装置の書き換え方法を示したフローチャートである。図9のフローチャートにおいて、1301、1302、13 03は処理である。

### [0079]

電荷注入の最終単位かの判断713で最終の場合、次の書き換えの書き込み条件の決定・記憶1301に進み、その後終了端子110につながる。ここで次の書き換えの書き込み条件の決定・記憶1301は、第1の電荷注入121及び第2の電荷注入122で実際に書き込みを実施したときの、例えば所定の回数書き込みパルス印加をした後の書き込み閾値電圧レベルや、所定の書き込みベリファイレベルに達するまで印加したパルス数又は時間などをもとに、電荷注入単位での特性の平均値又は最大値、最小値などから、過去の評価の結果などを踏まえて書き込み条件を算出、決定する処理である。なお、決定された書き込み条件は、揮発性メモリあるいは不揮発性メモリなどに記憶される。

### [0080]

次回の書き換えにおいて、第1の電荷注入では、電荷注入単位の設定・変更712から、第1の書き込みの条件の読み出し・設定1302につながり、この書き込み条件の読み出し・設定1302では過去の書き換えにおいて決定・記憶1301された条件を用いることになる。第2の電荷注入においても同様に、第2の書き込みの条件の読み出し・設定1303から開始され、第2の書き込み条件の読み出し・設定1303でも過去の書き換えにおいて決定・記憶1301された条件を用いる。

### [0081]

これによって、最も小さな単位としてメモリセルで第1及び第2の電荷注入の最適化を行うことができ、どのメモリセルでも均一に本発明の効果を得ることができる。また、次の書き換えの書き込み条件の決定・記憶1301を都度実施することで、書き換え回数などに応じた特性変動にも対応した第1、第2の電荷注入が実施できる。

## [0082]

《第5の実施形態》

図 1 0 は、本発明の第 5 の実施形態における不揮発性半導体記憶装置の書き換え方法を示したフローチャートである。図 1 0 のフローチャートにおいて、 1 4 0 1、 1 4 0 2、 1 4 0 3 は処理を示す。 1 4 0 1 は前回の書き込み時刻の読み出しを実施する処理であり、 1 4 0 2 は待ち時間の設定を変更する処理であり、 1 4 0 3 は書き込み時刻を記憶する処理である。

# [0083]

所定のメモリセルに対する書き込みフローは開始端子101から開始し、前回の書き込み時刻の読み出しを実施する処理1401を経て、更に待ち時間の設定を変更する処理1401は402を経て、所望の第1の書き込み条件を設定する処理102へ進む。処理1401は例えば、不揮発性メモリのある領域に、前回の書き込みを実施した時刻を記憶させておき、その情報を読み出すものである。処理1402は例えば、前回の書き込み時刻からの経過時間が長いとき、判断106の経過時間の設定を短くするものである。前回の書き込み時刻からの経過時間が長いときは、書き込みにより注入した電子と消去により注入したホールの結合は十分にされており、判断106の経過時間の設定を短くすることができ、書き込み時間を短縮できる。一方、前回の書き込み時刻からの経過時間が短いとき、当時間の設定を長くするものである。前回の書き込み時刻からの経過時間の設定を長くすることで電子とホールの結合を促し、データ保持特性を向上させる。

### [ 0 0 8 4 ]

判断108で書き込み完了と判断した場合、書き込み時刻を記憶する処理1403を経て、終了端子110へ進み一連の書き込みフローが終了する。処理1403は例えば、不揮発性メモリのある領域に、書き込み終了時の時刻を記憶させるものである。この情報は次回の書き換え時に使用する。

## [0085]

50

20

30

(17)

図11は、本発明の第5の実施形態の変形例を示したフローチャートである。図11のフローチャートにおいて、1501は第2の書き込みを実施するかを判断する処理である

[0086]

判断106において、時間計測を開始する処理105から、計測した時間が一定時間以上経過しているかを確認し、経過している場合は判断1501へ進む。判断1501において、前回の書き込み時刻からの経過時間が長いとき、第2の書き込みを実施せず、書き込み時刻を記憶する処理1403に進む。前回の書き込み時刻からの経過時間が長いときは、電子とホールの結合は十分にされ、第1の書き込み後の初期変動による電荷ロス分が少ないため、第2の書き込みを実施しなくてもよく、書き込み時間を短縮できる。一方、前回の書き込み時刻からの経過時間が短ければ、第2の書き込みを実施するために、第2の書き込みを実施する条件を設定する処理107へ進む。前回の書き込み時刻からの経過時間が短いときは、電子とホールの結合は十分でなく、第1の書き込み後の初期変動による電荷ロス分が多いため、第2の書き込みを実施し、データ保持特性を向上させる。

[0087]

図12は、本発明の第5の実施形態の他の変形例を示したフローチャートである。図1 2のフローチャートにおいて、1601は第2の書き込みを実施する条件を変更する処理 である。

[0088]

第2の書き込みを実施する条件を設定する処理107を経て、第2の書き込みを実施する条件を変更する処理1601へ進む。処理107は例えば、書き込みにおける電圧条件・パルス幅条件などの設定である。処理1601は例えば、前回の書き込み時刻からの経過時間が長いときは、電子とホールの結合は十分にされ、第1の書き込み後の初期変動による電荷ロス分が少ないため、第2の書き込みを高い電圧で実施しなくてもよく、過剰なストレスの印加を抑制できる。一方、前回の書き込み時刻からの経過時間が短ければ、第2の書き込みの電圧条件を高い設定に変更するものである。前回の書き込み時刻からの経過時間が短いときは、電子とホールの結合は十分でなく、第1の書き込み後の初期変動による電荷ロス分が多いため、第2の書き込みを高い電圧で実施し、データ保持特性を向上させる。

[0089]

処理1601を経て、第2の書き込みが完了したかの判断108に進む。判断108は 例えば、所定の回数書き込みパルス印加をしたかを確認するものである。

[0090]

本実施形態は、図13の構成によって実現できる。図13は、本発明の第5の実施形態における不揮発性半導体記憶装置を示している。メモリセルアレイ470を消去単位領域A(1)2371~消去単位領域A(N)2373に分割し、前記各消去単位領域毎に時間管理領域T(N)2376を含み、更に時間管理回路2321とセンスアンプ回路2390とを含み、センスアンプ回路2390をメモリセルアレイ470とのデータバスD2390と時間管理回路2321とのデータバスD2391との間に接続し、時間管理回路2321と書き込み条件設定回路410とをデータバスD2321で接続すること以外は、図5と同様の構成を有する。

[0091]

書き込みを行う場合の動作を説明する。まず、任意の消去単位領域 A ( 1 、 2 、・・・、N)に対する第 1 の書き込み動作終了後の第 2 の書き込み動作について説明する。時間管理回路 2 3 2 1 が発生する現在時刻をデータバス D 2 3 2 1 経由で書き込み条件設定回路 4 1 0 に設定し、データバス D 4 6 0 を経由してデータラッチ回路 4 6 0 に設定し、更にデータバス D 4 7 0 を経由したデータをアドレスデコーダ回路 4 5 0 によって、各々該当する時間管理領域 T ( 1 、 2 、・・・、N)に対して書き込みを行う。

[0092]

20

30

40

次に、任意の消去単位領域A(1、2、・・・、N)に対する第1の書き込み前の消去動作について説明する。消去動作前に各々該当する時間管理領域T(1、2、・・・、N)のデータを、データバスD2390を経由しセンスアンプ回路2390により読み出す。読み出されたデータは、先の第2の書き込み動作時刻を示しており、このデータを、D2391を経由し時間管理回路2321に入力し、時間管理回路2321により、先の第2の書き込み時刻と現在時刻を比較し、先の第2の書き込み時刻から現在までの経過待ち時間を算出すると共に、前記経過待ち時間情報を時間管理回路2321内に一時記憶する。その後、先の第2の書き込み時刻を読み出した消去単位領域A(1、2、・・・、N)に対する消去動作を行う。

### [0093]

次に、任意の消去単位領域 A (1、2、・・・、N)に対する第1の書き込み前の消去動作について説明する。先の消去動作時に時間管理回路2321内に一時記憶した前記経過待ち時間情報をデータバスD2321経由で書き込み条件設定回路410に設定する。書き込み条件設定回路410は、前記経過待ち時間情報をもとに、第1の書き込み条件を設定する。すなわち、前記経過待ち時間情報より、経過待ち時間が一定時間以上の場合には、経過待ち時間中に第1の書き込みベリファイによって、書き込み完了と判断した場合のタイマー回路420による第2の書き込みまでの待ち時間を短縮することができる。

### [0094]

以上より本実施形態によれば、先の第2の書き込み時刻から第1の書き込み動作前の消去動作までの経過待ち時間によって、電荷注入動作後の長時間の周辺電荷との結合による電荷ロス現象を利用して、データ保持特性を劣化させる周辺電荷を低減させたうえで、この長時間にわたる必要十分な周辺電荷の低減が行われた場合には、次の第1の書き込み完了後の第2の書き込みまでの待ち時間を短縮することができる。実際の用途においては、長時間にわたり保持されるデータが多いため、データ保持特性の向上と書き込み時間の短縮とを両立することができる。

### [0095]

# 《第6の実施形態》

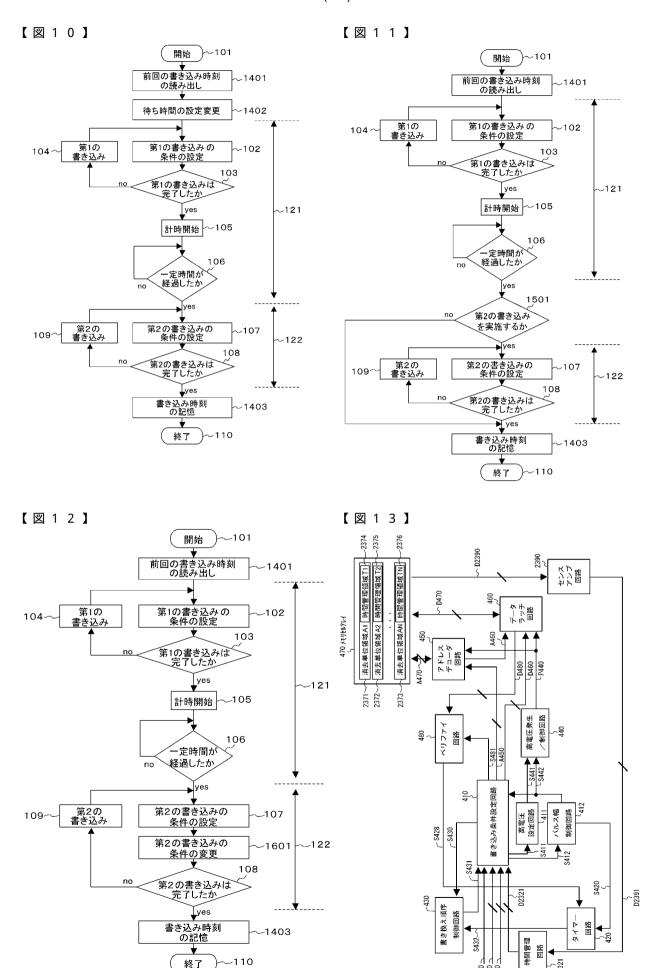

図14は、本発明の第6の実施形態における不揮発性半導体記憶装置の書き換え方法を示したフローチャートである。図14のフローチャートにおいて、1701は処理を示す。1701は周辺温度を検知する処理である。

### [0096]

所定のメモリセルに対する書き込みフローは開始端子101から開始し、周辺温度を検知する処理1701を経て、所望の第1の書き込み条件を設定する処理102へ進む。処理1701は例えば、抵抗に流れる電流量をモニターすることで周辺温度を検知するものである。

# [0097]

第2の書き込みを実施する条件を設定する処理107を経て、第2の書き込みを実施する条件を変更する処理1601へ進む。処理107は例えば、書き込みにおける電圧条件・パルス幅条件などの設定である。処理1601は例えば、周辺の温度が低いとき、第2の書き込みの電圧条件を低い設定に変更するものである。周辺の温度が低いときは、電子とホールの結合は温度により加速されず、第1の書き込み後の初期変動による電荷ロス分が少ないため、第2の書き込みを高い電圧で実施しなくてもよく、過剰なストレスの印加を抑制できる。一方、周辺の温度が高いとき、第2の書き込みの電圧条件を高い設定に変更するものである。周辺の温度が高いときは、電子とホールの結合は温度により加速され、第1の書き込み後の初期変動による電荷ロス分が多く、それを補うために第2の書き込みの電圧条件を高く設定し、データ保持特性を向上させる。

### [0098]

処理1601を経て、第2の書き込みが完了したかの判断108に進む。判断108は 例えば、所定の回数書き込みパルス印加をしたかを確認するものである。

# [0099]

40

30

10

20

なお、データ書き込み時の周辺温度の高さに応じて待ち時間を変化させてもよい。また、データ書き込み時の周辺温度の高さに応じて、第1の電荷注入のみを実施することとしてもよい。

# [0100]

《第7の実施形態》

図15は、本発明の第7の実施形態における不揮発性半導体記憶装置の書き換え方法を示したフローチャートである。図15のフローチャートにおいて、1801、1802は処理を示す。1801は書き換え回数の読み出しを実施する処理であり、1802は書き換え回数を記憶する処理である。

#### [0101]

所定のメモリセルに対する書き込みフローは開始端子101から開始し、今までの書き換え回数の読み出しを実施する処理1801を経て、第1の書き込みを実施する条件を設定する処理102へ進む。処理1801は例えば、不揮発性メモリのある領域に、今までの書き換え回数を記憶させておき、その情報を読み出すものである。

### [0102]

判断106において、時間計測を開始する処理105から、計測した時間が一定時間以上経過しているかを確認し、経過している場合は判断1501へ進む。判断1501において、今までの書き換え回数が少ないときは、データ保持特性を 劣化させる周辺電荷が少なく、第1の書き込み後の初期変動による電荷ロス分が少ないため、第2の書き込みを実施しなくてもよく、書き込み時間を短縮できる。一方、今までの書き換え回数が多いとき、第2の書き込みを実施するために、第2の書き込みを実施する条件を設定する処理107へ進む。今までの書き換え回数が多いとき、データ保持特性を 劣化させる周辺電荷が多く、第1の書き込み後の初期変動による電荷ロス分が多いため、第2の書き込みを実施し、データ保持特性を向上させる。

### [0103]

判断108で書き込み完了と判断した場合、書き換え回数を記憶する処理1802を経て、終了端子110へ進み一連の書き込みフローが終了する。処理1802は例えば、不揮発性メモリのある領域に、書き込み終了時の書き換え回数を記憶させるものである。この情報は次回の書き換え時に使用する。

### [0104]

なお、データ書き換え回数に応じて待ち時間を変化させてもよい。また、データ書き換え回数に応じて第 2 の電荷注入の電荷注入条件を変化させてもよい。

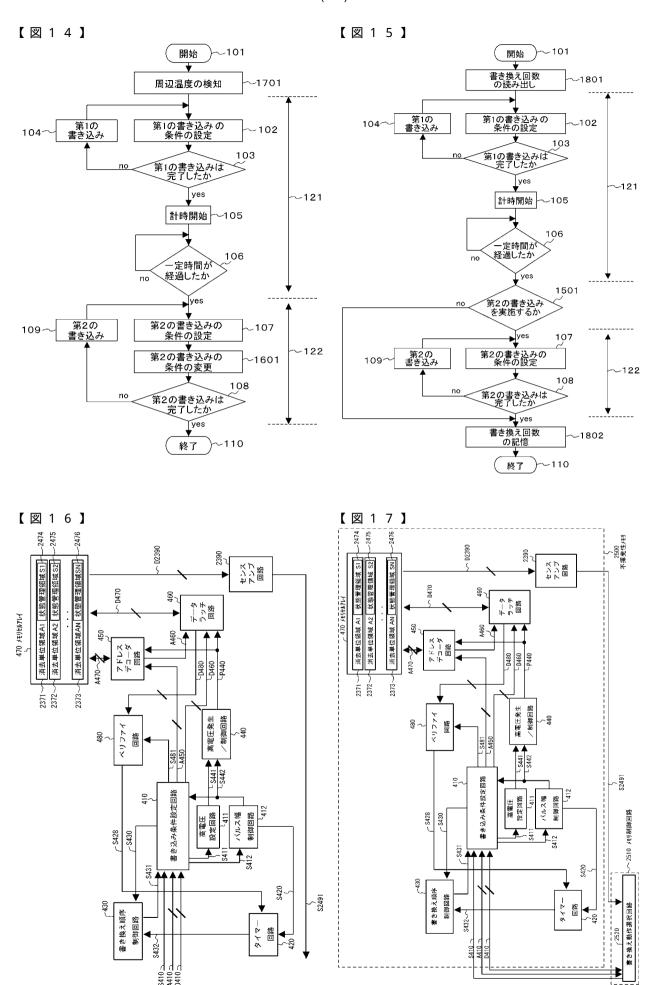

# [0105]

本実施形態は、図16の構成によって実現できる。図16は、本発明の第7の実施形態における不揮発性半導体記憶装置を示している。メモリセルアレイ470を消去単位領域A(1)2371~消去単位領域A(N)2373に分割し、前記各消去単位領域毎に状態管理領域S(N)2476を含み、更にセンスアンプ回路2390を含み、センスアンプ回路2390をメモリセルアレイ470とのデータバスD2390と状態信号出力S2491との間に接続すること以外は、図5と同様の構成を有する。

### [0106]

書き込みを行う場合の動作を説明する。まず、任意の消去単位領域 A ( 1 、 2 、・・・、N)に対する第 1 の書き込み動作について説明する。第 1 の書き込み動作時には各々該当する状態管理領域 S ( 1 、 2 、・・・、N )を消去する。

# [0107]

次に、任意の消去単位領域 A ( 1 、 2 、・・・、 N )に対する第 2 の書き込み動作について説明する。第 2 の書き込み動作時には各々該当する状態管理領域 S ( 1 、 2 、・・・、 N )にデータの書き込みを行う。

## [0108]

50

10

20

30

20

30

40

50

次に、任意の状態管理領域S(1、2、・・・、N)に書き込まれた状態の確認方法について説明する。書き込まれた状態の確認には任意の状態管理領域S(1、2、・・・、N)をアドレスデコーダ回路450により選択し、各々該当する状態管理領域S(1、2、・・・、N)のデータをデータバスD2390を経由しセンスアンプ回路2390によって読み出し、状態信号出力S2491に出力する。これにより、各々該当する消去単位領域A(1、2、・・・、N)が消去状態にあるか書き込み状態にあるかによって、消去単位領域毎に第2の書き込みまで完了しているか否かを判別することが可能となる。

### [0109]

なお、状態管理領域 S ( 1 、 2 、・・・、N )に対して該当消去単位領域への書き換え回数を書き込むデータとしてもよく、この場合には、消去単位領域毎の書き換え回数によっては、第 1 の書き込み完了後の第 2 の書き込みまでの待ち時間を短縮することができる

# [0110]

以上より図16の構成によれば、消去単位領域毎に状態管理領域を備えることで、領域毎に第1の書き込み後の状態か第2の書き込み後の状態かの判別が容易となり、制御性が向上する。また、状態管理領域に該当消去単位領域への書き換え回数を書き込むことで、消去単位領域毎の書き換え回数によっては、第1の書き込み完了後の第2の書き込みまでの待ち時間を短縮することができる。

#### [0111]

図17は、図16の不揮発性半導体記憶装置(不揮発性メモリ2500)を用いた電子機器を示している。不揮発性メモリ2500に電気的に接続されるメモリ制御回路2510を含み、前記メモリ制御回路2510内に書き換え動作選択回路2520を含み、前記書き換え動作選択回路2520に状態信号出力S2491を入力し、制御信号S410、アドレスバスA410、データバスD410を書き換え動作選択回路2520に接続すること以外は、図16と同様の構成を有する。

### [0112]

先に図16にて示したとおり、任意の消去単位領域 A (1、2、・・・、N )に対して 、第1の書き込み動作時には各々該当する状態管理領域S(1、2、・・・、N)を消去 し、任意の消去単位領域A(1、2、・・・、N)に対する第2の書き込み動作時には各 々該当する状態管理領域S(1、2、・・・、N)にデータの書き込みを行う。また、読 み出 し動作によって、状態管理領域 S ( 1 、 2 、・・・、N )に書き込まれた状態を確認 することにより、各々該当する消去単位領域A(1、2、・・・、N)が消去状態にある か書き込み状態にあるかによって、消去単位領域毎に第2の書き込みまで完了しているか 否かを判別することが可能となる。これらの動作を実施するために、不揮発性メモリ25 0 0 に対して、書き換え動作選択回路 2 5 2 0 から、第 1 の書き込み動作、第 2 の書き込 み動作、及び読み出し動作に必要な制御を制御信号 S 4 1 0 から入力し、アドレス信号を アドレスバスA410から入力し、データ入出力をデータバスD410を経由して行う。 また、状態管理領域S(1、2、・・・、N)に対して該当消去単位領域への書き換え回 数 を 書 き 込 む デ ー タ と し た 場 合 に は 、 消 去 単 位 領 域 A ( 1 、 2 、 ・ ・ 、 N ) 毎 の 書 き 換 え 回 数 が 状 態 信 号 出 力 S 2 4 9 1 を 経 由 し て 書 き 換 え 動 作 選 択 回 路 2 5 2 0 に 入 力 さ れ る よって、消去単位領域毎の書き換え回数によっては、第1の書き込み完了後の第2の書 き込みまでの待ち時間を短縮することが選択可能となる。あるいは、用途によっては、消 去単位領域毎に第1の書き込み完了後の第2の書き込み動作実施の有無を選択可能となる

### [0113]

以上より図17の構成によれば、消去単位領域毎の書き換え回数や市場での用途に応じて、第1の書き込み後の待ち時間の長さや第2の書き込みの有無を選択可能とすることで、信頼性向上や書き込み時間の抑制を最適化することが可能な電子機器を実現することが可能となる。

# [0114]

《第8の実施形態》

図18は、本発明の第8の実施形態における不揮発性半導体記憶装置の書き換え方法を示したフローチャートである。図18のフローチャートにおいて、1901は書き換え直前のデータ値の読み出しを実施する処理である。

[0115]

所定のメモリセルに対する書き込みフローは開始端子101から開始し、書き換え直前のデータ値の読み出しを実施する処理1901を経て、所望の第1の書き込み条件を設定する処理102へ進む。処理1901は例えば、データ"0"かデータ"1"かを判別する読み出しベリファイである。

[0116]

判断106において、時間計測を開始する処理105から、計測した時間が一定時間以上経過しているかを確認し、経過している場合は判断1501へ進む。判断1501において、書き換え直前のデータが"0"のとき、第2の書き込みを実施せず、終了端子110へ進み一連の書き込みフローが終了する。書き換え直前のデータが"0"のときは、電子とホールの結合は十分にされ、第1の書き込み後の初期変動による電荷ロス分が少ないため、第2の書き込みを実施しなくてもよく、書き込み時間を短縮できる。一方、書き換え直前のデータが"1"のとき、第2の書き込みを実施するために、第2の書き込みを実施する条件を設定する処理107へ進む。書き換え直前のデータが"1"のときは、電子とホールの結合は十分でなく、第1の書き込み後の初期変動による電荷ロス分が多いため、第2の書き込みを実施し、データ保持特性を向上させる。

[0117]

なお、書き換え直前のデータ値に応じて待ち時間を変化させてもよい。また、書き換え 直前のデータ値に応じて第2の電荷注入の電荷注入条件を変化させてもよい。

[ 0 1 1 8 ]

《第9の実施形態》

図19は、4値の多値メモリセルにおける閾値とメモリセル数の関係を示したものである。2001は消去状態のメモリセルであり、2002は第1の閾値電圧の書き込み状態のメモリセルであり、2004は第3の閾値電圧の書き込み状態のメモリセルであり、2004は第3の閾値電圧の書き込み状態のメモリセルである。消去状態、第1の閾値電圧、第2の閾値電圧、第3の閾値電圧の順に閾値が高くなっていく。

[0119]

図20は本発明の第9の実施形態における不揮発性半導体記憶装置の書き換え方法を示した図である。2005は消去を実施する処理であり、2006は第1の閾値電圧のメモリセルに対する第1の書き込みを実施する処理であり、2007は第2の閾値電圧のメモリセルに対する第1の書き込みを実施する処理であり、2009は第3の閾値電圧のメモリセルに対する第2の書き込みを実施する処理であり、2010は第2の閾値電圧のメモリセルに対する第2の書き込みを実施する処理であり、2010は第2の閾値電圧のメモリセルに対する第2の書き込みを実施する処理であり、2011は第1の閾値電圧のメモリセルに対する第2の書き込みを実施する処理であり、2011は第1の閾値電圧のメモリセルに対する第1の書き込み後の待ち時間であり、2011は第3の閾値電圧のメモリセルに対する第1の書き込み後の待ち時間であり、2011は第3の閾値電圧のメモリセルに対する第1の書き込み後の待ち時間である。

[0120]

所定のメモリセルに対する書き換えフローは消去を実施する処理 2 0 0 5 から開始し、第 1 の閾値電圧のメモリセルに対する第 1 の書き込みを実施する処理 2 0 0 6 を経て、第 2 の閾値電圧のメモリセルに対する第 1 の書き込みを実施する処理 2 0 0 7 を経て、第 3 の閾値電圧のメモリセルに対する第 1 の書き込みを実施する処理 2 0 0 8 へ進む。処理 2 0 0 5 はデータ書き換え前の消去であり、処理 2 0 0 6 は低い閾値電圧を設定するメモリセルへの第 1 の書き込みであり、処理 2 0 0 8 は別のより高い閾値電圧を設定するメモリセルへの第 1 の書き込みであり、処理 2 0 0 8 は別のより高い閾値電圧を設定するメモリ

10

20

30

40

セルへの第1の書き込みである。

# [0121]

処理2008を経て、第3の閾値電圧のメモリセルに対する第2の書き込みを実施する処理2009を経て、第2の閾値電圧のメモリセルに対する第2の書き込みを実施する処理2010を経て、第1の閾値電圧のメモリセルに対する第2の書き込みを実施する処理2011へ進む。処理2009は高い閾値電圧を設定するメモリセルへの第2の書き込みであり、処理2011は別のより低い閾値電圧を設定するメモリセルへの第2の書き込みであり、処理2011は別のより低い閾値電圧を設定するメモリセルへの第2の書き込みである。

## [0122]

ここで処理 2 0 1 1 と処理 2 0 0 6 の時間の差が 2 0 1 2 であり、第 1 の閾値電圧のメモリセルに対する第 1 の書き込み後の待ち時間である。同じく処理 2 0 1 0 と処理 2 0 0 7 の時間の差が 2 0 1 3 であり、第 2 の閾値電圧のメモリセルに対する第 1 の書き込み後の待ち時間である。同じく処理 2 0 0 9 と処理 2 0 0 8 の時間の差が 2 0 1 4 であり、第 3 の閾値電圧のメモリセルに対する第 1 の書き込み後の待ち時間である。

#### [ 0 1 2 3 ]

全てのメモリセルに対し同様のデータ保持特性の効果を得るためには、低い閾値電圧を設定するメモリセルに対しては、高い閾値電圧を設定するメモリセルより長い待ち時間を確保しなければならない。この構成によれば、高い閾値電圧を設定するメモリセルの書き込み時間を利用することで、本発明の実施による書き換え時間の増加を低減できる。

#### [ 0 1 2 4 ]

図 2 1 は、本発明の第 9 の実施形態の変形例を示した図である。これは、図 2 0 に対し、書き込みを実施するメモリセルの閾値電圧の順序を逆にしたものである。

### [ 0 1 2 5 ]

図21の方法によれば、設定する閾値電圧が高いほど長い待ち時間を確保することで、初期変動による電荷ロスの大きな閾値電圧の高いメモリセルのデータ保持特性を向上させると共に、低い閾値電圧を設定するメモリセルの書き込み時間を利用することで、本発明の実施による書き換え時間の増加を低減できる。

# [0126]

《第10の実施形態》

図 2 2 は、本発明の第 1 0 の実施形態における不揮発性半導体記憶装置の書き換え方法を示したフローチャートである。図 2 2 のフローチャートにおいて、 2 2 0 1 は開始端子、 2 2 1 1 は終了端子であり、また 2 2 0 3 から 2 2 0 6 、 2 2 0 8 から 2 2 1 0 は処理を示し、 2 2 0 2 、 2 2 0 7 は判断を示し、 2 2 1 2 、 2 2 1 3 は範囲を示す。

# [0127]

2 2 1 2 は消去前書き込みの範囲であり、2 2 1 3 がデータ書き込みの範囲である。2 2 0 2 は消去前書き込みの実施時に所定の閾値電圧レベルからの消去前書き込みであるかを判断する処理であり、2 2 0 7 は所定の閾値電圧レベルへのデータ書き込みであるかを判断する処理であり、2 2 0 3 、2 2 0 9 は第 1 の書き込みを実施する処理であり、2 2 0 4 、2 2 1 0 は第 2 の書き込みを実施する処理であり、2 2 0 6 は消去を実施する処理である。

### [0128]

図19に示すような3値以上の閾値電圧によってデータを記憶する多値の不揮発性メモリにおける書き換えについて説明する。開始端子2201から開始し、消去前書き込みの実施時に所定のレベルからの消去前書き込みであるかを判断する処理2202に進む。ここで所定のレベルとは例えば図19における第3の閾値電圧の書き込み状態のメモリセル2004のように、閾値電圧の最も高いレベルである。所定のレベルからの消去前書き込みである場合、所定レベルへの書き込み2205へ進み、そうでない場合、第1の書き込み2205とは例えば消去前書き込みレベルである。また消去前書き込みレベルが閾値電圧の最も

10

20

30

40

高いレベルと同じであるような場合は、所定レベルへの書き込み2205は省略することも可能である。また所定レベルからの消去前書き込みでない場合の第2の書き込み2204は、第2の実施形態でも説明のとおり電子とホールの結合によって低下したレベルを上昇させる必要がないので、省くことも可能である。

[ 0 1 2 9 ]

消去前書き込み2212が終了すると消去2206に進み、更にデータ書き込み2213の所定のレベルへのデータ書き込みであるかの判断2207に進む。ここで所定のレベルは基本的に消去前書き込みにおける判定2202で用いたレベルと同じ、例えば図19における第3の閾値電圧の書き込み状態のメモリセル2004のような、閾値電圧の最も高いレベルである。所定のレベルへのデータ書き込みである場合、第1の書き込み2209そして第2の書き込み2210へ進み、そうでない場合、所定レベルへの書き込み2208へと進む。データ書き込み2213が終了すると終了端子2211に進む。

[0130]

本書き換え方法は、多値で設定する閾値電圧レベルに応じて消去前書き込みあるいはデータ書き込みのいずれかで本発明を適用するものである。例えば、低い閾値電圧レベルに設定されるメモリセルに対しては、データ書き込みで本発明を適用する効果は必要な時間と比べ少ないので実施せずに、消去前書き込みのみで実施する。また逆に高い閾値電圧レベルに設定されるメモリセルに対しては、データ書き込みで本発明を適用することで、データ保持期間における特性の向上が図れるので実施し、消去前書き込みでは効果自体が少ないので実施しない。これによって全ての閾値レベルに設定される多値メモリセルに同等の効果を得ることができ、書き換え時間の増加を最小限にとどめたうえで、電荷保持特性の向上、書き換え回数の向上が多値メモリにおいても実現できる。

[0131]

更に高い閾値電圧レベルに設定されるメモリセルへの本発明の適用において、図21の 実施形態のように、高い閾値値電圧レベルを設定するメモリセルに対して第1の書き込み をまず実施し、第1の書き込みに付属の待ち時間の間に、低い閾値電圧レベルを設定する メモリセルの書き込みをすることで、書き換え時間の増加を抑え、より効率良いデータ保 持特性の向上が実現できる。

【産業上の利用可能性】

[0132]

以上説明してきたとおり、本発明によれば、メモリセルのデータ保持特性の向上が図れ トラップ層を有する不揮発性メモリなどとして有用である。

【図面の簡単な説明】

[ 0 1 3 3 ]

【図1】第1の実施形態における不揮発性半導体記憶装置の書き換え方法を示す図である

【図2】第1の実施形態における不揮発性半導体記憶装置のトラップされた電荷の挙動を示す図である。

【 図 3 】 第 1 の実施形態における不揮発性半導体記憶装置のメモリセル閾値電圧の変化を示す図である。

【図4】第1の実施形態を説明するための多値メモリのメモリセル閾値電圧分布の図である。

【図5】第1の実施形態における不揮発性半導体記憶装置の回路構成を示す図である。

【図6】第2の実施形態における不揮発性半導体記憶装置の書き換え方法を示す図である

【図7】第2の実施形態における不揮発性半導体記憶装置のトラップされた電荷の挙動を示す図である。

【図8】第3の実施形態における不揮発性半導体記憶装置の書き換え方法を示す図である

【図9】第4の実施形態における不揮発性半導体記憶装置の書き換え方法を示す図である

20

30

40

- 【図10】第5の実施形態における不揮発性半導体記憶装置の書き換え方法を示す図であ る。

- 【図11】第5の実施形態の変形例を示す図である。

- 【図12】第5の実施形態の他の変形例を示す図である。

- 【図13】第5の実施形態における不揮発性半導体記憶装置の回路構成を示す図である。

- 【図14】第6の実施形態における不揮発性半導体記憶装置の書き換え方法を示す図であ

- 【図15】第7の実施形態における不揮発性半導体記憶装置の書き換え方法を示す図であ

- 【図16】第7の実施形態における不揮発性半導体記憶装置の回路構成を示す図である。

- 【図17】第7の実施形態における不揮発性半導体記憶装置を用いた電子機器の回路構成 を示す図である。

- 【図18】第8の実施形態における不揮発性半導体記憶装置の書き換え方法を示す図であ

- 【 図 1 9 】 第 9 の 実 施 形 態 を 説 明 す る た め の 多 値 メ モ リ の メ モ リ セ ル 閾 値 電 圧 分 布 の 図 で ある。

- 【図20】第9の実施形態における不揮発性半導体記憶装置の書き換え方法を示す図であ

- 【図21】第9の実施形態の変形例を示す図である。

- 【 図 2 2 】 第 1 0 の 実 施 形 態 に お け る 不 揮 発 性 半 導 体 記 憶 装 置 の 書 き 換 え 方 法 を 示 す 図 で ある。

- 【図23】従来の不揮発性半導体記憶装置のメモリセル構造を示す図である。

- 【図24】従来の不揮発性半導体記憶装置のトラップされた電荷の挙動を示す図である。

- 【符号の説明】

- [ 0 1 3 4 ]

- 2 0 1 第1の書き込み直後のメモリセル閾値電圧の分布

- 2 0 2 一定時間経過後のメモリセル閾値電圧の分布

- 2 0 3 一定時間経過後に第2の書き込みを実施した直後のメモリセル閾値電圧の分布

- 2 0 4 寿命末期のメモリセル閾値電圧の分布

- 2 0 5 書き込みベリファイレベル

- 2 1 1 第1の書き込みにより注入した電子の確率密度分布

- 2 1 2 第 1 の書き込み以前の消去により注入したホールの確率密度分布

- 2 2 1 ホールと結合した後の電子の確率密度分布

- 2 2 2 電子と結合した後のホールの確率密度分布

- 2 3 1 ホールと結合した後に第2の書き込みにより注入した電子の確率密度分布

- 2 3 2 電子と結合した後のホールの確率密度分布

- 寿命末期の電子の確率密度分布 2 4 1

- 3 0 1 従来の閾値変動

- 3 0 2 本発明における閾値変動

- 3 0 3 読み出しレベル

- 3 1 1 従来の閾値変動量の書き換え回数依存性

- 3 1 2 本発明における閾値変動量の書き換え回数依存性

- 4 1 0 書き込み条件設定回路

- 4 1 1 高電圧設定回路

- 4 1 2 パルス幅制御回路

- 4 2 0 タイマー回路

- 4 3 0 書き換え順序制御回路

- 4 4 0 高電圧発生/制御回路

- 4 5 0 アドレスデコーダ回路

20

30

40

```

4 6 0 データラッチ回路

```

- 470 メモリセルアレイ

- 480 ベリファイ回路

- 9 0 1 多値メモリにおける 1 番目のレベルのデータのメモリセル閾値電圧の分布

- 902 多値メモリにおける2番目のレベルのデータのメモリセル閾値電圧の分布

- 903 多値メモリにおける3番目のレベルのデータのメモリセル閾値電圧の分布

- 904 多値メモリにおける4番目のレベルのデータのメモリセル閾値電圧の分布

- 1000 消去前書き込み直前のメモリセル閾値電圧の分布(データ"1")

- 1001 消去前書き込み直前のメモリセル閾値電圧の分布(データ"0")

- 1 0 0 2 消去前書き込みにおける、第 1 の書き込み後のメモリセル閾値電圧の分布

- 1003 一定時間経過後のメモリセル閾値電圧の分布

- 1004 消去ベリファイレベル

- 1005 書き込みベリファイレベル

- 1011,1021,1031 データ"0"側の電子の確率密度分布

- 1 0 1 2 , 1 0 2 2 , 1 0 3 2 データ"0"側のホールの確率密度分布

- 2 0 0 1 消去状態のメモリセル

- 2002 第1の閾値電圧の書き込み状態のメモリセル

- 2003 第2の閾値電圧の書き込み状態のメモリセル

- 2004 第3の閾値電圧の書き込み状態のメモリセル

- 2 3 2 1 時間管理回路

- 2 3 7 1 ~ 2 3 7 3 消去単位領域

- 2 3 7 4 ~ 2 3 7 6 時間管理領域

- 2 3 9 0 センスアンプ回路

- 2 4 7 4 ~ 2 4 7 6 状態管理領域

- 2 5 0 0 不揮発性メモリ

- 2 5 1 0 メモリ制御回路

- 2520 書き換え動作選択回路

- 3 0 0 1 半導体基板

- 3 0 0 2 チャネル領域

- 3003 第1の不純物領域

- 3004 第2の不純物領域

- 3 0 0 5 トップ絶縁膜

- 3006 トラップ層

- 3 0 0 7 ボトム絶縁膜

- 3 0 0 8 ゲート電極

- S 2 4 9 1 状態信号出力

10

【図1】

【図3】

(a)

【図4】

【図5】

# 【図6】

### 【図7】

# 【図8】

# 【図9】

~110

終了

S432~

2410 4410 441

> 2321

【図19】

# フロントページの続き

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(74)代理人 100124671

弁理士 関 啓

(74)代理人 100131060

弁理士 杉浦 靖也

(72)発明者 土岐 和啓

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 永井 裕康

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 三角 賢治

大阪府門真市大字門真1006番地 松下電器産業株式会社内

(72)発明者 小谷 秀人

大阪府門真市大字門真1006番地 松下電器産業株式会社内

F ターム(参考) 5B125 BA02 BA19 CA27 CA28 DB08 DB16 DC09 DE11 EB02 EB04 EB09 FA01 FA05