#### (19) **日本国特許庁(JP)**

# (12)公表特許公報(A)

(11)特許出願公表番号

特表2014-501009 (P2014-501009A)

(43) 公表日 平成26年1月16日(2014.1.16)

(51) Int.Cl. F I テーマコード (参考)

**GO 6 F 9/30 (2006.01)** GO 6 F 9/30 3 5 O B 5 B O 3 3 **GO 6 F 15/173 (2006.01)** GO 6 F 15/173 6 5 O S 5 B O 4 5

# 審查請求 未請求 予備審查請求 未請求 (全 30 頁)

(21) 出願番号 特願2013-540074 (P2013-540074) (86) (22) 出願日 平成23年11月18日 (2011.11.18) (85) 翻訳文提出日 平成25年7月16日 (2013.7.16)

(86) 国際出願番号 PCT/US2011/061487 (87) 国際公開番号 W02012/068513

(87) 国際公開日 平成24年5月24日 (2012.5.24)

(31) 優先権主張番号 61/415,210

(32) 優先日 平成22年11月18日 (2010.11.18)

(33) 優先権主張国 米国 (US) (31) 優先権主張番号 61/415, 205

(32) 優先日 平成22年11月18日 (2010.11.18)

(33) 優先権主張国 米国 (US) (31) 優先権主張番号 13/232,774

(32) 優先日 平成23年9月14日 (2011.9.14)

(33) 優先権主張国 米国(US)

(71) 出願人 390020248

日本テキサス・インスツルメンツ株式会社 東京都新宿区西新宿六丁目24番1号

(71) 出願人 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265 -5474 ダラス メイル ステイショ ン 3999 ピーオーボックス 655

474

(74)上記1名の代理人 100098497

弁理士 片寄 恭三

最終頁に続く

(54) 【発明の名称】データを移動させるための方法及び装置

#### (57)【要約】

計算ユニット(4308-1~4308-M、760 7-1~7607-P)内の第1のレジスタファイル( 4358-1~4358-8、7902)からプロセッ サ(4322、7614)内の第2のレジスタファイル (5206) ヘデータを移動するための方法が提供され る。データ移動リード(risc\_is\_mfvvr) 上の信号の状態が、計算ユニット内の第1のレジスタフ ァイルからプロセッサ内の第2のレジスタファイルへの データ移動命令を示すように変更される。プロセッサか ら計算ユニットに第1のアドレスリード(risc\_i s ra) でレーンアドレスが提供される。プロセッサ から計算ユニットに第2のアドレスリード(risc\_ is\_ra)で読み出しアドレスが提供され、計算ユニ ット内の第1のレジスタファイルからプロセッサ内の第 2のレジスタファイルにデータインタフェースリード( node\_regf\_rd)でデータが伝送される。

FIG. 4A FIG. 4B

FIG. 4

#### 【特許請求の範囲】

## 【請求項1】

装置であって、

第 1 のレジスタファイル ( 4 3 5 8 - 1 ~ 4 3 5 8 - 8 、 7 9 0 2 ) を有する計算ユニット ( 4 3 0 8 - 1 ~ 4 3 0 8 - M 、 7 6 0 7 - 1 ~ 7 6 0 7 - P ) 、及び

前記計算ユニットに結合されるプロセッサ(4322、7614)であって、前記第1のレジスタファイルからのデータ移動命令(MFVRC)を有する命令セットを含み、且つ圧縮する、前記プロセッサ、

を特徴とし、

前記プロセッサが、

第2のレジスタファイル(5206)と、

前記第1のレジスタファイルのための書き込みアドレスを示すためのアドレスリード(risc\_is\_ra)と、

データを伝送するためのデータインタフェースリード( n o d e \_ r e g f \_ r d ) と

データ移動リード(risc\_is\_mfvre)であって、前記データ移動リード上の信号の状態が変更されるとき、前記第1のレジスタファイルから前記第2のレジスタファイルへの前記データ移動命令を示すための、前記データ移動リードと、

を含む、装置。

# 【請求項2】

請求項1に記載の装置であって、前記アドレスリード(risc\_is\_ra)が複数の第2のアドレスリード(risc\_is\_ra)を更に特徴とする、装置。

#### 【請求項3】

請求項 2 に記載の装置であって、前記複数の第 2 のアドレスリード(risc\_is\_ra)が 5 ビット幅である、装置。

#### 【請求項4】

請求項1、2、又は3に記載の装置であって、前記プロセッサが、上位ハーフ書き込み、下位ハーフ書き込み、フル書き込み、又は読み出し、のいずれを実行するかを示すためのハーフワードリード(risc\_is\_hwz)を含む装置。

## 【請求項5】

請求項1、2、3、又は4に記載の装置であって、前記ハーフワードリード(risc\_is\_hwz)が複数のハーフワードリード(risc\_is\_hwz)を更に特徴とする装置。

## 【請求項6】

請求項 5 に記載の装置であって、前記複数のハーフワードリードが 2 ビット幅である装置。

# 【請求項7】

請求項1、2、3、4、5、又は6に記載の装置であって、前記データインタフェースリード(node\_regf\_rd)が、複数のデータインタフェースリード(node\_regf\_rd)を更に特徴とする装置。

# 【請求項8】

請求項1、2、3、4、5、6、又は7に記載の装置であって、前記計算ユニットが、 複数の単一入力多重データ(SIMD)機能ユニット(4308-1~4308-M)を 更に特徴とする装置。

#### 【請求項9】

請求項 1 、 2 、 3 、 4 、 5 、 6 、又は 7 に記載の装置であって、前記計算ユニットが、 複数のベクトルユニット( 7 6 0 7 - 1 ~ 7 6 0 7 - P)を更に特徴とする装置。

## 【請求項10】

方法であって、

計算ユニット(4308-1~4308-M、7607-1~7607-P)内の第1

10

20

30

30

40

のレジスタファイル(4358-1~4358-8、7902)からプロセッサ(432 2、7614)内の第2のレジスタファイル(5206)へのデータ移動命令(MFVR C)を示し、且つ前記第2のレジスタファイルへ圧縮するように、データ移動リード(r isc\_is\_mfvre)上の信号の状態を変更することと、

前記プロセッサから前記計算ユニットにアドレスリード( r i s c \_ i s \_ r a )で書き込みアドレスを提供することと、

前記計算ユニット内の前記第1のレジスタファイルから前記プロセッサ内の前記第2のレジスタファイルにデータインタフェースリード(node\_regf\_rd)でデータを伝送することと、

を特徴とする方法。

## 【請求項11】

請求項10に記載の方法であって、前記アドレスリード(risc\_is\_ra)が複数の第2のアドレスリード(risc\_is\_ra)を更に特徴とする方法。

#### 【請求項12】

請求項10又は11に記載の方法であって、ハーフワードリード(risc\_is\_hw z )で、上位ハーフ書き込み、下位ハーフ書き込み、フル書き込み、又は読み出しのいずれを実行するかを示すことを更に特徴とする方法。

# 【請求項13】

請求項10、11、又は12に記載の方法であって、前記ハーフワードリード(risc\_is\_hwz)が、複数のハーフワードリード(risc\_is\_hwz)を更に特徴とする方法。

#### 【請求項14】

請求項10、11、12、又は13に記載の方法であって、前記データインタフェースリード(node\_regf\_rd)が複数のデータインタフェースリード(node\_regf\_rd)を更に特徴とする方法。

#### 【請求項15】

システムであって、

計算ユニット(4308-1~4308-M、7607-1~7607-P)内の第1のレジスタファイル(4358-1~4358-8、7902)からプロセッサ(4322、7614)内の第2のレジスタファイル(5206)へのデータ移動命令(MFVRC)を示し、且つ前記第2のレジスタファイルへ圧縮するように、データ移動リード(risc\_is\_mfvre)上の信号の状態を変更するための手段と、

前記プロセッサから前記計算ユニットにアドレスリード(risc\_is\_ra)で書き込みアドレスを提供するための手段と、

前記計算ユニット内の前記第1のレジスタファイルから前記プロセッサ内の前記第2のレジスタファイルにデータインタフェースリード(node\_regf\_rd)でデータを伝送するための手段と、

を特徴とするシステム。

### 【請求項16】

請求項15に記載のシステムであって、前記アドレスリード(risc\_is\_ra) が複数の第2のアドレスリード(risc\_is\_ra)を更に特徴とするシステム。

#### 【請求項17】

請求項15又は16に記載のシステムであって、ハーフワードリード(risc\_is \_hwz)上で、上位ハーフ書き込み、下位ハーフ書き込み、フル書き込み、又は読み出 しのいずれを実行するかを示すための手段を更に特徴とするシステム。

# 【請求項18】

請求項15、16、又は17に記載のシステムであって、前記ハーフワードリード(risc\_is\_hwz)が、複数のハーフワードリード(risc\_is\_hwz)を更に特徴とするシステム。

### 【請求項19】

40

10

20

30

請求項15、16,17、又は18に記載のシステムであって、前記データインタフェースリード(node\_regf\_rd)が、複数のデータインタフェースリード(node\_regf\_rd)を更に特徴とするシステム。

【発明の詳細な説明】

【技術分野】

[0001]

本開示は、全般的にプロセッサに関し、より具体的には処理クラスタに関する。

【背景技術】

[0002]

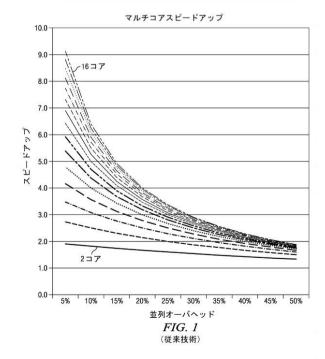

図1はマルチコアシステム(2~16コアの範囲)についての実行速度のスピードアップ対並列オーバーヘッドを示すグラフである。スピードアップとは、単一プロセッサの実行時間を並列プロセッサの実行時間で除したものである。図からわかるように、多数のコアから有意な利益を得るために、並列オーバーヘッドはゼロに近くなければならない。しかし並列プログラム間に何らかの相互作用が存在する場合、オーバーヘッドは極めて高くなる傾向があるため、完全に分離されたプログラムでなければ2又は3以上のプロセッサを効率的に使用するのは通常極めて難しい。従って、改善された処理クラスタが必要とされている。

#### 【発明の概要】

[00003]

従って、本開示の実施形態は方法を提供する。その方法は下記を特徴とする。すなわち、計算ユニット(4308-1~4308-M、7607-1~7607-P)内の第1のレジスタファイル(4358-1~4358-8、7902)からプロセッサ(4322、7614)内の第2のレジスタファイル(5206)へのデータ移動命令を示すように、データ移動リード(risc\_is\_mfvvr)上の信号の状態を変更することと、プロセッサ(4322、7614)から計算ユニット(4308-1~4308-M、7607-1~7607-P)に第1のアドレスリード(risc\_is\_ua)でレーンアドレスを提供することと、プロセッサ(4322、7614)から計算ユニット(4308-1~4308-M、7607-1~7607-P)に第2のアドレスリード(risc\_is\_ra)で読み出しアドレスを提供することと、計算ユニット(4308-1~4308-M、7607-1~7607-P)内の第1のレジスタファイル(4358-1~4358-8、7902)からプロセッサ(4322、7614)内の第2のレジスタファイル(5206)にデータインタフェースリード(node\_regf\_rd)でデータを伝送すること、である。

【図面の簡単な説明】

[0004]

【図1】マルチコアのスピードアップパラメータのグラフである。

[0005]

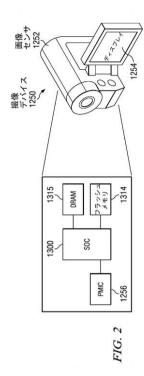

【 図 2 】 本 開 示 の 実 施 形 態 に 従 っ た シ ス テ ム の 図 で あ る 。

[0006]

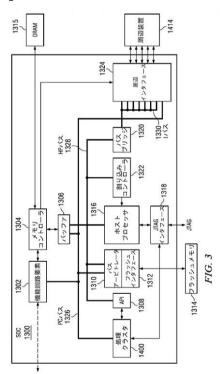

【図3】本開示の実施形態に従ったSOCの図である。

[0007]

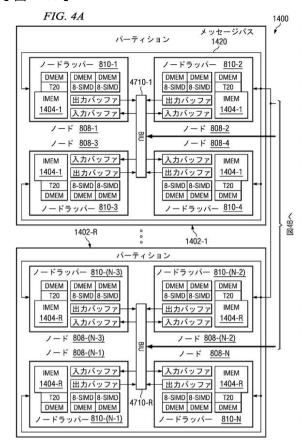

【図4A】本開示の実施形態に従った並列処理クラスタの図である。

【 図 4 B 】 本 開 示 の 実 施 形 態 に 従 っ た 並 列 処 理 ク ラ ス タ の 図 で あ る 。

[0008]

【 図 5 】 処 理 ク ラ ス タ 内 の ノ ー ド 又 は 計 算 要 素 の 一 部 分 の 図 で あ る 。

【図6A】処理クラスタ内のノード又は計算要素の一部分の図である。

【図6B】処理クラスタ内のノード又は計算要素の一部分の図である。

[0009]

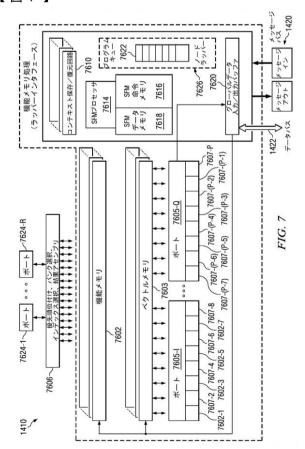

【図7】共有機能メモリのブロック図である。

[0010]

50

10

20

30

20

30

40

50

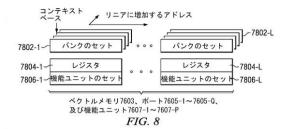

【図8】共有機能メモリのためのSIMDデータパスの図である。

[0011]

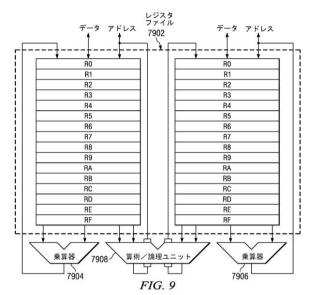

【図9】1つのSIMDデータパスの一部分の図である。

[0012]

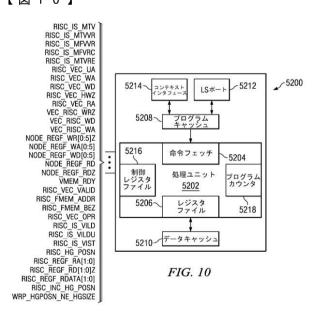

【図10】ノードプロセッサ又はRISCプロセッサのより詳細な図である。

[0013]

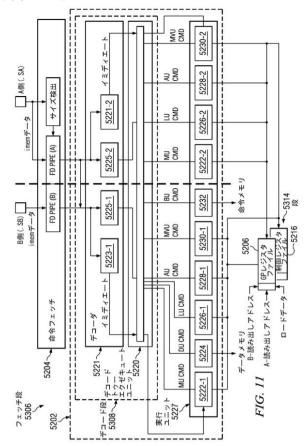

【図 1 1 】ノードプロセッサ又は R I S C プロセッサのためのパイプラインの一部分の例の図である。

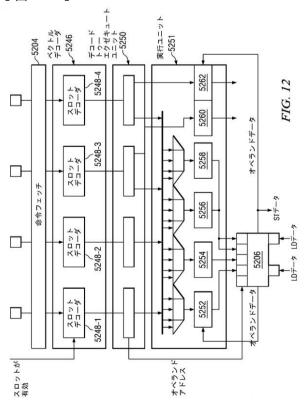

【図 1 2 】ノードプロセッサ又は R I S C プロセッサのためのパイプラインの一部分の例の図である。

【発明を実施するための形態】

[0014]

図2では、並列処理を実行するSOC用アプリケーションの例が見られる。この例では、撮像デバイス1250が示される。この(例えば携帯電話又はカメラであり得る)撮像デバイス1250は、概して、画像センサ1252、SOC1300、ダイナミックランダムアクセスメモリ(DRAM)1315、フラッシュメモリ1314、ディスプレイ1254、及び電力管理集積回路(PMIC)1256を含む。動作では、画像センサ1252は、(静止画像又はビデオであり得る)画像情報を捕捉することができ、この画像情報はSOC1300及びDRAM1315によって処理され得、不揮発性メモリ(即ち、フラッシュメモリ1314)に保存され得る。また、フラッシュメモリ1314に保存される画像情報は、SOC1300及びDRAM1315の使用によって、ディスプレイ1254上で使用するために表示され得る。また、撮像デバイス1250は、可搬型であることが多く、電源としてバッテリを含む。(SOC1300によって制御され得る)PMIC1256は、バッテリ寿命を長持ちさせるために電力使用量の調整を補助し得る。

[0015]

図3では、本開示の実施形態に従ったシステムオンチップ又はSOC1300の例が図 示されている。この(典型的には、OMAP(登録商標)等の集積回路又はICである) S О С 1 3 0 0 は、 (概 して 上述 の 並 列 処 理 を 実 行 す る ) 処 理 ク ラ ス タ 1 4 0 0 、 及 び 、 (上で説明及び参照された)ホスト環境を提供するホストプロセッサ1316を概して含 む。 ホストプロセッサ 1 3 1 6 は、ワイド(即ち、 3 2 ビット、 6 4 ビット等)RISC プロセッサ (例えばARM Cortex - A9等) であり得、バスアービトレータ13 1 0 、バッファ 1 3 0 6 、 ( ホストプロセッサ 1 3 1 6 がインタフェースバス又はIバス 1330上で周辺インタフェース1324にアクセスすることを許可する)バスブリッジ 1 3 2 0 、ハードウェアアプリケーションプログラミングインタフェース(API)13 08、及び割り込みコントローラ1322と、ホストプロセッサバス又はHPバス132 8上で通信する。処理クラスタ1400は、典型的に、(例えば、荷電結合デバイス、又 は C C D イン タフェースであり 得、 オフチップデバイスと通信し得る) 機能 回路要素 1 3 0 2 、バッファ 1 3 0 6 、バスアービトレータ 1 3 1 0 、及び周辺インタフェース 1 3 2 4 と、 処 理 ク ラ ス タ バ ス 又 は P C バ ス 1 3 2 6 上 で 、 通 信 す る 。 こ の 構 成 を 用 い て 、 ホ ス トプロセッサ 1 3 1 6 は、API1308を介して情報を提供する(即ち、所望の並列実 装に適合するように処理クラスタ1400を構成する)ことができ、一方、処理クラスタ 1 4 0 0 及びホストプロセッサ 1 3 1 6 はいずれも、(フラッシュインタフェース 1 3 1 2 を介して) フラッシュメモリ1314に、(メモリコントローラ1304を介して) D RAM1315に、直接アクセスできる。また、Joint Test Action Group(JTAG)インタフェース1318を介して、テスト及びバウンダリスキャ ンが実行され得る。

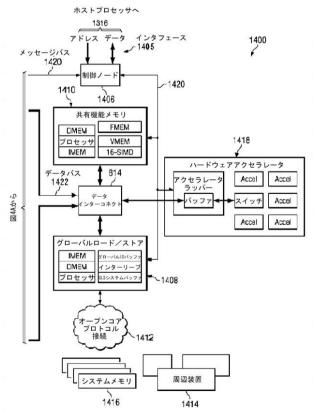

[0016]

図4を参照すると、本開示の実施形態に従った並列処理クラスタ1400の例が示されている。典型的には、処理クラスタ1400はハードウェア722に対応する。処理クラスタ1400は、概して、パーティション1402-1~1402-Rを含む。これらは

20

30

40

50

、ノード808-1~808-N、ノードラッパー810-1~810-N、命令メモリ1404-1~1404-R、及び(以下で詳しく説明する)バスインタフェースコニット又は(BIU)4710-1~4710-Rを含む。ノード808-1~808-Nは、各々データインターコネクト814に(各々のBIU4710-1~4710-R及びデータバス1422を介して)結合され、パーティション1402-1~1402-Rのための制御及びメッセージが制御ノード1406からメッセージ1420を介して提供される。また、グローバルロード/ストア(GLS)ユニット1408及び共有機能と明1410は、(後述のように)データ移動のための付加的な機能を提供する。それに加えて、レベル3又はL3キャッシュ1412、(概して、IC内には含まれない)周並で、レベル3又はL3キャッシュメモリ1314及び/又はDRAM1315、近に50C1300内に含まれないその他のメモリである)メモリ1416、及びハードウェアアクセラレータ(HWA)ユニット1418が処理クラスタ1400と共に用いられる。また、データ及びアドレスを制御ノード1406に通信するように、インタフェース1405が提供される。

### [0017]

処理クラスタ1400は、概して、データ伝送のために「プッシュ」モデルを使用する。データ伝送は要求応答型のアクセスではなく、概してポステッドライトとして現れる。これは、データ伝送が一方向であるため要求応答アクセスに比べてグローバルインターネクト(即ち、データインターコネクト814)の占有を2分の1に減らすという利点を有する。概して、インターコネクト814を介して要求をルーティングし、その後、応答が要求元へルーティングされ、その結果インターコネクト814上で2つの遷移が生成されることは望まれない。プッシュモデルは単一伝送を生成する。これは、ネットワークサイズが増大するとネットワークレイテンシが増大するため、またこのことが要求応答型トランザクションのパフォーマンスを低下させることは避けられないことであるため、スケーラビリティに関して重要である。

#### [0018]

プッシュモデルは、データフロープロトコル(即ち、812-1~812-N)と同様に、グローバルデータトラフィックを、正確さのために用いられるものまで概して最小化する一方、ローカルノードの利用率に対するグローバルデータフローの影響も概して最小化中する。大量のグローバルトラフィックであってもノード(即ち、808-i)のパフォーマンスに対する影響は、通常、皆無に近い。ソースはデータを(後述する)グローバル出力バッファに書き込み、伝送成功の確認を要求することなく継続する。データフロープロトコル(即ち、812-1~812-N)は、概して、インターコネクト814で単一伝送を用い、データをあて先へ移動する最初の試みでの伝送が成功することを確実にする。(後述する)グローバル出力バッファは(例えば)最大16出力まで保持することにをできるため、出力のための瞬時グローバル帯域幅が不充分になることに起因するノード(即ち、808-i)のストールの可能性が非常に低くなる。更に、瞬時帯域幅は、要求応答トランザクション又は伝送失敗の繰り返しによる影響を受けない。

## [0019]

最後に、プッシュモデルはプログラミングモデルに一層密接に適合する。言い換えるとプログラムは自己データを「フェッチ」せずに、その代わりに、プログラムの入力変数及び/又はパラメータは呼び出される前に書き込まれる。プログラミング環境では、入力変数の初期化は、ソースプログラムによるメモリへの書き込みとして行われる。処理クラスタ1400内では、これらの書き込みがポステッドライトに変換され、変数の値をノードコンテキストにポピュレートさせる。

# [0020]

(後述する)グローバル入力バッファは、ソースノードからデータを受け取るために用いられる。各ノード808-1~808-Nのためのデータメモリが単一ポートであるため、入力データの書き込みが、ローカルの単一入力多重データ(SIMD)による読み出しとコンフリクトすることがあり得る。入力データをグローバル入力バッファへ受け入れ

20

30

40

50

、そこで入力データが空きのデータメモリサイクルを待つことができることによって、この競合は回避される(即ち、SIMDアクセスとのバンクコンフリクトはない)。データメモリは、(例えば)32バンクを有し得るため、直ちにバッファがフリーになる可能性が非常に高い。しかしながら、伝送を確認するためのハンドシェイキングがないので、ノード(即ち、808‐i)はフリーのバッファエントリを持つはずである。所望とされる場合は、グローバル入力バッファは、バッファ位置をフリーにするために、ローカルノード(即ち、808‐i)をストールさせてデータメモリに強制的に書き込みを行うことができるが、このイベントは極めて希であるべきである。典型的には、グローバルカガデータメモリへ読み出されるべき状態にある間、他方がグローバルデータを書き込むための状態になり得るようにする。メッセージングインターコネクトは、グローバルデータインターコネクトとは分かれているが、同様にプッシュモデルを使用する。

[0021]

システムレベルでは、所望のスループットにスケーリングされた多数のノードを備えるSMP又は対称型多重処理のように、ノード808-1~808-Nが処理クラスタ1400は極めて多数のノードにまでスケーリングによってスケーリングが処理クラスタ14000は極めて多数のノードにまでスケーリングにがループ分けされ、各パーティションは1つ又は複数のノードを有する。パーティションは1つ又は複数のノードを有する。パーティションは1つ又は複数のノードを有する。パーティシコびり入きなプログラムで一層大量の出力データを計算させることによってスケーラビィインスを促進し、その結果、所望のスループット要件を達成する可能性を更に高めるのパーティション(即ち、1404-i)内のノードは、排他的命令メモリを用いる各ノードから共通命令メモリを用いる子とは、パーティション(即ち、1404-i)内のノードは、排他的命令メモリを用いると、1404-i)を共有することができる。の非他的バンクを有することができる。ノードが命令メモリ(即ち、1404-i)を共有するとき、それらのノードは、概して、同じプログラムを同期的に実行する。

[ 0 0 2 2 ]

また、処理クラスタ1400は非常に多数のノード(即ち、808-i)及びパーティション(即ち、1402-i)をサポートし得る。しかしながら、1つのパーティションについて4以上のノードを持つと概してノンユニフォームメモリアクセス(NUMA)アーキテクチャに類似するため、パーティション毎のノードの数は通常は4つに限定されている。この例では、パーティションは、(後でインターコネクト814に関連して説明する)1つ(又は複数)のクロスバーを介して接続される。クロスバーは概して横断帯域にが一定している。処理クラスタ1400は、現在、サイクル毎に1ノード幅のデータ(例えば、64、16ビットピクセル)を伝送するように設計されており、4サイクルに亘り、1サイクルにつき16ピクセルの4伝送に区分される。処理クラスタ1400は、概して、レイテンシトレラントであり、インターコネクト814がほぼ飽和(この状態を達成するのは合成プログラム以外では極めて難しいことに留意されたい)であっても、ノードストールを防止する。

[ 0 0 2 3 ]

典型的には、処理クラスタ1400はパーティション間で共有する下記のグローバルリソースを含む。

(1) 制御ノード1406。これは(メッセージバス1420で)システムワイドの メッセージングインターコネクト、イベント処理及びスケジューリング、及びホストプロ セッサ及びデバッガ(これらは全て後で詳しく説明する)へのインタフェースを提供する

(2) GLSユニット1408。これはプログラマブル縮小命令セット(RISC) プロセッサを含み、システムデータ移動を可能にする。システムデータ移動は、GLSデ

20

30

40

50

ータ移動スレッドとして直接コンパイルされ得る C + + プログラムによって記述され得る。これによって、ソースコードを修正することなく、クロスホスト環境でのシステムコードの実行が可能になり、また、システム又は(後述する) S I M D データメモリ内の任意のアドレス(変数)のセットに移動できるため、ダイレクトメモリアクセスよりもより一般的である。 G L S ユニット 1 4 0 8 は、(例えば) 0 - サイクルのコンテキストスイッチを備え、マルチスレッド化され、例えば、最大 1 6 スレッドまでサポートする。

(3) 共有機能メモリ1410。これは、一般のルックアップテーブル(LUT)及び統計収集機能(ヒストグラム)を提供する大型共有メモリである。また、これは大型共有メモリを使用して、リサンプリング及び歪補正等のノードSIMDにより(コストの理由で)充分サポートされていないピクセル処理をサポートし得る。この処理はネイティブタイプとして、スカラ、ベクトル、及び2Dアレイを実装する(例えば)6発行命令RISCプロセッサ(即ち、後で詳しく説明するSFMプロセッサ7614)を用いる。

(4) ハードウェアアクセラレータ1418。これは、プログラマビリティを必要としない機能のため、或いは電力及び/又は面積を最適化するために組み込まれ得る。アクセラレータは、サブシステムにはシステム内の他のノードとして現れ、制御及びデータフローに参加し、イベントを作成可能であり、スケジューリング可能である。またデバッガにとっては可視的である。(ハードウェアアクセラレータは、適用可能であるときは、専用のLUT及び統計収集を有し得る。)

(5) データインターコネクト814及びシステムオープンコアプロトコル(OCP)L3接続1412。これらは、ノードパーティション、ハードウェアアクセラレータ、及びシステムメモリ、及び、データバス1422上の周辺装置の間のデータ移動を管理する。(ハードウェアアクセラレータは、L3へのプライベート接続も有し得る)。

(6) デバッグインタフェース。これらは、図には示されていないが、本明細書中に記載される。

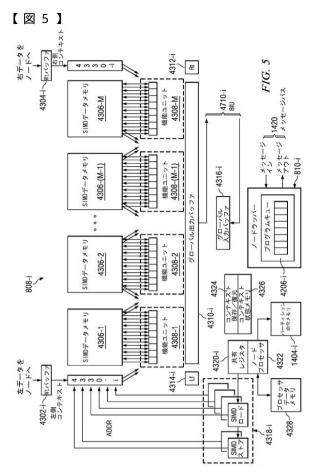

#### [0024]

図 5 を参照すると、ノード 8 0 8 - iの例の更なる詳細が見られる。ノード 8 0 8 - i は、処理クラスタ 1 4 0 0 内の計算要素であり、アドレス指定及びプログラムフロー制御のための基本要素はRISCプロセッサ又はノードプロセッサ 4 3 2 2 である。典型的には、このノードプロセッサ 4 3 2 2 は、(4 0 ビット命令内の 2 0 ビットイミディエート(immediate)フィールドの可能性のある) 2 0 ビット命令を備える、 3 2 ビットのデータパスを有することができる。ピクセル操作は、例えば 3 2 ピクセル機能ユニットのセットで、SIMD構成で、SIMDレジスタとSIMDデータメモリとの間で(例えば) 4 つのロードと(例えば) 2 つのストアを用いて並列に実行される(ノードプロセッサ 4 3 2 2 の命令セットは以下のセクション 7 で説明する)。命令パケットは、すべてのSIMD機能ユニット 4 3 0 8 - 1 ~ 4 3 0 8 - Mによって実行される 3 発行SIMD命令と並列に、(例えば) 1 つのRISCプロセッサコア命令、 4 つのSIMDロード、及び 2 つのSIMDストアを記述する。

# [0025]

典型的には、(ロードストアユニット4318‐iからの)ロード及びストアは、SIMDデータメモリ位置と、例えば、最大64、16ビットピクセルまで表すことができる、SIMDローカルレジスタとの間でデータを移動する。SIMDロード及びストアは間接アドレス指定(直接アドレス指定もサポートされている)に共有レジスタ4320‐iを用いるが、SIMDアドレス指定処理はこれらのレジスタを読み出し、アドレス指定コンテキストはコア4320によって管理される。コア4320は、レジスタのスピル/フィル、アドレス指定コンテキスト、及び入力パラメータのためのローカルメモリ4328を有する。ノード毎にパーティション命令メモリ1404‐iが提供され、そこでは、多数のノードに及ぶデータセット上で、より大きなプログラムを実行するために、多数のノードがパーティション命令メモリ1404‐iを共有することも可能である。

# [0026]

20

30

40

50

また、ノード808‐iは、並列処理をサポートするための幾つかの機能を組み込む。(Lf及びRtバッファ4314‐i及び4312‐iに関連し、概してノード808‐iのための入力/出力(IO)回路要素を含む)グローバル入力バッファ4316‐i及びグローバル出力バッファ4310‐iは、ノード808‐i入力及び出力を命令実行から切り離し、システムIOに起因してノードがストールする可能性を極めて低くする。入力は、通常、(SIMDデータメモリ4306‐1~4306‐M及び機能ユニット4308‐1~4308‐M内に保存される(これらは非常に一般的である)。SIMD出力データは、グローバル出力バッファ4210‐iに書れ、そこから処理クラスタ1400を介してルーティングされ、たとえ、システムのパカーマンスがその限界に近づいた場合(これも可能性が低い)でも、ノード(即ち、808‐i)がストールする可能性を低くする。SIMDデータメモリ4308‐1~4306‐M及び対応するSIMD機能ユニット4306‐1~4306・Mは、各々、集合的に「SIMDユニット」と称される。

#### [0027]

SIMDデータメモリ4306-1~4306-Mは、重複しないコンテキスト内に構 成され、可変サイズであり、関連又は非関連タスクのいずれかへ割り振られる。コンテキ ストは、水平及び垂直の両方向で充分に共有可能である。水平方向での共有はリードオン リーメモリ4330-i及び4332-iを使用し、それらは、典型的には、プログラム についてはリードオンリーであるが、書き込みバッファ4302-i及び4304-i、 ロード / ストア ( L S ) ユニット 4 3 1 8 - i 、又は他のハードウェアによって書き込み 可能である。また、これらのメモリ4330-i及び4332-iのサイズは、約512 × 2 ビットである。概してこれらのメモリ 4 3 3 0 - i 及び 4 3 3 2 - i はその上で操作 される中央ピクセル位置に対して、左方向及び右方向へのピクセル位置に対応する。これ らのメモリ4330-i及び4332-iは、書き込みをスケジューリングするために、 書き込み・バッファリング機構(即ち、書き込みバッファ4302・i及び4304・i )を使用し、そこでは、サイド・コンテキスト書き込みは、通常、ローカルアクセスとは 同期されていない。バッファ4302-iは、概して、同時に動作する(例えば)隣接す るピクセルコンテキストとのコヒーレンスを維持する。垂直方向の共有はSIMDデータ メモリ 4 3 0 6 - 1 ~ 4 3 0 6 - M内のサーキュラーバッファを用いる。サーキュラーア ドレス指定は、LSユニット4318-iによって適用されるロード及びストア命令によ ってサポートされているモードである。共有データは、概して、上述のシステムレベル依 存性プロトコルを用いてコヒーレントに保たれる。

# [ 0 0 2 8 ]

コンテキスト割り振り及び共有は、SIMDデータメモリ4306・1~4306・Mコンテキスト記述子によって、ノードプロセッサ4322に関連付けられるコンテキスト状態メモリ4326内に特定される。このメモリ4326は、例えば、16×16×32ビット又は2×16×256ビットRAMであり得る。また、これらの記述子は、コンテキスト間でデータがどのように共有されるかを、充分に一般的な方式で特定し、コンテキスト間のデータ依存性を取り扱うための情報を保持する。コンテキスト保存/復元メモリ4324は、レジスタ4320・iを並列に保存及び復元させることによって、(後で説明する)0・サイクルタスク切り替えをサポートするように使用される。SIMDデータメモリ4306・1~4306・M、及びプロセッサデータメモリ4328コンテキストは、各々のタスクのための非依存コンテキストエリアを用いて保存される。

#### [0029]

SIMDデータメモリ4306-1~4306-M、及びプロセッサデータメモリ43 28は、可変サイズの可変数コンテキストに区分される。垂直フレーム方向のデータは、 そのコンテキスト自体の中で保持及び再使用される。水平フレーム方向のデータは、コン テキストを共に水平グループにリンクさせることによって共有される。なお、コンテキス ト構成は、計算に関係するノード数及びそれらが互いにどのように相関するかとはほぼ無

20

30

40

50

関係であることに留意することが重要である。コンテキストの主目的は、画像データを、 このデータを操作するノードの構成に関係なく、保持、共有、及び再使用することである

[0030]

典型的には、SIMDデータメモリ4306・1~4306・Mは、機能ユニット4308・1~4308・Mによって操作される(例えば)ピクセル及び中間コンテキストを含む。SIMDデータメモリ4306・1~4306・Mは、概して、(例えば)最大16の分離コンテキストエリアに区分される。各分離コンテキストエリアは、プログラマブルベースアドレスを備え、コンパイラによってレジスタのスピル / フィルに使用される全てのコンテキストからアクセス可能な共通エリアを備える。プロセッサデータメモリ4328は、入力パラメータ、アドレス指定コンテキスト、及びレジスタ4320・iのためのスピル / フィルエリアを含む。プロセッサデータメモリ4328は、各々プログラマブルベースアドレスを備える、SIMDデータメモリ4306・1~4306・Mコンテキストに対応する(例えば)最大16の分離ローカルコンテキストエリアを有し得る。

[0031]

典型的には、ノード(即ち、ノード808‐i)は、8個のSIMDレジスタ(第1の構成)、32個のSIMDレジスタ(第2の構成)、及び32個のSIMDレジスタと、より小さい機能ユニットの各々に3つの予備実行ユニット(第3の構成)の例えば3つの構成を有する。

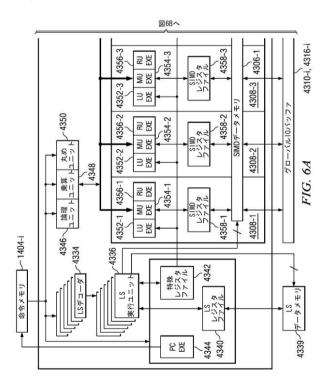

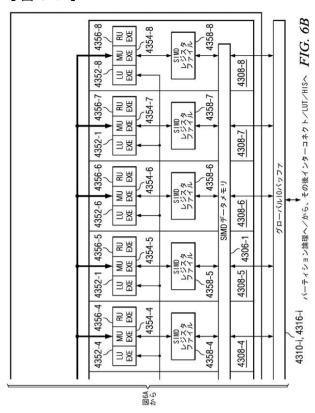

[ 0 0 3 2 ]

例として、図6では、SIMDユニット(即ち、SIMDデータメモリ4306-1及びSIMD機能ユニット4308-1)、ノードプロセッサ4322、及びLSユニット4318-iの例がより詳しく示されている。この例に示されるように、SIMD機能ユニット4308-iは、概して、8個のより小さい機能ユニット4338-1~4338-8で構成され、第3の構成を用いている。

[0033]

先ず、プロセッサコアを見ると、ノードプロセッサ4322は、概して、全ての制御関連命令を実行し、レジスタファイル4340及び4342(各々)に示されるSIMDユニットのための全てのアドレスレジスタ値及び特殊レジスタ値を保持する。(例えば)最大6個のメモリ命令が1サイクルで計算され得る。アドレスレジスタ値の場合、示されたSIMDユニットからノードプロセッサ4322にアドレスソースオペランドが送られ、ノードプロセッサ4322がレジスタ値を送り返し、次にそのレジスタ値がSIMDユニットによってアドレス計算のために使用される。同様に、特殊レジスタ値の場合、示されたSIMDユニットからノードプロセッサ4322に特殊レジスタソースオペランドが送られ、ノードプロセッサ4322はレジスタ値を送り返す。

[ 0 0 3 4 ]

ノードプロセッサ4322は、SIMDのための(例えば)15個の読み出しポート及び6個の書き込みポートを有し得る。典型的には、15個の読み出しポートは、6個のメモリ命令の各々のための2つのオペランド(即ち、1ssrc及び1ssrc2)を収容する(例えば)12個の読み出しポート、及び特殊レジスタファイル4312のための3つのポートを含む。典型的には、特殊レジスタファイル4342は、RCLIPMIN及びRCLIPMAXという名称の2つのレジスタを含み、これらのレジスタは共に提供されるべきものであって、概して、16エントリレジスタファイル4342の下位の4つのレジスタに限定される。次にRCLIPMAX及びRCLIPMINレジスタは、命令の中に直接特定される。他の特殊レジスタRND及びSCLは、4ビットレジスタ識別子によって特定され、16エントリレジスタファイル4342内の任意の場所に配置され得る。また、ノードプロセッサ4322は、命令メモリ1404-1を更新し得るプログラムカウンタ実行ユニット4344を含む。

[ 0 0 3 5 ]

ここで、LSユニット4318-i及びSIMDユニットを参照すると、各々の一般的

構造が図6に見られる。図示されるように、LSユニット4318-iは、概して、LSデコーダ4334、LS実行ユニット4336、論理ユニット4346、乗算ユニット4336、 は理ユニット4346、乗算ユニット4318-iのためのデータパスに関する詳細は後で記載する。より小らい機能ユニット4338-1~4338-8の各々は、概して(且つ各々が)、(例えばそれぞれ32個のレジスタを有し得る)SIMDレジスタファイル4358-1~4358-8、左論理ユニット4352-1~4352-8、乗算ユニット4354-1~4354-8、及び右論理ユニット4356-1~4356-8を含む。これらの左論理ユニット4352-8、乗算ユニット4354-8、及び右コニット4356-1~4356-8を含む。これらの左論理ユニット4356-8を含む。これらの左論理ユニット4358-1~4358-1~4358-1~800万年記録により、人で記載である。また、LSユニット4318-iと同様、各機能ユニット4338-1~4338-8のためのデータパスは、後で記載する。

# [0036]

また、ノード(即ち、ノード808‐i)のための3つの例示の構成では、幾つかの構成では、論理ユニット4352‐1)のサイズ、又は対応する命令は変化して及が、他は同じままであり得る。LSデータメモリ4339、ルックアップテーブル、及じとストグラムは、相対的に同じままとなる。好ましくは、LSデータメモリ4339は、は、カータメモリ4339、ルックアップテーブルでは、は、カータメモリ4339、ルックアップテーブルでは、は、カータンの位置がコンテキストベースアドレスを保持し、残りの位置がコンテキストベースアドレスを保持し、残りの位置がコンテキストベースアドレスを保持し、残りの位置がコンテキストベースルフはよりであり得る。(概して、ズがテーブルを選択する。とがテーブルを選択するに対応して、アーブルを選択するために用いられ得る。(概して、アーブルを選択するために用いられ得る。とがでは、4個のテーブルを自じて、アーブルを選択するために4ビットを自じてと共有し、アース指定のために8ビットを使用する。次の表1では、例示の3つの構成各々の命では、それらは種々の構成要素のサイズに対応し得る。

### 【表1】

| 構成要素                                                       | 第1の構成                 | 第2の構成                 | 第3の構成                 |

|------------------------------------------------------------|-----------------------|-----------------------|-----------------------|

| 4つのノード (即ち、<br>808·i) と共有されると<br>仮定される命令メモリ<br>(即ち、1404·i) | 1024×182 ピット<br>の4セット | 1024×252 ビット<br>の4セット | 1024×318 ビット<br>の4セット |

| 丸めユニット (即ち、<br>3450) 命令                                    | 16ビット                 | 22ビット                 | 22ビット                 |

| 乗算ユニット(即ち、<br>4348)命令                                      | 16ピット                 | 24ビット                 | 24ビット                 |

| 論理ユニット (即ち、<br>4346) 命令                                    | 16ピット                 | 24ビット                 | 24ビット                 |

| LSユニット命令                                                   | 132ビット                | 160ビット                | 156ビット                |

| ノードプロセッサ<br>4322 命令                                        | 0ピット                  | 20ビット                 | 20ビット                 |

| コンテクストスイッチ<br>表示                                           | 2ピット                  | 2ビット                  | 2ビット                  |

|                                                            | コンテクスト:<br>C: LS1: LS | コンテクスト:<br>C:LS1:T2   | コンテクスト:<br>C:LS1:T2   |

| 命令ラインの配置(命                                                 | 2:LS3:LS              | 0:LS2:LS              | 0:LS2:LS              |

| 令パケット形式)                                                   | 4:LS5:LS              | 3: LS4: LS            | 3:LS4:LS              |

|                                                            | 6: LU: MU:            | 5:LS6:LU:             | 5:LS6:LU:             |

|                                                            | RU                    | MU:RU                 | MU:RU                 |

#### [0037]

図 7 を参照すると、共有機能メモリ 1 4 1 0 が見られる。共有機能メモリ 1 4 1 0 は、概して、ノードにより(コストの理由で)充分サポートされない操作をサポートする、大型の集中メモリである。共有機能メモリ 1 4 1 0 の主な構成要素は、(各々が、例えば 4 8 ~ 1 0 2 4 K バイトの間で構成可能なサイズ及び構成を有する) 2 つの大型メモリ、機能メモリ 7 6 0 2 及びベクトルメモリ 7 6 0 3 である。この機能メモリ 7 6 0 2 は、高帯

10

20

30

20

30

40

50

[0038]

全ての処理ノード(即ち、808‐i)が機能メモリ7602及びベクトルメモリ7603にアクセスし得るという意味で、機能メモリ7602に提供されるデータは、SFMラスと般的に「共有」されている。機能メモリ7602に提供されるデータは、SFMラーは、全般的に、ノード(即ち、808‐i)を処理するための上述のコンテキス〇もまた、処理ノードは、典型的には、ベクトルメモリ7603でカロトコルを使用し、処理ノードは、典型的には、機能メモリ7603にできるが、処理ノードによっは、機能メモリ7602にできるが、処理ノードによっは、機能メモリ7602にできるが、処理ノードによっは、機能メモリ7602内の共通位置を読みにびが、処理ノード(即ち、808‐i)は、機能メモリ7602内の共通位置を読みにびが、処理ノード(即ち、808‐i)は、機能メモリ7602対しておりてきるが、(通常は)リードオンリードが機能メモリ7602領域への読み出し、操作のいずれかとしてである。また、処理ノードが機能メモリ7602領域への読み出し、書き込みアクセスを有することも可能であるが、これは所定のプログラムによるアクセスに限定されるべきである。

[0039]

図8を参照すると、共有機能メモリ1410のためのSIMDデータパス7800の例が見られる。例えば、8個のSIMDデータパス(これらは、16ビットパックデータを操作できるので、2つの16ビットハーフに区分され得る)が使用され得る。図示されるように、これらのSIMDデータパスは、全般的に、バンクのセット7802-1~7802-1~7802-1~7806-1~7806-1~7806-1~7806-1

[0040]

図9では、SIMDデータパス(即ち及び例えば、レジスタ7804-1~7804-Lの1つの一部分、及び機能ユニット7806-1~7806-Lの1つの一部分)の例が見られる。図示されるように、例えば、このSIMDデータパスは、16-エントリ、32ビットレジスタファイル7902、2つの16ビット乗算器7904及び7906、及び、同様に、1サイクル中に2つの16ビットパック操作を実行し得る、単一の32ビット算術/論理ユニット7908を含み得る。また、例として、各SIMDデータパスは、2つの、独立した16ビット演算、又は組み合わせた32ビット演算を実行し得る。例えば、これは、32ビットの加算器と組み合わせた16ビット乗算器を用いて32ビットの乗算を形成し得る。また、算術/論理ユニット7908は、加算、減算、論理演算(即ち、AND)、比較、及び条件移動を実行することが可能である。

[0041]

図 8 に戻ると、 S I M D データパスレジスタ 7 8 0 4 - 1 ~ 7 8 0 4 - L は、ベクトル メモリ 7 6 0 3 へのロード / ストアインタフェースを使用し得る。これらのロード及びス

20

30

40

50

トアは、ノード(即ち、808-i)による並列LUT及びヒストグラムアクセスのために提供されるベクトルメモリ7603の特徴を使用し得る。ノードのために各SIMDデータパスハーフは機能メモリ7602内へのインデックスを提供し得る。同様に、SFMプロセッサ7614内の各SIMDデータパスハーフは、独立ベクトルメモリ7603アドレスを提供し得る。アドレス指定は、概して、隣接するデータパスが(例えば)のカラ、ベクトル、及び8、16、又は32ビットデータのアレイなど、データタイプの高元指で、ベクトルが、リニアのベクトルメモリ7603アドレス指定モードと称される(ベクトルが、リニアのベクトルメモリ7603アドレス指定モードと称される(パックされたピクセルの暗示スとして、ベクトルパック化アドレス指定モードと称される(パックされたピクセルの暗示に、ベクトルパック化アドレス指定モードと称される(パックされたピクセルの暗示に、ベクトルパック化アドレス指定を用いて、SIMDによって暗示される(パックされたピクセルの暗示がして、ベクトルパック化アドレス指定を用いて、SIMDによってもは、二次元ベクトルメモリ7603アドレス指定を用いて、プログラミングラとは、二次元ベクトルメモリ7603アドレスおにを用いて、プログラミングラとによりに、プログラミングランはあたが単一ピクセルスはで演算したかのように書き込まれる。

[ 0 0 4 2 ]

ベクトル暗示データタイプは、概して、各SIMDデータパスによって個別に演算される8ピットchar、16ピットハーフワード、又は32ピットint、のいずれかのSIMD実装ベクトルである(即ち、図9)。これらのベクトルは、概して、プログラム内では明示的でなく、ハードウェア演算によって暗示される。また、これらのデータタイプは、明示的プログラムベクトル又はアレイ内のエレメントとして構成され得る。SIMDは、隠された2次元、又は3次元を、これらのプログラムベクトル又はアレイに、効果的に加算する。実際には、プログラミングビューは専用の32ピットデータメモリを備えるドーのSIMDデータパスであり得る。このメモリは従来のアドレス指定モードを用いてアクセスされる。ハードウェアでは、このビューは、32のSIMDデータパスの各ででプライベートデータメモリの外観を有するような方式でマッピングされるが、この機能性を共有機能メモリ1410に実装するために、ベクトルメモリ7603のワイドなバンクされた構成の利点を実装に利用する。

[0043]

SFMプロセッサ7614SIMDは、概して、記述子を用いて、ノードプロセッサ4322コンテキストに類似するベクトルメモリ7603コンテキスト内で動作する。記述子はバンクのセット7802・1に整列され、全体のベクトルメモリ7603にアクセスするのに充分に大きい(即ち、1024kBのサイズの場合、13ビット)ベースアドレスを有する。SIMDデータパスの各ハーフは、一番左のデータパスのための0から始まる6ビット識別子(POSN)で番号付けされる。ベクトル暗示アドレス指定の場合、この値のLSBは、概して無視され、残りの5ビットは、データパスによって生成されたベクトルメモリ7603アドレスをベクトルメモリ7603内のそれぞれのワードに整列させるために用いられる。

[0044]

処理クラスタ1400内で、汎用RISCプロセッサは様々な目的を果たす。例えば、(RISCプロセッサであり得る)ノードプロセッサ4322はプログラムフロー制御のために用いられ得る。RISCアーキテクチャの例を以下に説明する。

[0045]

図10を参照すると、RISCプロセッサ5200(即ち、ノードプロセッサ4322)の更に詳細な例が見られる。プロセッサ5200によって使用されるパイプラインは、概して、処理クラスタ1400内で一般のハイレベル言語(即ち、C/C++)を実行するためのサポートを提供する。動作においては、プロセッサ5200は、フェッチ、デコード、及び実行の3段のパイプラインを用いる。典型的には、コンテキストインタフェース5214及びLSポート5212が命令をプログラムキャッシュ508に提供し、その命令は命令フェッチ5204によってプログラムキャッシュ5208からフェッチされ得

る。命令フェッチ5204とプログラムキャッシュ5208との間のバスは、例えば、40ビット幅であり得、プロセッサ5200がデュアル発行命令(即ち、命令が40ビット又は20ビット幅であり得る)をサポートすることを可能にする。概して、(処理ユニット5202内の)「A側」及び「B側」の機能ユニットはより小さい命令(即ち、20ビット命令)を実行する。提供された命令を実行するために、処理ユニットは、レジスタファイル5206を「スクラッチパッド」として使用し得る。このレジスタファイル5206は、「A側」との間で共有される(例えば)16・エントリ、32ビットレジスタファイルであり得る。また、プロセッサ5200は、制御レジスタファイル5216及びプログラムカウンタ5218を含む。また、プロセッサ5200はバウンダリピン又はリードを介してアクセスされ得る。各例を、表2で説明する(「z」は、アクティブローピンを示す)。

# 【表2】

| Pin名          | 幅 | 方向 | 目的                                                                                         |

|---------------|---|----|--------------------------------------------------------------------------------------------|

|               |   |    | フラグ及びストラッピング                                                                               |

| risc_is_mtv   | 1 | 出力 | MT V 命令がデコードされるときデコード段5308でア<br>サートされる。 (複製を用いて、プロセッサ5200からベ<br>クトル又はS1MDレジスタへ移動する。)       |

| risc_is_mtvvr | 1 | 出力 | MTVVR命令がデコードされるときデコード段5308<br>でアサートされる。 (プロセッサ5200からベクトル又は<br>SIMDレジスタへ移動する)               |

| risc_is_mfvvr | 1 | 出力 | MF V V R命令がデコードされるときデコード段5308<br>でアサートされる。 (ベクトル又はS1MDレジスタからプロセッサ5200~移動する)                |

| risc_is_mfvre | 1 | 出力 | MF V R C 命令がデコードされるときデコード段5308<br>でアサートされる。 (コラブスを用いて、プロセッサ520<br>0からベクトル又はS1MDレジスタへ移動する。) |

| risc_is_mtvre | 1 | 出力 | MT V R E 命令がデコードされるときデコード段5308<br>でアサートされる。 (拡張を用いて、プロセッサ5200か<br>5ベクトル又はSIMDレジスタへ移動する。)   |

|              |     |    | クトル/SIMDレジスタ転送インタフェース                |

|--------------|-----|----|--------------------------------------|

| risc_vec_ua  | 5   | 出力 | MTVVR及びMFVVR命令のためのベクトル (又はSI         |

|              |     |    | MD) ユニット (a k a 「レーン」) アドレス。         |

|              | V.  |    | 実行段5310で駆動される。                       |

| risc_vec_wa  | 5   | 出力 | MTV、MTVRE、MTVVR命令の場合、                |

|              |     |    | ベクトル(又はS I MD)レジスタファイル書き込みアドレ        |

|              |     |    | A                                    |

|              |     |    | MFVVR及びMFVRC命令の場合、                   |

|              |     |    | 要求されたベクトルデータを受け取るためのGPRのアド           |

|              |     |    | レスを含む。                               |

|              |     |    | 実行段5310で駆動される。                       |

| risc_vec_wd  | 3 2 | 出力 | ベクトル (又はS IMD) レジスタファイル書き込みデータ       |

|              |     |    | 実行段5310で駆動される。                       |

| risc_vec_hwz | 2   | 出力 | ベクトル (又はS IMD) レジスタファイル書き込みハーフ       |

|              |     |    | ワード選択                                |

|              |     |    | 00=両方書き込む                            |

|              |     |    | 10=下位を書き込む                           |

|              |     |    | 0 1 = 上位を書き込む                        |

|              |     |    | 1 1 = 読み出す                           |

|              |     |    | vec_regf_enz のアサートでゲーティングされる。        |

|              |     |    | 実行段5310で駆動される。                       |

| risc_vec_ra  | 5   | 出力 | ベクトル (又はSIMD) レジスタファイル読み出しアドレ        |

|              |     |    | ス。                                   |

|              |     |    | 実行段5310で駆動される。                       |

| vec_rise_wrz | 1   | 入力 | レジスタファイル書き込みイネーブル。MFVVR又はMF          |

|              |     |    | VRC命令の結果として書き込みデータを戻すとき、ベクト          |

|              |     |    | ル (又はSIMD) によって駆動される。                |

| vec_rise_wd  | 3 2 | 出力 | ベクトル (又はS I MD) レジスタファイル書き込みデータ。     |

|              |     |    | 実行段5310で駆動される。                       |

| vec_rise_wa  | 4   | 入力 | 汎用レジスタファイル 5 2 0 6 アドレス。MF V V R 又はM |

|              |     |    | FVRC命令の結果として戻るベクトルデータのための宛           |

|              |     |    | て先である。                               |

10

20

30

20

30

40

50

|                        |         |    | ノードインタフェース                                                           |

|------------------------|---------|----|----------------------------------------------------------------------|

| node_regf_wr[0:<br>5]z | 1 b×6   | 入力 | レジスタファイル書き込みポート書き込みイネーブル                                             |

| node_regf_wa[0<br>:5]  | 4 b × 6 | 入力 | レジスタファイル書き込みポートアドレス。<br>ノードサポートのため、汎用レジスタファイル5206へ6<br>個の書き込みポートがある。 |

| node_regf_wd[0<br>:5]  | 3 2 b×6 | 入力 | レジスタファイル書き込みポートデータ。                                                  |

| node_regf_rd           | 512     | 出力 | レジスタファイル読み出しデータ。                                                     |

| node_regf_rdz          | 1       | 入力 | 汎用レジスタファイル5206コンテンツ読み出しイネー<br>ブル。                                    |

| vmem_rdy          | 1         | 入力 | ベクトルメモリレディ。                            |

|-------------------|-----------|----|----------------------------------------|

|                   |           |    | 通常存在し、不使用時はハイにストラップされる。                |

| risc_vec_valid    | 1         | 出力 | SFM命令レーンが有効であることを示す。                   |

|                   |           |    | これは通常アサートされるが、プロセッサ5200が非並列            |

|                   |           |    | 20ビット命令対の第2のハーフを実行しているとき、ディ            |

|                   |           |    | アサートされる。                               |

| rise_fmen_addr    | 20        | 出力 | ベクトル暗示ロード/ストアアドレスバス。                   |

| rise fmem bez     | 4         | 出力 | ベクトル暗示ロード/ストアバイトイネーブル。                 |

| rise vec opr      | 4         | 出力 | このバスは、ベクトル暗示ストアのためのベクトルユニッ             |

|                   |           |    | トソースレジスタ、又はベクトル暗示ロードのためのベク             |

|                   |           |    | トルユニット宛て先レジスタを表す。                      |

| risc_is_vild      | 1         | 出力 | ベクトル暗示符号付きロードフラグ。                      |

| risc_is_vildu     | 1         | 出力 | ベクトル暗示符号無しロードフラグ。                      |

| risc_is_vist      | 1         | 出力 | ベクトル暗示ストアフラグ。                          |

| risc_hg_posn      | 8         | 出力 | プロセッサ5200HG_POSN制御レジスタのカレン             |

|                   |           |    | トのコンテンツを反映する。                          |

| rise_regf_ra[l:0] | 4 b×2     | 入力 | レジスタファイル読み出しアドレスポート。2つのポート             |

|                   |           |    | がある。これらのピンは、レーン 0 (一番左) ベクトルユ          |

|                   |           |    | ニットによって駆動される。ベクトルユニットが、GPR             |

|                   |           |    | ファイルの下位の4レジスタの1つを読み出すことを許可             |

|                   |           |    | する。                                    |

| risc_regf_rd[1:0  | 1 b×2     | 入力 | ディアサート時は、risc_regf_rdata0/1 バス上のスイッチング |

| ]z                |           |    | をゲートオフする。rise_regf_rdata 上の有効データを読み出   |

|                   |           |    | すために、ローに駆動されるべきである。                    |

| risc_regf_rdata[l | 3 2 b × 2 | 出力 | レジスタファイル読み出しデータポート。2つのポートが             |

| :0]               |           |    | ある。これらのピンは、レーン〇(一番左)ベクトルユニ             |

|                   |           |    | ットによって駆動される。これらは、rise regf ra に関連す     |

|                   |           |    | る読み出しデータバスである。                         |

| rise_ine_hg_pos   | 1         | 出力 | BHGNE命令がデコードされるときDOでアサートされ             |

| n                 |           |    | る。                                     |

| wrp_hgposn_ne     | 1         | 入力 | SFMラッパーによってアサートされる。HG_POSN             |

| _hgsize           |           |    | 及びHG_SIZEのラッパーコピーが等しくないか否か             |

|                   |           |    | を示す。                                   |

# [0046]

図 1 1 を参照すると、プロセッサ 5 2 0 0 が、パイプライン 5 3 0 0 を備えてより詳細に示さているのが見られる。ここでは、(フェッチ段 5 3 0 6 に対応する)命令フェッチ 5 2 0 4 が A 側及び B 側に分割される。ここで、 A 側は、(1 つの 4 0 ビット命令又は 2 つの 2 0 ビット命令を有する 4 0 ビット幅の命令ワードであり得る)「フェッチパケット」の最初の 2 0 ビット(即ち、[1 9:0])を受け取り、 B 側はフェッチパケットの最後の 2 0 ビット(即ち、[3 9:2 0])を受け取る。典型的には、命令フェッチ 5 2 0 4 はフェッチパケット内の命令の構造及びサイズを決定し、それに応じて命令をディスパッチする(以下のセクション 7 . 3 で説明する)。

# [0047]

(デコード段 5 3 0 8 及び処理ユニット 5 2 0 2 の一部である) デコーダ 5 2 2 1 は命令フェッチ 5 2 0 4 からの命令をデコードする。デコーダ 5 2 2 1 は、概して、(インターミディエイトを生成するための)演算子フォーマット回路 5 2 2 3 - 1 及び 5 2 2 3 - 2 及びそれぞれ B 側及び A 側のためのデコード回路 5 2 2 5 - 1 及び 5 2 2 5 - 2 を含む。デコーダ 5 2 2 1 からの出力は、次に、(デコード段 5 3 0 8 及び処理ユニット 5 2 0 2 の一部である)デコードトゥーエクゼキューションユニット(decode‐to‐execution unit) 5 2 2 0 によって受け取られる。デコードトゥーエクゼキューションユニット 5 2 2 0 は、フェッチパケットを介して受け取る命令に対応する、実行ユニット 5 2 2 7 のためのコマンドを生成する。

## [0048]

実行ユニット 5 2 2 7 の A 側及び B 側も細分されている。実行ユニット 5 2 2 7 の B 側及び A 側の各々は、それぞれ、乗算ユニット 5 2 2 2 - 1 / 5 2 2 2 - 2、ブーランユニ

20

30

40

50

ット 5 2 2 6 - 1 / 5 2 2 6 - 2、加算 / 減算ユニット 5 2 2 8 - 1 / 5 2 2 8 - 2、及び移動ユニット 5 3 3 0 - 1 / 5 3 3 0 - 2を含む。また、実行ユニット 5 2 2 7 の B 側は、ロード / ストアユニット 5 2 2 4 及びブランチユニット 5 2 3 2 を含む。乗算ユニット 5 2 2 2 - 1 / 5 2 2 2 - 2、ブーランユニット 5 2 2 6 - 1 / 5 2 2 6 - 2、加算 / 減算ユニット 5 2 2 8 - 1 / 5 2 2 8 - 2、及び移動ユニット 5 3 3 0 - 1 / 5 3 3 0 - 2 は、それぞれ、(A側及び B側の各々のための、読み出しアドレスを含む)汎用レジスタファイル 5 2 0 6 にロードされたデータ上で、乗算演算、論理ブーラン演算、加算 / 減算演算、及びデータ移動演算を実行する。制御レジスタファイル 5 2 1 6 内で移動演算も実行され得る。

### [0049]

ベクトル処理モジュールを備えるRISCプロセッサが、概して共有機能メモリ141 0 と共に用いられる。このRISCプロセッサは、プロセッサ5200のために用いられ るRISCプロセッサと大体同じであるが、計算及びロード/ストア帯域幅を拡張するた めに、ベクトル処理モジュールを含む。このモジュールは、各々が1サイクルに4-演算 実行パケットを実行する能力のある、16個のベクトルユニットを含み得る。典型的な実 行パケットは、概して、ベクトルメモリアレイからのデータロード、2つのレジスタトゥ ーレジスタ演算、及び、ベクトルメモリアレイへの結果のストアを含む。このタイプのR ISCプロセッサは、80ビット幅又は120ビット幅の命令ワードを一般に使用する。 この命令ワードは、概して「フェッチパケット」を構成して、整列されない命令を含んで もよい。フェッチパケットは、プロセッサ5200に使用されるものと同様の、ベクトル ユニット命令及びスカラ命令を含み得る、 4 0 ビット及び 2 0 ビット命令の混合を含み得 る。典型的には、ベクトルユニット命令は20ビット幅であり得、一方、他の命令は(プ ロセッサ5200と同様)20ビット又は40ビット幅であり得る。また、ベクトル命令 は命令フェッチバスの全てのレーン上に提示され得るが、フェッチパケットがスカラ及び ベクトルユニット命令の両方を含む場合、ベクトル命令は(例えば)命令フェッチバスビ ット[39:0]上に提示され、スカラ命令は(例えば)命令フェッチバスビット[79 :401上に提示される。また、使用されない命令フェッチバスレーンは、NOPを用い てパディングされる。

# [0050]

次に「実行パケット」が1つ又は複数のフェッチパケットから形成され得る。部分実行パケットは完了まで命令キューの中に保持される。典型的には、実行段(即ち、5310)へ完全実行パケットが提出される。単一サイクル中に、(例えば)4つのベクトルユニット命令、(例えば)2つのスカラ命令、又は(例えば)20ビット及び40ビット命令の組合せが実行されてもよい。また、連続する20ビット命令がシリアルに実行されてもよい。カレントの20ビット命令のビット19が設定される場合、これはカレントの命及び後続の20ビット命令が実行パケットを形成することを示す。ビット19は、概して、アビット又は並列ビットと称され得る。アビットが設定されない場合、これは実行パケットの終了を示す。アビットが設定されない連続する20ビット命令は、20ビット命令のシリアル実行を引き起こす。なお、この(ベクトル処理モジュールを備える)RISCプロセッサは、以下の制約の任意のものを含んでもよいことにも留意されたい。

(1)(例えば)40ビット命令で、Pビットが1に設定されることは違反である。

(2)ロード又はストア命令は、命令フェッチバスのB側に現れるべきである(即ち、40ビットのロード及びストアの場合、ビット 79:40、20ビットのロード及びストアの場合、フェッチバスのビット 79:60)。

(3)単一のスカラロード又はストアは、違反ではない。

(4)ベクトルユニットでは、1つのフェッチパケット内に単一のロード及び単一のストアの両方が存在し得る。

(5)40ビット命令が、Pビットが1に等しい20ビット命令に先行されることは違反である。

(6) これらの違反状態を検出するためのハードウェアが適所に存在しない。これらの

制約はシステムプログラムツール718によって実施されることが予期されている。

## [0051]

図12を参照すると、ベクトルモジュールの例が見られる。ベクトルモジュールは、検出器デコーダ5246、デコードトゥーエクゼキューションユニット5250、及び実行ユニット5251を含む。また、ベクトルデコーダは、命令フェッチ5204から命令を受け取るスロットデコーダ5248・1~5248・4を含む。典型的には、スロットデコーダ5248・1及び5248・2は互いに類似した方式で動作し、スロットデコーダ5248・3及び5248・4はロード/ストアデコーディング回路要素を含む。次デコードトゥーエクゼキューションユニット5250は、ベクトルデコーダ5246のデードされた出力に基づいて、実行ユニット5251のための命令を生成し得る。スロットデコーダの各々は、(各々が汎用レジスタ5206内のデータ及びアドレスを使用する・デコーダの各々は、(各々が汎用レジスタ5254、移動ユニット5256、及び「ランユニット5258によって使用され得る命令を生成し得る。また、スロットデコーダのロード及びストア命令を生成し得る。

#### [ 0 0 5 2 ]

汎用レジスタファイル 5 2 0 6 は、 3 2 ビット汎用レジスタファイルによる 1 6 - エントリであり得る。汎用レジスタ(GPR)の幅はパラメータ化され得る。概して、プロセッサ 5 2 0 0 がノード(即ち、 8 0 8 - i )のために用いられる場合、 4 + 1 5 ( 1 5 はバウンダリピンによって制御される)の読み出しポート及び 4 + 6 ( 6 はバウンダリピンによって制御される)の書き込みポートがあり、一方、 G L S ユニット 1 4 0 8 のために用いられるプロセッサ 5 2 0 0 は、 4 個の読み出しポート及び 4 個の書き込みポートを有する。

#### [0053]

ノードプロセッサ 4 3 2 2 と S I M D (即ち、 S I M D データメモリ 4 3 0 6 - 1 及び機能ユニット 4 3 0 8 - 1 を含む S I M D ユニット)との間でデータを移動し得る命令を表 3 に示す。

### 【表3】

| 命令    | 説明                                                                                       |

|-------|------------------------------------------------------------------------------------------|

| MTV   | 全ての機能ユニット(即ち、4338-1)内でノードプロセッ<br>サ4322レジスタからSIMDレジスタ(即ち、SIMDレジ<br>スタファイル4318-1)にデータを移動する |

| MFVVR | 一番左のSIMD機能ユニット (即ち、4338-1) からノー<br>ドプロセッサ4322内のレジスタファイルにデータを移動す<br>る。                    |

| MTVRE | ノードプロセッサ4322内のレジスタを、機能ユニット(即<br>ち、4338-1)へ拡張する。<br>レジスタを32の機能ユニットへ拡張する。                  |

| MFVRC | S I M D 内 の 機能 ユニットレジスタ を、1 つ の 3 2 ビット (例えば) へ 圧縮する。                                    |

#### [0054]

次の表 4 は、プロセッサ 5 2 0 0 のための命令セットアーキテクチャの例を示す。ここで、

(1)ユニット表示、.SA及び.SBは、どちらの発行スロットが20ビット命令が実行するかを識別するために用いられる。

- (2) 40 ビット命令は、規則により、B側(.SB)で実行される。

- (3)基本形式は < ニーモニック > < ユニット > < カンマで区切られたオペランドリスト > である。

- (4)擬似コードは、C++シンタックスを有し、適切なライブラリを用いて、シミュレータ又は他のゴールデンモデルに直接含まれ得る。

10

20

30

# 【表4】

|  | b |  |

|--|---|--|

|  |   |  |

| シンタックス/擬似コード                                              | 説明                 |

|-----------------------------------------------------------|--------------------|

| MFVRC .(SB) s1(R5),s2(R4)                                 |                    |

| void ISA::OPC_MFVRC_40b_266 (Vreg &s1, Gpr &s2)           |                    |

| (                                                         |                    |

| Event initiate,complete;                                  |                    |

| Reg s2Save;                                               |                    |

| risc_is_mfvrcassert(1);                                   |                    |

| vec_regf_enzassert(0);                                    | MOVE VREG TO       |

| vec_regf_hwzassert(0x3);                                  | GPR, COLLAPSE      |

| vec_regf_raassert(s1);                                    |                    |

| s2Save = s2.address();                                    | VREGをGPRに<br>移動する。 |

| initiate.live(true);                                      | コラプス               |

| complete.live(vec_wdata_wrz.is(0));                       |                    |

| 1                                                         |                    |

| MFVVR .(SB) s1(R5), s2(R5), s3(R4)                        | +                  |

| void ISA::OPC_MFVVR_40b_264 (Vunit &s1, Vreg &s2,Gpr &s3) |                    |

| {                                                         |                    |

| Event initiate, complete;                                 | MOVE               |

|                                                           | UNIT/VREG TO       |

| Reg s3Save;                                               | GPR                |

| risc_is_mfvvrassert(1);                                   | UNIT/VREGを         |

| vec_regf_uaassert(s1);                                    | GPRに移動する           |

| vec_regf_hwzassert(0x3);                                  |                    |

| シンタックス/擬似コード                                                | 説明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| vec_regf_enzassert(0);                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| vec_regf_raassert(s2);                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| s3Save = s3.address();                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| initiate.live(true);                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| complete.live(vec_wdata_wrz.is(0));                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| }                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| MFVVR .SB s1(R5), s2(R5), s3(R4)                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| void ISA::OPC_MFVVR_40b_264 (Vunit &s1, Vreg &s2,Gpr &s3) { |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Reg s3Save;                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| risc_is_mfvvrassert(1);                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| risc_vec_uaassert(s1);                                      | MOVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| risc_vec_raassert(s2);                                      | VUNIT/VREG TO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| s3Save = s3.address();                                      | GPR.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| initiate.live(true);                                        | AND DESCRIPTION OF THE PROPERTY OF THE PROPERT |

| vec_risc_waassert(s3);                                      | VUNIT/VREGを<br>GPRに移動する                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| vec_risc_wd gets value of Vreg(risc_vec_ra);                | UI MICTORIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| complete.live(vee_rise_wrz.is(0)); //ditto                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ]                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |