### **PCT**

(30) Priority Data:

## WORLD INTELLECTUAL PROPERTY ORGANIZATION International Bureau

#### INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(51) International Patent Classification <sup>6</sup>:

H01L 21/18, 29/205

A2

(11) International Publication Number: WO 97/24752

(43) International Publication Date: 10 July 1997 (10.07.97)

(21) International Application Number: PCT/IB96/01377 (81) Designated States: JP, European patent (AT, BE, CH, DE, DK, ES, FI, FR, GB, GR, IE, IT, LU, MC, NL, PT, SE).

(22) International Filing Date: 6 December 1996 (06.12.96)

08/583,148 28 December 1995 (28.12.95) US upon receipt of that report.

(71) Applicant: PHILIPS ELECTRONICS N.V. [NL/NL]; Groenewoudseweg 1, NL-5621 BA Eindhoven (NL).

(71) Applicant (for SE only): PHILIPS NORDEN AB [SE/SE]; Kottbygatan 7, Kista, S-164 85 Stockholm (SE).

(72) Inventors: TASKER, Nikhil, R.; Prof. Holstlaan 6, NL-5656 AA Eindhoven (NL). MENSZ, Piotr, M.; Prof. Holstlaan 6, NL-5656 AA Eindhoven (NL). KHAN, Babar, A.; Prof. Holstlaan 6, NL-5656 AA Eindhoven (NL).

(74) Agent: SMEETS, Eugenius, T., J., M.; Internationaal Octrooibureau B.V., P.O. Box 220, NL-5600 AE Eindhoven (NL).

Published

Without international search report and to be republished upon receipt of that report.

(54) Title: A METHOD OF MANUFACTURING A HIGH VOLTAGE GaN-AIN BASED SEMICONDUCTOR DEVICE AND SEMICONDUCTOR DEVICE MADE

#### (57) Abstract

The present invention is directed to a technique for manufacturing semiconductor devices in which a one type GaN layer (2) is formed on a substrate (1) and semi-insulating AlN layer (3) is formed on one type GaN layer (2) with an opposite type GaN layer (4, 5) formed on the one type GaN layer (2) and partially below the AlN layer (4, 5). Highly efficient high power and high voltage semiconductor device are formed through this technique having better or similar properties to silicon type semiconductors.

## FOR THE PURPOSES OF INFORMATION ONLY

Codes used to identify States party to the PCT on the front pages of pamphlets publishing international applications under the PCT.

| AM | Armenia                  | GB  | United Kingdom               | MW | Malawi                   |

|----|--------------------------|-----|------------------------------|----|--------------------------|

| AT | Austria                  | GE  | Georgia                      | MX | Mexico                   |

| AU | Australia                | GN  | Guinea                       | NE | Niger                    |

| BB | Barbados                 | GR  | Greece                       | NL | Netherlands              |

| BE | Belgium                  | HU  | Hungary                      | NO | Norway                   |

| BF | Burkina Faso             | 1E  | Ireland                      | NZ | New Zealand              |

|    |                          | IT  | Italy                        | PL | Poland                   |

| BG | Bulgaria                 | JP  | Japan                        | PT | Portugal                 |

| BJ | Benin                    | KE  | Kenya                        | RO | Romania                  |

| BR | Brazil                   | KG  | Kyrgystan                    | RU | Russian Federation       |

| BY | Belarus                  |     | Democratic People's Republic | SD | Sudan                    |

| CA | Canada                   | KP  | of Korea                     | SE | Sweden                   |

| CF | Central African Republic | ••• |                              | SG | Singapore                |

| CG | Congo                    | KR  | Republic of Korea            |    | Slovenia                 |

| CH | Switzerland              | KZ  | Kazakhstan                   | SI |                          |

| CI | Côte d'Ivoire            | LI  | Liechtenstein                | SK | Slovakia                 |

| CM | Cameroon                 | LK  | Sri Lanka                    | SN | Senegal                  |

| CN | China                    | LR  | Liberia                      | SZ | Swaziland                |

| CS | Czechoslovakia           | LT  | Lithuania                    | TD | Chad                     |

| CZ | Czech Republic           | LU  | Luxembourg                   | TG | Togo                     |

| DE | Germany                  | LV  | Latvia                       | TJ | Tajikistan               |

| DK | Denmark                  | MC  | Monaco                       | TT | Trinidad and Tobago      |

|    |                          | MD  | Republic of Moldova          | UA | Ukraine                  |

| EE | Estonia                  | MG  | Madagascar                   | UG | Uganda                   |

| ES | Spain                    |     |                              | US | United States of America |

| FI | Finland                  | ML  | Mali                         |    | Uzbekistan               |

| FR | France                   | MN  | Mongolia                     | UZ |                          |

| GA | Gabon                    | MR  | Mauritania                   | VN | Viet Nam                 |

WO 97/24752 PCT/IB96/01377

# A METHOD OF MANUFACTURING A HIGH VOLTAGE Gan-Ain based semiconductor device and semiconductor device made

The present invention involves the structure and formation of high voltage semiconductor devices which in particular have GaN or AlN based p-n junction features.

Silicon based semiconducting devices have been around for some time for defining p-n structures, such as used in diodes, bipolar transistors and high voltage transistors. Silicon structures have limitations in electrical and optical properties.

5

10

Recent efforts have been made in obtaining semiconductor devices that do not rely on the properties of silicon. Particularly, attention has been directed to III-V compounds, and more particularly, attention has recently been directed at Galium Nitride (GaN) compounds.

For example, various high electron mobility transistors, light emitting diodes and MIS types of transistors have been disclosed in U.S. Patents 5,192,987 and 5,122,845, as well as Japanese Published Application Number 3-273632. These prior references provide GaN type transistor structure that work in the depletion zones with n-conducting layers or are used in and insulating capacity.

The presently claimed invention, on the other hand, seeks to provide semiconductor devices that can also be used at optical wavelengths for specific purposes, such as high power, high voltage devices.

This is achieved in the represent invention by forming p-type GaN on a substrate and using Aluminium Nitride (AlN) as a semi-insulating material for a gate dielectric. This gate insulating material of AlN is formed on the p-type GaN, while n-type GaN is formed at opposite sides of the gate and over the p-type material. The resulting p-n junctions establish high breakdown voltages, enabling larger values of source and drain voltages in transistor structures, for example.

The AlN, grown on the p-type GaN layer, is semi-insulating, and its thickness is less than critical layer thickness, i.e. around a couple of thousand angstroms.

10

15

20

25

30

The gate dielectric of AlN is defined by etching around a mask of different mask materials, such as SiO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, or preferably Si<sub>3</sub>N<sub>4</sub>, by a reactive ion etch (RIE), for example. A selective ion etch is used to form vertical sidewalls of the AlN gate dielectric. While a wet etch might be used, such as KOH, it would be at the expense of avoiding underetching of the AlN gate dielectric. However, such wet etch could etch the p-type GaN layer below the bottom level of the gate dielectric of AlN to enable a subsequent underetching of the gate dielectric. Also, ion beam etching where the beam is incident at an angle to be surface of the layers in the epitaxial structure may also be used. This would also rely on the etch rate of GaN being larger then that of AlN.

By underetching of the gate dielectric, source and drain regions can be formed at opposite sides of and below the gate dielectric. This forms and essential gate-source, drain overlap to define a shortened channel length below the gate dielectric. The source and drain regions are formed by regrowth of either n+ of n- type GaN, or both, on the p-type GaN layer. The growth rate at the sidewall of AlN would determine the geometry of the source, drain overlap with the gate. The formation of the source and drain regions can also be carried out by either ion implantation or diffusion, such as with Group VI elements of S or Se, or Group VI elements of Si or Ge, for example.

Other types of FET devices can be formed by the techniques of the present invention. For example, LDMOS type devices can be formed by using n-type GaN regrowth on the p-type GaN layer. To form LDMIS devices, for example, first a n-type GaN layer is formed at one side of the AlN gate dielectric followed by the formation of a n+ type GaN layer at the opposite side of the gate dielectric. Both layers would be formed partially below the gate dielectric. A subsequent regrowth of a n+ type GaN layer over part of the n-type GaN layer would lead to the LDMIS device with the appropriate electrode attachment.

While various substrate materials could be used in the present invention, the use of insulating sapphire (Al<sub>2</sub>O<sub>3</sub>) for isolation as the substrate material leads to transparent devices useful for devices. The use of insulating sapphire substrates also offers the advantages of SOI devices. Moreover, both GaN and sapphire have reasonably good values good values of thermal conductivity which is an advantage for good thermal dissipation in devices. The visible light transparency of GaN would eliminate adverse effects from visible illumination incident on these devices, such as leakage currents, because of the sub-band gap nature of the light. Alternatively, substrates of SiC may be used for its electrical and thermal properties to permit the advantages of a conducting, thick substrate which may be important in suppressing ESD. The use of an AlN buffer layer between a SiC

substrate and the GaN layer would permit device designs similar to Si based SOI devices using a thick oxide.

The advantages occurring by the present invention results from the respective band-gap values of both GaN and AlN. GaN has a band-gap energy of about 3.4 eV while AlN has a bandgap energy of about 6.2 eV. The system of GaN-AlN thus has a band-gap that can be varied from about 3.4 to 6.2 eV. A close lattice match also results with these two materials over the entire composition range, especially with the addition of a small fraction of In.

The energy band-gap difference manifests itself as both conduction and valence band discontinuity. Because of the energy band-gap values, the material system is transparent to light in the visible range. The large band-gap results in GaN having higher value of breakdown electric field for avalanching, i.e. 2 to 5x10<sup>6</sup> V/cm, compared to 5x10<sup>5</sup> V/cm for Si, for example. This enables the p-n junctions on GaN to have larger values of doping. The large energy band gap values and relatively stable nature of GaN and AlN would permit operation at elevated temperatures with lower leakage currents then available with Si.

In devices operating at high voltages, the carrier transport properties under high field conditions are an important consideration. For example, the forward saturation current would be determined by the carrier saturation velocity at high electric fields in a FET. GaN has an electron saturation velocity of  $2x10^7$  that compares favorably with the value for Si.

The material AlN with a 6.2 eV band-gap can be grown with semi-insulating properties by MOCVD. The AlN layer grown on GaN would be used as the insulating gate dielectric for IGFET devices. The AlN/GaN heterostructure has good interface properties with the AlN thickness less than the critical layer thickness or by adding In, and can be used in conjunction with a gate electrode to induce an inversion layer in GaN. The resulting MISFET structure is capable of being operated at high voltages. Other variations for LDMOS devices can also be incorporated.

25

The good thermal conductivity values of GaN and sapphire, as well as SiC, for the substrate is an advantage from standpoint of using devices according to the present invention for high power application. The use of a sapphire substrate offers the same advantages as Si in SOI devices. The reverse leakage current in p-n junctions would not be significantly effected by visible light incident on the device because of the below band-gap nature. Accordingly, the devices according to the present invention can be used in the

presence of illumination. Further, the use of transparent ITO contact materials for the gate, source and drain electrodes enables further use in device structures transparent to visible light.

An alternative process of the present invention involves forming the ptype GaN on a substrate, forming a layer of n-type GaN on the p-type layer, etching through 5 a part of the n-type layer into a part of the p-type layer, and then forming a layer of AlN over the etched parts of the n- and p-layers to provide the gate dielectric. Subsequent device formation can then be carried out to provide a device according to the present invention.

10

15

in which:

The invention will now be described with reference to the drawing figures

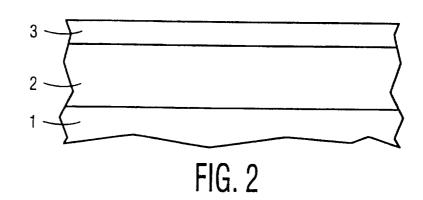

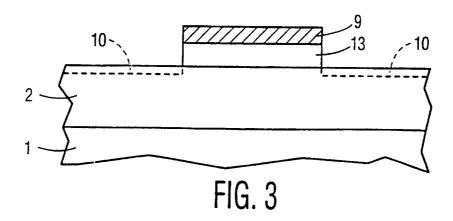

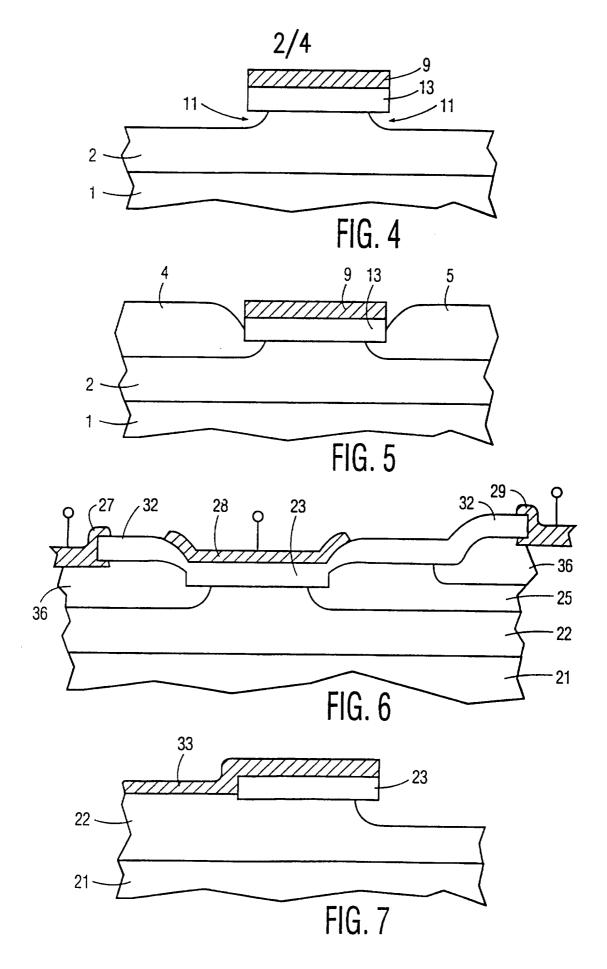

Figure 1 illustrates a MISFET according to the present invention; Figure 2, 3, 4 and 5 show different stages in the manufacture of the device in Figure 1;

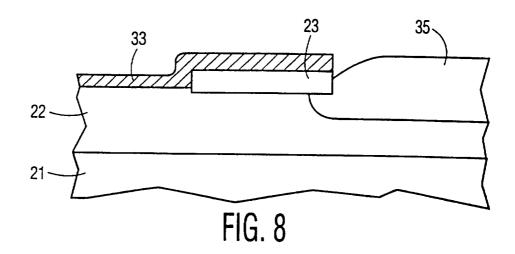

Figure 6 illustrates a LDMIS-FET according to the present invention; Figures 7, 8, 9 and 10 show different stages in the manufacture of the device in Figure 6; and

Figures 11A, 11B and 11C show different stages in an alternate technique according to the present invention. 20

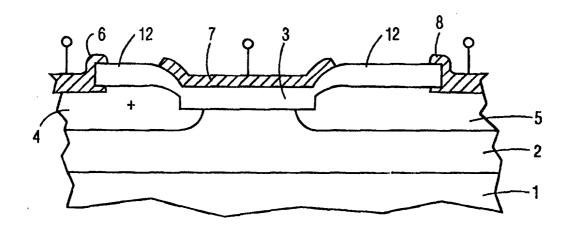

A transistor of the MIS type according to the present invention is shown in Figure 1. This structure includes a p-type layer 2 of GaN on a substrate 1, which may be of a sapphire material. A gate dielectric 3 of AlN is provided on a layer 2 with a layer 4, 5 25 of n+ type GaN at opposite sides of the gate dielectric 3. The n+ type GaN portions 4 and 5 form source and drain regions of the transistor structure with the accompanying electrode contacts 6 and 8 of a conductive material, such as ITO, being provided at ends of insulating extensions 12 at opposite sides of the gate dielectric 3 of AlN. The gate contact 7 is provided in contact with the gate dielectric 3 of AlN. 30

This semiconductor structure is manufactured according to the present invention as shown in Figures 2-5. In Figure 2 a p-type layer 2 of GaN is formed on a substrate 1, and overlying layer 3 of at least semi-insulating AlN is formed over the layer 2. The undoped AIN dielectric and the p-type GaN form a heterostructure where the AIN layer is formed to a thickness less than its critical layer thickness.

20

25

30

The AlN layer 3 is masked with a layer of  $Si_3N_4$  and subsequent etching is carried out to provide a vertical wall gate dielectric 13. A reactive ion etching technique will form the vertical walls although a wet etch could be used at the expense of an undercut under the gate dielectric 13. The p-type layer 2 of GaN is etched down to the line 10 in order to provide a subsequent underetch 11 of the layer 2 of GaN beneath the gate dielectric 13, as shown in Figure 4.

This under cutting of the layer 2 beneath the gate dielectric 13 by a selective isotropic etch, for example, enables the source and drain regions 4, 5 of n-type GaN to be provided below the gate dielectric, as shown in Figure 5. The channel region dimension below the gate dielectric 13 is controlled to obtain an overlap of the gate region with the source drain regions.

The source and drain regions 4, 5 are grown by forming layers of n+ type GaN both beneath the gate dielectric portions and over the p-type GaN at opposite sides of the gate dielectric 13. The growth rate of the n+ type GaN on the sidewalls of the gate dielectric and the undercut p-type GaN determines the geometry of the source, drain-gate overlap.

The subsequent removal of the masking layer 9 and the formation of the extensions 12 of insulating material from the gate dielectric, as shown in Figure 1, complete the construction of the transistor according to the present invention.

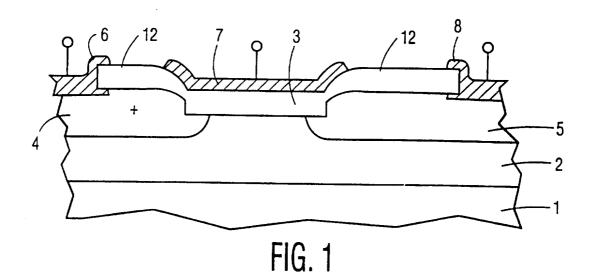

For LDMOS type devices, a growth of n-type GaN adjacent to the drain area is carried out to form a n- drift region 25 at a side of the gate dielectric 23, as is shown in Figure 6. The source and drain regions 24 and 26 are then formed of n+ type GaN at sides of the gate dielectric and the drift region, as is shown in Figure 6.

As shown in Figure 7, 8, 9 and 10, after the gate dielectric 23 is formed, one side of the device is masked together with the gate dielectric by a mask 33. Etching and undercutting is then carried out at one side of the gate dielectric as shown in Figure 7. Thereafter, the n-type layer 35 of GaN is formed at that side of the gate dielectric 23 and over the p+ type layer 22 of GaN at that side of the gate dielectric, as is shown in Figure 8.

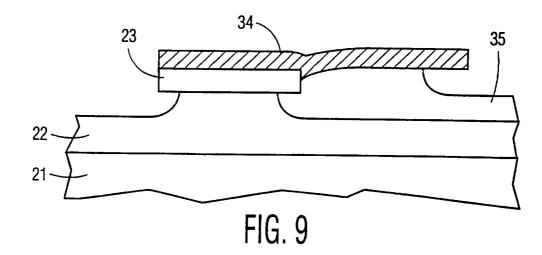

Then the masking layer 33 overlying the one side of the layer and the gate dielectric is removed and a second masking layer 34, covering the gate dielectric and part of the n-layer 35, is formed. Etching is then carried out of the unmasked portions of the p-type GaN layer 22 to undercut the gate dielectric at the side opposite to the n-layer 35 and the uncovered portion of the layer 35, as is shown in Figure 9.

5

10

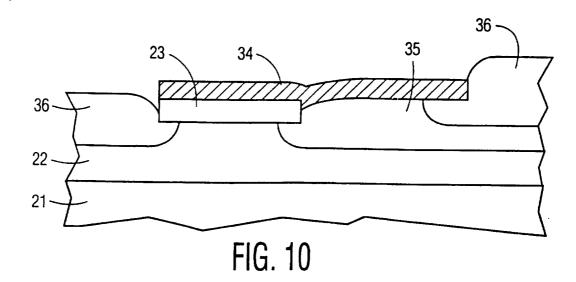

Then n+ portions 36 of GaN are formed both adjacent to the gate dielectric 23 and over the undercut part of the n-layer 35, shown in Figure 10. Appropriate source and drain electrical contacts 27, 29 are formed, together with gate contact 28, relative to insulating portions 32 extending from the gate dielectric, as seen in Figure 6.

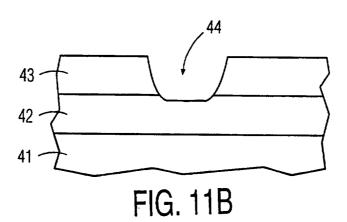

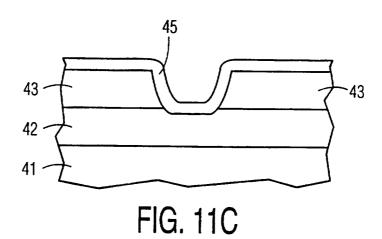

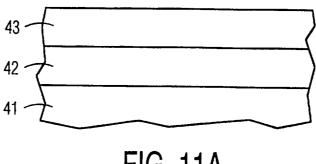

In an alternative to the manufacturing process for the present invention, an n+ type layer 43 of GaN can be grown over a p-type layer 42 on a substrate 41, as seen in Figure 11A. Thereafter, etching is carried out through the n+ layer 43 into the p-type layer 42, such as seen in Figure 11B, to form the cavity 44. Finally, a layer 45 of AlN is grown in the cavity and over the exposed surfaces of the n+ layer 43. Formation of contacts can be further carried out along the lines shown with respect to the devices of Figure 1 and 6.

As further alternatives, ion implantation or diffusion processes can be carried out to form the source and drain regions. The use of transparent contact materials, such as ITO, would make the present invention transparent to visible light.

WO 97/24752 7

Claims:

5

20

25

A method of manufacturing a high voltage semiconductor device. 1. comprising the steps of

> forming a layer (2) of one conductivity type GaN on a substrate (1). forming a semi-insulating layer (3) of AlN on said layer (2) of GaN, masking portions of the layer of AlN and portion (11)

etching said layer (3) of AlN and portions (11) of said layer (2) of GaN below masked portions of the layer (3) of AlN, and

forming an opposite conductivity type layer (4, 5) of GaN over said one conductivity type layer (2) of GaN and into areas below said masked portions of AlN to 10 provide p-n junctions.

- 2. A method according to Claim 1, wherein said one conductivity type layer (2) of GaN is p-type while said opposite conductivity type layer (4, 5) of GaN is n-type.

- A method according to Claim 1 or 2, wherein said opposite conductivity 3. type layer (4, 5) of GaN is n+-type.

- 15 4. A method according to Claim 1, 2 or 3, wherein at least part of said opposite conductivity type layer (4, 5) of GaN is n-type.

- 5. A method according to any of the preceding Claims, further comprising the steps of forming electrical contacts 27, 28, 29 to each of said layer (3) of AlN and parts of said opposite conductivity type layer (4, 5) of GaN at opposite sides of said layer (3) of AIN.

- 6. A method of manufacturing high voltage semiconductor devices, comprising the steps of

forming a layer (42) of GaN of one conductivity type on substrate (41), forming a layer (43) of GaN of an opposite type conductivity on said layer (42) of GaN of said one conductivity type,

etching through said layer (43) of opposite conductivity type GaN into said layer (42) of one conductivity type GaN to form a cavity (44), and forming a layer (45) of semi-insulating AlN over said opposite conductivity type layer (43) of GaN into said cavity (44).

PCT/IB96/01377 WO 97/24752 8

- A method according to Claim 6, further comprising the steps of forming 7. electrical contacts to each of said AlN layer (45) and parts of said opposite conductivity type layer (43) of GaN at opposite sides of said cavity (44).

- A semiconductor device, the structure of which comprises a substrate (1) 8. a layer (2) of GaN of one conductivity type on said substrate (1), a semi-insulating portion 5 (3) of AlN on said layer (2) of one conductivity type GaN, and a GaN layer (4, 5) of an opposite conductivity type on said GaN layer (2) of one conductivity type at opposite sides of said insulating portion (3) of AlN and disposed partially under said portions (3) of AlN.

- A semiconductor device according to any of the preceding Claims,

- wherein said substrate (1) is  $Al_2o_3$ . 10

WO 97/24752 PCT/IB96/01377

3/4

4/4

FIG. 11A