### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2020-188281 (P2020-188281A)

(43) 公開日 令和2年11月19日(2020.11.19)

| (51) Int.Cl. |                  |           | FΙ   |          |       |    | テーマコート    | ・ (参考) |

|--------------|------------------|-----------|------|----------|-------|----|-----------|--------|

| HO1L         | 27/11582         | (2017.01) | HO1L | 27/11582 |       |    | 5F083     |        |

| HO1L         | <i>2</i> 7/11575 | (2017.01) | HO1L | 27/11575 |       |    | 5 F 1 O 1 |        |

| HO1L         | 21/336           | (2006.01) | HO1L | 29/78    | 371   |    |           |        |

| HO1L         | 29/788           | (2006.01) | HO1L | 27/11556 |       |    |           |        |

| HO1L         | 29/792           | (2006.01) | HO1L | 27/11548 |       |    |           |        |

|              |                  |           | 審査請求 | 有 請求項    | の数 20 | ΟL | (全 23 頁)  | 最終頁に続く |

(21) 出願番号 特願2020-132094 (P2020-132094)

(62) 分割の表示 特願2018-546871 (P2018-546871)

の分割

原出願日 平成29年3月2日(2017.3.2)

(31) 優先権主張番号 15/068, 329

(32) 優先日 平成28年3月11日 (2016.3.11)

(33) 優先権主張国・地域又は機関

米国(US)

(71) 出願人 595168543

マイクロン テクノロジー, インク. アメリカ合衆国, アイダホ州 83716 -9632, ボイズ, サウス フェデラル

ウェイ 8000

(74)代理人 100121083

弁理士 青木 宏義

(74)代理人 100138391

弁理士 天田 昌行

(74)代理人 100074099

弁理士 大菅 義之

(74)代理人 100106851

弁理士 野村 泰久

最終頁に続く

## (54) 【発明の名称】メモリデバイス及びそれを形成する方法

### (57)【要約】 (修正有)

【課題】3次元不揮発性メモリデバイスの最適化された 階段状構造を提供する。

【解決手段】3次元不揮発性メモリデバイス102は、メモリデバイスに沿って配置された複数の階段状構造106、108、110と、メモリデバイスを通って延びる少なくとも1つのビア(コンタクトホール126と接点128)を含む少なくとも1つのランディング112と、複数のアクセス線と、階段状構造又は少なくとも1つのランディングのうちの少なくとも一方に近接して配置され且つ少なくとも1つのビアに動作可能に結合された少なくとも1つの制御部130と、を備える。少なくとも1つのランディングは、第1の階段状構造と第2の階段状構造との間に配置され、且つ、第1の階段状構造と第2の階段状構造とを分離する。第1及び第2の階段状構造の各々は、少なくとも1つのランディングの互いに反対側で少なくとも1つのランディングに隣接している

【選択図】図2

#### 【特許請求の範囲】

### 【請求項1】

3次元(3D)不揮発性メモリデバイス(NAND)であって、

前記メモリデバイスに沿って配置された複数の階段状構造であって、各階段状構造は少なくとも2つの導電性ステップを含み、前記少なくとも2つの導電性ステップのうちの各導電性ステップは、絶縁性材料によって、前記少なくとも2つの導電性ステップのうちの隣接する導電性ステップから少なくとも部分的に分離されている、複数の階段状構造と、

前記メモリデバイスを通って延びる少なくとも1つのビアを含む少なくとも1つのランディングであって、前記少なくとも1つのランディングは、前記複数の階段状構造のうちの第1の階段状構造と前記複数の階段状構造のうちの第2の階段状構造との間に配置され、且つ、前記第1の階段状構造と前記第2の階段状構造とを分離し、前記第1の階段状構造と前記第2の階段状構造の各々は、前記少なくとも1つのランディングの互いに反対側で前記少なくとも1つのランディングに隣接している、少なくとも1つのランディングと

複数のアクセス線であって、各アクセス線が、前記階段状構造の前記少なくとも2つの 導電性ステップのうちの1つの導電性ステップの導電性部分から前記少なくとも1つのビ アまで延びている、複数のアクセス線と、

前記階段状構造又は前記少なくとも1つのランディングのうちの少なくとも一方に近接して配置された少なくとも1つの制御部であって、前記少なくとも1つのビアに動作可能に結合された少なくとも1つの制御部と、

を備えるメモリデバイス。

### 【請求項2】

前記少なくとも1つの制御部は、ストリングドライバ回路、パスゲート、ゲートを選択するための回路、前記アクセス線を選択するための回路、信号を増幅するための回路、又は信号を検知するための回路、のうちの少なくとも1つを含む、請求項1に記載のメモリデバイス。

## 【請求項3】

前記少なくとも 1 つの制御部は、前記導電性ステップのうちの所望の 1 つを選択するための、前記アクセス線に電気的に結合されたパスゲートを含む、請求項 1 に記載のメモリデバイス。

### 【請求項4】

前記複数の階段状構造のうちの少なくとも幾つかはワード線プレート構造を含む、請求項1に記載のメモリデバイス。

## 【請求項5】

前記ワード線プレート構造はワード線チャージポンプに結合されている、請求項 4 に記載のメモリデバイス。

## 【請求項6】

前記ワード線プレート構造は、タングステンを含有する材料を含む、請求項 4 に記載の メモリデバイス。

### 【請求項7】

前記ワード線プレート構造に電気的に接続されたワード線ドライバを更に備える、請求項4に記載のメモリデバイス。

### 【請求項8】

前記複数の階段状構造のうちの1つの階段状構造はドレイン選択ゲート(SGD)構造を含む、請求項1に記載のメモリデバイス。

## 【請求項9】

各階段状構造の前記少なくとも 2 つの導電性ステップは金属材料を含む、請求項 1 に記載のメモリデバイス。

### 【請求項10】

前記少なくとも1つのビアは複数のビアを含み、各アクセス線が、前記階段状構造の少

10

20

30

40

なくとも 2 つの導電性ステップのうちの 1 つの導電性ステップの導電性部分から、前記複数のビアのうちの 1 つのビアまで延びている、請求項 1 に記載のメモリデバイス。

#### 【請求項11】

前記複数の階段状構造のうちの少なくとも 1 つを通って延びる半導体ピラーを更に備える、請求項 1 に記載のメモリデバイス。

#### 【請求項12】

メモリデバイスであって、

前記メモリデバイスに沿って配置された複数の階層状構造であって、各階層状構造が、 導電性部分を有する少なくとも2つの階層を含み、前記少なくとも2つの階層の各導電性 部分が、絶縁性材料によって、前記少なくとも2つの階層の隣接する導電性部分から少な くとも部分的に分離されている、複数の階層状構造と、

前記メモリデバイスを通って延びるビアを含むランディングであって、前記複数の階層 状構造のうちの第1の階層状構造と、前記複数の階層状構造のうちの前記第1の階層状構 造に隣接して配置された第2の階層状構造との間に配置されたランディングと、

前記ランディングに近接して配置され、且つ、前記ランディング内の前記ビアのうちの 少なくとも1つに結合された少なくとも1つの制御部と、

を備えるメモリデバイス。

### 【 請 求 項 1 3 】

前記階層状構造を通って延び、且つ、前記導電性部分に電子的に結合された半導体ピラーを更に備える、請求項12に記載のメモリデバイス。

#### 【請求項14】

前記少なくとも 2 つの階層の前記導電性部分は、それぞれ、ワード線プレートを含む、 請求項 1 3 に記載のメモリデバイス。

## 【請求項15】

前記ワード線プレートの各々はタングステンを含む、請求項 1 4 に記載のメモリデバイス。

#### 【請求項16】

前記少なくとも 1 つの制御部はワード線ドライバを含む、請求項 1 5 に記載のメモリデバイス。

## 【請求項17】

前記階層状構造に沿って延びるスタックスロット要素を更に備える、請求項 1 2 に記載のメモリデバイス。

#### 【請求項18】

前記スタックスロット要素は、置換ゲート工程において堆積された導電性材料上に配置された絶縁性材料を含む、請求項17に記載のメモリデバイス。

### 【請求項19】

メモリデバイスであって、

複数のピラーの状態に配列されたメモリセルのアレイと、

前記アレイのメモリセルと電気的に通じているワード線プレートを含む複数の階段状構造と、

前記アレイのメモリセルを選択するための少なくとも1つの制御デバイスと、

ビアを含む少なくとも1つのランディングであって、前記ビアは、前記少なくとも1つのランディングを通って前記少なくとも1つの制御デバイスまで延びており、前記少なくとも1つのランディングは、前記複数の階段状構造のうちの第1の階段状構造と、前記複数の階段状構造のうちの第2の階段状構造との間に配置されている、少なくとも1つのランディングと、

前記階段状構造のワード線プレートと前記ビアの第 1 の端部との間に結合されたアクセス線であって、前記ビアの第 2 の端部が前記少なくとも 1 つの制御デバイスに電気的に結合されている、アクセス線と、

を備えるメモリデバイス。

10

20

30

40

#### 【請求項20】

3次元(3D)不揮発性メモリデバイス(NAND)を形成する方法であって、

2 つの階段状構造の間に画定された前記メモリデバイスのランディングにおける材料の 積層を通る開口を形成することであって、前記 2 つの階段状構造は、半導体ピラーの一方 の側に配置され、且つ、前記半導体ピラーと電気的に通じている、ことと、

前記ランディングにおける前記材料の積層内の前記開口中にコンタクトを画定することと、

前記階段状構造の少なくとも 1 つのステップの導電性部分を、前記ランディングにおける前記材料の積層内の前記コンタクトのうちの少なくとも 1 つのコンタクトを介して制御部に電気的に結合することと、

を含む方法。

【発明の詳細な説明】

#### 【技術分野】

## [0001]

「関連出願へのクロスリファレンス 1

本願は、「CONDUCTIVE STRUCTURES, SYSTEMS AND DEVICES INCLUDING CONDUCTIVE STRUCTURES AND RELATED METHODS」と題して2016年3月11日に出願された米国特許出願第15/068,329号に基づく出願日の利益を請求する。

#### [00002]

#### 「技術分野 ]

本開示の実施形態は、導電性構造(例えば、細長い階段状導電性構造)であって導電性構造の少なくとも一部を通って延びる複数の接点(コンタクト)を有するもの、このような導電性構造を含むシステム、このような導電性構造を製造する方法、および細長い階段状導電性構造のための電気接続を形成する方法に関する。

### 【背景技術】

## [0003]

従来から、メモリデバイスは半導体ベースの集積回路という形でコンピュータをはじめ他の電子装置に組み込まれている。メモリデバイスには多様な種類があり、ランダムアクセスメモリ(RAM)、シンクロナスDRAM(SDRAM)、ダイナミックランダムアクセスメモリ(DRAM)、不揮発性メモリが含まれる。電子システムの性能や複雑性が増すにしたがい、メモリシステムへのメモリの増設の必要性も高まる。半導体産業の傾向として、一つの半導体チップ上の高密度回路として製造されるメモリデバイスはより小型化されている。素子のウエハー表面の専有面積がより小さくなるように少なくともいくつかの素子の形状を小さくすることでトランジスタ素子や回路の小型化が実現され得る。

## [0004]

このような高密度メモリアレイの製造コストを下げるには、部品の数を最小限にとどめなければならない。これは、別々のメモリチップを重ねる代わりに、一つのチップ上により高密度のメモリを搭載することを実現することを意味する。しかし、メモリアレイ内のメモリセルの数を増やす一方でメモリデバイスのサイズを小さくすると、それぞれのメモリデバイスを動作させるために必要な内部接続の数も増えることになる。

## [ 0 0 0 5 ]

例えば、不揮発性メモリ(例として、NANDフラッシュメモリ)では、メモリ密度を増やす一方法に、3次元(3D)アレイとも呼ばれる垂直方向メモリアレイを使用することがある。このような垂直方向メモリアレイは、例えば、Kitoらによる米国特許出願公開第2007/0252201、現在は2011年5月3日に発行された米国特許第7,936,004号、に開示されている。制御部による書き込みまたは読み出し機能のためにアレイの中のメモリセルが一意に選択されるように、従来の垂直方向メモリアレイは

10

20

30

40

導電性プレートとアクセス線(例えば、ワード線)の間の電気接続を必要とする。一種の垂直方向メモリアレイは、層状になった導電性プレート(ワード線プレートまたは制御ゲートプレートとも呼ばれる)の穴を通って延びる半導体ピラーを含み、ピラーと導電性プレートの各接合部には誘電体材料がある。このように、複数のトランジスタを各ピラーに沿って形成することができる。この構造では、ダイ上に上方(垂直方向)にアレイを構築することによって、ダイの単位面積あたりにあるトランジスタの数をより多くすることが可能となる。しかし、このようなデバイスでは、個々のメモリセルが複数の導電性接いの読み取り、書き込み、消去をするために、それぞれのメモリセルが複数の導電性接続(例えば、ワード線、ビット線、選択ゲート等)を備えていなければならない。高密度のメモリセルを有するメモリアレイにおいて、それぞれのメモリセルが効果的に効率よくこれらの接続を備えるのは困難となる。

[0006]

メモリセルの階層の数、すなわち導電性プレートの数が増えるにしたがって導電性プレートを接続するために必要な導電性接続の数も増える。通っている導電性接続の全てを収容するための十分なスペースがブロックの大きさ(例えば、スパン)内になくなるまで電性接続は増やすことができる。この時点で、導電性接続と制御部を追加で収容するには、重ねられたメモリアレイのサイズ(例えば、ピッチ)を大きくする必要がある。例えば、3次元NANDアレイでは、ブロックピッチは導電性接続を介してワード線信号を通め要性によって決められる。一般的に、アレイ内のメモリセルの数を増やすには、プレートの追加やそれに伴う接続を収容するためにブロックピッチも大きくする必要があるため、のようにプレートの数を増やすとワード線(WL)の総静電容量も増え、ポンプをよりのようにプレートの数を増やすとワード線(WL)の総静電容量も増え、ポンプをよりのようにプレートの数を増やすとワード線でののののようにプレートの数を増かすとワード線でののののののようにではであるため、より細かい粒度での消去が求められるデバイス)にとっては問題となる。

### 【発明の概要】

[0007]

本 発 明 の 3 次 元 ( 3 D ) 不 揮 発 性 メモリ デ バ イ ス ( N A N D ) は 、 前 記 メモ リ デ バ イ ス に沿って配置された複数の階段状構造であって、各階段状構造は少なくとも2つの導電性 ステップを含み、前記少なくとも2つの導電性ステップのうちの各導電性ステップは、絶 縁性材料によって、前記少なくとも2つの導電性ステップのうちの隣接する導電性ステッ プから少なくとも部分的に分離されている、複数の階段状構造と、前記メモリデバイスを 通って延びる少なくとも1つのビアを含む少なくとも1つのランディングであって、前記 少 な く と も 1 つ の ラ ン デ ィ ン グ は 、 前 記 複 数 の 階 段 状 構 造 の う ち の 第 1 の 階 段 状 構 造 と 前 記複数の階段状構造のうちの第2の階段状構造との間に配置され、且つ、前記第1の階段 状構造と前記第2の階段状構造とを分離し、前記第1の階段状構造と前記第2の階段状構 造の各々は、前記少なくとも1つのランディングの互いに反対側で前記少なくとも1つの ランディングに隣接している、少なくとも 1 つのランディングと、 複数のアクセス線であ って、各アクセス線が、前記階段状構造の前記少なくとも2つの導電性ステップのうちの 1つの導電性ステップの導電性部分から前記少なくとも1つのビアまで延びている、複数 の ア ク セ ス 線 と 、 前 記 階 段 状 構 造 又 は 前 記 少 な く と も 1 つ の ラ ン デ ィ ン グ の う ち の 少 な く とも一方に近接して配置された少なくとも1つの制御部であって、前記少なくとも1つの ビアに動作可能に結合された少なくとも1つの制御部と、を備える。

【図面の簡単な説明】

[0008]

【図1】本開示の実施形態にかかる、導電性構造と半導体デバイスを含む電子デバイスの 実施形態の略ブロック図を示す。

【図2】本開示の実施形態にかかる、導電性構造と半導体デバイスを含む電子デバイスの 一部の略字垂直断面図を示す。

【図3】本開示の実施形態にかかる、導電性構造と半導体デバイスを含む電子デバイスの 一部の等角図を示す。 10

20

30

40

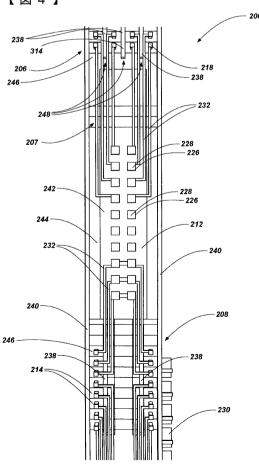

【 図 4 】 図 3 の 電 子 デ バ イ ス の 導 電 性 構 造 の 一 部 の 上 面 図 で あ る 。

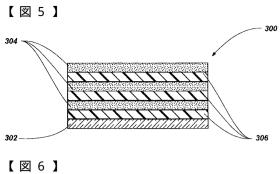

【図 5 】製造中の加工対象物の一部の略示垂直断面図であり、図 1 から図 4 に示される導電性構造の一部を形成するために用いられる本開示の方法の実施形態を示す。

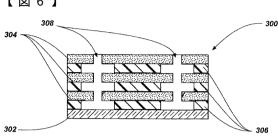

【図 6 】製造中の加工対象物の一部の略示垂直断面図であり、図 1 から図 4 に示される導電性構造の一部を形成するために用いられる本開示の方法の実施形態を示す。

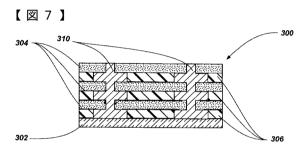

【図7】製造中の加工対象物の一部の略示垂直断面図であり、図1から図4に示される導電性構造の一部を形成するために用いられる本開示の方法の実施形態を示す。

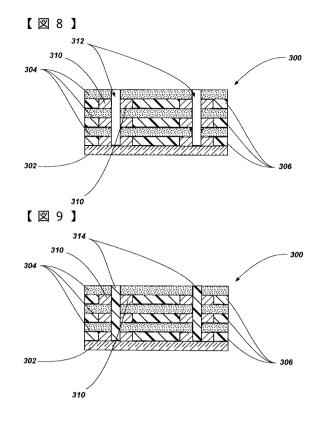

【図8】製造中の加工対象物の一部の略示垂直断面図であり、図1から図4に示される導電性構造の一部を形成するために用いられる本開示の方法の実施形態を示す。

【図9】製造中の加工対象物の一部の略示垂直断面図であり、図1から図4に示される導電性構造の一部を形成するために用いられる本開示の方法の実施形態を示す。

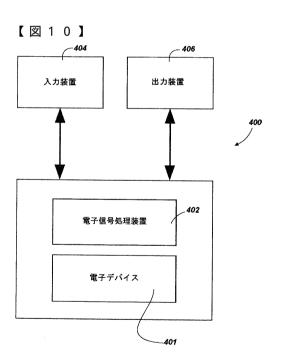

【図10】図1から図4に示される電子デバイスのような電子デバイス(例えば、メモリデバイス)を含む電子システムの一実施形態を示すブロック図を示す。

【発明を実施するための形態】

### [0009]

本明細書中に用いられる、「第一の(first)」、「第二の(second)」、「上方(over)」、「下方(under)」、「上(on)」、「下にある(underlying)」、「上にある(overlying)」等のあらゆる関係を示す語は本開示および図面を理解するうえでの明瞭性や簡便の理由で使用されるものであり、いかなる特定の優先度、方向または順序も含意せず、またいかなる特定の優先度、方向または順序にも依存するものではない。

[0010]

本明細書中に用いられる、「遠位の(distal)」および「近位の(proximal)」という用語は導電性構造が形成される基板に対する導電性構造の素子の位置を示すものである。例えば、「遠位の(distal)」という用語は基板から比較的離れた位置を指し、「近位の(proximal)」という用語は基板から比較的近接した位置を示す。

#### [0011]

本明細書中に用いられる、「横方向(lateral)」と「長手方向(longitudinal)」という用語は導電性構造が形成される基板に対する導電性構造の素子の方向を示すものである。特に、「横方向(lateral)」と「長手方向(longitudinal)」という用語は、導電性構造の近位の端から遠位の端までの軸に対して直角(例えば、垂直)に延びる平面に沿った(例えば、導電性構造の最遠位部分上に実質的に広がる平面に沿った)軸を示す。例えば、「横方向(lateral)」という用語は、導電性構造の近位の端から遠位の端までの軸に対して構造の短軸に沿って直角(例えば、垂直)方向を指す。「長手方向(longitudinal)」という用語は、導電性構造の近位の端から遠位の端までの軸に対して構造の長軸に沿って平行に延びる方向を指す。

### [0012]

以下の説明においては、本開示の実施形態の十分な説明を提供するために、材料の種類および処理条件などの具体的詳細事項を提供する。しかしながら、本開示の実施形態は、これらの具体的詳細事項を使用することなく実現されてもよいことを当業者には理解されたい。実際には、本開示の実施形態は、業界で使用される従来の半導体作製技術と組み合わせて実現されてもよい。また、以下の説明はデバイスやシステムを作製するための完全なプロセスフローとなるものではなくてよい。以下の構造は完全なデバイスやシステムを形成するものでもない。本開示の実施形態を理解するのに必要な処理動作や構造のみが以下に詳細に説明される。従来の作成技術によって完全な導電性構造や半導体デバイスを形成するために追加の動作が行われてもよい。さらに、以下に説明される動作は複数の動作に分けて行われてもよく、また、複数の動作が実質的に同時に行われてもよい。

[0013]

10

20

30

40

以下の詳細な説明においては、本明細書の一部を形成する添付の図面に対して参照がなされ、図面においては、例示として、本開示が実現され得る特定の実施形態が示される。これらの実施形態は、本開示を当業者が実現することを可能とするように十分詳細に記述される。しかしながら、他の実施形態が使用されてもよく、構造的、論理的および電気的変更が本開示の範囲から逸脱することなく行われてもよい。本明細書で提示される図示は、あらゆる特定のシステム、デバイス、構造またはメモリセルの実際の外観であることを意味するのではなく、本開示の実施形態を説明するために使用される単なる理想的な表現に過ぎない。本明細書に提示される図面は、必ずしも正確な縮尺で描かれるとは限らない。また、図面間で共通する素子は、同一の参照番号を保持することがある。

### [0014]

本明細書に用いられる、与えられたパラメータ、特性または条件についての「実質的に(substantially)」という用語は、許容可能な製造公差内などの小程度の差異で、与えられたパラメータ、特性または条件が満たされることを当業者が理解する程度を意味し、含む。例えば、実質的に満たされるパラメータは、少なくとも約90%満たされるか、少なくとも約95%満たされるか、または少なくとも約99%満たされる可能性がある。

### [0015]

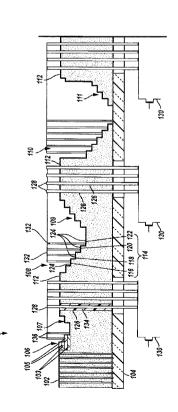

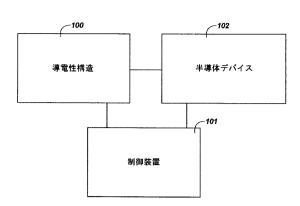

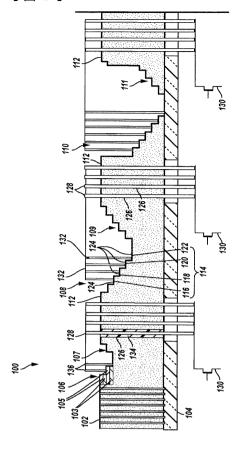

図1は、一つ以上の導電性構造100と一つ以上の半導体デバイス102(例えば、複数のメモリセルやCMOSデバイス)を含む、例えば、不揮発性メモリデバイス(例として、3次元NANDメモリデバイスといった垂直方向メモリデバイス)等の電子デバイスの略ブロック図を示す。例えば、この電子デバイスは一つ以上の半導体デバイス102と直接的または間接的に接続し通じている(例えば、電気的に通じており、直接的または間接的に接触している)一つ以上の導電性構造100を含み得る。なお、本明細書に記載される導電性構造は、NANDデバイスについて具体的な言及をするが、本開示はそれに限定されることはなく、他の半導体およびメモリデバイスに適用されてもよい。

### [0016]

いくつかの実施形態においては、電子デバイスは、以下により詳細に説明されるような 一つ以上の導電性構造100と半導体デバイス102を制御する回路を含む半導体デバイス(例えば、制御装置101)を含み得る。

## [ 0 0 1 7 ]

図1に示される電子デバイスは、例えば、コンピュータまたはコンピュータハードウェアコンポーネント、サーバまたは他のネットワークのハードウェアコンポーネント、携帯電話、デジタルカメラ、携帯情報端末(PDA)、ポータブルメディアプレーヤー(例えば、携帯音楽プレーヤー)等で構成され得る。電子デバイスは、さらに、少なくとも一つの(通常、「マイクロプロセッサ」と呼ばれる)電子信号処理装置を含んでいてもよい。電子デバイスは任意で、例えば、マウスまたは他のポインティングデバイス、キーボード、タッチパッド、タッチスクリーン、ボタン、またはコントロールパネル等、ユーザによって情報を電子デバイスに入力するための一つ以上の入力装置、および例えば、モニター、ディスプレイ、プリンタ、スピーカ等、情報(例えば、映像または音声出力)をユーザに出力するための一つ以上の出力装置を更に含んでいてもよい。

## [0018]

図2は、半導体デバイス102の一つ以上の部分と通信する(例えば、制御する)ための導電性と絶縁性の材料からなる一つ以上の層(例えば、階層)を基板104(例えば、アレイの土台)上に含み得る、導電性構造100と半導体デバイス102を含む電子デバイスの簡易化された断面図である。いくつかの実施形態では、基板104は、導電性構造100および/または半導体デバイス102へおよび/または導電性構造100および/または半導体デバイス102からの信号を通すための一つ以上の導電性材料と絶縁性材料を含んでもよい。例えば、基板104は、一つ以上の導電性構造100と半導体デバイス102を支持するおよび/基板104は、一つ以上の導電性構造100と半導体デバイス102を支持するおよび/

10

20

30

40

20

30

40

50

または絶縁する複数の部分を含んでもよく、ここには、アレイ下の回路(例えば、以下に 説明される制御部)および / または配線が電子デバイス用に設けられている。

#### [0019]

いくつかの実施形態において、導電性構造100および半導体デバイス102は(例えば、同時並行的に形成された)一体化構造から成り得る。別の実施形態においては、導電性構造100および半導体デバイス102は(例えば、別々に形成され)電気的に接続された別々の構造であってもよい。

### [0020]

本明細書中に説明される導電性材料は、いくつかの実施形態において、例えば、金属材料(例えば、W、Ni、窒化タンタル(TaN)、Pt、窒化タングステン(WN)、Au、窒化チタン(TiN)、または窒化チタンアルミニウム(TiAlN))、ポリシリコン、他の導電性材料またはこれらの組み合わせの材料から作られ得る。 【0021】

いくつかの実施形態では、基板104は、例えば、シリコン(例えば、ポリシリコン)、ゲルマニウム、ガリウムヒ素、および他のIII V族またはII VI族の半導体材料を含む、半導体系材料を含むあらゆる構造を含み得る。基板104は、例えば、従来の基板だけでなく他のバルク半導体基板でもよく、限定ではなく例として、シリコンオンインシュレーター(SOI)基板、シリコンオンサファイア(SOS)基板、またはシリコンのエピタキシャル層が別の材料によって支持されているもの、を含んでよい。さらに、以下の説明で「基板」と言及されている場合には、基板内または上に回路やデバイスの素子や部品を少なくとも部分的に形成するために、その前の処理工程の段階のものが用いられていてもよい。いくつかの実施形態において、基板104は、例えば、電子デバイスまたは半導体デバイス102(図1)の他の部分等を含む、導電性構造100が上方(例えば、上)に形成され得るあらゆる構造を含み得る。

#### [0022]

限定ではなく例として、本明細書中に説明される絶縁性材料(例えば、誘電体材料等の電気的絶縁性材料)は、酸化物材料(例えば、 $SiO_2$ 、 $Al_2O_3$ 等)、窒化物材料(例えば、 $Si_3N_4$ 、AlN等)、または例えば、酸窒化物材料、再酸化窒化酸化物材料、またはいわゆる「酸化物(oxide) 窒化物(nitride) 酸化物(oxide)」(ONO)構造等の酸化物材料と窒化物材料の組み合わせ等の、少なくとも部分的に電気的絶縁性材料である任意の適切なものを含んでもよい。いくつかの実施形態では、絶縁性材料はそれぞれ同種の材料、異種の材料、またはこれらの組み合わせからなるものであってもよい。

## [ 0 0 2 3 ]

導電性構造100の一つ以上の部分は、複数の段(ステップ)または階層を含む、いわゆる「階段状」構造として形成されてもよく、各段(各ステップ)は導電性材料103(例えば、ポリシリコン、金属等の他の導電性材料、またはこれらの組み合わせ)を少なくとも一つ含む。この階段状構造106、108、110の段(これらは、例えば、ワード線プレート、ビット線、選択ゲートとして機能、またはワード線プレート、ビット線、選択ゲートを選択する機能をしてもよい)は、半導体デバイス102の一部(例えば、メモリセルの一行)と通信する導電性材料103を含み得る。ある段の導電性材料103は、隣の段の導電性材料103から(例えば、絶縁性材料105によって)少なくとも部分的に(例えば、電気的におよび/または物理的に)分離または絶縁されている。明瞭性のために、導電性材料103と絶縁性材料105の二組(例えば、段)の一部のみが明瞭性のために示されている。

## [0024]

図示されるように、導電性構造100は、複数の階段状または階層状構造(例えば、半導体デバイス102寄りの片側に設置される二つ以上の階段状構造106、108、110)を含み得る。この場合、少なくとも二つの最も近い(例えば、横方向に隣り合う)階段状構造(例えば、階段状構造106と108)はランディング(1anding;踊り

20

30

40

50

場)112(例えば、実質的に平面、あるいは段形状がないランディング112)によって分離されている。換言すれば、階段状構造のそれぞれの対がランディング112によって分離されていてもよい。例えば、階段状構造106、108、110のそれぞれの隣り合う階段状構造106、108、110(例えば、それぞれの隣り合う階段状構造106、108、110)から分離されていてもよい。一つ以上の階段状構造106、108、110は向かい側の階段状構造107、109、111を含んでいてもよい。いくつかの実施例において、階段状構造107、109、111は主と含る階段状構造106、108、110を形成する際の副産物であり、いかなる電気接続も含まなくてもよい(例えば、導電性構造100においてアクティブな階段状構造106、108、110と比較すると積極的に利用されないダミーの階段状構造からなっていてもよい)。ランディング112が導電性構造100の頂上部を画定する一方で、この階段状構造の組(例えば106と107)のそれぞれは導電性構造100のスタジアム(stadium)(例えば、窪んだ部分)を画定する。

[0025]

いくつかの実施形態では、導電性構造100は複数の階段状または階層状構造を含んでもよく、これらは、例えば、「MEMORY DEVICES WITH STAIRS IN A STAIRCASE COUPLED TO TIERS OF MEMORY UNDER THE STAIRCASE」と題して2016年2月25日に出願された発明者Aaron Yipによる米国特許出願第15/053,291号に記載のものと類似していてもよく、この米国特許出願に開示される内容は援用によりここに組み込まれるものとする。

[0026]

いくつかの実施形態において、複数の段(ステップ)114の導電性材料103は、例えば複数のメモリセル等の半導体デバイス102へ電気信号を供給するための導電性プレート(例えば、ワード線プレート)を形成してもよい。

[ 0 0 2 7 ]

明瞭性のために、階段状構造108について具体的に言及する。しかしながら、他の階段状構造のどれもが同じ構造や構成要素を有していてもよいことが理解されよう。階段状構造108の複数の段114(例えば、段116、118、120、122)のそれぞれは、以下にさらに詳しく説明するように、複数の段114のそれぞれと一つ以上の接続(例えば、電気接続)を形成することを容易にするために、接点部124(例えば、絶縁性材料の下に設置される導電性のランディングパッド)を含んでいてもよい。いくつかの実施形態において、複数の段114のそれぞれは、一つ以上の隣り合う段114から(例えば、長手方向軸へ)ずれている接点部124を含み得る。例えば、段118は、隣り合う段(例えば、段116)を越えて長手方向に延びる接点部124(例えば、段118の導電性材料103の露出した端部)を含む。

[0028]

また、図 2 において、例えば、一つ以上のコンタクトホール 1 2 6 (例えば、スルーアレイビア(through array vias))等の開口部は、一つ以上のランディング 1 1 2 のところで、導電性構造 1 0 0 を通って延びていてもよい。例えば、階段状構造 1 0 8 に関連付けられたランディング 1 1 2 は、導電性構造 1 0 0 の遠位側から導電性構造 1 0 0 の下にある基板 1 0 4 へ延びるコンタクトホール 1 2 6 を含み得る。それでれのコンタクトホール 1 2 6 には導電性接点(コンタクト) 1 2 8 が配置されてもよい。この接点 1 2 8 は階段状構造 1 0 8 を通り、基板 1 0 4 を貫通して、導電性構造 1 0 0 の下に設置される一つ以上の制御部 1 3 0 等の別の導電性素子へと延びていてもよい。いくのの実施形態において、この接点 1 2 8 は、例えば、金属材料(例えば、タングステン(W)、ニッケル(Ni)、窒化タンタル(TaN)、Pt、窒化タングステン(WN)、Au、窒化チタン(TiN)、または窒化チタンアルミニウム(TiAIN))、ポリシリコン、または他の導電性材料等の導電性材料から形成されていてもよい。

20

30

40

50

### [0029]

## [0030]

ランディング 1 1 2 は、実質的に導電性構造 1 0 0 に沿って(例えば、導電性構造 1 0 0 の外側ではなく境界内に)導電性ビア(例えば、コンタクトホール 1 2 6 と接点 1 2 8 )を備える。例えば、導電性構造 1 0 0 の境界内に設置され、階段状構造 1 0 6、 1 0 7、 1 0 8、 1 0 9、 1 1 0、 1 1 1 を画定する材料(例えば、交互になっている誘電体および導電性の材料 1 0 3 と 1 0 5 )の層を貫通するこのような導電性ビア(例えば、コンタクトホール 1 2 6 と接点 1 2 8 )は、基板 1 0 4 に最も近い領域にアクセスするためにアクセス線を導電構造 1 0 0 の横方向側面の周りに通す必要なしにアクセス線 1 3 2 を導電性構造 1 0 0 に通すことを可能とする。

#### [ 0 0 3 1 ]

なお、本開示の実施形態は、図面上では便宜上、そして明瞭性のために、コンタクトホール 1 2 6 と接点 1 2 8 が実質的に同じ断面上に設置されるように示されている。コンタクトホールと接点は同じ断面上、異なる断面上、またはこれらの組み合わせに形成されてもよいと考えられる。

#### [0032]

いくつかの実施形態において、また階段状構造106に最も近いランディング112の一例で示したように、コンタクトホール126は接点128とコンタクトホール126の壁との間に配置され、接点128をランディング112の下にある導電性構造100の少なくとも一部から絶縁する絶縁用ライナー134を含み得る。例えば、導電性構造100のランディング112が、階段状構造106、108、110のように絶縁性と導電性の材料103と105のサンドイッチ型構造と類似している場合、絶縁用ライナー134は複数の段114の導電性材料103から接点128を絶縁し得る。しかしながら、別の実施形態において、導電性構造100が(以下に説明するような)置換ゲート構造を含む場合には、このようなライナーは不要となることもある。この場合、導電性構造100の部分でランディングの下にあるものが置換ゲート工程から除外される(例えば、遮蔽される、またはマスクされる)うえに誘電体材料からなる(例えば、誘電体材料のみからなる)

## [0033]

複数の段114の導電性材料103から垂直および/または水平に延び得るアクセス線132は複数の段114の導電性材料103を制御部130と(例えば、接点128を介して)電気的に結合してもよい。制御部130または複数の制御部130は、ストリングドライバ回路、パスゲート、ゲートを選択するための回路、導線(例えば、アクセス線132)を選択するための回路、信号を増幅するための回路、信号を検知するための回路のうちの少なくとも一つを含んでもよい。例えば、そして説明されるように、一つ以上の制御部130は、複数の段114の導電性材料103のうちの所望の一つを選択するため、アクセス線132と電気的に結合されたトランジスタ(例えば、いわゆる「パスゲート」)含んでもよい。

#### [0034]

同様に、階段状構造106、108、110のそれぞれは、それぞれの複数の段114から下にある導電性素子、例えばビア(例えば、コンタクトホール126と接点128)を通って制御部130、へと延びるアクセス線132を含んでもよい。

20

30

40

50

### [0035]

いくつかの実施形態において、一つ以上の階段状構造(例えば、階段状構造106)は(例えば、上述されるワード線プレートアクセス線132からは分離した)別の選択ゲートまたは別の複数の選択ゲートを含んでもよい。例えば、階段状構造106は、半導体デバイス102と通信する(例えば、メモリセルの特定のアレイを選択する)ドレイン側選択ゲート(SGD)として構成されていてもよく、選択ゲート136によって接点128を通ってSGD制御部130に結合されていてもよい。図示されるように、SGD階段状構造106は他の階段状構造108、110とは別であってもよい。しかしながら、別の実施形態において、SGD階段状構造106は、別の階段状構造の一部(例えば、基板104に対して、最遠位の二段等、別の階段状構造108の複数の段114の最遠位にあるものからなっていてもよく、この場合、複数の段114の残りは異なる電気接続用のランディングパッド(例えば、ワード線プレート用の接点部124)の役割を果たす。

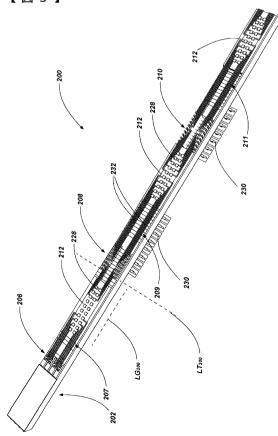

### [0036]

図3は導電性構造200と半導体デバイス202を含む電子デバイスの一部の等角図で ある。 導電性構造 2 0 0 および / または半導体デバイス 2 0 2 は図 1 と図 2 を参照して説 明された導電性構造100と半導体デバイス102と類似していてもよく、これらと同じ 特性と機能を一つ以上含んでいる。図3に示されるように、導電性構造200は複数の階 段状または階層状の構造(例えば、二つ以上の階段状構造206、208、210)を含 んでいてもよく、この場合、少なくとも二つの最も近い(例えば、隣り合う)階段状構造 (例えば、階段状構造 2 0 6 と 2 0 8 ) はランディング 2 1 2 (例えば、実質的に平面、 あるいは段形状がないランディング212)によって分離されている。例えば、階段状構 造 2 0 6 、 2 0 8 、 2 1 0 はランディング 2 1 2 によってそれぞれ他の階段状構造 2 0 6 208、210(例えば、それぞれの隣り合う階段状構造206、208、210)か ら分離されていてもよい。一つ以上の階段状構造206、208、210は向かい側の階 段状構造207、209、211を含んでいてもよい。いくつかの実施例において、これ らの階段構造207、209、211は主となる階段構造206、208、210を形成 する際の副産物であり、いかなる電気接続も含まなくてもよい(例えば、導電性構造20 0 において積極的に利用されないダミーの階段状構造からなっていてもよい)。ランディ ング212が導電性構造200の頂上部を画定する一方で、この階段状構造の組(例えば 2 0 6 と 2 0 7 ) のそれぞれは導電性構造 2 0 0 のスタジアム(例えば、窪んだ部分)を 画定する。

#### [0037]

図3に示されるように、例えば、対応する半導体デバイス202を制御するために活用される階段が必要数に達するまで、一連の階段状構造206、207、208、209、210、211とランディング212は連続していてよい。いくつかの実施形態では、導電性構造200の半導体デバイス202とは反対側の端は、この端で導電性構造200の導電性部分(例えば、ワード線プレートの導電性部分)を絶縁するために絶縁性材料からなるものでもよい。このような絶縁性材料は導電性構造200の横方向の長さまたは横方向軸LT200に沿って延びるスロット(例えば、以下に説明される置換ゲート(RG)工程によって画定されるスロット)に配置されていてもよい。

#### [0038]

アクセス線232は階段状構造206、208、210のそれぞれにある階段の導電性部分に結合されていてもよい。アクセス線232は細長い導電性構造200に沿って一つ以上のランディング212の接点228まで延び得る。接点228は階段状構造208を介して導電性構造200の下に設置される別の導電性素子、例えば一つ以上の制御部230、まで延びてもよい。

## [0039]

図4は図3の電子デバイスの導電性構造200の一部の上面図である。図3と図4を参照すると、導電性構造200は導電性構造200に沿って(例えば、導電性構造200の

20

30

40

50

長手方向の長さまたは長手方向軸 L G 2 0 0 の一部または大部分に沿って)延びるスタックスロットの形成を含んでもよい。このスタックスロットの形成は、例えば、導電性構造2 0 0 の横方向範囲内に設置される内側スタックスロット要素2 3 8 と、導電性構造2 0 0 の相対する横方向の外側範囲の最も近くに(例えば、相対する横方向の外側範囲に)設置される外側スタックスロット要素2 4 0 を含んでもよい。図示されるように、外側スタックスロット要素2 4 0 は導電性構造2 0 0 のそれぞれの横方向側面において導電性構造2 0 0 の横方向範囲の最も外側または境界を画定してもよい。

### [0040]

以下にさらに詳しく説明するように、スタックスロット要素238、240は(例えば、置換ゲート(RG)工程によって)少なくとも部分的に溝またはスロット内に堆積される導電性と絶縁性の両方の材料を含んでもよく、また、階段状構造206、208、210の段の導電性部分を形成するように作用してもよい。上述されるように、いくつかの実施形態では、スタックスロット要素は、導電性構造200の半導体デバイス202とは長手方向反対側の端に配置され、導電性構造200の長手方向の端(例えば、プレートの長手方向の端)を任意の隣り合うデバイスおよび/または導電性材料から絶縁するようにしてもよい。

### [0041]

さらに記載されるように、スタックスロット要素の少なくとも一部(例えば、内側スタックスロット要素 2 3 8 ) は不連続であってよい。例えば、内側スタックスロット要素 2 3 8 は、アクティブな階段状構造 2 0 6 、 2 0 8 、 2 1 0 の段に沿う領域にある導電性構造 2 0 0 の一部のみに沿って延びていればよい。このような実施形態において、ランディング 2 1 2 または導電性構造の接点 2 2 8 を囲む部分には内側スタックスロット要素 2 3 8 はなくてよい。例えば、ランディング 2 1 2 または導電性構造 2 0 0 の接点 2 2 8 を囲む部分には外側スタックスロット要素 2 3 8 はなくてもよい。

### [0042]

また、上述されるように、スタックスロット要素の別の部分(例えば、外側スタックスロット要素240)は導電性構造200に沿って実質的につながっている。例えば、外側スタックスロット要素240は、導電性構造200の一つ以上の側面の最も外側の範囲または境界を画定するために、導電性構造200(例えば、半導体デバイス202も共に)の少なくとも大部分(例えば、全体)に沿って延びていてもよい。

いくつかの実施形態においては、内側スタックスロット要素238は、階段状構造206、208、210のサブブロック(例えば、副段、副階層、サブプレート)を画定するよう機能してもよい。

## [0043]

いくつかの実施形態においては、スタックスロット要素238、240は、少なくとも部分的に、置換ゲート(RG)工程によって形成される誘電体材料または絶縁性材料からなり、導電性構造200の絶縁性の側面を画定してもよい。

### [0044]

図5から図9は完成前の構造等の製造中の加工対象物の一部の略示垂直断面図であり、 導電性構造200の一部を形成するために用いられる本開示の方法の実施形態を示す。特に、図5から図9はスタックスロット要素238、240を導電性構造200に形成する 置換ゲート(RG)工程の簡略化された理想的な例を示す。

## [0045]

以下に説明される実施形態のそれぞれは、導電性構造を形成する材料を導電性構造上で、例えば、成長させ、拡散させ、堆積させ、あるいは供給することによって形成されてもよい。これら各種の材料は、集積回路製造分野で周知の、例えば、堆積技術(例えば、化学蒸着(CVD)、物理蒸着(PVD)、原子層堆積(ALD)、スパッタリング、熱蒸発、またはメッキ)、酸化法(例えば、熱酸化、ISSG酸化)、およびパターニング技術(例えば、マスキングとエッチング)を用いて形成され得る。絶縁性材料は、化学蒸着

20

30

40

50

によって、オルトケイ酸テトラエチル(TEOS)を分解することによって、または集積 回路製造分野で周知の他の方法によって形成され得る。

## [0046]

さらに、これらの材料またはその一部分は、例えば、研磨(abrasion)または研磨(polishing)法(例えば、化学機械研磨(CMP)法、化学研磨法、機械平坦化法)、エッチング法、リフトオフ法、またはこれらの組み合わせを用いて除去され得る。エッチング法は、例えば、マスクと異方性エッチング工程(例えば、プラズマを用いる等の反応性イオンエッチング法)を用いて材料の一部分を除去する、またはマスクと等方性の工程(例えば、化学エッチング工程)を用いて材料の一部分を除去するなどのウェットまたはドライエッチングを含んでよい。なお、反応性イオンを生成するため用いられるガスの特定の組成、化学エッチャントの特定の組成、そしてエッチング法の操作パラメータは、マスクの組成、エッチングされる材料、および周囲の材料を基に選択され得る

[0047]

図5に示されるように、(例えば、最終的に階層状または段状の構造を画定するために利用される)材料の積層300が基板302の上に設けられている。この材料の積層300は交互になっている複数の材料(例えば、誘電体とみなされる交互になっている絶縁性の複数の材料)を含み得る。例えば、材料の積層300は絶縁性材料304とは異なる材料(例えば、窒化物)からなる犠牲材料306と交互に配置されている絶縁性材料304(例えば、酸化物)を含んでもよい。なお、以下に説明される動作は、階段状構造の形成前、形成後、または形成と同時に行われてもよい。

[ 0 0 4 8 ]

図6に示されるように、一つ以上のスロット308は(例えば、等方性エッチングや、 異方性エッチング後の等方性エッチング等によって)材料の積層300を通って基板30 2へ延びるように形成されてもよい。スロット308は、スロット308から犠牲材料3 06へと横方向に開口部を作るように、犠牲材料306の材料(例えば、窒化物)を選択 的に除去する等方性エッチャントによって形成されてもよい。

[0049]

図7に示されるように、犠牲材料306が除去されているスロット308の中に導電性材料310(例えば、タングステン等の金属)が堆積される。

[0050]

図8に示されるように、スロット308の中の導電性材料310の少なくとも一部が除去されてスロット312が形成される。例えば、スロット312を形成するため、スロット308の中の導電性材料310は異方性エッチングによって除去されてもよい。このような導電性材料310の一部の除去は、材料の積層300の一段(例えば、同じ高さ)にある導電性材料310を隣の段にある導電性材料310から分離する役割を果たす(例えば、これは材料の積層300の各段にある導電性部分の間でおこる短絡の確率を下げることを目的とする、例えば、ワード線プレートを形成する)。換言すれば、残る材料が絶縁性材料304によって分離されている導電性材料310となる(つまり、導電性材料は材料の層300の複数の段の間にまたがって延びない)ように材料の積層300の各段にある導電性材料310が除去される。

[0051]

図9に示されるように、別の絶縁性材料314がスロット312内に堆積される。このように、スタックスロット要素(例えば、図4に関連して説明されたスタックスロット要素238、240)が導電性材料310と絶縁性材料314と共に形成されてもよい。材料の積層300の犠牲材料306の段にある導電性材料310はここで、アクセス線132、232(図2から図4)に結合され得る、階段構造の接点部(例えば、図2を参照して説明されたような接点部124)を少なくとも部分的に画定してもよい。

[0052]

図3と図4に戻り、階段状構造206、208、210の導電性部分が置換ゲート工程

20

30

40

50

(例えば、上述されたもの)を用いて形成される実施形態において、ランディング212 に最も近い内側スタックスロット要素238および/または導電性構造200の接点22 8を囲む部分がないことで、コンタクトホール226を絶縁する必要なしに、導電性構造 100を通して直接形成されるそれぞれの接点228用に備えられるコンタクトホール2 2 6 の形成が可能となる。例えば、接点 2 2 8 を囲むランディング領域 2 4 2 は導電性構 造 2 0 0 の 近 位 部 分 か ら 導 電 性 構 造 2 0 0 の 遠 位 部 分 へ の 方 向 に ( 例 え ば 、 ラ ン デ ィ ン グ 領域 2 4 2 と下にある基板(例えば、基板 1 0 4 (図 2 ))間に延びる軸に沿って)導電 性材料が一切なくてもよい。つまり、図5から図9を参照して説明されたように、導電性 材料 3 1 0 はスタックスロット要素 2 3 8 、 2 4 0 ( 例えば、導電性材料 3 1 0 と絶縁性 材料314)が形成された材料の積層300のみに導入されている。そのため、スタック スロット要素 2 3 8 、 2 4 0 がなく、絶縁性材料のみからなるランディング領域 2 4 2 で は、ビア(例えば、コンタクトホール226と関連する接点228)をこのような絶縁性 材料に直接通して延ばすことが可能となる。反対に、ランディング212の別の外側領域 2 4 4 は 導電性 構造 2 0 0 の 近位 部分から 遠位 部分への方向に 導電性材料 3 1 0 を 含んで もよい。これらの領域244は外側スタックスロット要素240に最も近いからである。 これらのランディング 2 1 2 の外 側 領域 2 4 4 は階 段 状 構 造 2 0 6 、 2 0 8 、 2 1 0 の 段 が確実に半導体デバイス202と電子通信を続けられるようにすることができる。

## [0053]

いくつかの実施形態において、スタックスロット要素238、240(例えば、内側スタックスロット要素238)は、階段状構造206、208、210の分割されたサブプロックに少なくとも部分的には電子通信を続けさせる役割を果たす。例えば、階段状構造の一つ(例えば、階段状構造206)の一番下の(例えば、近位の)段(例えば、ワード線プレート)を画定するプレート246は、導電性構造200の長さに沿って(例えば、半導体デバイス202から離れる長手方向に)一つ以上の他の階段状構造206が高端で、階段状構造208の接続された最上の段(例えば、アクセス状構造208へと延びていてもよい。例えば、プレート246は階段状構造206に対する置換ゲート(RG)に投続された段)の画定もする。階段状構造206に対する置換ゲート(RG)に程の際に分割されるプレート246のサブブロックを電気的に接続するために、プレート246は(例えば、階段状構造206に最も近い内側スタックスロット要素238の一つ以上の端の周辺で(例えば、一つ以上の短絡領域248にて)短絡されてもよい。

## [0054]

特に、(例えば、図5から図9に関係して説明された工程による)内側スタックスロット要素238の形成中に、導電性材料310(例えば、タングステン)は犠牲材料306へ部分的に流れ込んでもよい。このような構成において、絶縁性材料314が導電性材料310に形成されたスロット312に配置された後であっても、導電性材料310は絶縁性材料314の一端の周囲に広がることもあり、内側スタックスロット要素238の端にプレート246の導電性材料のサブブロック間の短絡領域248(例えば、電気接続または短絡)を作りだす。この短絡については特に階段状構造206について説明されたが、階段状構造のどれもがこのような特性を含み得る。

## [0055]

図 1 から図 4 に示されるような電子デバイス(例えば、メモリデバイス)は本開示の電子システムの実施形態に用いられ得る。例えば、図 1 0 は本開示にかかる実例的な電子システム 4 0 0 のプロック図である。この電子システム 4 0 0 は、例えば、コンピュータまたはコンピュータハードウェアコンポーネント、サーバまたは他のネットワークハードウェアコンポーネント、携帯電話、デジタルカメラ、携帯情報端末(PDA)、ポータブルメディアプレーヤー(例えば、携帯音楽プレーヤー)等で構成され得る。電子システム 4 0 0 は、図 1 から図 4 に示し、これらの図を参照して説明された電子デバイスの実施形態(例えば、導電性構造 1 0 0 、2 0 0 と半導体デバイス 1 0 2 、 2 0 2 )のうちの一つ等の電子デバイス 4 0 1 を少なくとも一つを含む。電子システム 4 0 0 は、さらに、少なく

とも一つの(通常、「マイクロプロセッサ」と呼ばれる)電子信号処理装置402を含んでいてもよい。さらに、電子システム400は、例えば、マウスまたは他のポインティングデバイス、キーボード、タッチパッド、ボタン、またはコントロールパネル等、ユーザが電子システム400へ情報を入力するための一つ以上の入力装置404を任意で含んでもよい。電子システム400は、例えば、モニター、ディスプレイ、プリンタ、スピーカ等、情報(例えば、映像または音声出力)をユーザに出力するための一つ以上の出力装置406を更に含んでいてもよい。これら一つ以上の入力装置404と出力装置406は電子デバイス401と電子信号処理装置402のうち少なくとも一つと電子通信を行い得る

### [0056]

本開示の実施形態は、面積ペナルティおよび/または特別な自己絶縁型接点プロセス( self insulating contact process)の必要なしに階段 状構造の内側の金属化を妨げることによって下部の回路と直接通信ができる接点(例えば 、階段状領域間のランディングに設置されるスルーアレイビア(through av vias,TAVs))を利用して、一つ以上の半導体デバイス(例えば、ワード 線ドライバ、メモリセル等のCMOSデバイス)と通信できる導電性構造(例えば、複数 の階段状領域を有する細長い階段状構造)を形成する際に特に有益となり得る。このよう な構成は、階段状導電性構造の側面からおよび側面を越えて延びる構成の階段状導電性構 造の外側に接点が延びる従来の導電性構造と比較すると導電性構造を貫通してより直接的 な接続ルートを実現し得る。また、接点が導電性構造を通って延びるこのような構成は、 導電性構造の下に設置される導電性要素への接続のルートを比較的簡素化し短くすること を 実 現 す る こ と に よ っ て 階 段 状 構 造 上 に 狭 い ピ ッ チ の 配 線 を 形 成 す る 必 要 性 が 低 減 し 得 る 。さらに、置換ゲート(RG)工程が実施される実施形態において、絶縁性材料または誘 電体材料を直接通るビアが形成されてもよく、これによって周囲の導電性材料からこのビ アを絶縁する余分な処理工程を不要としてもよい。またさらに、本明細書中に開示された 置換ゲート工程によって不連続的なスタックスロットを形成することは、サブブロック同 士を接続するための導電性の段を追加する必要なしに階段構造の段のサブブロック間で電 気接続を形成することを可能とする。不連続的なスタックスロットを形成することで、さ らに、置換ゲート工程で変えられていない、TAVを通して延ばすための誘電体領域がで きる(例えば、置換ゲート工程は一般的に誘電体材料の除去と再積層を必要とする)。こ のような置換ゲート工程で変えられていないTAV用の誘電体領域は、誘電体材料の再積 層中に起こり得る不均質および/または欠損があるフィリングによる問題に左右されにく い。そしてさらに、細長い階段構造は、階段構造の周囲に広がる外側のアクセス線を収容 するための階段のピッチを大きくせずに、比較的少数の階層状ワード線プレートから階段 構造を通ってアクセス線を効率的に通すのに利用される、階段間の断続的なランディング 領域を備える。そして、横方向に延びる段の長手方向に隣り合う階層(つまり、長手方向 軸 と 横 方 向 軸 の 両 方 に 沿 っ て 段 が 付 い た 階 段 ) を 含 む 従 来 の 階 段 構 造 に 比 べ 、 一 つ の 軸 の みに沿って延びる階段(例えば、長手方向軸に沿ってのみ段が付いた階段)を含む細長い 階段構造は、十分なランディング領域を各段に備えながらも、製造が比較的単純となり得 る(例えば、材料エッチングの際にばらつきに対してより広い許容範囲を有し得る)。

## [ 0 0 5 7 ]

したがって、導電性構造は、導電性構造の長さに沿って設置される階段状構造を含み、それぞれの階段状構造は少なくとも二つの導電性の段からなる。この少なくとも二つの導電性の段のうち、それぞれの導電性の段は、絶縁性材料によって、少なくとも二つの導電性の段のうちの隣り合う導電性の段から少なくとも部分的に分離されている。導電性構造は、さらに、導電性構造を貫通して延びる少なくとも一つのビアを備えるランディングを少なくとも一つ含む。この少なくとも一つのランディングは、複数の階段状構造の第一の階段状構造の際にある複数の階段状構造の第二の階段状構造の間に設置される。

## [0058]

10

20

30

20

30

40

50

さらに、装置はメモリセルとメモリセルの隣に設置される導電性構造を含んでいてもよい。導電性構造は、さらに、メモリセルの一部を選択する少なくとも一つの制御装置と少なくとも一つのランディングを通って少なくとも一つの制御装置へと延びる複数のビアを備える少なくとも一つのランディングを含む。この少なくとも一つのランディングは、複数の階段状構造の第一の階段状構造と複数の階段状構造の第二の階段状構造の間に設置される。

[0059]

そしてさらに、システムは、少なくとも一つの電子信号プロセッサ、この少なくとも一つの電子信号プロセッサと電子通信するよう構成された半導体デバイス、および導電性構造を含み得る。導電性構造は、導電性構造の長さに沿って設置される複数の階段状構造を含み、それぞれの階段状構造は半導体デバイスと電子通信を行う。導電性構造は、さらに、複数の階段状構造の第一の階段状構造と複数の階段状構造の第二の階段状構造の間に設置される、少なくとも一つのランディングを含む。この少なくとも一つのランディングは、交互になっている第一の材料と第二の材料を含み、第一の材料と第二の材料は絶縁性材料と交互になっている第一の材料と第二の材料を通って延びるビアを備える。

[0060]

また、さらに、導電性構造を形成する方法は、二つの階段状構造の間に画定される導電性構造のランディングに材料の層を通る開口部を形成することであって、この二つの階段状構造は半導体デバイス寄りの片側に設置されて半導体デバイスと電子通信を行い、層の開口部に複数の接点を形成する、階段状構造の少なくとも一段の導電性部分と複数の接点のうち少なくとも一つの接点を電気的に結合すること、を含み得る。

[0061]

更に、限定ではなく例としての実施形態が以下に説明される。

[0062]

実施形態 1 : 導電性構造であって、導電性構造の長さに沿って設置される複数の階段状構造であり、それぞれの階段状構造は少なくとも二つの導電性の段を含み、少なくとも二つの導電性の段のそれぞれの導電性の段は絶縁性材料によって少なくとも二つの導電性の段のうちの隣り合う導電性の段から少なくとも部分的に分離される、複数の階段状構造、導電性構造を通って延びる少なくとも一つのビアを含む少なくとも一つのランディングであって、複数の階段状構造の第一の階段状構造と第一の階段状構造の隣に設置される複数の階段状構造の第二の階段状構造の間に設置される少なくとも一つのランディング、および、複数のアクセス線であって、それぞれのアクセス線が少なくとも二つの導電性の段のうち一つの導電性の段の導電性部分から少なくとも一つのビアまで延びる複数のアクセス線を含む導電性構造。

[0063]

実施形態 2 : 実施形態 1 の導電性構造であって、少なくとも一つのビアは複数のビアからなり、それぞれのアクセス線が階段状構造の少なくとも二つの導電性の段のうち一つの 導電性の段の導電性部分から複数のビアのうち一つのビアへ延びる。

[0064]

実施形態 3 : 上記の実施形態のうちいずれかの導電性構造であって、少なくとも一対の 追加の階段状構造と少なくとも一つの追加のランディングを更に含み、少なくとも一対の 追加の階段状構造のそれぞれの追加の階段状構造は少なくとも一組の別の階段状構造の反 対側にあり少なくとも一つの追加のランディングが間にある。

[0065]

実施形態 4 : 上記の実施形態のうちいずれかの導電性構造であって、複数の階段状構造のうち少なくとも一つには少なくとも一つの階段状構造の導電性の段に接続されるアクセス線がない。

[0066]

実施形態 5 : 上記の実施形態のうちいずれかの導電性構造であって、少なくとも一つのランディングは複数のランディングからなり、複数のランディングのうちそれぞれのラン

ディングは一組の階段状構造の間に設置される。

#### [0067]

実施形態 6 : 上記の実施形態のうちいずれかの導電性構造であって、少なくとも一つのランディングは交互になっている第一の材料と第二の材料の層によって画定され、第一の材料と第二の材料はそれぞれ絶縁性材料を含む。

#### [0068]

実施形態 7 : 上記の実施形態のうちいずれかの導電性構造であって、少なくとも一つの ランディングは交互になっている第一の材料と第二の材料の層によって画定され、第一の 材料は導電性材料を含み、第二の材料は絶縁性材料を含む。

## [0069]

実施形態 8 : 実施形態 7 の導電性構造であって、少なくとも一つのビアを少なくとも部分的に囲み、少なくとも一つのビアを少なくとも一つのランディングの導電性材料から絶縁する絶縁性ライナーを更に含む。

## [0070]

実施形態 9 : 上記の実施形態のうちいずれかの導電性構造であって、少なくとも一つのビアは複数の階段状構造と少なくとも一つのランディングの下にある少なくとも一つの制御部と動作可能に結合される。

#### [0071]

実施形態 1 0 : 上記の実施形態のうちいずれかの導電性構造であって、複数の階段状構造のうち少なくともいくつかはそれぞれワード線プレート構造を含む。

#### [0072]

実施形態 1 1 : 上記の実施形態のうちいずれかの導電性構造であって、複数の階段状構造のうち一つの階段状構造がドレイン側選択ゲート(SGD)構造を含む。

#### [0073]

実施形態 1 2 : 上記の実施形態のうちいずれかの導電性構造であって、導電性構造の長さに沿って延びる複数のスタックスロット要素を更に含む。

### [0074]

実施形態13:実施形態12の導電性構造であって、複数のスタックスロット要素は導電性構造の長さの大部分に沿って連続的に延びる複数の外側スタックスロット要素、および導電性構造の長さに沿って不連続的に延びる複数の内側スタックスロット要素を含む。

#### [0075]

実施形態14:実施形態13の導電性構造であって、複数の内側スタックスロット要素は複数の階段状構造の最も近くに設置される。

### [0076]

実施形態 1 5 : 実施形態 1 4 の導電性構造であって、少なくとも一つのランディングには複数の内側スタックスロット要素がない。

## [0077]

実施形態 1 6 : 実施形態 1 3 から 1 5 の導電性構造であって、複数のスタックスロット要素は置換ゲート工程で積層される導電性材料の上に設置される絶縁性材料を含む。

#### [0078]

実施形態17:導電性構造であって、導電性構造の長さに沿って設置される複数の階層状構造であり、それぞれの階層状構造は導電性部分を含む少なくとも二つの階層を含み、少なくとも二つの階層のそれぞれの導電性部分は絶縁性材料によって少なくとも二つの階層のうちの隣り合う導電性部分から少なくとも部分的に分離される、複数の階段状構造、および、ランディングで導電性構造を通って延びる複数のビアを含むランディングであって、複数の階層状構造の第一の階層状構造と第一の階層状構造の隣に設置される複数の階層状構造の第二の階層状構造の間に設置されるランディング、を含む導電性構造。

### [0079]

実施形態18:実施形態17の導電性構造であって、複数の階層状構造の少なくとも二つの階層の複数の導電性部分を複数のビアのそれぞれのビアに結合する複数のアクセス線

10

20

30

40

を更に含む。

## [0800]

実施形態 1 9 : 実施形態 1 7 または 1 8 の導電性構造であって、導電性構造の長さに沿って延びる複数のスタックスロット要素を更に含み、複数のスタックスロット要素のうち少なくとも一つのスタックスロット要素は導電性構造の長さに沿って不連続的に延びる。

#### [0081]

実施形態 2 0 : 実施形態 1 9 の導電性構造であって、少なくとも一つの不連続的なスタックスロット要素は階層状構造の少なくとも一つの階層を第一のサブ階層部分と第二のサブ階層部分に少なくとも部分的に、物理的にも電気的にも分離する。

## [0082]

実施形態 2 1 : 実施形態 2 0 の導電性構造であって、少なくとも一つの不連続的なスタックスロット要素の端に沿って画定される少なくとも一つの階層での短絡によって第一のサブ階層部分と第二のサブ階層部分が電気的に接続される。

## [0083]

実施形態 2 2 : 実施形態 1 9 から 2 1 の導電性構造であって、少なくとも一つの不連続的なスタックスロット要素は、導電性構造の横方向側面から離された、複数の階層状構造のうち一つの階層状構造内に横方向に設置される。

#### [0084]

実施形態 2 3 : 実施形態 2 2 の導電性構造であって、複数のスタックスロット要素のうち少なくとも別のスタックスロット要素は導電性構造の長さに沿って連続的に延び、少なくとも一つの連続的スタックスロット要素は導電性構造の横方向の側面の少なくとも一部分を画定する。

### [0085]

実施形態 2 4 : 複数のメモリセルのアレイ、および複数のメモリセルのアレイの隣に設置される導電性構造を含む装置であって、導電性構造は、導電性構造の長さに沿って設置され、それぞれの階段状構造がアレイの複数のメモリセルと電気通信を行う複数の階段状構造、アレイの複数のメモリセルを選択するための少なくとも一つの制御部、少なくとも一つのランディングを通り少なくとも一つの制御部へ延びる複数のビアを含む少なくとも一つのランディングであって、複数の階層状構造の第一の階層状構造と複数の階層状構造の第二の階層状構造の間に設置される少なくとも一つのランディング、および階段状構造の導電性部分と複数のビアの第一の端の間に結合される複数のアクセス線であって、複数のビアの第二の端は少なくとも一つの制御部と電気的に結合される複数のアクセス線、を含む。

## [0086]

実施形態 2 5 : 実施形態 2 4 の装置であって、階段状構造は複数のワード線プレートを含む。

## [0087]

実施形態 2 6 : 実施形態 2 4 または 2 5 の装置であって、複数のワード線プレートのそれぞれのワード線プレートは複数のワード線プレートのうち隣のワード線プレートの接点部から横方向にずれている接点部を含み、複数のアクセス線のそれぞれのアクセス線は複数のワード線プレートのそれぞれ一つと通信を行い、複数のワード線プレートのそれぞれ一つを複数のビアのそれぞれ一つと結合する。

### [0088]

実施形態27:少なくとも一つの電子信号処理装置、少なくとも一つの電子信号処理装置と電気的に通信するように構成される半導体デバイス、および導電性構造を含むシステムであって、導電性構造は、導電性構造の長さに沿って設置され、それぞれの階段状構造が半導体デバイスと電気通信を行う複数の階段状構造、複数の階段状構造のうち第一の階段状構造と複数の階段状構造のうち第二の階段状構造の間に設置される少なくとも一つのランディングであって、交互になっている第一の材料と第二の材料は絶縁性材料を含む少なくとも一つのランディング、および第一の材料と第二

10

20

30

40

の材料を通って延びる複数のビア、を含む。

## [0089]

実施形態 2 8 : 実施形態 2 7 のシステムであって、導電性構造の横方向の外側の境界から横方向に間隔をあけておかれる少なくとも一つのスタックスロット要素を更に含み、少なくとも一つのスタックスロット要素は階段状構造に最も近い導電性構造の長さに沿ってのみ延びている。

#### [0090]

実施形態29:実施形態28のシステムであって、スタックスロット要素は絶縁性材料と導電性材料を含み、導電性材料は階段状構造の一段の導電性部分を画定する。

#### [0091]

実施形態 3 0 : 実施形態 2 9 の導電性構造であって、複数のアクセス線を更に含み、それぞれのアクセス線は階段状構造の一段の導電性部分を複数のビアのそれぞれのビアに結合する。

## [0092]

実施形態 3 1 : 導電性構造を形成する方法であって、この方法は、二つの階段状構造の間に画定される導電性構造のランディングに材料の層を通して複数の開口部を形成する工程であって、二つの階段状構造は半導体デバイス寄りの片側に設置され電子通信を行い、材料の層の複数の開口部に複数の接点を形成する工程、および階段状構造の少なくとも一段の導電性部分と複数の接点のうち少なくとも一つの接点を電気的に結合する工程、を含む。

#### [0093]

実施形態32:実施形態31の方法であって、交互になっている絶縁性と導電性の材料で材料の層を形成する工程を更に含む。

#### [0094]

実施形態 3 3 : 実施形態 3 2 の方法であって、複数の開口部のそれぞれの開口部に、その中にある接点を囲むためのライナーを形成する工程を更に含む。

#### [0095]

実施形態34:実施形態31から33の方法であって、第一の絶縁性材料と第二の犠牲 絶縁性材料の交互になっている絶縁性材料で材料の層を形成する工程を更に含む。

## [0096]

実施形態 3 5 : 実施形態 3 4 の方法であって、材料の層を通る開口部を形成する工程、開口部の隣にある第二の犠牲絶縁材料の一部を第一の絶縁性材料の下にある第二の犠牲材料のある容量の分だけ除去する工程、および第二の犠牲材料の一部を除去した容量の分の導電性材料を開口部に積層し、階段状構造の少なくとも一段の導電性部分を形成する工程、を更に含む。

#### [0097]

実施形態36:実施形態35の方法であって、開口部内の導電性材料の一部を除去する工程、および開口部内に別の絶縁性材料を積層する工程、を更に含む。

#### [0098]

実施形態37:実施形態36の方法であって、別の絶縁性材料の周辺で、階段状構造の少なくとも一段の導電性部分と少なくとも一段の隣り合う別の導電性部分の間に電気接続を形成する工程、を更に含む。

### [0099]

実施形態38:実施形態31から37の方法であって、導電性構造のランディングをマスクして、複数の階段状構造のうち少なくとも一つの階段状構造に対して置換ゲート工程を行う工程、を更に含む。

#### [0100]

本開示は各種の変更や代替の形態が可能であるが、特定の実施形態が図面に例として示され本明細書中に詳細に説明されている。しかしながら、本開示はこの開示された特定の形態に限定されることを意図していない。本開示は、むしろ、以下に添付の請求項および

10

20

30

40

それらの法的均等物により定義されるような本開示の範囲内に属する全ての変更、組み合 わせ、均等物、および代替物を包含する。

### 【符号の説明】

## [0101]

- 100 導電性構造

- 1 0 1 制御装置

- 102 半導体デバイス

- 導 電 性 材 料 1 0 3

- 104 基板

- 1 0 5 絶縁性材料

- 106、107、108、109、110、111 階段状構造

- 112 ランディング

- 114、116、118、120、122 段(ステップ)

- 1 2 6 コンタクトホール

- 128 導電性接点(導電性コンタクト)

- 1 3 0 制御部

- 132 アクセス線

- 1 3 6 選択ゲート

- 200 導電性構造

- 2 0 2 半導体デバイス

- 206、207、208、209、210 211 階段状構造

- 2 1 2 ランディング

- 238、240 スタックスロット要素

- 3 0 0 材料の積層

- 3 0 2 基 板

- 3 0 4 絶縁性材料

- 3 0 6 犠牲材料

- 3 0 8 スロット

- 3 1 0 導電性材料

- 3 1 2 スロット

- 3 1 4 絶縁性材料

10

20

【図1】

【図2】

【図3】

【図4】

## フロントページの続き

(51) Int.CI. F I テーマコード (参考)

H 0 1 L 27/11556 (2017.01) H 0 1 L 27/11548 (2017.01)

(72)発明者 テッサリオル,パオロ

イタリア共和国,ヴェネト州 31044,モンテベッルーナ,ヴィア ガツィエ 56

(72)発明者 ウォルステンホルム,グラハム アール.

アメリカ合衆国,アイダホ州 83706,ボイズ,イーストリバーネスト コート 2945

(72)発明者 イップ,アーロン

アメリカ合衆国,カリフォルニア州 95030,ロス ガトス,ビスタ デ シエラ 254

F ターム(参考) 5F083 EP22 EP33 EP76 ER22 GA10 HA02 HA06 HA07 JA38 JA39

JA40 KA01 LA03 LA05 LA10 LA16 MA06 MA16

5F101 BB02 BD16 BD22 BD30 BD34 BE11