(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11) 特許番号

特許第3831353号 (P3831353)

(45) 発行日 平成18年10月11日 (2006.10.11)

(24) 登録日 平成18年7月21日 (2006.7.21)

(51) Int.C1. F 1

HO 1 L

27/105

(2006.01)

HO 1 L

27/10

4 4 7

HO 1 L

21/8246

(2006.01)

G 1 1 C

11/15

1 1 O

G 1 1 C

11/15

(2006.01)

HO 1 L

43/08

Z

HO1L 43/08 (2006.01)

請求項の数 12 (全 14 頁)

(21) 出願番号 特願2003-88413 (P2003-88413) (22) 出願日 平成15年3月27日 (2003.3.27)

(65) 公開番号 特開2004-296869 (P2004-296869A) (43) 公開日 平成16年10月21日 (2004.10.21) 審査請求日 平成15年8月26日 (2003.8.26) (73) 特許権者 000003078 株式会社東芝

東京都港区芝浦一丁目1番1号

(74)代理人 100058479

弁理士 鈴江 武彦

(74)代理人 100091351

弁理士 河野 哲

(74) 代理人 100088683

弁理士 中村 誠

|(74)代理人 100108855

弁理士 蔵田 昌俊

|(74)代理人 100084618

弁理士 村松 貞男

(74)代理人 100092196

弁理士 橋本 良郎

最終頁に続く

(54) 【発明の名称】磁気ランダムアクセスメモリ

## (57)【特許請求の範囲】

#### 【請求項1】

直交方向に交差するように配置された第1の配線および第2の配線と、

前記第1、第2の配線の交点に対応して配置され、磁性膜からなる固定層と自由層との間に非磁性層が挟まれた構造によってトンネル磁気抵抗効果を有し、長方形の長辺が前記第2の配線に沿い、短辺が前記第1の配線に沿い、長辺方向に沿うようにスピン方向が付与され、長辺軸を中心として短辺方向の中央部が上に凸となるように弯曲した形状を有する上面及び長辺軸を中心として短辺方向の中央部が下に凹となるように弯曲した形状を有する下面を有するトンネル磁気抵抗素子と、

前記トンネル磁気抵抗素子の上面を覆うように形成された導電性のハードマスクと、

前記ハードマスクと前記第1の配線とを電気的に接続する導電性のコンタクトと、

前記トンネル磁気抵抗素子の下面に接する接続用配線と、

前記接続用配線と前記第2の配線との間に介在する層間絶縁膜

とを具備することを特徴とする磁気ランダムアクセスメモリ。

### 【請求項2】

前記ハードマスクの材質はタンタルであることを特徴とする請求項1記載の磁気ランダム アクセスメモリ。

## 【請求項3】

前記層間絶縁膜は、前記トンネル磁気抵抗素子の<u>下面</u>に対向する部分がそれに連なる他の部分よりも突出していることを特徴とする請求項1または2記載の磁気ランダムアクセ

20

#### スメモリ。

### 【請求項4】

前記トンネル磁気抵抗素子の弯曲状態の短辺の両先端間の弦の長さよりも前記第2の配線の幅の方が狭いことを特徴とする請求項1乃至3のいずれか1項に記載の磁気ランダムアクセスメモリ。

#### 【請求項5】

前記トンネル磁気抵抗素子は、半導体基板上で複数の第1の配線と複数の第2の配線がそれぞれ交差する各交点に対応してアレイ状に配置されており、

前記第1の配線は書き込み/読み出し用のビット線であり、前記第2の配線は書き込みワード線であることを特徴とする請求項3または4記載の磁気ランダムアクセスメモリ。

### 【請求項6】

前記接続用配線を介して前記トンネル磁気抵抗素子に直列に電気的に接続され、前記半導体基板に形成されたドレイン・ソース領域を有する読み出しスイッチ用トランジスタをさらに具備することを特徴とする請求項1乃至5のいずれか1項に記載の磁気ランダムアクセスメモリ。

#### 【請求項7】

直交方向に交差するように配置された第1の配線および第2の配線と、

前記第1、第2の配線の交点に対応して配置され、磁性膜からなる固定層と自由層との間に非磁性層が挟まれた構造によってトンネル磁気抵抗効果を有し、長方形の長辺が前記第2の配線に沿い、短辺が前記第1の配線に沿い、長辺方向に沿うようにスピン方向が付与され、短辺軸を中心として長辺方向の中央部が上に凹となるように弯曲した形状を有する上面及び短辺軸を中心として長辺方向の中央部が下に凸となるように弯曲した形状を有する下面を有するトンネル磁気抵抗素子と、

前記トンネル磁気抵抗素子の上面を覆うように形成された導電性のハードマスクと、

前記ハードマスクと前記第1の配線とを電気的に接続する導電性のコンタクトと、

前記トンネル磁気抵抗素子の下面に接する接続用配線と、

前記接続用配線と前記第2の配線との間に介在する層間絶縁膜

とを具備することを特徴とする磁気ランダムアクセスメモリ。

### 【請求項8】

前記ハードマスクの材質はタンタルであることを特徴とする請求項 7 記載の磁気ランダム 30 アクセスメモリ。

## 【請求項9】

前記層間絶縁膜は、前記トンネル磁気抵抗素子の<u>下面</u>に対向する部分がそれに連なる他の部分よりも凹没していることを特徴とする請求項7または8記載の磁気ランダムアクセスメモリ。

### 【請求項10】

前記トンネル磁気抵抗素子の弯曲状態の長辺の両先端間の弦の長さよりも前記第1の配線の幅の方が狭いことを特徴とする請求項7至9のいずれか1項に記載の磁気ランダムアクセスメモリ。

### 【請求項11】

前記トンネル磁気抵抗素子は、複数の第1の配線と複数の第2の配線がそれぞれ交差する 各交点に対応してアレイ状に配置されており、

前記第1の配線はビット線であり、前記第2の配線は書き込みワード線であることを特徴とする請求項9または10記載の磁気ランダムアクセスメモリ。

## 【請求項12】

前記接続用配線を介して前記トンネル磁気抵抗素子に直列に電気的に接続され、前記半導体基板に形成されたドレイン・ソース領域を有する読み出しスイッチ用トランジスタをさらに具備することを特徴とする請求項7乃至11のいずれか1項に記載の磁気ランダムアクセスメモリ。

### 【発明の詳細な説明】

40

10

### [0001]

## 【発明の属する技術分野】

本発明は、磁気ランダムアクセスメモリ(Magnetic Random Access Memory; MRAM)に係り、特にトンネル型磁気抵抗効果により"1"/"0" 情報の記憶を行う素子を利用して構成した磁気メモリセルを行列状に配置したMRAMにおけるメモリセルの構造に関する。

#### [00002]

### 【従来の技術】

近年、新たな原理により情報を記憶するメモリが数多く提案されているが、そのうちの一つに、トンネル型磁気抵抗(Tunneling Magneto Resistive: 以後、TMR と表記する)効果を用いて"1"/"0"情報の記憶を行う強磁性トンネル接合(Magnetic Tunnel Junction; MT J)素子を利用して構成した磁気メモリセルを行列状に配置したMRAMが提案されている(例えば、非特許文献 1 参照)。

#### [0003]

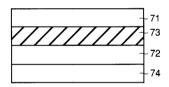

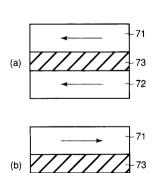

図8は、従来のMRAMで用いられるMTJ 素子の断面構造を概略的に示す。

#### [0004]

このMTJ 素子は、2つの磁性層(強磁性層、強磁性体膜)71,72 で1つの非磁性層(トンネルバリア膜)73を挟んだ構造を有し、2つの磁性層71,72 のスピンの向きが平行であるか反平行であるかによって"1"/"0"情報を記憶する。

## [0005]

通常、2つの磁性層71,72の一方側には反強磁性層74が配置される。反強磁性層74は、一方側の磁性層72のスピンの向きを固定することによって、他方側の磁性層71のスピンの向きのみを変えることにより情報を容易に書き換えるための部材である。ここで、スピン可変側の磁性層71は自由層(または記録層)、スピン固定側の磁性層72は固定層(またはピン層)と呼ばれる。

#### [0006]

図 9 ( a ) および ( b ) は、図 8 に示したMTJ 素子の 2 つの磁性層71,72 のスピンの向きを示している。

#### [0007]

図9(a)に示すように、2つの磁性層71,72のスピンの向き(図示矢印の向き)が平行(同じ)である場合は、2つの磁性層71,72に挟まれた絶縁層73のトンネル抵抗は最も低くなる(トンネル電流が最も大きくなる)。

## [0008]

図9(b)に示すように、2つの磁性層71,72のスピンの向きが反平行である場合は、2つの磁性層71,72に挟まれた絶縁層73のトンネル抵抗は最も高くなる(トンネル電流が最も小さくなる)。

### [0009]

MRAMでは、MTJ 素子の抵抗値が異なる 2 つの状態を、" 1 "情報の記憶状態(" 1 "状態) および" 0 "情報の記憶状態(" 0 "状態)に対応させている。

#### [ 0 0 1 0 ]

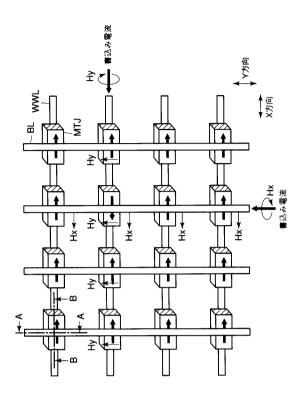

図 1 0 は、MRAMのセルアレイの一部の平面的なレイアウトの一例を模式的に示す図である 40

#### [0011]

複数の書き込み / 読み出し用のビット線BLと複数の書き込みワード線WWL が直交方向に配設され、その各交点に対応してMTJ 素子が配設される。このMTJ 素子は、長方形の長辺が書き込みワード線WWL に沿い、短辺がビット線BLに沿い、長辺方向に沿うようにスピン方向が付与されている。

### [0012]

各ビット線BLは、同一行(または列)の複数のMTJ素子の各固定層に接続されており、各書き込みワード線WWL は同一列(または行)の複数のMTJ素子の各自由層に近接して対向するように配置されている。

50

20

#### [0013]

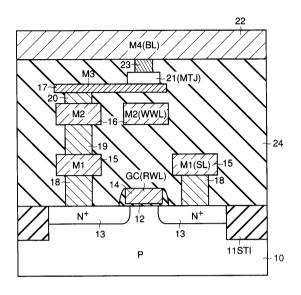

図 1 1 は、図 1 0 中の A - A 線に沿って書き込みワード線に垂直な断面におけるメモリセルの 1 個分に着目して構造の一例を示す断面図である。

#### [0014]

図12は、図10中のB-B線に沿ってビット線に垂直な断面における構造の一例を示す 断面図である。

#### [0015]

図11および図12において、10は半導体基板(例えばP型Si基板)、11はシャロウトレンチ型の素子分離領域(STI)、12はゲート酸化膜、13はスイッチ素子用のNMOSFETのドレイン領域またはソース領域となる不純物拡散層(N+)、14はゲート電極GC(読み出しワード線RWL)、15は第1金属配線層(M1)、16は第2金属配線層(M2)、17は第3金属配線層(M3)からなるMTJ接続用配線、18は第1金属配線層15を拡散層13へ電気的に接続するための導電性のコンタクト、19は第2金属配線層16から第1金属配線層15へ電気的に接続するための導電性のコンタクト、20は第3金属配線層17から第2金属配線層16へ電気的に接続するための導電性のコンタクト、21はMTJ素子、22は第4配線層(M4)、23は第4金属配線層22をMTJ素子21へ電気的に接続するための導電性のコンタクト、24は層間絶縁膜である。

#### [0016]

なお、図中、配線の用途として、(BL)は書き込み / 読み出し用のビット線、(WWL) は書き込みワード線、(SL)はソース線、(RWL) は読み出しワード線を表わしており、ソース線(SL)は接地電位に接続される。

### [0017]

次に、図10乃至図12を参照してMTJ素子に対する書き込み動作原理を説明する。

### [0018]

MTJ 素子に対する書き込みは、書き込みワード線WWL およびビット線(データ選択線)BLに電流を流し、両配線に流れる電流により作られる磁界を用いてMTJ素子のスピンの向きを平行または反平行にすることにより達成される。

#### [0019]

即ち、MTJ 素子へ情報を書き込む時には、ビット線BLには書き込みデータに応じて第1の方向またはそれとは逆の第2の方向に向かう電流を流して磁界Hxを発生させ、書き込みワード線WWL には第1の方向に向かう電流のみを流して磁界Hyを発生させることにより、合成磁界を用いて情報を書き込む。この際、ビット線BLに第1の方向に向かう電流を流すと、MTJ 素子のスピンの向きは平行となり、ビット線BLに第2の方向に向かう電流を流すと、MTJ 素子のスピンの向きは反平行となる。

### [0020]

MTJ 素子から情報を読み出す時には、読み出しワード線RWL を活性化させ、選択されたMT J 素子に接続されるスイッチ素子のみをオン状態として電流経路を作り、選択されたビット線BLから接地電位へ電流を流す。その結果、選択されたMTJ 素子のみにその抵抗値に応じた電流が流れるので、その電流値を検出することにより情報を読み出すことができる。

### [0021]

次に、MTJ素子のスピンの向きが変わる仕組みについて簡単に説明する。

## [0022]

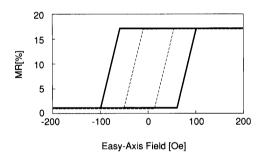

図13は、MTJ 素子の印加磁界の反転による抵抗値の変化特性(TMR 曲線)を示している

## [0023]

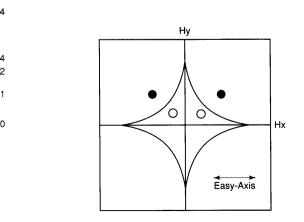

図14は、MTJ 素子のアステロイド曲線を示している。

## [0024]

図13に示すTMR 曲線のように、MTJ 素子の長辺(Easy-Axis 、容易軸)方向に磁界Hxをかけると、MTJ 素子の抵抗値は例えば17%程度変化する。この変化率(変化の前後の抵抗の比)は、MR比と呼ばれる。なお、MR比は、MTJ 素子の磁性層の性質により変化する。現在では、MR比が50%程度のMTJ 素子も得られている。

20

30

40

#### [0025]

MTJ 素子には、Easy-Axis 方向の磁界HxとHard-Axis (困難軸)方向の磁界Hyとの合成磁界が印加される。図13中の実線および点線に示すように、Hard-Axis 方向の磁界Hyの大きさによって、MTJ 素子の抵抗値を変えるために必要なEasy-Axis 方向の磁界Hxの大きさも変化する。

#### [0026]

この現象を利用することにより、アレイ状に配置されるメモリセルのうち、選択された書き込みワード線WWL および選択されたビット線BLの交点に対応して配置されているMTJ 素子のみにデータを書き込むことができる。この様子を図14に示すアステロイド曲線を用いて説明する。

### [0027]

図14中に示すように、Easy-Axis 方向の磁界HxとHard-Axis 方向の磁界Hyとの合成磁界の大きさがアステロイド曲線の外側(例えば、黒丸の位置)にあれば、MTJ 素子の磁性層のスピンの向きを反転させることができる。

#### [0028]

逆に、Easy-Axis 方向の磁界HxとHard-Axis 方向の磁界Hyとの合成磁界の大きさがアステロイド曲線の内側(例えば、白丸の位置)にある場合には、MTJ 素子の磁性層のスピンの向きを反転させることはできない。

#### [0029]

従って、Easy-Axis 方向の磁界HxとHard-Axis 方向の磁界Hyとの合成磁界の大きさを変え、合成磁界の大きさのHx-Hy 平面内における位置を変えることにより、MTJ 素子に対するデータの書き込みを制御できる。

### [0030]

ところで、書き込みワード線WWL とMTJ 素子との間の距離が書き込みビット線とMTJ 素子との間の距離よりも長く、書き込みワード線により多くの電流を流さなければならない。この書き込みワード線WWL から発生した磁界は、ループ状の曲線に沿って分布しており、従来は、MTJ 素子の自由層の中心部と端部で印加される磁界強度が異なっており、反転磁界に起因して書き込み電流が大きくなり、実用化の課題となっている。

## [0031]

### 【非特許文献1】

Roy Scheuerlein et.al."A 10ns Read and Write Non-Volatile Memory Array Using a Magnetic Tunnel Junction and FET Switch in each Cell", ISSCC2000 Technical Digest pp.128 ~ pp.129

### [0032]

## 【発明が解決しようとする課題】

上記したように従来のMRAMは、書き込み電流が大きい点が実用化上の課題となっている。

#### [0033]

本発明は上記の問題点を解決すべくなされたもので、書き込み電流を低減し得る磁気ランダムアクセスメモリを提供することを目的とする。

#### [0034]

## 【課題を解決するための手段】

本発明の第1の態様に係る磁気ランダムアクセスメモリは、交方向に交差するように配置された第1の配線および第2の配線と、前記第1、第2の配線の交点に対応して配置され、磁性膜からなる固定層と自由層との間に非磁性層が挟まれた構造によってトンネル磁気抵抗効果を有し、長方形の長辺が前記第2の配線に沿い、短辺が前記第1の配線に沿い、長辺方向に沿うようにスピン方向が付与され、長辺軸を中心として短辺方向の中央部が上に凸となるように弯曲した形状を有する上面及び長辺軸を中心として短辺方向の中央部が下に凹となるように弯曲した形状を有する下面を有するトンネル磁気抵抗素子と、前記トンネル磁気抵抗素子の上面を覆うように形成された導電性のハードマスクと、前記ハードマスクと前記第1の配線とを電気的に接続する導電性のコンタクトと、前記トンネル磁

10

20

30

40

気抵抗素子の<u>下面</u>に接する接続用配線と、前記接続用配線と前記第2の配線との間に介在する層間絶縁膜とを具備することを特徴とする。

#### [0035]

本発明の第2の態様に係る磁気ランダムアクセスメモリは、直交方向に交差するように配置された第1の配線および第2の配線と、前記第1、第2の配線の交点に対応して配置され、磁性膜からなる固定層と自由層との間に非磁性層が挟まれた構造によってトンネル磁気抵抗効果を有し、長方形の長辺が前記第2の配線に沿い、短辺が前記第1の配線に沿い、長辺方向に沿うようにスピン方向が付与され、短辺軸を中心として長辺方向の中央部が上に凹となるように弯曲した形状を有する上面及び短辺軸を中心として長辺方向の中央部が下に凸となるように弯曲した形状を有する下面を有するトンネル磁気抵抗素子と、前記トンネル磁気抵抗素子の上面を覆うように形成された導電性のハードマスクと、前記ハードマスクと前記第1の配線とを電気的に接続する導電性のコンタクトと、前記トンネル磁気抵抗素子の下面に接する接続用配線と、前記接続用配線と前記第2の配線との間に介在する層間絶縁膜とを具備することを特徴とする。

#### [0036]

#### 【発明の実施の形態】

以下、図面を参照して本発明の実施の形態を詳細に説明する。

### [0037]

#### <第1の実施形態>

第1の実施形態に係るMRAMは、図10を参照して前述したようなMTJ素子のアレイを有するものであり、複数の書き込み/読み出し用のビット線BL(第1の配線)と複数の書き込みワード線WWL (第2の配線)が直交方向に配設され、その各交点に対応してMTJ素子が配設されている。

#### [0038]

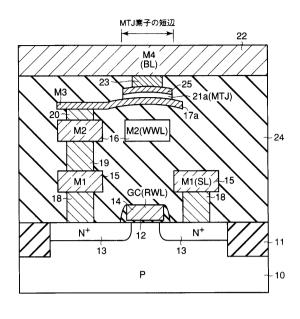

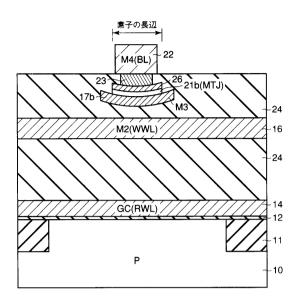

図1は、本発明の第1の実施形態に係るMRAMにおけるセルアレイの一部に沿って書き込みワード線に垂直な断面におけるメモリセルの1個分に着目してMTJ素子部およびスイッチ用NMOSFET 部の構造の一例を示す断面図である。

#### [0039]

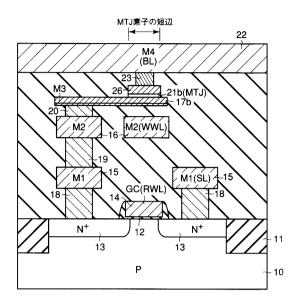

図2は、図1中のビット線に垂直な断面における構造の一例を示す断面図である。

#### [0040]

図 1 および図 2 において、10は半導体基板(例えば P 型 S i 基板)、11はシャロウトレンチ型の素子分離領域 (STI) 、12はゲート酸化膜、13はスイッチ素子用のNMOSFET のドレイン領域またはソース領域となる不純物拡散層 (N+)、14はゲート電極GC (読み出しワード線RWL)、15は第 1 金属配線層 (M1)、16は第 2 金属配線層 (M2)、17a は第 3 金属配線層 (M3)からなるMTJ 接続用配線、18は第 1 金属配線層15を拡散層13へ電気的に接続するための導電性のコンタクト、19は第 2 金属配線層16から第 1 金属配線層15へ電気的に接続するための導電性のコンタクト、20は第 3 金属配線層17から第 2 金属配線層16へ電気的に接続するための導電性のコンタクト、21a はMTJ 素子、22は第 4 金属配線層 (M4)、23は第 4 金属配線層22をMTJ 素子21a へ電気的に接続するための導電性のコンタクト、24は層間絶縁膜である。

## [0041]

なお、図中、配線の用途として、(BL)は書き込み / 読み出し用のビット線、(WWL) は書き込みワード線、(SL)はソース線、(RWL) は読み出しワード線を表わしており、ソース線(SL)は接地電位に接続される。

## [0042]

本例で使用されているMTJ 素子21a は、図 8 を参照して前述した従来のMTJ 素子と比べて、長方形(あるいは楕円形)の長辺軸を中心として短辺方向の中央部がビット線BLの方向に向かって膨らむ状態、つまり上面が長辺軸を中心として短辺方向の中央部が上に凸となるように弯曲した形状を有し、かつ下面が長辺軸を中心として短辺方向の中央部が下に凹となるように弯曲した形状を有する点が異なり、その他は同じである。即ち、スピン可

10

20

30

40

20

30

40

50

変側の自由層71とスピン固定側の固定層72との間にトンネルバリア膜73が挟まれた構造によってトンネル磁気抵抗効果を有する。そして、長辺が書き込みワード線WWL に沿い、短辺がビット線BLに沿い、長辺方向に沿うように書き込み容易軸(スピン方向)が付与されている。

## [0043]

このMTJ 素子21a の<u>上面</u>を覆うように導電性のハードマスク(例えばタンタルTa)25が形成され、MTJ 素子21a とビット線BLはハードマスク25を介して導電性のコンタクト23により電気的に接続されており、MTJ 素子21a の<u>下面</u>に接するように金属(例えばタンタルTa)からなるMTJ 接続用配線17a が形成されており、この接続用配線17a と書き込みワード線WWL との間に層間絶縁膜24が介在している。この層間絶縁膜24は、MTJ 素子21a の弯曲上下に対向する部分がそれに連なる他の部分よりもビット線BLの方向に向かって突出している。

#### [0044]

上記した第1の実施形態のMRAMは、MTJ 素子21a の長辺方向(スピン方向)がビット線BLと直交しており、書き込みワード線WWL から発生する磁界曲線にほぼ一致させるようにMT J 素子21a を反らせている。これにより、弯曲状態のMTJ 素子21a の自由層71の幅方向(短辺方向)の中心部と端部で印加される磁界強度が等しくなる。結果として、反転磁界が低減され、書き込み効率が向上し、書き込み電流が低減される。この場合、MTJ 素子21a の自由層の幅方向の端部に印加される磁界強度を強めるために、弯曲状態のMTJ 素子21a の短辺の両先端間の弦の長さが書き込みワード線WWL の幅よりも広いことが望ましい。

#### [0045]

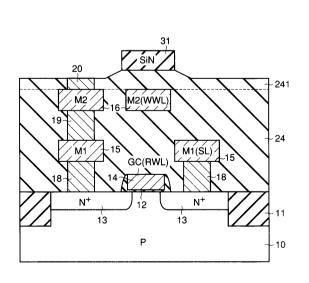

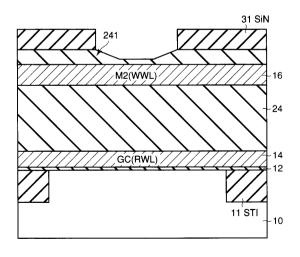

図3は、図1および図2に示した構造の形成工程の一例の一部について書き込みワード線に垂直な断面における構造を示す断面図である。層間絶縁膜24は複数層の絶縁膜からなり、ここでは説明の簡単化のために一部241 のみ説明する。

### [0046]

まず、P型Si基板10の表層部に選択的に素子分離領域STI 11を形成し、スイッチ用NMOSFETのゲート絶縁膜12、ゲート電極(GC)(読み出しワード線RWL)14、N+拡散層13からなるドレイン領域およびソース領域を形成する。次に、ドレイン領域上およびソース領域上にコンタクト18を形成し、さらに第1金属配線層(M1)15を形成する。次に、第1金属配線層15上にコンタクト19を形成し、さらに第2金属配線層(M2)(例えばCu配線)16を形成し、600nm程度の厚さの層間絶縁膜241(例えばHDP)および300nm程度の厚さの窒化シリコン(SiN)膜31を堆積する。

#### [0047]

次に、リソグラフィー技術および反応性イオンエッチング(RIE) 技術を用いてSiN 膜31を 所望のパターン形状にし、このSiN 膜31のパターンをマスクとして層間絶縁膜241 を斜め に角度を持たせてエッチング加工(ミリング)する。

## [0048]

この場合、後でMTJ 素子21a を繰り返しパターンとして形成するために、MTJ素子21a 相互間のスペース領域が溝となるように繰り返しパターンとして形成する。これにより、層間絶縁膜241 のうちで後工程でその上にMTJ 素子21a が形成される部分は、他の部分よりも上側に凸の状態になる。

## [0049]

次に、SiN 膜31のパターンを除去した後、図 1 中に示したように、第 2 金属配線層 16上にコンタクト20を形成し、さらに第 3 金属配線層 (M3) (例えばTa) 17aを30nm程度の厚さに堆積し、さらにMTJ 素子21a の各層を順次堆積し、さらに、ハードマスク(例えばTa) 25を150nm 程度の厚さに形成する。ここで、MTJ 素子21a の自由層は、通常、NiFeが使用されるが、CoNiFe,CoFe,CoCr,CoPt などを用いることも可能である。

#### [0050]

そして、リソグラフィー技術とRIE 技術を用いて、ハードマスク25およびMTJ 素子21a を 所望のパターン形状に加工し、さらに、リソグラフィー技術とRIE 技術を用いて、第3金 属配線層17a を所望のパターンに加工してMTJ 接続用配線を形成する。この場合、第3金属配線層17a の一部(前述したように層間絶縁膜241のうちで上側に凸の状態の部分上に形成されている部分) およびその上に形成されているMTJ 素子21a は、それぞれ上側に凸の状態に弯曲している。

### [0051]

次に、MTJ 素子21a の上面側のハードマスク25にコンタクトするコンタクト23および第 4 金属配線層 (M4)22を形成する。

### [0052]

なお、MTJ 素子21a とハードマスク25の厚さの比や材質の違いによる熱膨脹係数の違いを利用して前記したように弯曲させることも可能である。

### [0053]

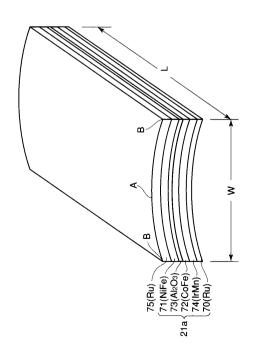

図 4 は、図 1 中のMTJ 素子21a 部を取り出してその積層構造の一例について詳細に説明する。

## [0054]

この積層構造は、図 1 中の第 3 金属配線層(M3)17a (例えばTa、30nm程度の厚さ)上に、バッファ層70、反強磁性層74、固定層72、トンネルバリア膜73、自由層71、キャップ層75が順次積層されており、その上に図 1 中のハードマスク(例えばTa、150nm 程度の厚さ)25が形成される。

#### [0055]

ここで、バッファ層70は、例えばRuからなり、3nm 程度の厚さである。反強磁性層74は、例えばIrMnからなり、10nm程度の厚さである。固定層72は、例えばCoFeからなり、3nm 程度の厚さである。トンネルバリア膜73は、例えばAI $_2$ O $_3$ からなり、1.5nm 程度の厚さである。自由層71は、例えばNiFeからなり、6nm 程度の厚さである。キャップ層75は、例えばRuからなり、10nm程度の厚さである。

#### [0056]

MTJ 素子21a 部のサイズの一例として、短辺方向の幅Wが $0.4~\mu$ m、長辺方向の長さLが 1.2  $\mu$ mとすると、短辺方向の中央の頂点Aに対して両端Bがそれぞれ例えば5nm 低くなるように上側に凸の状態に弯曲しており、その場合の曲率半径は $4~\mu$ m程度である。

## [0057]

## <第2の実施形態>

第2の実施形態に係るMRAMは、図10を参照して前述したようなMTJ素子のアレイを有するものであり、複数の書き込み/読み出し用のビット線BL(第1の配線)と複数の書き込みワード線WWL (第2の配線)が直交方向に配設され、その各交点に対応してMTJ素子21bが配設されている。

### [0058]

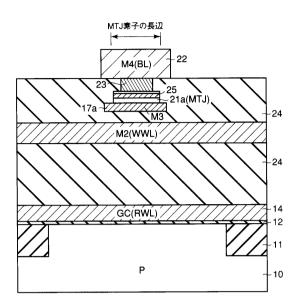

図 5 は、本発明の第 2 の実施形態に係るMRAMにおけるセルアレイの一部に沿ってビット線に垂直な断面における構造の一例を示す断面図である。

#### [0059]

図 6 は、図 5 中の書き込みワード線に垂直な断面におけるメモリセルの 1 個分に着目して MTJ 素子部およびスイッチ用NMOSFET 部の構造の一例を示す断面図である。

## [0060]

図5および図6に示す構造は、図1および図2に示した構造と比べて、MTJ素子21bの弯曲状態が異なり、その他は同じであるので図1中および図2中と同じ符号を付してその説明を省略する。

## [0061]

即ち、本例で使用されているMTJ 素子21b は、長方形(あるいは楕円形)の短辺軸を中心として長辺方向の中央部が書き込みワード線WWL の方向に向かって膨らむ状態、<u>つまり上面が短辺軸を中心として長辺方向の中央部が上に凹となるように弯曲した形状を有し、かつ下面が短辺軸を中心として長辺方向の中央部が下に凸となるように弯曲した形状を有</u>する。即ち、図8に示したように、スピン可変側の自由層71とスピン固定側の固定層72と

10

20

30

50

の間にトンネルバリア膜73が挟まれた構造によってトンネル磁気抵抗効果を有する。そして、長辺が書き込みワード線WWL に沿い、短辺がビット線BLに沿い、長辺方向に沿うように書き込み容易軸(スピン方向)が付与されている。

## [0062]

このMTJ 素子21b の上面を覆うように導電性のハードマスク(例えばタンタルTa)26が形成され、MTJ 素子21b とビット線BLはハードマスク26を介して導電性のコンタクト23により電気的に接続されており、MTJ 素子21b の下面に接するように金属(例えばタンタルTa)からなるMTJ 接続用配線17b が形成されており、この接続用配線17b と書き込みワード線WWL との間に層間絶縁膜24の一部が介在している。この層間絶縁膜24の一部は、MTJ素子21b の弯曲上下に対向する部分がそれに連なる他の部分よりも書き込みワード線WWLの方向に向かって凹没している。

### [0063]

上記した第2の実施形態のMRAMは、MTJ素子21bの長辺方向(スピン方向)がビット線BLと直交しており、ビット線BLから発生する磁界曲線にほぼ一致させるようにMTJ素子21bを反らせている。これにより、弯曲状態のMTJ素子21bの自由層の長さ方向(長辺方向)の中心部と端部で印加される磁界強度が等しくなる。結果として、反転磁界が低減され、書き込み効率が向上し、書き込み電流が低減される。この場合、MTJ素子21bの自由層の長さ方向の端部に印加される磁界強度を強めるために、弯曲状態のMTJ素子21bの長辺の両先端間の弦の長さがビット線BLの幅よりも広いことが望ましい。

## [0064]

図7は、図5および図6に示した構造の形成工程の一例の一部についてビット線に垂直な断面における構造を示す断面図である。層間絶縁膜24は複数層の絶縁膜からなり、ここでは説明の簡単化のために一部241 のみ説明する。

#### [0065]

まず、P型Si基板10の表層部に選択的に素子分離領域STI 11を形成し、スイッチ用NMOSFE Tのゲート絶縁膜12、ゲート電極(GC)(読み出しワード線RWL)14、N+拡散層13からなるドレイン領域およびソース領域を形成する。次に、ドレイン領域上およびソース領域上にコンタクト18を形成し、さらに第1金属配線層(M1)15を形成する。次に、第1金属配線層15上にコンタクト19を形成し、さらに第2金属配線層(M2)(例えばCu配線)16を形成し、600nm程度の厚さの層間絶縁膜241(例えばHDP)および300nm程度の厚さの窒化シリコン(SiN)膜31を堆積する。

## [0066]

次に、リソグラフィー技術およびRIE 技術を用いてSiN 膜31を所望のパターン形状にし、このSiN 膜31のパターンをマスクとして層間絶縁膜241 を斜めに角度を持たせてエッチング加工(ミリング)する。この場合、後でMTJ 素子21b を繰り返しパターンとして形成するために、MTJ 素子21b の配置予定領域が溝となるように繰り返しパターンとして形成する。

### [0067]

次に、SiN 膜31のパターンを除去した後、図 5 中に示したように、第 2 金属配線層 16上にコンタクト20を形成し、さらに第 3 金属配線層 (M3) (例えばTa) 17aを30nm程度の厚さに堆積し、さらにMTJ 素子21b の各層を順次堆積し、さらに、ハードマスク(例えばTa) 26を150nm 程度の厚さに形成する。ここで、MTJ 素子21b の自由層は、通常、NiFeが使用されるが、CoNiFe,CoFe,CoCr,CoPt などを用いることも可能である。

## [0068]

そして、リソグラフィー技術とRIE 技術を用いて、ハードマスク26およびMTJ 素子21b を 所望のパターン形状に加工し、さらに、リソグラフィー技術とRIE 技術を用いて、第3金 属配線層17b を所望のパターンに加工してMTJ 接続用配線を形成する。

#### [0069]

次に、MTJ 素子21b の上面側のハードマスク26にコンタクトするコンタクト23および第 4 金属配線層 (M4)22を形成する。

10

20

40

30

20

30

40

#### [0070]

なお、MTJ素子21bとハードマスク26の厚さの比や材質の違いによる熱膨脹係数の違いを 利用して前記したように弯曲させることも可能である。

#### [0071]

また、前記各実施形態において、大容量化、高密度実装のために、複数のMTJ素子が行列 状に配置されたメモリセルアレイ、複数本の書き込みワード線WWL、複数本のビット線BL などにより1つのセルアレイユニットを構成し、複数のセルアレイユニットを半導体基板 上に積み重ねらてセルアレイ積層構造を構成することも可能である。

### [0072]

また、本発明は、前記各実施形態におけるMTJ素子の記録層が多層構造からなる場合にも 10 適用可能である。

#### [0073]

#### 【発明の効果】

上述したように本発明の磁気ランダムアクセスメモリによれば、書き込み電流を低減させ ることができる。

#### 【図面の簡単な説明】

- 本発明の第1の実施形態に係るMRAMにおけるセルアレイの一部に沿って書き込 みワード線に垂直な断面におけるメモリセルの1個分に着目してMTJ素子部およびスイッ チ用NMOSFET 部の構造の一例を示す断面図。

- 【図2】 図1中のビット線に垂直な断面における構造の一例を示す断面図。

- 図1および図2に示した構造の形成工程の一例の一部について書き込みワード 線に垂直な断面における構造を示す断面図。

- 図1中のMTJ素子部を取り出してその積層構造の一例を詳細に示す断面図。 【図4】

- 本発明の第2の実施形態に係るMRAMにおけるセルアレイの一部に沿ってビット 【図5】 線に垂直な断面における構造の一例を示す断面図。

- 【図6】 図5中の書き込みワード線に垂直な断面におけるメモリセルの1個分に着目し てMTJ素子部およびスイッチ用NMOSFET部の構造の一例を示す断面図。

- 図5および図6に示した構造の形成工程の一例の一部についてビット線に垂直 な断面における構造を示す断面図。

- 【図8】 従来のMRAMで用いられるMTJ素子の構造を概略的に示す断面図。

- 図8中のMTJ素子の2つの磁性層のスピンの向きを示す図。

- 【図10】 MRAMのセルアレイの一部の平面的なレイアウトの一例を模式的に示す図。

- 【図11】 図 1 0 中の A - A 線に沿ってメモリセルの 1 個分に着目して断面構造の一例 を模式的に示す図。

- 【図12】 図10中のB-B線に沿ってメモリセルの1個分に着目して断面構造の一例 を模式的に示す図。

- 【図13】 MTJ素子の印加磁界の反転による抵抗値の変化特性(TMR曲線)を示す特性 図。

- 【図14】 MTJ 素子のアステロイド曲線を示す特性図。

### 【符号の説明】

10... 半 導体 基 板 ( P 型 S i 基 板 ) 、 11... 素 子 分 離 領 域 、 12... ゲ ー ト 酸 化 膜 、 13... ド レ イ ン 領 域またはソース領域となる不純物拡散層(N+)、14...ゲート電極、15...第 1 金属配線層、16 ... 第 2 金属配線層、17a ... 第 3 金属配線層(例えばタンタルTa)からなるMTJ 接続用配線 、18,19,20,23 …コンタクト、21a …MTJ 素子、22…第 4 金属配線層、24…層間絶縁膜、 25... 導電性のハードマスク ( 例えばタンタルTa ) 、 (BL)... ビット線、 (WWL) ... 書き込みワ ード線、(SL)…ソース線、(RWL) …読み出しワード線。

【図1】 【図2】

【図3】 【図4】

【図5】 【図6】

【図7】 【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

M3 M2(WWL) 【図14】

M4(BL)

GC(RWL)

## フロントページの続き

(72)発明者 浅尾 吉昭

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

(72)発明者 與田 博明

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝横浜事業所内

(72) 発明者 天野 実

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝研究開発センター内

(72)発明者 上田 知正

神奈川県川崎市幸区小向東芝町1番地 株式会社東芝研究開発センター内

## 審査官 井原 純

(56)参考文献 特開2003-282842(JP,A)

特開2003-332650(JP,A)

特開2001-168418(JP,A)

特表2004-519859(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 21/8246

G11C 11/15

H01L 27/105

H01L 43/08