# (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 110326280 B (45) 授权公告日 2022. 02. 22

- (21) 申请号 201780069711.6

- (22) 申请日 2017.12.25

- (65) 同一申请的已公布的文献号 申请公布号 CN 110326280 A

- (43) 申请公布日 2019.10.11

- (66) 本国优先权数据 201611207393.9 2016.12.23 CN

- (85) PCT国际申请进入国家阶段日 2019.05.31

- (86) PCT国际申请的申请数据 PCT/CN2017/118337 2017.12.25

- (87) PCT国际申请的公布数据 W02018/113795 ZH 2018.06.28

- (73) 专利权人 宁波舜宇光电信息有限公司 地址 315400 浙江省宁波市余姚市舜宇路 66-68号

- (72) 发明人 王明珠 赵波杰 陈振宇 郭楠 田中武彦

- (74) 专利代理机构 上海联益知识产权代理事务 所(特殊普通合伙) 31427 代理人 尹飞宇

- (51) Int.CI.

HO4N 5/225 (2006.01) GO3B 17/02 (2021.01)

*G03B* 17/28 (2021.01)

- (56) 对比文件

- CN 106131386 A, 2016.11.16

- CN 105681637 A,2016.06.15

- CN 102593116 A,2012.07.18

- CN 202617250 U,2012.12.19

- CN 101877944 A, 2010.11.03

#### 审查员 彭鹏翔

权利要求书3页 说明书46页 附图66页

#### (54) 发明名称

阵列摄像模组及其应用

## (57) 摘要

本发明公开了一阵列摄像模组及其应用,其中所述摄像模组包括至少一光学镜头至少一电路板组件。所述电路板组件进一步包括至少一感光芯片,至少一电路板以及至少一电子元器件,其中所述感光芯片和所述电路板被导通地连接,其中至少一个所述电子元器件被贴装于所述电路板的背面,所述光学镜头被保持在所述感光芯片的感光路径,通过这样的方式,能够减小所述阵列摄像模组的长度尺寸和宽度尺寸中的至少一个尺寸,以有利于所述阵列摄像模组的小型化,从而便于所述阵列摄像模组被应用于轻薄化的电子设备。

1.一阵列摄像模组,其特征在于,包括至少两光学镜头和一电路板组件,其中所述电路板组件进一步包括:

至少一电路板:

至少两感光芯片,其中每个所述感光芯片分别被导通地连接于所述电路板,其中每个 所述光学镜头分别被保持在每个所述感光芯片的感光路径;

至少一电子元器件,其中每个所述电子元器件分别被导通地连接于所述电路板,并且至少一个所述电子元器件位于所述电路板的背面;以及

至少一个连体包埋部,其中所述至少一个连体包埋部通过将流体状成型材料加入到所述至少一个电路板和一个下模具之间的至少一个下部成型空间,从而使所述至少一个下部成型空间中的所有部分通过至少一下部连通通道被流体成型材料填充;固化所述下部成型空间中的所述流体状成型材料和执行下模具的脱模操作而形成。

- 2.根据权利要求1所述的阵列摄像模组,其中所述电路板组件包括至少一包埋部,其中 所述包埋部一体地结合于所述电路板的背面。

- 3.根据权利要求2所述的阵列摄像模组,其中所述包埋部包埋凸出于所述电路板的背面的至少一个所述电子元器件的至少一部分。

- 4.根据权利要求2所述的阵列摄像模组,其中所述电路板的背面被所述包埋部结合的面积与所述电路板的背面的总面积的面积比值大于或者等于1:2,并且小于或者等于2:3。

- 5.根据权利要求2所述的阵列摄像模组,其中所述包埋部的中部和/或侧部具有至少一缺口。

- 6.根据权利要求1至5中任一所述的阵列摄像模组,其中所述电路板组件包括至少两个 所述电路板,其中每个所述感光芯片分别被导通地连接于每个所述电路板。

- 7.根据权利要求1至5中任一所述的阵列摄像模组,其中所述电路板组件包括一个所述 电路板,其中每个所述感光芯片分别被导通地连接于所述电路板。

- 8.根据权利要求7所述的阵列摄像模组,其中每个所述感光芯片分别被贴装于所述电路板的正面。

- 9.根据权利要求2至5中任一所述的阵列摄像模组,其中所述电路板组件包括一个所述 电路板,所述电路板具有至少一通孔状的容纳空间,所述包埋部的一部分暴露在所述电路 板的所述容纳空间,其中至少一个所述感光芯片被贴装于所述电路板的正面,和至少一个 所述感光芯片经所述电路板的所述容纳空间被贴装于所述包埋部。

- 10.根据权利要求8所述的阵列摄像模组,其中所述电路板组件进一步包括一模制基座,所述模制基座具有至少一光窗,其中所述模制基座一体地结合于所述电路板的正面,并且所述模制基座环绕在每个所述感光芯片的感光区域的四周,以使每个所述感光芯片的感光区域分别对应于所述模制基座的每个所述光窗,其中所述模制基座的每个所述光窗分别形成每个所述光学镜头和每个所述感光芯片之间的光线通路。

- 11.根据权利要求9所述的阵列摄像模组,其中所述电路板组件进一步包括一模制基座,所述模制基座具有至少一光窗,其中所述模制基座一体地结合于所述电路板的正面,并且所述模制基座环绕在每个所述感光芯片的感光区域的四周,以使每个所述感光芯片的感光区域分别对应于所述模制基座的每个所述光窗,其中所述模制基座的每个所述光窗分别形成每个所述光学镜头和每个所述感光芯片之间的光线通路。

- 12.根据权利要求10所述的阵列摄像模组,其中所述模制基座包埋至少一个所述感光芯片的非感光区域的至少一部分。

- 13.根据权利要求11所述的阵列摄像模组,其中所述模制基座包埋至少一个所述感光芯片的非感光区域的至少一部分。

- 14.根据权利要求10所述的阵列摄像模组,进一步包括至少一滤光元件,其中每个所述滤光元件分别被贴装于所述模制基座,并且每个所述滤光元件分别被保持在每个所述光学镜头和每个所述感光芯片之间。

- 15.根据权利要求10所述的阵列摄像模组,进一步包括至少一框型的支架和被贴装于 所述支架的至少一滤光元件,其中所述支架被贴装于所述模制基座,以藉由所述支架将所 述滤光元件保持在所述光学镜头和所述感光芯片之间。

- 16.根据权利要求10所述的阵列摄像模组,其中在所述包埋部成型于所述电路板的背面的同时,所述模制基座成型于所述电路板的正面。

- 17.根据权利要求11所述的阵列摄像模组,其中在所述包埋部成型于所述电路板的背面的同时,所述模制基座成型于所述电路板的正面。

- 18.根据权利要求10所述的阵列摄像模组,其中在所述包埋部成型于所述电路板的背面后,所述模制基座成型于所述电路板的正面。

- 19.根据权利要求11所述的阵列摄像模组,其中在所述包埋部成型于所述电路板的背面后,所述模制基座成型于所述电路板的正面。

- 20.根据权利要求1至5中任一所述的阵列摄像模组,其中所述电路板组件进一步包括至少一镜架,其中所述镜架具有至少一通光孔,其中所述镜架被贴装于所述电路板的正面,并且所述镜架环绕在每个所述感光芯片的感光区域的四周,以使每个所述感光芯片的感光区域分别对应于所述镜架的每个所述通光孔,其中所述镜架的每个所述通光孔分别形成每个所述光学镜头和每个所述感光芯片之间的光线通路。

- 21.根据权利要求8所述的阵列摄像模组,其中所述电路板组件进一步包括至少一镜架和至少一模制基座,所述镜架具有至少一通光孔,所述模制基座具有至少一光窗,其中所述镜架被贴装于所述电路板的正面,并且所述镜架环绕在所述感光芯片的感光区域的四周,以使所述感光芯片的感光区域对应于所述镜架的所述通光孔,其中所述模制基座一体地结合于所述电路板的正面,并且所述模制基座环绕在所述感光芯片的四周,以使所述感光芯片的感光区域对应于所述模制基座的所述光窗,其中所述模制基座和所述镜架相邻,并且所述镜架的所述通光孔和所述模制基座的所述光窗分别形成每个所述光学镜头和每个所述感光芯片之间的光线通路。

- 22.根据权利要求9所述的阵列摄像模组,其中所述电路板组件进一步包括至少一镜架和至少一模制基座,所述镜架具有至少一通光孔,所述模制基座具有至少一光窗,其中所述镜架被贴装于所述电路板的正面,并且所述镜架环绕在所述感光芯片的感光区域的四周,以使所述感光芯片的感光区域对应于所述镜架的所述通光孔,其中所述模制基座一体地结合于所述电路板的正面,并且所述模制基座环绕在所述感光芯片的四周,以使所述感光芯片的感光区域对应于所述模制基座环绕在所述感光芯片的四周,以使所述感光芯片的感光区域对应于所述模制基座的所述光窗,其中所述模制基座和所述镜架相邻,并且所述镜架的所述通光孔和所述模制基座的所述光窗分别形成每个所述光学镜头和每个所述感光芯片之间的光线通路。

- 23.一电子设备,其特征在于,包括:

- 一电子设备本体;和

根据权利要求1至22中任一所述的至少一个所述阵列摄像模组,其中所述阵列摄像模组被设置于所述电子设备本体。

- 24.根据权利要求23所述的电子设备,其中所述电子设备本体是智能手机。

- 25.一阵列摄像模组的制造方法,其特征在于,所述制造方法包括如下步骤:

- (a)以至少一个电子元器件位于一电路板的背面的方式导通地连接所述电子元器件于 所述电路板:

- (b)以每个感光芯片的感光区域朝向所述电路板的正面所在的侧部的方式导通地连接每个所述感光芯片于所述电路板;

- (c)分别保持每个光学镜头于每个所述感光芯片的感光路径;

- (d)将至少一个连体包埋部一体地结合到所述电路板的所述背面,其中所述连体包埋部包埋自所述电路板的所述背面突出的至少一个电子元件的至少一部分,以制得所述阵列摄像模组,其中所述至少一个连体包埋部通过将流体状成型材料加入到所述至少一个电路板和一个下模具之间的至少一个下部成型空间,从而使所述至少一个下部成型空间中的所有部分通过至少一下部连通通道被流体成型材料填充;固化所述下部成型空间中的所述流体状成型材料和执行下模具的脱模操作而形成。

- 26.根据权利要求25所述的制造方法,进一步包括步骤:一体地结合至少一包埋部于所述电路板的背面。

- 27.根据权利要求26所述的制造方法,进一步包括步骤:形成至少一缺口于所述包埋部。

- 28.根据权利要求27所述的制造方法,其中在上述方法中,在一体地结合所述包埋部于 所述电路板的背面的同时形成所述缺口。

- 29.根据权利要求25所述的制造方法,进一步包括步骤:一体地结合一模制基座于所述电路板的正面,并同时形成至少一光窗以供被每个所述感光芯片的感光区域对应。

- 30.根据权利要求26至28中任一所述的制造方法,进一步包括步骤:一体地结合一模制基座于所述电路板的正面,并同时形成至少一光窗以供被每个所述感光芯片的感光区域对应。

- 31.根据权利要求30所述的制造方法,其中在所述电路板的背面一体地结合所述包埋部的同时,一体地结合所述模制基座于所述电路板的正面。

- 32.根据权利要求30所述的制造方法,其中在所述电路板的背面一体地结合于所述包埋部后,一体地结合所述模制基座于所述电路板的正面。

# 阵列摄像模组及其应用

#### 技术领域

[0001] 本发明涉及光学成像领域,特别涉及一阵列摄像模组及其应用。

### 背景技术

[0002] 智能化和轻薄化是便携式电子设备的重要的发展方向,便携式电子设备在朝向智能化和轻薄化方向发展的过程中,必然要求被配置于便携式电子设备的各部分结构更趋向于小型化,这也意味着便携式电子设备对作为便携式电子设备的标准配置之一的摄像模组的体积和成像品质提出了更加苛刻的要求。因为双摄像头摄像模组比单镜头摄像模组在成像方面更有优势,这使得近年来双镜头摄像模组越来越成为便携式电子设备的首选,但是双镜头摄像模组的体积相对于单镜头摄像模组来说比较大,如何减小双镜头摄像模组的体积是业界亟需解决的技术问题。

[0003] 现在的双镜头摄像模组与传统的单镜头摄像模组在结构和制造过程上类似,其主要包括以下几个步骤:将两个感光芯片分别相互间隔地贴装在电路板的正面,将多个被动电子元器件以相互间隔地贴装于电路板的正面的方式布置在感光芯片的四周,将预制的镜架通过胶水贴装在电路板的正面,并使镜架的内表面与被动电子元器件的外表面保持安全距离,和保证每个感光芯片的感光区域分别对应于镜架的每个通光孔,将镜头直接贴装于镜架,或者将镜头通过马达或者镜筒贴装于镜架,并保证每个镜头保持在每个感光芯片的感光路径。尽管现在的双镜头摄像模组在成像方面优于单镜头摄像模组,但是现在的双镜头摄像模组仍然具有诸多的缺陷。

[0004] 例如,为了进一步提高双镜头摄像模组的成像能力以满足便携式电子设备的智能化的发展需要,双镜头摄像模组的感光芯片需要具有更大的感光面积,和被动电子元器件的数量和尺寸同时也需要更多和更大,而因为受限于现在的双镜头摄像模组的封装工艺,一方面需要将被动电子元器件布置在感光芯片的周向方向,另一方面需要在相邻被动电子元器件之间预留防干扰的安全距离,这导致双镜头摄像模组的尺寸会进一步增加,以至于不利于双镜头摄像模组的小型化,进而导致双镜头摄像模组的发展趋势与便携式电子设备的发展趋势背道而驰。换言之,在双镜头摄像模组的现有封装工艺的条件下,通过增加感光芯片的感光面积和增加被动电子元器件的数量以及增大被动电子元器件的尺寸的方式来提升双镜头摄像模组的成像能力的手段,必然导致双镜头摄像模组的体积越来越大。因此,如何解决在减小双镜头摄像模组的体积的前提下进一步提升双镜头摄像模组的成像能力的技术问题是业界亟需解决的难题。

[0005] 另外,通过现有封装工艺制作的阵列摄像模组还存在着另外的缺陷,例如,镜架需要被预制,并且通常情况下,镜架是注塑件,因为镜架的厚度尺寸较小且长宽尺寸相对较大,这种结构导致镜架会产生形变而影响其平整度,进而影响双镜头摄像模组的成像能力。并且可以理解的是,镜架的厚度尺寸越小且长宽尺寸越大,则镜架产生形变的可能性越大,以及镜架产生形变幅度越大,这也就越会影响双镜头摄像模组的成像能力。再例如,被预制后的镜架需要通过胶水被贴装于电路板的正面,首先,因为胶水是流质,在这个过程中胶水

容易污染镜架的内表面和被动电子元器件的外表面,甚至在制程控制不佳的情况下会污染感光芯片的感光面,而如果一旦上述情况出现,轻则影响双镜头摄像模组的成像能力,重则导致双镜头摄像模组报废;其次,在通过胶水贴装镜架于电路板的正面后,需要对其进行烘烤以使胶水固化,在这个过程中,被施涂的胶水是否均匀以及被布置在每个位置的胶水的收缩是否一致均会影响镜架的平整度,而一旦镜架的平整度受到影响,则势必会影响镜头的中心轴和感光芯片的中心轴的重合度以及影响藉由镜头和感光芯片形成的两个光学系统的同轴度,进而导致双镜头摄像模组的成像能力受到极大的影响。

# 发明内容

[0006] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述阵列摄像模组的尺寸能够被有效地减小,以使得所述阵列摄像模组特别适于被应用于追求轻薄化的电子设备。

[0007] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述阵列摄像模组的 长度尺寸和宽度尺寸中的至少一个尺寸能够被减小,以有利于所述阵列摄像模组的小型 化。

[0008] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述阵列摄像模组的长宽尺寸能够被有效地减小,从而当所述阵列摄像模组被应用于追求轻薄化的电子设备时,所述阵列摄像模组能够占用更小的空间,以利于所述阵列摄像模组朝向智能化方向发展。

[0009] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述电路板组件包括一电路板和至少一电子元器件,其中至少一个所述电子元器件被贴装于所述电路板的背面或者被半埋入所述电路板的背部,从而在所述电路板的正面被预留的用于贴装所述电子元器件的空间可以被减小,以有利于减少所述阵列摄像模组的长度尺寸和宽度尺寸中的至少一个尺寸。

[0010] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中每个所述电子元器件分别被贴装于所述电路板的背面和/或被半埋入所述电路板的背部,从而在所述电路板的正面不需要预留用于贴装所述电子元器件的空间,以有利于减少所述阵列摄像模组的长度尺寸和宽度尺寸。

[0011] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中被贴装于所述电路板的背面的至少一个所述电子元器件被一包埋部包埋,以阻止所述电子元器件和外部环境接触,从而避免所述电子元器件的表面被氧化。

[0012] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述包埋部能够补强所述电路板的强度,以保证所述电路板的平整度。

[0013] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中即便是所述电路板的厚度尺寸被减小,通过所述包埋部补强所述电路板的方式,也能够保证所述电路板的平整度。例如,所述电路板可以是较薄的PCB板、FPC板、软硬结合板等。

[0014] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中被贴装于所述电路板的背面的至少一个所述电子元器件被所述包埋部包埋,从而藉由所述包埋部分隔相邻的所述电子元器件,通过这样的方式,即便是相邻两个所述电子元器件的距离较近时,相邻的所

述电子元器件也不会出现相互干扰的不良现象,从而改善所述阵列摄像模组的成像品质。

[0015] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述包埋部在成型的过程中一体地结合于所述电路板,通过这样的方式,不仅能够减少所述阵列摄像模组的制造步骤,而且能够保证所述包埋部与所述电路板结合的可靠性和稳定性。

[0016] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述包埋部具有至少一缺口,从而在后续将所述阵列摄像模组组装于一电子设备时,所述电子设备的元器件能够被容纳于所述包埋部的所述缺口,以使得在所述电子设备的长宽方向能够使所述电子设备与所述阵列摄像模组重叠,从而有利于所述电子设备朝向轻薄化的方向发展。

[0017] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述阵列摄像模组的至少一感光芯片能够被贴装于所述电路板组件的所述电路板的正面。

[0018] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中至少一个所述感光芯片能够被贴装于所述包埋部,以保证所述感光芯片的平整度,和进一步降低所述阵列摄像模组的高度尺寸。

[0019] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中至少一个所述感光芯片的感光面和另外的所述感光芯片的感光面之间具有高度差,以提高所述阵列摄像模组的成像能力。

[0020] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中至少一个所述感光芯片的感光面和另外的所述感光芯片的感光面具有高度差,以增加所述阵列摄像模组的功能。

[0021] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中在所述阵列摄像模组的高度方向,所述电子元器件和所述感光芯片能够相互对应,以使得所述阵列摄像模组的所述电子元器件可以不再像传统的阵列摄像模组那样使电子元器件只能够沿着感光芯片的周向布置,通过这样的方式,能够有效地减小所述阵列摄像模组的长度尺寸和宽度尺寸中的至少一个尺寸。

[0022] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述电路板具有至少一容纳空间,以供容纳所述感光芯片,从而进一步降低所述阵列摄像模组的高度尺寸。

[0023] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述电路板的正面形成一模制基座,从而一方面,所述模制基座不需要被预制,另一方面,在所述模制基座和所述电路板组件之间不需要被施涂胶水或者类似的粘着剂。

[0024] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述模制基座可以包埋被贴装于所述电路板的正面的至少一个所述电子元器件,从而在所述模制基座和所述电子元器件之间不需要被预留安装距离,通过这样的方式,有利于减小所述阵列摄像模组的尺寸。

[0025] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述模制基座用于阻止所述电子元器件和外部环境接触,从而避免所述电子元器件的表面氧化。

[0026] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述模制基座能够隔离相邻所述电子元器件,从而,即便是相邻两个所述电子元器件的距离较近时,相邻的所述电子元器件也不会出现相互干扰的不良现象,从而改善所述阵列摄像模组的成像品质。

[0027] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述模制基座隔离所

述电子元器件和所述感光芯片的感光区域,以避免所述感光芯片的感光区域被污染。

[0028] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述模制基座包埋被贴装于所述电路板的正面的所述电子元器件,以藉由所述电子元器件避免所述模制基座从所述电路板上脱落,从而保证所述阵列摄像模组的可靠性。

[0029] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述模制基座能够补强所述电路板的强度,以保证所述电路板的平整度。

[0030] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中即便是所述电路板的尺寸被减小,通过所述模制基座补强所述电路板的方式,也能够保证所述电路板的平整度。例如,所述电路板可以是较薄的PCB板、FPC板、软硬结合板等。

[0031] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述包埋部和所述模制基座均能够使相邻所述电子元器件的距离更近,从而在所述电路板的有限的贴装面积上能够被贴装更多数量和更大尺寸的所述电子元器件,以提高所述阵列摄像模组的性能。

[0032] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述感光芯片的外侧边到所述电路板的边缘的距离可以是0.1mm~3mm,例如在设有引线的一侧,述感光芯片的外侧边到所述电路板的边缘的距离可以是0.1mm~3mm,优选为0.3mm~1mm。

[0033] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述感光芯片的外侧边到所述电路板的边缘的距离可以是0.05mm~3mm,例如在没有引线的一侧,所述感光芯片的外侧边到所述电路板的边缘的距离可以是0.05mm~3mm,优选为0.1mm~0.8mm。

[0034] 本发明的一个目的在于提供一阵列摄像模组及其应用,其中所述包埋部的厚度可以是0.1mm~2mm,优选为0.2mm~1mm。

[0035] 依本发明的一个方面,本发明提供一阵列摄像模组,其包括至少两光学镜头和一电路板组件,其中所述电路板组件进一步包括:

[0036] 至少一电路板;

[0037] 至少两感光芯片,其中每个所述感光芯片分别被导通地连接于所述电路板,其中每个所述光学镜头分别被保持在每个所述感光芯片的感光路径;以及

[0038] 至少一电子元器件,其中每个所述电子元器件分别被导通地连接于所述电路板, 并且至少一个所述电子元器件位于所述电路板的背面。

[0039] 根据本发明的一个实施例,所述电路板组件包括至少一包埋部,其中所述包埋部一体地结合于所述电路板的背面。

[0040] 根据本发明的一个实施例,所述包埋部包埋凸出于所述电路板的背面的至少一个所述电子元器件的至少一部分。

[0041] 根据本发明的一个实施例,所述电路板的背面被所述包埋部结合的面积与所述电路板的背面的总面积的面积比值大于或者等于1:2,并且小于或者等于2:3。

[0042] 根据本发明的一个实施例,所述包埋部的中部和/或侧部具有至少一缺口。

[0043] 根据本发明的一个实施例,所述电路板组件包括至少两个所述电路板,其中每个所述感光芯片分别被导通地连接于每个所述电路板。

[0044] 根据本发明的一个实施例,所述电路板组件包括一个所述电路板,其中每个所述 感光芯片分别被导通地连接于所述电路板。

[0045] 根据本发明的一个实施例,每个所述感光芯片分别被贴装于所述电路板的正面。

[0046] 根据本发明的一个实施例,所述电路板组件包括一个所述电路板,所述电路板具有至少一通孔状的容纳空间,所述包埋部的一部分暴露在所述电路板的所述容纳空间,其中至少一个所述感光芯片被贴装于所述电路板的正面,和至少一个所述感光芯片经所述电路板的所述容纳空间被贴装于所述包埋部。

[0047] 根据本发明的一个实施例,所述电路板组件进一步包括一模制基座,所述模制基座具有至少一光窗,其中所述模制基座一体地结合于所述电路板的正面,并且所述模制基座环绕在每个所述感光芯片的感光区域的四周,以使每个所述感光芯片的感光区域分别对应于所述模制基座的每个所述光窗,其中所述模制基座的每个所述光窗分别形成每个所述光学镜头和每个所述感光芯片之间的光线通路。

[0048] 根据本发明的一个实施例,所述模制基座包埋至少一个所述感光芯片的非感光区域的至少一部分。

[0049] 根据本发明的一个实施例,所述阵列摄像模组进一步包括至少一滤光元件,其中每个所述滤光元件分别被贴装于所述模制基座,并且每个所述滤光元件分别被保持在每个所述光学镜头和每个所述感光芯片之间。

[0050] 根据本发明的一个实施例,所述阵列摄像模组进一步包括至少一框型的支架和被贴装于所述支架的至少一滤光元件,其中所述支架被贴装于所述模制基座,以藉由所述支架将所述滤光元件保持在所述光学镜头和所述感光芯片之间。

[0051] 根据本发明的一个实施例,在所述包埋部成型于所述电路板的背面的同时,所述模制基座成型于所述电路板的正面。

[0052] 根据本发明的一个实施例,在所述包埋部成型于所述电路板的背面后,所述模制基座成型于所述电路板的正面。

[0053] 根据本发明的一个实施例,所述电路板组件进一步包括至少一镜架,其中所述镜架具有至少一通光孔,其中所述镜架被贴装于所述电路板的正面,并且所述镜架环绕在每个所述感光芯片的感光区域的四周,以使每个所述感光芯片的感光区域分别对应于所述镜架的每个所述通光孔,其中所述镜架的每个所述通光孔分别形成每个所述光学镜头和每个所述感光芯片之间的光线通路。

[0054] 根据本发明的一个实施例,所述电路板组件进一步包括至少一镜架和至少一模制基座,所述镜架具有至少一通光孔,所述模制基座具有至少一光窗,其中所述镜架被贴装于所述电路板的正面,并且所述镜架环绕在所述感光芯片的感光区域的四周,以使所述感光芯片的感光区域对应于所述镜架的所述通光孔,其中所述模制基座一体地结合于所述电路板的正面,并且所述模制基座环绕在所述感光芯片的四周,以使所述感光芯片的感光区域对应于所述模制基座的所述光窗,其中所述模制基座和所述镜架相邻,并且所述镜架的所述通光孔和所述模制基座的所述光窗分别形成每个所述光学镜头和每个所述感光芯片之间的光线通路。

[0055] 依本发明的另一个方面,本发明进一步提供一电子设备,其包括:

[0056] 一电子设备本体;和

[0057] 至少一阵列摄像模组,其中所述阵列摄像模组被设置于所述电子设备本体,其中 所述阵列摄像模组包括至少两光学镜头和一电路板组件,其中所述电路板组件进一步包 括: [0058] 至少一电路板;

[0059] 至少两感光芯片,其中每个所述感光芯片分别被导通地连接于所述电路板,其中每个所述光学镜头分别被保持在每个所述感光芯片的感光路径;以及

[0060] 至少一电子元器件,其中每个所述电子元器件分别被导通地连接于所述电路板, 并且至少一个所述电子元器件位于所述电路板的背面。

[0061] 根据本发明的一个实施例,所述电子设备本体是智能手机。

[0062] 根据本发明的一个实施例,所述阵列摄像模组是所述智能手机的后置摄像模组。

[0063] 依本发明的另一个方面,本发明进一步提供一电路板组件,其包括:

[0064] 至少一电路板:

[0065] 至少两感光芯片,其中每个所述感光芯片分别被导通地连接于所述电路板;以及

[0066] 至少一电子元器件,其中每个所述电子元器件分别被导通地连接于所述电路板, 并且至少一个所述电子元器件位于所述电路板的背面。

[0067] 根据本发明的一个实施例,所述电路板组件进一步包括至少一包埋部,其中所述包埋部一体地结合于所述电路板的背面。

[0068] 根据本发明的一个实施例,所述包埋部包埋凸出于所述电路板的背面的至少一个 所述电子元器件的至少一部分。

[0069] 根据本发明的一个实施例,所述电路板的背面被所述包埋部结合的面积与所述电路板的背面的总面积的面积比值大于或者等于1:2,并且小于或者等于2:3。

[0070] 根据本发明的一个实施例,所述包埋部的中部和/或侧部具有至少一缺口。

[0071] 根据本发明的一个实施例,所述电路板组件包括至少两个所述电路板,其中每个所述感光芯片分别被导通地连接于每个所述电路板。

[0072] 根据本发明的一个实施例,所述电路板组件包括一个所述电路板,其中每个所述 感光芯片分别被导通地连接于所述电路板。

[0073] 根据本发明的一个实施例,每个所述感光芯片分别被贴装于所述电路板的正面。

[0074] 根据本发明的一个实施例,所述电路板组件包括一个所述电路板,所述电路板具有至少一通孔状的容纳空间,所述包埋部的一部分暴露在所述电路板的所述容纳空间,其中至少一个所述感光芯片被贴装于所述电路板的正面,和至少一个所述感光芯片经所述电路板的所述容纳空间被贴装于所述包埋部。

[0075] 根据本发明的一个实施例,所述电路板组件进一步包括一模制基座,所述模制基座具有至少一光窗,其中所述模制基座一体地结合于所述电路板的正面,并且所述模制基座环绕在每个所述感光芯片的感光区域的四周,以使每个所述感光芯片的感光区域分别对应于所述模制基座的每个所述光窗。

[0076] 根据本发明的一个实施例,所述模制基座包埋至少一个所述感光芯片的非感光区域的至少一部分。

[0077] 根据本发明的一个实施例,在所述包埋部成型于所述电路板的背面的同时,所述模制基座成型于所述电路板的正面。

[0078] 根据本发明的一个实施例,在所述包埋部成型于所述电路板的背面后,所述模制基座成型于所述电路板的正面。

[0079] 依本发明的另一个方面,本发明进一步提供一连体电路板组件,其包括:

[0080] 一拼板单元,其中所述拼板单元包括至少一电路板;

[0081] 至少一电子元器件,其中每个所述电子元器件分别被导通地连接于所述电路板, 并且至少一个所述电子元器件位于所述电路板的背面;以及

[0082] 一连体包埋部,其中所述连体包埋部一体地结合于所述电路板的背面。

[0083] 根据本发明的一个实施例,所述连体电路板组件进一步包括至少一连体模制基座,其中所述连体模制基座具有至少一光窗,其中所述连体模制基座一体地结合于所述电路板的正面,并且所述电路板的正面的电路板连接件暴露在所述连体模制基座的所述光窗。

[0084] 根据本发明的一个实施例,所述连体电路板组件进一步包括至少一连体模制基座和至少一感光芯片,其中所述连体模制基座具有至少一光窗,其中在所述感光芯片被导通地连接于所述电路板后,所述连体模制基座一体地结合于所述电路板的正面,并且所述连体模制基座环绕在所述感光芯片的感光区域的四周,以使所述感光芯片的感光区域对应于所述连体模制基座的所述光窗。

[0085] 根据本发明的一个实施例,所述连体模制基座结合所述感光芯片的非感光区域的至少一部分区域。

[0086] 根据本发明的一个实施例,所述连体包埋部包埋凸出于所述电路板的背面的至少一个所述电子元器件的至少一部分。

[0087] 根据本发明的一个实施例,在所述连体包埋部一体地结合于所述电路板的背面的同时,所述连体模制基座一体地结合于所述电路板的正面。

[0088] 根据本发明的一个实施例,在所述连体包埋部一体地结合于所述电路板的背面后,所述连体模制基座一体地结合于所述电路板的正面。

[0089] 依本发明的另一个方面,本发明进一步提供一阵列摄像模组的制造方法,其中所述制造方法包括如下步骤:

[0090] (a) 以至少一个电子元器件位于一电路板的背面所在的侧部的方式导通地连接所述电子元器件于所述电路板;

[0091] (b) 以每个感光芯片的感光区域朝向所述电路板的正面所在的侧部的方式导通地连接每个所述感光芯片于所述电路板:以及

[0092] (c)分别保持每个光学镜头于每个所述感光芯片的感光路径,以制得所述阵列摄像模组。

[0093] 根据本发明的一个实施例,所述制造方法进一步包括步骤:一体地结合至少一包埋部于所述电路板的背面。

[0094] 根据本发明的一个实施例,所述制造方法进一步包括步骤:形成至少一缺口于所述包埋部。

[0095] 根据本发明的一个实施例,在上述方法中,在一体地结合所述包埋部于所述电路板的背面的同时形成所述缺口。

[0096] 根据本发明的一个实施例,所述制造方法进一步包括步骤:一体地结合一模制基座于所述电路板的正面,并同时形成至少一光窗以供被每个所述感光芯片的感光区域对应。

[0097] 根据本发明的一个实施例,所述制造方法进一步包括步骤:一体地结合一模制基

座于所述电路板的正面,并同时形成至少一光窗以供被每个所述感光芯片的感光区域对应。

[0098] 根据本发明的一个实施例,在所述电路板的背面一体地结合所述包埋部的同时, 一体地结合所述模制基座于所述电路板的正面

[0099] 根据本发明的一个实施例,在所述电路板的背面一体地结合于所述包埋部后,一体地结合所述模制基座于所述电路板的正面。

[0100] 依本发明的另一个方面,本发明提供一阵列摄像模组,其包括至少两光学镜头和一电路板组件,其中所述电路板组件进一步包括:

[0101] 至少一电路板;

[0102] 至少两感光芯片,其中每个所述感光芯片分别被导通地连接于所述电路板,每个所述光学镜头分别被保持在每个所述感光芯片的感光路径,其中至少一个所述感光芯片的感光面和其他的所述感光芯片的感光面具有高度差;以及

[0103] 至少一电子元器件,其中每个所述电子元器件分别被导通地连接于所述电路板, 并且至少一个所述电子元器件位于所述电路板的背面。

[0104] 根据本发明的一个实施例,所述电路板组件包括至少两个所述电路板,每个所述 感光芯片分别被导通地连接于每个所述电路板。

[0105] 根据本发明的一个实施例,所述电路板组件包括一个所述电路板,每个所述感光芯片分别被导通地连接于所述电路板。

[0106] 根据本发明的一个实施例,至少一个所述电路板具有至少一容纳空间,其中被导通地连接于具有所述容纳空间的所述电路板的所述感光芯片芯片被保持在所述电路板的所述容纳空间,和另外的所述感光芯片被贴装于所述电路板的正面,从而使至少一个所述感光芯片的感光面和其他的所述感光芯片的感光面具有高度差。

[0107] 根据本发明的一个实施例,至少一个所述电路板具有至少一通孔状的容纳空间,其中被导通地连接于具有所述容纳空间的所述电路板的所述感光芯片被贴装于所述电路板的背面,并且所述感光芯片的感光区域被暴露在所述电路板的所述容纳空间,另外的所述感光芯片被贴装于所述电路板的正面,从而使至少一个所述感光芯片的感光面和其他的所述感光芯片的感光面具有高度差。

[0108] 根据本发明的一个实施例,所述电路板具有至少一容纳空间,其中至少一个所述感光芯片被保持在所述电路板的所述容纳空间,和另外的所述感光芯片被贴装于所述电路板的正面,从而使至少一个所述感光芯片的感光面和其他的所述感光芯片的感光面具有高度差。

[0109] 根据本发明的一个实施例,所述电路板具有至少一通孔状的容纳空间,其中至少一个所述感光芯片被贴装于所述电路板的背面,并且所述感光芯片的感光区域被暴露在所述电路板的所述容纳空间,另外的所述感光芯片被贴装于所述电路板的正面,使至少一个所述感光芯片的感光面和其他的所述感光芯片的感光面具有高度差。

[0110] 根据本发明的一个实施例,所述电路板组件进一步包括一模制基座,所述模制基座具有至少一光窗,其中所述模制基座一体地结合于所述电路板的正面,并且所述模制基座环绕在所述感光芯片的四周,以使所述感光芯片的感光区域对应于所述模制基座的所述光窗。

[0111] 根据本发明的一个实施例,所述电路板组件进一步包括一模制基座和一镜架,其中所述模制基座具有至少一光窗,所述模制基座具有至少一通光孔,其中所述模制基座一体地结合于所述电路板的正面,并且所述模制基座环绕在至少一个所述感光芯片的四周,以使所述感光芯片的感光区域对应于所述模制基座的所述光窗,其中所述镜架被贴装于所述电路板的正面,并且所述镜架环绕在另外的所述感光芯片的四周,以使所述感光芯片的感光区域对应于所述镜架的所述通光孔,并且所述模制基座和所述镜架相邻。

[0112] 根据本发明的一个实施例,所述模制基座进一步包埋所述感光芯片的非感光区域。

[0113] 根据本发明的一个实施例,所述电路板组件进一步包括一包埋部,其中所述包埋部一体地结合于所述电路板的背面。

[0114] 根据本发明的一个实施例,所述包埋部的中部和/或侧部具有至少一缺口。

[0115] 根据本发明的一个实施例,所述电路板的背面被所述包埋部结合的面积与所述电路板的背面的总面积的面积比值大于或者等于1:2,并且小于或者等于2:3。

[0116] 根据本发明的一个实施例,在所述包埋部一体地结合于所述电路板的背面的同时,所述模制基座一体地结合于所述电路板的正面。

[0117] 根据本发明的一个实施例,在所述包埋部一体地结合于所述电路板的背面后,所述模制基座结合于所述电路板的正面。

[0118] 根据本发明的一个实施例,至少一个所述电路板具有至少一通光孔的容纳空间,其中所述电路板组件进一步包括一包埋部,所述包埋部一体地结合于每个所述电路板的背面,并且所述包埋部的一部分暴露在所述电路板的所述容纳空间,其中至少一个所述感光芯片被贴装于所述电路板的正面,和另外的所述感光芯片经由所述电路板的所述容纳空间被贴装于所述包埋部,从而使至少一个所述感光芯片的感光面和其他的所述感光芯片的感光面具有高度差。

[0119] 根据本发明的一个实施例,所述电路板具有至少一通光孔的容纳空间,其中所述电路板进一步包括一包埋部,所述包埋部一体地结合于所述电路板的背面,并且所述包埋部的一部分暴露在所述电路板的所述容纳空间,其中至少一个所述感光芯片被贴装于所述电路板的正面,和另外的所述感光芯片经由所述电路板的所述容纳空间被贴装于所述包埋部,从而使至少一个所述感光芯片的感光面和其他的所述感光芯片的感光面具有高度差。

[0120] 依本发明的另一个方面,本发明进一步提供一电子设备,其包括一电子设备本体和被设置于所述电子设备本体的至少一阵列摄像模组,其中所述阵列摄像模组进一步包括至少两光学镜头和一电路板组件,其中所述电路板组件进一步包括:

[0121] 至少一电路板:

[0122] 至少两感光芯片,其中每个所述感光芯片分别被导通地连接于所述电路板,每个所述光学镜头分别被保持在每个所述感光芯片的感光路径,其中至少一个所述感光芯片的感光面和其他的所述感光芯片的感光面具有高度差;以及

[0123] 至少一电子元器件,其中每个所述电子元器件分别被导通地连接于所述电路板, 并且至少一个所述电子元器位于所述电路板的背面。

[0124] 根据本发明的一个实施例,所述电子设备是智能手机。

[0125] 根据本发明的一个实施例,所述阵列摄像模组是所述智能手机的前置摄像模组,

或者所述阵列摄像模组是所述智能手机的后置摄像模组。

[0126] 根据本发明的另一个方面,本发明进一步提供一电路板组件,其包括:

[0127] 至少一电路板:

[0128] 至少两感光芯片,其中每个所述感光芯片分别被导通地连接于所述电路板,其中至少一个所述感光芯片的感光面和其他的所述感光芯片的感光面具有高度差;以及

[0129] 至少一电子元器件,其中每个所述电子元器件分别被导通地连接于所述电路板, 并且至少一个所述电子元器件的自由侧朝向所述电路板的背面。

[0130] 根据本发明的一个实施例,所述电路板组件至少两个所述电路板,每个所述感光芯片分别被导通地连接于每个所述电路板。

[0131] 根据本发明的一个实施例,所述电路板组件包括一个所述电路板,每个所述感光芯片分别被导通地连接于所述电路板。

[0132] 根据本发明的一个实施例,至少一个所述电路板具有至少一容纳空间,其中被导通地连接于具有所述容纳空间的所述电路板的所述感光芯片芯片被保持在所述电路板的所述容纳空间,和另外的所述感光芯片被贴装于所述电路板的正面,从而使至少一个所述感光芯片的感光面和其他的所述感光芯片的感光面具有高度差。

[0133] 根据本发明的一个实施例,至少一个所述电路板具有至少一通孔状的容纳空间,其中被导通地连接于具有所述容纳空间的所述电路板的所述感光芯片被贴装于所述电路板的背面,并且所述感光芯片的感光区域被暴露在所述电路板的所述容纳空间,另外的所述感光芯片被贴装于所述电路板的正面,从而使至少一个所述感光芯片的感光面和其他的所述感光芯片的感光面具有高度差。

[0134] 根据本发明的一个实施例,所述电路板具有至少一容纳空间,其中至少一个所述感光芯片被保持在所述电路板的所述容纳空间,和另外的所述感光芯片被贴装于所述电路板的正面,从而使至少一个所述感光芯片的感光面和其他的所述感光芯片的感光面具有高度差。

[0135] 根据本发明的一个实施例,所述电路板具有至少一通孔状的容纳空间,其中至少一个所述感光芯片被贴装于所述电路板的背面,并且所述感光芯片的感光区域被暴露在所述电路板的所述容纳空间,另外的所述感光芯片被贴装于所述电路板的正面,使至少一个所述感光芯片的感光面和其他的所述感光芯片的感光面具有高度差。

[0136] 根据本发明的一个实施例,所述电路板组件进一步包括一模制基座,所述模制基座具有至少一光窗,其中所述模制基座一体地结合于所述电路板的正面,并且所述模制基座环绕在所述感光芯片的四周,以使所述感光芯片的感光区域对应于所述模制基座的所述光窗。

[0137] 根据本发明的一个实施例,所述电路板组件进一步包括一模制基座和一镜架,其中所述模制基座具有至少一光窗,所述模制基座具有至少一通光孔,其中所述模制基座一体地结合于所述电路板的正面,并且所述模制基座环绕在至少一个所述感光芯片的四周,以使所述感光芯片的感光区域对应于所述模制基座的所述光窗,其中所述镜架被贴装于所述电路板的正面,并且所述镜架环绕在另外的所述感光芯片的四周,以使所述感光芯片的感光区域对应于所述镜架环绕在另外的所述感光芯片的四周,以使所述感光芯片的感光区域对应于所述镜架的所述通光孔,并且所述模制基座和所述镜架相邻。

[0138] 根据本发明的一个实施例,所述模制基座进一步包埋所述感光芯片的非感光区

域。

[0139] 根据本发明的一个实施例,所述电路板组件进一步包括一包埋部,其中所述包埋部一体地结合于所述电路板的背面。

[0140] 根据本发明的一个实施例,所述包埋部包埋凸出于所述电路板的背面的至少一个 所述电子元器件的至少一部分。

[0141] 根据本发明的一个实施例,所述包埋部的中部和/或侧部具有至少一缺口。

[0142] 根据本发明的一个实施例,所述电路板的背面被所述包埋部结合的面积与所述电路板的背面的总面积的面积比值大于或者等于1:2,并且小于或者等于2:3。

[0143] 根据本发明的一个实施例,至少一个所述电路板具有至少一通光孔的容纳空间,其中所述电路板组件进一步包括一包埋部,所述包埋部一体地结合于每个所述电路板的背面,并且所述包埋部的一部分暴露在所述电路板的所述容纳空间,其中至少一个所述感光芯片被贴装于所述电路板的正面,和另外的所述感光芯片经由所述电路板的所述容纳空间被贴装于所述包埋部,从而使至少一个所述感光芯片的感光面和其他的所述感光芯片的感光面具有高度差。

[0144] 根据本发明的一个实施例,所述电路板具有至少一通光孔的容纳空间,其中所述电路板进一步包括一包埋部,所述包埋部一体地结合于所述电路板的背面,并且所述包埋部的一部分暴露在所述电路板的所述容纳空间,其中至少一个所述感光芯片被贴装于所述电路板的正面,和另外的所述感光芯片经由所述电路板的所述容纳空间被贴装于所述包埋部,从而使至少一个所述感光芯片的感光面和其他的所述感光芯片的感光面具有高度差。

## 附图说明

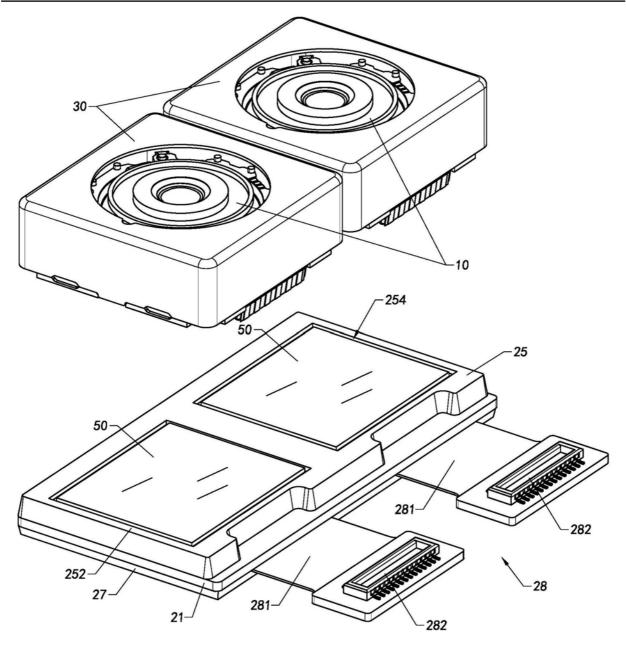

[0145] 图1是依本发明的一较佳实施例的一阵列摄像模组的使用状态的示意图。

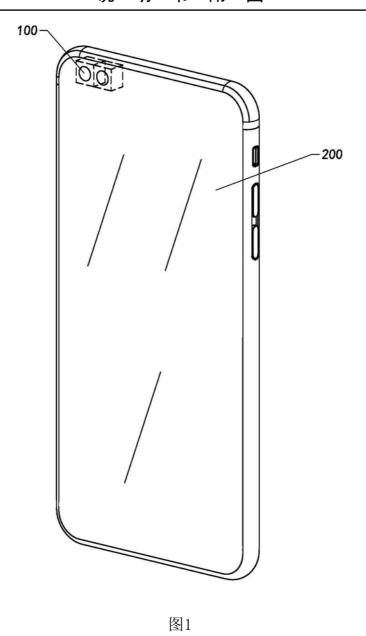

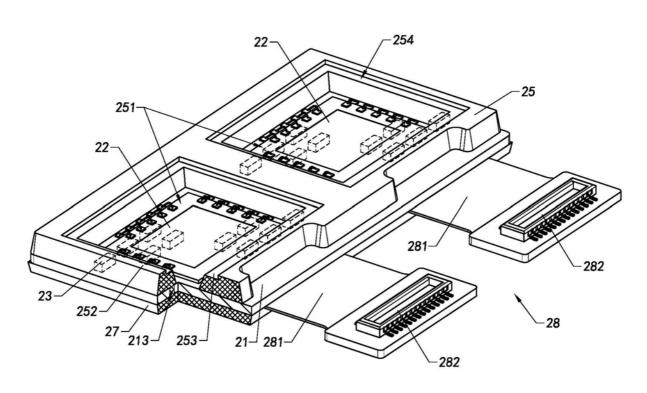

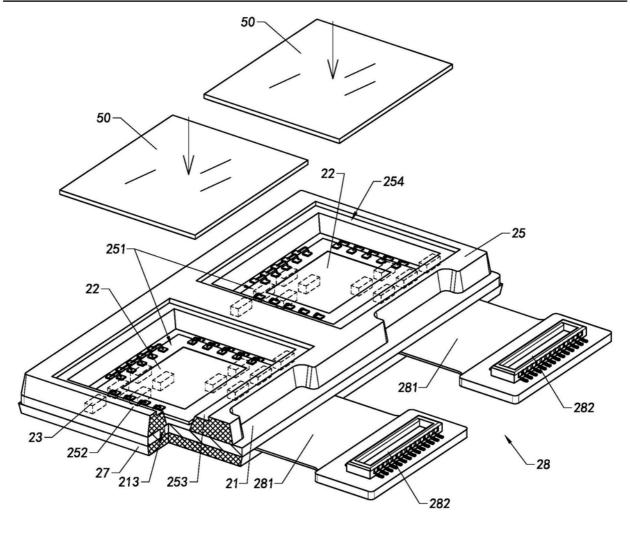

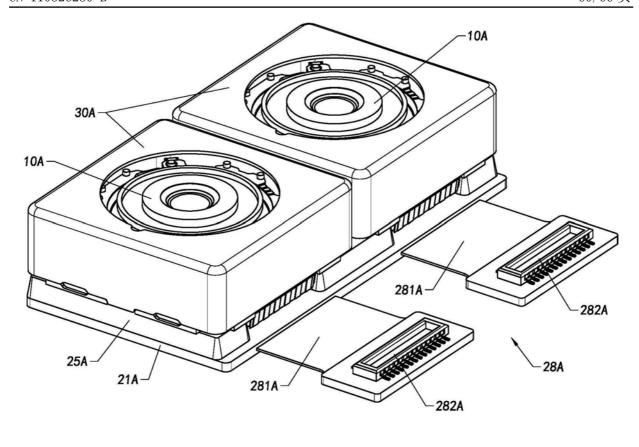

[0146] 图2是依本发明的上述较佳实施例的所述阵列摄像模组的立体图。

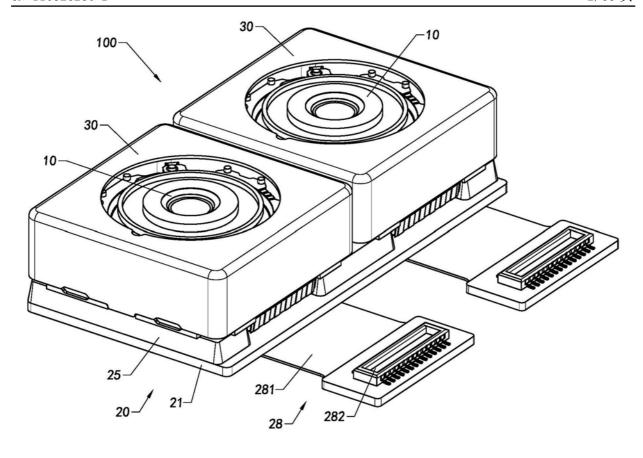

[0147] 图3是依本发明的上述较佳实施例的所述阵列摄像模组的分解图。

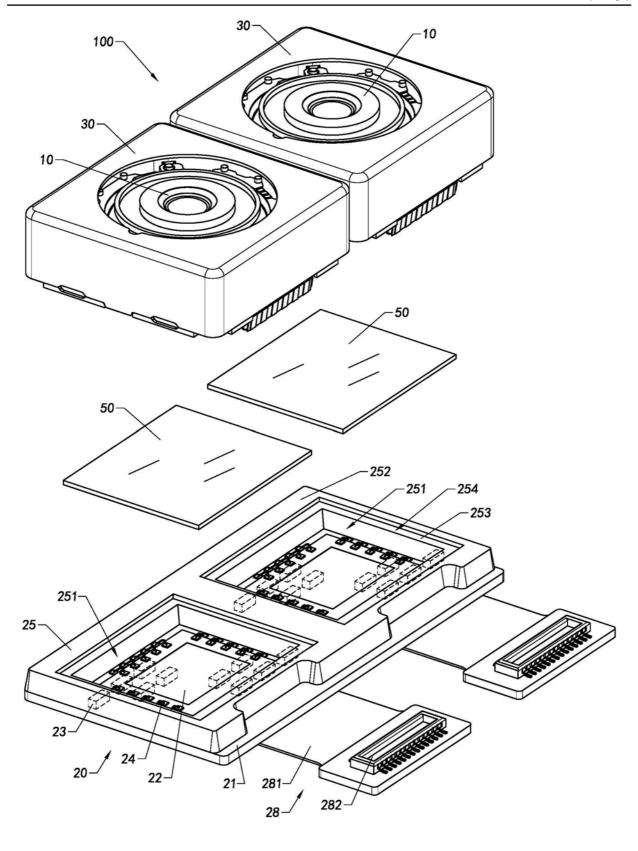

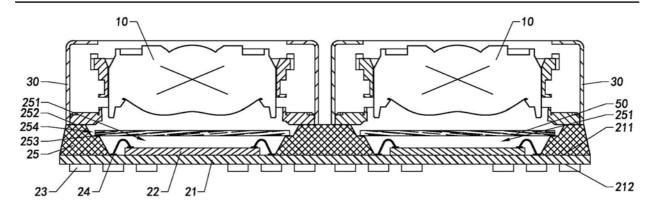

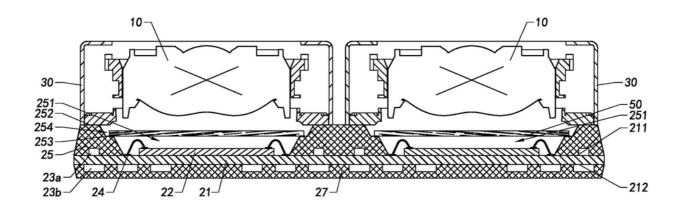

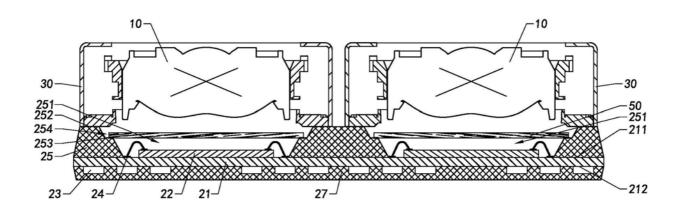

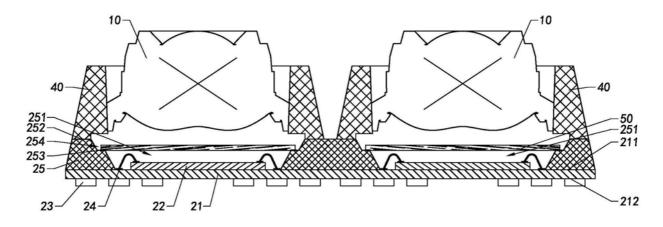

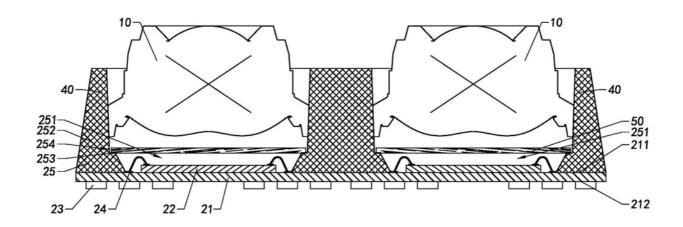

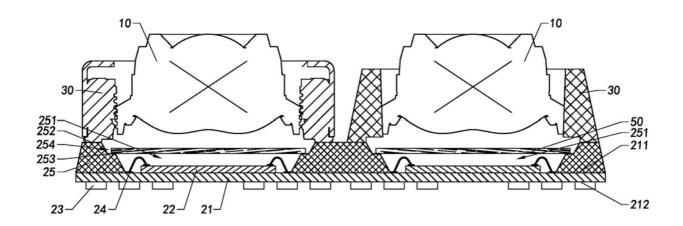

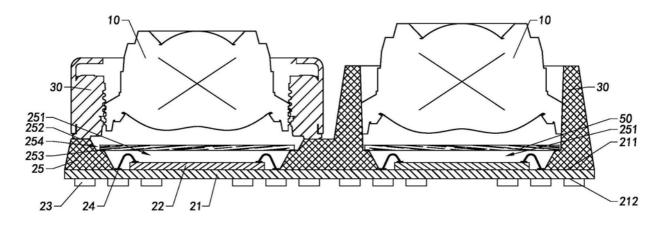

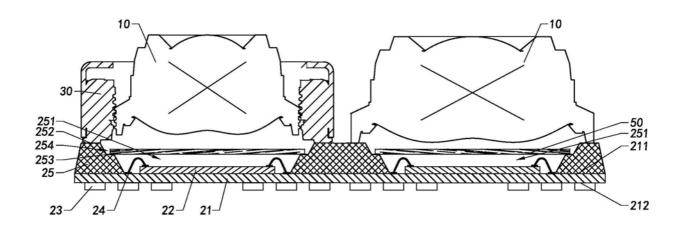

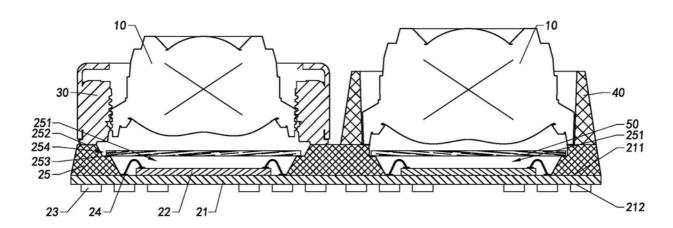

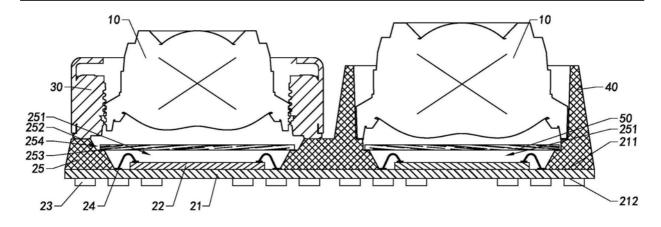

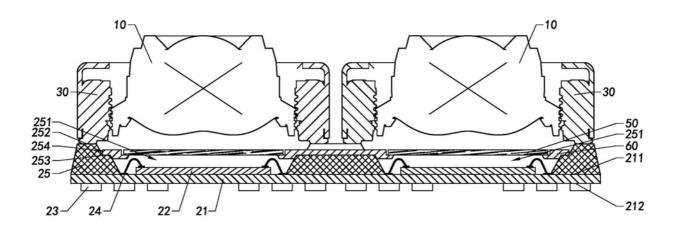

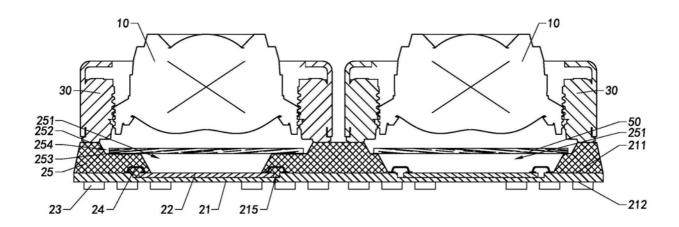

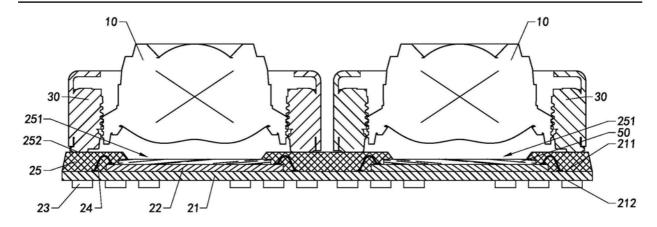

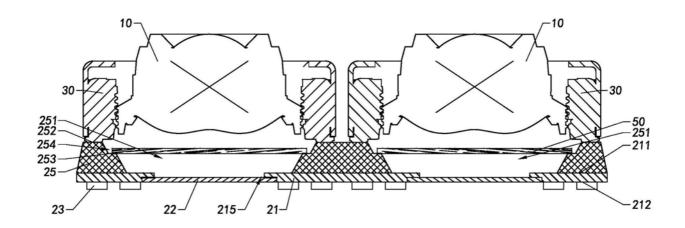

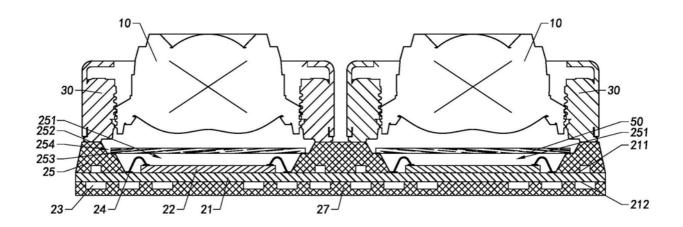

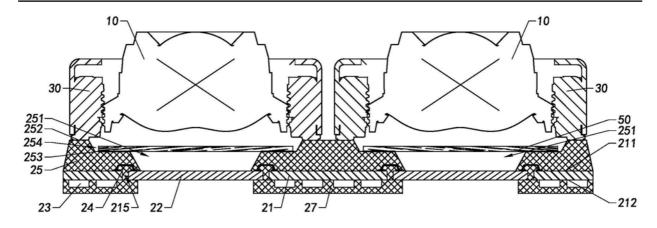

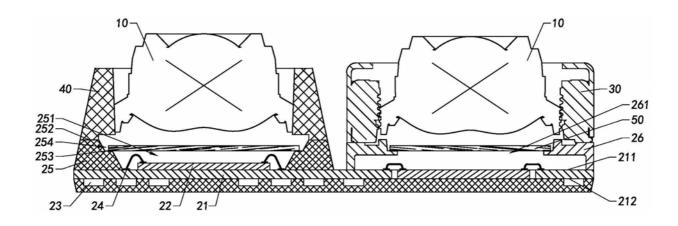

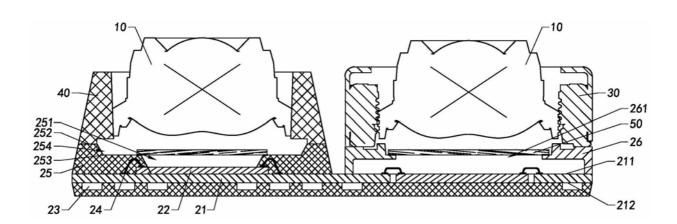

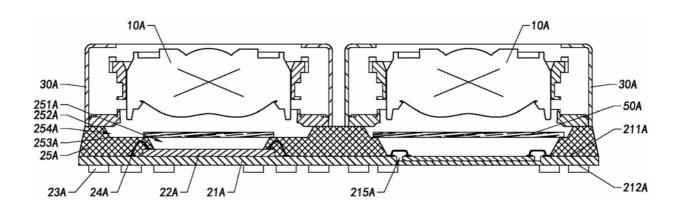

[0148] 图4是依本发明的上述较佳实施例的所述阵列摄像模组的剖视图。

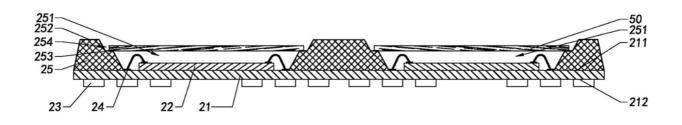

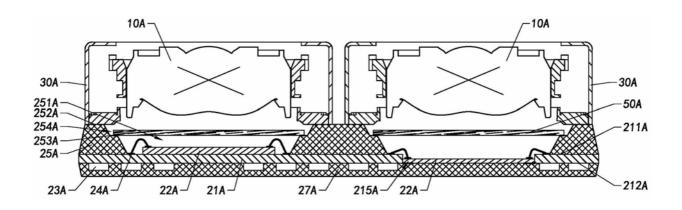

[0149] 图5是依本发明的上述较佳实施例的所述阵列摄像模组的电路板组件的剖视图。

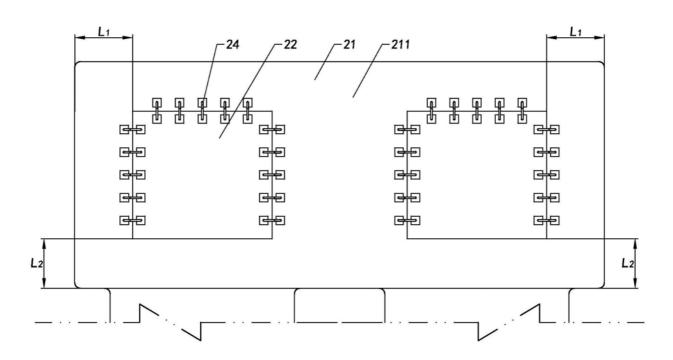

[0150] 图6是依本发明的上述较佳实施例的所述阵列摄像模组的电路板组件的俯视图。

[0151] 图7是依本发明的上述较佳实施例的所述阵列摄像模组的一个变形实施方式的剖视示意图。

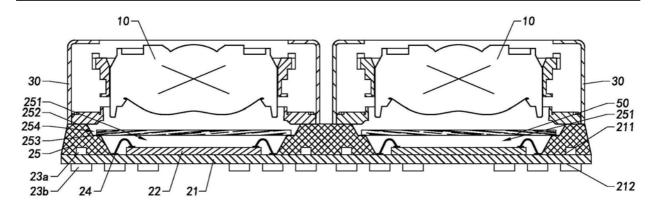

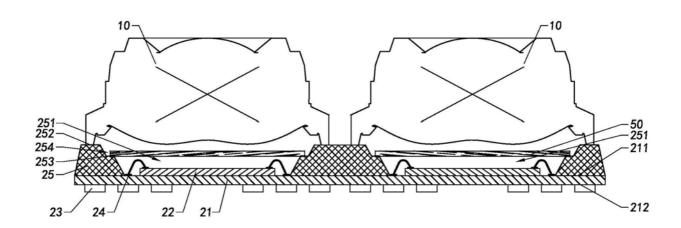

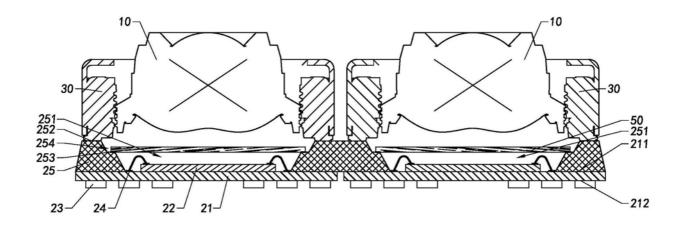

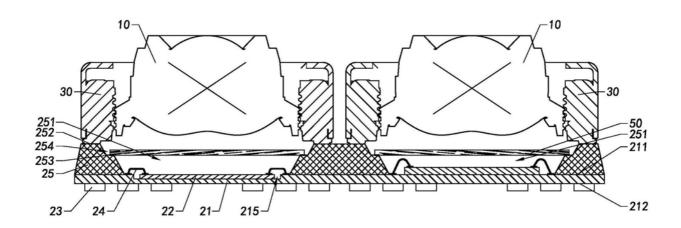

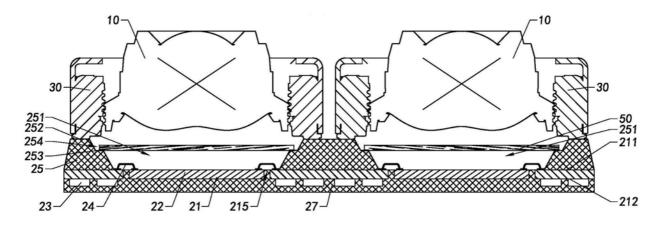

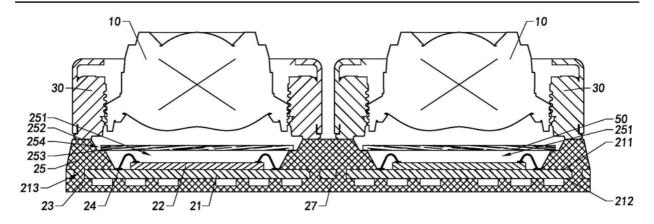

[0152] 图8是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的 剖视示意图。

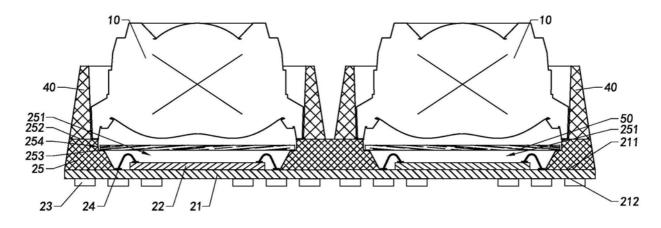

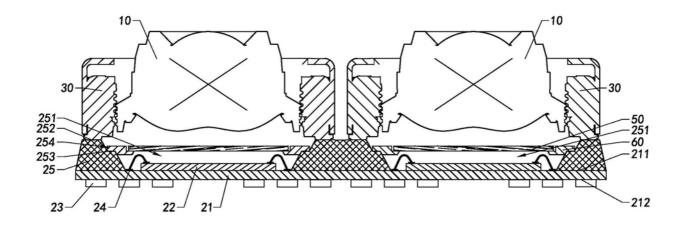

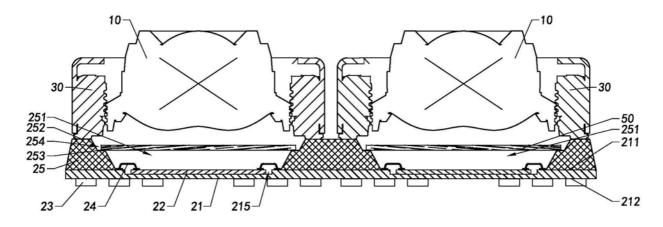

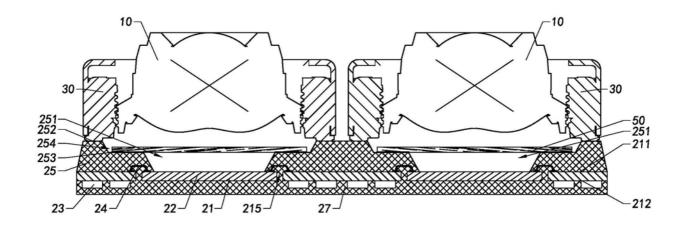

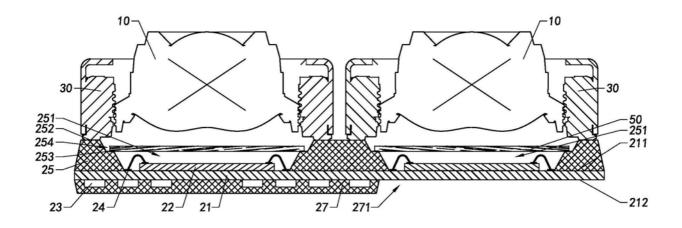

[0153] 图9是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的 剖视示意图。

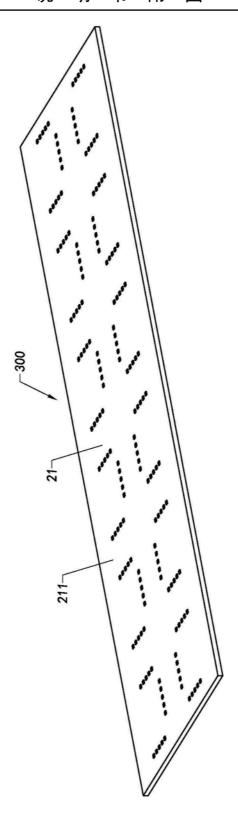

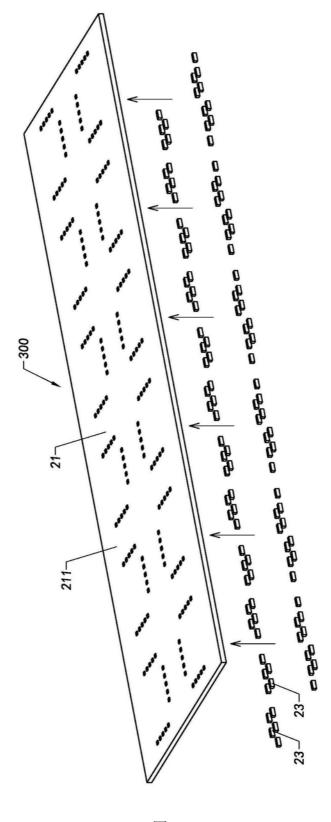

[0154] 图10是依本发明的上述较佳实施例的所述阵列摄像模组的一个制造步骤的示意图。

[0155] 图11是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

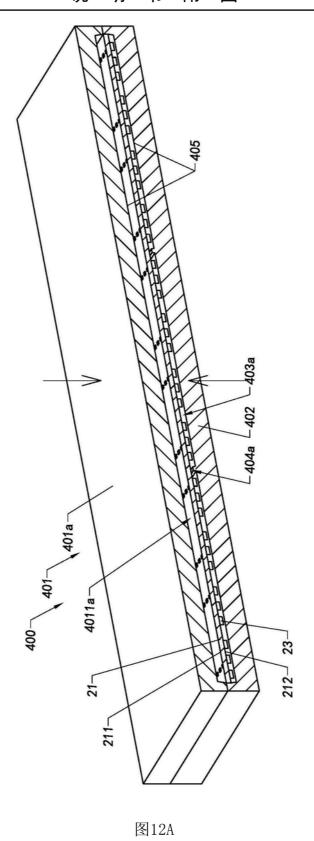

[0156] 图12A和图12B是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

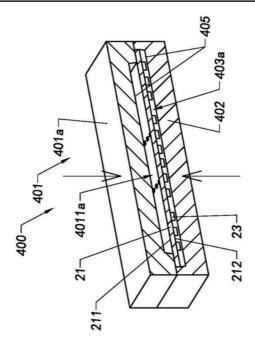

- [0157] 图13是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

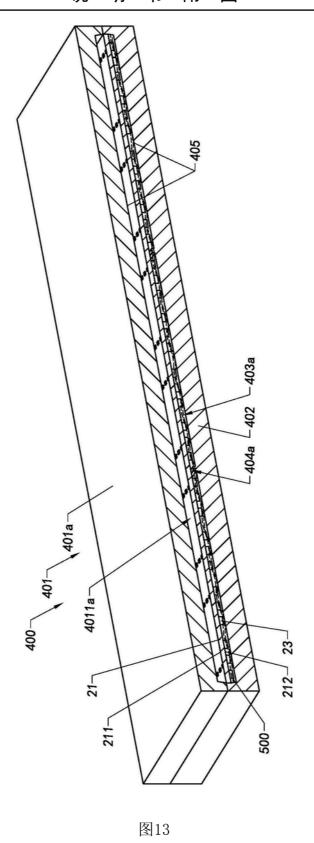

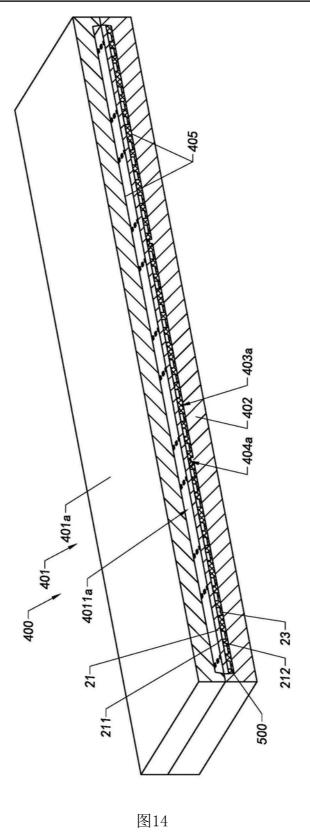

- [0158] 图14是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

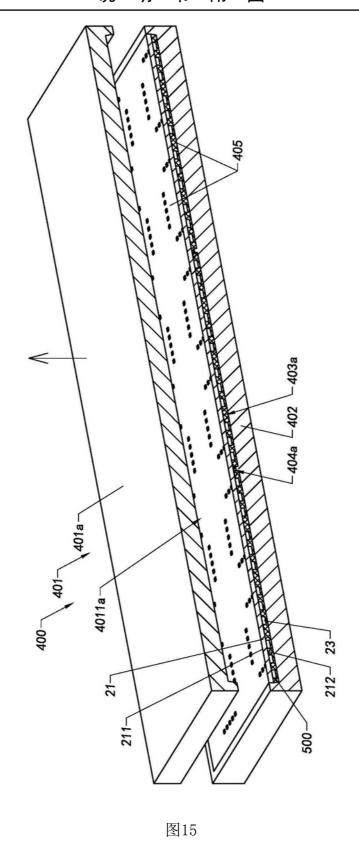

- [0159] 图15是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

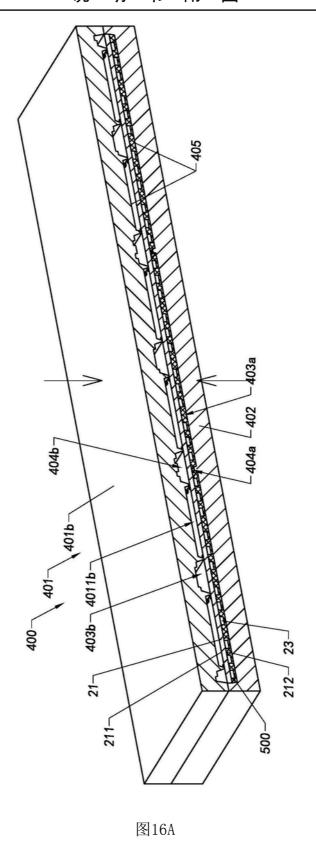

- [0160] 图16A和图16B是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

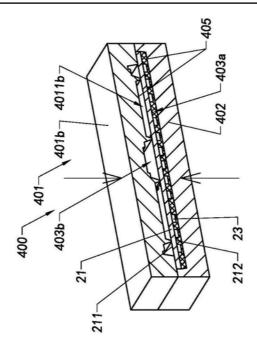

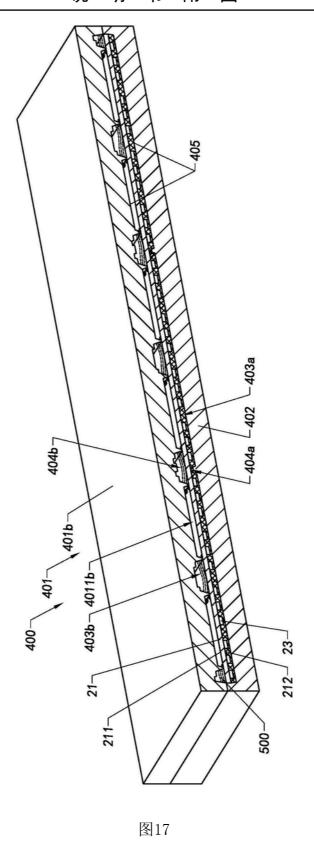

- [0161] 图17是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

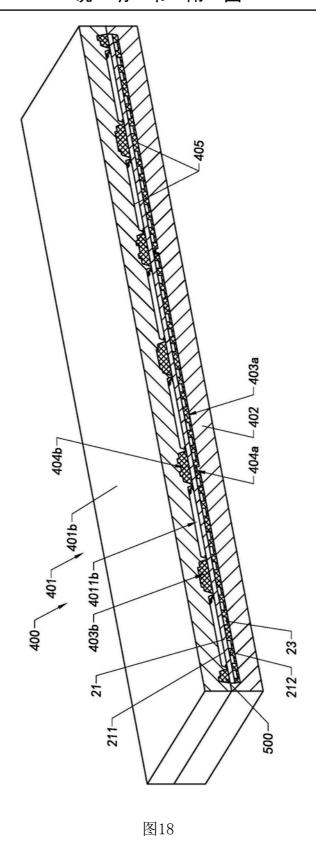

- [0162] 图18是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

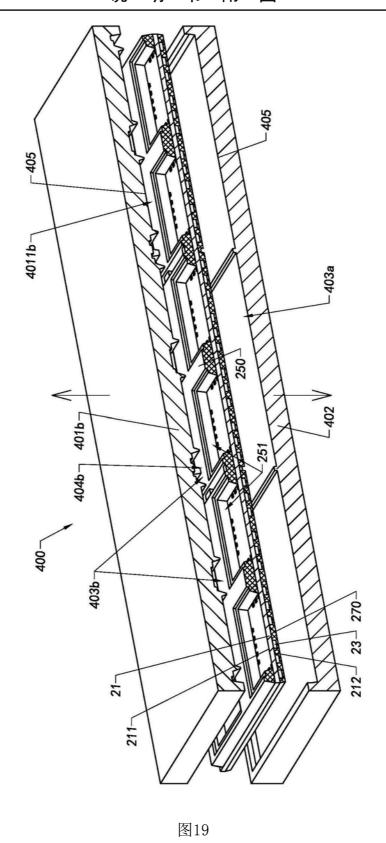

- [0163] 图19是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

- [0164] 图20是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

- [0165] 图21是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

- [0166] 图22是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

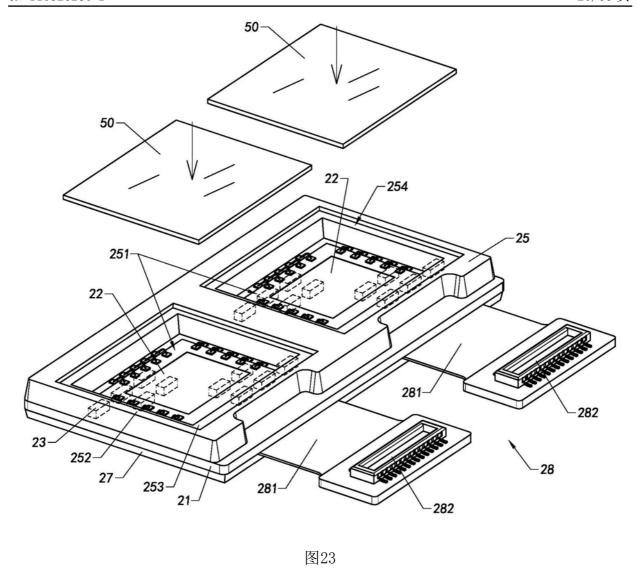

- [0167] 图23是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

- [0168] 图24是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

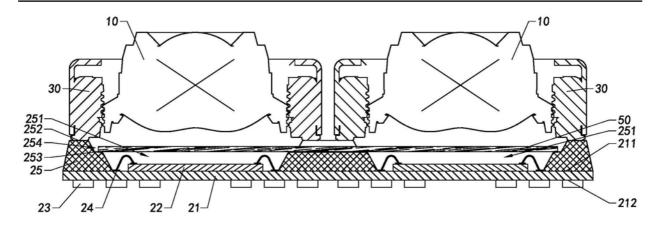

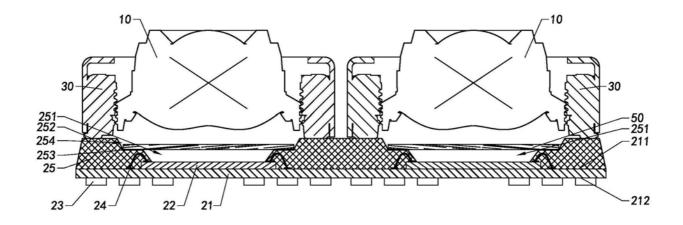

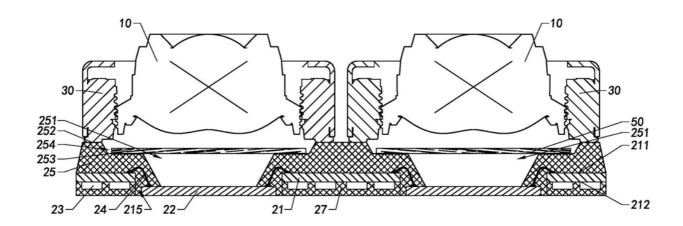

- [0169] 图25是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的剖视示意图。

- [0170] 图26是依本发明的上述较佳实施例的所述阵列摄像模组的一个制造步骤的示意图。

- [0171] 图27是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

- [0172] 图28A和图28B是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

- [0173] 图29是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

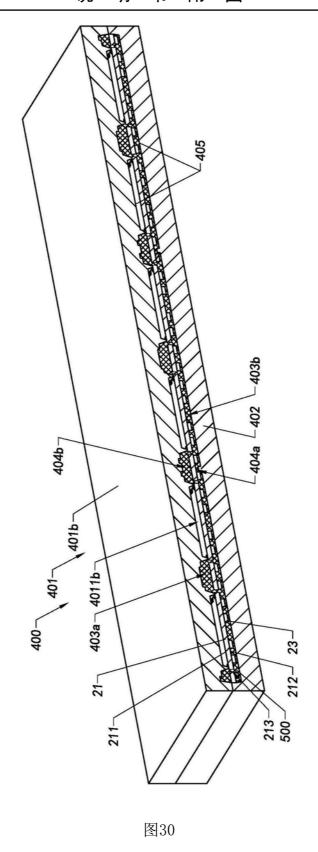

- [0174] 图30是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

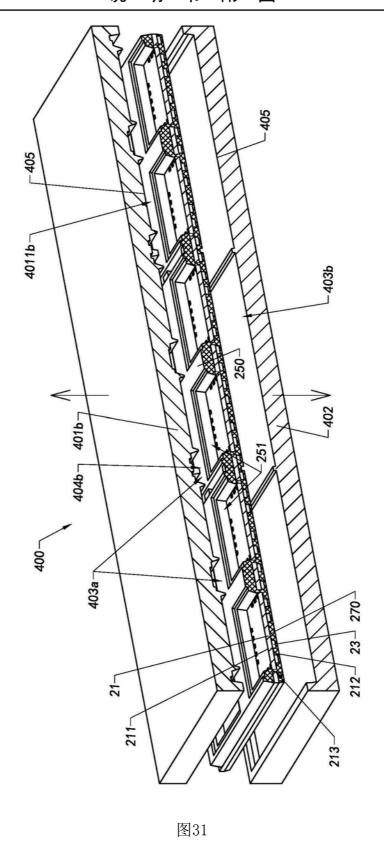

- [0175] 图31是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

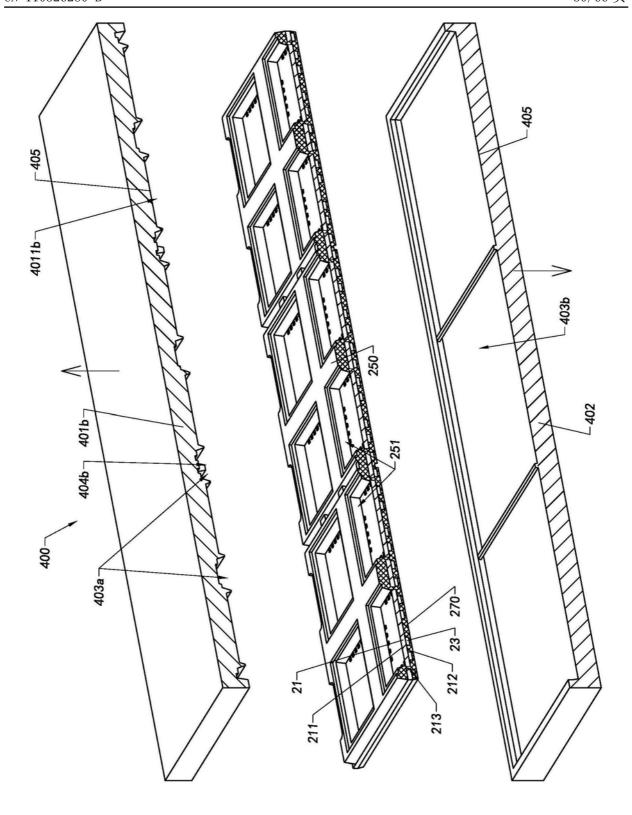

- [0176] 图32是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示

意图。

[0177] 图33是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

[0178] 图34是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

[0179] 图35是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

[0180] 图36是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

[0181] 图37是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造步骤的示意图。

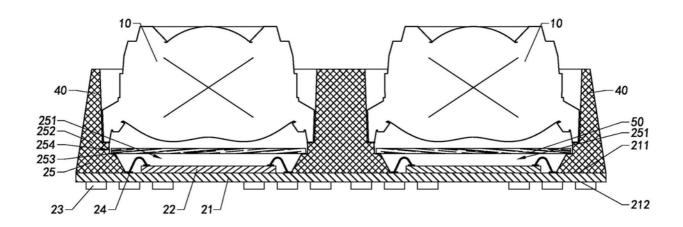

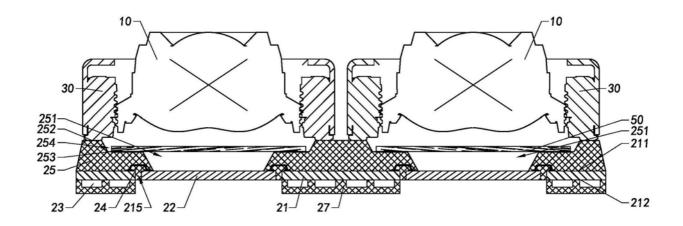

[0182] 图38是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的剖视示意图。

[0183] 图39是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的剖视示意图。

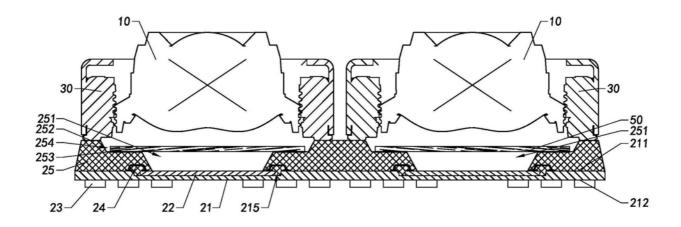

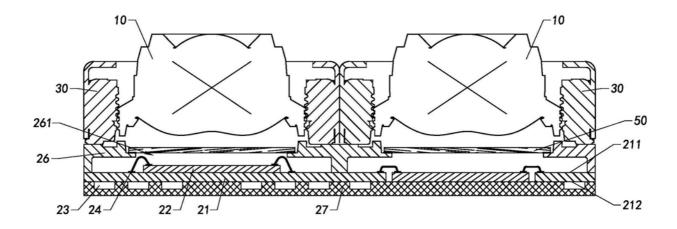

[0184] 图40是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的剖视示意图。

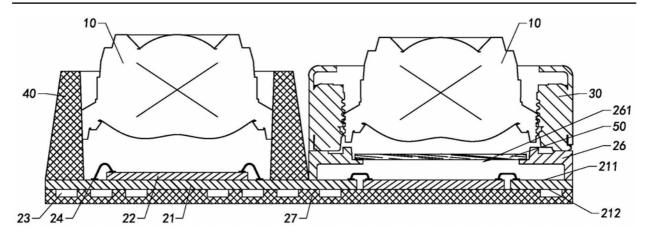

[0185] 图41是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的剖视示意图。

[0186] 图42是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的剖视示意图。

[0187] 图43是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的剖视示意图。

[0188] 图44是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的剖视示意图。

[0189] 图45是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的剖视示意图。

[0190] 图46是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的剖视示意图。

[0191] 图47是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的剖视示意图。

[0192] 图48是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的剖视示意图。

[0193] 图49是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的剖视示意图。

[0194] 图50是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的剖视示意图。

[0195] 图51是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的剖视示意图。

[0196] 图52是依本发明的上述较佳实施例的所述阵列摄像模组的另一个变形实施方式的剖视示意图。

[0197] 图53是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0198] 图54是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0199] 图55是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0200] 图56是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0201] 图57是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0202] 图58是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0203] 图59是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0204] 图60是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0205] 图61是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0206] 图62是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的剖视示意图。

[0207] 图63是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的剖视示意图。

[0208] 图64A是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0209] 图64B是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0210] 图65是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0211] 图66是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的剖视示意图。

[0212] 图67是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0213] 图68是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0214] 图69是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0215] 图70是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的

剖视示意图。

[0216] 图71是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0217] 图72是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0218] 图73是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0219] 图74是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0220] 图75是依本发明的上述较佳实施例的所述阵列摄像模组另一个变形实施方式的 剖视示意图。

[0221] 图76是依本发明的一个较佳实施例的一阵列摄像模组的一个制造流程示意图。

[0222] 图77是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造流程示意图。

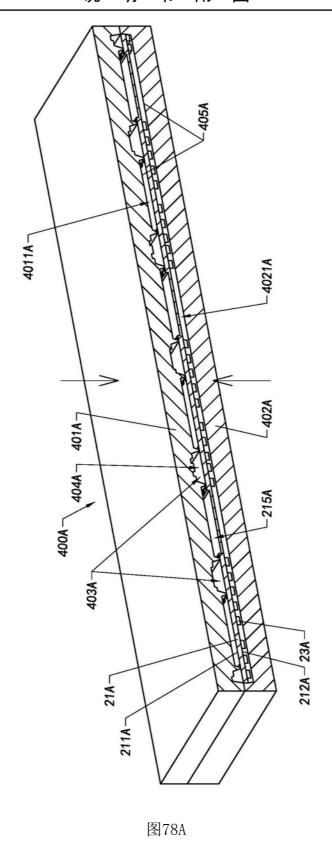

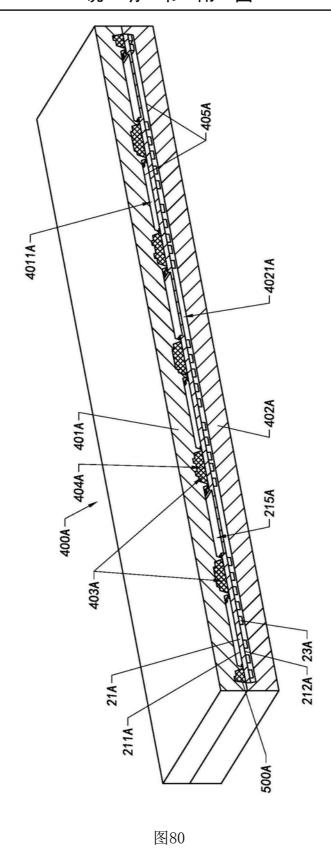

[0223] 图78A和图78B是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造流程示意图。

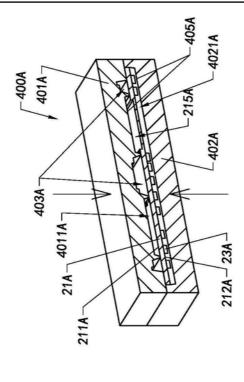

[0224] 图79是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造流程示意图。

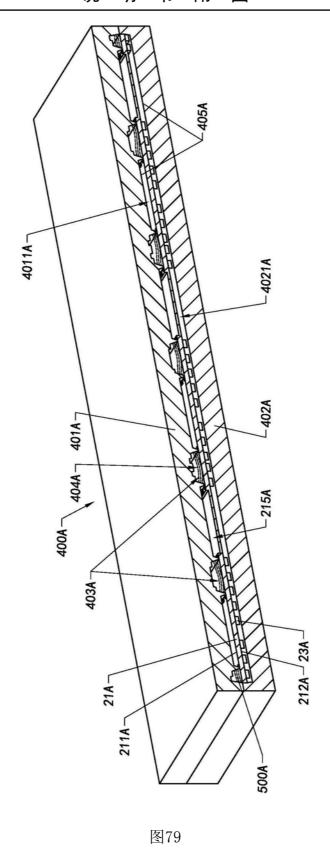

[0225] 图80是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造流程示意图。

[0226] 图81是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造流程示意图。

[0227] 图82是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造流程示意图。

[0228] 图83是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造流程示意图。

[0229] 图84是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造流程示意图。

[0230] 图85是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造流程示意图。

[0231] 图86是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造流程示意图。

[0232] 图87是依本发明的上述较佳实施例的所述阵列摄像模组的另一个制造流程示意图。

[0233] 图88是依本发明的上述较佳实施例的所述阵列摄像模组的立体示意图。

[0234] 图89是依本发明你的上述较佳实施例的所述阵列摄像模组的应用状态示意图。

[0235] 图90是依本发明的上述较佳实施例的所述摄像模组的另一个变形实施方式的剖视示意图。

[0236] 图91是依本发明的上述较佳实施例的所述摄像模组的另一个变形实施方式的剖

视示意图。

[0237] 图92是依本发明的上述较佳实施例的所述摄像模组的另一个变形实施方式的剖视示意图。

[0238] 图93是依本发明的上述较佳实施例的所述摄像模组的另一个变形实施方式的剖视示意图。

[0239] 图94是依本发明的上述较佳实施例的所述摄像模组的另一个变形实施方式的剖视示意图。

[0240] 图95是依本发明的上述较佳实施例的所述摄像模组的另一个变形实施方式的剖视示意图。

[0241] 图96是依本发明的上述较佳实施例的所述摄像模组的另一个变形实施方式的剖视示意图。

[0242] 图97是依本发明的上述较佳实施例的所述摄像模组的另一个变形实施方式的剖视示意图。

[0243] 图98是依本发明的上述较佳实施例的所述摄像模组的另一个变形实施方式的剖视示意图。

[0244] 图99是依本发明的上述较佳实施例的所述摄像模组的另一个变形实施方式的剖视示意图。

[0245] 图100是依本发明的上述较佳实施例的所述摄像模组的另一个变形实施方式的剖视示意图。

[0246] 图101是依本发明的上述较佳实施例的所述摄像模组的另一个变形实施方式的剖视示意图。

[0247] 图102是依本发明的上述较佳实施例的所述摄像模组的另一个变形实施方式的剖视示意图。

[0248] 图103是依本发明的上述较佳实施例的所述摄像模组的另一个变形实施方式的剖视示意图。

[0249] 图104是依本发明的上述较佳实施例的所述摄像模组的另一个变形实施方式的剖视示意图。

#### 具体实施方式

[0250] 以下描述用于揭露本发明以使本领域技术人员能够实现本发明。以下描述中的优选实施例只作为举例,本领域技术人员可以想到其他显而易见的变型。在以下描述中界定的本发明的基本原理可以应用于其他实施方案、变形方案、改进方案、等同方案以及没有背离本发明的精神和范围的其他技术方案。

[0251] 本领域技术人员应理解的是,在本发明的揭露中,术语"纵向"、"横向"、"上"、"下"、"前"、"后"、"左"、"右"、"竖直"、"水平"、"顶"、"底""内"、"外"等指示的方位或位置关系,其仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此上述术语不能理解为对本发明的限制。

[0252] 可以理解的是,术语"一"应理解为"至少一"或"一个或多个",即在一个实施例中,

一个元件的数量可以为一个,而在另外的实施例中,该元件的数量可以为多个,术语"一"不能理解为对数量的限制。

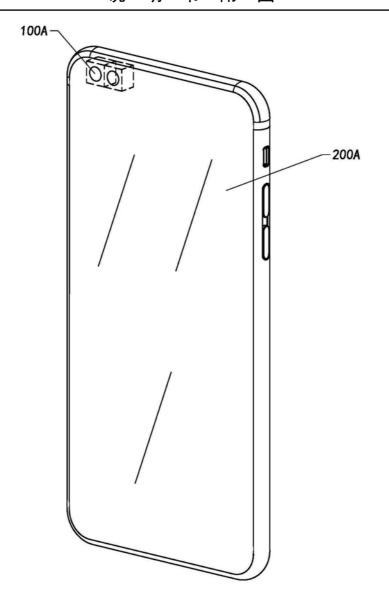

[0253] 参考本发明的说明书附图之附图1至图6,依本发明的一较佳实施例的一阵列摄像模组100在接下来的描述中被阐述,其中在附图1中示出的所述阵列摄像模组100的一个使用状态,例如,在附图1示出的示例中,一个所述阵列摄像模组100能够被应用于被具体实施为智能手机的一电子设备本体200,以使所述阵列摄像模组100能够和所述电子设备本体200相互结合而形成一电子设备。

[0254] 值得一提的是,尽管在附图1示出的示例中,所述阵列摄像模组100的数量为一个,且所述阵列摄像模组100被设置于所述电子设备本体200的后部,在其他的示例中,所述阵列摄像模组100的数量不限于一个,并且所述阵列摄像模组100的位置也不限于被设置于所述电子设备本体200的后部,例如所述阵列摄像模组100可以被设置于所述电子设备本体200的前部,当然,所述阵列摄像模组100被设置在所述电子设备本体200的其他位置也是可能的。

[0255] 另外,所述电子设备本体200尽管在附图1中被实施为智能手机,在本发明的其他示例中,所述电子设备本体200也可以被实施为平板电脑、笔记本电脑、相机、个人数字助理、电纸书、MP3/4/5等任何能够被配置所述阵列摄像模组100的电子设备。当然,本领域的技术人员应当理解,在冰箱、洗衣机、电视机等传统的家电上配置所述阵列摄像模组100也是可能的,或者在防盗门、墙壁等建筑上配置所述阵列摄像模组100也是可能的,因此,所述阵列摄像模组100的应用环境和使用方式并不应被视为对本发明的所述阵列摄像模组的内容和范围的限制。

[0256] 值得一提的是,在附图1示出的所述阵列摄像模组100的这个具体的应用中,所述电子设备本体200被实施为智能手机,所述阵列摄像模组100被设置在所述电子设备本体200的后部以形成所述智能手机的一个后置摄像模组。本领域技术人员应当理解的是,在其他的可能示例中,所述阵列摄像模组100还可以被设置在所述电子设备本体200的前部以形成所述智能手机的一个前置摄像模组。

[0257] 参考附图2至图6,所述阵列摄像模组100包括至少两光学镜头10和一电路板组件20,其中所述电路板组件20包括至少一电路板21、至少两感光芯片22以及至少一电子元器件23,其中所述感光芯片22和所述电路板21被导通地连接,每个所述电子元器件23均被贴装于所述电路板21,所述光学镜头10被保持在所述感光芯片22的感光路径。被物体反射的光线能够自所述光学镜头10进入所述阵列摄像模组100的内部,以在后续被所述感光芯片22接收和成像,从而获得与所述物体相关联的图像。

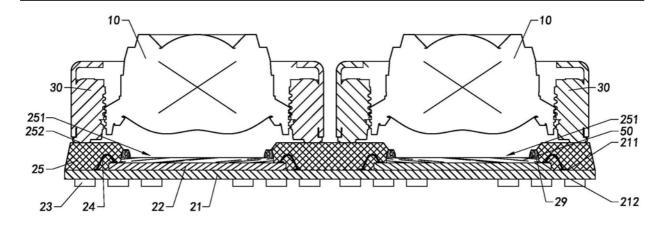

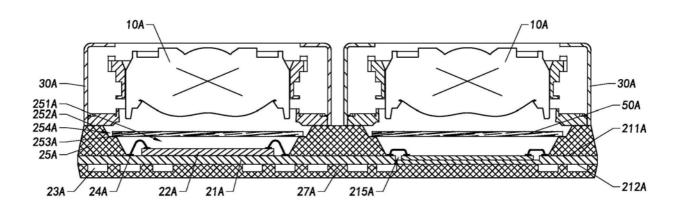

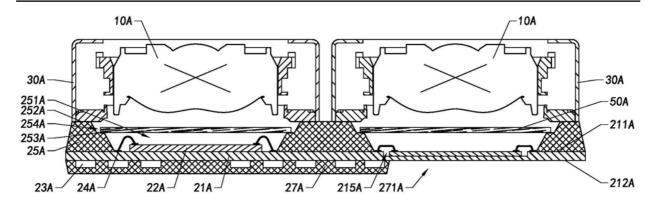

[0258] 例如,在附图4和图5示出的所述阵列摄像模组100的这个具体的示例中,所述阵列摄像模组100包括两个所述光学镜头10和一个所述电路板组件20,以使所述阵列摄像模组100形成一个双镜头摄像模组,其中所述电路板组件20包括一个所述电路板21、两个所述感光芯片22以及多个所述电子元器件23,其中两个所述感光芯片22相互间隔地被贴装于所述电路板21的一侧,每个所述电子元器件23分别被相互间隔地贴装于所述电路板21的另外一侧,每个所述光学镜头10分别被保持在每个所述感光芯片22的感光路径。被物体反射的光线能够分别自每个所述光学镜头10进入所述阵列摄像模组100的内部,然后被分别被对应位置的每个所述感光芯片22接收和成像,从而获得与所述物体相关联的图像。

[0259] 值得一提的是,尽管在接下来的描述和说明书附图中以所述阵列摄像模组100被实施为双镜头生想模组为例来灰阐述本发明的所述阵列摄像模组100的内容和特征,但本领域技术人员应当理解的是,本发明的所述阵列摄像模组100还可以包括三个以上的所述感光芯片22和三个以上的所述光学镜头10。因此,以所述阵列摄像模组100被实施为双镜头摄像模组为例来阐述本发明的所述阵列摄像模组100的内容和特征的方式仅为示例,其并不应被视为对本发明的所述阵列摄像模组100的内容和范围的限制。

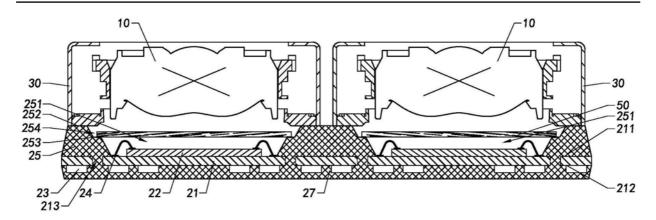

[0260] 进一步参考附图4和图5,所述电路板21具有一正面211和对应于所述正面211的一背面212,每个所述感光芯片22可以以被贴装于所述电路板21的所述正面211的方式和所述电路板21结合在一起。相应地,每个所述电子元器件23可以以被贴装于所述电路板21的所述背面212的方式和所述电路板21结合在一起。换言之,每个所述电子元器件23在所述电路板21的所述背面212和所述电路板21相导通。

[0261] 值得一提的是,在本发明的所述阵列摄像模组100的其他可能的示例中,至少一个所述电子元器件23也可以在所述电路板21的所述正面211被导通地连接于所述电路板21。也就是说,在所述阵列摄像模组100的这个具体的示例中,至少一个所述电子元器件23可以在所述电路板21的所述正面211被导通地连接于所述电路板21,另外的所述电子元器件23可以在所述电路板21的所述背面212被导通地连接于所述电路板21。

[0262] 还值得一提的是,尽管在附图4和图5中示出了所述电子元器件23以所述电子元器件23被贴装于所述电路板21的所述背面212的方式被导通地连接于所述电路板21,在本发明的所述阵列摄像模组100的其他可能的示例中,所述电子元器件23也可以以所述电子元器件23的至少一部分被埋入所述电路板21的方式被导通地连接于所述电路板21。

[0263] 值得一提的是,在本发明的所述阵列摄像模组100的一个示例中,所述电子元器件23可以被实施为电阻、电容、继电器、处理器等被动电子元器件。换言之,所述电子元器件23的类型在本发明的所述阵列摄像模组100中不受限制。

[0264] 进一步地,所述电路板组件20包括至少一组引线24,其中每个所述引线24的两个端部分别连接于所述电路板21和所述感光芯片22,以藉由每个所述引线24导通所述感光芯片22和所述电路板21。

[0265] 例如,在一个示例中,可以先将所述感光芯片22贴装于所述电路板21的所述正面211,然后再通过诸如打线等工艺在所述感光芯片22和所述电路板21之间设置每个所述引线24,以藉由每个所述引线24导通所述电路板21和所述感光芯片22。可以理解的是,所述感光芯片22的平整度受限于所述电路板21的平整度。当然,在另外的一些示例中,也可以不需要将所述感光芯片22和所述电路板21直接贴装在一起,从而使所述感光芯片22的平整度可以不受所述电路板21的平整度的影响,或者即便是将所述感光芯片22贴装于所述电路板21,所述感光芯片22的平整度也可以不受所述电路板21的平整度的影响,通过这样的方式,能够使所述电路板21选择厚度更薄的板材制得。

[0266] 所述引线24的打线方向在本发明的所述阵列摄像模组100中不受限制,例如所述引线24的打线方向可以从所述感光芯片22至所述电路板21,也可以从所述电路板21至所述感光芯片22,当然,所述引线24还可以有其他的方式被用于导通所述感光芯片22和所述电路板21,本发明的所述阵列摄像模组100在这方面不受限制。可以理解的是,所述引线24的材料在本发明的所述阵列摄像模组100中也不受限制,例如所述引线24可以是但不限于金

线、银线、铜线等。

[0267] 当然,可以理解的是,在一些示例中,所述感光芯片22可以预设芯片连接件,所述电路板21可以预设电路板连接件,所述引线24的两个端部可以分别和所述感光芯片22的芯片连接件与所述电路板21的电路板连接件相互接触,而导通所述感光芯片22和所述电路板21,例如所述引线24的两个端部可以分别被焊接在所述感光芯片22的芯片连接件和所述电路板21的电路板连接件,从而藉由所述引线24导通所述感光芯片22和所述电路板21。值得一提的是,所述感光芯片22的芯片连接件和所述电路板21的电路板连接件的形状和尺寸可以不受限制,例如所述感光芯片22的芯片连接件和所述电路板21的电路板连接件可以分别被实施为但不限于盘状、球状等。

[0268] 参考附图6,在设有所述引线24的一侧,设所述感光芯片22的外边沿到所述电路板21的外边缘的距离为L1,在没有所述引线24的一侧,设所述感光芯片22的外边沿到所述电路板21的外边缘的距离为L2,其中L1的最小距离为0.1mm~3mm,优选为0.3mm~0.8mm,其中L2的最小距离为0.05mm~3mm,优选为0.1mm~0.5mm。

[0269] 参考附图4和图5,在本发明的所述阵列摄像模组100的这个实施例中,每个所述电子元器件23分别被相互间隔地贴装于所述电路板21的所述背面212,也就是说,每个所述电子元器件23可以不需要被布置在所述感光芯片22的周向,这样,有利于减少所述电路板组件20的长宽尺寸,从而减少所述阵列摄像模组100的长宽尺寸,以使得所述阵列摄像模组100能够被应用于追求轻薄化的所述电子设备。

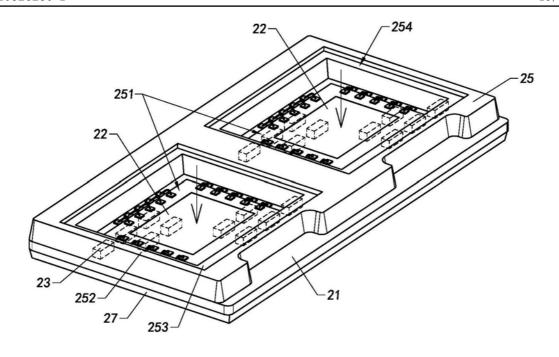

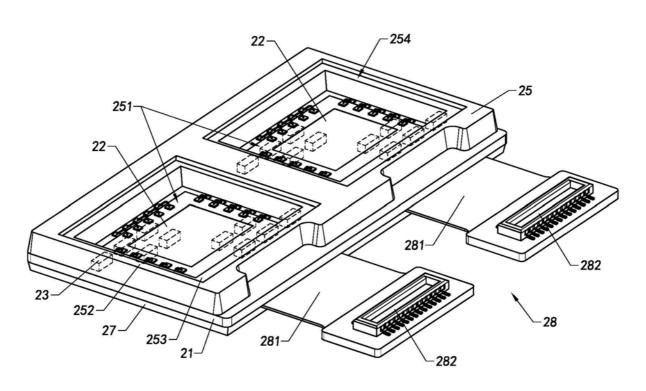

[0270] 所述电路板组件20进一步包括一模制基座25,其中所述模制基座25可以一体地形成于所述电路板21的所述正面211,其中所述模制基座25具有至少一光窗251,所述感光芯片22的感光区域对应于所述光窗251,以藉由所述模制基座25的所述光窗251形成所述光学镜头10和所述感光芯片22的光线通路。

[0271] 例如,在附图4和图5示出的所述阵列摄像模组100的这个具体的示例中,所述模制基座25具有两个相互独立的所述光窗251,其中每个所述感光芯片22的感光区域分别对应于所述模制基座25的每个所述光窗251,以藉由所述模制基座25的每个所述光窗251分别形成每个所述光学镜头10和每个所述感光芯片22的光线通路。也就是说,被物体反射的光线在自每个所述光学镜头10进入所述阵列摄像模组100的内部后,能够经由所述模制基座25的每个所述光窗251后被每个所述感光芯片22的感光区域接收,并在后续藉由每个所述感光芯片22进行光电转化而成像。

[0272] 所述模制基座25可以通过模制工艺一体地成型于所述电路板21的所述正面211,通过这样的方面,在所述模制基座25和所述电路板21之间不需要设置诸如胶水等用于连接所述模制基座25和所述电路板21的物质,这样,不仅能够降低所述阵列摄像模组100的高度尺寸,而且还能够有效保证所述电路板21的平整度,以改善所述阵列摄像模组100的成像品质。另外,因为在所述模制基座25和所述电路板21的所述正面211之间不需要设置诸如胶水等用于连接所述模制基座25和所述电路板21的物质,因此,所述阵列摄像模组100的高度尺寸能够被降低,以有利于所述阵列摄像模组100被应用于更轻薄的所述电子设备。更为重要的是,所述模制基座25在成型的过程中一体地结合于所述电路板21,从而一方面所述模制基座25不需要被预制,另一方面不用担心所述模制基座25在未结合于所述电路板21之前出现变形的不良现象。并且,所述模制基座25能够补强所述电路板21的强度,以保证所述电路

板21的平整度,从而即便是所述电路板21被选用较薄的PCB板、FPC板、软硬结合板等厚度更薄的电路板时,所述模制基座25也能够保证所述电路板21的平整度,通过这样的方式,多个所述感光芯片22的同轴度也能够被保证。

[0273] 所述阵列摄像模组100进一步包括至少一驱动器30,其中所述光学镜头10被可驱动地设置于所述驱动器30,所述驱动器30被设置于所述模制基座25,以藉由所述驱动器30和所述模制基座25相互配合而使所述光学镜头10被保持在所述感光芯片22的感光路径。所述驱动器30能够驱动所述光学镜头10沿着所述感光芯片22的感光路径移动,以调整所述阵列摄像模组100的焦距,从而使得阵列摄像模组100具有自动对焦和变焦能力。优选地,所述驱动器30可以被实施为但不限于音圈马达。

[0274] 例如,在附图2至图4示出的所述阵列摄像模组100的这个具体的示例中,所述驱动器30的数量被实施为两个,其中每个所述光学镜头10分别被可驱动地设置于每个所述驱动器30,每个所述驱动器30分别以每个所述光学镜头10对应于所述模制基座25的每个所述光窗251的方式被贴装于所述模制基座25,以藉由每个所述驱动器30将每个所述光学镜头10保持在每个所述感光芯片22的感光路径。

[0275] 值得一提的是,在本发明的所述阵列摄像模组100的一些具体的示例中,每个所述驱动器30分别以同时且同幅度的方式驱动每个所述光学镜头10沿着每个所述感光芯片22的感光路径移动。在本发明的所述阵列摄像模组100的另外一些具体的示例中,每个所述驱动器30分别单独地驱动每个所述光学镜头10沿着每个所述感光芯片22的感光路径移动。例如在附图4示出的所述阵列摄像模组100的这个具体的示例中,位于附图左侧的所述驱动器30能够驱动所述光学镜头10沿着所述感光芯片22的感光路径移动,而位于附图右侧的所述驱动器30可以不动。

[0276] 进一步参考附图4,所述阵列摄像模组100可以包括至少一滤光元件50,其中每个所述滤光元件50分别被保持在每个所述感光芯片22和每个所述光学镜头10之间,以用于过滤自每个所述光学镜头10进入所述阵列摄像模组100的内部的光线中的杂光,从而改善所述阵列摄像模组100的成像品质。所述滤光元件50的类型不受限制,例如所述滤光元件50可以被实施为但不限于红外截止滤光片。

[0277] 例如,在附图4示出的所述阵列摄像模组100的这个具体的示例中,所述阵列摄像模组100包括两个所述滤光元件50,其中每个所述滤光元件50分别被贴装于所述模制基座25,并且每个所述滤光元件50分别被保持在每个所述感光芯片22和每个所述光学镜头10之间,以藉由每个所述滤光元件50过滤自每个所述光学镜头10进入所述阵列摄像模组100的内部的光线中的杂光。尽管如此,本领域的技术人员应当理解的是,在本发明的所述阵列摄像模组100的另外一些具体的示例中,所述阵列摄像模组100也可以包括一个所述滤光元件50,此时,两个以上的所述感光芯片22可以对应于同一个所述滤光元件50的不同位置,以藉由所述滤光元件50过滤自每个所述光学镜头10进入所述阵列摄像模组100的内部的光线中的杂光。

[0278] 值得一提的是,在所述阵列摄像模组100包括两个以上的所述滤光元件50的示例中,每个所述滤光元件50的类型可以一样,也可以不一样,其根据需要被选择,本领域技术人员应当理解的是,若所述阵列摄像模组100的每个所述滤光元件50的类型不同,则所述阵列摄像模组100的每个光学系统可以具有不同的成像特色。值得一提的是,所述阵列摄像模

组100的每个光学系统藉由一个所述感光芯片22和被保持在所述感光芯片22的感光路径的一个所述光学镜头10形成。例如,在附图4示出的所述阵列摄像模组100的这个具体的示例中,位于附图左侧的所述滤光元件50的类型和位于附图右侧的所述滤光元件50的类型可以不同。

[0279] 更进一步地,所述模制基座25具有一外贴装面252和至少一内贴装面253,每个所述内贴装面253分别围绕在所述模制基座25的每个所述光窗251的周围,所述外贴装面252围绕在每个所述内贴装面253的周围,其中每个所述驱动器30可以被贴装于所述模制基座25的所述外贴装面252的不同位置,每个所述滤光元件50可以分别被贴装于所述模制基座25的每个所述内贴装面253,通过这样的方式,能够使每个所述光学镜头10被分别保持在每个所述感光芯片22的感光路径,和使每个所述滤光元件50分别被保持在每个所述感光芯片22和每个所述光学镜头10之间。

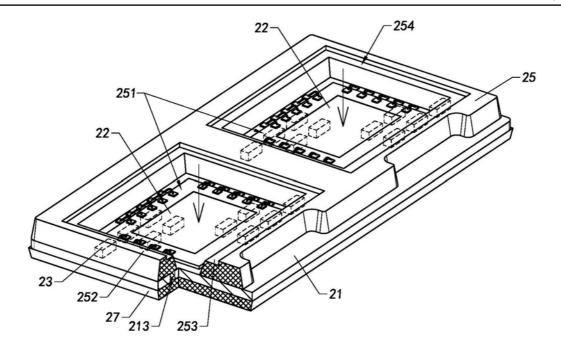

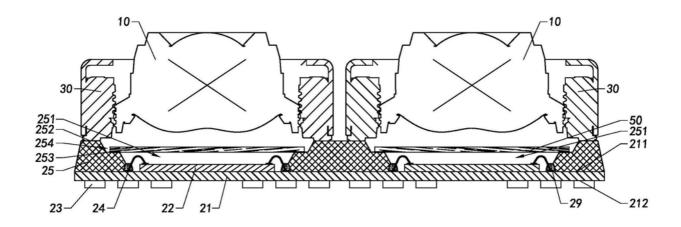

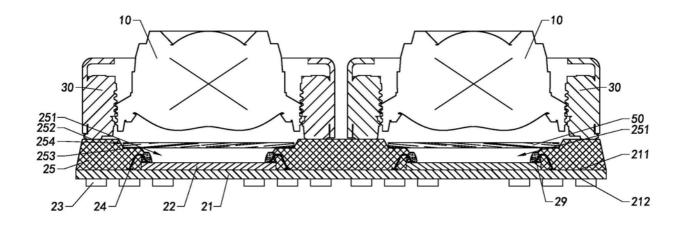

[0280] 在一个示例中,所述模制基座25的所述外贴装面252和所述内贴装面253可以处于同一个平面。在另一个示例中,所述模制基座25的所述外贴装面252和所述内贴装面253可以具有高度差,以形成所述模制基座25的至少一贴装槽254。具体地,所述模制基座25的所述内贴装面253所在的平面低于所述外贴装面252所在的平面,从而所述模制基座25在所述内贴装面253对应的位置形成所述贴装槽254,这使得被贴装于所述内贴装面253的所述滤光元件50被保持在所述贴装槽254内,通过这样的方式,能够进一步降低所述阵列摄像模组100的高度尺寸,参考附图4示出的所述阵列摄像模组100。

[0281] 值得一提的是,在附图4示出的所述阵列摄像模组100的这个具体的示例中,所有的所述电子元器件23均可以被相互间隔地贴装于所述电路板21的所述背面212,而在附图7示出的所述阵列摄像模组100的一个变形实施方式中,至少一个所述电子元器件23可以被贴装于所述电路板21的所述背面212,另外的所述电子元器件23可以被贴装于所述电路板21的所述正面211。为了便于接下来的阐述,将被贴装于所述电路板21的所述正面211的所述电子元器件23定义为一第一电子元器件23a,和将被贴装于所述电路板21的所述背面212的所述电子元器件23定义为一第二电子元器件23b。

[0282] 也就是说,所述电路板组件20可以包括至少一个所述第一电子元器件23a和至少一个所述第二电子元器件23b,其中每个所述第一电子元器件23a分别被相互间隔地贴装于所述电路板21的所述正面211,每个所述第二电子元器件23b分别被相互间隔地贴装于所述电路板21的所述背面212。

[0283] 值得一提的是,将所述电子元器件23按照所述电子元器件23被贴装的位置区分为所述第一电子元器件23a和所述第二电子元器件23b,仅仅是为了便于描述和便于理解本发明的所述阵列摄像模组100,其并不构成对本发明的所述阵列摄像模组100的内容和范围的限制,其中所述第一电子元器件23a和所述第二电子元器件23b的类型可以是相同的。

[0284] 另外,可以将实现同一种功能或者同一类功能的所述电子元器件23贴装在所述电路板21的一侧,而将实现另一种功能或者另一类功能的所述电子元器件23贴装在所述电路板21的另一侧,本发明的所述阵列摄像模组100在这些方面均不受限制。

[0285] 在每个所述第一电子元器件23a被相互间隔地贴装于所述电路板21的所述正面211后,每个所述第一电子元器件23a可以被布置在所述感光芯片22的周向方向。例如,每个所述第一电子元器件23a可以被布置在所述感光芯片22的一个侧部,或者相对的两个侧部,

或者相邻的两个侧部,或者多个侧部。在每个所述第二电子元器件23b被相互间隔地贴装于所述电路板21的所述背面212后,在所述阵列摄像模组100的高度方向,所述第二电子元器件23b可以和所述感光芯片22相互重叠,或者所述第二电子元器件23b可以和所述第一电子元器件23a相互重叠,从而有利于减小所述阵列摄像模组100的长宽尺寸,以利于所述阵列摄像模组100被应用于追求轻薄化和智能化的所述电子设备。

在附图7示出的所述阵列摄像模组100的这个示例中,至少一个所述第一电子元器 件23a的至少一部分能够被所述模制基座25包埋。优选地,所述模制基座25能够包埋全部的 所述第一电子元器件23a,通过这样的方式,一方面,所述第一电子元器件23a能够防止所述 模制基座25从所述电路板21的所述正面211脱落,另一方面,所述模制基座25能够阻止所述 第一电子元器件23a和外部环境接触,从而避免所述第一电子元器件23a的表面出现氧化等 不良现象,第三方面,所述模制基座25能够隔离相邻的所述第一电子元器件23a,从而避免 相邻所述第一电子元器件23a出现相互干扰等不良现象,以改善所述阵列摄像模组100的成 像品质,第四方面,所述模制基座25能够隔离相邻的所述第一电子元器件23a,从而使得相 邻所述第一电子元器件23a的距离更近,这样有利于在有限面积的所述电路板21上贴装数 量更多和尺寸更大的所述第一电子元器件23a,以利于提高所述阵列摄像模组100的性能, 第五方面,在所述模制基座25和所述第一电子元器件23a之间不需要预留安全距离,从而使 得所述阵列摄像模组100的长宽尺寸和高度尺寸都能够被缩小,以利于所述阵列摄像模组 100的小型化,第六方面,所述模制基座25能够隔离所述第一电子元器件23a和所述感光芯 片22的感光区域,以避免所述感光芯片22的感光区域被所述第一电子元器件23a的表面脱 落的杂质等污染物或者从所述第一电子元器件23a和所述电路板21的连接位置脱落的焊粉 等污染物污染,以有利于保证所述阵列摄像模组100的成像品质。

[0287] 在附图4和图7示出的所述阵列摄像模组100的这些示例中,所述第二电子元器件23b是裸露的。而在附图8示出的所述阵列摄像模组100的这个具体的示例中,所述第二电子元器件23b也可以被包埋起来。具体地说,所述电路板组件20进一步包括至少一包埋部27,其中所述包埋部27一体地形成于所述电路板21的所述背面212,以包埋至少一个所述第二电子元器件23b的至少一部分。

[0288] 附图9示出了所述阵列摄像模组100的另一个变形实施方式,与附图4示出的所述阵列摄像模组100不同的是,在附图9示出的所述阵列摄像模组100的这个具体的示例中,所述电路板组件20包括至少一个所述包埋部27,其中所述包埋部27一体地结合于所述电路板21的所述背面212,并且所述包埋部27能够包埋凸出于所述电路板21的所述背面212的至少一个所述电子元器件23的至少一部分。

[0289] 优选地,所述包埋部27可以包埋凸出于所述电路板21的所述背面212的全部的所述电子元器件23,通过这样的方式,一方面,所述电子元器件23能够防止所述包埋部27从所述电路板21的所述背面212脱落,另一方面,所述包埋部27能够阻止所述电子元器件23和外部环境接触,从而避免所述电子元器件23的表面出现氧化等不良现象,第三方面,所述包埋部27能够隔离相邻的所述电子元器件23,从而避免相邻的所述电子元器件23出现相互干扰等不良现象,以改善所述阵列摄像模组100的成像品质,第四方面,所述包埋部27能够隔离相邻的所述电子元器件23,从而使得相邻所述电子元器件23的距离更近,这样有利于在有限面积的所述电路板21上贴装数量更多和尺寸更大的所述电子元器件23,以利于提高所述

阵列摄像模组100的性能,第五方面,所述包埋部27还能够保证所述电路板21的平整度,从而使得所述电路板21可以选用厚度更薄的板材,例如FPC电路板或者软硬结合板,以有利于降低所述阵列摄像模组100的高度尺寸。

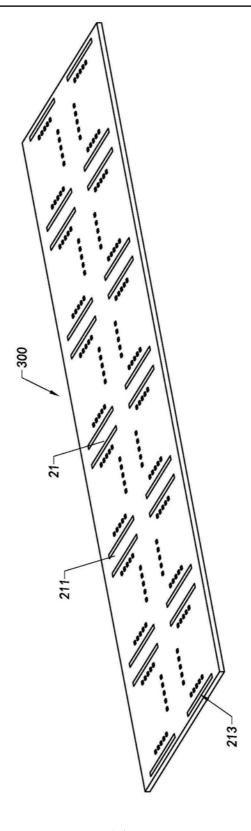

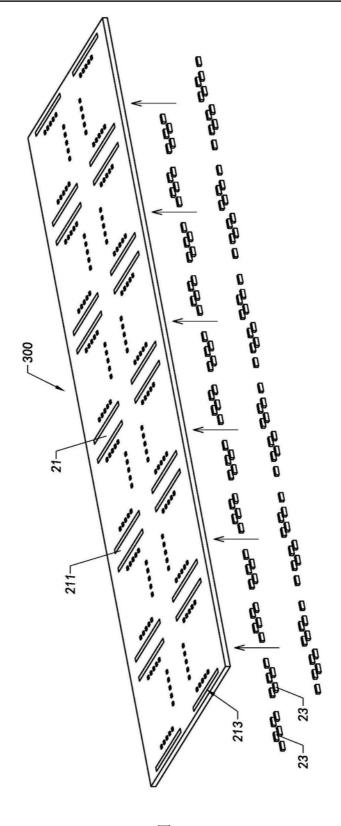

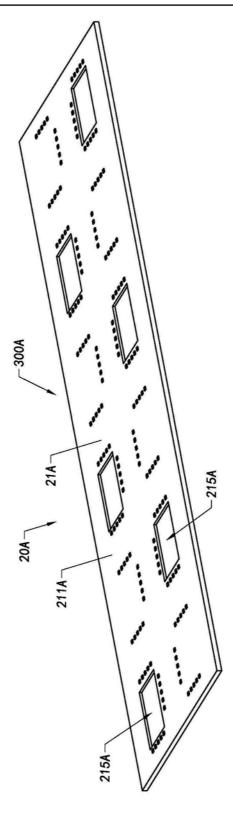

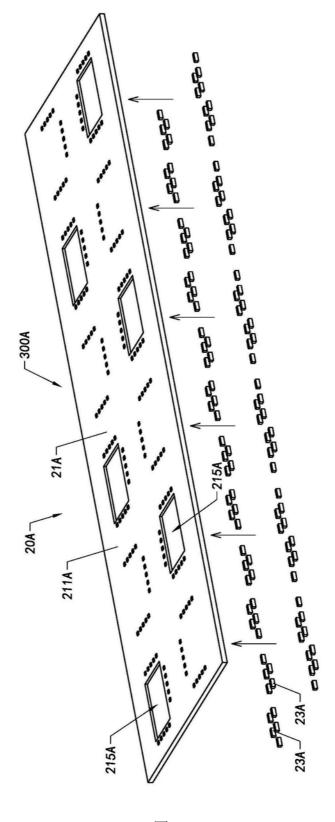

[0290] 本发明的说明书附图之附图10至图22示出了所述阵列摄像模组100的制造流程,其中在附图10示出的阶段,可以将两个以上的所述电路板21排列在一起而形成一拼板单元300,以便于在后续执行模制工艺。例如,可以将多个所述电路板21排列成但不限于两排而形成所述拼板单元300。当然,本领域技术人员应当理解的是,在本发明的所述阵列摄像模组100的其他示例中,所述拼板单元300可以包括更多排的所述电路板21。

[0291] 值得一提的是,所述电路板21可以在形成后被排列而形成所述拼板单元300,例如单独形成的所述电路板21可以被排列在一个基底上而形成所述拼板单元300,或者多个所述电路板21可以是一体式结构,其在被完成模制工艺后被进行切割而分离。在本发明的接下来的描述中,以多个所述电路板21是一体式结构为例,继续对所述阵列摄像模组100的制造流程进行揭露和阐述。

[0292] 在附图11示出的阶段,可以将每个所述电子元器件23分别在所述电路板21的所述背面212贴装于所述电路板21。尽管如此,本领域的技术人员应当理解的是,一些所述电子元器件23可以被贴装于所述电路板21的所述背面212,而另一些所述电子元器件23也可以被贴装于所述电路板21的所述正面211。本发明的所述阵列摄像模组100在这方面不受限制。

[0293] 值得一提的是,尽管在附图11中示出的所述阵列摄像模组100的具体示例中,所述电子元器件23被贴装于所述电路板21的所述背面212,在另一些具体的示例中,所述电子元器件23的至少一部分也可以被埋入到所述电路板21的所述背面212,例如,所述电子元器件23的一部分可以埋入所述电路板21,并且所述电子元器件23的另一部分暴露在或者凸出于所述电路板21的所述背面212。可选地,所述电子元器件23也可以全部被埋入到所述电路板21。

[0294] 还值得一提的是,在单独地制作每个所述电路板21,再将每个所述电路板21排列成所述拼板单元300的示例中,也可以首先在所述电路板21的所述背面212贴装每个所述电子元器件23,然后再排列每个所述电路板21而形成所述拼板单元300。

[0295] 另外,所述电路板21可以被排列成不同于附图10和图11示出的样式,或者所述电路板21也可以没有被排列,从而在后续的模制工艺中,可以单独地在所述电路板21上执行模制工艺而形成与所述电路板21一体地结合的所述模制基座25。

[0296] 优选地,所述拼板单元300的相邻所述电路板21之间的距离的范围是0.01mm~500mm(包括0.01mm和500mm),以便于在模制工艺完成后,对所述电路板21进行分割。优选地,相邻所述基板311之间的距离范围是0.05mm~200mm(包括0.05mm和200mm)。另外,为了提高局部成型的稳定性,所述拼板单元300的最小尺寸范围是1mm~10000mm(包括1mm和10000mm),优选为10mm~1000mm(包括10mm和1000mm)。

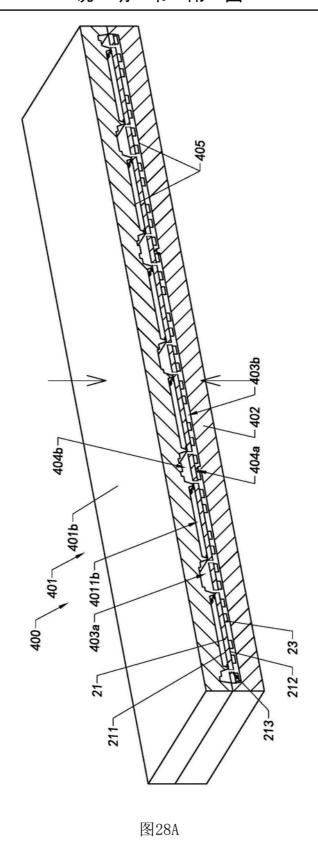

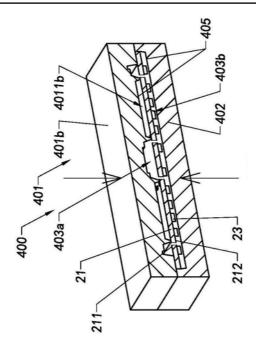

[0297] 参考附图12A至图15,将所述拼板单元300放置在一成型模具400中进行模制工艺,其中所述成型模具400包括一上模具401和一下模具402,其中所述上模具401和所述下模具402中的至少一个模具能够被操作,以使所述成型模具400的所述上模具401和所述下模具402能够被合模和拔模。优选地,所述上模具401包括一第一上模具401a和一第二上模具

401b,其中所述第一上模具401a和所述下模具402中的至少一个模具能够被操作,以使所述第一上模具401a和所述下模具402能够被合模和拔模,和所述第二上模具401b和所述下模具402中的至少一个模具能够被操作,以使所述第二上模具401b和所述下模具402能够被合模和拔模。

[0298] 参考附图12A和图12B,所述拼板单元300被放置于所述成型模具400的所述第一上模具401a和所述下模具402之间,并且在所述拼板单元300和所述下模具402之间形成至少一下部成型空间403a。所述拼板单元300的所述电路板21的所述背面212朝向所述下模具402,凸出于所述电路板21的所述背面212的所述电子元器件23被保持在所述下部成型空间403a,并避免所述下模具402的内壁接触所述电子元器件23,通过这样的方式,能够避免所述电子元器件23因受压或者因接触所述下模具402的内壁而被损坏。优选地,在所述拼板单元300和所述下模具402之间还形成至少一下部连通通道404a,以供连通相邻所述下部成型空间403a。优选地,所述第一上模具401a具有至少一第一避让空间4011a,其中在所述第一上模具401a和所述下模具402被合模且所述拼板单元300被保持在所述第一上模具401a和所述下模具402之间后,凸出于所述电路板21的所述正面211的电路板连接件被保持在所述第一上模具301a的所述第一避让空间4011a,以避免凸出于所述电路板21的所述正面211的电路板连接件受压而损坏。

[0299] 所述成型模具400还可以包括一覆盖膜405,其中所述覆盖膜405被重叠地设置于所述第一上模具401a的内表面和所述下模具402的内表面,从而在所述第一上模具401a和所述下模具402被执行合模操作后,所述覆盖膜405能够被保持在所述第一上模具401a和所述电路板21的所述正面211之间,和被保持在所述下模具402和所述电路板21的所述背面212之间,从而避免所述第一上模具401a和所述下模具402因与所述电路板21的表面接触而损坏所述电路板21的所述正面211和所述背面212。优选地,所述覆盖膜405具有弹性,从而在所述第一上模具401a和所述下模具402被合模时,所述覆盖膜405能够吸收所述第一上模具401a和所述下模具402因合模而产生的冲击力作用于所述电路板21,以保护所述电路板21。

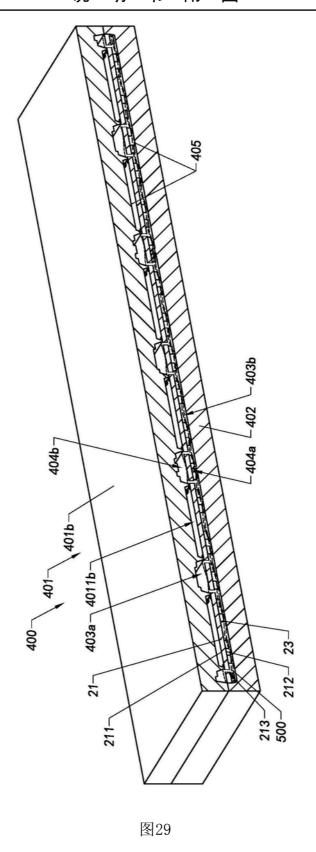

[0300] 参考附图13至图15,将一流体状的成型材料500加入到至少一个所述下部成型空间403a内,所述成型材料500会通过所述下部连通通道404a填充满所述成型模具400的全部的所述下部成型空间403a,并且在所述成型材料500在所述下部成型空间403a内固化且对所述成型模具400进行拔模操作后,形成与所述电路板21的所述背面212一体地结合的一连体包埋部270,其中所述连体包埋部270包埋凸出于所述电路板21的所述背面212的所述电子元器件23。

[0301] 参考附图16A和图16B,操作所述第二上模具401b和所述下模具402,以使所述第二上模具401b和所述下模具402被合模,从而在所述第二上模具401bb和所述拼板单元400之间形成至少一上部成型空间403b。所述拼板单元300的所述电路板21的所述正面211朝向所述上部成型空间403b。优选地,在所述拼板单元300和所述第二上模具401b之间还可以形成至少一上部连通通道404b,以供连通相邻所述上部成型空间403b。优选地,所述第二上模具401bb具有至少一第二避让空间4011b,其中在所述第二上模具401b和所述下模具402被合模且所述拼板单元300被保持在所述第二上模具401b和所述下模具402之间后,凸出于所述电路板21的所述正面211的电路板连接件被保持在所述第二上模具401b的所述第二避让空电路板21的所述正面211的电路板连接件被保持在所述第二上模具401b的所述第二避让空

间4011b,以避免凸出于所述电路板21的所述正面211的电路板连接件受压而损坏。

[0302] 所述覆盖膜405被重叠地设置于所述第二上模具401b的内表面,从而在所述第二上模具401b和所述下模具402被执行合模操作后,所述覆盖膜405能够被保持在所述第二上模具401b和所述电路板21的所述正面211之间,以避免所述第二上模具401b因与所述电路板21的表面接触而损坏所述电路板21的所述正面211。因为所述覆盖膜405具有弹性,从而在所述第二上模具401b和所述下模具402被合模时,所述覆盖膜405能够吸收所述第二上模具401b和所述下模具402因合模而产生的冲击力作用于所述电路板21,以保护所述电路板21。

[0303] 参考附图17至图19,将流体状的所述成型材料500加入到至少一个所述上部成型空间403b内,所述成型材料500会通过所述上部连通通道404b填充满所述成型模具400的全部的所述上部成型空间404,并且在所述成型材料500在所述上部成型空间403b内固化且对所述成型模具400进行拔模操作后,形成与所述电路板21的所述正面211一体地结合于一连体模制基座250,和同时形成每个所述光窗251,其中凸出于所述电路板21的所述正面211的电路板连接件位于所述光窗251内。

[0304] 值得一提的是,所述覆盖膜405能够通过产生变形的方式阻止在所述第二上模具401b和所述电路板21的所述正面211之间产生缝隙,从而在附图17和图18示出的阶段,不仅能够阻止流体状的所述成型材料500自所述上部成型空间403b或所述上部连通通道404b进入所述第二避让空间4011b,而且能够阻止流体状的所述成型材料500进入所述第二上模具401b和所述电路板21的所述正面211之间而出现"飞边"的不良现象。另外,所述覆盖膜405的提供能够便于所述第二上模具401b和所述下模具402拔模。可以理解的是,在对所述成型模具400执行拔模工艺后得到一连体电路板组件200。所述连体电路板组件200包括所述电路板21、被贴装于所述电路板21的所述电子元器件23以及一体地结合于所述电路板21的所述连体包埋部270和/或所述连体模制基座250。也就是说,所述连体电路板组件200可以只包括所述连体包埋部270和所述连体模制基座250。也就是说,所述连体电路板组件200可以只包括所述连体包埋部270和所述连体模制基座250。也就是说,所述连体电路板组件200可以只包括所述连体包埋部270和所述连体模制基座250。也的一个。

[0305] 值得一提的是,所述成型材料500可以是但不限于固体颗粒、液体、液体和固体颗粒的混合物。

[0306] 进一步参考附图20示出的阶段,在通过所述成型模具400藉由模制工艺在所述拼板单元300上模制所述连体包埋部270和所述连体模制基座250而得到所述连体电路板组件200后,可以对组成所述拼板单元300的所述电路板21、所述连体模制基座250和所述连体包埋部270进行分割,以得到所述电路板组件20的半成品,例如,可以通过切割或者蚀刻等工艺去除所述电路板21、所述连体模制基座250和所述连体包埋部270的多余的部分,以得到所述电路板组件20的半成品,其中所述连体模制基座250在被分割后形成所述模制基座25,所述连体包埋部270在被分割后形成所述包埋部27。

[0307] 在附图21示出的阶段,经由所述模制基座25的所述光窗251将所述感光芯片22贴装于所述电路板21的正面,和藉由打线工艺在所述感光芯片22的芯片连接件和所述电路板21的电路板连接件之间所述引线24,以得到所述电路板组件20,其中所述感光芯片22的感光区域对应所述模制基座25的所述光窗251。

[0308] 进一步地,所述电路板组件20包括一连接板单元28,其中所述连接板单元28进一步包括至少一连接板281和被设置于所述连接板281的自由端的至少一安装件282,其中在

附图22示出的阶段,所述连接板单元28的所述连接板281能够被贴装于所述电路板21,并使 所述电路板21和所述连接板281被导通。优选地,所述连接板单元28的所述连接板281可以 变形,从而有利于在后续将所述阵列摄像模组100组装于所述电子设备。

[0309] 值得一提的是,尽管在附图22示出的阶段,所述连接板单元28的所述连接板281被贴装于所述电路板21的所述背面212,在本发明的所述阵列摄像模组100的其他可能的示例中,所述连接板单元28的所述连接板281也可以被贴装于所述电路板21的所述正面211。可选地,所述连接板单元28的所述连接板281和所述电路板21也可以是一体式结构。

[0310] 还值得一提的是,尽管在附图2和图22示出的所述阵列摄像模组100的这个具体的示例中,所述连接板单元28的所述连接板281的连接端被贴装在所述电路板21的宽度方向,以使所述连接板281被保持在所述阵列摄像模组100的侧部,在本发明的所述阵列摄像模组100的另外一些示例中,所述连接板单元28的所述连接板281的连接端也可以被贴装于所述电路板21的长度方向,以使所述连接板281被保持在所述阵列摄像模组100的端部。本发明的所述阵列摄像模组100在这方面不受限制。

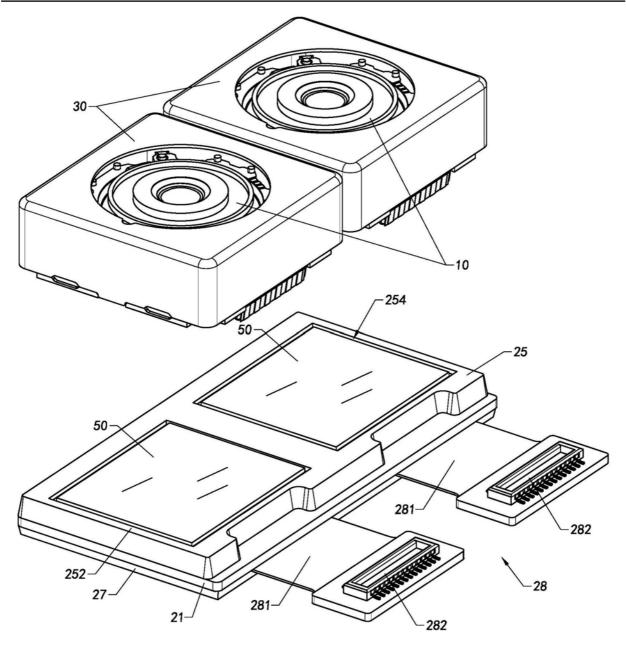

[0311] 参考附图23示出的阶段,将所述滤光元件50贴装于所述模制基座25的所述内贴装面253,以使所述滤光元件50被保持在所述感光芯片22的感光路径。和在附图24示出的阶段,将组装有所述光学镜头10的所述驱动器30贴装于所述模制基座25的所述外贴装面252,以使所述光学镜头10被保持在所述感光芯片22的感光路径,和使所述滤光元件50被保持在所述光学镜头10和所述感光芯片22之间,从而制得附图9示出的所述阵列摄像模组100。

[0312] 附图25示出了所述阵列摄像模组100的一个变形实施方式,与附图8示出的所述阵列摄像模组100不同的是,在附图25示出的所述阵列摄像模组100的具体的示例中,所述电路板21可以具有至少一成型通道213,其中所述成型通道213自所述电路板21的所述正面211延伸至所述背面214,从而在模制工艺中,可以同时形成所述模制基座25和所述包埋部27。

[0313] 具体地说,在附图26示出的阶段,提供所述拼板单元300,和在附图27示出的阶段,将所述电子元器件23贴装在所述电路板21的所述背面212。在附图28A和图28B示出的阶段,将所述拼板单元300放置于所述成型模具400的所述第二上模具401b和所述下模具402之间,以在所述第二上模具401b和所述拼板单元300之间形成所述上部成型空间403b和所述上部连通通道404b,和在所述下模具402和所述拼板单元300之间形成所述下部成型空间403a和所述下部连通通道404a,其中所述电路板21的所述正面211朝向所述第二上模具401b,并且凸出于所述电路板21的所述正面211的电路板连接件被保持在所述第二上模具401b的第二避让空间4011b,和所述电路板21的所述背面212朝向所述下模具402,并且凸出于所述电路板21的所述背面212前的所述下部成型空间403a。所述覆盖膜405被保持在所述第二上模具401b和所述电路板21的所述正面211之间,和被保持在所述下模具402和所述电路板21的所述正面212之间。

[0314] 在附图29至图32示出的阶段,将流体状的所述成型材料500加入到所述上部成型空间403a或所述下部成型空间403b之后,所述成型材料500会经由所述上部连通通道404b、所述下部连通通道404a和所述电路板21的所述成型通道213填充满所有的所述上部成型空间403b和所述下部成型空间403a,并且在所述成型材料500在所述上部成型空间403b、所述下部成型空间403a和所述电路板21的所述成型通道213内固化且对所述成型模具400进行

拔模操作后,形成与所述电路板21的所述背面212一体地结合的所述连体包埋部270,和形成与所述电路板21的所述正面211一体地结合的所述连体模制基座250,其中所述连体包埋部270包埋凸出于所述电路板21的所述背面212的所述电子元器件23,其中所述连体模制基座250形成所述光窗251。

[0315] 参考附图33示出的阶段,在通过所述成型模具400藉由模制工艺在所述拼板单元300上模制所述连体包埋部270和所述连体模制基座250而得到所述连体电路板组件200后,可以对组成所述拼板单元300的所述电路板21、所述连体模制基座250和所述连体包埋部270进行分割,以得到所述电路板组件20的半成品,例如,可以通过切割或者蚀刻等工艺去除所述电路板21、所述连体模制基座250和所述连体包埋部270的多余的部分,以得到所述电路板组件20的半成品,其中所述连体模制基座250在被切割后形成所述模制基座25,所述连体包埋部270在被切割后形成所述包埋部27。

[0316] 在附图34示出的阶段,经由所述模制基座25的所述光窗251将所述感光芯片22贴装于所述电路板21的正面,和藉由打线工艺在所述感光芯片22的芯片连接件和所述电路板21的电路板连接件之间所述引线24,以得到所述电路板组件20,其中所述感光芯片22的感光区域对应所述模制基座25的所述光窗251。

[0317] 在附图35示出的阶段,所述连接板单元28的所述连接板281能够被贴装于所述电路板21,并使所述电路板21和所述连接板281被导通。

[0318] 参考附图36示出的阶段,将所述滤光元件50贴装于所述模制基座25的所述内贴装面253,以使所述滤光元件50被保持在所述感光芯片22的感光路径。和在附图37示出的阶段,将组装有所述光学镜头10的所述驱动器30贴装于所述模制基座25的所述外贴装面252,以使所述光学镜头10被保持在所述感光芯片22的感光路径,和使所述滤光元件50被保持在所述光学镜头10和所述感光芯片22之间,从而制得附图25示出的所述阵列摄像模组100。

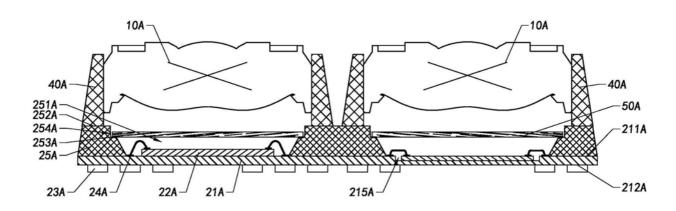

[0319] 与附图4示出的所述阵列摄像模组100不同的是,在附图38示出的所述阵列摄像模组100的这个具体的示例中,所述阵列摄像模组100被实施为定焦摄像模组,具体地说,所述阵列摄像模组100包括至少两镜筒40,其中每个所述光学镜头10分别被组装于每个所述镜筒40,每个所述镜筒40分别被贴装于所述模制基座25的所述外贴装面252的不同位置,并且藉由每个所述镜筒40将每个所述光学镜头10分别保持在每个所述感光芯片22的感光路径。

[0320] 在附图39示出的这个示例中,所述阵列摄像模组100的每个所述镜筒40也可以一体地延伸于所述模制基座25。也就是说,每个所述镜筒40和所述模制基座25能够在同一道模制工艺中一体地结合于所述电路板21的所述正面211。

[0321] 在附图40示出的这个示例中,所述阵列摄像模组100的每个所述光学镜头10也可以直接被贴装于所述模制基座25,从而使得每个所述光学镜头10分别被对应于每个所述感光芯片22。换言之,在附图40示出的所述阵列摄像模组100的这个具体的示例中,每个所述光学镜头10能够以分别被贴装于所述模制基座25的所述外贴装面252的不同位置的方式被保持在每个所述感光芯片22的感光路径。

[0322] 在附图41示出的这个示例中,所述阵列摄像模组100的每个所述光学镜头10可以被直接地贴装于所述模制基座25,然后在每个所述光学镜头10的外部设置所述镜筒40,以藉由所述镜筒40保护所述光学镜头。例如,每个所述光学镜头10能够分别以被贴装于所述模制基座25的所述外贴装面252的不同位置的方式被设置于每个所述光学镜头10的外部,

以使得每个所述镜筒40分别以环绕在每个所述光学镜头10的四周的方式保护每个所述光学镜头10。优选地,所述镜筒40和所述光学镜头10可以接触,也可以不接触。

[0323] 在附图42示出的这个示例中,所述阵列摄像模组100的所述镜筒40可以是一体地延伸于所述模制基座25,同时每个所述光学镜头10可以被直接地贴装于所述模制基座25的所述外贴装面252的不同位置,以藉由所述镜筒40以环绕在所述光学镜头10的外部的方式保护所述光学镜头10。

[0324] 在附图43示出的这个示例中,所述阵列摄像模组100可以同时提供所述驱动器30和所述镜筒40,例如所述驱动器30和所述镜筒40相互邻近地被贴装于所述模制基座25的所述外贴装面252的不同位置,其中一个所述光学镜头10被可驱动地设置于所述驱动器30,另一个所述光学镜头10被设置于所述镜筒40,以藉由所述驱动器30和所述镜筒40分别将每个所述光学镜头10保持在每个所述感光芯片22的感光路径。。

[0325] 在附图44示出的这个示例中,与附图43示出的所述阵列摄像模组100不同的是,所述阵列摄像模组100的所述镜筒40也可以一体地延伸于所述模制基座25。换言之,在所述阵列摄像模组100的这个具体的示例中,所述镜筒40可以一体地延伸于所述模制基座25,和所述驱动器30被贴装于所述模制基座25,从而藉由所述驱动器30和所述镜筒40分别将每个所述光学镜头10保持在每个所述感光芯片22的感光路径。

[0326] 在附图45示出的这个示例中,所述阵列摄像模组100也可以没有所述镜筒40,从而一个所述光学镜头10被可驱动地设置于所述驱动器30,和所述驱动器30以被贴装于所述模制基座45的方式被保持在所述感光芯片22的感光路径,另一个所述光学镜头10以被直接贴装于所述模制基座25的方式被保持在所述感光芯片22的感光路径。

[0327] 在附图46示出的这个示例中,所述光学镜头10被直接贴装于所述模制基座25,所述镜筒40被贴装于所述模制基座25,并且所述镜筒40位于所述光学镜头10的外侧,以用于保护所述光学镜头10。

[0328] 在附图47示出的这个示例中,所述光学镜头10被直接贴装于所述模制基座25,所述镜筒40一体地延伸于所述模制基座25,所述镜筒40位于所述光学镜头10的外侧,以用于保护所述光学镜头10。

[0329] 在附图48示出的这个示例中,所述电路板21的数量可以超过一个,例如所述电路板21的数量可以和所述感光芯片22的数量一致,例如在这个示例中,所述电路板21的数量可以被实施为两个,所述模制基座25可以和两个所述电路板21同时结合在一起。值得一提的是,所述模制基座25能够一体地结合于两个所述电路板21,通过这样的方式,所述模制基座25能够保证两个所述电路板21的平整度,进而保证分别被贴装于每个所述电路板21的两个所述感光芯片22的的同轴度。

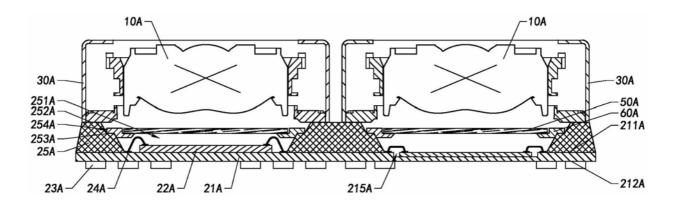

[0330] 在附图49示出的这个示例中,所述阵列摄像模组100还可以包括至少一框型的支架60,例如所述支架60的数量可以和所述滤光元件50的数量一致,其中每个所述滤光元件50分别被贴装于每个所述支架60,每个所述支架60分别被贴装于所述模制基座25,以藉由每个所述支架60使每个所述滤光元件50分别被保持在每个所述感光芯片22的感光路径。

[0331] 值得一提的是,通过所述支架60将所述滤光元件50保持在所述感光芯片22的感光路径的方式能够减小所述滤光元件50的长宽尺寸,以降低所述阵列摄像模组100的成本。

[0332] 在附图50示出的这个示例中,所述滤光元件50的数量可以被实施为一个,其中所

述滤光元件50被贴装于所述模制基座25,以使得每个所述光学镜头10分别对应于所述滤光元件50的不同位置。

[0333] 在附图51示出的这个示例中,所述支架60的数量也可以被实施为一个,其中多个所述滤光元件50均能够被贴装于所述支架60,所述支架60被贴装于所述模制基座25,以使得每个所述光学镜头10和每个所述感光芯片22分别对应于所述滤光元件50的不同位置。

[0334] 在附图52示出的这个示例中,所述电路板21具有一个所述容纳空间215,其中一个所述感光芯片22被容纳于所述容纳空间215,另一个所述感光芯片22被可以被贴装于所述电路板21的表面,从而使得两个所述感光芯片22具有高度差。换言之,两个所述感光芯片22的感光面可以没有处于同一个水平面,通过这样的方式,有利于改善所述阵列摄像模组100的成像品质和扩充所述阵列摄像模组100的功能。

[0335] 在附图53示出的这个示例中,所述电路板21具有两个所述容纳空间215,每个所述容纳空间215均被实施为凹槽,从而,两个所述感光芯片22均可以被容纳于所述容纳空间215,以减低所述阵列摄像模组100的高度,从而有利于所述阵列摄像模组100被应用于更轻薄的所述电子设备。在附图53中,所述模制基座25可以仅成型于所述电路板21的所述正面211的一部分,而在附图54的这个示例中,所述模制基座25可以进一步地包埋所述感光芯片22的非感光区域的至少一部分,以使所述电路板21、所述感光芯片22、所述引线24和所述模制基座25一体地结合。

[0336] 值得一提的是,在制造附图54示出的所述阵列摄像模组100的这个具体的示例中,在所述拼板单元300的所述电路板21的所述背面212贴装所述电子元器件23,和在所述电路板21的所述正面211贴装所述感光芯片22,并通过打线工艺以在所述感光芯片22的芯片连接件和所述电路板21的电路板连接件之间形成所述引线24的方式导通地连接所述感光芯片22和所述电路板21。值得一提的是,贴装所述感光芯片22和所述电子元器件23的先后顺序在本发明的所述阵列摄像模组100中不受限制。接着,通过模制工艺使所述模制基座25一体地结合于所述电路板21和所述感光芯片22的非感光区域,此时,所述模制基座25能够包埋所述引线24。值得一提的是,在通过模制工艺在所述电路板21和所述感光芯片22的非感光区域形成所述模制基座25的过程中,所述成型模具400的所述覆盖膜405能够避免出现"飞边"的不良现象和避免所述上模具401刮伤所述感光芯片22,以提高所述阵列摄像模组100的产品良率。

[0337] 在附图55示出的这个示例中,所述阵列摄像模组100的所述模制基座25可仅包埋一部分所述感光芯片22的非感光区域,参考附图55,所述模制基座25可以仅包埋附图左侧的所述感光芯片22的非感光区域,而没有包埋附图右侧的所述感光芯片22的非感光区域。

[0338] 在附图56示出的这个示例中,所述电路板21可以具有两个被实施为通孔的所述容纳空间215,其中所述电路板21的所述背面212在被贴装至少一个所述电子元器件23之后,形成一体地结合于所述电路板21的所述版背面212的所述包埋部27,所述包埋部27可以包埋至少一个所述电子元器件23的至少一部分。所述感光芯片22可以通过所述电路板21的所述容纳空间215贴装在所述包埋部27上,然后通过所述引线24使所述电路板21和所述感光芯片22被导通。所述模制基座25可以仅成型于所述电路板21的所述正面211的一部分,而在附图57的这个示例中,所述模制基座25还可以进一步地包埋所述感光芯片22的非感光区域的至少一部分,以使所述电路板21、所述感光芯片22、所述引线24和所述模制基座25一体地

结合。

[0339] 在附图58示出的这个示例中,所述模制基座25可以进一步包埋所述感光芯片22的非感光区域的至少一部分,以使所述模制基座25、所述电路板21和所述感光芯片22一体地结合,通过这样的方式,有利于进一步减小所述阵列摄像模组100的长宽尺寸。

[0340] 在附图59示出的这个示例中,所述滤光元件50重叠地设置于所述感光芯片22,所述模制基座25包埋所述滤光元件50的外边沿,以使所述模制基座25、所述电路板21、所述感光芯片22和所述滤光元件50一体地结合。

[0341] 在附图60示出的这个示例中,所述电路板21的所述正面211设有一个框形的支承元件29或者形成所述支承元件29,所述模制基座25包埋所述支承元件29的至少一部分。

[0342] 在附图61示出的这个示例中,所述感光芯片22的非感光区域的至少一部分设有所述支承元件29或者形成所述支承元件29,所述模制基座25包埋所述支承元件29的至少一部分。

[0343] 在附图62示出的这个示例中,所述滤光元件50的外边沿设有所述支承元件29或者 形成所述支承元件29,所述模制基座25包埋所述支承元件29的至少一部分。

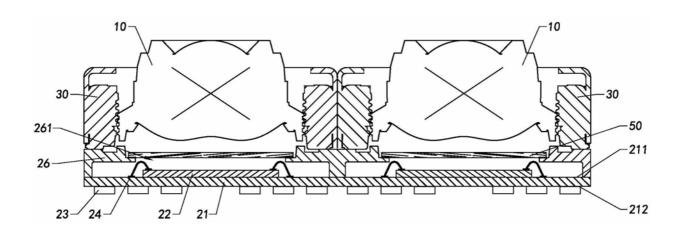

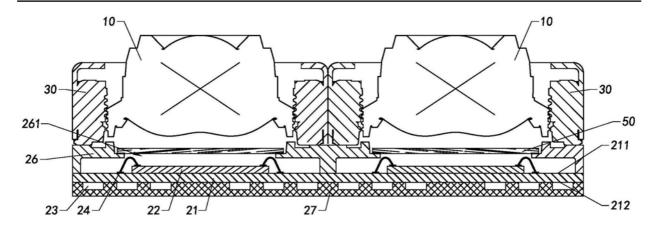

[0344] 在附图63示出的这个示例中,所有的所述感光芯片22均可以被以倒装的工艺和所述电路板21导通。

[0345] 在附图64A示出的这个示例中,所述阵列摄像模组100也可以没有模制形成所述模制基座25,而是提供至少一个所述镜架26。具体地说,所述镜架26具有至少两通光孔261,其中每个所述滤光元件50分别被贴装于所述镜架26,并且所述镜架26的每个所述通光孔261分别对应于每个所述滤光元件50。所述镜架26被贴装于所述电路板21的所述正面211,并使每个所述感光芯片22的感光区域分别对应于所述镜架26的每个所述通光孔261,从而每个所述滤光元件50分别被保持在每个所述感光芯片22的感光路径。每个所述驱动器30分别被贴装于所述镜架26,并且每个所述驱动器30分别被组装于每个所述驱动器30的每个所述光学镜头10保持在每个所述感光芯片22的感光路径,此时,每个所述滤光元件50分别被保持在每个所述光学镜头10和每个所述感光芯片22之间。

[0346] 与附图64A示出的所述阵列摄像模组100不同的是,在附图64B示出的所述阵列摄像模组100的这个变形实施方式中,所述阵列摄像模组100的所述电路板组件20进一步包括至少一个所述包埋部27,其中所述包埋部27一体地结合于所述电路板21的所述背面212的至少一部分。优选地,所述包埋部27包埋凸出于所述电路板21的所述背面212的至少一个所述电子元器件23的至少一部分。更优选地,所述包埋部7包埋凸出于所述电路板21的所述背面212的全部的所述电子元器件23。

[0347] 在附图65示出的这个示例中,一部分所述电子元器件23可以被贴装于所述电路板21的所述背面212,且被贴装于所述电路板21的所述背面212的所述电子元器件23裸露,另一部分所述电子元器件23可以被贴装于所述电路板21的所述正面211。

[0348] 在附图66示出的这个示例中,所述电路板组件20可以形成一体地结合于所述电路板21的所述背面212的所述包埋部27,其中所述包埋部27包埋至少一个所述电子元器件23。优选地,所述包埋部27包埋所有的所述电子元器件23b。

[0349] 在附图67示出的这个示例中,所述电路板21具有被实施通孔的至少一成型空间213,以连通于所述电路板21的所述正面211和所述背面212,其中成型材料在穿过所述成型

空间213且在固结后,在所述电路板21的所述正面211形成所述模制基座25和在所述电路板21的所述背面212形成所述包埋部27,其中所述模制基座25和所述包埋部27可以一体地结合。本领域技术人员应理解,上述描述及附图中所示的本发明的实施例只作为举例而并不限制本发明。

[0350] 在附图68示出的这个示例中,所述电路板21可以具有至少一个被实施为通孔的所述容纳空间215,为了便于说明,在附图68示出的这个具体示例中,所述电路板21具有两个被实施为通孔的所述容纳空间215,从而在模制工艺中,所述感光芯片22可以被保持在所述电路板21的所述容纳空间215内,所述成型模具300的下模具在所述感光芯片22的下表面顶住所述感光芯片22,所述成型模具300的上模具在所述感光芯片22的上表面顶住所述感光芯片22,从而藉由所述成型模具300的上模具和所述下模具夹持住所述感光芯片22,然后通过向所述成型模具300中加入成型材料的方式形成所述包埋部27和所述模制基座25中的至少一个。

[0351] 在附图69示出的这个示例中,所述感光芯片22的上表面也可以低于所述电路板21的所述正面211,例如所述感光芯片22的上表面可以和所述电路板21的所述背面212平齐,甚至所述感光芯片22的上表面可以低于所述电路板21的所述背面212,也就是说,所述感光芯片22相对于所述电路板21的高度可以被方便地调节。当然,在另外的一些实施例中,所述包埋部27也可以进一步包埋所述感光芯片22的下表面,如图70。

[0352] 进一步参考附图70,所述阵列摄像模组100的所述包埋部27具有至少一缺口271,从而在后续将所述阵列摄像模组100组装于一个所述电子设备本体200以形成所述电子设备时,所述电子设备的元器件(例如电阻、电容等)能够被容纳于所述包埋部27的所述缺口271,从而在所述电子设备的长宽方向能过使所述电子设备的元器件与所述阵列摄像模组100的所述包埋部27相互重叠,从而有利于所述电子设备朝向轻薄化的方向发展。

[0353] 优选地,在附图70示出的所述阵列摄像模组100的这个具体的示例中,所述包埋部27的所述缺口271对应于所述感光芯片22,其中所述包埋部27的所述缺口271可以在所述包埋部27成型的过程中形成。更优选地,所述阵列摄像模组100的所述包埋部27的所述缺口271形成于所述包埋部27的中部,从而所述包埋部27环绕在所述缺口271的四周。换言之,从所述阵列摄像模组100的俯视视角来看,所述包埋部27的形状可以呈但不限于"口"字形、"田"字形、"日"字形等。

[0354] 在附图71示出的这个示例中,所述阵列摄像模组100的所述包埋部27的所述缺口271形成于所述包埋部27的侧部。也就是说,所述包埋部27在成型的过程中可以仅结合于所述电路板21的所述背面212的一侧或者一端,从而在所述电路板21的所述背面212的另一侧或者另一端形成所述缺口271。

[0355] 本领域技术人员应当理解的是,因为所述包埋部27是通过模制工艺藉由所述成型材料500一体地结合于所述电路板21的所述背面212而形成的,因此,所述包埋部27结合的所述电路板21的所述背面212的位置和尺寸的灵活度比较高,例如,在本发明的所述附图71示出的所述阵列摄像模组100的这个具体的示例中,所述电路板21的所述背面212被所述包埋部27结合的面积与所述电路板21的所述背面212的总面积的面积比的比值可以是1:2,或者面积比的比值可以是2:3,或者面积比的比值的范围为大于等于1:2且小于等于2:3。尽管如此,本领域技术人员应当理解的是,上述揭露的所述电路板21的所述背面212被所述包埋

部27的结合的面积与所述电路板21的所述背面212的总面积的面积比的比值范围为大于等于1:2且小于等于2:3仅为示例,其并不应被视为对本发明的所述阵列摄像模组100的内容和范围的限制。换言之,所述电路板21的所述背面212被所述包埋部27结合的面积在本发明的所述阵列摄像模组100中不受限制,只要所述包埋部27能够包埋所述电子元器件23即可。[0356] 在附图72示出的这个示例中,所述阵列摄像模组100的所述电路板21具有至少一个被实施为通孔的所述容纳空间215,其中通过模制工艺在所述电路板21的所述背面212可以形成一体地结合于所述电路板21的所述背面212的至少一部分的所述包埋部27。优选地,在附图72示出的所述阵列摄像模组100的这个具体的示例中,所述包埋部27进一步包埋凸出于所述电路板21的所述背面212的所述电子元器件23。在所述包埋部27结合于所述电路板21的所述背面212之后,所述电路板21的所述容纳空间215对应于所述包埋部27。换言之,所述包埋部27的一部分裸露在所述电路板21的所述容纳空间215对应于所述包埋部27。换言之,所述包埋部27的一部分裸露在所述电路板21的所述容纳空间215。

[0357] 一个所述感光芯片22被贴装于所述电路板21的所述正面211,另一个所述感光芯片22经由所述电路板21的所述容纳空间215被贴装于所述包埋部27,然后通过打线工艺在每个所述感光芯片22的芯片连接件和所述电路板21的电路板连接件之间形成所述引线24,以藉由所述引线24导通地连接每个所述感光芯片22和所述电路板21。

[0358] 在附图72示出的所述阵列摄像模组100的这个具体的示例中,所述镜座26被贴装于所述电路板21的所述正面211,并且每个所述感光芯片22的感光区域分别对应于所述镜座26的每个所述通光孔261,以使所述镜座26环绕在每个所述感光芯片22的四周,此时,被贴装于所述镜座26的每个所述滤光元件50分别被保持在每个所述感光芯片22的感光路径。每个所述驱动器30分别被贴装于所述镜座26,以藉由每个所述驱动器30分别将被可驱动地设置于每个所述驱动器30的每个所述光学镜头10分别保持在每个所述感光芯片22的感光路径,并且每个所述滤光元件50分别被保持在每个所述感光芯片22和每个所述光学镜头10之间。

[0359] 与附图72示出的所述阵列摄像模组100不同的是,在附图73示出的所述阵列摄像模组100的这个具体的示例中,所述阵列摄像模组100的所述镜座26的所述通光孔261的数量少于所述感光芯片22的数量,参考附图73示出的这个具体的示例,所述镜座26被贴装于所述电路板21的一个端部,从而使被贴装于所述包埋部27的所述感光芯片22的感光区域对应于所述镜座26的所述通光孔261,并且被贴装于所述镜座26的所述滤光元件50被保持在所述感光芯片22的感光路径,所述驱动器30被贴装于所述镜座26,以藉由所述驱动器30将被可驱动地设置于所述驱动器30的所述光学镜头10保持在所述感光芯片22的感光路径,并且所述滤光元件50被保持在所述光学镜头10和所述感光芯片22之间。另外,所述阵列摄像模组100进一步包括一个所述镜筒40,其中所述镜筒40被贴装于所述电路板21的另一个端部,以藉由所述镜筒40将被设置于所述镜筒40的所述光学镜头10保持在所述感光芯片22的感光路径。

[0360] 与附图73示出的所述阵列摄像模组100不同的是,在附图74示出的所述阵列摄像模组100的这个具体的示例中,在所述电路板21的所述正面211形成一体地结合于所述电路板21的所述模制基座25,并且所述模制基座25环绕在被贴装于所述电路板21的所述正面211的所述感光芯片22的感光区域的四周,以使被贴装于所述电路板21的所述正面211的所述感光芯片22的感光区域对应于所述模制基座25的所述光窗251。所述滤光元件50被贴装

于所述模制基座25,并使所述滤光元件50被保持在所述感光芯片22的感光路径。所述镜筒40被贴装于所述模制基座25,以藉由所述镜筒40将被设置于所述镜筒40的所述光学镜头10保持在所述感光芯片22的感光路径。

[0361] 与附图74示出的所述阵列摄像模组100不同的是,在附图75示出的所述阵列摄像模组100的这个具体的示例中,所述模制基座25进一步包埋所述感光芯片22的非感光区域的至少一部分,以进一步减小所述阵列摄像模组100的长宽尺寸。

[0362] 依本发明的另一个方面,本发明进一步提供一阵列摄像模组的制造方法,其中所述制造方法包括如下步骤:

[0363] (a) 以至少一个电子元器件23的自由侧朝向一电路板21的背面212所在的侧部的方式导通地连接所述电子元器件23于所述电路板21;

[0364] (b) 以每个感光芯片22的感光区域朝向所述电路板21的正面211所在的侧部的方式导通地连接每个所述感光芯片22于所述电路板21;以及

[0365] (c) 分别保持每个光学镜头10于每个所述感光芯片22的感光路径,以制得所述阵列摄像模组100。

[0366] 所述制造方法进一步包括步骤:一体地结合至少一包埋部27于所述电路板21的背面212。值得一提的是,在本发明的所述制造方法的一个示例中,一体地结合于所述包埋部27于所述电路板21的所述背面212的步骤可以在所述步骤(a)之后和在所述步骤(b)之前,从而在所述步骤(a)中,在所述电路板21的所述背面212导通所述电子元器件23后,一体地结合于所述包埋部27于所述电路板21的所述背面212,然后在所述步骤(b)中,在所述电路板21的所述正面211导通地连接每个所述感光芯片22。而在本发明的所述制造方法的另一个示例中,一体地结合于所述包埋部27于所述电路板21的所述背面212的步骤也可以在所述步骤(b)之后,从而在所述电路板21的所述正面212导通地连接每个所述感光芯片22之后,再一体地结合于所述包埋部27于所述电路板21的所述背面212。

[0367] 参考本发明的说明书附图之附图87至图89,依本发明的一较佳实施例的一阵列摄像模组100A在接下来的描述中被阐述,其中在附图89中示出的所述阵列摄像模组100A的一个使用状态,例如,在附图89示出的示例中,一个所述阵列摄像模组100A能够被应用于被具体实施为智能手机的一电子设备本体200A,以使所述阵列摄像模组100A能够和所述电子设备本体200A相互结合而形成一电子设备。

[0368] 值得一提的是,尽管在附图89示出的示例中,所述阵列摄像模组100A的数量为一个,且所述阵列摄像模组100A被设置于所述电子设备本体200A的后部,在其他的示例中,所述阵列摄像模组100A的数量不限于一个,并且所述阵列摄像模组100A的位置也不限于被设置于所述电子设备本体200A的后部,例如所述阵列摄像模组100A可以被设置于所述电子设备本体200A的前部,当然,所述阵列摄像模组100A被设置在所述电子设备本体200A的其他位置也是可能的。

[0369] 另外,所述电子设备本体200A尽管在附图89中被实施为智能手机,在本发明的其他示例中,所述电子设备本体200A也可以被实施为平板电脑、笔记本电脑、相机、个人数字助理、电纸书、MP3/4/5等任何能够被配置所述阵列摄像模组100A的电子设备。当然,本领域的技术人员应当理解,在冰箱、洗衣机、电视机等传统的家电上配置所述阵列摄像模组100A也是可能的,或者在防盗门、墙壁等建筑上配置所述阵列摄像模组100A也是可能的,因此,

所述阵列摄像模组100A的应用环境和使用方式并不应被视为对本发明的所述阵列摄像模组的内容和范围的限制。

[0370] 值得一提的是,在附图89示出的所述阵列摄像模组100A的这个具体的应用中,所述电子设备本体200A被实施为智能手机,所述阵列摄像模组100A被设置在所述电子设备本体200A的后部以形成所述智能手机的一个后置摄像模组。本领域技术人员应当理解的是,在其他的可能示例中,所述阵列摄像模组100A还可以被设置在所述电子设备本体200A的前部以形成所述智能手机的一个前置摄像模组。

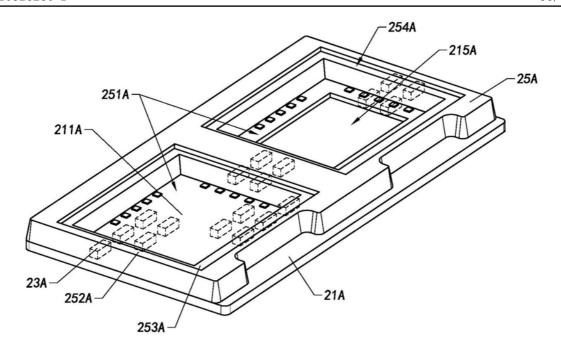

[0371] 参考附图87至图89,所述阵列摄像模组100A包括至少两光学镜头10A和一电路板组件20A,其中所述电路板组件20A包括至少一电路板21A、至少一感光芯片22A以及至少一电子元器件23A,其中每个所述感光芯片22A分别和所述电路板21A被导通地连接,并且至少一个所述感光芯片22A的感光面和另外的所述感光芯片22A的感光面具有高度差,每个所述电子元器件23A均被贴装于所述电路板21A,每个所述光学镜头10A分别被保持在每个所述感光芯片22A的感光路径。被物体反射的光线能够分别自每个所述光学镜头10A进入所述阵列摄像模组100A的内部,以在后续分别被每个所述感光芯片22A接收和成像,从而获得与所述物体相关联的图像。值得一提的是,在本发明的所述阵列摄像模组100A中所涉及的所述感光芯片22A的感光面是指所述感光芯片22A的朝向所述光学镜头10A的侧面。

[0372] 例如,在附图87和图88示出的所述阵列摄像模组100A的这个具体的示例中,所述阵列摄像模组100A包括两个所述光学镜头10A和一个所述电路板组件20A,其中所述电路板组件20A包括一个所述电路板21A、两个所述感光芯片22A以及多个所述电子元器件23A,其中两个所述感光芯片22A相互间隔地被贴装于所述电路板21A的一侧,并且两个所述感光芯片22A的感光面具有高度差,每个所述电子元器件23A分别被相互间隔地贴装于所述电路板21A的另外一侧,每个所述光学镜头10A分别被保持在每个所述感光芯片22A的感光路径。被物体反射的光线能够分别自每个所述光学镜头10A进入所述阵列摄像模组100A的内部,然后被分别被对应位置的每个所述感光芯片22A接收和成像,从而获得与所述物体相关联的图像。

[0373] 在本发明的所述阵列摄像模组100A中,通过使至少一个所述感光芯片22A的感光面和另外的所述感光芯片22A的感光面之间具有高度差的方式,能够提高所述阵列摄像模组100A的成像能力,和增加所述阵列摄像模组100A的功能。例如,在附图87和图88示出的所述阵列摄像模组100A的这个具体的示例中,所述阵列摄像模组100A的两个所述感光芯片22A可以分别获得不同焦距的图像。也就是说,通过将两个所述感光芯片22A的感光面设置为具有高度差的方式,能够使藉由所述光学镜头10A和所述感光芯片22A形成的两个光学系统具有不同的焦距,从而获得不同焦距的图像,这种方式有利于极大地提高所述阵列摄像模组100A的成像能力。在本发明的所述阵列摄像模组100A的另外一些示例中,所述阵列摄像模组100A的一个所述感光芯片22A能够被用于获取与所述物体相关的图像,而另一个所述感光芯片22A能够记录与所述物体相关的景深,从而在后续所述电子设备的其他机构能够将一个所述感光芯片22A获取的与所述物体相关的图像和另一个所述感光芯片22A获取的与所述物体相关的图像和另一个所述感光芯片22A获取的与所述物体相关的图像和另一个所述感光芯片22A获取的与所述物体相关的图像和另一个所述感光芯片22A获取的与所述物体相关的图像和另一个所述感光芯片22A获取的与所述物体相关的图像和另一个所述感光芯片20A获取的与所述物体相关的图像和另一个所述感光芯片20A获取的与所述物体相关的图像和另一个所述感光芯片20A获取的与所述物体相关的图像和另一个所述感光芯片20A获取的与所述物体相关的图像和另一个所述感光芯片20A获取的成像能力。

[0374] 另外,在本发明们的所述阵列摄像模组100A的其他示例中,至少一个所述感光芯

片22A的感光区域的面积与其他的所述感光芯片22A的感光区域的面积不同。例如,在附图87和图88示出的所述阵列摄像模组100A的这个具体的示例中,两个所述感光芯片22A具有不同面积的感光区域。

进一步参考附图87和图88,所述电路板21A具有一正面211A和对应于所述正面 [0375] 211A的一背面212A以及具有至少一容纳空间215A,其中所述电路板21A的所述正面211A和 所述背面212A相互对应以界定所述电路板21A的厚度,其中所述容纳空间215A自所述电路 板21A的所述正面211A向所述背面212A方向延伸。每个所述感光芯片22A可以以被贴装于所 述电路板21A的所述正面211A的方式和所述电路板21A结合在一起,并且一个所述感光芯片 22A能够被容纳于所述电路板21A的所述容纳空间215A,从而使得两个所述感光芯片22A的 感光面具有高度差。例如,在附图87示出的所述阵列摄像模组100A的这个具体的示例中,尽 管两个所述感光芯片22A均被贴装于所述电路板21A的所述正面211A,但位于附图右侧的所 述感光芯片22A被保持在所述电路板21A的所述容纳空间215A,通过这样的方式,使得位于 附图左侧所述感光芯片22A的感光面高于位于附图右侧的所述感光芯片22A的感光面,从而 使得两个所述感光芯片22A的感光面具有高度差。相应地,每个所述电子元器件23A可以以 被贴装于所述电路板21A的所述背面212A的方式和所述电路板21A结合在一起。换言之,每 个所述电子元器件23A在所述电路板21A的所述背面212A和所述电路板21A相导通。也就是 说,在附图87示出的所述阵列摄像模组100A的这个具体的示例中,每个所述电子元器件23A 均位于所述电路板21A的所述背面212A。

[0376] 值得一提的是,在本发明的所述阵列摄像模组100A的其他可能的示例中,至少一个所述电子元器件23A也可以在所述电路板21A的所述正面211A被导通地连接于所述电路板21A。也就是说,在所述阵列摄像模组100A的这个具体的示例中,至少一个所述电子元器件23A可以在所述电路板21A的所述正面211A被导通地连接于所述电路板21A,另外的所述电子元器件23A可以在所述电路板21A的所述背面212A被导通地连接于所述电路板21A。

[0377] 还值得一提的是,尽管在附图87和图88中示出了所述电子元器件23A以所述电子元器件23A被贴装于所述电路板21A的所述背面212A的方式被导通地连接于所述电路板21A,在本发明的所述阵列摄像模组100A的其他可能的示例中,所述电子元器件23A也可以以所述电子元器件23A的至少一部分被埋入所述电路板21A的方式被导通地连接于所述电路板21A。

[0378] 值得一提的是,在本发明的所述阵列摄像模组100A的一个示例中,所述电子元器件23A可以被实施为电阻、电容、继电器、处理器等被动电子元器件。换言之,所述电子元器件23A的类型在本发明的所述阵列摄像模组100A中不受限制。

[0379] 进一步地,所述电路板组件20A包括至少一组引线24A,其中每个所述引线24A的两个端部分别连接于所述电路板21A和所述感光芯片22A,以藉由每个所述引线24A导通所述感光芯片22A和所述电路板21A。

[0380] 例如,在一个示例中,可以先将所述感光芯片22A贴装于所述电路板21A的所述正面211A,然后再通过诸如打线等工艺在所述感光芯片22A和所述电路板21A之间设置每个所述引线24A,以藉由每个所述引线24A导通所述电路板21A和所述感光芯片22A。可以理解的是,所述感光芯片22A的平整度受限于所述电路板21A的平整度。当然,在另外的一些示例中,也可以不需要将所述感光芯片22A和所述电路板21A直接贴装在一起,从而使所述感光

芯片22A的平整度可以不受所述电路板21A的平整度的影响,或者即便是将所述感光芯片22A贴装于所述电路板21A,所述感光芯片22A的平整度也可以不受所述电路板21A的平整度的影响,通过这样的方式,能够使所述电路板21A选择厚度更薄的板材制得,在后续的揭露中,本发明会对如何使所述感光芯片22A的平整度不受所述电路板21A的平整度的限制的方式进行阐述。

[0381] 所述引线24A的打线方向在本发明的所述阵列摄像模组100A中不受限制,例如所述引线24A的打线方向可以从所述感光芯片22A至所述电路板21A,也可以从所述电路板21A至所述感光芯片22A,当然,所述引线24A还可以有其他的方式被用于导通所述感光芯片22A和所述电路板21A,本发明的所述阵列摄像模组100A在这方面不受限制。可以理解的是,所述引线24A的材料在本发明的所述阵列摄像模组100A中也不受限制,例如所述引线24A可以是但不限于金线、银线、铜线等。

[0382] 当然,可以理解的是,在所述阵列摄像模组100A的一些示例中,所述感光芯片22A可以预设芯片连接件,所述电路板21A可以预设电路板连接件,所述引线24A的两个端部可以分别和所述感光芯片22A的芯片连接件与所述电路板21A的电路板连接件相互接触,而藉由所述引线24A导通所述感光芯片22A和所述电路板21A,例如所述引线24A的两个端部可以分别被焊接在所述感光芯片22A的芯片连接件和所述电路板21A的电路板连接件,从而藉由所述引线24A导通所述感光芯片22A的芯片连接件和所述电路板21A。值得一提的是,所述感光芯片22A的芯片连接件和所述电路板21A的电路板连接件的形状和尺寸可以不受限制,例如所述感光芯片22A的芯片连接件和所述电路板21A的电路板连接件可以分别被实施为但不限于盘状、球状等。

[0383] 参考附图87和图88,在本发明的所述阵列摄像模组100A的这个实施例中,每个所述电子元器件23A分别被相互间隔地贴装于所述电路板21A的所述背面212A,也就是说,每个所述电子元器件23A可以不需要被布置在所述感光芯片22A的周向方向,这样,有利于减少所述电路板组件20A的长度尺寸和宽度尺寸中的至少一个尺寸,从而减少所述阵列摄像模组100A的长度尺寸和宽度尺寸中的至少一个尺寸,以使得所述阵列摄像模组100A能够被应用于追求轻薄化的所述电子设备。优选地,将每个所述电子元器件23A分别被相互间隔地贴装于所述电路板21A的所述背面212A的方式,能够同时减小所述电路板组件20A的长度尺寸和宽度尺寸,进而同时减小所述阵列摄像模组100A的长度尺寸和宽度尺寸,以在将所述阵列摄像模组100A装配于所述电子设备本体200A时而形成所述电子设备时,所述阵列摄像模组100A能够占用所述电子设备本体200A时而形成所述电子设备时,所述阵列摄像模组100A能够占用所述电子设备本体200A的内部的更少的空间,从而不仅有利于所述电子设备的轻薄化,而且还有利于所述电子设备被配置更多的智能部件,以使所述电子设备朝向智能化的方向发展。

[0384] 所述电路板组件20A进一步包括一模制基座25A,其中所述模制基座25A可以一体地形成于所述电路板21A的所述正面211A,其中所述模制基座25A具有至少一光窗251A,所述感光芯片22A的感光区域对应于所述光窗251A,以藉由所述模制基座25A的所述光窗251A 形成所述光学镜头10A和所述感光芯片22A的光线通路。也就是说,自所述光学镜头10A进入所述阵列摄像模组100A的内部的光线在穿过所述模制基座25A的所述光窗251A后能够被所述感光芯片22A接收和成像。

[0385] 例如,在附图87和图88示出的所述阵列摄像模组100A的这个具体的示例中,所述

模制基座25A具有两个相互独立的所述光窗251A,其中每个所述感光芯片22A的感光区域分别对应于所述模制基座25A的每个所述光窗251A,以藉由所述模制基座25A的每个所述光窗251A分别形成每个所述光学镜头10A和每个所述感光芯片22A的光线通路。也就是说,被物体反射的光线在自每个所述光学镜头10A进入所述阵列摄像模组100A的内部后,能够经由所述模制基座25A的每个所述光窗251A后被每个所述感光芯片22A的感光区域接收,并在后续藉由每个所述感光芯片22A进行光电转化而成像。

[0386] 所述模制基座25A可以通过模制工艺一体地成型于所述电路板21A的所述正面211A,通过这样的方式,在所述模制基座25A和所述电路板21A之间不需要设置诸如胶水等用于连接所述模制基座25A和所述电路板21A的物质,这样,不仅能够降低所述阵列摄像模组100A的高度尺寸,而且还能够有效保证所述电路板21A的平整度,以改善所述阵列摄像模组100A的成像品质。另外,因为在所述模制基座25A和所述电路板21A的所述正面211A之间不需要设置诸如胶水等用于连接所述模制基座25A和所述电路板21A的物质,因此,所述阵列摄像模组100A的高度尺寸能够被降低,以有利于所述阵列摄像模组100A被应用于更轻薄的所述电子设备。更为重要的是,所述模制基座25A在成型的过程中一体地结合于所述电路板21A,从而一方面所述模制基座25A不需要被预制,另一方面不用担心所述模制基座25A在未结合于所述电路板21A之前出现形变的不良现象。并且,所述模制基座25A能够补强所述电路板21A的强度,以保证所述电路板21A的平整度,从而即便是所述电路板21A被选用较薄的PCB板、FPC板、软硬结合板等厚度更薄的电路板时,所述模制基座25A也能够保证所述电路板21A的平整度,通过这样的方式,多个所述感光芯片22A的同轴度也能够被保证。

[0387] 所述阵列摄像模组100A进一步包括至少一驱动器30A,其中所述光学镜头10A被可驱动地设置于所述驱动器30A,所述驱动器30A被设置于所述模制基座25A,以藉由所述驱动器30A和所述模制基座25A相互配合而使所述光学镜头10A被保持在所述感光芯片22A的感光路径。所述驱动器30A能够驱动所述光学镜头10A沿着所述感光芯片22A的感光路径移动,以调整所述阵列摄像模组100A的焦距,从而使得阵列摄像模组100A具有自动对焦和变焦能力。优选地,所述驱动器30A可以被实施为但不限于音圈马达。

[0388] 例如,在附图87和图88示出的所述阵列摄像模组100A的这个具体的示例中,所述驱动器30A的数量被实施为两个,其中每个所述光学镜头10A分别被可驱动地设置于每个所述驱动器30A,每个所述驱动器30A分别以每个所述光学镜头10A对应于所述模制基座25A的每个所述光窗251A的方式被贴装于所述模制基座25A,以藉由每个所述驱动器30A将每个所述光学镜头10A保持在每个所述感光芯片22A的感光路径。

[0389] 值得一提的是,在本发明的所述阵列摄像模组100A的一些具体的示例中,每个所述驱动器30A分别以同时且同幅度的方式驱动每个所述光学镜头10A沿着每个所述感光芯片22A的感光路径移动。在本发明的所述阵列摄像模组100A的另外一些具体的示例中,每个所述驱动器30A分别单独地驱动每个所述光学镜头10A沿着每个所述感光芯片22A的感光路径移动。例如在附图87示出的所述阵列摄像模组100A的这个具体的示例中,位于附图左侧的所述驱动器30A能够驱动所述光学镜头10A沿着所述感光芯片22A的感光路径移动,而位于附图右侧的所述驱动器30A可以不动,这样能够使两个光学系统具有不同的焦距。

[0390] 进一步参考附图87,所述阵列摄像模组100A可以包括至少一滤光元件50A,其中每个所述滤光元件50A分别被保持在每个所述感光芯片22A和每个所述光学镜头10A之间,以

用于过滤自每个所述光学镜头10A进入所述阵列摄像模组100A的内部的光线中的杂光,从而改善所述阵列摄像模组100A的成像品质。所述滤光元件50A的类型不受限制,例如所述滤光元件50A可以被实施为但不限于红外截止滤光片。

[0391] 例如,在附图87示出的所述阵列摄像模组100A的这个具体的示例中,所述阵列摄像模组100A包括两个所述滤光元件50A,其中每个所述滤光元件50A分别被贴装于所述模制基座25A,并且每个所述滤光元件50A分别被保持在每个所述感光芯片22A和每个所述光学镜头10A之间,以藉由每个所述滤光元件50A过滤自每个所述光学镜头10A进入所述阵列摄像模组100A的内部的光线中的杂光。尽管如此,本领域的技术人员应当理解的是,在本发明的所述阵列摄像模组100A的另外一些具体的示例中,所述阵列摄像模组100A也可以包括一个所述滤光元件50A,此时,两个以上的所述感光芯片22A可以对应于同一个所述滤光元件50A的不同位置,以藉由所述滤光元件50A过滤自每个所述光学镜头10A进入所述阵列摄像模组100A的内部的光线中的杂光。

[0392] 值得一提的是,在所述阵列摄像模组100A包括两个以上的所述滤光元件50A的示例中,每个所述滤光元件50A的类型可以一样,也可以不一样,其根据需要被选择,本领域技术人员应当理解的是,若所述阵列摄像模组100A的每个所述滤光元件50A的类型不同,则所述阵列摄像模组100A的每个光学系统可以具有不同的成像特色。值得一提的是,所述阵列摄像模组100A的每个光学系统藉由一个所述感光芯片22A和被保持在所述感光芯片22A的感光路径的一个所述光学镜头10A形成。例如,在附图87示出的所述阵列摄像模组100A的这个具体的示例中,位于附图左侧的所述滤光元件50A的类型和位于附图右侧的所述滤光元件50A的类型可以不同。

[0393] 更进一步地,继续参考附图87,所述模制基座25A具有一外贴装面252A和至少一内贴装面253A,每个所述内贴装面253A分别围绕在所述模制基座25A的每个所述光窗251A的周围,所述外贴装面252A围绕在每个所述内贴装面253A的周围,其中每个所述驱动器30A可以被贴装于所述模制基座25A的所述外贴装面252A的不同位置,每个所述滤光元件50A可以分别被贴装于所述模制基座25A的每个所述内贴装面253A,通过这样的方式,能够使每个所述光学镜头10A被分别保持在每个所述感光芯片22A的感光路径,和使每个所述滤光元件50A分别被保持在每个所述感光芯片22A和每个所述光学镜头10A之间。

[0394] 在所述阵列摄像模组100A的一个示例中,所述模制基座25A的所述外贴装面252A和所述内贴装面253A可以处于同一个平面。在所述阵列摄像模组100A的另一个示例中,所述模制基座25A的所述外贴装面252A和所述内贴装面253A可以具有高度差,以形成所述模制基座25A的至少一贴装槽254A。具体地,所述模制基座25A的所述内贴装面253A所在的平面低于所述外贴装面252A所在的平面,从而所述模制基座25A在所述内贴装面253A对应的位置形成所述贴装槽254A,这使得被贴装于所述内贴装面253A的所述滤光元件50A被保持在所述贴装槽254A内,通过这样的方式,能够进一步降低所述阵列摄像模组100A的高度尺寸,参考附图87示出的所述阵列摄像模组100A。

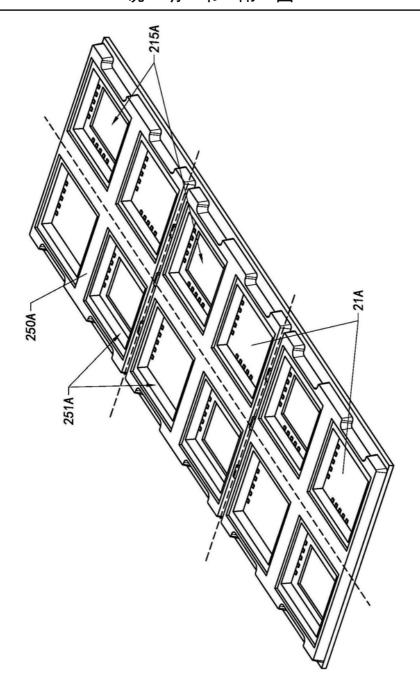

[0395] 本发明的说明书附图之附图76至图87示出了所述阵列摄像模组100A的制造流程,其中在附图76示出的阶段,可以将两个以上的所述电路板21A排列在一起而形成一拼板单元300A,以便于在后续执行模制工艺。例如,可以将多个所述电路板21A排列成但不限于两排而形成所述拼板单元300A。当然,本领域技术人员应当理解的是,在本发明的所述阵列摄

像模组100A的其他示例中,所述拼板单元300A可以包括更多排的所述电路板21A。

[0396] 值得一提的是,所述电路板21A可以在形成后被排列而形成所述拼板单元300A,例如单独形成的所述电路板21A可以被排列在一个基底上而形成所述拼板单元300A,或者多个所述电路板21A可以是一体式结构,其在被完成模制工艺后被进行切割而分离。在本发明的接下来的描述中,以多个所述电路板21A是一体式结构为例,继续对所述阵列摄像模组100A的制造流程进行揭露和阐述。

[0397] 在附图77示出的阶段,可以将每个所述电子元器件23A分别在所述电路板21A的所述背面212A贴装于所述电路板21A。尽管如此,本领域的技术人员应当理解的是,一些所述电子元器件23A可以被贴装于所述电路板21A的所述背面212A,而另一些所述电子元器件23A也可以被贴装于所述电路板21A的所述正面211A。本发明的所述阵列摄像模组100A在这方面不受限制。

[0398] 值得一提的是,尽管在附图77中示出的所述阵列摄像模组100A的具体示例中,所述电子元器件23A被贴装于所述电路板21A的所述背面212A,在另一些具体的示例中,所述电子元器件23A的至少一部分也可以被埋入到所述电路板21A的所述背面212A,例如,所述电子元器件23A的一部分可以埋入所述电路板21A,并且所述电子元器件23A的另一部分暴露在或者凸出于所述电路板21A的所述背面212A。可选地,所述电子元器件23A也可以全部被埋入到所述电路板21A。

[0399] 还值得一提的是,在单独地制作每个所述电路板21A,再将每个所述电路板21A排列成所述拼板单元300A的示例中,也可以首先在所述电路板21A的所述背面212A贴装每个所述电子元器件23A,然后再排列每个所述电路板21A而形成所述拼板单元300A。

[0400] 另外,所述电路板21A可以被排列成不同于附图76和图77示出的样式,或者所述电路板21A也可以没有被排列,从而在后续的模制工艺中,可以单独地在所述电路板21A上执行模制工艺而形成与所述电路板21A一体地结合的所述模制基座25A。

[0401] 优选地,所述拼板单元300A的相邻所述电路板21A之间的距离的范围是0.01mm~500mm(包括0.01mm和500mm),以便于在模制工艺完成后,对所述电路板21A进行分割。优选地,相邻所述基板311之间的距离范围是0.05mm~200mm(包括0.05mm和200mm)。另外,为了提高局部成型的稳定性,所述拼板单元300A的最小尺寸范围是1mm~10000mm(包括1mm和10000mm),优选为10mm~1000mm(包括10mm和1000mm)。

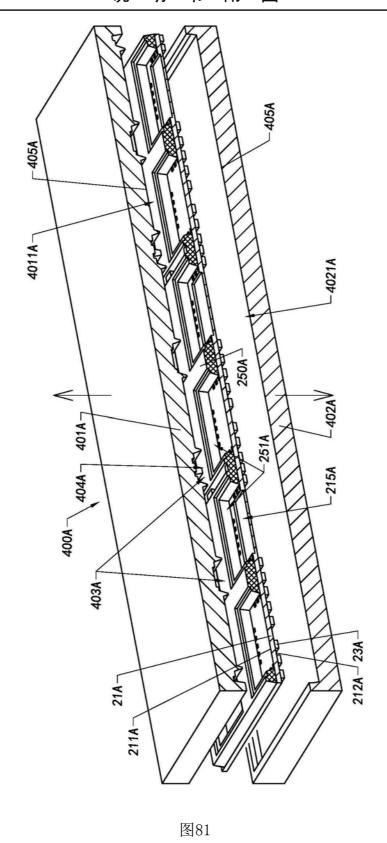

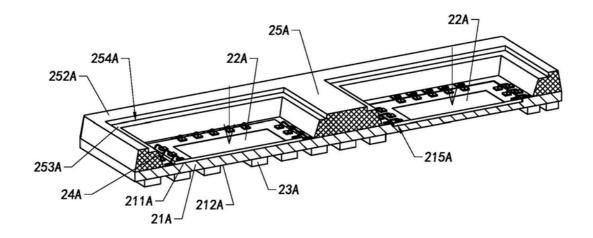

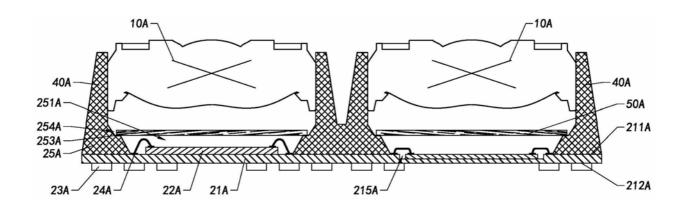

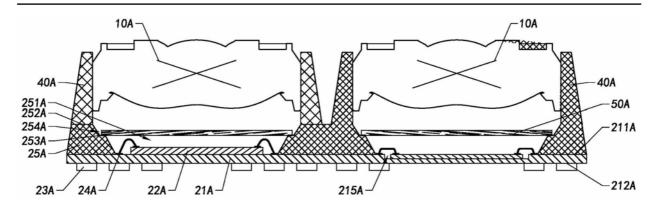

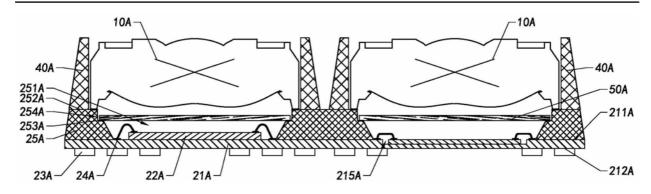

[0402] 参考附图78A至图81,将所述拼板单元300A放置于一成型模具400A中进行模制工艺,其中所述成型模具400A包括一上模具401A和一下模具402A,其中所述上模具401A和所述下模具402A中的至少一个模具能够被操作,以使所述成型模具400A的所述上模具401A和所述下模具402A能够被合模和拔模。

[0403] 参考附图78A和图78B,所述拼板单元300A被放置于所述成型模具400A的所述上模具401A和所述下模具402A之间,并且在所述拼板单元300A和所述上模具401A之间形成至少一成型空间403A,所述拼板单元300A的所述电路板21A的所述正面211A朝向所述上模具401A。优选地,所述上模具401A具有至少一上模避让空间4011A,其中在所述上模具401A和所述下模具402A被合模且所述拼板单元300A被保持在所述上模具401A和所述下模具402A之间后,凸出于所述电路板21A的所述正面211A的电路板连接件被保持在所述上模具401A的所述上模避让空间4011A,以避免凸出于所述电路板21A的所述正面211A的电路板连接件

受压而损坏,从而在对所述拼板单元300A执行模制工艺的过程中保证所述电路板21A的可靠性。优选地,在所述上模具401A和所述下模具402A被合模后,在所述上模具401A和所述拼板单元300A之间还形成至少一连通通道404A,以供连通相邻所述成型空间403A。另外,所述下模具402A具有至少一下模避让空间4021A,其中在所述上模具401A和所述下模具402A被合模后,所述拼板单元300A的所述电路板21A的所述背面212A朝向所述下模具402A,并且凸出于所述电路板21A的所述背面212A的所述电子元器件23A或者所述电子元器件23A的裸露在所述电路板21A的所述背面212A的自由侧被保持在所述下模具402A的所述下模避让空间4021A,以避免所述下模具402A的内表面因与所述电子元器件23A的外表面接触而损坏所述电子元器件23A,从而在对所述拼板单元300A执行模制工艺的过程中保证所述电路板21A和所述电子元器件23A的可靠性。

[0404] 继续参考附图78A和图78B,所述成型模具400A还包括一覆盖膜405A,其中所述覆盖膜405A被重叠地设置于所述上模具401A的内表面和所述下模具402A的内表面,从而在所述上模具401A和所述下模具402A被执行合模操作后,所述覆盖膜405A被保持在所述上模具401A和所述电路板21A的所述正面211A之间,和被保持在所述下模具402A和所述电路板21A的所述背面212A之间,从而避免所述上模具401A和所述下模具402A因直接与所述电路板21A的所述正面211A和所述背面212A的表面接触而损坏所述电路板21A的所述正面211A和所述背面212A。优选地,所述覆盖膜405A具有弹性,从而在所述成型模具400A的所述上模具401A和所述下模具042被合模时,所述覆盖膜405A能够吸收所述上模具401A和所述下模具402A因合模而产生的冲击力,以避免该冲击力作用于所述电路板21A,从而保护所述电路板21A。

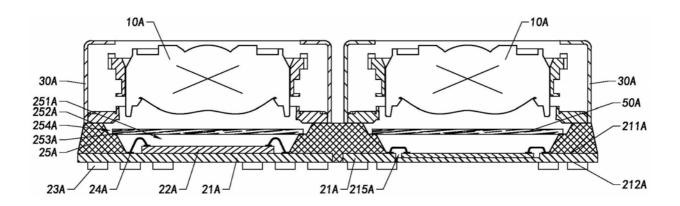

[0405] 参考附图79至图81,将一流体状的成型材料500A加入到至少一个所述成型空间403A内,所述成型材料500A会通过所述连通通道404A填充满所述成型模具400A的所有的所述成型空间403A,并且在所述成型材料500A在所述成型空间403A内固化且对所述成型模具400A进行拔模操作后,形成与所述电路板21A的所述正面211A一体地结合的一连体模制基座250A,和同时形成所述连体模制基座250A的多个所述光窗251A。在对所述上模具401A和所述下模具402A执行拔模的过程中,因为所述覆盖膜405A能够隔离所述上模具401A的内表面和所述连体模制基座250A,从而所述覆盖膜405A有利于所述上模具401A被拔模,且能够避免所述上模具401A刮伤所述连体模制基座250A的表面,尤其是所述覆盖膜405A能够避免所述上模具401A刮伤所述连体模制基座250A的用于形成所述光窗251A的内表面。

[0406] 值得一提的是,所述成型材料500A可以是但不限于固体颗粒、液体、液体和固体颗粒的混合物。

[0407] 另外,在附图78A和图78B示出的阶段,在所述成型模具400A的所述上模具401A和所述下模具402A被合模时,所述覆盖膜405A能够通过产生变形的方式阻止在所述上模具401A和所述电路板21A的所述正面211A之间产生缝隙,从而在附图79和图80示出的阶段,不仅能够阻止流体状的所述成型材料500A自所述成型空间403A或所述连通通道404A进入所述上模避让空间4011A,而且能够阻止所述成型材料500A进入所述上模具401A和所述电路板21A的所述正面211A之间而出现"飞边"的不良现象。

[0408] 值得一提的是,在对所述上模具401A和所述下模具402A执行拔模后可以得到一连体电路板组件200A,其中所述连体电路板组件200A包括所述电路板21A、被导通地连接于所

述电路板21A的所述电子元器件23A以及一体地结合于所述电路板21A的所述连体模制基座250A。

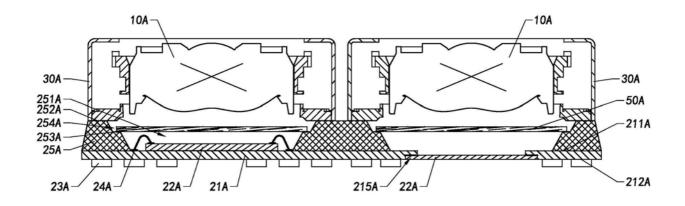

[0409] 进一步参考附图82A和图82B示出的阶段,在通过所述成型模具400A藉由模制工艺在所述拼板单元300A上模制所述连体模制基座250A而得到所述连体电路板组件200A后,可以对组成所述拼板单元300A的所述电路板21A和所述连体模制基座250A进行分割,以得到所述电路板组件20A的半成品,例如,可以通过切割或者蚀刻等工艺去除所述电路板21A和所述连体模制基座250A的多余的部分,以得到所述电路板组件20A的半成品,其中所述连体模制基座250A在被分割后形成所述模制基座25A,所述连体模制基座250A的所述光窗251A。

[0410] 在附图83示出的阶段,经由所述模制基座25A的所述光窗251A将所述感光芯片22A贴装于所述电路板21A的正面,和藉由打线工艺在所述感光芯片22A的芯片连接件和所述电路板21A的电路板连接件之间所述引线24A,以得到所述电路板组件20A,其中所述感光芯片22A的感光区域对应所述模制基座25A的所述光窗251A。

[0411] 参考附图84示出的阶段,将所述滤光元件50A贴装于所述模制基座25A的所述内贴装面253A,以使所述滤光元件50A被保持在所述感光芯片22A的感光路径。在附图85示出的阶段,将组装有所述光学镜头10A的所述驱动器30A贴装于所述模制基座25A的所述外贴装面252A,以使所述光学镜头10A被保持在所述感光芯片22A的感光路径,和使所述滤光元件50A被保持在所述光学镜头10A和所述感光芯片22A之间。

[0412] 进一步地,所述电路板组件20A包括一连接板单元28A,其中所述连接板单元28A进一步包括至少一连接板281A和被设置于所述连接板281A的自由端的至少一安装件282A,其中在附图86示出的阶段,所述连接板单元28A的所述连接板281A能够被贴装于所述电路板21A,并使所述电路板21A和所述连接板281A被导通。优选地,所述连接板单元28A的所述连接板281A可以变形,从而有利于在后续将所述阵列摄像模组100A组装于所述电子设备。

[0413] 值得一提的是,尽管在附图86示出的阶段,所述连接板单元28A的所述连接板281A被贴装于所述电路板21A的所述背面212A,以制得所述阵列摄像模组100A。在本发明的所述阵列摄像模组100A的其他可能的示例中,所述连接板单元28A的所述连接板281A也可以被贴装于所述电路板21A的所述正面211A。可选地,所述连接板单元28A的所述连接板281A和所述电路板21A也可以是一体式结构。

[0414] 还值得一提的是,尽管在附图86示出的所述阵列摄像模组100A的这个具体的示例中,所述连接板单元28A的所述连接板281A的连接端被贴装在所述电路板21A的宽度方向,以使所述连接板281A被保持在所述阵列摄像模组100A的侧部,在本发明的所述阵列摄像模组100A的另外一些示例中,所述连接板单元28A的所述连接板281A的连接端也可以被贴装于所述电路板21A的长度方向,以使所述连接板281A被保持在所述阵列摄像模组100A的端部。本发明的所述阵列摄像模组100A在这方面不受限制。

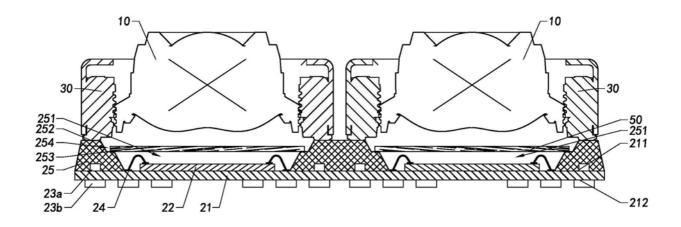

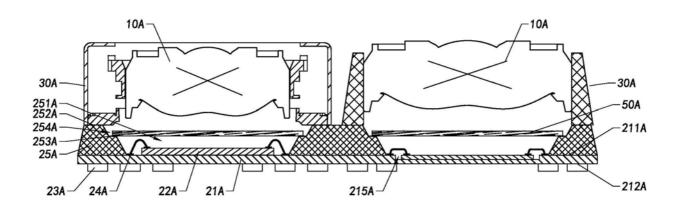

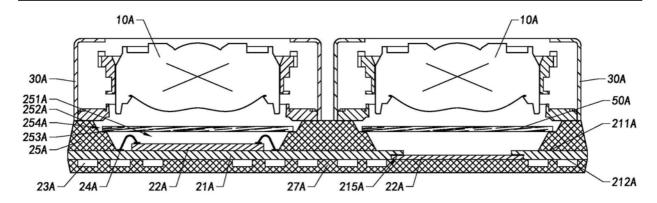

[0415] 附图90示出了所述阵列摄像模组100A的一个变形实施方式,与附图88示出的所述阵列摄像模组100A不同的是,在附图90示出的所述阵列摄像模组100A的这个具体的实施方式中,所述电路板组件20A进一步包括一包埋部27A,其中所述包埋部27A一体地结合于所述电路板21A的所述背面212A。优选地,所述包埋部27A能够包埋凸出于所述电路板21A的所述背面212A的至少一个所述电子元器件23A的至少一部分。更优选地,所述包埋部27A能够包

埋凸出于所述电路板21A的所述背面212A的全部的所述电子元器件23A。所述包埋部27A通过包埋凸出于所述电路板21A的所述背面212A的所述电子元器件23A的方式,一方面,所述包埋部27A能够隔离所述电子元器件23A的表面和外部环境以避免所述电子元器件23A被氧化,另一方面,所述包埋部27A能够隔离相邻所述电子元器件23A以避免相邻所述电子元器件23A出现相互干扰的不良现象,再一方面,因为所述包埋部27A能够通过隔离相邻所述电子元器件23A的方式避免相邻的所述电子元器件23A出现相互干扰的不良现象,从而相邻所述电子元器件23A之间的距离可以被设置的更近,这样,有利于减小所述阵列摄像模组100A的长度尺寸和宽度尺寸中的至少一个尺寸,从而有利于所述阵列摄像模组100A的小型化。另外,因为所述包埋部27A能够通过隔离相邻所述电子元器件23A的方式避免相邻的所述电子元器件23A出现相互干扰的不良现象,从而在所述电路板21A提供相同贴装面积的情况下,所述电路板21A的所述背面212A可以被贴装更多数量和更大尺寸的所述电子元器件23A,以有利于进一步提高所述阵列摄像模组100A的成像能力。

[0416] 另外,所述包埋部27A通过一体地结合于所述电路板21A的所述背面212A的方式能够进一步补强所述电路板21A,从而使所述电路板21A具有更好的平整度,因为所述阵列摄像模组100A的多个所述感光芯片22A均被贴装于所述电路板21A的所述正面211A,因此,保证所述电路板21A的平整度能够提高多个所述感光芯片22A的感光路径的平行度,这对于保证和提高所述阵列摄像模组100A的成像能力是非常重要的。

[0417] 值得一提的是,所述包埋部27A可以采用与所述模制基座25A结合于所述电路板21A的所述正面211A的方式结合于所述电路板21A的所述背面212A。可选地,在所述模制基座25A结合于所述电路板21A的所述正面211A的同时,所述包埋部27A结合于所述电路板21A的所述背面212A。还可选地,在所述模制基座25A结合于所述电路板21A的所述正面211A后,所述包埋部27A结合于所述电路板21A的所述背面212A,或者在所述模制基座25A结合于所述电路板21A的所述正面211A前,所述包埋部27A结合于所述电路板21A的所述背面212A。本发明的所述阵列摄像模组100A在这方面不受限制。

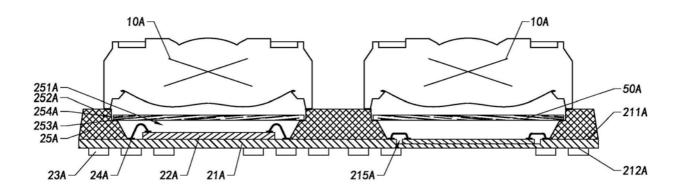

[0418] 附图91示出了所述阵列摄像模组100A的一个变形实施方式,与附图90示出的所述阵列摄像模组100A不同的是,在附图91示出的所述阵列摄像模组100A的这个具体的示例中,所述包埋部27A结合所述电路板21A的所述背面212A的一部分,以在所述包埋部27A的中部和/或侧部形成一缺口271A,例如在附图91示出的所述阵列摄像模组100A的这个具体的示例中,所述包埋部27A结合于所述电路板21A的所述背面212A的一侧,而在所述电路板21A的所述背面212A的一侧,而在所述电路板21A的所述背面212A的所述电路板21A的所述电路板21A的所述电路板21A的所述背面212A的总面积的面积比值为1:2,或者2:3。可选地,所述包埋部27A结合的所述电路板21A的所述背面212A的面积与所述电路板21A的所述背面212A的面积与所述电路板21A的所述背面212A的面积与所述电路板21A的所述背面212A的面积与所述电路板21A的所述背面212A的面积与所述电路板21A的所述背面212A的面积与所述电路板21A的所述背面212A的总面积的面积比的比值范围为大于或者等于1:2,且小于或者等于2:3。尽管如此,本领域技术人员应当理解的是,上述揭露的所述电路板21A的所述背面212A的总面积的面积比的比值范围为大于等于1:2且小于等于2:3仅为示例,其并不应被视为对本发明的所述阵列摄像模组100A的内容和范围的限制。换言之,所述电路板21A的所述背面212A被所述包埋部27A包埋的面积在本发明的所述阵列摄像模组100A中不受限制,只要所述包埋部27A能够包埋所述电子元器件23A即可。

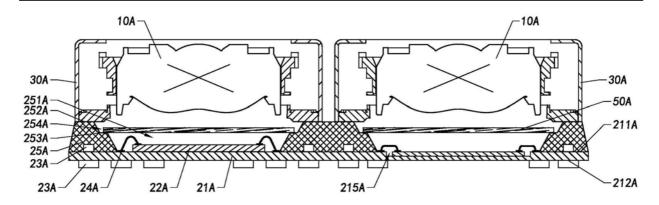

[0419] 附图92示出了所述阵列摄像模组100A的一个变形实施方式,与附图88示出的所述阵列摄像模组100A不同的是,在附图92示出的所述阵列摄像模组100A的这个具体的示例中,所述模制基座25A包埋至少一个所述感光芯片22A的非感光区域,通过这样的方式,能够进一步减小所述阵列摄像模组100A的长度尺寸和宽度尺寸中的至少一个尺寸,以有利于所述阵列摄像模组100A的小型化。优选地,所述模制基座25A包埋感光面较高的所述感光芯片22A的非感光区域,例如,在附图92示出的所述阵列摄像模组100A的这个具体的示例中,位于附图左侧的所述感光芯片22A的非感光区域被所述模制基座27包埋。

[0420] 本领域技术人员可以理解的是,在附图92示出的所述阵列摄像模组100A的这个具体的示例中,可以先贴装所述感光芯片22A于所述电路板21A的所述正面211A,然后再对被贴装有所述感光芯片22A的所述拼板单元300A执行模制工艺,以得到结合于所述拼板单元300A的所述电路板21A的所述正面212的所述模制基座25A,并且所述模制基座25A可以包埋所述感光芯片22A的非感光区域。

[0421] 值得一提的是,在本发明的所述阵列摄像模组100A中通过所述模制基座25A包埋所述感光芯片22A的非感光区域的方式,能够藉由所述模制基座25A保证所述感光芯片22A的平整度,从而使所述感光芯片22A的平整度可以不再局限于所述电路板21A的平整度,并且所述模制基座25A也能够起到补强所述电路板21A的作用,这样,即便是所述电路板21A被选用较薄的PCB板、FPC板、软硬结合板等电路板时,所述电路板21A的平整度也能够被保证,以能够进一步降低所述阵列摄像模组100A的高度尺寸。

[0422] 优选地,所述模制基座25A也可以包埋所有的所述感光芯片22A的非感光区域,因此,本领域技术人员应当理解的是,在附图92示出的所述阵列摄像模组100A仅为举例,以用于揭露本发明的所述阵列摄像模组100A的所述模制基座25A能够包埋所述感光芯片22A的非感光区域,而并不应被视为对本发明的所述阵列摄像模组100A的内容和范围的限制。

[0423] 附图93示出了所述阵列摄像模组100A的一个变形实施方式,与附图88示出的所述阵列摄像模组100A不同的是,在附图93示出的所述阵列摄像模组100A的这个具体的示例中,所述阵列摄像模组100A还可以包括至少一框型的支架60A,其中所述滤光元件50A被贴装于所述支架60A,所述支架60A被贴装于所述模制基座25A的所述内贴装面253A,以藉由所述支架60A和所述模制基座25A将所述滤光元件50A保持在所述感光芯片22A的感光路径。本发明的所述阵列摄像模组100A通过将所述滤光元件50A贴装于所述支架60A,和将所述支架60A贴装于所述模制基座25A,以藉由所述支架60A和所述模制基座25A将所述滤光元件50A保持在所述感光芯片22A的感光路径的方式,能够减小所述滤光元件50A的长宽尺寸,以降低所述阵列摄像模组100A的制造成本。

[0424] 优选地,所述支架60A被保持在所述模制基座25A的所述贴装槽254A内,通过这样的方式,能够进一步降低所述阵列摄像模组100A的高度尺寸。

[0425] 优选地,多个所述滤光元件50A可以被贴装于同一个所述支架60A,如附图93示出的这样。可选地,所述滤光元件50A的数量和所述支架60A的数量一致,从而每个所述滤光元件50A可以分别被贴装于每个所述支架60A,每个所述支架60A分别被贴装于所述模制基座25A,以藉由每个所述支架60A使每个所述滤光元件50A分别被保持在每个所述感光芯片22A的感光路径。

[0426] 附图94示出了所述阵列摄像模组100A的另一个变形实施方式,与附图88示出的所

述阵列摄像模组100A不同的是,在附图94示出的所述阵列摄像模组100A的这个具体的示例中,一部分所述电子元器件23A被贴装于所述电路板21A的所述背面212A,另一部分所述电子元器件23A被贴装于所述电路板21A的所述正面211A,其中所述模制基座25A可以包埋凸出于所述电路板21A的所述正面211A的至少一个所述电子元器件23A的至少一部分。优选地,所述模制基座25A可以包埋凸出于所述电路板21A的所述正面211A的全部的所述电子元器件23A,从而所述模制基座25A可以隔离所述电子元器件23A和外部环境以避免所述电子元器件23A的表面被氧化,和隔离相邻所述电子元器件23A,以避免相邻的所述电子元器件23A出现相互干扰的不良现象。

[0427] 与传统的摄像模组不同的是,在本发明的所述阵列摄像模组100A的这个具体的示例中,所述阵列摄像模组100A通过所述模制基座25A在成型的过程中包埋所述电子元器件23A的方式,使得无论在所述阵列摄像模组100A的高度方向还是长宽方向,在所述模制基座25A和所述电子元器件23A之间均不需要被预留安全距离,从而有利于减小所述阵列摄像模组100A的长宽尺寸和高度尺寸,以有利于所述阵列摄像模组100A的小型化。

[0428] 附图95示出了所述阵列摄像模组100A的另一个变形实施方式,与附图88示出的所述阵列摄像模组100A不同的是,在附图95示出的所述阵列摄像模组100A的这个具体的示例中可以没有所述驱动器30A,具体地说,所述阵列摄像模组100A包括至少两镜筒40A,其中每个所述光学镜头10A分别被组装于每个所述镜筒40A,每个所述镜筒40A分别以每个所述光学镜头10A分别被保持在每个所述感光芯片22A的感光路径的方式被贴装于所述模制基座25A的所述外贴装面252A。换言之,每个所述镜筒40A分别被用于将每个所述光学镜头10A保持在每个所述感光芯片22A的感光路径。

[0429] 附图96示出了所述阵列摄像模组100A的另一个变形实施方式,与附图95示出的所述阵列摄像模组100A不同的示例,在附图96示出的所述阵列摄像模组100A的这个具体的示例中,每个所述镜筒40A可以分别与所述模制基座25A一体地成型,即,每个所述镜筒40A分别一体地延伸于所述模制基座25A。优选地,多个所述镜筒40A也可以是一体式结构。

[0430] 附图97示出了所述阵列摄像模组100A的另一个变形实施方式,与附图95示出的所述阵列摄像模组100A不同的是,在附图97示出的所述阵列摄像模组100A的这个具体的示例中,至少一个所述镜筒40A被贴装于所述模制基座25A,和另外的所述镜筒40A一体地延伸于所述模制基座25A,并且延伸于所述模制基座25A的所述镜筒40A和被贴装于所述模制基座25A的所述镜筒40A相邻。

[0431] 附图98示出了所述阵列摄像模组100A的另一个变形实施方式,与附图88示出的所述阵列摄像模组100A不同的是,在附图98示出的所述阵列摄像模组100A的这个具体的示例中,至少一个所述驱动器30A被贴装于所述模制基座25A的所述外贴装面251,和至少一个所述镜筒40A被贴装于所述模制基座25A的所述外贴装面252A,并且所述驱动器30A和所述镜筒40A相邻。

[0432] 附图99示出了所述阵列摄像模组100A的另一个变形实施方式,与附图88示出的所述阵列摄像模组100A不同的是,在附图99示出的所述阵列摄像模组100A的这个具体的示例中,每个所述光学镜头10A可以被直接贴装于所述模制基座25A的所述外贴装面252A,从而使每个所述光学镜头10A分别被保持在每个所述感光芯片22A的感光路径。

[0433] 附图100示出了所述阵列摄像模组100A的另一个变形实施方式,与附图99示出的

所述阵列摄像模组100A不同的是,在附图100示出的所述阵列摄像模组100A的这个具体的示例中,将每个所述镜筒40A以每个所述镜筒40A分别环绕在每个所述光学镜头10A的周围的方式贴装于所述模制基座25A,并且所述光学镜头10A和所述镜筒40A的内壁可以不接触。本发明的所述阵列摄像模组100A可以通过将所述镜筒40A环绕在所述光学镜头10A的四周的方式保护所述光学镜头10A,以避免在运输或者安装所述阵列摄像模组100A的过程中碰触到所述光学镜头10A而导致所述阵列摄像模组100A损坏。可选地,每个所述镜筒40A也可以分别一体地延伸于所述模制基座25A。

[0434] 附图101示出了所述阵列摄像模组100A的另一个变形实施方式,与附图88示出的所述阵列摄像模组100A不同的是,所述阵列摄像模组100A包括两个以上的所述电路板21A,例如,所述电路板21A的数量和所述感光芯片22A的数量可以一致。具体的说,参考附图101,以所述阵列摄像模组100A包括两个所述感光芯片22A和两个所述电路板21A为例,其中位于附图左侧的所述电路板21A没有所述容纳空间215A,而位于附图右侧的所述电路板21A设有所述容纳空间215A,其中被贴装于位于附图右侧的所述电路板21A的所述感光芯片22A被保持在所述电路板21A的所述容纳空间215A内,以使得被贴装于附图左侧的所述电路板21A的所述感光芯片22A的感光面和被贴装于附图右侧的所述电路板21A的所述感光芯片22A的感光面之间具有高度差。

[0435] 附图102示出了所述阵列摄像模组100A的另一个变形实施方式,与附图88示出的所述阵列摄像模组100A不同的是,所述电路板21A的所述容纳空间215A为通孔状的所述容纳空间215A。在附图102示出的所述阵列摄像模组100A的这个具体的示例中,以所述阵列摄像模组100A包括两个所述感光芯片22A为例对所述阵列摄像模组100A的内容和特征继续揭露和阐述,其中所述电路板21A的位于附图右侧的部分具有通孔状的所述容纳空间215A,左侧的所述感光芯片22A被贴装于所述电路板21A的左侧的所述正面211A,而右侧的所述感光芯片22A被贴装于所述电路板21A的右侧的所述背面212A,并且右侧的所述感光芯片22A的感光区域暴露在所述电路板21A的所述容纳空间215A,从而使得两个所述感光芯片22A的感光面具有高度差。

[0436] 附图103示出了所述阵列摄像模组100A的另一个变形实施方式,与附图102示出的所述阵列摄像模组100A不同的是,在附图103示出的所述阵列摄像模组100A的这个具体的示例中,所述电路板21A的所述背面212A进一步结合有所述包埋部27A,以藉由所述包埋部27A包埋凸出于所述电路板21A的所述背面212A的所述电子元器件23A。优选地,所述包埋部27A还可以结合附图右侧的所述感光芯片22A的背面的至少一部分。

[0437] 附图104示出了所述阵列摄像模组100A的另一个变形实施方式,与附图103示出了所述阵列摄像模组100A不同的是,在附图104示出的所述阵列摄像模组100A的这个具体的示例中,右侧的所述感光芯片22A可以没有被贴装于所述电路板21A的所述背面212A,而是在所述包埋部27A以所述包埋部27A的一部分被保持在所述电路板21A的所述容纳空间215A的方式结合于所述电路板21A的所述背面212A之后,将右侧的所述感光芯片22A贴装于所述包埋部27A,从而使得两个所述感光芯片22A的感光面具有高度差。

[0438] 本领域的技术人员可以理解的是,以上实施例仅为举例,其中不同实施例的特征可以相互组合,以得到根据本发明揭露的内容很容易想到但是在附图中没有明确指出的实施方式。

[0439] 本领域的技术人员应理解,上述描述及附图中所示的本发明的实施例只作为举例而并不限制本发明。本发明的目的已经完整并有效地实现。本发明的功能及结构原理已在实施例中展示和说明,在没有背离所述原理下,本发明的实施方式可以有任何变形或修改。

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12B

图16B

图20

图21

图22

<u>\_\_\_\_</u>

图24

图25

图26

图27

图28B

图32

图33

图34

图35

图36

图37

图38

图39

图40

图41

图42

图43

图44

图45

图46

图47

图48

图49

图50

图51

图52

图53

图54

图55

图56

图57

图58

图59

图60

图61

图62

图63

图64A

图64B

图65

图66

图67

图68

图69

图70

图71

图72

图73

图74

图75

图76

图77

图78B

图82A

图82B

图83

图84

图85

图86

图87

图88

图89

图90

图91

图92

图93

图94

图95

图96

图97

图98

图99

图100

图101

图102

图103

图104