# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(11) 공개번호 10-2009-0078803(43) 공개일자 2009년07월20일

(51) Int. Cl.

**H01L 21/82** (2006.01)

(21) 출원번호10-2009-7007923(22) 출원일자2007년09월20일

심사청구일자 없음

(85) 번역문제출일자 2009년04월17일

(86) 국제출원번호 PCT/US2007/079070

(87) 국제공개번호 **WO 2008/036837** 국제공개일자 **2008년03월27일**

(30) 우선권주장

60/826,354 2006년09월20일 미국(US) 60/944,653 2007년06월18일 미국(US) 리트 506 헨리 어드미니스트레이션 빌딩 352 (72) 발명자

(71) 출원인

로저스 존 에이.

오브 일리노이즈

미국 일리노이주 61822 샴페인 밸리브룩 2803

더 보오드 오브 트러스티스 오브 더 유니버시티

미국 61801 일리노이 어바나 사우쓰 라이트 스트

누쪼 랄프 쥐.

미국 일리노이주 61821 샴페인 노팅햄 코트 노쓰

2413

(뒷면에 계속)

(74) 대리인

리앤목특허법인

전체 청구항 수 : 총 97 항

# (54) 전사가능한 반도체 구조들, 디바이스들 및 디바이스 컴포넌트들을 만들기 위한 릴리스 방안들

# (57) 요 약

복수의 기능 레이어(functional layer)들과 복수의 릴리스 레이어(release layer)들을 가지는 멀티레이어 구조 (multilayer structure)를 제공하는 단계; 및 1 이상의 릴리스 레이어들을 분리함으로써 멀티레이어 구조로부터 기능 레이어들을 릴리스하여, 복수의 전사가능한(transferable) 구조들을 생성하는 단계;에 의해 디바이스 또는 디바이스 컴포넌트를 만드는 방법들이 제공된다. 전사가능한 구조들은 디바이스 기판 또는 디바이스 기판에 의해 지지되는 디바이스 컴포넌트 상으로 프린팅된다. 본 방법들과 시스템들은 고품질 저비용의 광전 디바이스 (photovoltaic device)들, 전사가능한 반도체 구조들, (광)전자 디바이스들 및 디바이스 컴포넌트들을 만들기 위한 수단을 제공한다.

### 대표도

# (72) 발명자

# 메이틀 매튜

미국 일리노이주 61820 샴페인 사우스 랜돌프 스트 리트 311

### 고형조

미국 일리노이주 61801 어바나 사우쓰 굿윈 애버뉴 300 515번

# 윤종성

미국 일리노이주 61801 어바나 웨스트 그린 스트리 트 1107 아파트 627호

# 머나드 에티앙

미국 일리노이주 61801 어바나 노쓰 라인뷰 913 **바카 알프레드 제이**.

미국 일리노이주 61802 어바나 사우스 버뮤다 드라 이브 1601

### 특허청구의 범위

#### 청구항 1

디바이스 또는 디바이스 컴포넌트를 만들기 위한 방법에 있어서, 상기 방법은,

복수의 기능 레이어(functional layer)들과 복수의 릴리스 레이어(release layer)들을 구비하는 멀티레이어 구조(multilayer structure)를 제공하는 단계[여기서, 상기 릴리스 레이어들의 적어도 일부는 상기 멀티레이어 구조에서 기능 레이어들 사이에 위치함];

1 이상의 상기 기능 레이어들로부터 1 이상의 상기 릴리스 레이어들 또는 상기 릴리스 레이어들의 일부를 분리함으로써 상기 멀티레이어 구조로부터 상기 기능 레이어들의 적어도 일부를 릴리스하여, 복수의 전사가능한 (transferable) 구조들을 생성하는 단계; 및

1 이상의 상기 전사가능한 구조들을 디바이스 기판 또는 디바이스 기판에 의해 지지되는 디바이스 컴포넌트 상에 프린팅하여, 상기 디바이스 또는 상기 디바이스 컴포넌트를 만드는 단계;

를 구비하는 것을 특징으로 하는 방법.

# 청구항 2

제 1 항에 있어서.

상기 멀티레이어 구조로부터 상기 기능 레이어들의 적어도 일부를 릴리스하는 단계는, 적어도 한 쌍의 인접 레이어들을 물리적으로 분리하는 단계;를 구비하고,

상기 한 쌍의 인접 레이어들은 상기 멀티레이어 구조에서 한 기능 레이어에 인접하게 위치하는 릴리스 레이어를 구비하는 것을 특징으로 하는 방법.

### 청구항 3

제 1 항에 있어서,

상기 멀티레이어 구조로부터 상기 기능 레이어들의 적어도 일부를 릴리스하는 단계는,

상기 멀티레이어 구조에서 1 이상의 상기 릴리스 레이어들의 적어도 일부를 제거하는 단계;

를 구비하는 것을 특징으로 하는 방법.

### 청구항 4

제 1 항에 있어서,

상기 멀티레이어 구조로부터 상기 기능 레이어들의 적어도 일부를 릴리스하는 단계는,

1 이상의 릴리스 레이어들을 에칭하는 단계:

1 이상의 릴리스 레이어들에 열적으로 충격을 주는(thermally shocking) 단계:

상기 릴리스 레이어들을 레이저 소스(laser source)로부터의 전자기적 방사(electromagnetic radiation)에 노출시켜 1 이상의 릴리스 레이어들을 애블레이팅(ablating) 또는 분해하는 단계: 그리고

상기 릴리스 레이어들을 화학 약품에 접촉시켜 1 이상의 릴리스 레이어들을 분해하는 단계:로 이루어진 그룹으로부터 선택되는 기법을 이용하여, 1 이상의 상기 기능 레이어들로부터 1 이상의 상기 릴리스 레이어들 또는 상기 릴리스 레이어들의 일부를 분리하는 단계;

를 구비하는 것을 특징으로 하는 방법.

### 청구항 5

제 1 항에 있어서,

상기 기능 레이어들은 상기 멀티레이어 구조로 노출된, 레이저 소스로부터의 전자기적 방사에 대해 적어도 부분

적으로 투명(transparent)하고,

상기 전자기적 방사는 상기 릴리스 레이어들의 적어도 일부를 애블레이팅 또는 분해할 수 있으며,

상기 방법은.

상기 멀티레이어 구조를 상기 레이저 소스로부터의 상기 전자기적 방사에 노출시켜, 1 이상의 상기 릴리스 레이어들의 적어도 일부를 애블레이팅 또는 분해하는 단계;

를 더 구비하는 것을 특징으로 하는 방법.

#### 청구항 6

제 5 항에 있어서,

상기 멀티레이어 구조는 기판 상에서 지지되고,

상기 전자기적 방사는 상기 기판을 적어도 부분적으로 관통하여, 1 이상의 상기 릴리스 레이어들의 적어도 일부를 애블레이팅 또는 분해하는 것을 특징으로 하는 방법.

### 청구항 7

제 1 항에 있어서,

상기 멀티레이어 구조로부터 상기 기능 레이어들의 적어도 일부를 릴리스하는 단계는.

1 이상의 상기 릴리스 레이어들에 계면 크랙(interfacial crack)을 도입하는 단계; 및

상기 계면 크랙의 확대를 야기하기 위해 상기 릴리스 레이어들을 기계적으로 압박하여(mechanically stressing), 1 이상의 기능 레이어들을 릴리스하는 단계;

를 구비하는 것을 특징으로 하는 방법.

### 청구항 8

제 7 항에 있어서,

상기 크랙은 1 이상의 상기 릴리스 레이어들에 기계적으로, 화학적으로 또는 열적으로 도입되는 것을 특징으로 하는 방법.

# 청구항 9

제 1 항에 있어서.

상기 멀티레이어 구조에서 상기 기능 레이어들은 한번에 하나씩 릴리스되는 것을 특징으로 하는 방법.

### 청구항 10

제 1 항에 있어서,

상기 멀티레이어 구조에서 하나보다 많은 상기 기능 레이어들이 동시에 릴리스되는 것을 특징으로 하는 방법.

### 청구항 11

제 1 항에 있어서,

1 이상의 기능 레이어들과 물리적으로 접촉하는 마스크 레이어(mask layer)를 제공하는 단계;를 더 구비하고,

상기 마스크 레이어는, 상기 멀티레이어 구조로부터 상기 기능 레이어들의 적어도 일부를 릴리스하는 단계 동안에, 1 이상의 기능 레이어들이 상기 멀티레이어 구조로 제공되는 에칭액(etchant), 솔벤트(solvent) 또는 화학 약품(chemical agent)에 노출되는 것을 방지할 수 있는 것을 특징으로 하는 방법.

### 청구항 12

제 1 항에 있어서,

상기 멀티레이어 구조로부터 상기 기능 레이어들의 적어도 일부를 릴리스하는 단계에 앞서, 1 이상의 상기 기능 레이어들과 접촉하는 캐리어 필름(carrier film)을 제공하는 단계;

를 더 구비하는 것을 특징으로 하는 방법.

#### 청구항 13

제 1 항에 있어서,

1 이상의 미리 선택된 마이크로사이즈 또는 나노사이즈 물리적 치수(physical dimension)들을 가지는 상기 전사가능한 구조들을 생성하기 위해, 적어도 하나의 상기 기능 레이어들에 움푹 들어감 특징(recessed feature)들을 만드는 단계;

를 더 구비하는 것을 특징으로 하는 방법.

### 청구항 14

제 13 항에 있어서,

적어도 하나의 상기 기능 레이어들에 움푹 들어감 특징들을 만드는 단계는,

포토리소그래피(photolithography): 소프트 리소그래피(soft lithography): 전자 빔 직접 기록(electron beam direct writing): 및 포토애블레이션 패터닝(photoablation patterning): 방법들로 이루어진 그룹으로부터 선택되는 패터닝 기법을 이용하여 실행되는 것을 특징으로 하는 방법.

### 청구항 15

제 1 항에 있어서,

1 이상의 상기 전사가능한 구조들을 상기 디바이스 기판 또는 상기 디바이스 기판에 의해 지지되는 디바이스 컴 포넌트 상에 프린팅하는 단계는,

접촉 프린팅(contact printing)을 통해 실행되는 것을 특징으로 하는 방법.

### 청구항 16

제 15 항에 있어서,

1 이상의 상기 전사가능한 구조들을 상기 디바이스 기판 또는 상기 디바이스 기판에 의해 지지되는 디바이스 컴 포넌트 상에 프린팅하는 단계는,

건식 전사 접촉 프린팅(dry transfer contact printing): 소프트 리소그래피 마이크로전사 프린팅(soft lithographic microtransfer printing): 및 소프트 리소그래피 나노전사 프린팅(soft lithographic nanotransfer printing):으로 이루어진 그룹으로부터 선택되는 기법을 통해 실행되는 것을 특징으로 하는 방법.

# 청구항 17

제 16 항에 있어서,

전사가능한 구조를 프린팅하는 단계는,

타겟 기판(target substrate)을 상기 기능 레이어에 접촉시키고 상기 기능 레이어로부터 상기 타겟 기판을 제거하여, 상기 기능 레이어의 적어도 일부를 상기 멀티레이어 구조로부터 상기 타겟 기판으로 전사하는 단계;

를 구비하는 것을 특징으로 하는 방법.

### 청구항 18

제 16 항에 있어서,

전사가능한 구조를 프린팅하는 단계는,

탄성 스탬프(elastomeric stamp)를 상기 기능 레이어에 접촉시키고 상기 기능 레이어로부터 상기 탄성 스탬프를 제거하여, 상기 기능 레이어를 상기 멀티레이어 구조로부터 상기 탄성 스탬프로 전사하는 단계;

를 구비하는 것을 특징으로 하는 방법.

### 청구항 19

제 1 항에 있어서,

1 이상의 상기 전사가능한 구조들을 상기 디바이스 기판 또는 상기 디바이스 기판에 의해 지지되는 디바이스 컴 포넌트 상에 프린팅하는 단계는,

솔루션 프린팅(solution printing)을 통해 실행되는 것을 특징으로 하는 방법.

### 청구항 20

제 19 항에 있어서,

1 이상의 상기 전사가능한 구조들을 상기 디바이스 기판 또는 상기 디바이스 기판에 의해 지지되는 디바이스 컴 포넌트 상에 프린팅하는 단계는,

유체 셀프 어셈블리(fluidic self assembly): 잉크 젯 프린팅(ink jet printing): 열적 전사 프린팅(thermal transfer printing): 및 스크린 프린팅(screen printing):으로 이루어진 그룹으로부터 선택되는 기법을 통해 실행되는 것을 특징으로 하는 방법.

### 청구항 21

제 1 항에 있어서,

상기 멀티레이어 구조의 적어도 하나의 상기 기능 레이어들은 반도체 레이어 또는 일련의 반도체 레이어들을 구비하는 것을 특징으로 하는 방법.

### 청구항 22

제 21 항에 있어서,

상기 일련의 반도체 레이어들은,

단결정(single crystalline) 반도체 레이어: 유기질(organic) 반도체 레이어: 무기질(inorganic) 반도체 레이어: III-V 반도체 레이어: 및 그룹 IV 원소 또는 화합물 반도체(elemental or compound semiconductor):로 이루어진 그룹으로부터 선택되는 적어도 하나의 반도체 레이어를 구비하는 것을 특징으로 하는 방법.

### 청구항 23

제 21 항에 있어서,

상기 일련의 반도체 레이어들은 상이한 반도체 물질들을 구비하는 적어도 두 개의 반도체 레이어들을 구비하는 것을 특징으로 하는 방법.

### 청구항 24

제 1 항에 있어서,

상기 멀티레이어 구조의 적어도 하나의 상기 기능 레이어들은 1 이상의 절연 레이어(dielectric layer)들 또는 1 이상의 전도체 레이어(conductor layer)들을 구비하는 것을 특징으로 하는 방법.

### 청구항 25

제 1 항에 있어서,

상기 멀티레이어 구조는 1 이상의 기능 레이어들과 물리적으로 접촉하도록 제공되는 1 이상의 캐리어 필름 (carrier film)들을 더 구비하는 것을 특징으로 하는 방법.

### 청구항 26

제 1 항에 있어서,

상기 멀티레이어 구조의 적어도 하나의 상기 기능 레이어들은 전자적(electronic), 광학적(optical) 또는 전자-광학적(electro-optic) 디바이스나 전자적, 광학적 또는 전자-광학적 디바이스의 컴포넌트를 구비하는 것을 특징으로 하는 방법.

### 청구항 27

제 26 항에 있어서.

상기 멀티레이어 구조의 적어도 하나의 상기 기능 레이어들은,

P-N 접합: 박막 트랜지스터: 단일 접합 솔라 셀(single junction solar cell): 다중 접합 솔라 셀: 포토다이오 드: 발광 다이오드: 레이저: CMOS 디바이스: MOSFET 디바이스: MESFET 디바이스: 그리고 HEMT 디바이스:로 이루 어진 그룹으로부터 선택되는 전자적, 광학적 또는 전자-광학적 디바이스나 전자적, 광학적 또는 전자-광학적 디바이스의 컴포넌트를 구비하는 것을 특징으로 하는 방법.

### 청구항 28

제 1 항 내지 제 27 항 중의 어느 한 항에 있어서,

기판 상에 상기 멀티레이어 구조를 생성하는 단계;를 더 구비하고,

적어도 하나의 릴리스 레이어가 상기 기능 레이어들과 상기 기판 사이에 제공되는 것을 특징으로 하는 방법.

### 청구항 29

제 28 항에 있어서,

상기 기판 상에 상기 멀티레이어 구조를 생성하는 단계는,

기상 에피택시(vapor-phase epitaxy): 분자-빔 에피택시(molecular-beam epitaxy): 증발식 증착(evaporation deposition): 금속유기질 화학적 증기 증착(metalorganic chemical vapor deposition): 화학적 증기 증착(chemical vapor deposition): 화학적 증기 증착(physical vapor deposition): 스퍼터링 증착(sputtering deposition): 졸-겔 코팅(sol-gel coating): 전자 빔 증발식 증착(electron beam evaporation deposition): 플라즈마-강화 화학적 증기 증착(plasma-enhanced chemical vapor deposition): 원자 레이어 증착(atomic layer deposition): 액상 에피택시(liquid phase epitaxy): 전기화학적 증착(electrochemical deposition): 및 스핀 코팅(spin coating):으로 이루어진 그룹으로부터 선택되는 기법을 이용하여 실행되는 것을 특징으로 하는 방법.

# 청구항 30

제 28 항에 있어서,

기판 상에 상기 멀티레이어 구조를 생성하는 단계: 상기 멀티레이어 구조로부터 상기 기능 레이어들의 적어도 일부를 릴리스하는 단계: 및 1 이상의 상기 전사가능한 구조들을 프린팅하는 단계:를 반복하는 단계;를 더 구비하고,

기판 상에 상기 멀티레이어 구조를 생성하는 단계: 상기 멀티레이어 구조로부터 상기 기능 레이어들의 적어도 일부를 릴리스하는 단계: 및 1 이상의 상기 전사가능한 구조들을 프린팅하는 단계:를 반복하는 상기 단계 동안 에 상기 기판이 재사용되는 것을 특징으로 하는 방법.

## 청구항 31

제 28 항에 있어서,

상기 기능 레이어들의 적어도 일부, 릴리스 레이어들 또는 상기 멀티레이어 구조의 둘 다(both)는 상기 기판 상에 에피택셜형으로 성장된(epitaxially grown) 박막(thin film)들인 것을 특징으로 하는 방법.

# 청구항 32

제 31 항에 있어서,

상기 기능 레이어들과 릴리스 레이어들은 상기 기판 상에 에피택셜형으로 성장되는 미리 선택된 일련의 박막들

을 구비하는 것을 특징으로 하는 방법.

#### 청구항 33

제 32 항에 있어서.

상기 미리 선택된 일련의 박막들은 상기 기판 상에 에피택셜형으로 성장된, 교호하는(alternating) 릴리스 레이어들과 기능 레이어들을 구비하는 것을 특징으로 하는 방법.

### 청구항 34

제 1 항에 있어서,

상기 멀티레이어 구조의 상기 기능 레이어들은 약 5nm에서 약 50,000nm에 이르는 범위로부터 선택되는 두께들을 가지는 것을 특징으로 하는 방법.

### 청구항 35

제 1 항에 있어서,

상기 멀티레이어 구조는 약 2 내지 약 200 개의 기능 레이어들을 구비하는 것을 특징으로 하는 방법.

### 청구항 36

제 1 항에 있어서,

상기 멀티레이어 구조는 약 2 내지 약 200 개의 릴리스 레이어들을 구비하는 것을 특징으로 하는 방법.

#### 청구항 37

제 1 항에 있어서,

광전 디바이스(photovoltaic device)나 디바이스 어레이, 트랜지스터 디바이스나 디바이스 어레이, 발광 다이오 드 디바이스나 디바이스 어레이, 레이저나 레이저 어레이, 또는 센서나 센서 어레이를 만드는 방법을 구비하는 것을 특징으로 하는 방법.

# 청구항 38

제 1 항에 있어서,

집적된 전자 희로, 마이크로전자기계 디바이스(microelectromechanical device) 또는 나노전자기계 디바이스 (nanoelectromechanical device)를 만드는 방법을 구비하는 것을 특징으로 하는 방법.

### 청구항 39

전사가능한 반도체 구조들을 만드는 방법에 있어서, 상기 방법은,

복수의 기능 레이어들과 복수의 릴리스 레이어들을 구비하는 멀티레이어 구조를 제공하는 단계[여기서, 상기 릴리스 레이어들의 적어도 일부는 상기 멀티레이어 구조에서 기능 레이어들 사이에 위치하고, 상기 기능 레이어들의 적어도 일부는 1 이상의 반도체 박막들을 구비함]; 및

1 이상의 상기 기능 레이어들로부터 1 이상의 상기 릴리스 레이어들 또는 상기 릴리스 레이어들의 일부를 분리 함으로써 상기 멀티레이어 구조로부터 상기 기능 레이어들의 적어도 일부를 릴리스하여, 상기 전사가능한 반도 체 구조들을 생성하는 단계;

를 구비하는 것을 특징으로 하는 방법.

# 청구항 40

제 39 항에 있어서,

기판 상에 상기 멀티레이어 구조를 생성하는 단계;를 더 구비하고,

적어도 하나의 릴리스 레이어가 상기 기능 레이어들과 상기 기판 사이에 제공되는 것을 특징으로 하는 방법.

### 청구항 41

제 40 항에 있어서,

기판 상에 상기 멀티레이어 구조를 생성하는 단계: 및 상기 멀티레이어 구조로부터 상기 기능 레이어들의 적어 도 일부를 릴리스하는 단계:를 반복하는 단계;를 더 구비하고,

기판 상에 상기 멀티레이어 구조를 생성하는 단계: 및 상기 멀티레이어 구조로부터 상기 기능 레이어들의 적어도 일부를 릴리스하는 단계:를 반복하는 상기 단계 동안에 상기 기판이 재사용되는 것을 특징으로 하는 방법.

#### 청구항 42

광전 디바이스(photovoltaic device)나 디바이스 어레이를 만들기 위한 방법에 있어서, 상기 방법은,

복수의 기능 레이어들과 복수의 릴리스 레이어들을 구비하는 멀티레이어 구조를 제공하는 단계[여기서, 상기 릴리스 레이어들의 적어도 일부는 상기 멀티레이어 구조에서 기능 레이어들 사이에 위치하고, 상기 기능 레이어들의 적어도 일부는 광전 셀(photovoltaic cell)들을 구비함];

1 이상의 상기 기능 레이어들로부터 1 이상의 상기 릴리스 레이어들 또는 상기 릴리스 레이어들의 일부를 분리함으로써 상기 멀티레이어 구조로부터 상기 기능 레이어들의 적어도 일부를 릴리스하여, 복수의 전사가능한 광전 셀들을 생성하는 단계; 및

접촉 프린팅(contact printing) 또는 솔루션 프린팅(solution printing)에 의해, 1 이상의 상기 전사가능한 광전 셀들을 디바이스 기판 또는 디바이스 기판에 의해 지지되는 디바이스 컴포넌트 상에 프린팅하여, 상기 전자디바이스 또는 상기 전자 디바이스 컴포넌트를 만드는 단계;

를 구비하는 것을 특징으로 하는 방법.

### 청구항 43

제 42 항에 있어서,

상기 기능 레이어들의 상기 광전 셀들은 미리 선택된 일련의 반도체 박막들을 구비하는 것을 특징으로 하는 방법.

#### 청구항 44

제 43 항에 있어서,

1 이상의 미리 선택된 마이크로사이즈 또는 나노사이즈 물리적 치수(physical dimension)들을 가지는 상기 전사 가능한 광전 셀들을 생성하기 위해, 적어도 하나의 상기 기능 레이어들에 움푹 들어감 특징(recessed feature) 들을 만드는 단계;

를 더 구비하는 것을 특징으로 하는 방법.

# 청구항 45

디바이스 또는 디바이스 컴포넌트를 만들기 위한 방법에 있어서, 상기 방법은,

기판 표면의 적어도 일부 상에 희생 레이어(sacrificial layer)를 제공하는 단계[상기 희생 레이어는 수신 표면 (receiving surface)을 가짐];

상기 희생 레이어를 패턴화하여 한 패턴의 노출된 기판 표면을 생성하는 단계;

상기 희생 레이어 수신 표면의 적어도 일부 및 노출된 기판 표면 패턴 상에 기능 레이어를 증착하여, 상기 패턴 의 노출된 기판에 상응하는 1 이상의 기능 레이어 앵커(anchor)들을 생성하는 단계; 및

상기 기능 레이어의 적어도 일부를 릴리스하여[여기서, 상기 패턴의 기능 레이어 앵커들은 상기 기판에 적어도 부분적으로 고정된 채로 남아 있고, 상기 기판에 고정되지 않은 상기 기능 레이어의 적어도 일부는 릴리스됨], 복수의 전사가능한 구조들을 생성하는 단계;

를 구비하는 것을 특징으로 하는 방법.

### 청구항 46

제 45 항에 있어서,

1 이상의 상기 전사가능한 구조들을 디바이스 기판 또는 디바이스 기판에 의해 지지되는 디바이스 컴포넌트 상 에 프린팅하는 단계;

를 더 구비하는 것을 특징으로 하는 방법.

### 청구항 47

제 46 항에 있어서,

상기 릴리스하는 단계는,

탄성 스탬프(elastomeric stamp)를 상기 기능 레이어의 적어도 일부에 접촉시키는 단계; 및

상기 기능 레이어와의 접촉으로부터 상기 스탬프를 제거하여, 상기 기판에 고정되지 않은 상기 기능 레이어의 적어도 일부를 제거하는 단계;

를 구비하는 것을 특징으로 하는 방법.

### 청구항 48

제 46 항에 있어서,

상기 릴리스하는 단계는,

상기 디바이스 기판 표면을 상기 기능 레이어의 적어도 일부에 접촉시키는 단계; 및

상기 기능 레이어와의 접촉으로부터 상기 디바이스 기판 표면을 제거하여, 상기 기판에 고정되지 않은 상기 기능 레이어의 적어도 일부를 상기 디바이스 기판 또는 상기 디바이스 기판 표면에 의해 지지되는 디바이스 컴포 넌트로 전사하는 단계;

를 구비하는 것을 특징으로 하는 방법.

### 청구항 49

제 45 항에 있어서,

상기 릴리스하는 단계는,

상기 희생 레이어를 에칭하는 단계:

상기 희생 레이어에 열적으로 충격을 주는(thermally shocking) 단계:

상기 희생 레이어를 레이저 소스(laser source)로부터의 방사(radiation)에 노출시켜 애블레이팅(ablating) 또는 분해하는 단계: 그리고

상기 희생 레이어를 화학 약품에 접촉시켜 상기 희생 레이어를 분해하는 단계:로 이루어진 그룹으로부터 선택되는 기법을 이용하는 것을 특징으로 하는 방법.

### 청구항 50

제 45 항 내지 제 49 항 중의 어느 한 항에 있어서,

상기 기능 레이어는 멀티레이어 구조의 일부인 것을 특징으로 하는 방법.

### 청구항 51

멀티레이어 어레이(multilayer array)에 제공되는 복수의 전사가능한 반도체 엘리먼트들을 제작(fabricating)하기 위한 방법에 있어서, 상기 방법은,

외부 표면을 가지는 웨이퍼를 제공하는 단계[상기 웨이퍼는 무기질 반도체를 구비함];

상기 외부 표면에 제 1 마스크를 제공함으로써 상기 외부 표면의 선택된 영역들을 마스킹하여, 상기 웨이퍼의

상기 외부 표면의 마스킹된 영역(masked region)들 및 마스킹되지 않은 영역(unmasked region)들을 생성하는 단계;

상기 웨이퍼의 상기 외부 표면의 상기 마스킹되지 않은 영역들을 에칭하여, 상기 외부 표면으로부터 상기 웨이퍼 내부로 확장하는 복수의 돋을새김 특징(relief feature)들을 생성하는 단계[여기서, 상기 돋을새김 특징들 각각의 적어도 일부는 적어도 하나의 윤곽 측면(contoured side surface)을 가지고, 그 윤곽 측면은 상기 적어도 하나의 측면의 길이를 따라 공간적으로 변하는 윤곽 모양(contour profile)을 가짐];

제 2 마스크를 제공함으로써 상기 윤곽 측면들을 마스킹하여[여기서, 상기 윤곽 측면은 상기 제 2 마스크에 의해 부분적으로만 마스킹됨], 상기 측면들의 길이를 따라 제공되는 마스킹된 영역들 및 마스킹되지 않은 영역들 생성하는 단계; 및

상기 측면들의 마스킹되지 않은 영역들을 에칭하여, 상기 멀티레이어 어레이에 제공되는 상기 복수의 전사가능 한 반도체 엘리먼트들을 생성하는 단계;

를 구비하는 것을 특징으로 하는 방법.

### 청구항 52

제 51 항에 있어서,

상기 웨이퍼는 벌크 반도체 웨이퍼(bulk semiconductor wafer)인 것을 특징으로 하는 방법.

### 청구항 53

제 51 항에 있어서,

상기 웨이퍼는 (111) 방위(orientation)를 가지는 실리콘 웨이퍼인 것을 특징으로 하는 방법.

#### 청구항 54

제 51 항에 있어서,

상기 웨이퍼의 상기 외부 표면의 상기 마스킹되지 않은 영역들을 에칭하는 단계는,

상기 움푹 들어감 특징(recessed feature)들의 측면들을 에칭액(etchant)들과 에칭 저항 물질(etch resist material)들에 주기적으로 노출시킴으로써 실행되는 것을 특징으로 하는 방법.

# 청구항 55

제 54 항에 있어서,

상기 에칭하는 단계는,

상기 움푹 들어감 특징(recessed feature)들의 측면들을 반응성 이온 에칭액(reactive ion etchant)들과 에칭 저항 물질(etch resist material)들에 주기적으로 노출시킴으로써 실행되는 것을 특징으로 하는 방법.

## 청구항 56

제 54 항에 있어서,

상기 에칭하는 단계는,

유도성으로 결합된 플라즈마 반응성 이온 에칭(ICPRIE: Inductively Coupled Plasma Reactive Ion Etching), 버퍼 산화물 에칭액(BOE: Buffered Oxide Etchant) 또는 유도성으로 결합된 플라즈마 반응성 이온 에칭(ICPRIE) 기법과 버퍼 산화물 에칭액(BOE) 에칭 기법 양자(both)의 조합을 이용하여 실행되는 것을 특징으로 하는 방법.

#### 청구항 57

제 51 항에 있어서,

상기 윤곽 측면(contoured side surface)들의 상기 윤곽 모양(contour profile)들은 상기 측면들의 길이들의

세로축(longitudinal axis)을 교차하는 길이들을 확장하는 복수의 특징들을 가지는 것을 특징으로 하는 방법.

#### 청구항 58

제 57 항에 있어서,

상기 윤곽 모양(contour profile)들의 상기 특징들은, 상기 측면들 상에 제공되는 릿지(ridge)들: 리플(ripple)들: 및 부채 형상의 움푹 들어감 특징(scalloped shaped recessed feature)들:로 이루어진 그룹으로부터 선택되는 것을 특징으로 하는 방법.

### 청구항 59

제 56 항 내지 제 58 항 중의 어느 한 항에 있어서,

상기 릿지(ridge)들, 리플(ripple)들 또는 부채 형상의 움푹 들어감 특징(scalloped shaped recessed feature)들은, 상기 제 2 마스크를 제공함으로써 상기 윤곽 측면들을 마스킹하여 상기 측면들의 상기 마스킹되지 않은 영역들을 생성하는 단계 동안에, 전조 마스크(shadow mask)들로서 기능하는 것을 특징으로 하는 방법.

### 청구항 60

제 51 항에 있어서,

제 2 마스크를 제공함으로써 상기 윤곽 측면들을 마스킹하는 단계는,

마스크 물질의 경사진 증기 증착(angled vapor deposition)을 통해 실행되는 것을 특징으로 하는 방법.

### 청구항 61

제 51 항에 있어서,

상기 측면들의 마스킹되지 않은 영역들을 에칭하는 단계는 이방성 에칭(anisotropic etching)을 통해 실행되는 것을 특징으로 하는 방법.

# 청구항 62

제 61 항에 있어서,

상기 웨이퍼는 (111) 방위(orientation)를 가지는 실리콘 웨이퍼이고,

상기 측면들의 마스킹되지 않은 영역들을 에칭하는 단계는 선택적으로(preferentially) 상기 실리콘 웨이퍼의 <110> 방향들을 따르는 이방성 에칭을 통해 실행되는 것을 특징으로 하는 방법.

### 청구항 63

제 61 항에 있어서,

상기 이방성 에칭은 상기 측면의 마스킹되지 않은 영역들을 강한 염기(strong base)에 노출시킴에 의해 제공되는 것을 특징으로 하는 방법.

### 청구항 64

제 51 항에 있어서,

상기 측면들의 마스킹되지 않은 영역들을 에칭하는 단계는 상기 전사가능한 반도체 엘리먼트들을 생성하고,

상기 엘리먼트들 각각은 브릿지 엘리먼트(bridge element)를 통해 상기 웨이퍼에 연결되는 것을 특징으로 하는 방법.

# 청구항 65

제 51 항에 있어서,

상기 제 1 마스크, 상기 제 2 마스크 또는 그 둘 다(both)는 에칭 저항성 마스크(etch resistant mask)인 것을 특징으로 하는 방법.

### 청구항 66

기판 상에 복수의 전사가능한 반도체 엘리먼트들을 어셈블링(assembling)하는 방법에 있어서, 상기 방법은,

제 51 항의 멀티레이어 어레이에 제공되는 상기 복수의 전사가능한 반도체 엘리먼트들을 제공하는 단계;

상기 기판 상에 상기 전사가능한 반도체 엘리먼트들을 프린팅하는 단계;

를 구비하는 것을 특징으로 하는 방법.

### 청구항 67

전자 디바이스 또는 전자 디바이스의 컴포넌트를 만드는 방법에 있어서, 상기 방법은,

제 51 항의 멀티레이어 어레이에 제공되는 상기 복수의 전사가능한 반도체 엘리먼트들을 제공하는 단계;

기판 상에 상기 전사가능한 반도체 엘리먼트들을 프린팅하여, 상기 전자 디바이스 또는 상기 전자 디바이스의 컴포넌트를 만드는 단계;

를 구비하는 것을 특징으로 하는 방법.

# 청구항 68

제 66 항 또는 제 67 항에 있어서,

상기 프린팅하는 단계는 접촉 프린팅(contact printing)에 의해 실행되는 것을 특징으로 하는 방법.

#### 청구항 69

제 66 항 또는 제 67 항에 있어서,

상기 프린팅하는 단계는,

상기 멀티레이어의 상이한 레이어들에 전사가능한 반도체를 순차적으로(sequentially) 프린팅하는 단계;인 것을 특징으로 하는 방법.

# 청구항 70

제 69 항에 있어서,

상기 어레이의 제 1 레이어에 반도체 엘리먼트들을 프린팅하는 것은 상기 제 1 레이어 아래에 위치하는, 상기 어레이의 한 레이어에서 1 이상의 전사가능한 반도체 엘리먼트들을 노출시키는 것을 특징으로 하는 방법.

## 청구항 71

멀티레이어 어레이의 전사가능한 반도체 엘리먼트들을 생성하기 위한 방법에 있어서, 상기 방법은,

외부 표면을 가지는 기판을 제공하는 단계;

상기 기판의 상기 외부 표면에 의해 지지되는 멀티레이어 구조를 제공하는 단계[여기서, 상기 멀티레이어 구조 는 일련의 교호하는(alternating) 반도체 레이어들과 희생 레이어들을 구비함];

상기 멀티레이어 구조로부터 물질을 제거함으로써 1 이상의 움푹 들어감 특징(recess feature)들을 생성하는 단계; 및

상기 1 이상의 움푹 들어감 특징(recess feature)들에 이질적 앵커 엘리먼트(heterogeneous anchor element)를 증착 또는 코팅하여, 상기 반도체 레이어들 각각의 적어도 일부를 상기 기판 외부 표면, 또는 상기 멀티레이어 구조의 반도체 상단-레이어(top-layer) 아래의 1 이상의 반도체 레이어들, 또는 그 둘 다(both)에 고정시키는 단계;

를 구비하는 것을 특징으로 하는 방법.

### 청구항 72

제 71 항에 있어서,

상기 움푹 들어감 특징은 상기 멀티레이어 구조의 상단 레이어로부터 상기 기판 외부 표면으로 횡단하여 (traverse) 상기 기판 외부 표면의 영역들을 노출시키고,

상기 이질적 앵커 엘리먼트는 상기 반도체 레이어들 각각을 상기 기판 외부 표면에 고정시키는 것을 특징으로 하는 방법.

### 청구항 73

제 71 항에 있어서,

상기 움푹 들어감 특징은 상기 멀티레이어 구조의 제 1 반도체 상단 레이어로부터 상기 상단 레이어 아래의 제 2 반도체 레이어로 횡단하고(traverse),

상기 이질적 앵커 엘리먼트는 상기 제 1 반도체 레이어를 상기 제 2 반도체 레이어에 고정시키는 것을 특징으로 하는 방법.

# 청구항 74

제 71 항 내지 제 73 항 중의 어느 한 항에 있어서,

상기 증착 또는 코팅하는 단계는,

기상 에피택시(vapor-phase epitaxy): 분자-빔 에피택시(molecular-beam epitaxy): 증발식 증착(evaporation deposition): 금속유기질 화학적 증기 증착(metalorganic chemical vapor deposition): 화학적 증기 증착(chemical vapor deposition): 화학적 증기 증착(chemical vapor deposition): 스퍼터링 증착(sputtering deposition): 졸-겔 코팅(sol-gel coating): 전자 빔 증발식 증착(electron beam evaporation deposition): 플라즈마-강화 화학적 증기 증착(plasma-enhanced chemical vapor deposition): 원자 레이어 증착(atomic layer deposition): 액상 에피택시(liquid phase epitaxy): 전기화학적 증착(electrochemical deposition): 및 스핀 코팅(spin coating):으로 이루어진 그룹으로부터 선택되는 기법을 이용하여 실행되는 것을 특징으로 하는 방법.

### 청구항 75

제 73 항에 있어서,

상기 제 1 반도체 상단 레이어 아래에 있는 상기 희생 레이어를 선택적으로 제거하는 단계;

상기 제 1 반도체 상단 레이어를 릴리스하는 단계;

상기 앵커 엘리먼트를 제거하는 단계; 및

상기 생성하는 단계와 상기 중착하는 단계를 반복하여, 상기 제 2 반도체 레이어를 상기 제 2 반도체 레이어 아래에 있는 제 3 반도체 레이어에 고정시키는 단계;

를 더 구비하는 것을 특징으로 하는 방법.

### 청구항 76

제 75 항에 있어서,

상기 프로세스는 모든 반도체 레이어들이 상기 기판 외부 표면으로부터 제거될 때까지 반복되는 것을 특징으로 하는 방법.

### 청구항 77

제 76 항에 있어서,

상기 기판은 웨이퍼를 구비하고,

제 2 멀티레이어 구조를 지지하기 위해 상기 기판이 재사용되는 것을 특징으로 하는 방법.

### 청구항 78

제 72 항에 있어서,

상기 희생 레이어들을 제거하는 단계;

상기 반도체 레이어들을 릴리스하는 단계;

상기 앵커 엘리먼트들을 제거하는 단계; 및

상기 기판의 상기 외부 표면에 의해 지지되는 제 2 멀티레이어 구조를 제공함으로써 상기 기판을 재사용하고, 상기 반도체 레이어들 각각을 상기 기판 외부 표면에 고정시키는 앵커(anchor)를 생성하기 위한 단계들을 반복 하는 단계;

를 더 구비하는 것을 특징으로 하는 방법.

# 청구항 79

기판에 고정된 전사가능한 반도체 엘리먼트를 만드는 방법에 있어서, 상기 방법은,

상기 기판의 외부 표면에 의해 지지되는 상기 전사가능한 반도체 엘리먼트를 생성하는 단계;

상기 전사가능한 반도체 엘리먼트와 물리적으로 접촉하는, 그리고 상기 기판 또는 그 기판 상에 제공되는 구조와 물리적으로 접촉하는 이질적 앵커 엘리먼트를 제공하여, 상기 반도체 엘리먼트를 상기 기판에 고정시키는 단계;

를 구비하는 것을 특징으로 하는 방법.

### 청구항 80

제 79 항에 있어서,

상기 이질적 앵커 엘리먼트를 제공하는 단계는,

상기 기판의 일부를 덮는 한 레이어의 물질을 증착 또는 코팅하는 단계;

를 구비하는 것을 특징으로 하는 방법.

# 청구항 81

제 80 항에 있어서,

상기 레이어는 상기 기판의 상기 외부 표면의 일부를 덮는 것을 특징으로 하는 방법.

### 청구항 82

제 80 항에 있어서,

상기 전사가능한 반도체 엘리먼트를 생성하는 단계는, 상기 외부 표면 또는 그 외부 표면 상에 제공되는 구조의 1 이상의 노출된 영역들을 노출시키고,

상기 이질적 앵커 엘리먼트를 제공하는 단계는, 상기 외부 표면 또는 그 외부 표면 상에 제공되는 구조의 상기 노출된 영역들의 적어도 일부 상에 상기 레이어를 증착 또는 코팅하는 단계;를 구비하는 것을 특징으로 하는 방법.

### 청구항 83

제 80 항에 있어서,

상기 레이어의 물질은 박막 구조(thin film structure)를 구비하는 것을 특징으로 하는 방법.

# 청구항 84

제 80 항에 있어서,

상기 레이어의 물질은 저항 물질(resist material)을 구비하는 것을 특징으로 하는 방법.

### 청구항 85

제 80 항에 있어서,

상기 레이어의 물질은 SiN 또는 PECVD 절연체를 구비하는 것을 특징으로 하는 방법.

#### 청구항 86

제 80 항에 있어서,

상기 레이어의 물질은, 상기 전사가능한 반도체 엘리먼트의 한 측면에 접촉하도록 제공되고 그리고 상기 전사가능한 반도체 엘리먼트의 한 측면을 따라 확장하며,

상기 레이어의 물질은, 상기 기판 또는 그 기판 상에 제공되는 구조의 상기 외부 표면에서 종결하고 그리고 상기 기판 또는 그 기판 상에 제공되는 구조의 상기 외부 표면과 접촉하는 것을 특징으로 하는 방법.

### 청구항 87

제 86 항에 있어서,

상기 레이어의 물질은, 상기 전사가능한 반도체 엘리먼트의 한 측면을 상기 기판 또는 그 기판 상에 제공되는 구조의 상기 외부 표면에 연결하는 포스트 구조(post structure)를 구비하는 것을 특징으로 하는 방법.

### 청구항 88

제 79 항에 있어서,

상기 전사가능한 반도체 엘리먼트는 단일 반도체 레이어를 구비하는 것을 특징으로 하는 방법.

### 청구항 89

제 79 항에 있어서,

상기 전사가능한 반도체 엘리먼트는 복수의 반도체 레이어들을 가지는 멀티레이어 구조를 구비하는 것을 특징으로 하는 방법.

### 청구항 90

제 79 항에 있어서,

상기 전사가능한 반도체 엘리먼트를 생성하는 단계는, 상기 기판의 외부 표면에 의해 지지되는, 멀티레벨 어레이의 전사가능한 반도체 엘리먼트들을 제공하는 단계;를 구비하고,

상기 이질적 앵커 엘리먼트를 제공하는 단계는, 상기 멀티레이어 어레이에서 상기 전사가능한 반도체 엘리먼트들의 측면들에 접촉하고 그리고 상기 기판 또는 그 기판 상에 제공되는 구조의 상기 외부 표면의 일부에 접촉하는 한 레이어의 물질을 증착 또는 코팅하는 단계;를 구비하는 것을 특징으로 하는 방법.

# 청구항 91

제 79 항에 있어서,

상기 이질적 앵커 엘리먼트는 에칭 방지 레이어(etch stop layer)로서 기능하는 것을 특징으로 하는 방법.

### 청구항 92

전사가능한 반도체 엘리먼트를 어셈블링(assembling)하는 방법에 있어서, 상기 방법은,

제 79 항의 상기 기판에 고정된 전사가능한 반도체 엘리먼트를 제공하는 단계;

상기 전사가능한 반도체 엘리먼트를 프린팅(printing)에 의해 디바이스 기판 상으로 전사하는(transferring) 단계;

를 구비하는 것을 특징으로 하는 방법.

### 청구항 93

제 92 항에 있어서,

상기 전사가능한 반도체 엘리먼트를 프린팅에 의해 상기 디바이스 기판 상으로 전사하는 단계는, 접촉 프린팅 (contact printing)에 의해 실행되는 것을 특징으로 하는 방법.

### 청구항 94

제 93 항에 있어서,

상기 전사가능한 반도체 엘리먼트를 프린팅에 의해 상기 디바이스 기판 상으로 전사하는 단계는,

상기 전사가능한 반도체 엘리먼트를 접촉 표면을 가지는 전사 디바이스(transfer device)에 접촉시키는 단계[여기서, 상기 접촉 표면과 상기 전사가능한 반도체 엘리먼트 간의 접촉은 상기 전사가능한 반도체 엘리먼트를 상기 접촉 표면에 결속시킴]:

상기 이질적 앵커링 엘리먼트를 분쇄하는 방식으로 상기 전사 디바이스를 이동시킴으로써, 상기 전사가능한 반도체 구조를 상기 기판으로부터 상기 전사 디바이스로 전사하여, 상기 전사가능한 반도체 엘리먼트를 가지는 상기 접촉 표면을 형성하는 단계[상기 전사가능한 반도체 엘리먼트는 상기 접촉 표면 상에 배치됨]:

상기 접촉 표면 상에 배치되는 상기 전사가능한 반도체 엘리먼트를 상기 디바이스 기판의 수신 표면(receiving surface)에 접촉시키는 단계: 그리고

상기 적합성 전사 디바이스(conformable transfer device)의 상기 접촉 표면과 상기 전사가능한 반도체 엘리먼트를 분리하여[여기서, 상기 전사가능한 반도체 엘리먼트는 상기 수신 표면 상으로 전사됨], 상기 전사가능한 반도체 엘리먼트를 상기 기판의 상기 수신 표면 상에 어셈블링(assembling)하는 단계:

에 의해 실행되는 것을 특징으로 하는 방법.

# 청구항 95

디바이스를 만드는 방법에 있어서, 상기 방법은,

제 71 항의 상기 기판에 고정된 전사가능한 반도체 엘리먼트를 제공하는 단계;

상기 전사가능한 반도체 엘리먼트를 프린팅에 의해 디바이스 기판 상으로 전사하는 단계;

를 구비하는 것을 특징으로 하는 방법.

#### 청구항 96

제 95 항에 있어서,

상기 전사가능한 반도체 엘리먼트를 프린팅에 의해 상기 디바이스 기판 상으로 전사하는 단계는, 접촉 프린팅 (contact printing)에 의해 실행되는 것을 특징으로 하는 방법.

### 청구항 97

제 96 항에 있어서,

상기 전사가능한 반도체 엘리먼트를 프린팅에 의해 상기 디바이스 기판 상으로 전사하는 단계는,

상기 전사가능한 반도체 엘리먼트를 접촉 표면을 가지는 전사 디바이스(transfer device)에 접촉시키는 단계[여기서, 상기 접촉 표면과 상기 전사가능한 반도체 엘리먼트 간의 접촉은 상기 전사가능한 반도체 엘리먼트를 상기 접촉 표면에 결속시킴]:

상기 이질적 앵커링 엘리먼트를 분쇄하는 방식으로 상기 전사 디바이스를 이동시킴으로써, 상기 전사가능한 반도체 구조를 상기 기판으로부터 상기 전사 디바이스로 전사하여, 상기 전사가능한 반도체 엘리먼트를 가지는 상기 접촉 표면을 형성하는 단계[상기 전사가능한 반도체 엘리먼트는 상기 접촉 표면 상에 배치됨]:

상기 접촉 표면 상에 배치되는 상기 전사가능한 반도체 엘리먼트를 상기 디바이스 기판의 수신 표면(receiving surface)에 접촉시키는 단계: 그리고

상기 적합성 전사 디바이스(conformable transfer device)의 상기 접촉 표면과 상기 전사가능한 반도체 엘리먼

트를 분리하여[여기서, 상기 전사가능한 반도체 엘리먼트는 상기 수신 표면 상으로 전사됨], 상기 전사가능한 반도체 엘리먼트를 상기 기판의 상기 수신 표면 상에 어셈블링(assembling)하는 단계:

에 의해 실행되는 것을 특징으로 하는 방법.

### 명 세 서

# 기술분야

- <1> [CROSS-REFERENCE TO RELATED APPLICATIONS]

- <2> 본 출원은 2006년 9월 20일 미국에 출원된 임시출원 US 60/826,354와 2007년 6월 18일 미국에 출원된 임시출원 US 60/944,653의 우선권 이익을 주장한다. 그 임시출원들 각각은 본 개시와 일치하는 범위만큼 참조에 의해 여기에 병합된다.

# 배경기술

디바이스 기판(device substrate)들 및 그 디바이스 기판들에 의해 지지되는 디바이스 컴포넌트(device component)들 상에 구조들[나노구조(nanostructure)들, 마이크로구조(microstructure)들, 연성 전자소자들 (flexible electronics), 및 다양한 다른 패턴 구조(patterned structure)들을 포함함]을 프린팅(printing)함에 있어서 다양한 플랫폼(platform)들이 이용가능하다. 예를 들어, 다수의 특허들 및 특허출원들이 넓은 범위의 구조들을 만들고 프린팅하기 위한 상이한 방법들 및 시스템들을 설명한다. 그러한 특허들 및 특허출원들로서 미국 특허출원 제11/115,954호(18-04. 2005년 4월 27일 출원), 제11/145,574호(38-04A. 2005년 6월 2일 출원), 제11/145,542호(38-04B. 2005년 6월 2일 출원), 제11/1423,287호(38-04C. 2006년 6월 9일 출원), 제11/423,192호(41-06. 2006년 6월 9일 출원), 제11/421,654호(43-06. 2006년 6월 1일 출원), 그리고 미국 특허 제60/826,354호(151-06P. 2006년 9월 20일 출원)가 있으며, 이들 각각은 여기의 개시와 일치하는 범위만큼 참조에 의해 여기에 병합된다. 전사가능한 반도체 엘리먼트(transferable semiconductor element)들을 생성하기 위한 방법들 및 구조들에 대한 요구가 현재 존재한다. 디바이스와 디바이스 컴포넌트들을 만들기 위한 높은 처리율 (high-throughput)의 프로세싱과 양립가능한 낮은 비용의 방법들 및 구조들이 특히 요구된다.

## 발명의 상세한 설명

- <4> [SUMMARY OF THE INVENTION]

- C1바이스 기판들 상에 프린팅될 수 있는 구조들 또는 디바이스 기판들 상에 프린팅될 수 있는 디바이스 컴포넌 트들을 저비용으로 생성하는 것을 촉진하기 위한 방법들 및 관련 시스템들이 제공된다. 이것은 개별적인 레이어 들로의 접근을 제공하도록 구성되는 멀티레이어 구조 스택들을 제공함으로써 달성된다. 기능 레이어들인 개별적인 레이어들이 특히 유용하며, 그 기능 레이어들은 디바이스 및 다비이스 컴포넌트들로 계속해서 통합된다. 순 차적으로 한 레이어씩 접근하는 방식 또는 2 이상의 레이어들을 동시에 접근하는 방식을 제공하는 릴리스 방안들에 의해 개별적인 레이어들이 접근된다. 그 기능 레이어들은 넓은 범위의 프린팅 방법들 및 시스템들에 의해 디바이스들 또는 디바이스 컴포넌트들로 프린트되거나 통합될 수 있다. 이 멀티레이어 스택 시스템들은, 단일 프로세스에서 다수의 레이어들에 포함된 다수의 프린트가능(printable) 또는 전사가능(transferable) 기능 구조들을 생성하여, 프린트가능 또는 전사가능 구조나 레이어당(per) 비용을 줄이고 목적 디바이스 또는 디바이스 컴포넌트의 최종 비용을 줄일 수 있는 능력을 제공한다.

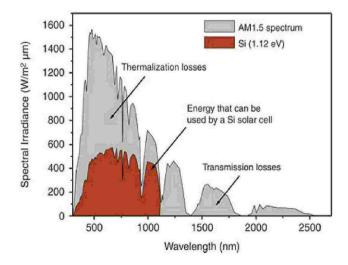

- (6> 일 측면에서, 본 발명은 광전소자의 솔라 셀(solar cell)로 통합될 수 있는 복수의 기능 레이어들을 가지는 멀티레이어 구조들에 의해 저비용 및/또는 고성능 광전소자들을 만들기 위한 방법들을 제공한다. 이 멀티레이어 접근법은 많은 이유들로 인해 유리하다. 예를 들어, 다수의 솔라 셀들이 단일 증착 실행에서 성장될 수 있고, 그럼으로써 성장 챔버(growth chamber)들의 로딩(loading)과 언로딩(unloading), 성장 기판 표면 준비, 및 단일 레이어 제작 접근법들에 의해 현재 요구되는 버퍼 레이어들의 증착을 회피할 수 있다. 이것은 솔라 셀 레이어당(per) 제조 비용의 측면에서 현저한 감소를 가져올 수 있고, 그럼으로써 솔라 셀 디바이스 컴포넌트에 대한 비용을 줄일 수 있다. 또한, 모 기판(mother substrate)으로부터 기능 레이어들을 완전히 들어 올릴 수 있는 (lifting-off) 능력은 동일한 모 기판 상에 추가적인 멀티레이어 구조들을 구성함으로써 모 기판을 재사용할 수 있는 능력을 제공한다. 더하여, 멀티레이어 구성은 용이하게 열을 소산시키고(easily heat sunk), 플라스틱들 및 넓은 범위의 형성 인자(form factor)들을 가지는 다른 기판들로 쉽게 프린팅될 수 있는 전사가능한 구조들을

제공할 수 있다.

- <7> 일 실시예에서, 복수의 기능 레이어들과 복수의 릴리스 레이어들을 가지는 멀티레이어 구조를 제공함으로써 디바이스 또는 디바이스 컴포넌트를 만들기 위한 방법이 제공된다. 이 구성에 있어서, 그 릴리스 레이어들의 적어도 일부는 기능 레이어들로의 접근을 제공하기 위해 기능 레이어들의 사이에 위치한다. 기능 레이어들의 적어도 일부는 1 이상의 기능 레이어들로부터 1 이상의 릴리스 레이어들 또는 그 릴리스 레이어들의 일부를 분리함으로써 멀티레이어 구조로부터 릴리스된다. 이 기능 레이어 릴리스는 기판 상으로 프린팅될 수 있는 구조를 생성한다.

- 전촉 프린팅과 같이 이 분야에서 알려진 어떤 프린팅 수단[예컨대, 접촉 프린팅(contact printing), 액체 프린팅(liquid printing), 건식 전사 접촉 프린팅(dry transfer contact printing), 소프트 리소그래피 마이크로전사 프린팅(soft lithographic microtransfer printing) 및 소프트 리소그래피 나노전사 프린팅(soft lithographic nanotransfer printing), 솔루션 프린팅(solution printing), 유체 셀프 어셈블리(fluidic self assembly), 잉크 젯 프린팅(ink jet printing), 열적 전사 프린팅(thermal transfer printing) 그리고 스크린 프린팅(screen printing)]에 의해, 1 이상의 전사가능한 구조들을 디바이스 기판 또는 디바이스 기판에 의해 지지되는 디바이스 컴포넌트 상에 프린팅함으로써, 디바이스 또는 디바이스 컴포넌트가 만들어진다.

- <9> 릴리스(release)는 널리 사용되며, 멀티레이어 구조에서 어느 레이어의 적어도 일부를 다른 레이어들로부터 분 리하기 위한 어떤 수단을 가리킨다. 예를 들어, 멀티레이어 하위구조(multilayer substructure)로부터 기능 레 이어의 적어도 일부를 릴리스하는 단계는 적어도 한 쌍의 인접 레이어들을 물리적으로 분리하는 것일 수 있다. 그 인접 레이어들은 멀티레이어 구조에서 기능 레이어에 인접하는 릴리스 레이어일 수 있다. 릴리스 레이어는 릴리스 자극(release stimulus)에 응답하여 기능 레이어의 적어도 일부를 릴리스하는 것을 촉진하도록 구성된다. 예를 들어, 릴리스 자극은 릴리스 레이어의 적어도 일부를 제거하여 인접 기능 레이어의 릴리스를 촉 진하는 화학적 또는 물리적 자극을 구비할 수 있다. 그러나, 타겟 릴리스 레이어에 영향을 미칠 수 있는 어떤 자극이 사용될 수도 있다. 릴리스 단계들의 다른 예시들은 1 이상의 릴리스 레이어들을 에칭하는 것, 1 이상의 릴리스 레이어들에 열적으로 충격을 주는 것(thermally shocking), 릴리스 레이어들을 레이저 소스(laser source)로부터의 전자기적 방사(electromagnetic radiation)에 노출시켜 1 이상의 릴리스 레이어들을 애블레이 팅(ablating)하는 것, 그리고 릴리스 레이어들을 화학 약품에 접촉시켜 1 이상의 릴리스 레이어들을 분해하는 것을 포함한다[그러나, 그것들로만 한정되는 것은 아니다]. 일 측면에서, 기능 레이어들은 그 레이어의 말단들 에 위치하는 앵커링 수단(anchoring means)에 의해 인접 레이어들에 연결되고, 그래서 기능 레이어를 들어 올리 기 위한 그 말단들에서의 언더컷팅(undercutting)에 의해 릴리스가 달성된다. 대안적으로, 앵커(anchor)들이 패 턴들로서 희생 레이어 또는 릴리스 레이어에 제공되어, 기판 또는 인접 레이어에 고정된 앵커들이 제공된다. 이 앵커들은 끊길 수 있는 테더 포인트들(breakable tether point)을 설계함에 있어서의 추가적 유연성 (flexibility)을 제공하여 기능 레이어 부분들의 제어된 들어 올림(controlled lift-off)을 촉진한다. 선택적으 로, 여기에 개시되는 어떤 방법들에서, 들어 올려진 기능 레이어에 고정된 채로 남아 있는 레이어들이 제거된다. 일 측면에서, 들어 올림(lift-off)은 멀티레이어 구조를 탄성 스탬프(elastomeric stamp)와 같은 스 탬프에 접촉시킴으로써 달성된다. 선택적으로, 들어 올림 구조(lift-off structure)를 표면에 접촉 프린팅하는 것을 촉진하기 위해 스탬프가 이용된다.

- <10> 릴리스 레이어로 계기(signal)를 전송하는 것을 촉진하기 위해서, 그 계기(signal)가 통과하는 어떤 1 이상의 기능 레이어들은 그 계기(signal)를 적어도 부분적으로 전송할 수 있다. 예를 들어, 전자기적 방사 (electromagnetic radiation)인 어느 계기(signal)에 대하여, 기능 레이어들은 릴리스 레이어들의 적어도 일부를 애블레이팅할 수 있는 그 전자기적 방사에 대해 적어도 부분적으로 투명(transparent)하다. 대안적으로, 전자기적 방사가 반대 측면[예컨대, 멀티레이어 구조를 지지하는 기판의 다른 측면]으로부터 전송되는 경우에는, 기판이 그 전자기적 방사에 대해 적어도 부분적으로 투명하다.

- <11> 릴리스를 위한 다른 수단은 릴리스 레이어에 위치하는 계면 크랙(interfacial crack)이다. 그러한 크랙은 시스템에[예컨대, 릴리스 레이어에] 압력(stress)을 인가함으로써 1 이상의 기능 레이어들을 들어 올리는 것을 촉진한다. 그 크랙은 이 분야에서 알려진 어떠한 수단[화학적 또는 열적으로 생성된 힘]에 의해 도입될 수 있다[그러나, 그것들로만 한정되는 것은 아니다].

- <12> 일 측면에서, 여기에 개시되는 어떤 방법들은 멀티레이어 구조의 적어도 일부를 마스킹하는 단계를 더 포함할 수 있다. 예를 들어, 마스크 레이어가 1 이상의 기능 레이어들과 물리적으로 접촉한다. 그러한 마스크들은, 1 이상의 기능 레이어들이 멀티레이어 구조로부터 기능 레이어들의 적어도 일부를 릴리스하기 위해 릴리스 계기

(release signal)로서 제공되는 에칭액(etchant), 솔벤트(solvent) 또는 화학 약품(chemical agent)에 노출되는 것을 적어도 부분적으로 방지할 수 있다. 기능 레이어가 고품질 레이어[에칭액과 같은 릴리스 계기(release signal)에 의해 쉽게 손상되며 매우 비싼 고품질 레이어]인 어플리케이션들에서 그러한 마스크가 유용할 것이다.

- <13> 다른 측면에서, 멀티레이어 하위구조(multilayer substructure)로부터 기능 레이어들의 적어도 일부를 릴리스하는 단계를 더 촉진하기 위해, 캐리어 필름(carrier film)이 1 이상의 기능 레이어들과 접촉하도록 제공된다.

- <14> 여기에 제공되는 방법들과 시스템들은 넓은 범위의 외형(geometry)을 가지는 넓은 범위의 전사가능한 구조들을 생성하는 데 유용하다. 따라서, 본 방법은 넓은 범위의 디바이스를 위한 다수의 디바이스 제조 프로세스들 및 디바이스 컴포넌트 제조에 통합될 수 있다. 일 측면에서, 그 전사가능한 구조는 레이어-타입 외형(layer-type geometry)을 가진다. 다른 측면에서, 적어도 하나의 기능 레이어들이 1 이상의 미리 선택된 마이크로사이즈 또는 나노사이즈 물리적 치수(physical dimension)들을 가지는 전사가능한 구조들을 생성하도록, 이 분야에서 알려진 어떤 방법에 의해 움푹 들어감 특징(recessed feature)들이 제공된다. 예를 들어, 적어도 하나의 기능 레이어들에 움푹 들어감 특징(recessed feature)들을 생성하는 것은, 선택적으로 포토리소그래피 (photolithography), 소프트 리소그래피(soft lithography), 전자 빔 직접 기록(electron beam direct writing), 또는 포토애블레이션 패터닝(photoablation patterning)과 같은 패터닝 기법을 사용하여 실행된다.

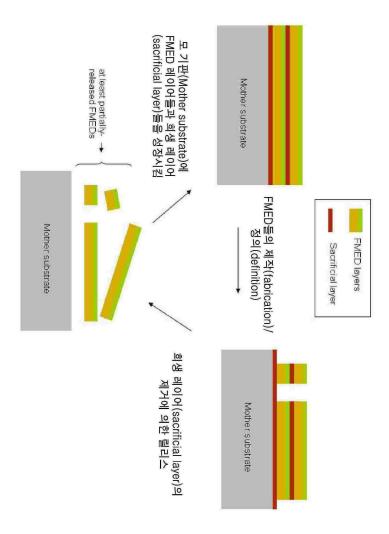

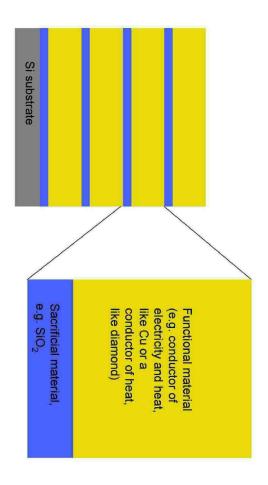

- 본 발명의 기능 레이어는 널리 사용되며, 디바이스 또는 디바이스 컴포넌트 내에서 유용한 물질을 가리킨다. 다양한 디바이스들 및 디바이스 컴포넌트들을 위한 넓은 어플리케이션을 가지는 기능 레이어는 반도체 또는 일런의[예컨대, 복수의] 반도체 레이어들을 가지는 멀티레이어이다. 기능 레이어 구성(composition) 및 외형 (geometry)은 그 기능 레이어의 기능 또는 목적 사용에 의거하여 선택된다. 예를 들어, 그 일련의 반도체 레이어들은, 단결정(single crystalline) 반도체 레이어: 유기질(organic) 반도체 레이어: 무기질(inorganic) 반도체 레이어: III-V 반도체 레이어: 및 그룹 IV 원소 또는 화합물 반도체(elemental or compound semiconductor):로 이루어진 그룹으로부터 선택되는 적어도 하나의 반도체 레이어일 수 있다. 다른 측면에서, 그 일련의 반도체 레이어들은 상이한 반도체 물질들을 가지는 적어도 두 개의 반도체 레이어들이다. 일 측면에서, 적어도 하나의 상기 기능 레이어들은 1 이상의 절연 레이어(dielectric layer)들 또는 1 이상의 전도체 레이어(conductor layer)들로부터 만들어진다. 일 실시예에서, 멀티레이어에서 어느 한 기능 레이어는 다른 기능레이어들과 상이할 수 있다. 일 실시예에서, 멀티레이어에서 모든 기능레이어들이 동일하다. 일 실시예에서, 멀티레이어에서 어느 한 기능 레이어는, 복수의 반도체 레이어들과 같은, 개별적인 레이어들의 복합 레서피(complex recipe)이다. 본 출원의 일부로서 포함된 도면들에서, 이 기능 레이어들로부터 도출되는 구조들은 "기능 물질 엘리먼트들 또는 디바이스들(FMEDs: functional materials elements or devices)"로 지칭된다.

- <16> 여기에 설명되는 어느 방법들에서 유용한 다른 기능 레이어들은 전자적, 광학적 또는 전자-광학적 디바이스나 전자적, 광학적, 전자-광학적 디바이스의 컴포넌트인 기능 레이어들을 포함한다[그러나, 그것들로만 한정되는 것은 아니다]. 그것은 P-N 접합, 박막 트랜지스터, 단일 접합 솔라 셀(single junction solar cell), 다중 접합 솔라 셀, 포토다이오드, 발광 다이오드, 레이저, CMOS 디바이스, MOSFET 디바이스, MESFET 디바이스, 또는 HEMT 디바이스의 일부일 수 있다.

- <17> 일 실시예에서, 어떤 멀티레이어 구조들은 기판 상에 생성된다. 일 측면에서, 기능 레이어와 기판 사이에 위치하는 릴리스 레이어와 같이, 적어도 하나의 릴리스 레이어가 멀티레이어 구조와 기판 사이에 제공된다. 다른 측면에서, 릴리스 레이어는 멀티레이어 구조와 기판 사이에 제공되지 않는다. 그 경우에는, 모 기판(mother substrate) 및/또는 인접 기능 레이어가 그 기판으로부터 기능 레이어를 릴리스할 수 있는 능력을 제공한다. 일 측면에서, 모 기판 자체가 릴리스 레이어이다.

- <18> 멀티레이어 구조 및 구체적으로 그 멀티레이어 구조의 개별적인 레이어들은 이 분야에서 알려진 바와 같이 기판표면 상에 증착 또는 성장될 수 있다. 예를 들어, 표면 상에 레이어들을 성장 또는 증착시키기 위한 1 이상의어떤 수단들은, 에피택설형 성장(epitaxial growth), 증발식 증착(evaporation deposition), 기상 에피택시(vapor-phase epitaxy), 분자-빔 에피택시(molecular-beam epitaxy), 금속유기질 화학적 증기 증착(metalorganic chemical vapor deposition), 화학적 증기 증착(chemical vapor deposition), 물리적 증기 증착(physical vapor deposition), 스퍼터링 증착(sputtering deposition), 졸-겔 코팅(sol-gel coating), 전자 빔 증발식 증착(electron beam evaporation deposition), 플라즈마-강화 화학적 증기 증착(plasma-enhanced chemical vapor deposition), 원자 레이어 증착(atomic layer deposition), 액상 에피택시(liquid phase epitaxy), 전기화학적 증착(electrochemical deposition), 및 스핀 코팅(spin coating)을 포함하는 다양한 기

법들로부터 선택될 수 있다[그러나, 그것들로만 한정되는 것은 아니다]. 그러한 방식으로, 다수의 전사가능한 구조들이 시스템으로부터 생성되며, 최종 기능 레이어[예컨대, 기판 표면에 가장 가까운 레이어]를 릴리스하고 선택적으로 그 기판이 다시 재사용된다. 그러한 재사용은 기판 자체가 손상되거나, 파괴되거나, 또는 최종 디바이스나 디바이스 컴포넌트로 통합되는 제조 프로세스들에 비해서 비용 절감을 불러온다.

- <19> 선택적으로 멀티레이어 구조는, 교호하는(alternating) 릴리스 레이어들과 기능 레이어들과 같이, 기판 상에 에 피택셜형으로 성장되는 미리 선택된 일련의 박막들을 가지는 릴리스 레이어 및/또는 기능 레이어를 포함한다. 일 실시예에서, 기능 레이어들은 약 5mm에서 약 50,000mm에 이르는 범위로부터 선택되는 두께들을 가진다. 일실시예에서, 멀티레이어 구조는 약 2 내지 약 200 개의 기능 레이어들 및/또는 약 2 내지 약 200 개의 릴리스 레이어들을 가진다. 릴리스 레이어는 시스템 구성에 의거하여 1mm 정도로 얇을 수 있다. 다른 실시예들에서, 릴리스 레이어는 더 두꺼울 수 있다[예를 들어, 약 1μm와 2μm 사이]. 릴리스 레이어 물질의 구성에 관한 실제 선택은, 고품질 기능 레이어들을 성장[예컨대, 에피택셜형 성장(epitaxial growth)]시키는 것이 요구되는가와 같은, 다수의 파라미터들에 기초하여 행해진다. 성장이 에피택셜형이 아니라면, 릴리스 레이어 구성 제한이 경감될 수 있다. 또한, 릴리스 레이어 구성은 멀티레이어 구조로부터 기능 레이어들을 릴리스하기 위한 릴리스 방안과 양립가능해야 한다. 예를 들어, 릴리스 메커니즘이 크랙킹(cracking)에 의하면, 최적의 크랙킹을 촉진하기위해 영률(Young's modulus)이 선택될 수 있다.

- <20> 많은 상이한 디바이스들이 여기에 개시되는 어떤 방법들을 이용하여 만들어질 수 있다. 일 측면에서, 본 발명은 광전 디바이스(photovoltaic device)나 디바이스 어레이, 트랜지스터 디바이스나 디바이스 어레이, 발광 다이오 드 디바이스나 디바이스 어레이, 레이저나 레이저 어레이, 센서나 센서 어레이, 집적된 전자 회로, 마이크로전 자기계 디바이스(microelectromechanical device) 또는 나노전자기계 디바이스(nanoelectromechanical device)를 만드는 방법을 제공한다.

- <21> 일 실시예에서, 본 발명의 어떤 방법들은 전사가능한 반도체 구조들을 만들기 위한 것이다. 예를 들어, 전사가능한 반도체 구조들은, 1 이상의 기능 레이어들로부터 1 이상의 릴리스 레이어들 또는 릴리스 레이어들의 일부를 분리함으로써 멀티레이어 구조로부터 기능 레이어들의 적어도 일부를 릴리스하는 것에 의해, 1 이상의 반도체 박막들을 가지는 기능 레이어의 적어도 일부로부터 만들어진다. 비슷하게, 미리 선택된 일련의 반도체 박막들을 가지는 광전 셀(photovoltaic cell)과 같은 광전 셀인 기능 레이어의 적어도 일부를 제공함으로써 광전 디바이스나 디바이스 어레이를 만들기 위한 방법들이 제공된다.

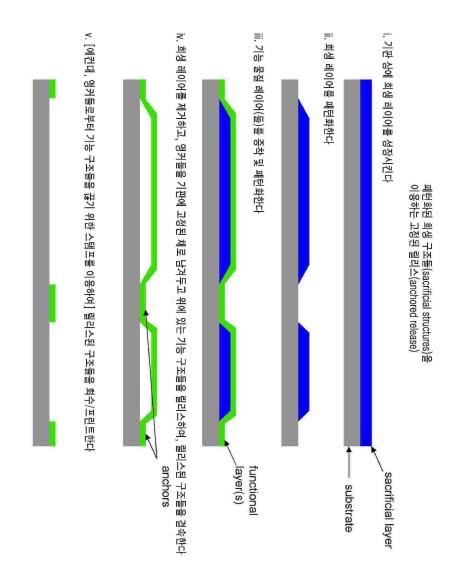

- <22> 다른 실시예에서, 본 발명은 디바이스 또는 디바이스 컴포넌트를 만들기 위한 방법이며, 거기에서 희생 레이어 (sacrificial layer)가 기판 표면의 적어도 일부 상에 제공된다. 희생 레이어는 기판으로부터 기능 레이어를 제 거하는 것을 촉진하는 물질을 가리키기 위해 널리 사용된다. 희생 레이어는 기능 레이어 물질을 수신하기 위한 수신 표면을 가진다. 상응하는 패턴으로 밑에 있는 기판 또는 기판 상의 필름이나 코팅을 드러내기 위해서 이 분야에서 알려진 어떤 수단에 의해 희생 레이어가 선택적으로 패턴화된다. 기능 레이어가 후속적으로 증착될 때 에 노출된 기판의 패턴은 그 기능 레이어의 잠재적 앵커 영역(potential anchor region)들에 상응한다. 특히, 증착된 기능 레이어는 두 영역들을 가진다. 즉, 희생 레이어에서의 패턴화된 영역들에 상응하는 "앵커 영역 (anchor region)"과 밑에 있는 기판으로부터 기능 레이어를 분리하는 희생 레이어가 있는 "비고정 영역 (unanchored region)"을 가진다. 앵커들(anchors)은 비고정 영역에 상응하는 패턴에서 기능 레이어의 제어된 들 어 올림(controlled lift-off)을 촉진하기 위한 브릿지 엘리먼트(bridge element)들로서 기능할 수 있다. 기능 레이어의 일부가 릴리스되고[여기서, 그 패턴의 기능 레이어 앵커(functional layer anchor)들은 기판에 적어도 부분적으로 고정된 채로 남아 있고, 기판에 고정되지 않은 기능 레이어의 적어도 일부가 릴리스됨], 그럼으로써 복수의 전사가능한 구조들을 생성한다. 그 전사가능한 구조들은 선택적으로 디바이스 기판 또는 디바이스 기판 에 의해 지지되는 디바이스 컴포넌트 상으로 프린팅되어, 그 디바이스 또는 그 디바이스 컴포넌트가 만들어진다. 여기에서 설명되는 접촉 프린팅(contact printing) 또는 솔루션 프린팅(solution printing)과 같 은, 이 분야에서 알려진 어떠한 프린팅 수단이 이용될 수 있다.

- <23> 일 실시예에서, 릴리스 단계는 탄성 스탬프(elastomeric stamp)를 기능 레이어의 적어도 일부에 접촉시키는 단계 및 기능 레이어와의 접촉으로부터 스탬프를 제거하여 기판에 고정되지 않은 기능 레이어의 적어도 일부를 제거하는 단계를 구비한다.

- <24> 다른 실시예에서, 릴리스 단계는, 희생 레이어를 에칭하는 단계: 희생 레이어에 열적으로 충격을 주는 (thermally shocking) 단계: 희생 레이어를 레이저 소스(laser source)로부터의 방사(radiation)에 노출시켜 애블레이팅(ablating) 또는 분해하는 단계: 그리고 희생 레이어를 화학 약품에 접촉시켜 희생 레이어를 분해하

는 단계:로 이루어진 그룹으로부터 선택되는 기법을 이용한다. 그러면 그 기능 레이어는 선택적으로 이 분야에서 알려진 어떠한 수단[예컨대, 앵커들로부터 기능 구조들을 선택적으로 끊는 스탬프]에 의해 제거 또는 회수되고, 그럼으로써 희생 레이어에 원래 적용되었던 패턴에 상응할 수 있는 프린팅된 기능 구조(printed functional structure)들이 제공된다.

- ②5> 일 실시예에서, 본 발명의 멀티레이어 프로세스들로 통합되는 앵커들을 제공하기 위해 어떤 패터닝 프로세스들이 여기에 개시된다. 예를 들어, 복수의 기능 물질들 및/또는 기능 레이어들을 제어 가능하게 릴리스하기 위한추가적 수단을 제공하기 위해 기능 레이어들을 분리하는 본 발명의 1 이상의 릴리스 레이어들에 그 패터닝이 적용될 수 있다.

- ○26> 다른 실시예에서, 본 발명은 멀티레이어 어레이에 제공되는 복수의 전사가능한 반도체 엘리먼트들을 제작하기 위한 방법이다. 그러한 프로세스들은 단일 레이어로부터 그리고/또는 다수 레이어들[각각의 레이어가 복수의 엘리먼트들을 생성할 수 있음]로부터 아주 많은 엘리먼트들을 제조하는 것을 제공하며, 또한 추가적인 엘리먼트 프로세싱[밑에 있는 표면에 부착된 엘리먼트들의 프로세싱을 포함]을 위한 능력을 제공한다. 예를 들어, 그 방법은 외부 표면을 가지는 웨이퍼[예컨대, 무기질 반도체를 구비하는 웨이퍼]를 제공하는 단계들을 구비할 수 있다. 그 외부 표면에 제 1 마스크를 제공함으로써 그 외부 표면의 선택된 영역들이 마스킹되어, 그 외부 표면의 마스킹된 영역(masked region)들과 마스킹되지 않은 영역(umasked region)들이 생성된다. 웨이퍼 외부 표면의 마스킹되지 않은 영역들을 에청하는 것에 의해, 외부 표면으로부터 웨이퍼 내부로 확장하는 복수의 돋을새김 특징(relief feature)들이 생성된다. 이러한 방식으로, 돋을새김 특징들 각각의 적어도 일부는 적어도 하나의 윤곽 측면(contoured side surface)을 가지고, 그 윤곽 측면은 적어도 하나의 측면의 길이를 따라 공간적으로 변하는 윤곽 모양(contour profile)을 가진다. 다른 하나의 마스킹 단계에서, 제 2 마스크가 윤곽 측면들을 마스킹한다[여기서, 그 윤곽 측면은 제 2 마스크에 의해 부분적으로만 마스킹됨]. 이것은 측면들의 길이를 따라 제공되는 마스킹된 영역들 및 마스킹되지 않은 영역들을 생성한다. 그 마스킹되지 않은 영역들이 에칭되어, 멀티레이어 어레이에 제공되는 복수의 전사가능한 반도체 엘리먼트들이 생성된다.

- <27> 이 방법들 중의 어떤 것은 선택적으로 벌크 반도체 웨이퍼(bulk semiconductor wafer)인 웨이퍼[예를 들어, (111) 방위(orientation)를 가지는 실리콘 웨이퍼]를 사용한다.

- 28> 일 측면에서, 웨이퍼 외부 표면의 마스킹되지 않은 영역들을 에칭하는 단계는, 움푹 들어감 특징(recessed feature)들의 측면들을 에칭액(etchant)들과 에칭 저항 물질(etch resist material)들에 주기적으로 노출시킴 [예컨대, 움푹 들어감 특징(recessed feature)들의 측면들을 반응성 이온 에칭액(reactive ion etchant)들과 에칭 저항 물질(etch resist material)들에 주기적으로 노출시킴]으로써 실행된다. 다른 하나의 측면에서, 그 에칭 단계는, 유도성으로 결합된 플라즈마 반응성 이온 에칭(ICPRIE: Inductively Coupled Plasma Reactive Ion Etching), 버퍼 산화물 에칭액(BOE: Buffered Oxide Etchant) 또는 유도성으로 결합된 플라즈마 반응성 이온 에칭(ICPRIE) 기법과 버퍼 산화물 에칭액(BOE) 에칭 기법 양자(both)의 조합을 이용하여 실행된다.

- 29> 일 실시예에서, 윤곽 측면(contoured side surface)들의 윤곽 모양(contour profile)들은 그 측면들의 길이들의 세로축(longitudinal axis)을 교차하는 길이들을 확장하는 복수의 특징들을 가진다. 예를 들어, 윤곽 모양(contour profile)들은 그 측면들 상에 제공되는 릿지(ridge)들, 리플(ripple)들, 및/또는 부채 형상의 움푹들어감 특징(scalloped shaped recessed feature)들일 수 있다. 그 릿지(ridge)들, 리플(ripple)들 또는 부채 형상의 움푹 들어감 특징(scalloped shaped recessed feature)들 중의 어느 것은, 제 2 마스크를 제공함으로써 윤곽 측면들을 마스킹하여 측면들의 마스킹되지 않은 영역들을 생성하는 단계 동안에, 전조 마스크(shadow mask)들로서 기능한다.

- <30> 본 발명의 일 측면에서, 제 2 마스크를 제공함으로써 윤곽 측면들을 마스킹하는 단계는 마스크 물질의 경사진 증기 증착(angled vapor deposition)을 통해 실행된다.

- <31> 일 측면에서, 측면들의 마스킹되지 않은 영역들을 에칭하는 단계는 이방성 에칭(anisotropic etching)을 통해 실행된다. 예컨대, 웨이퍼는 (111) 방위(orientation)를 가지는 실리콘 웨이퍼이고, 측면들의 마스킹되지 않은 영역들을 에칭하는 단계는 선택적으로(preferentially) 실리콘 웨이퍼의 <110> 방향들을 따르는 이방성 에칭을 통해 실행된다. 그 이방성 에칭은 선택적으로 측면의 마스킹되지 않은 영역들을 강한 염기(strong base)에 노출 시킴에 의해 제공된다.

- <32> 일 실시예에서, 측면들의 마스킹되지 않은 영역들을 에칭하는 단계는 전사가능한 반도체 엘리먼트들을 생성하고, 그 엘리먼트들 각각은 브릿지 엘리먼트(bridge element)를 통해 웨이퍼에 연결된다.

- <33> 선택적이라고 설명되는 어떤 시스템들은 에칭 저항성 마스크(etch resistant mask)인 마스크[예컨대, 에칭 저항성 마스크(etch resistant mask)들인 제 1 마스크와 제 2 마스크]를 가진다.

- <34> 다른 측면에서 본 발명은, 여기에 개시되는 어떤 프로세스들에 의해 복수의 전사가능한 반도체 엘리먼트들을 제공하고 기판 상에 그 전사가능한 반도체 엘리먼트들을 프린팅함으로써, 기판 상에 복수의 전사가능한 반도체 엘리먼트들을 어셈블링(assembling)하는 방법이다. 예를 들어, 전자 디바이스 또는 전자 디바이스의 컴포넌트를 만드는 방법들이 제공된다. 그 방법은 본 발명의 프로세스에 의해 멀티레이어 어레이에 제공되는 복수의 전사가능한 반도체 엘리먼트들을 제공하는 단계들을 구비한다. 그 전사가능한 반도체 엘리먼트들이 기판 상에 프린팅되어, 전자 디바이스 또는 전자 디바이스의 컴포넌트가 만들어진다. 여기에 개시되는 어떤 방법들은 접촉 프린팅(contact printing)에 의해 실행되는 프린팅 단계를 사용한다. 여기에 개시되는 어떤 방법들은 멀티레이어의상이한 레이어들에 전사가능한 반도체를 순차적으로(sequentially) 프린팅하는 것에 의해 실행되는 프린팅 단계를 가진다.

- 235> 일 실시예에서, 어레이의 제 1 레이어에 반도체 엘리먼트들을 프린팅하는 것은 그 제 1 레이어 아래에 위치하는, 어레이의 한 레이어에서 1 이상의 전사가능한 반도체 엘리먼트들을 노출시킨다. 본 발명의 다른 실시 예는 동질적(homogeneous) 및/또는 이질적(heterogeneous) 앵커링 방안들(anchoring strategies)에 의해 전사 가능한 반도체 엘리먼트들을 만드는 방법들이다. 그러한 앵커링은 비고정(non-anchored) 시스템들 및 프로세스들에 비해서 다수의 이점들[예컨대, 전사가능한 엘리먼트들을 지지하는 웨이퍼의 더 효율적인 사용, 강화된 전사 제어(transfer control) 및 강화된 등록 전사(registered transfer)]을 제공한다. 특히, 앵커들 또는 브릿지 엘리먼트들은 릴리스되거나 전사되는 엘리먼트들의 외형(geometry)에 대한 로컬 제어(localized control)를 제공한다.

- 동질적 앵커링(homogeneous anchoring)[예컨대, 도 20, 도 35, 도 37]은 기능 레이어의 필수 부분(integral part)인 앵커를 가리킨다. 일반적으로, 동질적 앵커링 시스템들에 의해 전사가능한 엘리먼트들을 만드는 방법들은 선택적으로, 웨이퍼를 제공하는 단계, 웨이퍼 표면의 적어도 일부 상에 희생 레이어를 중착하는 단계, 이 분야에서 알려진 어떠한 수단에 의해 반도체 엘리먼트들을 정의하는 단계, 그리고 앵커 영역들을 정의하는 단계에 의한다. 그 앵커 영역들은 반도체 엘리먼트의 특정 영역들에 상응한다. 그 앵커 영역들은 반도체 레이어의 외형적 구성(geometrical configuration)에 상응할 수 있다. 예컨대, 앵커들은 상대적으로 넓은 표면 영역들에 의해정의되고 브릿지(brideg)나 테더(tether) 엘리먼트들에 의해 전사가능한 엘리먼트들에 연결된다[예컨대, 도 19, 도 20, 도 37 참조]. 그러한 외형은, 단일-레이어 실시예 또는 멀티-레이어 실시예에 대하여, 특정한 비고정(non-anchored) 영역들을 들어 올리는 것을 촉진하는 수단을 제공한다. 대안적으로, 앵커들은 밑에 있는 웨이퍼에 부착되거나 연결되는 반도체 영역들에 상응한다[예컨대, 도 35]. 희생 레이어를 제거하는 것은 밑에 있는 웨이퍼에 물리적으로 연결된 반도체의 일부가 남아 있는 동안에 반도체 엘리먼트들을 제거 또는 전사하는 수단을 제공한다.

- ○37> 이질적 앵커링(heterogeneous anchoring)[예컨대, 도 21, 도 22]은 기능 레이어의 필수 부분(integral part)이 아닌 앵커를 가리킨다. 즉, 반도체 레이어와는 상이한 물질로 만들어진 앵커들, 또는 동일한 물질로 만들어지지 만 전사가능한 반도체 옐리먼트들이 시스템에 배치된 후에 정의되는 앵커들을 가리킨다. 동질적 앵커링에 비해서 이질적 앵커링이 가지는 하나의 이점은 효과적인 사용가능 웨이퍼 지문(wafer footprint)에 대한 추가적 향상과 더 나은 전사 정의 방안들(transfer defining strategies)에 관련된다. 이질적 방안 실시예에서, 웨이퍼가 제공되고, 그 웨이퍼는 희생 레이어로 코팅되고, 반도체 엘리먼트들이 정의되며, 반도체 영역들을 고정하는 이질적 앵커 엘리먼트들이 증착된다. 일 측면에서, 그 앵커는 저항 물질(resist material)[예컨대, 포토레지스트 (photoresist) 또는 SiN(silicon nitride)]이거나, 비고정 영역들이 저항하지 못하는 들어 올리는 힘(lift-off force)에 저항할 수 있으며 앵커링할 수 있는 정도의 굳기(rigidity)를 가지는 다른 물질이다. 그 앵커는 최상단 반도체 레이어로부터 밑에 있는 레이어들을 통해 밑에 있는 웨이퍼 기판에 미칠 수 있다. 희생 레이어의 제거는 앵커 영역들이 웨이퍼에 연결된 채로 남아 있는 동안에 예를 들어 접촉 전사(contact transfer)에 의해 비고정 영역들을 제거하는 수단을 제공한다. 다른 실시예에서, 멀티-레이어 시스템에 있어서, 앵커는 상단 레이어를 밑에 있는 반도체 레이어에 고정하는 것을 제공한다. 대안적으로, 앵커링 시스템은 단일-레이어 반도체 레이어 시스템들을 위한 것이다.

- <38> 선택적으로 어떤 앵커링 시스템들은 1 이상의 희생 레이어, 기능 레이어, 및 릴리스 레이어를, 노출된 웨이퍼 기판 및/또는 밑에 있는 노출된 반도체 레이어를 생성하기 위해 이 분야에서 알려진 어떠한 수단에 의해, 패터 닝함으로써 만들어진다. 이 앵커링 시스템들은 복수의 전사가능한 반도체 엘리먼트들을 만드는 데, 그리고 그

전사가능한 반도체 엘리먼트들로부터 전자 디바이스들 또는 디바이스 컴포넌트들을 만드는 데 유용하다.

# 실시예

- <77> 도면들을 참조함에 있어서, 유사한 참조 번호들은 유사한 엘리먼트들을 지시하며, 1 이상의 도면에서 표시된 동일한 번호는 동일한 엘리먼트를 가리킨다. 또한, 이하에서, 다음의 정의들이 적용된다.

- <78> "전사가능(transferable)함" 또는 "프린트가능(printable)함"은 교환가능하게 사용되며, 기판들 상에 또는 기판 들 내에 전사(transfer), 어셈블리(assembly), 패터닝(patterning), 조직(organizing) 및/또는 집적 (integrating)될 수 있는 물질(material)들, 구조들, 디바이스 컴포넌트들 및/또는 집적된 기능 디바이스 (integrated functional device)들에 관련된다. 어느 한 실시예에서, "전사가능함"은, "멀티레이어 (multilayer) 구조로부터 디바이스 기판이나 디바이스 기판에 의해 지지되는 디바이스 또는 컴포넌트로"와 같이, 한 기판으로부터 다른 기판으로 구조나 엘리먼트의 직접 전사를 가리킨다. 대안적으로, "전사가능함"은, 구조나 엘리먼트를 들어 올려(lift-off) 그 구조나 엘리먼트를 디바이스 기판이나 디바이스 기판 상에 있는 컴 포넌트로 전사하는 스탬프(stamp)와 같은, 중간 기판(intermediate substrate)을 통해 프린트되는 구조나 엘리 먼트를 가리킨다. 어느 한 실시예에서, 프린팅은 기판을 높은 온도[즉, 약 400℃ 이하의 온도]에 노출시키지 않 고 행해질 수 있다. 본 발명의 어느 한 실시예에서, 프린트가능한 또는 전사가능한 물질들, 엘리먼트들, 디바이 스 컴포넌트들 및 디바이스들은 솔루션 프린팅(solution printing) 또는 건식 전사 접촉 프린팅(dry transfer contact printing)을 통해 기판들 상에 또는 기판들 내에 전사, 어셈블리, 패터닝, 조직 및/또는 집적될 수 있 다. 비슷하게, "프린팅"은, 스탬프로서 기능하는 기판 또는 그 자체로 타겟(예컨대, 디바이스) 기판인 기판과 같은, 기판들 상에 또는 기판들 내에 전사, 어셈블리, 패터닝, 조직 및/또는 집적되는 것을 가리키기 위해 넓게 사용된다. 그러한 직접 전사 프린팅은 디바이스 기판에 대한, 멀티레이어 구조의 기능적 상단-레이어 (functional top-layer)의 저비용이며 상대적으로 단순한 반복 전사를 제공한다. 이것은 별도의 스탬프 기관을 필요로 하지 않으면서 예를 들어 웨이퍼(wafer)로부터 타겟 기판으로의 블랭킷 전사(blanket transfer)를 달성 한다. "타겟 기판(target substrate)"은 전사된 구조를 지지하게 될, 요구되는 최종 기판을 가리키기 위해 넓게 사용된다. 어느 한 실시예에서, 타겟 기판은 디바이스 기판이다. 어느 한 실시예에서, 타겟 기판은 그 자체로 기판에 의해 지지되는 디바이스 컴포넌트 또는 엘리먼트이다.

- <79> 본 발명의 "전사가능한 반도체 엘리먼트들(transferable semiconductor elements)"은, 예를 들어 건식 전사 접 촉 프린팅 및/또는 솔루션 프린팅 방법들에 의해, 기판 표면들 상에 어셈블리 및/또는 집적될 수 있는 반도체 구조들을 구비한다. 어느 한 실시예에서, 본 발명의 전사가능한 반도체 엘리먼트들은 단일의 단위(unitary) 크 리스탈, 폴리크리스탈 또는 마이크로크리스탈 무기질 반도체 구조들이다. 이러한 설명의 문맥에서, 단위 구조 (unitary structure)는 기계적으로 연결된 특징들을 가지는 모놀리식 엘리먼트(monolithic element)이다. 본 발명의 반도체 엘리먼트들은 도핑되지 않거나 도핑(dope)될 수 있고, 도펀트(dopant)들의 선택된 공간적인 분포 를 가질 수 있으며, 복수의 상이한 도펀트 물질들[P 및 N 타입 도펀트들을 포함함]로 도핑될 수 있다. 본 발명 은 약 1 마이크론(micron) 이상인 적어도 하나의 단면 치수(cross sectional dimension)를 가지는 마이크로구 조의(microstructured) 전사가능한 반도체 엘리먼트들 및 약 1 마이크론 이하인 적어도 하나의 단면 치수를 가 지는 나노구조의(nanostructured) 전사가능한 반도체 엘리먼트들을 포함한다. 많은 어플리케이션들에서 유용한 전사가능한 반도체 엘리먼트들은, 통상적인 고온 프로세싱 기법들을 이용하여 생성되는 고순도(high purity) 크 리스탈 반도체 웨어퍼들과 같은, 고순도 벌크 물질(bulk material)들의 "탑 다운(top down)" 프로세싱으로부터 도출되는 엘리먼트들을 구비한다. 어느 한 실시예에서, 본 발명의 전사가능한 반도체 엘리먼트들은, 전도 레이 어(conducting layer), 절연 레이어(dielectric layer), 전극, 추가적 반도체 구조 또는 이들의 어떠한 조합과 같은, 적어도 하나의 추가적 디바이스 컴포넌트 또는 구조에 연결되는 반도체 조직을 가지는 집합물 구조 (composite structure)들을 구비한다. 어느 한 실시예에서, 본 발명의 전사가능한 반도체 엘리먼트들은 신축가 능(stretchable) 반도체 엘리먼트들 및/또는 이질적(heterogeneous) 반도체 엘리먼트들을 구비한다.

- "기능 레이어(functional layer)"는, 디바이스나 디바이스 컴포넌트 내로 통합될 수 있으며 그 디바이스나 디바이스 컴포넌트에게 적어도 부분적인 기능성(partial functionality)을 제공하는 레이어를 가리킨다. 특정한 디바이스나 디바이스 컴포넌트에 의존하여, 기능 레이어는 넓은 범위의 구성(composition)들을 가진다. 예를 들어, 솔라 어레이(solar array)인 디바이스가, 여기에 제공되듯이 그 자체가 복수의 별개 레이어들로 이루어지는 기능 레이어를 포함하는, III-V 마이크로 솔라 셀들(III-V micro solar cells)의 시작 기능 레이어 (starting functional layer)로부터 만들어 질 수 있다. 그러한 레이어들의 릴리스(release) 및 후속 프린팅 (subsequent printing)은 광전 디바이스(photovoltaic device)나 디바이스 컴포넌트를 구성(construct)하기 위

한 기초를 제공한다. 반대로, 전자소자들(MESFETs), LED들, 또는 광학 시스템들에 통합하기 위한 기능 레이어는 상이한 레이어 구성(configuration and/or composition)들을 가질 수 있다. 따라서, 멀티레이어 구조로 통합되 는 특정한 기능 레이어는 그 기능 레이어가 통합되게 될 최종 디바이스나 디바이스 컴포넌트에 의존한다.

- "릴리스 레이어(release layer)"[때로는 "희생 레이어(sacrificial layer)"라고 지칭됨]는 1 이상의 기능 레이어들을 적어도 부분적으로 분리하는 레이어를 가리킨다. 예를 들어, 물리적, 열적(thermal), 화학적 및/또는 전자기적 자극에 응답하여 물리적으로 분리되는 릴리스 레이어에 의하는 것과 같이, 릴리스 레이어는 제거될 수있거나 멀티레이어 구조의 다른 레이어들로부터 기능 레이어를 분리하는 것을 촉진하기 위한 다른 수단을 제공할 수 있다. 따라서, 실제의 릴리스 레이어 구성(composition)은 분리를 제공하게 될 수단에 가장 부합하도록 선택된다. 분리를 위한 수단은, 계면 장애(interface failure)에 의하거나 릴리스 레이어 희생(release layer sacrifice)에 의하는 것과 같이, 이 분야에서 알려진 1 이상의 어떠한 분리 수단에 의한다. 릴리스 레이어는 그자체가, 멀티레이어 구조의 나머지 부분에 부착된 채로 남아 있는 기능 레이어 또는 멀티레이어 구조의 나머지 부분으로부터 분리된 기능 레이어와 같은, 기능 레이어에 연결된 채로 남을 수 있다. 선택적으로 릴리스 레이어는 후속적으로 기능 레이어로부터 분리 및/또는 제거된다.

- <82> "기판에 의해 지지됨(supported by a substrate)"은 기판 표면 상에 적어도 부분적으로 존재하는 구조 또는 그구조와 기판 표면의 사이에 위치하는 1 이상의 중간 구조들 상에 적어도 부분적으로 존재하는 구조를 가리킨다. 또한 "기판에 의해 지지됨(supported by a substrate)"이라는 용어는 기판에 부분적으로 또는 완전히 삽입된 구조들을 가리킬 수 있다.

- "솔루션 프린팅(solution printing)"은, 전사가능한 반도체 엘리먼트들과 같은 1 이상의 구조들이 캐리어 매체 (carrier medium) 내로 분산(disperse)되고 일치된 방식으로(in a concerted manner) 기판 표면의 선택된 영역들에 전달(deliver)되는 프로세스들을 가리키도록 의도된다. 예시적인 솔루션 프린팅 방법에서, 기판 표면의 선택된 영역들로 구조들을 전달하는 것은, 패터닝(patterning)을 받은 기판 표면의 형태적(morphology) 및/또는 물리적 특성들에 무관한 방법들에 의해 달성된다. 본 발명에서 이용가능한 솔루션 프린팅 방법들은 잉크 젯 프린팅(ink jet printing), 열적 전사 프린팅(thermal transfer printing), 및 모세관 액션 프린팅(capillary action printing)을 포함하지만, 그것들로만 한정되는 것은 아니다.

- <84> 본 방법들에서, 전사가능한 반도체 엘리먼트들을 어셈블링(assembling), 조직(organizing) 및/또는 집적 (integrating)하기 위한 유용한 접촉 프린팅 방법들은 건식 전사 접촉 프린팅(dry transfer contact printing), 마이크로접촉 또는 나노접촉 프린팅(microcontact or nanocontact printing), 마이크로전사 또는 나노전사 프린팅(microtransfer or nanotransfer printing) 및 셀프 어셈블리 지원 프린팅(self assembly assisted printing)을 포함한다. 본 발명에서 접촉 프린팅을 이용하는 것이 유익하다. 왜냐하면, 그것이 서로에 대해 상대적인 선택된 방위(orientation)들 및 위치들에 복수의 전사가능한 반도체를 어셈블리 및 집적하는 것 을 허용하기 때문이다. 또한 본 발명에서 접촉 프린팅은, 반도체들[예컨대, 무기질 반도체들, 단일의 크리스탈 반도체들, 유기질 반도체들, 탄소 나노물질(carbon nanomaterial)들 등], 절연체들(dielectrics), 및 전도체들 (conductors)을 포함하는, 여러 가지 클래스(diverse class)들의 물질들과 구조들의 효과적인 전사, 어셈블리 및 집적을 가능하게 한다. 선택적으로 본 발명의 접촉 프린팅 방법들은, 디바이스 기판 상에 미리 패턴된 1 이 상의 디바이스 컴포넌트들에 대해 상대적인 미리 선택된 위치들 및 공간적 방위들에, 전사가능한 반도체 엘리먼 트들을 고정밀 등록 전사 및 어셈블리(high precision registered transfer and assembly)하는 것을 제공한다. 또한 접촉 프린팅은 넓은 범위의 기판 타입들과 양립가능하다. 그 기판 타입들은 [글래스들(glasses), 세라믹들 (ceramics) 및 금속들과 같은] 통상적인 강성(rigid) 또는 반강성(semi-rigid) 기판들, 그리고 [연성 기판 (flexible substrate)들, 가요성 기판(bendable substrate)들, 형상가능 기판(shapeable substrate)들, 적합성 기판(conformable substrate)들 및/또는 신축가능 기판(stretchable substrate)들과 같이,] 특정한 어플리케이 션들에 대하여 매력적인 물리적 및 기계적 특성들을 가지는 기판들을 포함한다. 전사가능한 반도체 구조들의 접 촉 프린팅 어셈블리(contact printing assembly)는 예를 들어 저온[예컨대, 298K 이하] 프로세싱과 양립가능하 다. 이 속성은 현재의 광학 시스템들이 어느 범위의 기판 물질들[폴리머(polymer) 및 플라스틱(plastic) 기판들 과 같이, 고온에서 분해(decompose) 또는 열화(degrade)되는 것들을 포함함]을 이용하여 구현될 수 있도록 해준 다. 또한 디바이스 엘리먼트들에 대한 접촉 프린팅 전사, 어셈블리 및 집적은 유익하다. 왜냐하면, 그것이, 롤-투-롤 프린팅(roll-to-roll printing) 및 플렉소그래픽 프린팅(flexographic printing) 방법들과 시스템들과 같은, 저비용 및 높은 처리율의 프린팅 기법들과 시스템들을 통해 구현될 수 있기 때문이다. "접촉 프린팅 (contact printing)"은, 스탬프 표면으로부터 기판 표면으로 특징들을 전사하는 것을 촉진하는 스탬프에 의하는 것과 같이, 건식 전사 접촉 프린팅을 넓게 가리킨다. 어느 한 실시예에서, 스탬프는 탄성 스탬프(elastomeric

stamp)이다. 대안적으로, 전사는 타켓(예컨대, 디바이스) 기판으로 직접 이루어질 수 있다. 다음의 참조 문헌들은 셀프 어셈블리(self assembly) 기법들에 관련된다. 그 셀프 어셈블리 기법들은, 접촉 프린팅 및/또는 솔루션 프린팅 기법들을 통해 전사가능한 반도체 엘리먼트들을 전사, 어셈블리 및 상호연결하기 위한 본 발명의 방법들에서 사용될 수 있다. 그 참조 문헌들은 그들 전체로서 참조에 의해 여기에 병합된다.

- <85> (1) "Guided molecular self-assembly: a review of recent efforts", Jiyun C Huie Smart Mater. Struct. (2003) 12, 264-271;

- <86> (2) "Large-Scale Hierarchical Organization of Nanowire Arrays for Integrated Nanosystems", Whang, D.; Jin, S.; Wu, Y.; Lieber, C. M. Nano Lett. (2003) 3(9), 1255-1259;

- <87> (3) "Directed Assembly of One-Dimensional 1 차원 Nanostructures into Functional Networks", Yu Huang, Xiangfeng Duan, Qingqiao Wei, and Charles M. Lieber, Science (2001) 291, 630-633;

- <88> (4) "Electric-field assisted assembly and alignment of metallic nanowires", Peter A. Smith et al., Appl. Phys. Lett. (2000) 77(9), 1399-1401.

- "캐리어 필름(carrier film)"은 레이어들의 분리를 촉진하는 물질을 가리킨다. 캐리어 필름은, 제거될 레이어에 인접하게 위치하는 금속 또는 금속 포함 물질과 같은, 한 레이어의 물질(a layer of material)일 수 있다. 캐리어 필름은 집합 물질(composite of materials)일 수 있다[폴리머 물질(polymeric material) 또는 포토레지스트물질(photoresist material)에 통합되거나 부착되는 것을 포함함]. 그 물질에 인가되는 들어 올리는 힘(lift-off force)은 밑에 있는 레이어[예를 들어, 기능 레이어]로부터 그 집합 물질을 릴리스하는 것을 제공한다.

- <90> "반도체(semiconductor)"는 매우 낮은 온도에서는 절연물이지만 약 300K의 온도에서는 상당한 전기적 전도성 (electrical conductivity)을 가지는 어떤 물질을 가리킨다. 본 설명에서, 반도체라는 용어의 사용은 마이크로 전자소자들(microelectronics) 및 전자 디바이스들 분야에서의 이 용어의 사용과 일치하도록 의도된다. 본 발명 에서 유용한 반도체들은 실리콘, 게르마늄 및 다이아몬드와 같은 엘리먼트 반도체(element semiconductor)들, 그리고 그룹 IV 화합물 반도체들[예컨대, SiC, SiGe], 그룹 III-V 반도체들[예컨대, AlSb, AlAs, Aln, AlP, BN, GaSb, GaAs, GaN, GaP, InSb, InAs, InN, InP], 그룹 III-V 삼원(ternary) 반도체 합금들[예컨대, Al<sub>x</sub>Ga<sub>1</sub>-<sub>x</sub>As], 그룹 II-VI 반도체들[예컨대, CsSe, CdS, CdTe, ZnO, ZnSe, ZnS, ZnTe], 그룹 I-VII 반도체들[예컨대, CuCl], 그룹 IV-VI 반도체들[예컨대, PbS, PbTe, SnS], 레이어 반도체들[예컨대, PbI<sub>2</sub>, MoS<sub>2</sub>, GaSe], 산화물 (oxide) 반도체들[예컨대, CuO and Cu₂O]과 같은 화합물 반도체(compound semiconductor)들을 구비할 수 있다. 반도체라는 용어는, 어느 어플리케이션이나 디바이스에 대하여 유용하고 유익한 전자적 특성을 제공하기 위한, 진성 반도체(intrinsic semiconductor)들 및 1 이상의 선택된 물질들로 도핑되는 외인성 반도체(extrinsic semiconductor)들[p-타입 도핑 물질들 및 n-타입 도핑 물질들을 가지는 반도체를 포함함]을 포함한다. 반도체라 는 용어는 반도체들 및/또는 도펀트(dopant)들의 혼합물을 구비하는 집합 물질을 포함한다. 본 발명의 일부 어 플리케이션들에 대하여 유용한 특정 반도체 물질들은 Si, Ge, SiC, AlP, AlAs, AlSb, GaN, GaP, GaAs, GaSb, InP, InAs, GaSb, InP, InAs, InSb, ZnO, ZnSe, ZnTe, CdS, CdSe, ZnSe, ZnTe, CdS, CdSe, CdTe, HgS, PbS, PbSe, PbTe, AlGaAs, AlInAs, AlInP, GaAsP, GaInAs, GaInP, AlGaAsSb, AlGaInP, 및 GaInAsP를 포함하지만, 그것들로만 한정되는 것은 아니다. 다공성(porous) 실리콘 반도체 물질들은 센서들, 그리고 발광 다이오드(LED: light emitting diode)들와 고체 상태 레이저(solid state laser)들과 같은 발광 물질들의 분야에서 본 발명의 어플리케이션들에 대하여 유용하다. 반도체 물질들의 불순물들(impurities)은 그 반도체 물질 외의 원자들 (atoms), 엘리먼트들(elements), 이온들(ions) 및/또는 분자들(molecules)이거나 그 반도체 물질에 제공되는 도펀트(dopant)들이다. 불순물들은, 반도체 물질들에 존재하며 반도체 물질들의 전자적 특성에 부정적으로 영향 을 미칠 수 있는 바람직하지 않은 물질들이다. 그러한 물질들로서 산소, 탄소, 그리고 중금속들을 포함하는 금 속들이 있지만, 그것들로만 한정되는 것은 아니다. 중금속 불순물들은 주기율표 상에서 구리와 납 사이의 그룹 엘리먼트들, 칼슘, 나트륨, 그리고 모든 이온들(ions), 화합물들(compounds) 및/또는 그들의 복합체들 (complexes)을 포함하지만, 그것들로만 한정되는 것은 아니다.

- <91> "절연체(dielectric)" 및 "절연 물질(dielectric material)"은 본 설명에서 동의적으로(synonymously) 사용되며 전기적 전류의 흐름에 높게 저항하는 물질(substance)을 가리킨다. 유용한 절연 물질들은 SiO<sub>2</sub>, Ta<sub>2</sub>O<sub>5</sub>, TiO<sub>2</sub>, ZrO<sub>2</sub>, Y<sub>2</sub>O<sub>3</sub>, Si<sub>3</sub>N<sub>4</sub>, STO, BST, PLZT, PMN, 및 PZT를 포함하지만, 그것들로만 한정되는 것은 아니다.

- <92> "디바이스 전계 효과 이동도(device field effect mobility)"는 트랜지스터와 같은 전자 디바이스의 전계 효과

이동도를 가리키며, 그 전자 디바이스에 상응하는 출력 전류 데이터를 이용하여 계산된다.

- <93> 본 발명은 다음의 비-한정적인 예시들에 의해 더 이해될 수 있다. 여기에 인용되는 모든 참조 문헌들은 본 개시와 일치하는 범위만큼 참조에 의해 여기에 병합된다. 여기의 설명이 많은 특이성들을 포함한다고 하더라도, 그것들이 본 발명의 범위를 한정하는 것으로 해석되어서는 안되며, 단지 본 발명의 바람직한 실시예들 일부에 대한 예시들을 제공하는 것으로 해석되어야 한다. 따라서, 본 발명의 범위는 주어진 예시들에 의하기보다는 첨부된 청구항들과 그들의 균등물들에 의해 결정되어야 한다.

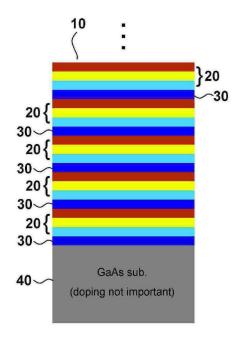

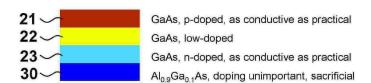

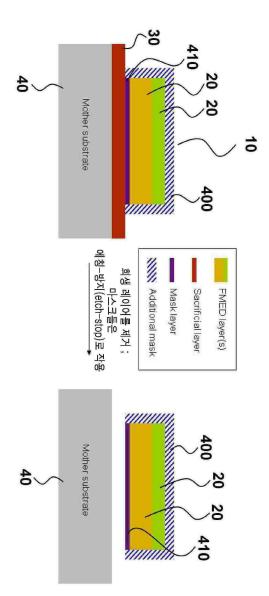

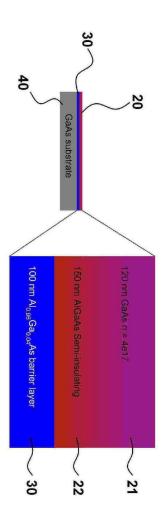

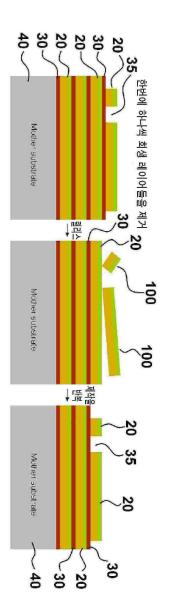

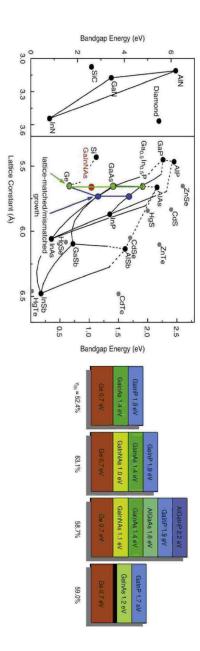

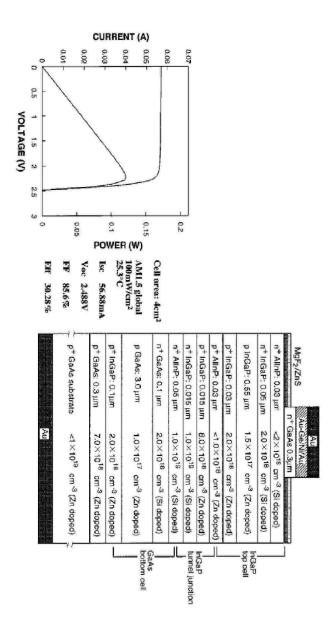

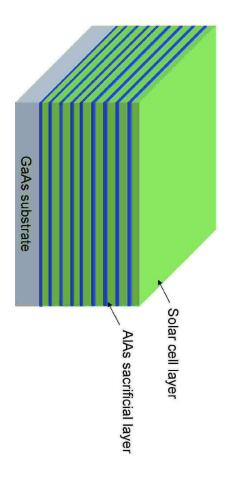

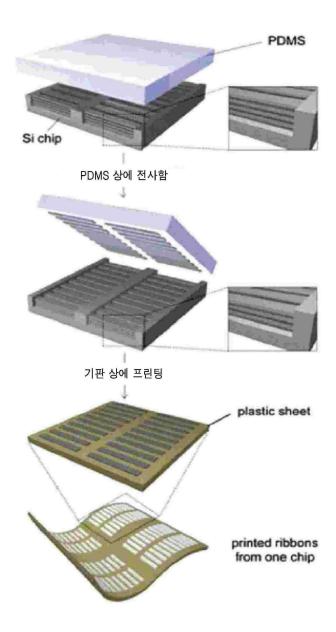

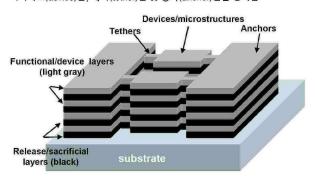

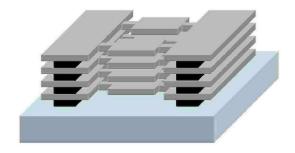

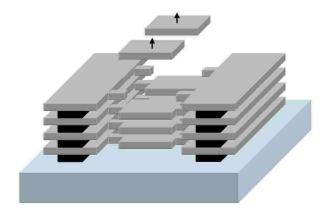

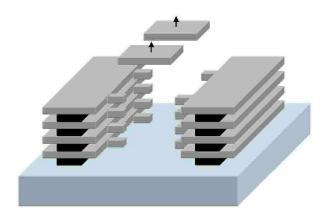

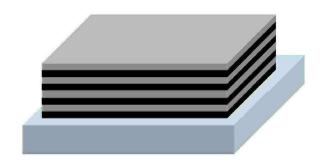

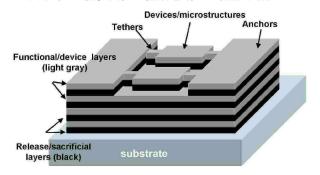

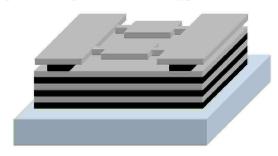

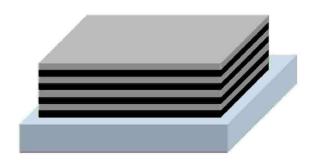

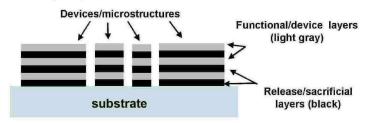

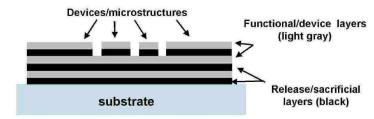

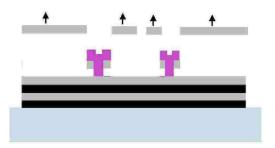

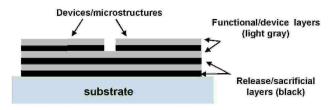

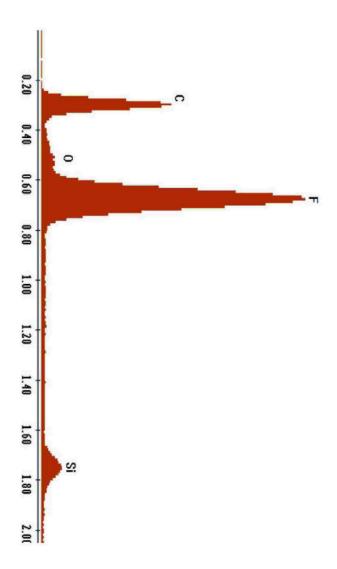

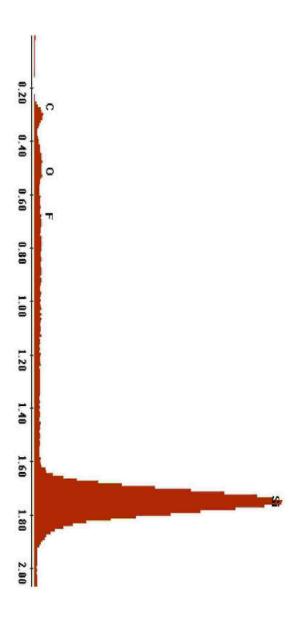

- 본 발명의 일 측면은 멀티-레이어 프로세성을 통해 저비용 방식으로 디바이스나 디바이스 컴포넌트 내에 통합될수 있는 FMED들을 제공하고 있다. 복수의 기능 레이어들(FMED들. 20)을 가지는 멀티레이어 구조(10)의 일 예시가 도 1에 제공되어 있다. 기능 레이어들(20)은 릴리스 레이어(30)에 의해 인접 기능 레이어들로부터 분리된다. 복수의 기능 레이어들(20)과 릴리스 레이어들(30)은 기판(40) 상에서 지지되며, 기능 레이어(20) 자체는 복수의 레이어들의 집합물(composite)이다. 예를 들어, 기능 레이어(20)는 도시된 바와 같이, 솔라 셀(solar cell)들에서 유용한, III-V 에필레이어(epilayer)들[예컨대, p-도핑된 GaAs 상단 레이어(21), 낮게-도핑된 GaAs 중간 레이어(22), 및 n-도핑된 GaAs 하단 레이어(23)]을 구비할 수 있다. 최하단 레이어는 도핑되거나 도핑되지 않는 릴리스 레이어(30. Al<sub>0.9</sub>Ga<sub>0.1</sub>As) 상에서 지지된다. 릴리스 레이어(30)는 멀티레이어 구조(10)에서 1 이상의 기능 레이어들(20)에 대한 접근을 촉진한다.

- <95> 상이한 종류의 자극제들(stimuli)에 의한 릴리스의 예시들은 삽입된 희생 레이어(embedded sacrificial laye r)나 희생 레이어들을 에칭(etching), 용해(dissolution), 연소(burning)함[어떠한 제거 수단]으로써 릴리스하는 것을 포함한다[표 1 참조]. 예를 들어, 릴리스 레이어 또는 릴리스 레이어들은 FMED들보다 2 배 이상 빠르게 선택적으로 에칭/용해/연소/제거될 수 있다. 그리고, 희생 레이어들의 제거를 위해 사용되는 약품(agent)에 대한 노출로부터 FMED들을 보호하기 위해서 구조들이나 레이어들의 마스킹(masking)이 채택될 수 있다. 릴리스 레이어들은 한번에 하나씩 제거되거나, 2 이상의 희생 레이어들이 동시에 제거된다.

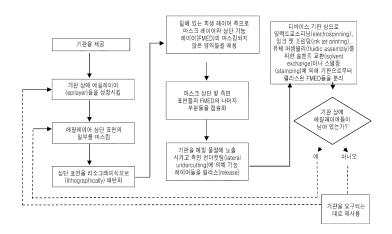

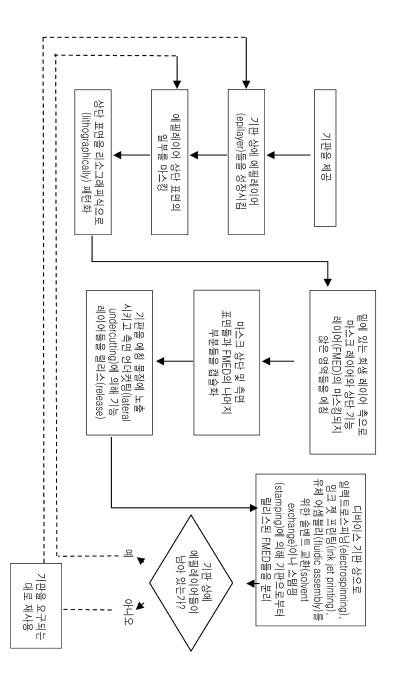

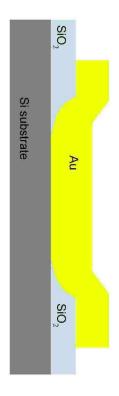

- <96> 도 2a는 기능 레이어(20)의 적어도 일부분을 코팅(coat)하는 마스크 레이어(mask layer. 410)[기능 레이어(20) 과 릴리스 레이어(30)의 사이에 있음]를 갖춘 멀티레이어 구조(10)를 나타낸다. 선택적으로 마스크 레이어(41 0)는, 마스크 400에 의해 커버되지 않는 나머지 부분들을 둘러싸는 마스크 400과 같은, 추가 마스크(additional mask. 400)를 구비한다. 도 2a에서, 릴리스 레이어(30)는 희생 레이어(sacrificial layer)로 표시되어 있고, 기능 레이어(20)는 2 개의 레이어들을 가지는 FMED로 표시되어 있다. 마스크 400 및 410은 희생 레이어(30)를 제거하는 에칭 수단(etchent means)으로부터 기능 레이어(20)를 보호하기 위한 에칭-방지(etch-stop)로서 작용할 수 있고, 그럼으로써 기판(40)으로부터 레이어들(20)을 들어 올리는 것(lift-off)을 촉진한다. 도 2b는 캡슐화 마스크(encapsulating mask)를 이용하여 멀티레이어 구조로부터 전사가능한 FMED들을 생성하기 위한 프로세스를 요약하는 흐름도이다[도 2b 참조].

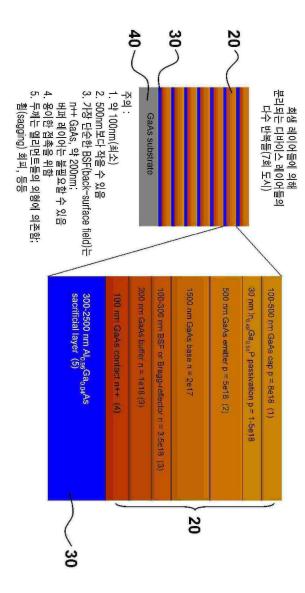

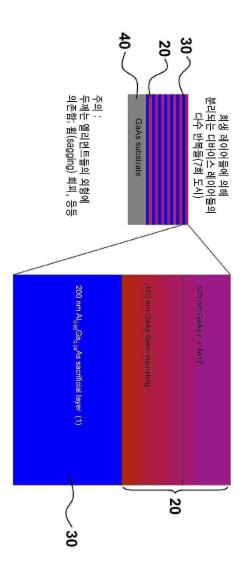

- <97> MESFET들에서의 이용에 대해 유용한 구조가 도 2c에 제공되어 있다. 도 2c에서, 기능 레이어(20)는 120nm 두께의 GaAs 제 1 레이어(21)와 150nm 두께의 AlGaAs 반-절연(semi-insulating) 제 2 레이어(22)를 구비한다. 릴리스 레이어(30)는 기판(40)으로부터 30을 분리하는 것을 촉진할 수 있는 100nm 두께의 Al<sub>0.96</sub>Ga<sub>0.04</sub> 장벽 레이어 (barrier layer)이다.

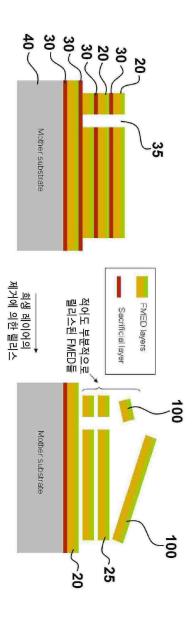

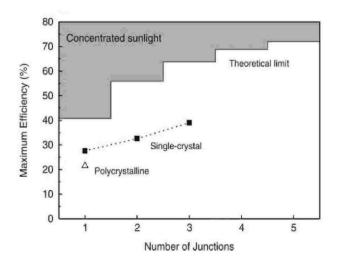

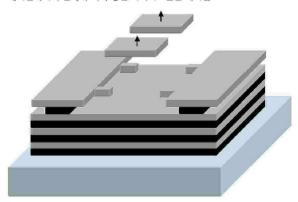

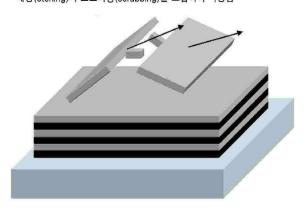

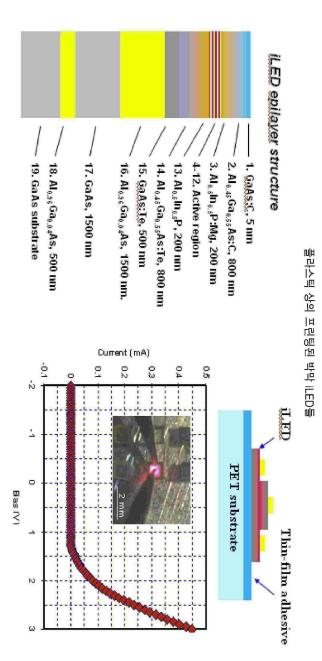

- <98> 예시 1: 광전소자들(photovoltaics), 전자소자들(electronics) 및 LED들을 위한 전사가능한 구조들의 릴리스.

- <99> 도 3a 및 도 3b는 다수 릴리스 레이어들을 동시에 제거함[도 3a] 및 릴리스 레이어들을 순차적으로 한 레이어씩 제거함[도 3b]을 위한 방법들과 구조들을 개략적으로 나타낸다. 도 3a에서, 멀티레이어 구조(10)의 일부분이 에칭 수단(etchant means)에 노출되며, 그럼으로써 에칭된 접근 통로(35)가 형성된다. 통로(35)는 복수의 릴리스 레이어들(30)[이 예시에서는 3 개]에 대한 동시적인 접근을 제공한다. 이러한 방식으로, 복수의 전사가능한 구조들(100)은, 디바이스 기판 또는 기판에 의해 지지되는 디바이스 컴포넌트와 같이, 이 분야에서 알려진 어떠한 수단에 의해, 관심있는 표면에 프린팅하는 데 이용가능하다[예컨대, 액체 프린팅(liquid printing), 접촉 프린팅(contact printing), 등등].

- <100> 도 3b는 한 레이어씩 제거하는 예(layer-by-layer removal)를 나타낸다. 도 3b에서, 하나의 단일 기능 레이어 (20)로부터 전사가능한 구조들(100)을 제공하기 위해서, 단지 하나의 단일 기능 레이어(20)만이 릴리스되도록 에칭 접근 채널(35)은 최상단 기능 레이어(20)에만 미친다. 필요하다면, 릴리스 레이어들(30)을 제거하기 위한 화학 수단(chemical means)을 도입하기 전에 기능 레이어(20)는 마스크(미도시)에 의해 보호될 수 있다. 그 프로세스는 각각의 추가 기능 레이어(20)에 대하여 반복된다. 도 3에 도시된 프로세스에서, 멀티레이어 구조(10)

를 지지하는 모 기판(mother substrate. 40)은 재사용될 수 있다.

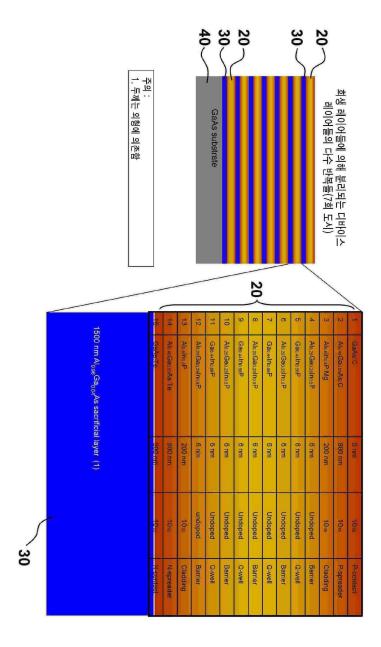

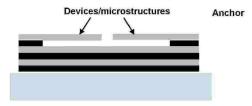

- <101> 상이한 디바이스들이나 디바이스 컴포넌트들을 만들기 위한 상이한 기능/릴리스 레이어 구성들 및 외형 (geometry)의 다수 예시들이 도 3c 내지 도 3e에 제공되어 있다. 도 3c는 광전소자들(photovoltaics)을 만들기 위한 FMED들을 가지는 구조의 예시를 제공한다. 도 3c에서 AlGaAs는 릴리스 레이어이다. 도 3d는 전자소자들 (electronics)[예컨대, MESFET들]을 만들기 위한 FMED들을 가지는 멀티레이어 구조의 예시를 제공한다. 도 3e는 LED들을 만들기 위한 FMED들을 가지는 멀티레이어 구조의 예시를 제공한다. 간결성을 위해, 기능 레이어(20)의 15-레이어 구조는 표 2에 재현되었다. 도 4 및 도 5는 다수 기능 레이어들을 릴리스하는 프로세스에서 사용되는 단계들을 나타내거나[도 4], 기능 레이어들을 순차적으로 한 레이어씩 릴리스하는(layer-by-layer release) 프로세스에서 사용되는 단계들을 나타낸다[도 5].

- 기능 레이어들은, 삽입된 릴리스 레이어나 희생 레이어의 언더컷팅(undercutting), 에칭(etching), 용해 (dissolution), 연소(burning), 등등[모든 제거 수단]과 같은, 이 분야에서 알려진 어떠한 수단에 의해 릴리스된다. 기능 레이어들을 릴리스함에 있어 다양한 자극제들(stimuli)을 사용하는 다양한 방안들이 있으며, 그 일부가 표 1에 제공되어 있다. 또한 표 1은 기능 및 릴리스 레이어들의 구성이 채택된 릴리스 방안에 의거하여 선택될 수 있다는 점을 보여준다. 희생 레이어 또는 희생 레이어들은 FMED들을 구성하는 기능 레이어들보다 약 2 배 이상 빠르게 선택적으로 에칭/용해/연소/제거된다. 선택적으로, 희생 레이어들의 제거를 위해 사용되는 약품에 대한 노출로부터 FMED들(20)을 보호하기 위하여 마스크 레이어(400)가 제공된다[도 2a 참조]. 릴리스 레이어들은 한번에 하나씩 제거될 수 있거나, 복수의 릴리스 레이어들이 동시에 제거될 수 있다[도 3a와 도 3b를비교, 도 4의 흐름도와 도 5의 흐름도를 비교].

- <103> 기능 레이어들의 동시적인 릴리스가 도 3a 및 도 4에 나타나 있다. 도 4는 추가적 전사가능한 FMED들의 후속적 인 생성을 위한 기판의 선택적 재사용과 함께 "한번에 다수의 레이어들(multiple-layers-at-a-time)" 방식에 의 해 광전소자들을 위한 FMED들을 릴리스하는 것을 나타낸다. 기능 레이어들은 에피택셜형 성장 반도체들 (epitaxially grown semiconductors)을 구비한다. 또한 그 프로세스는 도 12에서 설명되는 프로세스와 비슷하 게 비결정(amorphous) 또는 다결정(polycrystalline) 물질들에 대하여 동작한다. 간단하게, GaAs 기판이 얻어진 다. 도 3c에 도시된 에필레이어들을 예를 들어, MOCVD, MBE 등에 의해 GaAs 기판 상에 성장시킨다[각각 트랜지 스터들, LED들에 대한 도 3d, 도 3e의 비슷한 프로세스]. 필요에 따라 성장에 앞서 기판을 선-처리(pretreat)한다[선택적으로 CMP가 요구된다]. 기능 및 희생 레이어들을 증착(depositing)하거나 에피택셜형으로 성 장(epitaxially growing)시키기 전에, 기판에 인접하는 GaAs의 약 ~200nm 버퍼 레이어(buffer layer)를 성장시 킨다. 상단 에필레이어의 표면 일부분은 패터닝을 위한 리소그래피(lithography)의 형태로 그리고 플라즈마-강 화 화학적 증기 증착(PECVD: Plasma-Enhanced Chemical Vapor Deposition)에 의해 SiO₂로 마스킹될 수 있다. 표면으로부터 어떤 Al<sub>0.96</sub>Ga<sub>0.04</sub>As 희생 레이어 내부[예를 들어, 기판에 가장 가까운 희생 레이어 내부]의 어느 거 리까지 Cl/Ar/H 플라즈마(plasma)를 이용하여 에필레이어들의 마스킹되지 않은 영역들을 에칭한다. 그 희생 레 이어가 기판으로부터 가장 먼 것이면 안된다[그 경우에는, 릴리스가 도 3b 및 도 5에 도시된 바와 같은 "한번에 하나씩(one-at-a-time)" 프로세스에 해당될 것이다]. 기판을 농축된 HF에 노출하여, 그 노출된 희생 레이어들을 적어도 부분적으로 제거하고 희생 레이어들 위의 기능 에필레이어들을 측면 언더컷팅(lateral undercutting)에 의해 릴리스한다[HF는 그것이 희생 레이어를 공격하는 것보다 더 느리게{1/10 미만의 에칭율(etch rate)} 기능 에필레이어들을 공격한다]. 일렉트로스피닝(electrospinning), 잉크 젯 프린팅(ink jet printing) 또는 유체 어셈블리(fluidic assembly)를 위한 솔벤트 교환(solvent exchange)이나 스탬핑(stamping) 등에 의해 기판으로 부터 릴리스된 FMED들을 분리한다. HF를 사용하여 희생 레이어들의 나머지 부분들을 제거한다. 위에 있는 (overlying) 기능 에필레이어들의 나머지 부분들[앵커링 구조(anchoring structure)들 등]을 씻고/닦아낸다 (wash/rub away). 제거된 레이어들의 바로 아래에 원래 있던 기능 레이어들이 이제 노출되어 기판의 표면 상에 있다. 마스킹과 HF 제거 사이의 단계들을 반복함으로써, 기판 상에 아무 희생 레이어들도 남지 않을 때까지 기 능 레이어들의 세트들[각각의 세트는 희생 레이어들에 의해 분리됨]을 릴리스한다. 선택적인 기판의 재사용을 위해, 이러한 단계들이 요구되는 바에 따라 반복된다.

- <104> 단일 기능 레이어의 릴리스가 도 3b 및 도 5에 도시되어 있다. GaAs 웨이퍼와 같은 기판은 도 3c에 도시된 기능 레이어와 같은 에필레이어들의 성장[MOCVD, MBE 등에 의함]에 대하여 지지(support)를 제공한다. 그 기판은 필요에 따라 성장에 앞서 선-처리(pre-treat)될 수 있다[예컨대, CMP]. 릴리스 및 기능 레이어들의 증착이나 에피택결형 성장(epitaxial growth) 전에 기판에 인접하는 GaAs의 ~200nm 버퍼 레이어(buffer layer)를 성장시키는 것이 필요할 수 있다. 패터닝을 위한 어떤 형태의 리소그래피(lithography)로 그리고 플라즈마-강화 화학적 증

기 증착(PECVD: Plasma-Enhanced Chemical Vapor Deposition)에 의해 SiO<sub>2</sub>로 상단 에필레이어의 표면 일부분을 마스킹한다. 표면으로부터 제 1 Al<sub>0.96</sub>Ga<sub>0.04</sub>As 희생 레이어 내부의 어느 거리까지 Cl/Ar/H 플라즈마(plasma)를 이용하여 에필레이어들의 마스킹되지 않은 영역들을 에칭한다. 기판을 농축된 HF에 노출하여, 그 노출된 희생 레이어[하나]를 적어도 부분적으로 제거하고 희생 레이어 위의 에필레이어들[기능 레이어들]을 측면 언더컷팅 (lateral undercutting)에 의해 릴리스한다[HF는 그것이 희생 레이어를 공격하는 것보다 더 느리게{1/10 미만의 에칭율(etch rate)} 기능 에필레이어들을 공격한다].

- <105> 도 3b, 도 3c 및 도 5를 참조한다. 표면으로부터 에필레이어들을 통해 기판 내부의 어느 거리까지 CI/Ar 플라즈마를 이용하여 에필레이어들의 마스킹되지 않은 영역들을 에칭한다. 에필레이어들의 나머지 부분들을 상단 및 측면 표면들이 커버되도록 포토레지스트(photoresist)로 캡슐화한다. 기판을 [수성 구연산(aqueous citric acid) + H<sub>2</sub>O<sub>2</sub>]에 노출하여, GaAs 기판을 에칭하고 희생 레이어들 위의 기능 에필레이어들[기능 레이어들]을 측면 언더컷팅에 의해 릴리스한다[습식 에칭액(wet etchant)은 그것이 GaAs 기판을 공격하는 것보다 더 느리게{1/10 미만의 에칭율(etch rate)} 장벽 에필레이어(barrier epilayer)를 공격하며, 기능 GaAs 레이어들은 그들을 캡슐화하는 포토레지스트에 의해 습식 에칭액으로부터 보호된다]. 도 2에서, AlGaAs 에필레이어는 "마스크(400)"에 상응하며, 포토레지스트 캡슐화는 "추가 마스크(additional mask. 410)"에 상응한다.

- <106> 어떤 릴리스된 FMED들은 일렉트로스피닝(electrospinning), 잉크 젯 프린팅(ink jet printing) 또는 유체 어셈 블리(fluidic assembly)를 위한 솔벤트 교환(solvent exchange)이나 스탬핑(stamping) 등에 의해 기판으로부터 분리될 수 있다.

- <107> 또한 릴리스는 에칭으로부터 FMED들을 보호하기 위한 마스크 레이어 및/또는 이방성 에칭(anisotropic etchin g)을 위한 직접적인 에칭에 의해 달성된다[예컨대, Si 111, Si 110]{여기의 내용과 일치하는 범위만큼 참조에 의해 여기에 병합되는 미국 임시출원 제60/826,354호(2006년 9월 20일 출원됨, "Bulk Quantities of Single Crystal Silicon Micro-/Nanoribbons Generated from Bulk Wafers", Atty. ref. no. 151-06P)를 참조}.

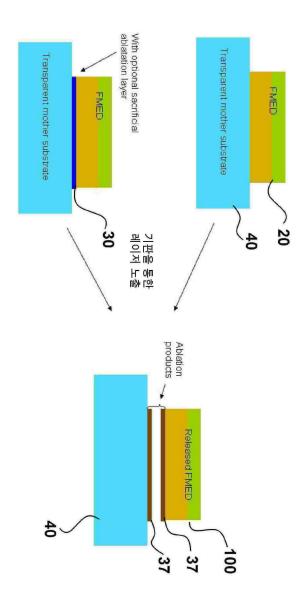

- <108> 예시 2: 레이저 애블레이션(laser ablation)에 의한 전사가능한 구조들의 릴리스.

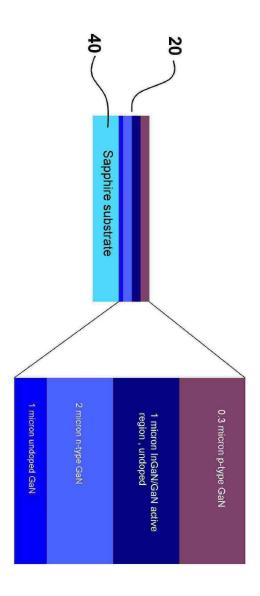

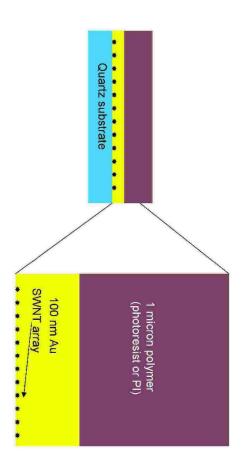

- <109> 방법들은 그라인딩(grinding)/폴리싱(polishing)/에칭(etching)에 의해 모 기판(mother substrate)을 제거함에 의한 릴리스 또는 열 충격(thermal shock)[예컨대, 열 팽창 계수 부정합(thermal expansion coefficient mismatch)]에 의한 릴리스를 포함한다. 또한 릴리스는 삽입된 레이어들의 애블레이션 (ablation)/분해(decomposition)/화학 반응(chemical reaction)[예컨대, 레이저-유도 가열(laser-induced heating)에 의해 야기된 애블레이션/분해/화학 반응]에 의할 수도 있다. 도 6a는 레이저 애블레이션 릴리스 방 법(laser ablation release method)의 개략도를 제공한다. 멀티레이어 구조가 얹혀 있는 표면의 기판(40) 반대 면 상에 위치하는 레이저에 의하는 것과 같이, 기능 레이어(20)를 지지하고 있는 적어도 부분적으로 투명한 기 판(40)을 통해 전자기적 방사(electromagnetic radiation)가 도입된다. 레이저-유도 가열(laser-induced heating)은 20과 40 사이의 계면 표면의 장애(failure of interfacial surface)에 의하거나 레이저-애블레이팅 민감 릴리스 표면(laser-ablating sensitive release surface. 30)의 적어도 부분적인 제거에 의한 전사가능한 FMED(100)의 릴리스를 야기한다. 릴리스 표면(30)은, 애블레이션 결과물들(ablation products. 37)로 지시되는 바와 같이, 구조(100)나 기판(40) 중의 어느 하나 또는 양쪽 모두에 대하여 부분적으로 부착된 채로 남을 수 있 다. 그 결과물들(37)은 요구되는 바에 따라 후속적으로 제거된다. 도 6b는 레이저 애블레이션(laser ablation) 에 의해 LED들을 위한 FMED들을 릴리스하는 데 적당한 기판의 예시이다. 기판(40)은 사파이어 기판(sapphire substrate)에 상응한다. 도 6c는 레이저 애블레이션에 의해 또는 주위 조건들에 자발적인 화학 반응/분해/애블 레이션에 의해 LED들을 위한 FMED들을 릴리스하는 것을 나타낸다. 도 10은 상이한 릴리스 계기들(release signals)[예컨대, 전기(electricity) 및/또는 열(heat)]에 의해 릴리스 레이어들을 선택적으로 제거함으로써 다 결정(polycrystalline)/비결정(amorphous) FMED 물질들을 릴리스하기 위한 기본적 방안을 나타낸다. 도 12는 희생 레이어들의 제거에 의한 비결정 FMED 구조들의 릴리스를 나타낸다.

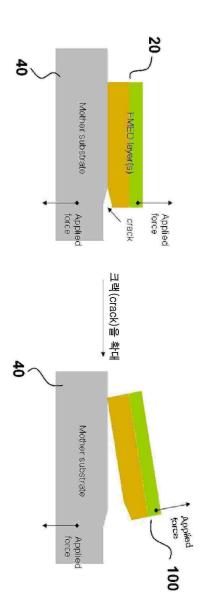

- <110> 예시 3: 유도된 계면 크랙(interfacial crack)의 확대에 의한 전사가능한 구조들의 릴리스.

- <111> 다른 릴리스 메커니즘으로서, FMED들과 모 기판 간의 계면(interface)에 크랙을 도입하고 그 크랙을 확대 (propagate)하기 위해[도 7a 참조] 모 기판으로부터 FMED들을 당겨 떼어내는[예컨대, 고무 스탬프(rubber stamp)를 이용하여] 방식이 있다. 크랙은 다수의 방식으로, 예를 들어, 기계적으로[예컨대, 절단(cutting)에 의해. 도 8b, 도 8c 및 도 12 참조], 화학적으로[예컨대, 에칭에 의해], 또는 열적으로[예컨대, 열 팽창 계수 부정합(thermal expansion coefficient mismatch)에 의해 유도된 충격에 의해] 도입될 수 있다.

- <112> 선택적으로, 전사가능한 구조를 릴리스하기 위한 위의 어떠한 수단은 캐리어 구조(carrier structure)[예를 들어, 탄소 나노튜브들(carbon nanotubes)을 프린팅하기 위한 캐리어 구조로서의 골드 필름(gold film)과 같은 {"Nature Nanotech. Vol 2, p.230" 참조} 캐리어 필름(carrier film){도 8a 참조}]와 조합된다. 이 프로세스는 개별적으로 제작하기 힘든, 많은, 기계적으로 부드러운, 기계적으로 연약한, 화학적으로 연약한, 작은[예컨대,약 50nm 미만, 분자들, SWNT 등] FMED들에 대하여 효과적일 수 있다. 도 8b 및 도 8c는 전사가능한 FMED들을 릴리스하기 위한 캐리어 필름과 기판의 사이에 크랙을 기계적으로 유도하기 위한 구조 및 프로세스의 예시들을 각 제공한다.

- <113> 여기에 설명되는 어떠한 방법들에 의한 릴리스는 선택적으로, 도 9a에 도시된 바와 같이[그리고 도 4 및 도 5에 선택적으로 제공된 바와 같이] 모 기판(40)을 재사용하여 향상된 제조 비용 절감을 제공하는 프로세스에 통합된 다.

- <114> 도 19는 릴리스 레이어들[희생 레이어들]의 부분적 제거[한번에 수 개의 릴리스 레이어들을 제거{도 3a 참조}] 에 의한 기능 레이어들의 부분적 릴리스를 나타내는 개략도이다. 릴리스 레이어들이 부분적으로 제거된 후에 디 바이스들이 기판에 결속된(tethered) 채로 남아있기 때문에, 릴리스가 "부분적(partial)"이라고 지칭된다. 디바 이스들의 완전 릴리스 또는 분리는, 예를 들어, 탄성체 스탬프(elastomer stamp)를 이용한 테더링 구조 (tethering structure)들의 분쇄(fracture) 및 회수(retrieval)에 의한, 그들의 제거 시에 일어난다. 또한 이 도면은 멀티레이어 스택들의 재-증착(re-deposition)을 위해 기판을 준비하기 위하여 앵커링 구조(anchoring structure)들을 제거하는 단계들을 보여준다. 도 19에 도시된 프로세스에 따라 프린트가능한(printable) 디바이 스들을 산출할 수 있는 멀티레이어 구조들의 어떤 예시들이 도 3c 내지 도 3e에 도시되어 있다. 그 프로세스의 상세 내용이 도 4에 도시되어 있다. 도 4는 추가적 전사가능한 FMED들의 후속적인 생성을 위한 기판의 선택적 재사용과 함께 "한번에 다수의 레이어들(multiple-layers-at-a-time)" 방식에 의해 광전소자들을 위한 FMED들을 릴리스하는 것을 나타낸다. 기능 레이어들은 에피택셜형 성장 반도체들(epitaxially grown semiconductors)을 구비한다. 또한 그 프로세스는 도 12에서 설명되는 프로세스와 비슷하게 비결정(amorphous) 또는 다결정 (polycrystalline) 물질들에 대하여 동작한다. 간단하게, GaAs 기판이 얻어진다. 도 3c에 도시된 에필레이어들 을 예를 들어, MOCVD, MBE 등에 의해 GaAs 기판 상에 성장시킨다[각각 트랜지스터들, LED들에 대한 도 3d, 도 3e의 비슷한 프로세스]. 필요에 따라 성장에 앞서 기판을 선-처리(pre-treat)한다[선택적으로 CMP가 요구된다]. 기능 및 희생 레이어들을 증착(depositing)하거나 에피택셜형으로 성장(epitaxially growing)시키기 전에, 기판 에 인접하는 GaAs의 약 ~200nm 버퍼 레이어(buffer layer)를 성장시킨다. 상단 에필레이어의 표면 일부분은 패 터닝을 위한 리소그래퍼(lithography)의 형태로 그리고 플라즈마-강화 화학적 증기 증착(PECVD: Plasma-Enhanced Chemical Vapor Deposition)에 의해 SiO2로 마스킹될 수 있다. 표면으로부터 어떤 Alo96Gao04As 희생 레이어 내부[예를 들어, 기판에 가장 가까운 희생 레이어 내부]의 어느 거리까지 Cl/Ar/H 플라즈마(plasma)를 이용하여 에필레이어들의 마스킹되지 않은 영역들을 에칭한다. 그 희생 레이어가 기판으로부터 가장 먼 것이면 안된다[그 경우에는, 릴리스가 도 3b 및 도 5에 도시된 바와 같은 "한번에 하나씩(one-at-a-time)" 프로세스에 해당될 것이다]. 기판을 농축된 HF에 노출하여, 그 노출된 희생 레이어들을 적어도 부분적으로 제거하고 희생 레이어들 위의 기능 에필레이어들을 측면 언더컷팅(lateral undercutting)에 의해 릴리스한다[HF는 그것이 희생 레이어를 공격하는 것보다 더 느리게{1/10 미만의 에칭율(etch rate)} 기능 에필레이어들을 공격한다]. 일렉트 로스피닝(electrospinning), 잉크 젯 프린팅(ink jet printing) 또는 유체 어셈블리(fluidic assembly)를 위한 솔벤트 교환(solvent exchange)이나 스탬핑(stamping) 등에 의해 기판으로부터 릴리스된 FMED들을 분리한다. HF 를 사용하여 희생 레이어들의 나머지 부분들을 제거한다. 위에 있는(overlying) 기능 에필레이어들의 나머지 부 분들[앵커링 구조(anchoring structure)들 등]을 씻고/닦아낸다(wash/rub away). 제거된 레이어들의 바로 아래 에 원래 있던 기능 레이어들이 이제 노출되어 기판의 표면 상에 있다. 마스킹과 HF 제거 사이의 단계들을 반복 함으로써, 기판 상에 아무 희생 레이어들도 남지 않을 때까지 기능 레이어들의 세트들[각각의 세트는 희생 레이 어들에 의해 분리됨]을 릴리스한다. 선택적인 기판의 재사용을 위해, 이러한 단계들이 요구되는 바에 따라 반복 된다.

- <115> 도 20은 릴리스 레이어들[희생 레이어]의 부분적 제거[한번에 하나씩 릴리스 레이어를 제거{도 3b 참조}]에 의한 기능 레이어들의 부분적 릴리스를 나타내는 개략도이다. 릴리스 레이어들이 부분적으로 제거된 후에 디바이스들이 기판에 결속된(tethered) 채로 남아있기 때문에, 릴리스가 "부분적(partial)"이라고 지칭된다. 디바이스들의 완전 릴리스 또는 분리는, 예를 들어, 탄성체 스탬프(elastomer stamp)를 이용한 테더링 구조(tethering structure)들의 분쇄(fracture) 및 회수(retrieval)에 의한, 그들의 제거 시에 일어난다. 또한 이 도면은 "한번에 한 레이어씩 릴리스하는 프로세스(one-layer-at-a-time release process. 도 3b 참조)"를 반복하기 위해

기판을 준비하기 위하여 그리고 멀티레이어 스택들의 재-증착(re-deposition)을 위해 기판을 준비하기 위하여 앵커링 구조(anchoring structure)들을 제거하는 단계들을 보여준다. 여기에 도시된 프로세스에 따라 프린트가 능한(printable) 디바이스들을 산출할 수 있는 멀티레이어 구조들의 어떤 예시들이 도 3c 내지 도 3e에 도시되 어 있다. 그 프로세스의 상세 내용이 도 5에 도시되어 있다. GaAs 웨이퍼와 같은 기판은 도 3c에 도시된 기능 레이어와 같은 에필레이어들의 성장[MOCVD, MBE 등에 의함]에 대하여 지지(support)를 제공한다. 그 기판은 필 요에 따라 성장에 앞서 선-처리(pre-treat)될 수 있다[예컨대, CMP]. 릴리스 및 기능 레이어들의 증착이나 에피 택셜형 성장(epitaxial growth) 전에 기판에 인접하는 GaAs의 ~200nm 버퍼 레이어(buffer layer)를 성장시키는 것이 필요할 수 있다. 패터닝을 위한 어떤 형태의 리소그래피(lithography)로 그리고 플라즈마-강화 화학적 증 기 증착(PECVD: Plasma-Enhanced Chemical Vapor Deposition)에 의해 SiO₂로 상단 에필레이어의 표면 일부분을 마스킹한다. 표면으로부터 제 1 Al<sub>0.96</sub>Ga<sub>0.04</sub>As 희생 레이어 내부의 어느 거리까지 Cl/Ar/H 플라즈마(plasma)를 이 용하여 에필레이어들의 마스킹되지 않은 영역들을 에칭한다. 기판을 농축된 HF에 노출하여, 그 노출된 희생 레 이어[하나]를 적어도 부분적으로 제거하고 희생 레이어 위의 에필레이어들[기능 레이어들]을 측면 언더컷팅 (lateral undercutting)에 의해 릴리스한다[HF는 그것이 희생 레이어를 공격하는 것보다 더 느리게{1/10 미만의 에칭율(etch rate)} 기능 에필레이어들을 공격한다]. 일렉트로스피닝(electrospinning), 잉크 젯 프린팅(ink jet printing) 또는 유체 어셈블리(fluidic assembly)를 위한 솔벤트 교환(solvent exchange)이나 스탬핑 (stamping) 등에 의해 기판으로부터 릴리스된 FMED들을 분리한다. 마스킹과 HF 제거 사이의 단계들을 반복함으 로써, 기판 상에 아무 희생 레이어들도 남지 않을 때까지 기능 레이어들을 릴리스한다. 선택적인 기판의 재사용 을 위해, 이러한 단계들이 요구되는 바에 따라 반복된다.

<116>

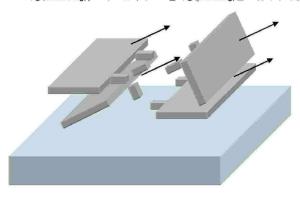

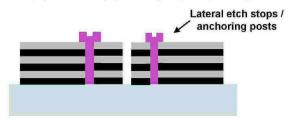

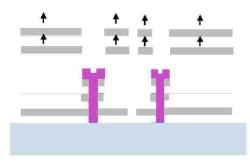

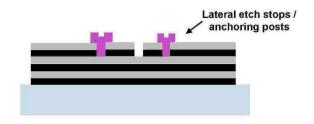

도 21은 한번에 수 개의 릴리스 레이어들[희생 레이어들]을 제거함으로써[도 3a 참조] 측면 에칭-방지(lateral etch stop)들 또는 앵커링 포스트(anchoring post)들을 이용하여 기능 레이어들을 부분적으로 릴리스하는 것의 개략도이다. 릴리스 레이어들이 제거된 후에 디바이스들이 측면 에칭-방지들/앵커링 포스트들을 통해 기판에 결 속된(tethered) 채로 남아있기 때문에, 릴리스가 "부분적(partial)"이라고 지칭된다. 디바이스들의 완전 릴리스 또는 분리는, 예를 들어, 탄성체 스탬프(elastomer stamp)를 이용한 테더링 구조(tethering structure)들의 분 쇄(fracture) 및 회수(retrieval)에 의한, 그들의 제거 시에 일어난다. 또한 이 도면은 멀티레이어 스택들의 재 -증착(re-deposition)을 위해 기판을 준비하기 위하여 측면 에칭-방지들/앵커링 포스트들을 제거하는 단계들을 보여준다. 여기에 도시된 프로세스에 따라 프린트가능한(printable) 디바이스들을 산출할 수 있는 멀티레이어 구조들의 어떤 예시들이 도 3c 내지 도 3e에 도시되어 있다. 그 프로세스의 상세 내용이 이하에 설명된다. 기능 레이어들은 에피택셜형 성장 반도체들(epitaxially grown semiconductors)을 구비한다. 또한 그 프로세스는 도 12에서 설명되는 프로세스와 비슷하게 비결정(amorphous) 또는 다결정(polycrystalline) 물질들에 대하여 동작 한다. 간단하게, GaAs 기판이 얻어진다. 도 3c에 도시된 에필레이어들을 예를 들어, MOCVD, MBE 등에 의해 GaAs 기판 상에 성장시킨다[각각 트랜지스터들, LED들에 대한 도 3d, 도 3e의 비슷한 프로세스]. 필요에 따라 성장에 앞서 기판을 선-처리(pre-treat)한다[선택적으로 CMP가 요구된다]. 기능 및 희생 레이어들을 증착(depositing) 하거나 에피택셜형으로 성장(epitaxially growing)시키기 전에, 기판에 인접하는 GaAs의 약 ~200nm 버퍼 레이어 (buffer layer)를 성장시킨다. 상단 에필레이어의 표면 일부분은 패터닝을 위한 리소그래피(lithography)의 형 대로 그리고 플라즈마-강화 화학적 증기 증착(PECVD: Plasma-Enhanced Chemical Vapor Deposition)에 의해 SiO<sub>2</sub>로 마스킹될 수 있다. 표면으로부터 어떤 Al<sub>0.96</sub>Ga<sub>0.04</sub>As 희생 레이어 내부[예를 들어, 기판에 가장 가까운 희 생 레이어 내부]의 어느 거리까지 Cl/Ar/H 플라즈마(plasma)를 이용하여 에필레이어들의 마스킹되지 않은 영역 들을 에칭한다. 그 희생 레이어가 기판으로부터 가장 먼 것이면 안된다[그 경우에는, 릴리스가 도 3b 및 도 5에 도시된 바와 같은 "한번에 하나씩(one-at-a-time)" 프로세스에 해당될 것이다]. 저압 화학적 증기 증착(lowpressure chemical vapor deposition)에 의해 질화 규소(silicon nitride)의 부합 코팅(conformal coating)을 증착한다. 측면 에칭-방지들 및/또는 앵커링 포스트들을 정의하기 위해서, 예를 들어, 불소 플라즈마(fluorine plasma)를 이용한 에칭 및 포토리소그래피(photolithography)에 의해 질화 규소를 패턴화한다. 기판을 농축된 HF에 노출하여, 그 노출된 희생 레이어들을 적어도 부분적으로 제거하고 희생 레이어들 위의 기능 에필레이어들 을 측면 언더컷팅(lateral undercutting)에 의해 릴리스한다[HF는 그것이 희생 레이어를 공격하는 것보다 더 느 리게{1/10 미만의 에칭율(etch rate)} 기능 에필레이어들을 공격한다]. 일렉트로스피닝(electrospinning), 잉크 젯 프린팅(ink jet printing) 또는 유체 어셈블리(fluidic assembly)를 위한 솔벤트 교환(solvent exchange)이 나 스탬핑(stamping) 등에 의해 기판으로부터 릴리스된 FMED들을 분리한다. HF를 사용하여 희생 레이어들의 나 머지 부분들을 제거한다. 질화 규소를 제거하기 위해 불소 플라즈마를 사용한다. 위에 있는(overlying) 기능 에 필레이어들의 나머지 부분들[앵커링 구조(anchoring structure)들 등]을 씻고/닦아낸다(wash/rub away). 제거 된 레이어들의 바로 아래에 원래 있던 기능 레이어들이 기판의 표면 상에 깨끗하게 노출될 때까지 HF, 불소 플 라즈마 및 씻는 단계를 반복한다. 마스킹(masking)과 세척(cleaning) 사이의 단계들을 반복함으로써, 기판 상에 아무 희생 레이어들도 남지 않을 때까지 기능 레이어들의 세트들[각각의 세트는 희생 레이어들에 의해 분리됨]을 릴리스한다. 선택적인 기판의 재사용을 위해, 이러한 단계들이 요구되는 바에 따라 반복된다.

<117>

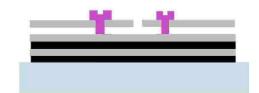

- 도 22는 한번에 하나씩 릴리스 레이어[희생 레이어]를 제거함으로써[도 3b 참조] 측면 에칭-방지(lateral etch stop)들 또는 앵커링 포스트(anchoring post)들을 이용하여 기능 레이어들을 부분적으로 릴리스하는 것의 개략 도이다. 릴리스 레이어들이 제거된 후에 디바이스들이 측면 에칭-방지들/앵커링 포스트들을 통해 기판에 결속된 (tethered) 채로 남아있기 때문에, 릴리스가 "부분적(partial)"이라고 지칭된다. 디바이스들의 완전 릴리스 또 는 분리는, 예를 들어, 탄성체 스탬프(elastomer stamp)를 이용한 테더링 구조(tethering structure)들의 분쇄 (fracture) 및 회수(retrieval)에 의한, 그들의 제거 시에 일어난다. 또한 이 도면은 "한번에 한 레이어씩 릴리 스하는 프로세스(one-layer-at-a-time release process. 도 3b 참조)"를 반복하고 멀티레이어 스택들의 재-증 착(re-deposition)을 위해 기판을 준비하기 위하여 측면 에칭-방지들/앵커링 포스트들을 제거하는 단계들을 보 여준다. 도 22에 도시된 프로세스에 따라 프린트가능한(printable) 디바이스들을 산출할 수 있는 멀티레이어 구 조들의 어떤 예시들이 도 3c 내지 도 3e에 도시되어 있다. 그 프로세스의 상세 내용이 이하에 설명된다. GaAs 웨이퍼와 같은 기판은 도 3c에 도시된 기능 레이어와 같은 에필레이어들의 성장[MOCVD, MBE 등에 의함]에 대하 여 지지(support)를 제공한다. 그 기판은 필요에 따라 성장에 앞서 선-처리(pre-treat)될 수 있다[예컨대, CMP]. 릴리스 및 기능 레이어들의 증착이나 에피택셜형 성장(epitaxial growth) 전에 기판에 인접하는 GaAs의 ~200nm 버퍼 레이어(buffer layer)를 성장시키는 것이 필요할 수 있다. 패터닝을 위한 어떤 형태의 리소그래피 (lithography)로 그리고 플라즈마-강화 화학적 증기 증착(PECVD: Plasma-Enhanced Chemical Vapor Depositio n)에 의해 SiO<sub>2</sub>로 상단 에필레이어의 표면 일부분을 마스킹한다. 표면으로부터 제 1 Al<sub>0.96</sub>Ga<sub>0.04</sub>As 희생 레이어 내부의 어느 거리까지 Cl/Ar/H 플라즈마(plasma)를 이용하여 에필레이어들의 마스킹되지 않은 영역들을 에칭한 다. 저압 화학적 증기 증착(low-pressure chemical vapor deposition)에 의해 질화 규소(silicon nitride)의 부합 코팅(conformal coating)을 증착한다. 측면 에칭-방지들 및/또는 앵커링 포스트들을 정의하기 위해서, 예 를 들어, 불소 플라즈마(fluorine plasma)를 이용한 에칭 및 포토리소그래피(photolithography)에 의해 질화 규소를 패턴화한다. 기판을 농축된 HF에 노출하여, 그 노출된 희생 레이어[하나]를 적어도 부분적으로 제거하고 희생 레이어 위의 에필레이어들[기능 레이어들]을 측면 언더컷팅(lateral undercutting)에 의해 릴리스한다[HF 는 그것이 희생 레이어를 공격하는 것보다 더 느리게{1/10 미만의 에칭율(etch rate)} 기능 에필레이어들을 공 격한다]. 일렉트로스피닝(electrospinning), 잉크 젯 프린팅(ink jet printing) 또는 유체 어셈블리(fluidic assembly)를 위한 솔벤트 교환(solvent exchange)이나 스탬핑(stamping) 등에 의해 기판으로부터 릴리스된 FMED들을 분리한다. HF를 사용하여 희생 레이어들의 나머지 부분들을 제거한다. 질화 규소를 제거하기 위해 불 소 플라즈마를 사용한다. 위에 있는(overlying) 기능 에필레이어들의 나머지 부분들[앵커링 구조(anchoring structure)들 등]을 씻고/닦아낸다(wash/rub away). 제 1 희생 레이어의 바로 아래에 원래 있던 기능 레이어들 이 기판의 표면 상에 깨끗하게 노출될 때까지 HF, 불소 플라즈마 및 씻는 단계를 반복한다. 마스킹과 HF 제거 사이의 단계들을 반복함으로써, 기판 상에 아무 희생 레이어들도 남지 않을 때까지 기능 레이어들을 릴리스한다. 선택적인 기판의 재사용을 위해, 이러한 단계들이 요구되는 바에 따라 반복된다.

- <118> 도 23은 기능 레이어들이 도 20에서 설명된 것과 비슷한 프로세스를 통해 부분적으로 릴리스된 후에, 점착-방지 (anti-stiction) 또는 활성화(activation) 레이어들을 갖춘 기능 레이어들을 포스트-릴리스 처리하는 것(post-release treatment)에 관한 개략도이다. 점착-방지 또는 활성화 레이어들[때때로 셀프-어셈블리 모놀레이어 (SAM: self-assembled monolayer)들]은 릴리스된 레이어들과 밑에 있는 레이어들 간의 접착을 회피[점착-방지 (anti-stiction)]하거나 릴리스된 레이어들과 다른 어떤 실체(entity)[예컨대, 탄성체 스탬프들(elastomer stamps), 나노입자들(nanoparticles), 생물학적 실체들(biological entities) 등] 간의 접착을 증진[활성화 (activation)]하도록 작용한다. 도 23에 도시된 프로세스가 적용될 수 있는 시스템의 예시가 도 3d에 도시되어 있다. 예컨대, 포토리소그래피(photolithography) 및 염소 플라즈마 에칭(chlorine plasma etching)에 의해 디 바이스들을 정의하고 HF에 의해 AlGaAs 릴리스 레이어를 부분적으로 제거한 후에, 유기질 티올-종결 분자 (organic thiol-terminated molecule)의 에탄올 솔루션(ethanolic solution)이 노출된 GaAs 표면들을 처리하는 데 사용될 수 있다. 점착-방지(anti-stiction)를 위해, 이 분자는 알칸티올(alkanethiol)[예컨대, 핵사데카네티올(hexadecanethiol)] 또는 과불소화 알칸티올(perfluorinated alkanethiol)일 수 있다. 활성화(activation)를 위해, 그 티올(thiol)은 반응성 화학 그룹들(reactive chemical groups)[예컨대, 옥탄디티올(octanedithiol)] 에 의해 추가적으로 종결될 수 있다.

- <119> 도 35 및 도 36은 앵커링 방안의 추가적인 예시를 제공한다. 그 앵커링 방안은, 이질적 앵커링 방안

(heterogeneous anchoring strategy)[도 21 참조]에 의하는 것과 같이, 잘 정의된 위치들에서 앵커링 구조들로부터 끊기는 전사가능한 구조들의 생성을 더 향상시킨다. 특히, 동질적 앵커링(homogeneous anchoring)[도 20 참조]에 대한 이질적 앵커링(heterogeneous anchoring)의 장점들은 끊길 수 있는 테더 포인트(breakable tether point)들을 설계함에 있어서의 유연성, 강화된 전사 제어, 및 전사 등록가능성(transfer registrability)의 향상을 포함한다. 또한, 다양한 앵커링 프로세스들은 웨이퍼 기판 영역의 더 효율적인 사용을 제공한다. 패턴화된 희생 영역들은 전사가능한 구조들이 잘 정의된 위치들에서 앵커링 구조들로부터 끊기는 것을 보장할 능력을 제공한다. 또한, 패턴화된 희생 영역들은 영역 범위를 증가시킨다. 예를 들어, 앵커링 구조들이 희생 레이어를 제거하는 약품에 의해 언더컷팅되지 않기 때문에, 그들은 전사가능한 구조의 구멍 (perforation)들보다 넓지 않아도 된다. 도 36은 도 35에 도시된 앵커링 개념을 나타내는 것으로서, 그것의 실제 적용예이다[실리콘 웨이퍼로부터 플라스틱으로 가장 투명한 골드 메시(gold mesh)를 프린팅함].

- <120> 여기에 개시된 프로세스들은 멀티레이어 디바이스로부터 기판이나 기판에 의해 지지되는 컴포넌트로 구조들을 높은 처리율로 프린팅하여 제조 시간과 비용을 감소시키는 데 특히 적합하다. 예를 들어, 도 37은 7-레이어 구조의 SEM이며, 인접하는 GaAs 레이어들은 Alo.gGao.1As 레이어들에 의해 분리된다. 에피구조(epistructure)들은 인산(phosphoric acid) 및 과산화수소(hydrogen peroxide)에 의해 에칭된다. 멀티레이어 마이크로구조들은 포토리소그래피 및 습식 에칭에 의해 GaAS 기판 상의 에필레이어들로부터 가공된다(machined).

- <121> 도 38은 7 GaAs 레이어들의 동시적 릴리스 후에 PDMS 스탬프들 상으로 회수되는 7 GaAs 레이어들의 포토그래프이다. 비슷한 회수가 여기에 개시된 개별적으로 한 레이어씩 릴리스하는 방식(layer-by-layer release)에 대하여도 예상된다. 간단하게, 릴리스 절차는 S1802 포토레지스트로 에피구조를 마스킹하는 것에 관련된다. 그 마스킹된 구조는 1분 동안 H<sub>3</sub>PO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>:DI{1:13:12}로 에칭된다. 포토레지스트가 아세톤(acetone)에 의해 벗겨지고 이후에 릴리스 레이어들이 35 초 동안 49% HF에 의해 화학적으로 제거되며 N<sub>2</sub>에 의한 건식 린싱(dry rinsing)이 실행된다. 레이어들은 PDMS 스탬프들을 이용하여 순차적으로 박리된다(exfoliated)[도 38에 1 내지 8로 표시됨]. 제 8 스탬프는 "잔존물들(left-overs)"을 체크하는 데 사용된다. 도 39는 PDMS 스탬프 표면 상의 멀티레이어 도너(donor) 기판으로부터 박리된 GaAs 레이어의 광학 이미지를 제공한다. 이 레이어들은 디바이스 기판으로 또는 컴포넌트나 디바이스 기판으로 프린팅되도록 준비된다.

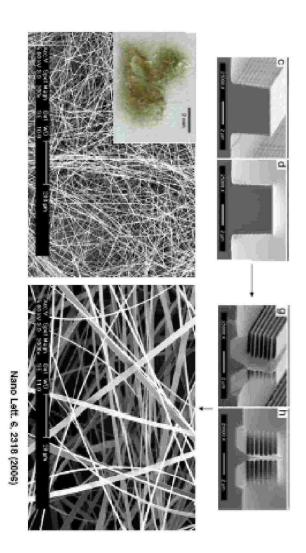

- <122> 예시 4: 벌크 웨어퍼(Bulk Wafer)들로부터 생성되는 대량의 단결정 실리콘 마이크로-/나노리본들(Single-Crystal Silicon Micro-/Nanoribbons).

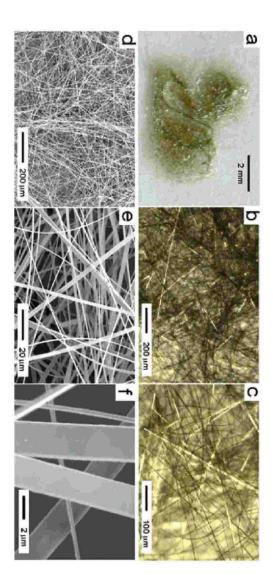

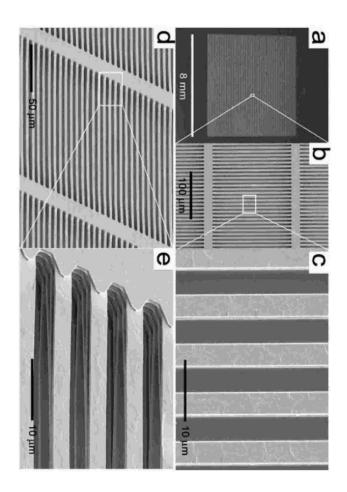

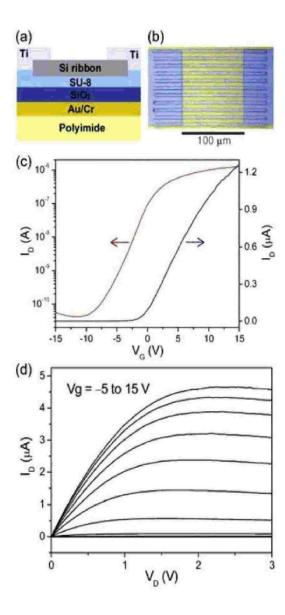

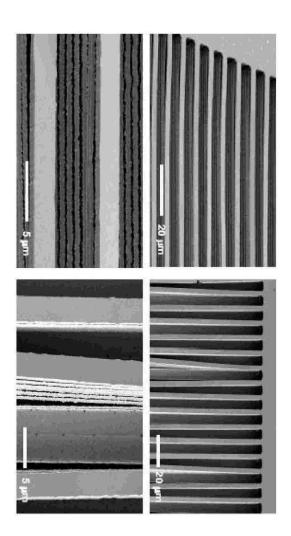

- <123> 이 예시는 벌크 실리콘[111] 웨이퍼들로부터 대량으로 치수적으로 균일한 고품질의 단결정 실리콘 마이크로- 및 나노리본들을 생산하기 위한 방안을 설명한다. 이 프로세스는, 웨이퍼의 전체 표면에 걸쳐 균일한 두께들 및 리소그래피식으로 정의된 길이들과 폭들을 가지는 멀티레이어 스택 리본들(multilayer stacks of ribbons)을 생산하기 위해서, 측벽들 상에 정의된 제어된 리플 구조(controlled rippled structure)들을 갖춘 에칭 트렌치 (etched trench)들을 이용하며 또한 마스킹 물질들의 경사진 증발증착(angled evaporation) 및 실리콘의 이방성 습식 에칭(anisotropic wet etching)을 이용한다. 수십에서 수백 나노미터의 두께들, 마이크로미터 범위의 폭들, 및 수 센티미터에 이르는 길이들을 가지는 리본들이 이 접근법을 이용하여 대량으로 생산된다. 프린팅 프로세스들은 그러한 리본들의 조직된 어레이를 다른 범위의 기판들로 한 레이어씩 전사하는 것을 가능하게 한다. 플라스틱 기판들 상에 형성되는 박막 타입 트랜지스터들에서 이 리본들에 의해 좋은 전기적 특성들[이동도 (mobilities)들 ~190 cm²V¹s¹, on/off > 10⁴]이 달성될 수 있으며, 그럼으로써 하나의 잠재적인 영역의 어플리케이션을 구현할 수 있다.

- 전자 분야, 광전자 분야, 센싱, 및 다른 분야들에서의 다수의 어플리케이션들에 대하여 와이어(wire)들, 리본 (ribbon)들, 및 입자(particle)들의 형태인 단결정 실리콘의 나노구조 엘리먼트(nanostructured element)들이 관심 받고 있다. 리본 외형(ribbon geometry)은 어떤 특정한 디바이스들에 대하여 중요하다. 왜냐하면, 그것이, 예를 들어, 화학 센싱(chemical sensing) 및 광 검출(photodetection)을 위한 넓은 평탄 표면들, 그리고 트랜지스터들의 채널 영역들을 효율적으로 채울 수 있는 외형들을 제공하기 때문이다. 실리콘 나노와이어 (nanowires)들<sup>1</sup>을 위해 이용되는 잘 개발된 화학 합성 접근법들(well-developed chemical synthetic approaches)에 관련된 성장 기법(growth technique)들이 적응되고 적용되어 Si 나노리본(nanoribbon)들<sup>2</sup>을 생산할 수 있었다. 그러나, 산화물들(oxides)[ZnO, SnO<sub>2</sub>, Ga<sub>2</sub>O<sub>3</sub>, Fe<sub>2</sub>O<sub>3</sub>, In<sub>2</sub>O<sub>3</sub>, CdO, PbO<sub>2</sub> 등등]<sup>3</sup>, 황화물들 (sulfides)[CdS, ZnS]<sup>4</sup>, 질화물(nitride)[GaN]<sup>5</sup>, 그리고 셀레나이드들(selenides)[CdSe, ZnSe, Sb<sub>2</sub>Se<sub>3</sub>]<sup>6</sup>과 같은

물질들에 대한 이 절차들과 그 비슷한 것들에 의해 제공되는 리본들의 산출들 및 치수 제어(dimensional control)의 레벨들은 아직 조심스럽다. 반면에, 반도체 웨이퍼들의 상단 표면들을 리소그래피식으로 프로세싱하 는 것에 의존하는 접근법들은 잘 제어된 두께들, 폭들, 길이들, 결정도(crystallinity), 및 도핑 레벨(doping level)들을 가능하게 한다. 이 방법들은, 마이크로미터로부터 나노미터에 이르는 범위의 두께들을 가지며 Si, SiGe, 이중 레이어(bilayered) Si/SiGe, GaAs, GaN, 및 다른 것들로 구성되는 리본(ribbon)들, 튜브(tube)들, 및 얇은 막(membrane)들을 형성할 수 있다<sup>7-12</sup>. 또한, 다양한 프로세스들이 조직된 어레이들 형태의 이 엘리먼트 들을 디바이스 집적을 위해 다른 기판들로 전사할 수 있다. 이 "탑 다운(top down)" 접근법은 성장 기법(growth technique)들에 비해서 3 가지 중요한 단점들을 가진다. 첫째, ~100nm 미만의 폭들을 가지는 엘리먼트들은 리소 그래피에서의 실제적 제한들로 인해서 제작하기 어렵다. 둘째, 박막 또는 벌크 웨이퍼 형태로 성장될 수 있는 그 물질들만이 사용될 수 있다. 셋째, 많은 어플리케이션들에 대하여 가장 중대한 점으로서, 마이크로-/나노구 조들의 대량 생산은 많은 수의 웨이퍼들[그들 각각이 매우 비쌀 수 있음]을 필요로 한다. 첫째 단점은 그러한 작은 치수들을 가지는 구조들을 필요로 하지 않는 많은 어플리케이션들에 무관하다. 물론 둘째 단점은 많은 중 요한 물질들[예컨대, 실리콘]에 적용되지 않는다. 이 예시는 셋째 제한을 다루는 결과들을 제시한다. 특히, 그 것은 단일 프로세싱 시퀀스에서 표준 벌크 Si 웨이퍼들로부터 수십 나노미터 이하의 두께들을 가지는 많은 수의 고품질 Si 리본들을 생성하기 위한 단순 방법을 도입한다. 간단하게, 그 접근법은 잘 정의된 리플 측벽 형태들 (rippled sidewall morphologies)을 갖춘 트렌치들을 생산하기 위해서, 에칭 마스크를 통한 실리콘 웨이퍼들의 제어 깊이 반응성 이온 에칭(controlled deep reactive ion etching)으로 시작한다. 이 리플들 상에 일정한 각 도로 증착되는 금속의 조준된 플럭스(collimated flux)는 웨이퍼의 표면에 평행한 평면들을 따라서 실리콘의 높 은 이방성 습식 에칭에 대한 마스크들로 동작하는 분리된 금속 라인들을 생성한다. 이 단일의 에칭 단계는 멀티 레이어 스택 외형들인 대량의 실리콘 리본들을 생성한다. 이 리본들은 웨이퍼로부터 제거될 수 있으며, 트랜지 스터들과 같은 디바이스들로의 집적을 위해서, 리소그래피식으로 정의된 그들의 공간적 정렬(spatial order)을 지키거나 지키지 않으면서 요구되는 기판들 상으로 프린팅되는 솔루션 캐스트 또는 건식 전사가 수행된다. 이 접근법은 표준 청정실 프로세싱 장비(standard cleanroom processing equipment)에만 의존한다. 그 결과, 그것 은, 실리콘 마이크로-/나노구조들에 관심을 가지지만 직접 합성 기법들을 사용하여 대량으로 그들을 생성하는 데 필요한 레서피(recipe)들과 특화된 성장 챔버(specialized growth chamber)들을 가지지 않는 연구자들에게 유용할 수 있다.

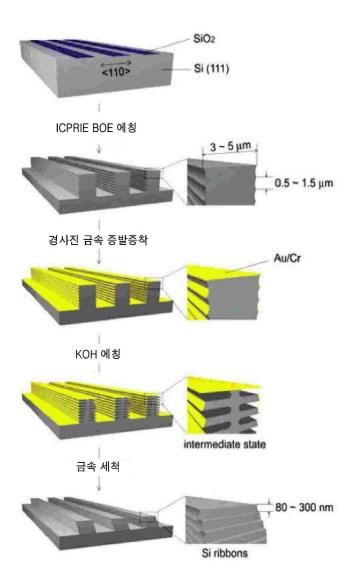

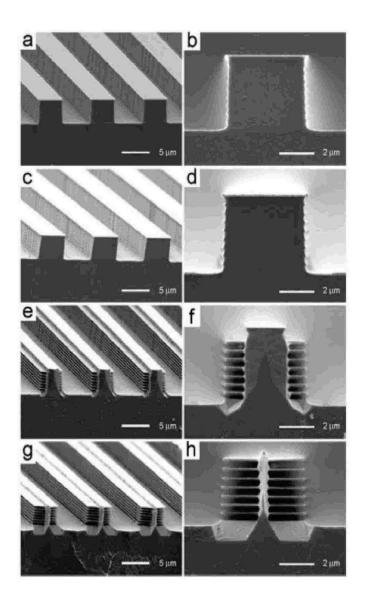

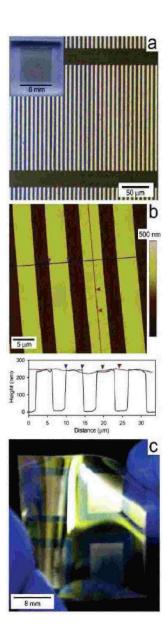

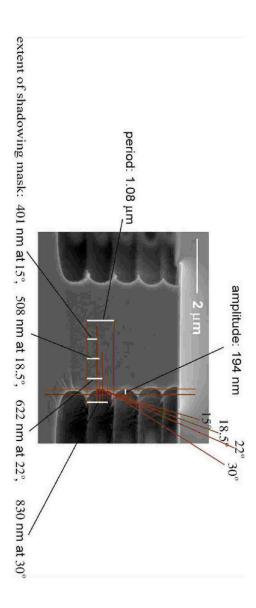

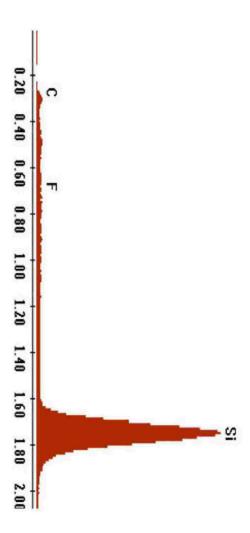

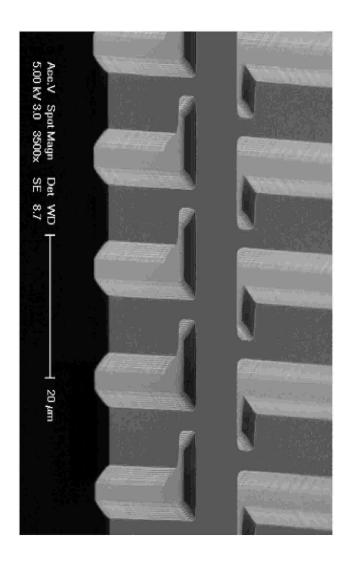

도 25는 제작 시퀀스의 개략도를 제시한다. 처음 단계에서, 2시간 동안 1100℃에서의 건식 열 산화(dry thermal oxidation)는 웨이퍼의 표면 상에 얇은[~150nm] SiO<sub>2</sub> 레이어를 생산했다. 접착 증진제(adhesion promoter)[1,1,1,3,3,3-hexamethyldidilazane (HMDS, Acros Organics)]를 코팅한 후에, 접촉 모드 포토리소그 래피[Shipley 1805 photoresist (PR) and MF-26A developer]는 PR 마스크를 제공했다. 5분 동안 110℃에서의 어닐링(annealing)이 그 뒤를 따른다. 1분 30초 동안 버퍼 산화물 에칭액(buffered oxide etchant)[BOE, Transene Co.] 솔루션에서의 습식 에칭 그리고 아세톤에서의 잔여 PR 세척은 SiO2 라인들을 웨이퍼 상에 생성했 다. 이 라인들은 실리콘의 유도성으로 결합된 플라즈마 반응성 이온 에칭(inductively coupled plasma reactive ion etching)[STS-ICPRIE, STS Mesc Multiplex Advanced Silicon Etcher]을 위한 마스킹 레이어들을 제공했다. 에칭 트렌치들의 측벽들이 {110} 평면들을 노출시키도록, 그 라인들의 방위는 도 25에 도시된 바와 같이 <110> 방향에 수직이었다. 주로 ICPRIE 도구들은 실리콘을 에칭하는 것과 그 에칭에 대하여 측벽들을 보호 하기 위해 불소 중합체(fluoropolymer)를 증착하는 것을 교대하는 싸이클들을 이용함으로써 높은 종횡비 구조 (high aspect ratio structure)들 및 평평한 수직 측벽들을 생산하도록 설계된다<sup>13</sup>. 그 대신에 우리는 그 프로 세스 싸이클들을 수정하여 가스 흐름율(gas flow rate), 전극 파워(electrode power), 챔버 압력(chamber pressure), 및 에칭 싸이클 기간(etching cycle duration)의 적당한 제어를 통해 이 측벽들에 잘 제어된 리플 구조의 돋을새김(well-controlled rippled structures of relief)을 조각하였다. 각각 80nm에서 1.5μm 및 50-450nm에 이르는 범위의 주기들과 크기들을 가지는 리플들은 프로세싱된 영역들[4인치. 웨이퍼 사이즈] 위에 반 복적으로 그리고 균일하게 달성될 수 있다. 예시로서, 각각 540nm 및 130nm의 주기들과 크기들을 생산함에 있어 서 파라미터들은 다음과 같다. 가스 흐름, 에칭에 대하여 O₂/SF<sub>6</sub> = 13/130sccm[cubic centimeter per minute at STP] 그리고 증작에 대하여 C<sub>4</sub>F<sub>8</sub> = 110sccm; 가스 압력, 94mTorr; 에칭 파워, 유도성 결합 플라즈마(ICP: inductive coupled plasma)/플래튼(P: platen)에 대하여 600/12W; 증착 파워, ICP/P에 대하여 600/0W; 에칭 기 간, 7초; 증착 기간, 5초. 증착 싸이클들 간의 에칭 조건들은 이 리플 구조들을 정의한다.  $\mathrm{SF}_6/\mathrm{O}_2$  혼합물이 거의 등방성 에칭을 주기 때문에, 리플들의 크기들과 주기들은 관련되어 있다. 가장 작은 리플 구조는 80nm의 주기와

<125>

50nm의 크기를 가진다; 가장 큰 리플 구조는 1.5μm의 주기와 450nm의 크기를 가진다. 에칭된 샘플들을 10분 동 안 100℃의 NH40H/H202/H20 = 1:1:5에 가라앉히는(immersing) 것은 측벽들 상의 불소 중합체를 제거시켰다. 그 샘플을 2분 동안 BOE 솔루션에 담그는(dipping) 것[탈이온화된 물에서의 린싱(rinsing in deionized water)이 그 뒤를 따름]은 잔여  $SiO_2$  레이어를 제거시켰다. 다음에, 조준된 플럭스 $(collimated\ flux)$ 에 의한 Cr/Au[3/47nm]의 경사진[웨이퍼의 정규 축으로부터 15°] 전자 빔 증발증착은 돌출된 돋을새김(overhang relief)에 연관된 전조(shadowing)로 인해 모든 리플들의 낮은 영역들[높은 영역들은 아님]을 따라서 물리적 에 칭 마스크들을 형성시켰다. 증발증착 각도는 그 전조의 정도를 제어한다. KOH 솔루션[PSE-200, Transene Co., 110℃]에 의한 이방성 습식 화학 에칭은 <110> 방향을 따라서 Si를 제거시켰다[측벽들을 따라서 노출된 Si의 모 든 영역들에서 시작함]. {110} 평면들을 따르는 KOH의 에칭율(etching rate)은 {111} 평면들을 따르는 경우보다 수 백배 정도 더 빠르다. 왜냐하면, {110} 평면들이 {111} 평면들보다 더 낮은 밀도의 원자들과 더 높은 밀도의 현수 결합(dangling bond)들을 가지기 때문이다<sup>14</sup>. 그 결과, 이 에칭은 웨이퍼의 표면에 평행한 방향으로 각 트 렌치의 한 측면으로부터 인접 측면으로 완전하게 진행되었고, 그럼으로써 리플 구조[즉, 주기와 크기] 및 경사 진 증발증착에 의해 결정되는 두께들을 가지는 멀티레이어 스택들의 개별적인 리본들을 릴리스한다.  $\mathrm{KI/I_2[aq]}$ 솔루션 [2.67/0.67 wt %]에 의한 Cr/Au의 제거와 볼륨으로 HCl/H₂O₂/H₂O = 1:1:1 및 HF[aq]에 의한 추가적 세척 은 제작(fabrication)을 완성시켰다. 고주파 분해(sonication)는 다른 기판들로의 캐스팅을 위해 리본들을 준비 시키기 위해서 리본들을 솔루션[예컨대, CH<sub>3</sub>OH] 내로 릴리스하였다.