# UK Patent Application (19) GB (11) 2 050 667 A

- (21) Application No 8014283

- (22) Date of filing 30 Apr 1980

- (30) Priority data

- (31) 79/15425

- (32) 3 May 1979

- (33) United Kingdom (GB)

- (43) Application published **7 Jan 1981**

- (51) INT CL<sup>3</sup>

G01R 13/00 G09G 3/30

3/36

- (52) Domestic classification G5C A310 A342 HB G4H 13D 14B SU

- (56) Documents cited None

- (58) Field of search **G5C**

- (71) Applicant

The Secretary of State for

Defence, Whitehall,

London SW1A 2HB

- (72) Inventor

Ian Alexander Shanks

- (74) Agent J. B. Edwards

## (54) Dual Waveform Display

(57) Two waveforms to be simultaneously displayed are sampled, digitized and stored. An electro-optic display, e.g. liquid crystal or electro-luminescent has a first m set and a second n set of matrix electrodes, cartesian or polar. In one form the m electrodes are divided into subsets of odd  $m_{\rm o}$  and even  $m_{\rm e}$  rows X. Coded waveforms  $V_{\rm l}$ , each having a different shape over a period T are applied to subset  $m_{\rm o}$  whilst another e.g. median

voltage is applied to subset  $m_{\rm e}$  followed by the converse. Selected ones of the coded waveforms  $V_{\rm l}$  are generated and applied to the n electrodes Y, the choice being related to successive stored sample values of the two traces and the order of coded waveforms on the m set of electrodes. Traces are therefore displayed at intersections where the same voltage waveform occurs periodically and simultaneously on both electrodes, making the r.m.s. p.d. access the element below the critical level.

The drawings originally filed were informal and the print here reproduced is taken from a later filed formal copy.

GB 2 050 667 A

5

10

15

20

25

30

35

40

45

50

55

60

5

10

# **SPECIFICATION Double Trace Electro Optic Display**

This invention relates to a method and apparatus for displaying two waveforms or traces simultaneously.

Conventionally waveforms are displayed on cathode ray tubes in which a stream of high energy electrons is swept across a phosphor screen where it impinges and causes a visible glow. It is possible to make such tubes very small e.g. down to about 3 cm diameter or diagonal but their power consumption is still high for a truly portable display. Also high voltages e.g. ~1 to 5 kV are required and the accuracy and resolution of the information displayed may be degraded compared to a larger tube.

One type of electro-optic display that has the advantage of low power consumption and low operating voltage is the liquid crystal display device. This typically comprises a thin, e.g. 12  $\mu$ m, layer of liquid crystal material contained between glass plates coated on their inner surfaces with electrodes at least one of which is transparent e.g. Stannic Oxide. These electrodes may be arranged in the form of strips with those on one plate orthogonal to those on the other plate, i.e. a matrix of row and column electrodes, so forming a plurality of intersections. The electrodes may also be arranged to display information in polar co-ordinate form or in any suitable set of curvilinear co-ordinates. By applying selected electric voltages to the electrodes the liquid crystal material at their intersection is caused to change its optical property e.g. to go from light scattering to clear or between transparent and opaque states. Each area of intersection may be termed an element. Thus with the application of suitable 20 voltages at a plurality of intersections, elements can collectively display information, for example a waveform can be displayed. One method of applying the voltages is to use signals which differ from one another by a small phase difference and applying the same phase to a particular row and to particular column electrodes with different phases elsewhere. In this method all intersections in a particular column are 'on' except that one at the particular row and column. This is described in co-

25 pending U.K. Patent Application No. 45,957/75, U.S. Patent No. 4,127,848. (Serial No. 1539737). Another type of electro-optic display that can be addressed in matrix form is the a.c. electroluminescent display in which the application of an alternating voltage across a doped phosphor layer causes light emission.

A problem common to matrix addressing is that the intersections not required to display 30 information must receive voltages suitably different from the intersections required to show information. This problem is eased if the information required to be displayed is in the form of a single valued trace e.g. a square waveform. In this case each row and column electrode can be addressed simultaneously with its appropriate waveform. However for a 127×128 element display this requires at least 128 different waveforms. In the invention described in U.K. Patent Application No. 45,957/75 35 (Serial No. 1339737) a master waveform is divided into 128 waveforms whose minimum phase difference is  $2\pi/128$ . Alternatively a poly frequency (e.g. 128 different frequencies) or poly-pulse width (e.g. 128 pulse widths) may be used.

In U.K. Patent Application No. 30898/78 (Serial No. 2001794) binary or multi-level coded waveforms are used. For a 128×128 display 128 different waveforms are generated and applied 40 simultaneously one to each row electrode and appropriate ones of these 128 waveforms applied simultaneously to the column electrodes. The codes may be for example binary numbers or pseudo random binary sequences of logic ones and zeros. To display two waveform traces simultaneously it is necessary to say use odd columns for one waveform and even columns for the second waveform, thereby reducing display resolution by a factor of two.

The display of two traces simultaneously using conventional multiplexing techniques is not possible for large displays, e.g. a 100×100 matrix, with present materials since the ratio of the R.M.S. voltage at intersections that are ON to the R.M.S. voltage when OFF is too low e.g. about 1.09 for a 100×100 matrix display.

As used herein a matrix display is defined as a display having a set of n electrodes and a set of m50 electrodes forming  $n \times m$  intersections or elements whereby information to be displayed is obtained by altering the optical property of the display at a desired number of intersections, the optical property being achieved by applications of appropriate voltage waveforms to the two sets of electrodes.

As used herein a threshold voltage is that R.M.S. voltage above which a desired observable optical effect occurs, e.g. liquid crystal becomes clear from a scattering state or transparent from an 55 opaque state or vice versa.

According to this invention a method of addressing a matrix display having a set of m and a set of n electrodes forming  $m \times n$  electrode intersections to display two waveform traces comprises the steps of generating a series of coded waveforms V<sub>i</sub> of common fundamental frequency but different shapes, applying the coded waveforms in turn to some of the m set of electrodes whilst the others receive 60 another voltage signal, and simultaneously applying ones of the coded waveforms to one or more of the n set electrodes, so that the two waveform traces are displayed collectively at electrode intersections where the same coded waveform occurs on its two associated m, n electrodes to give a below display threshold R.M.S. voltage and elsewhere a minimum R.M.S. voltage which is above the threshold voltage.

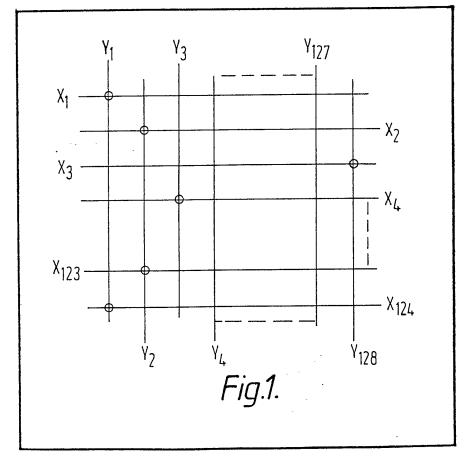

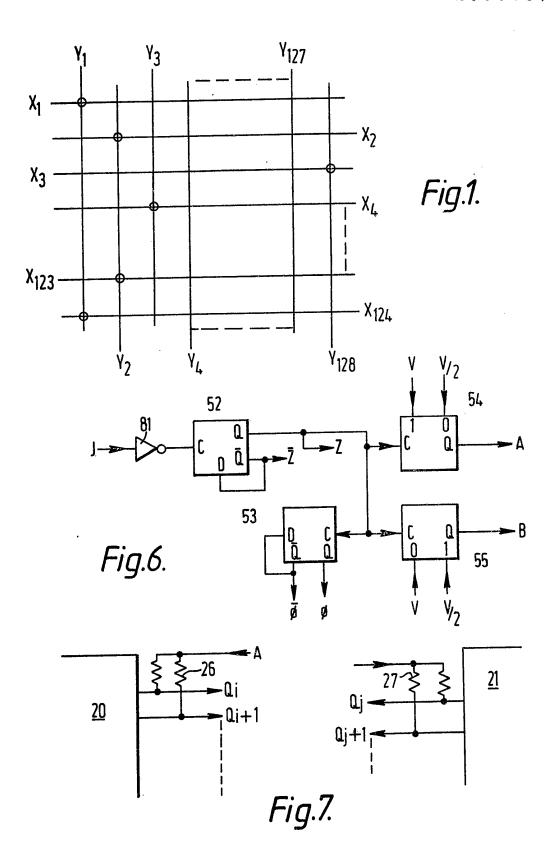

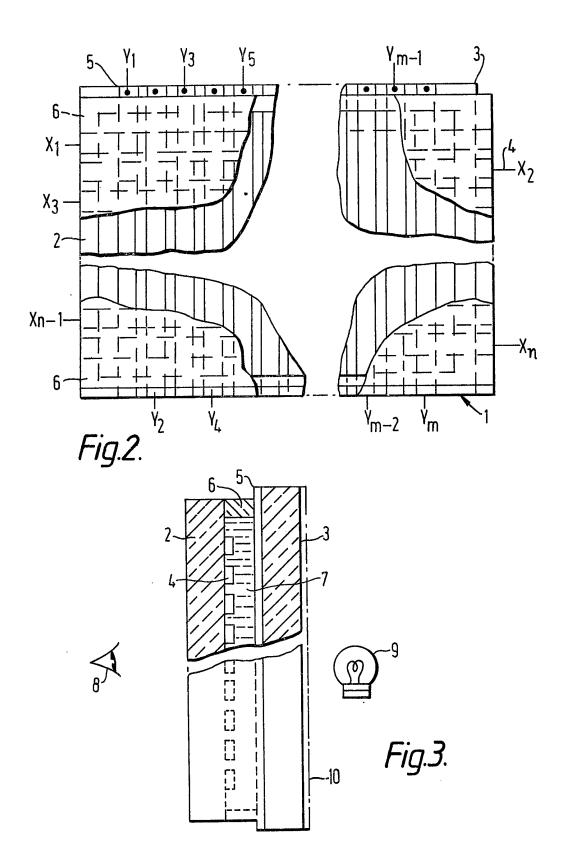

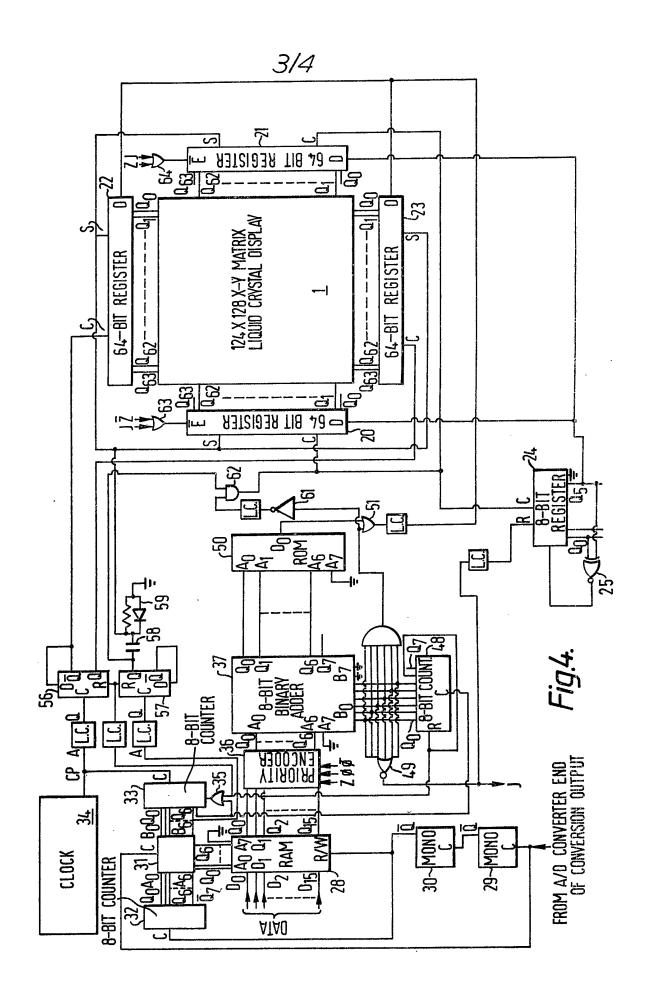

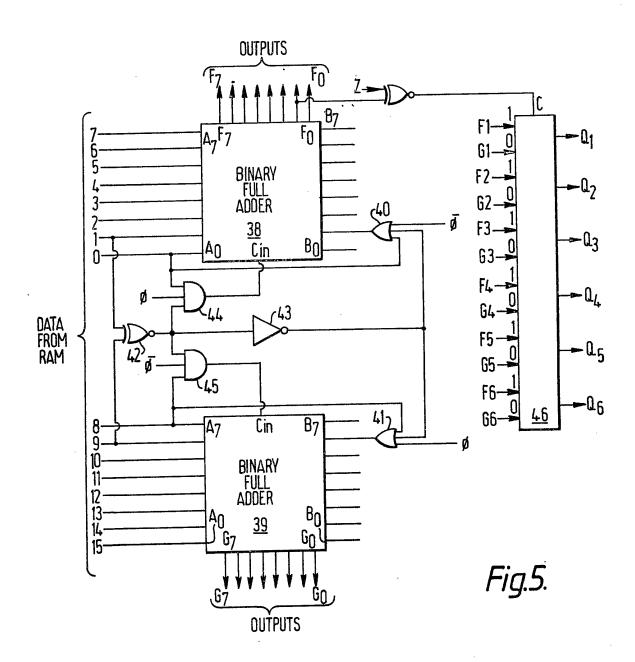

According to this invention apparatus for simultaneously displaying two waveform traces comprises an electro-optic display having a first m set and a second n set of electrodes arranged in a matrix having  $m \times n$  display elements, means for generating a plurality of coded waveforms of different shape over a period T, means for applying a different coded waveform to some of the first set of electrodes whilst another voltage is applied to the remainder of the first set of electrodes so that all 5 electrodes in the first set receive a coded waveform and said another voltage in turn, means for selectively producing ones of the coded waveforms for application to the second set of electrodes simultaneously with voltages applied to the first set of electrodes the choice of such selectively produced coded waveforms being related for each successive n electrode to successive sample values 10 of the two traces and to the order of coded waveforms on the first set of electrodes, the arrangement 10 being such that the two waveform traces appear collectively at intersections where the same waveform occurs periodically and simultaneously on both m, n electrodes to produce a below display threshold voltage level and the voltage at other intersections is above threshold level. The coded waveforms may, for at least a portion of their period, be pseudo random binary 15 sequence waveforms or Walsh functions. The other voltage signal may be a steady, d.c., voltage of half 15 the voltage level of the difference between the logic zero level and the logic one level in the binary coded waveforms V<sub>i</sub>. The m electrodes may be arranged alternately in two sub sets so that V<sub>i</sub> is applied to odd alternate m electrodes whilst V/2 is applied to the remaining even m electrodes, followed by  $V_i$ applied to the even m electrodes and V/2 to the odd m electrodes. 20 The matrix may be in cartesian X, Y format r,  $\theta$  polar co-ordinate format, or other curvilinear form. 20 The means for generating a plurality of waveform may include a programmed memory e.g. a read only memory (ROM), a pseudo-random number generator, such as a shift register with exclusive OR or exclusive NOR feedback, or a binary code generator such as a binary counter whose outputs in the form of logic zeros and ones form different waveforms for each binary number generated; other forms of 2 level coding or multi-level coding are possible. 25 The two waveform traces may be sampled through a low pass filter and may be fed to a charge coupled device (CCD) whose filtered or unfiltered output is fed via sample and hold circuit or directly into an analogue to digital converter (A/D converter). The two traces W<sub>1</sub>, W<sub>2</sub> signals may be read into the CCD (used as an analogue shift register) at a high rate, until the CCD is full, and read out at a slower rate compatible with standard low power low speed A/D converters. This mode of operation of the CCD 30 is known as bandwidth compression. To obtain a Y shift to a displayed waveform  $W_1,W_2$  an offset voltage may be applied to the A/D converter or a Y shift may be obtained by adding or subtracting a digital number to the output of the A/D converter. A Y expansion (or contraction) may be obtained by applying a variable gain amplifier or attenuator before the A/D converter or by altering the full scale reference level of the A/D converter. 35 An X shift or expansion/contraction may be obtained by logic circuits which alter the start or sequence of the read-out of the memory used to define the signals to the second set of electrodes. The waveform traces W<sub>1</sub>, W<sub>2</sub> to be displayed may be e.g. sine waves or other continuous or piecewise continuous functions. Alternatively they may be discontinuous functions as for example 40 when it is required to illustrate signal levels from a plurality of sensors e.g. temperature or strain 40 gauges. Each sensor output may have a specific position along the X axis of a display and the sensor output value along the Y axis. This may be arranged so that when all sensor outputs are at their correct value the display is all along the one horizontal line i.e. the error between desired and measured sensor outputs is displayed. Furthermore different coloured areas of the display may be associated with desired operating ranges so that if an error signal is displayed it will be coloured green if within certain 45 limits, amber between this range and other limits and red if it lies outside both these ranges. The invention will now be described, by way of example only, with reference to the accompanying drawings of which:-Figure 1 is a diagrammatic view of a matrix display; 50 Figure 2 is a view of a liquid crystal display; 50 Figure 3 is a cross-sectioanl view of Figure 3; Figure 4 is a block diagram showing the display and drive voltage circuits for a 124×128 element display; Figure 5 is a circuit diagram of the priority encoder shown in outline in Figure 4; 55 Figure 6 shows timing circuitry for a part of Figure 4; 55 Figure 7 shows how a voltage source is connected to part of Figure 4. As shown in the diagrammatic view Figure 1 a matrix display comprises 124 row and 128 column electrodes arranged as X, Y cartesian co-ordinate having 124x128 display elements formed at the intersections of the electrodes. The circled intersections are in their OFF state and collectively 60 display the two traces required. 60 The traces to be displayed are sampled and each analogue sample converted to a digital value. Thus in each sample time there will be two digital numbers for display on each column of the display. The voltages applied to the electrodes are in the form of pseudo random binary sequence

waveforms having 31 periods of logic "1" and 32 periods of logic "0" each followed by a 64th period 65 having logic "1". These have the property that  $(V_i - V_j)$ =constant (when  $i \neq j$ , and i, j are integers). For the

25

row electrodes 62 different codes V<sub>1</sub>, V<sub>2</sub> ... V<sub>62</sub> are applied one to each odd row X<sub>1</sub>, X<sub>3</sub> ... X<sub>123</sub> respectively for a time period T<sub>1</sub> followed by a d.c. voltage of ½V for the following time period T<sub>2</sub> (equal to T<sub>1</sub>); this is repeated continuously. Meantime, from the right hand end of the matrix, during T<sub>1</sub> the voltage ½V is applied to even row electrodes X<sub>2</sub>, X<sub>4</sub>, X<sub>6</sub>, ... X<sub>124</sub> followed by codes V<sub>1</sub>, V<sub>2</sub>, ... V<sub>62</sub> to row electrode X<sub>2</sub>, X<sub>4</sub>, ... X<sub>124</sub> respectively. Thus each row electrode receives V<sub>1</sub>, ½V, V<sub>1</sub> ... etc. (Where *i*=1, 2 ... 62). The reasons for applying voltages to alternate rows from both sides of the display is to provide more space to connect signals to the finely spaced electrodes and to separate the electronic drivers to the odd and even row electrodes.

For a given intersection to adopt its OFF state identical codes are applied during either  $T_1$  or  $T_2$  to both the associated X, Y electrodes. For example, for  $X_1$ ,  $Y_1$  to be in an OFF state,  $V_1$  is applied to row electrode  $X_1$  and column electrode  $Y_1$  during all periods  $T_1$ . Intersection  $X_{124}$   $Y_1$  is also required to be in an OFF state and therefore code  $V_{62}$  is applied to column  $Y_1$  for the periods  $T_2$ . The column  $Y_1$  thus alternately receives codes  $V_1$  and  $V_{62}$  in periods  $V_1$ ,  $V_2$  and row  $V_{124}$  receives  $V_1$ ,  $V_2$  and row  $V_1$  receives  $V_2$ .

If the binary coded logic levels 0, 1 represent voltage levels 0 and V the R.M.S. value of the electric potential at an OFF intersection say X<sub>1</sub>, Y<sub>1</sub>, is:—

RMS

$$V_{\text{OFF}} = \left(\frac{(\frac{1}{2})^2}{2} + o\right)^{\frac{1}{2}} V = \frac{V}{2\sqrt{2}}$$

The value of V must be such that RMS  $V_{OFF} \leq V_c$  the threshold voltage at which an element turns from OFF to ON.

20 At an ON intersection, say X2, Y1, the voltage is

20

25

30

35

40

5

10

15

RMS

$$V_{ON} = V \left( \frac{(\frac{1}{2})^2}{2} + \frac{1^2}{4} \right)^{\frac{1}{2}} = \frac{V\sqrt{3}}{2\sqrt{2}}$$

The ratio

$$\frac{\text{RMS V}_{\text{oN}}}{\text{RMS V}_{\text{OFF}}} = \sqrt{3} = 1.732$$

and is high enough to be used with known liquid crystal materials.

Similarly at column  $Y_2$  the codes applied are  $V_{62}$  and  $V_1$  in time periods  $T_1$ ,  $T_2$  respectively corresponding to the codes applied to rows  $X_{123}$  and  $X_2$ . This gives a below  $V_c$  voltage at intersections  $X_2Y_2$ , and  $X_{123}Y_2$ .

In column Y<sub>128</sub> only X<sub>3</sub>Y<sub>128</sub> intersection is shown to be displayed. Thus the codes to Y<sub>128</sub> are V<sub>2</sub> and V<sub>x</sub>, where V<sub>x</sub> is also a pseudo random code, e.g. V<sub>x</sub>=V<sub>63</sub>, during time periods T<sub>1</sub>, T<sub>2</sub> respectively whilst the code V<sub>2</sub> is applied to row X<sub>3</sub>. The use of code V<sub>x</sub> allows one or no intersections to be displayed in a given column.

As with codes applied to the rows the codes applied to the columns are from both sides (top and bottom) to the display with alternate columns fed from the top or bottom.

Inherent in the above is the fact that two OFF elements in any one column cannot both lie in an odd row  $X_1, X_3 \ldots$  or both lie on an even row  $X_2, X_4 \ldots$ . The reason for this is that odd rows  $X_1, X_3 \ldots$  receive code  $V_1$  followed by  $\frac{1}{2}V$  and the column code must be  $V_1$  in time period  $V_1$ ; only one code can be applied to a column in T1 representing only one OFF element. The same reasoning applies for even rows  $V_2, V_4 \ldots$  since only one code can be applied to an even column during period  $V_2$ . As a result information on each sample of the two traces to be displayed is examined for a possible conflict i.e. both traces to appear on an odd (or even) row. If there is no conflict, both of the trace samples can be displayed accurately on its appropriate row. However, if there is a conflict then one trace, in each sample time slot, must be given priority to appear at its correct row position. The other trace sample

must be displaced one row up or down. The pseudo random codes have 32 logic zero periods and 31 logic one periods and therefore to provide a net a.c. over 128 such periods an additional logic one period is applied to all row and column electrodes. Each such period should be ~256  $\mu$ sec to give a fundamental frequency for the drive waveforms of  $\gtrsim$ 30 Hz to avoid flicker of the display. The sequence is as shown in Table 1.

#### Table 1

|   |            | Peri             | od T       | Peri             | od T <sub>2</sub> |   |

|---|------------|------------------|------------|------------------|-------------------|---|

|   | Electrodes | 63×256 μsec      | 1×256 μsec | 63×256 µsec      | 1×256 μsec        |   |

|   | Odd rows   | V, '             | V '        | V/2 <sup>'</sup> | V/2               |   |

| 5 | Even rows  | V/2              | V/2        | V,               | V                 | 5 |

| • | Columns    | $V_{\mathbf{k}}$ | V          | V <sub>m</sub>   | V                 |   |

$V_i$ ,  $V_j$ ,  $V_k$ ,  $V_m$  are pseudo random binary codes V and V/2 are d.c. voltage levels with V=logic one.

Pseudo random binary number sequences may be generated as follows. If a 3-bit register with

10 exclusive NOR feedback from its first and third outputs (i.e. its first and third stage outputs are

connected to an exclusive NOR gate whose output is fed back into the shift register) then the stages of

the register will show the following states as it is clocked from a starting point of content 000.

10

|    |             | Table 2 | 2     |       |    |

|----|-------------|---------|-------|-------|----|

|    | Clock Pulse |         |       |       |    |

| 15 | Number      | Bit 1   | Bit 2 | Bit 3 | 15 |

|    | 0           | 0       | 0     | 0     |    |

|    | 1           | 1       | 0     | 0     |    |

|    | 2           | 0       | 1     | 0     |    |

|    | 3           | 1       | 0     | 1     |    |

| 20 | 4           | 1       | 1     | 0     | 20 |

|    | 5           | 0       | 1     | 1     |    |

|    | 6           | 0       | 0     | 1     |    |

|    | (7)         | 0       | 0     | 0     |    |

The binary number constituted by bits 1 to 3 jumps randomly within its possible range until on clock

25 pulse 7 the sequence starts to repeat. The bit 1 output consists of a pseudo random sequence of "1" and "0" states until it starts to repeat itself on clock pulse 7. This is also referred to as an M-sequence (M for maximum) by mathematicians. If bit 3 is connected into a further 4-bit shift register which is clocked synchronously with the first register then 7 outputs in all are obtained. These give the following binary waveforms:

25

| Table 3                            |                                           |                                         |                                                                                                                                                         |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                           | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------|-------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register Output Clock Pulse Number |                                           |                                         |                                                                                                                                                         |                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Number                             | 0                                         | 1                                       | 2                                                                                                                                                       | 3                                                                                                                                                                                                                                                           | 4                                                                                                                                                                                                                                                                                                                                                                                                        | 5                                                                                                                                                                                                                                                                                                                                                                                                                            | 6                                                                                                                                                                                                         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1                                  | 0                                         | 1                                       | 0                                                                                                                                                       | 1                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2                                  | 0                                         | 0                                       | 1                                                                                                                                                       | 0                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3                                  | 0                                         | 0                                       | 0                                                                                                                                                       | 1                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4                                  | 1                                         | 0                                       | 0                                                                                                                                                       | 0                                                                                                                                                                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5                                  | 1                                         | 1                                       | 0                                                                                                                                                       | 0                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6                                  | 0                                         | 1                                       | 1                                                                                                                                                       | 0                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | . 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7                                  | 0                                         | 0                                       | 1                                                                                                                                                       | 1                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                                                                                                                                                                                                                                                                                                                                                                            | 0                                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |