# (19) 대한민국특허청(KR) (12) 특허공보(B1)

(51) Int. CI.6(45) 공고일자1997년04월04일H04Q 1/00(11) 공고번호특1997-0004859(24) 등록일자1997년04월04일

(21) 출원번호 특1994-0011547 (65) 공개번호 특1995-0035476 (22) 출원일자 1994년05월26일 (43) 공개일자 1995년12월30일

(73) 특허권자 대우통신주식회사 박성규

인천광역시 서구 가좌동 531-1

(72) 발명자 오종환

서울특별시 동대문구 용두 1동 51-2 3/3

(74) 대리인 장성구, 김원준

# 심사관 : 정종일 (책자공보 제4929호)

# (54) 전전자 교환기의 하이웨이 레이트 변환장치

# 요약

내용 없음.

#### 대표도

#### 도1

## 명세서

[발명의 명칭]

전전자 교환기의 하이웨이 레이트 변환장치

[도면의 간단한 설명]

제1도는 하이웨이 레이트 변환장치의 연결구성도.

제2도는 본 발명의 전체구성도.

제3도는 루프백 조정부의 내부 구성도.

\* 도면의 주요 부분에 대한 부호의 설명

11,12 : 어드레스 발생부 13 : 데이타 전송 조정부

14 : 읽기/쓰기(R/W) 어드레스 조정부 15,24 : 데이타 송신부

16 : 역다중화기 17,23 : PCM 데이타 메모리부

18 : 데이타 수신 및 선택부 19 : 루프백 조정부 20 : 비트 동기 조정부 21 : 데이타 수신부

22 : 다중화기

[발명의 상세한 설명]

본 발명은 전전자 교환기의 공간 분할 스위치 장치와 중계선 정합 장치 사이에 설치되는 하이웨이 레이트 변환장치에 관한 것이다.

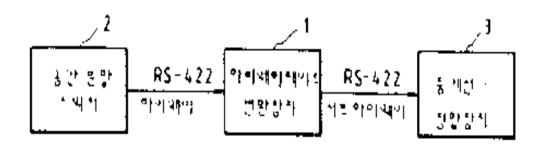

하이웨이 레이트 변환장치의 일반적인 동작을 제1도를 참조하여 살펴보면, 제1도는 하이웨이 레이트 변환 장치의 주변장치와의 일반적인 접속 구성도로서, 도면에서 1은 하이웨이 레이트 변환장치, 2는 공간 분할 스위치, 3은 중계선 정합장치를 각각 나타낸다.

하이웨이 레이트 변환장치(1)는 공간분할 스위치(2)로부터 하이웨이를 통하여 병렬 8비트 및 8.192Mbps의 전송속도로 입력되는 PCM 데이타를 직렬로 변환하여 2.048Mbps의 전송속도로 바꾸어 32개의 서브하이웨이로 내보내 주거나 그 반대의 기능을 수행한다.

그리고, 하이웨이 레이트 변환장치(1)와 공간 분할 스위치와의 이격에 따른 타임 딜레이 보상기능이 있다.

그런데 종래의 하이웨이 레이트 변환장치는, 공간 분할 스위치와의 PCM 데이타 전송은 한 프레임내 1024 채널에 PCM 데이타를 한번만 전송할 수 있도록 되어 있었고, PCM 데이타 전송로 시험기능이 존재하지 않 았다. 따라서, 종래의 하이웨이 레이트변환장치는 여분의 전송채널이 남아도 효율적으로 사용할 수 없었고 PCM 데이타 전송로 시험기능이 없이 PCM 데이타 전송로 기능 고장시 문제가 발생되었다.

이와 같은 종래 기술의 문제점을 해결하기 위하여 안출된 본 발명은, 전전자 교환기의 공간 분할 스위치와 하이웨이 레이트 변환장치 사이의 8.192Mbps 전송속도를 갖는 하이웨이 정합에 있어서, PCM 데이타 전송을 종래보다 더욱 신뢰성 있게 전송할 수 있고 PCM 데이타 전송로의 정상동작 여부도 파악할 수 있는하이웨이 레이트 변환장치를 제공하는데 그 목적이 있다.

상기 목적을 달성하기 위하여 본 발명은, 종래의 하이웨이 레이트 변환장치에 있어서, 한 프레임내에 동일한 데이타를 여러번 보낼 수 있도록 어드레스 발생부로 스트랩(Strap) 조정신호를 제공하는 데이타 전송 조정부와, 역다중화기로부터 전송로 시험장치로부터의 시험데이타를 루프백(Loop-Back)시켜 다중화기로 제공하되, 외부의 제어신호에 따라 루프백되는 신호를 상기 데이타 수신부로부터의 소정 채널신호로 대치하는 기능을 포함하는 루프백 조정부를 더 구비하도록 하였다.

이하, 첨부된 제2도 이하의 도면을 참조하여 본 발명의 일실시예를 상세히 설명한다.

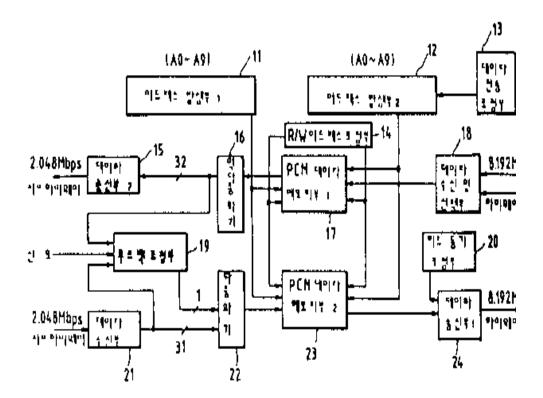

제2도는 본 발명에 따른 하이웨이 레이트 변환장치의 구성도로서, 도면에서 11과 12는 어드레스 발생부, 13은 데이타 전송 조정부, 14는 읽기/쓰기(R/W) 어드레스 조정부, 15와 24는 데이타 송신부, 16은 역다중화기, 17과 23은 PCM 데이타 메모리부, 18은 데이타 수신 및 선택부, 19는 루프백 조정부, 20은 비트 동기 조정부, 21은 데이타 수신부, 22는 다중화기를 각각 나타낸다.

도면에 도시한 바와 같이, 본 발명에 따른 하이웨이 레이트 변환장치는, 공간분할 스위치 측으로부터의 데이타(8.192Mbps)를 수신하여 유효한 데이타만 선택하여 출력하는 데이타 수신 및 선택부(18)와, 상기 데이타 수신 및 선택부(18)에서 수신한 데이타를 저장하는 PCM 데이타 메모리부 1(17)와, 상기 PCM 데이 타 메모리부 1(17)로부터 저장되었던 데이타를 제공받아 역다중화하여 출력하는 역다중화기(16)와. 상기 역다중화기(16)에서 출력되는 역다중화된 신호를 중계선 정합장치 측의 하이웨이)2.048Mbps)로 출력하는 데이타 송신부 2(15)와, 중계선 정합장치 측의 하이웨이(2.048Mbps)로부터 입력되는 데이타를 수신하여 출력하는 데이타 수신부(21)와, 상기 데이타 수신부(21)로부터 제공받는 데이타를 다중화하여 출력하는 다중화기(22)와, 상기 다중화기(22)에서 다중화되어 출력되는 데이타를 저장하는 PCM 데이타 메모리부 2(23)와, 상기 PCM 데이타 메모리부 2(23)에 저장되었던 데이타를 제공받아 공간분할 스위치측의 하이웨 이(8.192Mbps)로 출력하는 데이타 송신부 1(24)와, 상기 데이타 송신부 1(24)로 비트동기 조정신호를 제 공하는 비트동기 조정부(20)와, 상기 PCM 데이타 메모리부 1(17)로는 역다중화기(16)로 제공될 데이타에 대한 쓰기 어드레스를 제공하고 상기 PCM 데이타 메모리부 2(23)로는 다중화기(22)의 출력 데이타에 대한 읽기 어드레스를 제공하는 어드레스 발생부 1(11)와, 상기 PCM 데이타 메모리부 1(17)로는 데이타 수신 및 선택부(18)로부터 입력되는 데이타에 대한 읽기 어드레스를 제공하고 상기 PCM 데이타 메모리부 2(2 3)로는 데이타 송신부 1(24)로 출력될 데이타에 대한 쓰기 어드레스를 제공하는 어드레스 발생부 2(12)와, 한 프레임내에 동일한 데이타를 여러번 보낼 수 있도록 상기 어드레스 발생부 2(12)로 스트랩 조정신호를 제공하는 데이타 전송 조정부(13)와, 상기 역다중화기(16)로부터 전송로 시험장치로부터의 시 험데이타를 루프백시켜 상기 다중화기(22)로 제공하되, 외부의 제어신호에 따라 루프백되는 신호를 상기 데이타 수신부(21)로부터의 소정 채널신호로 대치하는 기능을 포함하는 루프백 조정부(19)를 구비한다.

종래의 하이웨이 레이트 변환장치에서도 동일하게 적용되었던 구성요소들의 상세한 동작설명은 위의 기능 설명으로 갈음하기로 하고, 이하에서는 본 발명에 따라 새로이 부가된 구성요소의 구성 및 세부적인 동작 에 대하여 살펴보기로 한다.

하나의 하이웨이 레이트 변환장치는 한 프레임내에 1024채널의 PCM 데이타를 전송할 수 있다.

그러나 한 프레임내에 수용되는 1024채널이 모두 사용되지 않고 일부만 사용되는 경우가 발생되는데, 이러한 경우 전송되는 PCM 데이타의 신뢰성과 효율성을 높이기 위해 PCM 데이타 조정부(13)에서 스트랩으로 조정하여 한 프레임내에 동일 데이타를 여러번 보낼 수 있게 하고 수신되는 PCM 데이타중 유효한 PCM 데이타만 수신하는 기능을 수행하도록 하였다.

예를들면, 상기 어드레스 발생부 2(12)에서 발생되는, 공간분할 스위치와 PCM 데이타를 송신하기 위해 사용되는 어드레스중 상위 3비트를 스트랩해서 결합하여 어드레스 상위 3비트 값을 임의로 조정하면 한 프레임내에 동일한 데이타를 8회까지 전송할 수 있게 된다.

어드레스 최상위 비트가 항상 '0'이 되도록 하면 한 프레임내에 0-511번까지의 동일데이타를 2회 전송 가능하고 어드레스 상위 2비트를 '0'이 되게 하면 한 프레임내에 0-255번지까지의 동일 데이타를 4회 전송 가능하고 상위 어드레스 3비트를 '0'이 되게 하면 한 프레임내에 0-127번지까지의 동일 데이타를 8회 전송 가능하다.

위와 같이 어드레스중 상위 3비트를 임의로 조정하면 공간분할 스위치로부터 하이웨이 레이트 변환장치로 입력되는 PCM 데이타중 유효한 데이타만 공간분할 스위치로부터 PCM 데이타와 같이 하이웨이 변환장치로 들어오는 밸리드(Valid) 비트의 제어를 받아 PCM 데이타 메모리부 1에 저장한다.

또한, 본 발명은 PCM 데이타 전송로 시험을 위해 전송측정장치로부터 오는 데이타를 전송측정장치로 루프백시켜 주는 기능을 가지는데, 이의 기능수행은 루프백 조정부(19)에서 수행한다.

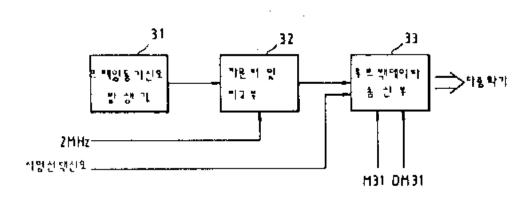

제3도는 상기 루프백 조정부(19)의 내부구성도로서, 도면에서 31은 프레임 동기신호 발생기, 32는 카운터 및 비교부, 33은 루프백 데이타 송신부를 각각 나타낸다.

도면에 도시한 바와 같이 루프백 조정부(19)는, 프레임 동기신호를 발생시키는 프레임 동기신호 발생기(31)와, 외부에서 제공되는 클럭(2MHz)을 이용하여 상기 프레임 동기신호 발생기(31)의 출력신호를 계수하다가 기설정해 놓은 값과 동일한지를 비교하여 그 결과를 루프백 명령신호로서 출력하는 카운터 및 비교부(32)와 상기 카운터 및 비교부(32)의 출력을 입력받고 외부로부터의 시험선택신호를 입력받아 역다중화기(16)를 통해 전송측정장치로부터 수신한 PCM 데이타를 상기 다중화기(22)를 통해 루프백시키는 루프백 데이타 송신부(33)를 구비한다.

시험선택신호가 논리적으로 하이(High)가 되면 루프백 데이타 송신부(33)에서는 항상 데이타 수신부(21)로부터 입력되는 32번째 서브하이웨이의 PCM 데이타(M31)가 출력되고, 시험선택 신호가 논리적으로 로우가 되면, 27번째 채널에서만 상기 역다중화기(16)로부터 출력되는 32번째 서브하이웨어의 PCM 데이타의 27번째 데이타로 대체되어서 출력되는 전송로 점검을 위한 루프백 기능이 수행되는 것이다.

따라서, 상기와 같이 구성되어 동작하는 본 발명은, 전전자 교환기에 있어서, 하이웨이 레이트 변환장치에서 공간분할 스위치와의 PCM 데이타 전송시 통화로를 효율적으로 사용할 수 있는 효과가 있다.

# (57) 청구의 범위

#### 청구항 1

공간분할 스위치 측으로부터의 데이타(8.192Mbps)를 수신하여 유효한 데이타만을 선택하여 출력하는 데이 타 수신 및 선택부(18)와, 상기 데이타 수신 및 선택부(18)에서 수신한 데이타를 저장하는 제1PCM 데이타 메모리부 1(17)와, 상기 제1 PCM 데이타 메모리부 1(17)로부터 저장되었던 데이타를 제공받아 역다중화하 여 출력하는 역다중화기(16)와, 상기 역다중화기(16)에서 출력되는 역다중화된 신호를 중계선 정합장치 측의 하이웨이(2.048Mbps)로 출력하는 제2데이타 송신부(15)와, 중계선 정합장치 측의 하이웨이 (2.048Mbps)로부터 입력되는 데이타를 수신하여 출력하는 데이타 수신부(21)와, 상기 데이타 수신부(21) 로부터 제공받는 데이타를 다중화하여 출력하는 다중화기(22)와, 상기 다중화기(22)에서 다중화되어 출력 되는 데이타를 저장하는 제2PCM 데이타 메모리부(23)와, 상기 제2PCM 데이타 메모리부(23)에 저장되었던 데이타를 제공받아 공간분할 스위치측의 하이웨이(8.192Mbps)로 출력하는 제1데이타 송신부(24)와, 상기 제1데이타 송신부(24)로 비트동기 조정신호를 제공하는 비트동기 조정부(20)와, 상기 제1PCM 데이타 메모 리부(17)로는 역다중화기(16)로 제공될 데이타에 대한 쓰기 어드레스를 제공하고 상기 제2PCM 데이타 메 모리부(23)로는 다중화기(22)의 출력 데이타에 대한 읽기 어드레스를 제공하는 제1어드레스 발생부(11)와 상기 제1PCM 데이타 메모리부(17)로는 데이타 수신 및 선택부(18)로부터 입력되는 데이타에 대한 읽기 어 드레스를 제공하고 상기 제2 PCM 데이타 메모리부(23)로는 제1데이타 송신부(24)로 출력될 데이타에 대한 쓰기 어드레스를 제공하는 제2어드레스 발생부(12)를 구비하는 하이웨이 레이트 변환장치에 있어서, 한 프레임내에 동일한 데이타를 여러번 보낼 수 있도록 상기 제2어드레스 발생부(12)로 스트랩 조정신호를 제공하는 데이타 전송 조정부(13)와; 상기 역다중화기(16)로부터 전송로 시험장치로부터의 시험데이타를 루프백시켜 상기 다중화기(22)로 제공하되, 외부의 제어신호에 따라 루프백되는 신호를 상기 데이타 수신 부(21)로부터의 소정 채널신호로 대치하는 기능을 포함하는 루프백 조정부(19)를 더 구비하도록 한 것을 특징으로 하는 전전자 교환기의 하이웨이 레이트 변환장치.

#### 청구항 2

제1항에 있어서, 상기 루프백 조정부(19)는 프레임 동기신호를 발생시키는 프레임 동기신호 발생기(31)와; 외부에서 제공되는 클럭(2MHz)을 이용하여 상기 프레임 동기신호 발생기(31)의 출력신호를 계수하다가 기설정해 놓은 값과 동일한지를 비교하여 그 결과를 루프백 명령신호로서 출력하는 카운터 및 비교부(32)와; 상기 카운터 및 비교부(32)의 출력을 입력받고 외부로부터의 시험선택신호를 입력받아 상 기 역다중화기(16)를 통한 전송측정장치로부터의 PCM 데이타를 다중화기(22)를 통해 루프백시키는 루프백 데이타 송신부(33)를 구비하는 것을 특징으로 하는 전전자 교환기의 하이웨이 레이트 변환장치.

#### 청구항 3

제2항에 있어서, 상기 루프백 데이타 송신부(33)는 시험선택신호가 논리적으로 하이가 되면 항상 데이타수신부(21)로부터 입력되는 32번째 서브하이웨이의 PCM 데이타가 출력되고, 시험선택신호가 논리적으로로우가 되면, 27번째 채널에서만 상기 역다중화기(16)로부터 출력되는 32번째 서브하이웨이의 PCM 데이타의 27번째 데이타로 대체되어서 출력되도록 구성하는 것을 특징으로 하는 전전자 교환기의 하이웨이 레이트 변환장치.

## 도면

## 도면1

# 도면2

# 도면3