# (19) 国家知识产权局

# (12) 发明专利申请

(10) 申请公布号 CN 115268154 A (43) 申请公布日 2022.11.01

(21) 申请号 202110474950.8

(22) 申请日 2021.04.29

(71) 申请人 北京京东方显示技术有限公司 地址 100176 北京市大兴区经济技术开发 区经海一路118号

申请人 京东方科技集团股份有限公司

(72) 发明人 赵重阳 缪应蒙 薄灵丹 曲莹莹 陈东川 刘建涛

(74) 专利代理机构 北京同达信恒知识产权代理 有限公司 11291

专利代理师 王迪

(51) Int.CI.

*G02F* 1/1362 (2006.01) *G02F* 1/1368 (2006.01)

权利要求书1页 说明书7页 附图2页

## (54) 发明名称

一种阵列基板及显示面板

#### (57) 摘要

本发明涉及显示技术领域,公开了一种阵列基板及显示面板,该阵列基板包括:基板以及设于基板上的扫描线、扫描信号线、数据线对、薄膜晶体管、像素电极,基板具有显示区,显示区包括阵列分布的子像素区;两条相邻的扫描线构成一个扫描线组,扫描信号线沿列方向延伸,一条扫描信号线仅与一个扫描线组中的两个扫描线电性连接;每个数据线对包括两条数据线,子像素列与数据线对一一对应设置,数据线对中的两条数据线沿列方向在对应的子像素区内穿过;沿行方向,每相邻的两个子像素区之间设置有遮光条。该阵列基板中,数据线在对应的子像素区中穿行,行方向上的子像素区之间设置遮光条进行遮光,有效增大了子像素区的光效区,提高光透过率。

1.一种阵列基板,其特征在于,包括:

基板,所述基板具有显示区,显示区包括阵列分布的多个子像素区;

扫描线,设置于所述基板上,且所述扫描线位于相邻的两行所述子像素区之间并沿行方向延伸,两条相邻的所述扫描线构成一个扫描线组,且任意两个所述扫描线组中,其中一个扫描线组中的扫描线与另一个扫描线组中的扫描线彼此互不相同;

扫描信号线,所述扫描信号线沿列方向延伸,所述扫描信号线位于相邻的两个子像素区列之间,且一条所述扫描信号线仅与一个所述扫描线组中的两条扫描线电性连接;

数据线对,设置于所述基板上,每个所述数据线对包括两条间隔且并行设置的数据线, 所述数据线沿列方向延伸,所述子像素列与所述数据线对一一对应设置,在相互对应的子 像素列与数据线对中,所述数据线对中的两条数据线沿列方向在对应的子像素区内穿过;

薄膜晶体管,所述薄膜晶体管与所述扫描线电性连接且与所述数据线电性连接;

像素电极,所述像素电极位于所述子像素区内且与所述薄膜晶体管电性连接,所述像 素电极在所述衬底基板上正投影与对应的两条所述数据线在所述衬底上的正投影交叠设 置:

沿行方向,每相邻的两个子像素区之间设置有遮光条。

- 2.根据权利要求1所述的阵列基板,其特征在于,所述数据线与所述像素电极之间设置 有有机绝缘层以隔绝。

- 3.根据权利要求2所述的阵列基板,其特征在于,还包括与所述像素电极对应的公共电极、以及与所述公共电极电连接的公共电极线。

- 4.根据权利要求3所述的阵列基板,其特征在于,所述公共电极位于所述数据线背离所述基板的一侧,且所述像素电极位于所述公共电极背离所述数据线的一侧;所述有机绝缘层位于所述数据线与所述公共电极之间;所述公共电极与所述像素电极之间设置有钝化层以隔绝。

- 5.根据权利要求3所述的阵列基板,其特征在于,所述遮光条为金属遮光条,且所述金属遮光条与所述公共电极线电性连接。

- 6.根据权利要求5所述的阵列基板,其特征在于,所述遮光条与所述扫描线同层制备。

- 7.根据权利要求1所述的阵列基板,其特征在于,所述薄膜晶体管包括依次层叠设置的栅极、栅绝缘层、有源层、绝缘层和与所述有源层电性连接的源、漏电极:

其中,所述栅极与所述扫描线同层制备;所述源、漏电极与所述数据线同层设置。

- 8.根据权利要求3所述的阵列基板,其特征在于,所述扫描信号线中,部分扫描信号线与所述扫描线无电性连接,且所述部分扫描信号线与所述公共电极线电性连接。

- 9.根据权利要求1所述的阵列基板,其特征在于,所述扫描信号线与所述数据线同层制备。

- 10.根据权利要求1所述的阵列基板,其特征在于,所述像素电极包括多个间隔设置且依次连接的电极条。

- 11.根据权利要求1-10任一项所述的阵列基板,其特征在于,还包括沿所述行方向设置并与扫描线对应以用于遮光的遮光层。

- 12.一种显示面板,其特征在于,包括如权利要求1-11任一项所述的阵列基板。

# 一种阵列基板及显示面板

#### 技术领域

[0001] 本发明涉及显示技术领域,特别涉及一种阵列基板及显示面板。

## 背景技术

[0002] 随着显示技术的不断发展,LCD显示已经占据了显示行业的主导地位,而采用ADS (高级超维场转换技术)结构的产品具有宽视角、响应速度块和对比度高等优点成为了主流的显示模式;对于目前的全面屏产品负载大于常规产品,尤其是要达到超高分辨率级别,如8K级别,12K级别,产品的驱动将面临困难,就需要采用2G2D (2个Gate走线同时驱动、2个Data走线同时驱动)的像素架构来进行像素的驱动了,不过对于超高分辨率的产品,由于分辨率高,像素尺寸小,本身透过率较低,如果做成全面屏产品,像素中需要增加与数据线平行的Gate信号线给Gate走线传输信号,透过率下降会更加明显,因此,如何提声高分辨率的全面屏产品的光透过率是目前亟需解决的问题。

# 发明内容

[0003] 本发明公开了一种阵列基板及显示面板,该阵列基板中,数据线对中的数据线在对应的子像素区中穿行,行方向上的子像素区之间设置遮光条进行遮光,有效增大了子像素区的光效区,提高光透过率。

[0004] 为达到上述目的,本发明提供以下技术方案:

[0005] 一种阵列基板,包括:

[0006] 基板,所述基板具有显示区,显示区包括阵列分布的多个子像素区;

[0007] 扫描线,设置于所述基板上,且所述扫描线位于两行所述子像素区之间并沿行方向延伸,两条相邻的所述扫描线构成一个扫描线组,且任意两个所述扫描线组中,其中一个扫描线组中的扫描线与另一个扫描线组中的扫描线彼此互不相同;

[0008] 扫描信号线,所述扫描信号线沿列方向延伸,所述扫描信号线位于相邻的两个子像素区列之间,且一条所述扫描信号线仅与一个所述扫描线组中的两条扫描线电性连接;

[0009] 数据线对,设置于所述基板上,每个所述数据线对包括两条间隔且并行设置的数据线,所述数据线沿列方向延伸,所述子像素列与所述数据线对一一对应设置,在相互对应的子像素列与数据线对中,所述数据线对中的两条数据线沿列方向在对应的子像素区内穿过;

[0010] 薄膜晶体管,所述薄膜晶体管与所述扫描线电性连接且与所述数据线电性连接;

[0011] 像素电极,所述像素电极位于所述子像素区内且与所述薄膜晶体管电性连接,所述像素电极在所述衬底基板上正投影与对应的两条所述数据线在所述衬底上的正投影交 叠设置:

[0012] 沿行方向,每相邻的两个子像素区之间设置有遮光条。

[0013] 上述阵列基板中,在基板上包括显示区,在显示区的周侧设置有布线区,显示区内 具有阵列分布的多个子像素区,多个子像素区行列分布,在基板上有相互垂直的行方向和 列方向:其中,扫描线设置在基板上,并且扫描线沿着行方向延伸,多个扫描线沿着列方向 依次间隔排列分布,且扫描线位于相邻的两行子像素区之间,其中,每两条相邻的扫描线构 成一个扫描线组,每个扫描线组中的两个扫描线与其它扫描线组中的扫描线均不相同:基 板上还设置有扫描信号线,多条扫描信号线沿列方向延伸,扫描信号线可以设置在两个相 邻的两个子像素区列之间,并且,一条扫描信号线仅对应一个扫描线组中的两条扫描线,并 与对应的两个扫描线电性连接,具体地,扫描线信号线可以均匀分布在基板上,每个扫描信 号线与相对应的两个扫描线电性连接,用于给扫描信号线提供电信号,即在扫描线进行扫 描时,可以同时给两个扫描线提供电信号,同时驱动两个扫描线,且扫描信号线沿列方向延 伸,可以将扫描线的驱动电路在基板中沿列方向上的一边引入,进而减小基板的其它三边 的边框宽度;在基板上设置多个数据线对,每个数据线对包括两条间隔设置的数据线,数据 线沿着列方向延伸设置,并且沿着行方向排列分布,数据线对与子像素区列一一对应设置, 在相互对应的数据线对和子像素区列中,数据对中的两条数据线沿着列方向在对应的子像 素区内穿过,在显示区内的数据线可以划分为两部分,沿着列方向,一部分与子像素区相 对,另一部分与两个相邻的子像素区之间的间隔相对,其中,每条数据线中与子像素区对应 的部位与子像素区交叠;其中,在子像素区内设置有像素电极,像素电极与数据线对中的两 个数据线也交叠设置,在子像素区内,除了数据线遮挡的区域,其它区域都是光效区,并且, 沿着行方向排列的子像素区中,每相邻的两个子像素区之间设置有遮光条,遮光条用于遮 盖两个行方向上的两个相邻子像素之间的间隔,避免漏光,并且避免混色;其中,相比于现 有技术,数据线对中的两个数据线设置在子像素区的两侧,也就是在行方向上相邻的两个 子像素区之间的间隔内设置有两个数据线,这两个数据线之间为避免短路风险,需要间隔 一定的距离,则会增大两个子像素区之间的间隔距离,增大了沿着列方向布置的遮光区的 宽度,这些遮光区都没有光效,挤占了子像素区的光效区,使子像素区的光效区缩减,而本 实施例中,数据线在子像素内穿行,遮光条沿着列方向延伸设置在相邻的子像素区之间,在 列方向上,遮光条可以避免子像素区之间的混色,并且遮光条的沿着行方向上的宽度可以 缩减,极大的减小了行方向两个子像素区之间的遮光宽度,可以有效增大子像素区的光效 区,提高光透过率,上述阵列基板中的子像素区的透光率较现有技术中像素结构可以有较 大提升,上述阵列基板应用于高分辨率的全面屏产品中,可以有效解决高分辨率的全面屏 产品的光透过率低的问题,提升高分辨率的全面屏产品的光透过率。

[0014] 因此,上述阵列基板中,数据线对中的数据线在对应的子像素区中穿行,行方向上的子像素区之间设置遮光条进行遮光,有效增大了子像素区的光效区,提高光透过率。

[0015] 可选地,所述数据线与所述像素电极之间设置有有机绝缘层以隔绝。

[0016] 可选地,所述阵列基板还包括与所述像素电极对应的公共电极、以及与所述公共电极电连接的公共电极线。

[0017] 可选地,所述公共电极位于所述数据线背离所述基板的一侧,且所述像素电极位于所述公共电极背离所述数据线的一侧;所述有机绝缘层位于所述数据线与所述公共电极之间;所述公共电极与所述像素电极之间设置有钝化层以隔绝。

[0018] 可选地,所述遮光条为金属遮光条,且所述金属遮光条与所述公共电极线电性连接。

[0019] 可选地,所述遮光条与所述扫描线同层制备。

[0020] 可选地,所述薄膜晶体管包括依次层叠设置的栅极、栅绝缘层、有源层、绝缘层和与所述有源层电性连接的源、漏电极:

[0021] 其中,所述栅极与所述扫描线同层制备;所述源、漏电极与所述数据线同层设置。

[0022] 可选地,所述扫描信号线中,部分扫描信号线与所述扫描线无电性连接,且所述部分扫描信号线与所述公共电极线电性连接。

[0023] 可选地,所述扫描信号线与所述数据线同层制备。

[0024] 可选地,所述像素电极包括多个间隔设置且依次连接的电极条。

[0025] 可选地,所述阵列基板还包括沿所述行方向设置并与扫描线对应以用于遮光的遮光层。

[0026] 本发明还提供了一种显示面板,包括如上述技术方案提供的任意一种阵列基板。

# 附图说明

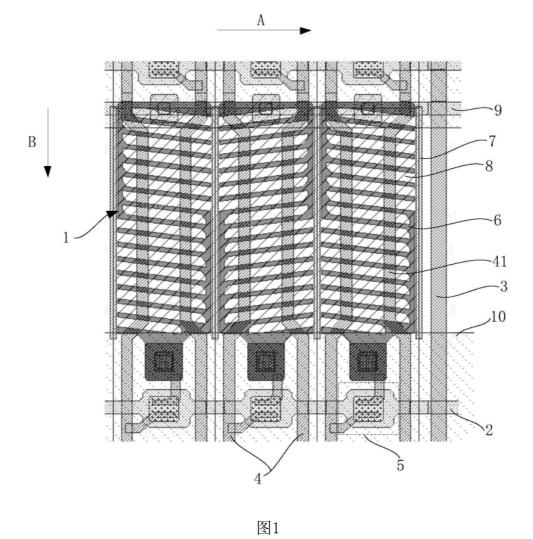

[0027] 图1为本发明实施例提供的一种阵列基板的局部结构示意图:

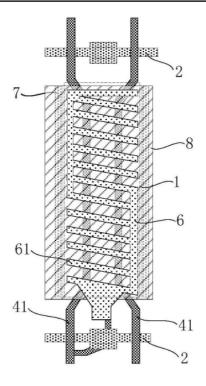

[0028] 图2为本发明实施例提供的一种阵列基板中的子像素的结构示意图:

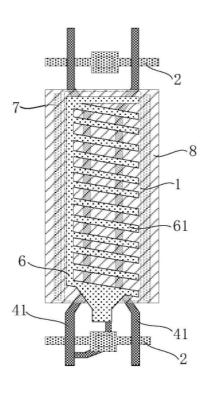

[0029] 图3为本发明实施例提供的一种阵列基板中的子像素的结构示意图;

[0030] 图标:1-子像素区;2-扫描线;3-扫描信号线;4-数据线对;5-薄膜晶体管;6-像素电极;7-遮光条;8-公共电极;9-公共电极线;10-遮光层;41-数据线;61-电极条。

## 具体实施方式

[0031] 下面将结合本发明实施例中的附图,对本发明实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

如图1和图2所示,其中,图1中,以下行方向如图1中A方向所示,列方向如图1中B方 [0032] 向所示。本发明实施例提供了一种阵列基板,包括:基板,基板具有显示区,显示区包括阵列 分布的多个子像素区1:扫描线2,设置于基板上,扫描线2位于两行子像素区之间并沿行方 向延伸,两条相邻的扫描线构成一个扫描线组,且任意两个扫描线组中,其中一个扫描线组 中的扫描线与另一个扫描线组中的扫描线彼此互不相同,也就是,多个扫描线划分为多个 扫描线组,每个扫描线组中的两个扫描线是相邻的,并且两个相邻的扫描线组中的扫描线 没有共用的扫描线,两个扫描线组中的扫描线是彼此不同的扫描线;扫描信号线3,扫描信 号线3沿列方向延伸,扫描信号线3位于相邻的两个子像素区列之间,且一条扫描信号线3仅 与一个扫描线组中的两条扫描线2电性连接;数据线对4,设置于基板上,每个数据线对4包 括两条间隔且并行设置数据线41,数据线41沿列方向延伸,子像素列与数据线对一一对应 设置,在相互对应的子像素列与数据线对中,数据线对中的两条数据线41沿列方向在对应 的子像素区1内穿过;薄膜晶体管5,薄膜晶体管5与扫描线2电性连接且与数据线4电性连 接;像素电极6,像素电极6位于子像素区1内且与薄膜晶体管5电性连接,像素电极6在衬底 基板上正投影与对应的两条数据线41在衬底上的正投影交叠设置;沿行方向,每相邻的两 个子像素区之间设置有遮光条7。

[0033] 上述阵列基板中,包括基板以及设于基板上的扫描线、扫描信号线、数据线、薄膜

晶体管、像素电极,基板上包括显示区,在显示区的周侧设置有布线区,显示区内具有阵列 分布的多个子像素区,多个子像素区行列分布,在基板上有相互垂直的行方向和列方向;其 中,扫描线设置在基板上,并且扫描线沿着行方向延伸,多个扫描线沿着列方向依次间隔排 列分布,且扫描线位于相邻的两行子像素区之间,其中,每两条相邻的扫描线构成一个扫描 线组,多个扫描线形成多个扫描线组,每个扫描线组中的两个扫描线与其它扫描线组中的 扫描线均不相同;基板上还设置有扫描信号线,多条扫描信号线沿列方向延伸,扫描信号线 可以设置在两个相邻的两个子像素区列之间,并且,一条扫描信号线仅对应一个扫描线组 中的两条扫描线,并与对应的两个扫描线电性连接,具体地,扫描线信号线可以均匀分布在 基板上,每个扫描信号线与相对应的两个扫描线电性连接,用于给扫描信号线提供电信号, 即在扫描线进行扫描时,可以同时给两个扫描线提供电信号,同时驱动两个扫描线,且扫描 信号线沿列方向延伸,可以将扫描线的驱动电路在基板中沿列方向上的一边引入,进而减 小基板的其它三边的边框宽度;在基板上设置多个数据线对,每个数据线对包括两条间隔 设置的数据线,数据线沿着列方向延伸设置,并且沿着行方向排列分布,数据线对与子像素 区列一一对应设置,在相互对应的数据线对和子像素区列中,数据对中的两条数据线沿着 列方向在对应的子像素区内穿过,在显示区内的数据线可以划分为两部分,沿着列方向,一 部分与子像素区相对,另一部分与两个相邻的子像素区之间的间隔相对,其中,每条数据线 中与子像素区对应的部位与子像素区交叠;其中,在子像素区内设置有像素电极,像素电极 与数据线对中的两个数据线也交叠设置,在子像素区内,除了数据线遮挡的区域,其它区域 都是光效区,其中,这里的光效区,是指子像素区中可以有效透光的区域,并且,沿着行方向 排列的子像素区中,每相邻的两个子像素区之间设置有遮光条,遮光条用于遮盖两个行方 向上的两个相邻子像素之间的间隔,避免漏光,并且避免混色;其中,相比于现有技术,数据 线对中的两个数据线设置在子像素区的两侧,也就是在行方向上相邻的两个子像素区之间 的间隔内设置有两个数据线,这两个数据线之间为避免短路风险,需要间隔一定的距离,则 会增大两个子像素区之间的间隔距离,增大了沿着列方向布置的遮光区的宽度,这些遮光 区都没有光效,挤占了子像素区的光效区,使子像素区的光效区缩减,而本实施例中,数据 线在子像素内穿行,遮光条沿着列方向延伸设置在相邻的子像素区之间,在列方向上,遮光 条可以避免子像素区之间的混色,并且遮光条的沿着行方向上的宽度可以缩减,极大的减 小了行方向两个子像素区之间的遮光宽度,可以有效增大子像素区的光效区,提高光透过 率,上述阵列基板中的子像素区的透光率较现有技术中像素结构可以有较大的提升,上述 阵列基板应用于高分辨率的全面屏产品中,可以有效解决高分辨率的全面屏产品的光透过 率低的问题,提升高分辨率的全面屏产品的光透过率。

[0034] 因此,上述阵列基板中,数据线对中的数据线在对应的子像素区中穿行,行方向上的子像素区之间设置遮光条进行遮光,有效增大了子像素区的光效区,提高光透过率。

[0035] 具体地,上述阵列基板中,数据线与像素电极之间设置有有机绝缘层以隔绝。在基板上的层结构设置上,在数据线与像素电极的层结构叠置方向上,数据线和像素电极之间设置有机绝缘层进行彼此绝缘,并且,有机绝缘层的层厚度可以根据实际需求适当加厚,可以减弱甚至避免数据线与像素电极之间的电场,防止数据线电压跳变时对像素电极产生电压拉动,避免发生信号串扰不良,避免影响显示效果,可以有利于保证正常显示效果。

[0036] 具体地,如图1所示,上述阵列基板还包括与像素电极对应的公共电极8、以及与公

共电极8电连接的公共电极线9,公共电极线给公共电极提供稳定电压,保证正常显示功能。 [0037] 具体地,公共电极设置在基板上,公共电极位于数据线背离基板的一侧,且像素电极位于公共电极背离数据线的一侧;有机绝缘层位于数据线与公共电极之间;公共电极与像素电极之间设置有钝化层以隔绝。也就是,沿着基板上的层结构叠置方向,公共电极位于数据线与像素电极之间,并且公共电极与数据线之间设置有机绝缘层进行隔绝,公共电极与像素电极之间有钝化层进行隔绝,公共电极位于数据线与像素电极之间,可以有效的屏蔽数据线与像素电极之间的电场,防止数据线电压跳变时对像素电极产生电压拉动,出现信号串扰不良;可以有效保证子像素正常显示,并且公共电极设置在数据线与像素电极之间来屏蔽两者之间的电场,则数据线与公共电极之间的有机绝缘的层厚度可以适当的设置小一点,起到绝缘作用就可以,不需要依靠有机绝缘层屏蔽数据线和像素电极之间的电场了,可以有利于减小显示面板的厚度,有利于显示面板轻薄化设计。

[0038] 具体地,上述遮光条为金属遮光条,且金属遮光条与公共电极线电性连接。遮光条与公共电极线可以通过过孔连接,可以使基板上的公共电极的公共电信号均一性更好。

[0039] 具体地,上述遮光条可以与扫描线同层制备,也就是遮光条和扫描线可以在同一金属层中通过图形化处理时制备形成,可以节省制备工序,简化制备流程。

[0040] 具体地,上述阵列基板中,薄膜晶体管包括依次层叠设置的栅极、栅绝缘层、有源层、绝缘层和与有源层电性连接的源、漏电极;其中,栅极可以与扫描线同层制备;源、漏电极可以与数据线同层设置,并且,薄膜晶体管的漏极通过过孔与像素电极电性连接。

[0041] 具体地,上述阵列基板中,对于扫描信号线的数量以及与扫描线组的对应设置关系,扫描信号线设置多条,一般对于扫描信号线的设置,同一条扫描信号线仅对应一个扫描线组中的两条扫描线设置,从数量设置上来说,扫描信号线的数量至少设置扫描线数量的一半,也就是使扫描信号线的数量正好与扫描线的数量对应,实现同时给两个扫描线电信号驱动;或者,也可以设置扫描信号线的数量可以多于扫描线组的数量,多个扫描信号线中除了与扫描线电性连接之外,还会有一部分扫描信号线闲置,这一部分闲置的扫描信号线与与扫描线无电性连接,可以将这部分闲置的扫描信号线局置,这一部分闲置的扫描信号线与与扫描线无电性连接,可以将这部分闲置的扫描信号线与公共电极线电性连接,可以进一步提升显示面板的公共电极的公共电信号的均一性;也或者,在设置扫描信号线的数量多于扫描线组的数量过多时,比如,扫描信号线的数量比扫描线组的数量的多倍以上时,可以设置两条或三条扫描信号线对应一个扫描线组,也就是,两条或三条扫描信号线各自连接到同一个扫描线组,两条或三条扫描信号线同时给一个扫描线组提供扫描信号,可以有效减小阻值。

[0042] 其中,为了保证像素开口率一致性,可以在相邻的两个像素单元之间设置一条扫描信号线,其中,要保证一条扫描信号线与一个扫描线组对应并且电性连接,没有与扫描线连接的扫描信号线可以连接到公共电极线。需要说明的是,上述一条扫描信号线仅与一个扫描线组对应,指的是,同一条扫描信号线只能对应一个扫描线组,只是限定一条扫描信号线只连接到一个扫描线组,但是,一个扫描线组可以同时连接两个以上不同的扫描信号线,当扫描信号线数量过多时,可以两个不同的扫描信号线分别连接到同一个扫描线组,两个不同的扫描信号线同时给同一个扫描线组提供扫描信号,一个扫描线组可以对应多个扫描信号线。

[0043] 具体地,为便于说明扫描信号线的数量和分布设置,以下以8K分辨率,像素单元是

行方向×列方向为7680×4320的像素结构来说明,其中,行方向上,每一行设置为7680个像素单元,每个像素单元是沿行方向排列的3个子像素,列方向上,每一列设置4320个像素单元;

[0044] 对于以上8K分辨率的像素结构,可以有2160个扫描线组,则可以只设置2160条扫描信号线,扫描信号线与扫描线组一一对应设置;

[0045] 或者,可以每列像素单元的一侧设置一条扫描信号线,每个像素单元配一条扫描信号线,在显示面板上均匀设置扫描信号线,有利于提高像素开口率的一致性,则就有7680条扫描信号线,7680为2160的三倍还余1200,所以,可以设置三条扫描信号线连接到同一个扫描线组的两个扫描线,其中,每一个扫描信号线与扫描线组中的两个扫描线都连接,也就是,有三条扫描信号线同时给一个扫描线组中的两个扫描线提供扫描信号,多余的1200条扫描信号线可以电连接到公共电极线。

[0046] 具体地,扫描信号线与数据线同层制备,并且扫描信号线可以与扫描线通过过孔连接以实现电连接,利用同一金属层进行图形化处理同时形成扫描信号线和数据线,节约一张mask,减少制备工序。需要说明的是,扫描信号线也可以与数据线非同层制备,也就是扫描信号线与数据线分两层金属层,利用不同的mask制备,对于扫描信号线的制备,本实施例不做局限。

[0047] 具体地,为了避免数据对中的两个数据线的距离过近而导致短路,将每个数据线对中的两个数据线之间需要有一定的间隔距离,具体地,每个数据线对中的两个数据线之间的间隔距离设置为大于等于5μm,具体地,该处两个数据线之间的间隔距离是指该两个数据线彼此相邻的侧边之间距离;将每个所述数据线对中的两个数据线之间的间隔距离设置为大于等于5μm,可以有效避免发生短路不良的问题,具体地,两个数据线之间的间隔距离和数据线的厚度、材料等因素有关系,只要保证两个相邻的数据线之间不会发生短路,数据线对中的两个数据线之间的间隔距离设置可以为6μm、7μm、7.5μm、8μm、9μm或者其它数值,本实施不做局限。

[0048] 需要说明的是,根据本实施例中数据线的设置,相邻的两个数据线对中,属于不同数据线对的两个相邻的数据线之间的间隔距离也是大于等于7μm的,由于根据本实施例中的像素结构设置,在结构布置时,属于不同数据线对的两个相邻的数据线之间的间隔距离肯定会比较大,会大于7μm,一般不会带来短路问题。

[0049] 具体地,如图1所示,上述阵列基板还包括沿行方向设置并与扫描线对应以用于遮光的遮光层10,这里的遮光层形成遮光黑矩阵,沿着基板的行方向上,设置遮光层遮挡扫描线以及扫描线与子像素区之间的漏光区域,可以有效避免混色。

[0050] 具体地,如图2和图3所示,为了进一步增大光透过率,可以将像素电极6设置为多个间隔设置且依次连接的电极条61,其中,多个电极条61依次间隔并排设置,从多个电极条的排列方向上,一部分电极条的同一端依次连接,另一部分电极条的另一端依次连接,位于中间部位的电极条两端均连接,以使两部分电极条电连接起来,形成一"马"字型像素电极,如图2所示,可以有效提升像素的光透过率。需要说明的是,像素电极中的多个电极条的同一端依次练连接,可以形成梳子形状的像素电极,如图3所示,或者,多个电极条也可以是其它连接方式,形成其它的形状结构,本实施例不做局限。

[0051] 本实施例还提供了一种显示面板,包括如上述实施例提供的任意一种阵列基板。

本实施例中的显示面板为ADS显示面板,显示面板中的像素结构中,子像素区的光效区增大,有效提升了光透过率,其中,相比于现有技术中ADS显示面板,本实施例中的显示面板光透过率可以有效提升大于26%,另外,相比于现有的IPS显示面板,透过率提升也大于20%,有效解决了目前高分辨率全面屏产品透过率较低的问题,提升高分辨率的全面屏产品的光透过率。

[0052] 显然,本领域的技术人员可以对本发明实施例进行各种改动和变型而不脱离本发明的精神和范围。这样,倘若本发明的这些修改和变型属于本发明权利要求及其等同技术的范围之内,则本发明也意图包含这些改动和变型在内。

图2

图3