#### (19) **日本国特許庁(JP)**

# (12) 特許公報(B2)

(11)特許番号

特許第4979212号 (P4979212)

(45) 発行日 平成24年7月18日(2012.7.18)

(24) 登録日 平成24年4月27日(2012.4.27)

| (51) Int.Cl.                           |             | FΙ                  |                     |           |          |        |

|----------------------------------------|-------------|---------------------|---------------------|-----------|----------|--------|

| HO1L 29/78                             | (2006.01)   | HO1L                | 29/78               | 3 O 1 D   |          |        |

| HO1L 21/336                            | (2006.01)   | HO1L                | 27/08               | 102D      |          |        |

| HO1L 27/088                            | (2006.01)   | HO1L                | 29/78               | 3 O 1 Y   |          |        |

| HO1L 21/823                            | 4 (2006.01) | HO1L                | 21/28               | 3 O 1 D   |          |        |

| HO1L 21/28                             | (2006.01)   | HO1L                | 21/28               | 3 O 1 R   |          |        |

|                                        |             |                     |                     | 請求項の数 7   | (全 13 頁) | 最終頁に続く |

| (21) 出願番号 特願2005-250499 (P2005-250499) |             | (73) 特許権者 311003743 |                     |           |          |        |

| (22) 出願日 平成17年8月31日 (2005.8.31)        |             |                     | オンセミコンダクター・トレーディング・ |           |          |        |

| (65) 公開番号 特開2007-67127 (P2007-67127A)  |             | リミテッド               |                     |           |          |        |

| (43) 公開日 平成19年3月15日 (2007.3.15)        |             | 英国領バミューダ・エイチエム 11 ハ |                     |           |          |        |

| 審査請求日 平成20年7月29日 (2008.7.29)           |             | ミルトン・チャーチストリート2・クラレ |                     |           |          |        |

|                                        |             |                     |                     | ンドンハウス・   | コーダン サ   | ービシーズ  |

|                                        |             |                     |                     | リミテッド 気   | 付        |        |

|                                        |             |                     | (74) 代理人            | 100091605 |          |        |

弁理士 岡田 敬

(74)代理人 100147913

弁理士 岡田 義敬

(74)代理人 100166833

弁理士 白石 直子

最終頁に続く

# (54) 【発明の名称】半導体装置及びその製造方法

# (57)【特許請求の範囲】

# 【請求項1】

半導体層と、前記半導体層に形成されるドレイン領域、<u>一環状の</u>ソース領域及びバックゲート領域と、前記半導体層上面に形成されるゲート酸化膜と、前記ゲート酸化膜上に形成されるゲート電極と、前記半導体層上面に形成される絶縁層と、前記ドレイン領域、前記ソース領域または前記ゲート電極上の前記絶縁層に形成されたコンタクトホールとを有する半導体装置において、

前記バックゲート領域内には、前記ソース領域及びバックゲート引き出し領域が形成され、前記バックゲート引き出し領域は、前記ソース領域上のコンタクトホールの開口形状に合わせて、前記ソース領域よりも深部まで形成され、且つ、前記バックゲート引き出し領域は、前記ソース領域に囲まれている領域より、前記ソース領域の深部に形成されている領域の方が広い領域に渡り形成され、

前記ソース領域と前記ドレイン領域との間に配置される前記バックゲート領域がチャネル領域として用いられることを特徴とする半導体装置。

#### 【請求項2】

前記ソース領域は前記半導体層表面から1.0 μm以下の深さまで形成されており、前記バックゲート引き出し領域は前記半導体層表面から1.5 μm以下の深さまで形成されていることを特徴とする請求項1に記載の半導体装置。

#### 【請求項3】

半導体層にバックゲート領域、ドレイン領域を形成し、前記半導体層上にゲート酸化膜及

びゲート電極を形成する工程と、

前記バックゲート領域内の所望の領域上にレジストマスクを被覆した状態でイオン注入を行い、前記レジストマスクを囲むように<u>前記バックゲート領域内に</u>ソース領域を形成<u>し</u>、前記ソース領域と前記ドレイン領域との間の前記バックゲート領域をチャネル領域とする工程と、

前記半導体層上面に絶縁層を形成し、前記バックゲート領域上面であり、前記ソース領域に囲まれた領域が露出するように、前記絶縁層にソース電極用のコンタクトホールを形成する工程と、

前記ソース電極用のコンタクトホールを介して前記バックゲート領域にイオン注入を行い、前記ソース領域に囲まれた領域及び前記ソース領域よりも深部まで拡散するバックゲート引き出し領域を<u>前記バックゲート領域内に</u>形成する工程とを有することを特徴とする 半導体装置の製造方法。

#### 【請求項4】

前記バックゲート引き出し領域を形成する工程では、イオン注入条件の異なる2回のイオン注入工程を行い、1回目の不純物の導入量は2回目の不純物の導入量よりも多いことを特徴とする請求項3に記載の半導体装置の製造方法。

#### 【請求項5】

前記バックゲート引き出し領域を形成する工程では、1回目の不純物の導入量は、前記バックゲート引き出し領域と前記ソース領域とが重畳する領域が前記ソース領域となる条件であることを特徴とする請求項4に記載の半導体装置の製造方法。

#### 【請求項6】

前記バックゲート引き出し領域を形成する工程では、1回目の加速電圧は不純物が前記ソース領域を突き抜けない条件であることを特徴とする請求項4または請求項5に記載の半導体装置の製造方法。

#### 【請求項7】

前記バックゲート引き出し領域を形成する工程では、2回目の加速電圧は不純物が前記ソース領域を突き抜ける条件であり、前記ソース領域より深部に前記コンタクトホールの開口部形状の前記バックゲート引き出し領域を形成することを特徴とする請求項4から請求項6のいずれか1項に記載の半導体装置の製造方法。

### 【発明の詳細な説明】

### 【技術分野】

# [0001]

本発明は、デバイスサイズを縮小し、合わせて寄生トランジスタ動作を防止する半導体装置及びその製造方法に関する。

# 【背景技術】

#### [0002]

従来の半導体装置では、シリコン基板表面にN型のドレインウェル領域及びP型のバックゲート領域が形成されている。ドレインウェル領域には、更に、高濃度のN型のドレイン領域が形成されている。一方、バックゲート領域には、N型のソース領域が形成されている。ドレイン領域とソース領域との間のシリコン基板表面にはゲート電極が形成されている。そして、バックゲート領域には、更に、ソース電極と接続するP型の拡散層が形成され、Nチャネル型のMOSFETが形成されている。この構造により、バックゲート領域とソース領域とは同電位に保たれ、寄生NPNトランジスタの動作が抑止されている(例えば、特許文献1参照。)。

#### [0003]

従来の半導体装置の製造方法では、MOSFET形成領域において、基板表面に酸化膜を形成した後、イオン注入法により、ドレイン領域として用いるN型の拡散層、バックゲート領域として用いるP型の拡散層を形成する。その後、必要に応じて、イオン注入法により、バックゲート領域として用いるP型の拡散層及びソース領域として用いるN型の拡散層に、ソース電極と接続するP型の拡散層を

10

20

30

40

形成する。そして、ソース領域として用いるN型の拡散層及びバックゲート領域として用いるP型の拡散層と接続するようにソース電極を形成する。その結果、バックゲート領域として用いるP型の拡散層とソース領域として用いるN型の拡散層とは同電位となり、寄生NPNトランジスタの動作が抑止される(例えば、特許文献2参照。)。

【特許文献 1 】特開 2 0 0 1 - 1 1 9 0 1 9 号公報(第6 - 7 頁、第1 - 3 図)

【 特 許 文 献 2 】 特 開 平 9 - 1 3 9 4 3 8 号 公 報 ( 第 5 - 6 頁 、 第 4 - 6 図 )

【発明の開示】

【発明が解決しようとする課題】

[0004]

上述したように、従来の半導体装置では、バックゲート領域にソース領域、寄生トランジスタ動作を抑止するP型の拡散層を形成した後に、ソース電極用のコンタクトホールが形成される。そして、ソース電極は、該コンタクトホールを介して、P型の拡散層とソース領域とに接続している。この構造により、コンタクトホール形成時にP型の拡散層を形成する際のマスクずれ及びコンタクトホールを形成する際のマスクずれが考慮され、コンタクトホールの幅が大きくなってしまう。その結果、デバイスサイズを縮小し難いという問題がある。

[0005]

また、従来の半導体装置では、Nチャネル型のMOSFET素子内の寄生NPNトランジスタ動作を抑止するために、バックゲート領域に、P型の拡散層が形成されている。しかしながら、P型の拡散層は熱拡散工程により形成されるため、バックゲート領域深部での形成領域が狭くなってしまう。この構造により、バックゲート領域深部での抵抗値が低減し難く、寄生NPNトランジスタ動作を抑止し難いという問題がある。一方、バックゲート領域深部において、P型の拡散層を広い領域に渡り形成する場合には、熱拡散時間が多くなり、横方向拡散も考慮する必要がある。この場合には、デバイスサイズが、必要以上に大きくなってしまうという問題がある。

[0006]

また、従来の半導体装置の製造方法では、Nチャネル型のMOSFET素子内の寄生NPNトランジスタ動作を抑止するため、バックゲート領域に、P型の拡散層を形成する。このとき、バックゲート領域の抵抗値を低減し、寄生NPNトランジスタのベース抵抗値を低減するため、不純物濃度の高いP型の拡散層を形成する。しかしながら、P型の拡散層を形成する際のマスクずれにより、P型の拡散層がゲート電極下方のチャネルが形成される領域に形成されてしまう場合がある。この場合、寄生NPNトランジスタ動作を抑止できるが、MOSFETのしきい値(Vth)が変調するという問題がある。

[0007]

また、従来の半導体装置の製造方法では、シリコン基板にMOSFETのバックゲート領域、ソース領域及びバックゲート領域にP型の拡散層を形成した後に、シリコン基板上に絶縁層を形成する。そして、公知のフォトリソグラフィ技術を用い、絶縁層にコンタクトホールを形成した後、ソース電極等を形成する。この製造方法により、ソース電極用のコンタクトホールを形成する際には、P型の拡散層に対するマスクずれの他に、P型の拡散層を形成する際のマスクずれも考慮する必要がある。そのため、ソース電極用のコンタクトホールの幅が大きくなり、デバイスサイズを縮小し難いという問題がある。

【課題を解決するための手段】

[0008]

上述した各事情に鑑みて成されたものであり、本発明の半導体装置では、半導体層と、前記半導体層に形成されるドレイン領域、ソース領域及びバックゲート領域と、前記半導体層上面に形成されるゲート酸化膜と、前記ゲート酸化膜上に形成されるゲート電極と、前記半導体層上面に形成される絶縁層と、前記ドレイン領域、前記ソース領域または前記ゲート電極上の前記絶縁層に形成されたコンタクトホールとを有する半導体装置において、前記バックゲート領域にはバックゲート引き出し領域が形成され、前記バックゲート引き出し領域は前記ソース領域よりモ深部まで形成され、且つ、前記ソース領域より深部に

10

20

30

40

位置する前記バックゲート引き出し領域は、少なくとも前記ソース領域上の前記コンタクトホールの開口領域全てに形成されていることを特徴とする。従って、本発明では、ソース領域の下方にもバックゲート引き出し領域が形成されている。この構造により、バックゲート領域深部での抵抗値が低減され、寄生トランジスタの動作を抑止することができる

#### [0009]

また、本発明の半導体装置では、前記バックゲート引き出し領域は、前記ソース領域に 囲まれている領域より、前記ソース領域の深部に形成されている領域の方が広い領域に渡 り形成されていることを特徴とする。従って、本発明では、コンタクト抵抗を低減しつつ 、バックゲート領域深部での抵抗値を低減することができる。この構造により、ソース電 極用のコンタクトホール形状の微細化を図り、デバイスサイズを縮小することができる。

[0010]

また、本発明の半導体装置の製造方法では、半導体層にバックゲート領域、ドレイン領域を形成し、前記半導体層上にゲート酸化膜及びゲート電極を形成した後、前記バックゲート領域の所望の領域上にレジストマスクを被覆した状態でイオン注入を行い、前記バックゲート領域上のレジストマスクを除去した領域を囲むようにソース領域を形成する工程と、前記半導体層上面に絶縁層を形成し、前記絶縁層にコンタクトホールを形成した後、前記バックゲート領域上に位置する前記コンタクトホールを介して前記バックゲート領域にイオン注入を行い、前記バックゲート領域上のレジストマスクを除去した領域にイオン注入を行い、前記バックゲート領域上のレジストマスクを除去した領域にバックゲート引き出し領域を形成する工程とを有することを特徴とする。従って、本発明では、ソース電極用のコンタクトホールを形成した後に、該コンタクトホールを利用してバックゲート引き出し領域を形成する。この製造方法により、ソース電極用のコンタクトホール形状を小さくすることができ、デバイスサイズを縮小することができる。

#### [0011]

また、本発明の半導体装置の製造方法では、前記バックゲート引き出し領域を形成する工程では、イオン注入条件の異なる2回のイオン注入工程を行い、1回目の不純物の導入量は2回目の不純物の導入量よりも多いことを特徴とする。従って、本発明では、絶縁層をマスクとし、ソース電極用のコンタクトホールを利用してバックゲート引き出し領域を形成する。この製造方法により、2回目のイオン注入工程に起因するチャネリングを抑止することができる。

[0012]

また、本発明の半導体装置の製造方法では、前記バックゲート引き出し領域を形成する 工程では、1回目の不純物の導入量は、前記バックゲート引き出し領域と前記ソース領域 とが重畳する領域が前記ソース領域となる条件であることを特徴とする。従って、本発明 では、ソース領域に囲まれたバックゲート領域に対し、バックゲート引き出し領域を形成 する。この製造方法により、ソース電極用のコンタクトホール形成後に、該コンタクトホ ールを利用してバックゲート引き出し領域を形成することができる。

# [0013]

また、本発明の半導体装置の製造方法では、前記バックゲート引き出し領域を形成する 工程では、1回目の加速電圧は不純物が前記ソース領域を突き抜けない条件であることを 特徴とする。従って、本発明では、1回目のイオン注入時の加速電圧を小さくすることで 、1回目のイオン注入工程に起因するチャネリングを低減することができる。

[0014]

また、本発明の半導体装置の製造方法では、前記バックゲート引き出し領域を形成する 工程では、2回目の加速電圧は不純物が前記ソース領域を突き抜ける条件であり、前記ソ ース領域より深部に前記コンタクトホールの開口部形状の前記バックゲート引き出し領域 を形成することを特徴とする。従って、本発明では、ソース領域より深部にバックゲート 引き出し領域を形成することで、寄生トランジスタの動作を抑止することができる。

### 【発明の効果】

10

20

30

#### [0015]

本発明では、バックゲート領域において、バックゲート引き出し領域が、ソース電極用のコンタクトホールの開口形状に合わせて、ソース領域よりも深部まで形成されている。この構造により、バックゲート領域での抵抗値を低減することができ、寄生トランジスタの動作を抑止することができる。

#### [0016]

また、本発明では、ソース電極用のコンタクトホールの開口形状に合わせて、バックゲート引き出し領域が形成されている。この構造により、ソース電極用のコンタクトホール 形状の微細化を図り、デバイスサイズを縮小することができる。

#### [0017]

また、本発明では、ソース領域を一環状に形成した後に、絶縁層に形成されたコンタクトホールを利用して、バックゲート引き出し領域を形成する。この製造方法により、バックゲート引き出し領域形成時のマスクずれ及びソース電極用のコンタクトホール形成時のマスクずれを考慮する必要がない。その結果、ソース電極用のコンタクトホール形状の微細化を図り、デバイスサイズを縮小することができる。

#### [0018]

また、本発明では、絶縁層をマスクとして、2回のイオン注入工程によりバックゲート引き出し領域を形成する。そして、1回目の不純物の導入量は、2回目の不純物の導入量よりも多い。この製造方法により、2回目のイオン注入を高加速電圧で行った場合でも、チャネリングを抑制することができる。

#### [0019]

また、本発明では、バックゲート引き出し領域を形成する際、2回目のイオン注入時の加速電圧は、不純物がソース領域より深部に形成される条件である。この製造方法により、ソース電極用のコンタクトホールの開口形状に合わせて、ソース領域よりも深部までバックゲート引き出し領域を形成できる。そして、バックゲート領域での抵抗値を低減することができ、寄生トランジスタの動作を抑止することができる。

# 【発明を実施するための最良の形態】

# [0020]

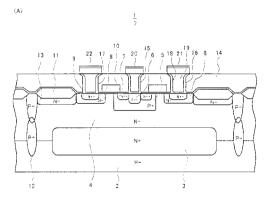

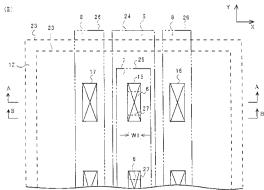

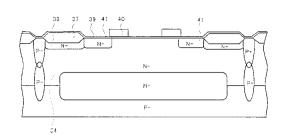

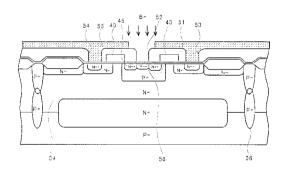

以下に、本発明の一実施の形態である半導体装置について、図1~図2を参照し、詳細に説明する。図1(A)は、本実施の形態の半導体装置を説明するための断面図である。図1(B)は、本実施の形態の半導体装置を説明するための平面図である。図2は、本実施の形態の半導体装置を説明するための断面図である。

#### [0021]

図1(A)に示す如く、Nチャネル型MOSトランジスタ1は、主に、P型の単結晶シリコン基板2と、N型の埋込拡散層3と、N型のエピタキシャル層4と、バックゲート領域として用いられるP型の拡散層5、6と、ソース領域として用いられるN型の拡散層7と、ドレイン領域として用いられるN型の拡散層8、9と、ゲート電極10とから構成されている。

### [0022]

N型のエピタキシャル層 4 が、 P型の単結晶シリコン基板 2 上に形成されている。基板 2 とエピタキシャル層 4 には、 N型の埋込拡散層 3 が形成されている。尚、本実施の形態での基板 2 及びエピタキシャル層 4 が本発明の「半導体層」に対応する。そして、本実施の形態では、基板 2 上に 1 層のエピタキシャル層 4 が形成されている場合を示すが、この場合に限定するものではない。例えば、本発明の「半導体層」としては、基板のみの場合でも良く、基板上面に複数のエピタキシャル層が積層されている場合でも良い。また、基板は、 N型の単結晶シリコン基板、化合物半導体基板でも良い。

#### [0023]

P型の拡散層 5 が、エピタキシャル層 4 に形成されている。 P型の拡散層 5 には、その 形成領域を重畳させるように、 P型の拡散層 6 が形成されている。 P型の拡散層 6 はエピ タキシャル層 4 表面から 1 . 5 (μm程度)以下の深さまで形成されている。そして、 P 10

20

30

40

型の拡散層 5 、 6 は、バックゲート領域として用いられる。尚、本実施の形態での P 型の拡散層 6 が本発明の「バックゲート引き出し領域」に対応する。

#### [0024]

N型の拡散層 7 が、 P型の拡散層 5 に形成されている。 N型の拡散層 7 は、ソース領域として用いられる。 N型の拡散層 7 と P型の拡散層 6 とはソース電極に接続し、同電位となる。 そして、 N型の拡散層 7 はエピタキシャル層 4 表面から 1 . 0 (μ m 程度)以下の深さまで形成されている。

### [0025]

N型の拡散層 8 、 9 が、エピタキシャル層 4 に形成されている。 N型の拡散層 8 、 9 はドレイン領域として用いられる。そして、ゲート電極 1 0 下方に位置し、N型の拡散層 7 とN型の拡散層 8 との間に位置する P型の拡散層 5 は、チャネル領域として用いられる。

[0026]

ゲート電極10は、ゲート酸化膜上面に形成されている。ゲート電極10は、例えば、ポリシリコン膜とタングステンシリコン膜とにより所望の膜厚となるように形成されている。

#### [0027]

LOCOS(Local Oxidation of Silicon)酸化膜11が、エピタキシャル層4に形成されている。LOCOS酸化膜11の平坦部では、その膜厚が、例えば、3000~5000 程度となる。N型の拡散層8とP型の分離領域12との間のLOCOS酸化膜11の下方には、N型の拡散層13が形成されている。N型の拡散層13は、エピタキシャル層4表面が反転することを防止している。

[0028]

絶縁層 1.4 が、エピタキシャル層 4 上面に形成されている。絶縁層 1.4 は、 B P S G (B o r o n P h o s p h o S i l i c a t e G l a s s ) 膜、 S O G (S p i n O n G l a s s ) 膜等により、形成されている。そして、公知のフォトリソグラフィ技術を用い、例えば、 C H F  $_3$  + O  $_2$  系のガスを用いたドライエッチングにより、絶縁層 1.4 にコンタクトホール 1.5 、 1.6 、 1.7 が形成されている。

#### [0029]

コンタクトホール 1 5 、 1 6 、 1 7 には、バリアメタル膜 1 8 及びタングステン(W)膜 1 9 が埋設されている。タングステン膜 1 9 の表面には、アルミシリコン銅(A 1 S i C u )膜及びバリアメタル膜が選択的に形成され、ソース電極 2 0 及びドレイン電極 2 1 、2 2 が形成されている。尚、図 1 に示した断面では、ゲート電極 1 0 への配線層は図示していないが、その他の領域で配線層と接続している。

[0030]

図1(B)に示す如く、点線23で囲まれる領域が分離領域12を示し、一点鎖線24の内側の領域がP型の拡散層5を示し、二点差線25の内側の領域がN型の拡散層7を示し、三点鎖線26の内側の領域がN型の拡散層8を示している。図示したように、分離領域12で囲まれた領域には、P型の拡散層5及びN型の拡散層8が、図示したY軸方向に延在している。N型の拡散層8は、P型の拡散層5を挟むようにP型の拡散層5の両側に形成されている。一方、P型の拡散層5にはN型の拡散層7が形成され、N型の拡散層7には、実線27で示すように、P型の拡散層6がY軸方向に一定間隔で形成されている。

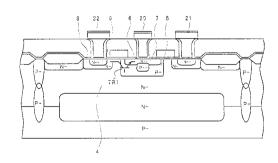

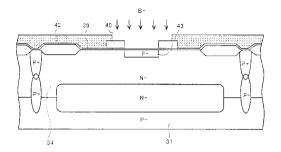

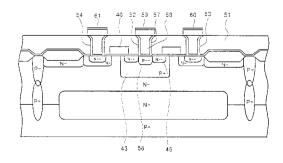

[0031]

図1(A)に示す断面図は、図1(B)に示すA・A線方向の断面図であり、エピタキシャル層4表面にP型の拡散層6が露出している領域である。一方、図2に示す断面図は、図1(B)に示すB・B線方向の断面図であり、N型の拡散層7の下方にP型の拡散層6が形成されている。詳細は半導体装置の製造方法の説明で後述するが、P型の拡散層6は、コンタクトホール15を形成した後に、それぞれ異なる条件の2回のイオン注入工程により、形成されている。この製造方法により、コンタクトホール15の形状に合わせてP型の拡散層6が形成されるので、コンタクトホール15を形成する際に、P型の拡散層6を形成する際のマスクず

10

20

30

40

れも考慮する必要がない。その結果、コンタクトホール15の幅W1を狭めることができ、MOSトランジスタ1サイズを縮小することができる。そして、1枚のウエハから取れる個数を増大させることができる。

#### [0032]

更に、N型の拡散層 7 に囲まれる領域では、P型の拡散層 6 は点線 2 7 (図 1 ( B ) 参照)で囲まれる領域に形成されている。一方、N型の拡散層 7 より深部では、P型の拡散層 6 はコンタクトホール 1 5 の開口形状に合わせて形成されている。つまり、P型の拡散層 6 は、N型の拡散層 7 より深部において、N型の拡散層 7 に囲まれる領域よりも広い領域に渡り形成されている。この構造により、P型の拡散層 5 深部での抵抗値を低減し、MOSトランジスタ 1 内の寄生トランジスタ動作を抑止することができる。

# [0033]

ここで、図2に示すように、寄生NPNトランジスタ(TR1)について説明する。寄生NPNトランジスタは、N型のエピタキシャル層 4、N型の拡散層 8、9からなるコレクタ領域と、P型の拡散層 5、6からなるベース領域と、N型の拡散層 7 からなるエミッタ領域とから構成されている。MOSトランジスタ1の動作時では、P型の拡散層 6 とN型の拡散層 7 とはソース電極と接続し、ベース領域とエミッタ領域とは同電位に保たれ、寄生NPNトランジスタは動作しない。例えば、MOSトランジスタ1のターンオフ時に、ゲート電極 1 0 下方の反転層(P型の拡散層 5 に形成されている自由キャリア(電子)が流れている領域)を流れる自由キャリア(電子)が、P型の拡散層 5 を経由してP型の拡散層 6 へと流れる。このとき、P型の拡散層 5、6の抵抗値が大きい場合には、寄生NPNトランジスタのベース・エミッタ間に電位差が生じ、寄生NPNトランジスタがON動作する。

#### [0034]

そこで、上述したように、P型の拡散層 6 が、コンタクトホール 1 5 の形状に合わせて、N型の拡散層 7 の下方に形成される構造により、P型の拡散層 5 、 6 の抵抗値を低減することができる。そして、寄生 N P N トランジスタのベース・エミッタ間の電位差を小さくすることで、寄生 N P N トランジスタの O N 動作を防止することができる。その結果、M O S トランジスタ 1 の安全動作領域を広げることができる。

### [0035]

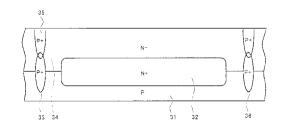

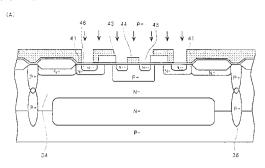

次に、本発明の一実施の形態である半導体装置の製造方法について、図3から図8を参照し、詳細に説明する。図3から図6(A)及び図7から図8は、本実施の形態における半導体装置の製造方法を説明するための断面図である。図6(B)は、本実施の形態における半導体装置の製造方法を説明するための平面図である。尚、以下の説明では、分離領域で区画された、1つの素子形成領域に、例えば、Nチャネル型のMOSトランジスタを形成する場合に関し説明するが、この場合に限定するものではない。例えば、その他の素子形成領域に、Pチャネル型のMOSトランジスタ、NPN型のトランジスタ、縦型PNPトランジスタ等を形成し、半導体集積回路装置を形成する場合でも良い。

#### [0036]

先ず、図3に示す如く、P型の単結晶シリコン基板31を準備する。基板31の表面から、公知のフォトリソグラフィ技術を用い、N型不純物、例えば、リン(P)をイオン注入し、N型の埋込拡散層32を形成する。次に、基板31の表面から、公知のフォトリソグラフィ技術を用い、P型不純物、例えば、ホウ素(B)をイオン注入し、P型の埋込拡散層33を形成する。その後、基板31をエピタキシャル成長装置のサセプタ上に配置する。そして、ランプ加熱によって基板31に、例えば、1200 程度の高温を与えると共に反応管内にSiHCl<sub>3</sub>ガスとH<sub>2</sub>ガスを導入する。この工程により、基板31上に、例えば、比抵抗0.1~2.0 ・cm、厚さ1.0~10.0μm程度のエピタキシャル層34を成長させる。

# [0037]

その後、エピタキシャル層 3 4 の表面から、公知のフォトリソグラフィ技術を用い、P型不純物、例えば、ホウ素(B)をイオン注入し、P型の拡散層 3 5 を形成する。そして

10

20

30

40

、P型の埋込拡散層33とP型の拡散層35とが連結することで、分離領域36が形成される。上述したように、分離領域36により、基板31及びエピタキシャル層34は、複数の島領域に区分される。

#### [0038]

尚、本実施の形態での基板 3 1 及びエピタキシャル層 3 4 が本発明の「半導体層」に対応する。そして、本実施の形態では、基板 3 1 上に 1 層のエピタキシャル層 3 4 が形成されている場合を示すが、この場合に限定するものではない。例えば、本発明の「半導体層」としては、基板のみの場合でも良く、基板上面に複数のエピタキシャル層が積層されている場合でも良い。また、基板は、N型の単結晶シリコン基板、化合物半導体基板でも良い。

[0039]

次に、図4に示す如く、LOCOS酸化膜37を形成する部分に開口部が設けられた絶縁層をマスクとして用い、N型不純物、例えば、リン(P)をイオン注入し、N型の拡散層38を形成する。その後、LOCOS酸化膜37を形成することで、N型の拡散層38をLOCOS酸化膜37に対して位置精度良く形成することができる。そして、エピタキシャル層34上に、シリコン酸化膜39、ポリシリコン膜及びタングステンシリコン膜を、順次、堆積する。公知のフォトリソグラフィ技術を用い、ポリシリコン膜及びタングステンシリコン膜を選択的に除去し、ゲート電極40を形成する。尚、ゲート電極40下方のシリコン酸化膜39はゲート酸化膜として用いられる。その後、N型不純物、例えば、リン(P)をイオン注入し、N型の拡散層41を形成する。N型の拡散層41はドレイン領域として用いられる。

[0040]

次に、図5に示す如く、エピタキシャル層34上にフォトレジスト42を形成する。そして、公知のフォトリソグラフィ技術を用い、P型の拡散層43が形成される領域上のフォトレジスト42に開口部を形成する。その後、P型不純物、例えば、ホウ素(B)をイオン注入し、P型の拡散層43を形成する。

[0041]

次に、図6(A)に示す如く、エピタキシャル層34上にフォトレジスト44を形成する。そして、公知のフォトリソグラフィ技術を用い、N型不純物、例えば、リン(P)をイオン注入し、N型の拡散層45、46を形成する。N型の拡散層45はP型の拡散層43に重畳して形成される。N型の拡散層45とP型の拡散層43とが重畳する領域は、N型の不純物濃度とP型の不純物濃度とが補正され、N型の拡散領域となり、ソース領域として用いられる。一方、N型の拡散層46はドレイン領域として用いられ、ドレイン領域はN型の拡散層41、46とにより二重拡散構造となる。

[0042]

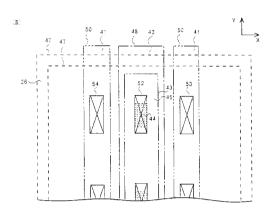

ここで、図6(B)はMOSトランジスタのパターン図の一部を示している。点線47で囲まれる領域が分離領域36を示し、一点鎖線48の内側の領域がP型の拡散層43を示し、二点差線49の内側の領域がN型の拡散層45を示し、三点鎖線50の内側の領域がN型の拡散層41を示している。図示したように、N型の拡散層45が形成されるP型の拡散層43には、その一部にフォトレジスト44が被覆されている。尚、図6(A)に示すように、N型の拡散層45、46が形成されていない領域にはフォトレジスト44が被覆されているが、図6(B)では省略している。

[0043]

その後、リン(P)をイオン注入し、P型の拡散層43にN型の拡散層45を形成し、フォトレジスト44を除去する。つまり、P型の拡散層43上にフォトレジスト44が形成されていた領域は、P型の拡散層43の状態のままである。

[0044]

次に、図7に示す如く、エピタキシャル層34上に絶縁層51として、例えば、BPSG(Boron Phospho Silicate Glass)膜、SOG(Spin On Glass)膜等を堆積する。そして、公知のフォトリソグラフィ技術を用い

10

20

30

40

10

20

30

40

50

、例えば、 $CHF_3 + O_2$ 系のガスを用いたドライエッチングで、絶縁層 5.1 にコンタクトホール 5.2 、 5.3 、 5.4 を形成する。

#### [0045]

絶縁層51上にフォトレジスト55を形成し、コンタクトホール52が開口した状態となるように、フォトレジスト55を選択的に除去する。そして、コンタクトホール52を介してエピタキシャル層34に、P型不純物、例えば、ホウ素(B)をイオン注入する。このとき、図6(B)に実線で示すように、コンタクトホール52は形成されている。コンタクトホール52の開口領域には、N型の拡散層45と、N型の拡散層45に周囲を囲まれたP型の拡散層43とが位置している。そのため、コンタクトホール52から注入されたホウ素(B)により、P型の拡散層43にはP型の拡散層56が形成される。一方、コンタクトホール52内のN型の拡散層45に注入されたホウ素(B)は、N型の不純物濃度とP型の不純物濃度との補正により、N型の拡散層45の状態のままである。

#### [0046]

具体的には、コンタクトホール 5 2 を利用して、 2 回のイオン注入工程により、 P 型の拡散層 5 6 を形成する。 P 型の拡散層 5 6 を形成する際の 1 回目のイオン注入条件は、 例えば、ホウ素( B )を加速電圧 4 0 ~ 6 0 k e V 、導入量 1 . 0 × 1 0  $^{1}$   $^{4}$  ~ 1 . 0 × 1 0  $^{1}$   $^{6}$  / c m  $^{2}$  である。 2 回目のイオン注入条件は、 例えば、ホウ素( B )を加速電圧 7 0 ~ 9 0 k e V 、導入量 1 . 0 × 1 0  $^{1}$   $^{3}$  ~ 1 . 0 × 1 0  $^{1}$   $^{5}$  / c m  $^{2}$  である。

#### [0047]

#### [0048]

また、この製造方法により、コンタクトホール 5 2 の形成位置に合わせて、 2 回のイオン注入工程により、 P 型の拡散層 5 6 を形成できる。そのため、コンタクトホール 5 2 形成前に P 型の拡散層 5 6 を形成する工程を省略できる。そして、 P 型の拡散層 5 6 を形成する際のマスクずれを考慮することなく、ゲート電極 4 0 下方に位置する P 型の拡散層 4 3 の不純物濃度が高くなることはない。その結果、 M O S トランジスタの V t h 値が変調することを防止することができる。

#### [0049]

更に、P型の拡散層 5 6 を形成するイオン注入工程時に、コンタクトホール 5 2 を利用することで、P型の拡散層 5 6 とコンタクトホール 5 2 とのマスクずれを考慮する必要がない。例えば、P型の拡散層 5 6 を形成した後にコンタクトホール 5 2 を形成する場合には、コンタクトホール 5 2 幅に加えて、マスクずれ幅としてコンタクトホール 5 2 の周囲に 0 . 6 (μm)程度必要とされる。しかしながら、本実施の形態では、マスクずれ幅を考慮する必要はなく、図 7 に示す断面では、コンタクトホール 5 2 の左右に考慮されるマスクずれ幅(1 . 2 μm程度)を省くことができる。そして、MOSトランジスタサイズを縮小することができる。

#### [0050]

更に、P型の拡散層56を形成するイオン注入工程時に、絶縁層51をマスクとして用

いて、 P 型の拡散層 5 6 を形成する。そのため、フォトレジストをマスクとする場合と比 較し、不純物の導入量により開口部近傍のマスクがだれることが無く、1回目のイオン注 入工程時に、不純物の導入量の多い工程を行うことができる。この製造方法により、2回 目のイオン注入時には、1回目よりも加速電圧が大きくなるが、チャネリングを抑制する ことができる。これは、1回目の加速電圧の低いイオン注入工程により、エピタキシャル 層34表面にはアモルファス化したスルー膜が形成されているからである。

尚、本実施の形態での P 型の拡散層 5 6 が本発明の「バックゲート引き出し領域」に対 応する。

# [0052]

最後に、図8に示す如く、コンタクトホール52、53、54内壁等にバリアメタル膜 57を形成する。その後、コンタクトホール52、53、54内をタングステン(W)膜 58で埋設する。そして、タングステン膜58上面に、CVD法により、アルミ・シリコ ン-銅(Al-Si-Cu)膜、バリアメタル膜を堆積する。その後、公知のフォトリソ グラフィ技術を用い、アルミ・シリコン・銅膜及びバリアメタル膜を選択的に除去し、ソ ース電極59及びドレイン電極60、61を形成する。尚、図8に示した断面では、ゲー ト電極への配線層は図示していないが、その他の領域で配線層と接続している。

#### [0053]

尚、本実施の形態では、P型の拡散層43にN型の拡散層45を形成し、コンタクトホ ール52を形成した後に、コンタクトホール52を利用してP型の拡散層56を形成する 場合について説明したが、この場合に限定するものではない。例えば、P型の拡散層43 にN型の拡散層45を形成し、フォトレジストをマスクして用いP型の拡散層56を形成 した後にコンタクトホール52を形成する場合でも良い。この場合でも、P型の拡散層5 6 を所望の領域に形成することができ、MOSトランジスタの寄生NPNトランジスタの 動作トランジスタ動作を抑止することができる。

#### [0054]

また、本実施の形態では、P型の拡散層56を形成する際に、コンタクトホール52を 介して、加速電圧の異なる2回のイオン注入工程により形成する場合について説明したが 、この場合に限定するものではない。例えば、コンタクトホール52を介して、3回、4 回等、複数回のイオン注入工程によりP型の拡散層56を形成する場合でも良い。その他 、本発明の要旨を逸脱しない範囲で、種々の変更が可能である。

# 【図面の簡単な説明】

#### [0055]

【図1】本発明の実施の形態における半導体装置を説明する(A)断面図、(B)平面図 である。

【図2】本発明の実施の形態における半導体装置を説明する断面図である。

- 【図3】本発明の実施の形態における半導体装置の製造方法を説明する断面図である。

- 【図4】本発明の実施の形態における半導体装置の製造方法を説明する断面図である。

- 【図5】本発明の実施の形態における半導体装置の製造方法を説明する断面図である。

- 40 【図6】本発明の実施の形態における半導体装置の製造方法を説明する(A)断面図、( B) 平面図である。

【図7】本発明の実施の形態における半導体装置の製造方法を説明する断面図である。

【図8】本発明の実施の形態における半導体装置の製造方法を説明する断面図である。

# 【符号の説明】

#### [0056]

- Nチャネル型MOSトランジスタ

- P 型の単結晶シリコン基板

- N型のエピタキシャル層

- 5 P型の拡散層

- P型の拡散層

20

10

- 7 N型の拡散層

- 8 N型の拡散層

- 10 ゲート電極

- 15 コンタクトホール

【図2】

【図3】

# 【図4】

# 【図5】

【図6】

【図7】

【図8】

### フロントページの続き

(51) Int.CI. F I

H 0 1 L

29/417

(2006.01)

H 0 1 L

29/50

M

H 0 1 L

29/423

(2006.01)

H 0 1 L

29/58

G

H 0 1 L

29/49

(2006.01)

H 0 1 L

21/90

C

H 0 1 L

21/768

(2006.01)

(72)発明者 大竹 誠治

大阪府守口市京阪本通2丁目5番5号 三洋電機株式会社内

(72)発明者 神田 良

大阪府守口市京阪本通2丁目5番5号 三洋電機株式会社内

(72)発明者 菊地 修一

大阪府守口市京阪本通2丁目5番5号 三洋電機株式会社内

# 審査官 松本 陶子

(56)参考文献 特開2004-335633(JP,A)

特開2002-314065(JP,A)

特開2002-314066(JP,A)

特開昭59-094874(JP,A)

特開昭60-117778(JP,A)

特開2002-141502(JP,A)

# (58)調査した分野(Int.CI., DB名)

H01L 29/49