#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

WIPOIPCT

## (19) World Intellectual Property **Organization**

International Bureau

12 November 2020 (12.11.2020)

(10) International Publication Number WO 2020/225588 A1

(51) International Patent Classification:

H01L 21/02 (2006.01) H01L 21/761 (2006.01) H01L 21/20 (2006.01) H01L 29/16 (2006,01) H01L 21/22 (2006.01) H01L 29/167 (2006.01)

(21) International Application Number:

PCT/IB2019/053661

(22) International Filing Date:

H01L 21/74 (2006.01)

04 May 2019 (04.05.2019)

(25) Filing Language:

English

(26) Publication Language:

**English**

- (71) Applicant: TRIEYE LTD. [IL/IL]; 7 Shevah St., 6777937 Tel Aviv (IL).

- (72) Inventors: KATZIR, Eran; 31A Moshe Kole St., 9371257 Jerusalem (IL), IMMER, Vincent; 13 HaZeit St., 3090448 Zichron Yaakov (IL). KAPACH, Omer; 9/5 Ha-Rav Shmuel Braukh St., 9738008 Jerusalem (IL). BAKAL, Avra-

ham; 144 Jabotinsky St., 6299111 Tel Aviv (IL). LEVY, Uriel; 13 Hakfar St., 5552507 Kiryat Ono (IL).

- (74) Agent: NATHAN & ASSOCIATES PATENT AGENTS LTD; P.O. BOX 10178, 6110101 Tel-Aviv (IL).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ,

(54) Title: LOW LEAKAGE CURRENT GERMANIUM-ON-SILICON PHOTO-DEVICES

#

UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### **Published:**

— with international search report (Art. 21(3))

## LOW LEAKAGE CURRENT GERMANIUM-ON-SILICON PHOTO-DEVICES

### **FIELD**

Embodiments disclosed herein relate in general to germanium (GE) - on - silicon (Si) photo-devices (also referred to as "optoelectronic" devices) and more particularly to structures and methods of reducing leakage currents in such photo-devices.

## **BACKGROUND**

10

15

20

25

30

5

Ge-on-Si microelectronic devices (e.g. diodes and transistors) and optoelectronic devices (e.g. photodiodes) are known. The high carrier mobility in Ge compared to that in Si is advantageous for high-speed electronics. Furthermore, the ability of Ge to absorb light in the infrared band of 1000 to 1600 nm (also referred to as the short wave infrared or "SWIR" band) led to the development of Ge-based devices on the telecommunication and infrared (IR) imaging markets. With the development of various epitaxial Ge deposition/growth methods such as chemical vapor deposition (CVD), an interest in the integration of Ge materials in complementary metal oxide semiconductor (CMOS) circuit technology has developed.

In CVD of Ge on Si, due to high lattice mismatch of around 4.2% between Si and Ge, the surface tension causes the Ge lattice to develop high a treading dislocation density (TDD), which degrades device performance. Various methods to suppress the high TDD during growth have been proposed. Known methods include growing a graded buffer layer of Si<sub>x</sub>Ge<sub>1-x</sub> alloy material between the Ge and the Si, varying Ge growth parameters, and using a Ge seed layer. The latter involves the patterning and etching of an insulator (e.g. a SiO<sub>2</sub> layer) that covers the silicon substrate, exposing only small portion of the Si wafer (defined as "seed region") to the CVD growth of Ge seed-like structures. The patterning and etching of the SiO<sub>2</sub> causes epitaxial lateral overgrowth of Ge layers outside of the Ge seed area. As the threading dislocations are not parallel to the growth direction, this process forces them to glide from the Si/Ge interface to the edge of the oxide, and to annihilate them in the seed region, allowing the Ge overgrowth to be relatively free from threading dislocations. This in turn enhances the electrical properties of the device.

The use of variously known techniques as above still leaves Ge-on-Si devices with leakage (or "parasitic") currents that diminish device performance. When the seed is grown directly on the Si wafer, there is no barrier for carrier movement from the Si to the seed and vice versa, and thus there is carrier transport in the seed. In many Ge devices formed on a Si carrier wafer, the Si carrier wafer is biased to ground and a leakage of carriers can be transported through the seed into the Ge layer and can be measured as an undesired transport current.

Therefor there is a need for, and it would be advantageous to have structures and methods that minimize or completely block the leakage current and which separate electrically the Si and Ge layers in Ge-on-Si photo-devices.

**SUMMARY**

5

10

15

20

25

30

Embodiments disclosed herein teach structures that block leakage currents at the Ge/Si seed interface and separate electrically the Ge layer for the Si substrate (wafer), and methods for their formation and use. In an embodiment, the Si substrate is doped locally prior to Ge epitaxial layer growth (in an area to be referred to henceforth as a "locally doped Si region"). The local doping is of opposite type to that of the Si substrate as well as to that of the Ge seed. For example, if the Si substrate and the Ge seed are N doped, then the locally doped Si region is P doped. For example, if the Si substrate and the Ge seed are P doped, then the locally doped Si region is N doped. The doping in the Ge seed and the intermediate layer may be uniform or non-uniform (varying). The structure formed locally (in the Ge seed area) is thus similar to that of a bipolar junction transistor (BJT) with two "back-to-back" (or "head-to-head") diodes. That is, this "local" structure in the Ge seed area includes a PN (or NP) junction connected to a NP (or PN) junction in series. When a voltage is applied between the seed layer and the substrate (and through the locally doped Si region), it reduces the barrier of one junction but increases the barrier of the other junction, resulting in current blocking. Consequently, the undesired leakage current can be reduced, especially when the Ge epitaxial layer is designed to be part of an optoelectronic component such as a photodiode (PD), in which the leakage current is a "dark" current that needs to be reduced as much as possible. The advantage of this structure and its method of use is in the reduced sensitivity of the dark current on voltage polarity, where there is always one junction in

reverse bias mode, in contrast with a single standard PN junction where the behavior of the junction is less controlled and where the energy barrier depends on the voltage polarity.

In exemplary embodiments, there are provided semiconductor structures comprising: a Si substrate, a Ge seed layer and a Ge epitaxial layer separated by respective interfaces that share a common plane normal, wherein the Si substrate and the Ge seed layer have a same first doping type with a first doping level; and a locally doped region formed in the Si layer adjacent to the Ge seed layer and having a second doping type with a second doping level, wherein the locally doped region is designed to reduce leakage currents between the Si substrate and the Ge epitaxial layer when an electrical bias is applied to the structure.

5

10

15

20

25

30

In exemplary embodiments, there are provided optoelectronic devices comprising: a Si substrate, a Ge seed layer and a Ge epitaxial layer separated by respective interfaces that share a common plane normal, wherein the Si substrate and the Ge seed layer have a same first doping type with a first doping level; and a locally doped region formed in the Si layer adjacent to the Ge seed layer and having a second doping type with a second doping level, wherein the locally doped region is designed to reduce leakage currents between the Si substrate and the Ge epitaxial layer when an electrical bias is applied to the structure; and biasing means for applying the electrical bias between the Si substrate and the Ge epitaxial layer.

In exemplary embodiments, there are provided methods comprising: forming a structure comprising a Si substrate, a Ge seed layer and a Ge epitaxial layer separated by respective interfaces that share a common plane normal, wherein the Si substrate and the Ge seed layer have a same first doping type with a first doping level; and a locally doped region formed in the Si layer adjacent to the Ge seed layer and having a second doping type with a second doping level, wherein the locally doped region is designed to reduce leakage currents between the Si substrate and the Ge epitaxial layer when an electrical bias is applied to the structure.

In some embodiments, a method further comprises forming biasing means for applying the electrical bias between the Si substrate and the Ge epitaxial layer.

In some of the structures and optoelectronic devices, the first doping type is n-type and wherein the second doping type is p-type.

In some of the structures and optoelectronic devices, the first doping type is p-type and wherein the second doping type is n-type.

In some of the structures and optoelectronic devices, the Ge epitaxial layer has a doping type that is the same as the first doping type.

In some of the structures and optoelectronic devices, the Ge epitaxial layer has intrinsic doping.

In some of the structures and optoelectronic devices, the second doping level is higher than the first doping level.

In general, optoelectronic devices disclosed herein are useful for light detection in the SWIR range.

### BRIEF DESCRIPTION OF THE DRAWINGS

Non-limiting examples of embodiments disclosed herein are described below with reference to figures attached hereto that are listed following this paragraph. The drawings and descriptions are meant to illuminate and clarify embodiments disclosed herein, and should not be considered limiting in any way. Like elements in different drawings may be indicated by like numerals. Elements in the drawings are not necessarily drawn to scale. In the drawings:

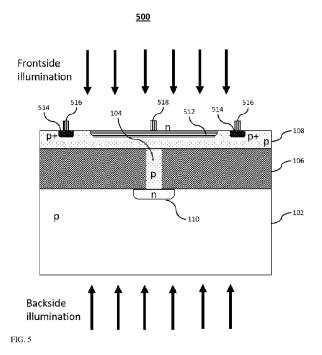

- FIG. 1A illustrates schematically in a side view an embodiment of a Ge/locally doped Si/Si PNP structure disclosed herein;

- FIG. 1B illustrates schematically in a side view an embodiment of a Ge/locally doped Si/Si

NPN structure disclosed herein;

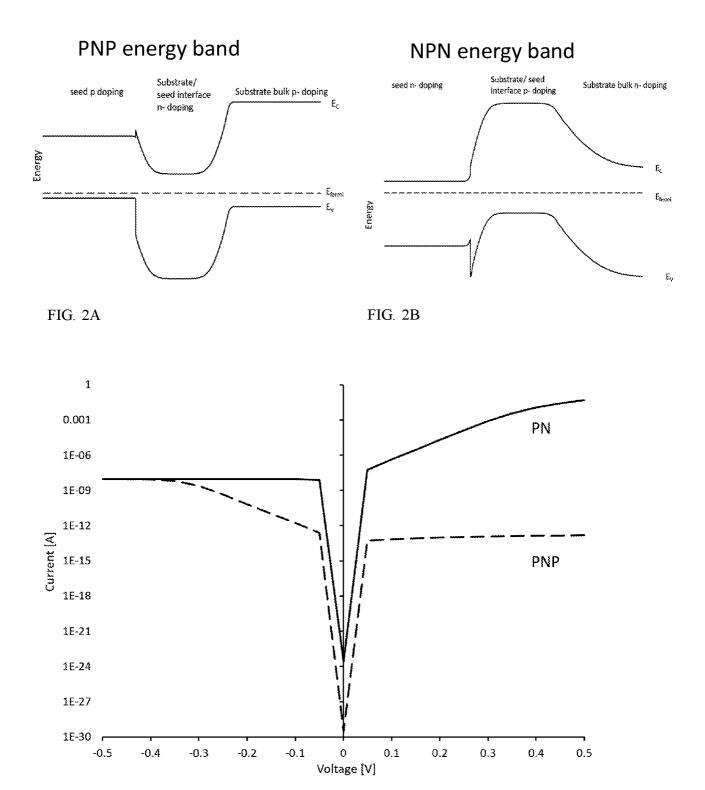

- FIG. 2A illustrates schematically an energy band profile of the structure in FIG. 1A;

- FIG. 2B illustrates schematically an energy band profile of the structure in FIG. 1B;

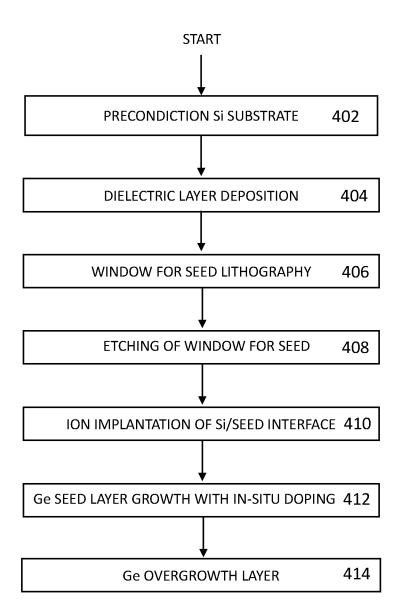

- FIG. 3 illustrates schematically a typical current transport in NPN and PNP structure disclosed herein;

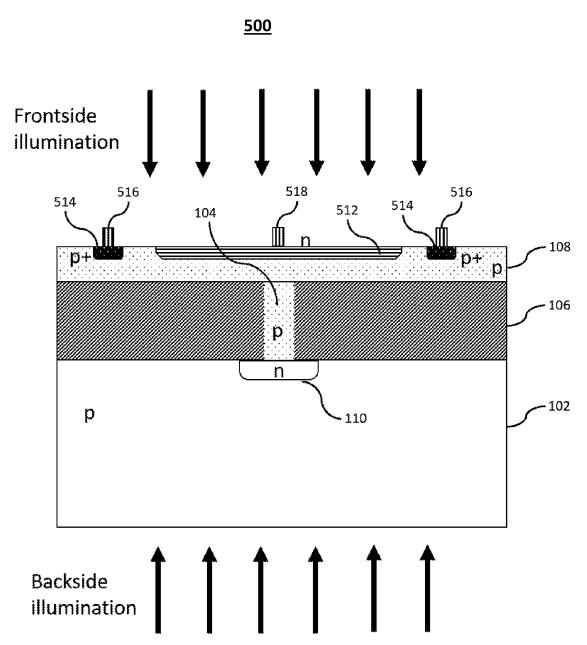

- FIG. 4 shows a flow diagram of an exemplary and non-limiting embodiment of a process for fabricating a structure as in FIGS. 1A and 1B;

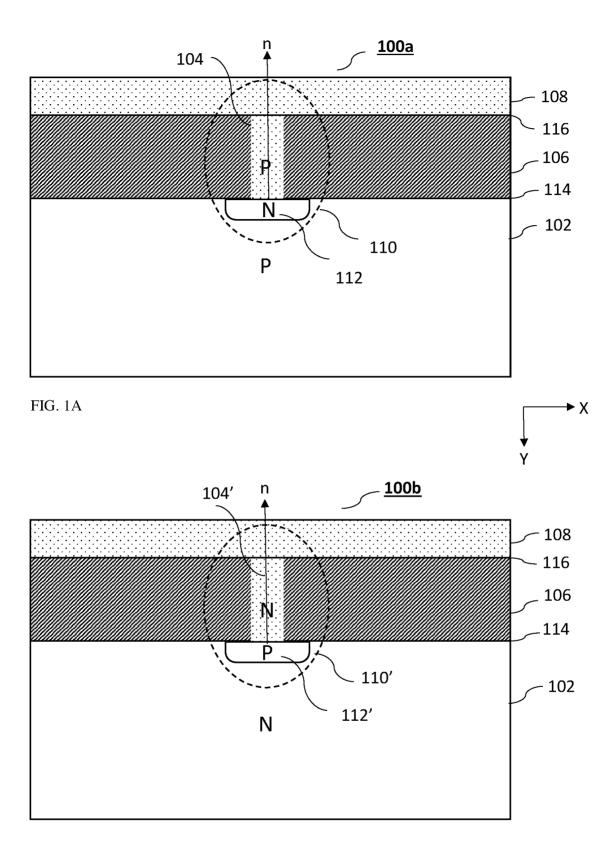

- FIG. 5 shows an exemplary photodiode fabricated in a structure as in FIG. 1A.

25

5

10

## **DETAILED DESCRIPTION**

5

10

15

20

25

30

Embodiments disclosed herein teach inventive leakage-reducing structures, methods of fabricating such structures in the Ge-Si material system, and photo-devices based on such structures. The structures include certain doping profiles through a Ge seed layer and the underlying Si substrate. In general, this simple, highly efficient and low-cost method can be used when using a Ge seed and lateral overgrowth epitaxy on a Si substrate.

Referring now to the drawings, FIG. 1A illustrates schematically in a side view an embodiment of a Ge/locally doped Si/Si substrate structure numbered 100a disclosed herein. FIG. 1B illustrates schematically in a side view an embodiment of a Ge/locally doped Si/Si substrate structure numbered 100b disclosed herein. Structure 100a includes a Si substrate (or "layer") 102, a Ge seed layer 104 grown in an opening (e.g. etched region) of an insulator (dielectric) layer (e.g. SiO<sub>2</sub>) 106 and a Ge epitaxial layer 108 laterally overgrown from the seed over the insulator layer to form a Ge-on-Si structure. Layer 102 is separated from layer 104 (and insulator 106) by an interface 114 and layer 104 (and insulator 106) is separated from layer 108 by an interface 116. Interfaces 114 and 116 share a plane normal "n". Structure 100a further includes locally, in a region marked by an oval 110, a locally n-doped doped Si region 112. In a vertical (Y according to the exemplary coordinate system) direction, oval 110 marks a structure comprising Ge seed 104 (and epitaxial layer 108) doped p-type, locally n-type doped Si region 112 and Si substrate 102 doped p-type. Therefore, the structure marked by oval 112 may be referred to as PNP structure 112.

Similarly, structure 100b has in a region marked by an oval 110' (also referred to as "locally doped region") and in a vertical (Y) direction, a NPN structure comprising Ge seed 104 (and epitaxial layer 108) doped n-type, a locally Si region 112' doped p-type and Si substrate 102 doped n-type. Therefore, the structure marked by oval 112' may be referred to as NPN structure 112'.

PNP structure **112** may be obtained for example as follows: starting with a p-type Si substrate **102**, an intrinsic or doped Ge layer **108** is overgrown over insulator **106** from an p-type Ge seed layer **104**. The p-type doping of the seed is formed using, for example, an in-situ doping method. The seed pattern is defined using standard lithography and etching in the dielectric layer. Prior to the Ge layer growth, locally n-type doped region **110** is formed in Si substrate **102** at the

interface between the Ge seed and the Si wafer, for example, by ion implantation or diffusion. Given the ion implantation or diffusion conditions, the resulting doping profile of region **112** is known. An exemplary profile can be seen in FIG. 2A.

NPN structure 112' may be similarly obtained for example as follows: starting with a n-type Si substrate 102, an intrinsic or doped Ge layer 108 is overgrown over insulator 106 from a n-type Ge seed layer 104. The n-type doping of the seed is formed using, for example, an in-situ doping method. The seed pattern is defined using standard lithography and etching in the dielectric layer. Prior to the Ge layer growth, locally p-type doped region 112' is formed in Si substrate 102 at the interface between the Ge seed and the Si wafer, for example, by ion implantation or diffusion. Given the ion implantation or diffusion conditions, the resulting doping profile of region 112' is known. An exemplary profile can be seen in FIG. 2B.

5

10

15

20

25

30

The doping levels (dopant concentrations) of the layers in PNP structure **112** or NPN structure **112'** may vary as follows: the doping (P or N) of the Si substrate may vary between  $1x10^{15}$  cm<sup>-3</sup> and  $1x10^{17}$  cm<sup>-3</sup>, the doping (N or P) of locally doped region **112** or **112'** may vary between  $1x10^{17}$  cm<sup>-3</sup> and  $1x10^{19}$  cm<sup>-3</sup> and the doping (P or N) of the Ge seed may vary between  $1x10^{16}$  cm<sup>-3</sup> and  $1x10^{18}$  cm<sup>-3</sup>. In a non-limiting example, the locally doped region thickness may be about 100 nm.

In a particular and non-limiting example of a PNP structure **112**, Si substrate **102** may be p-type doped with boron to a level of about  $1x10^{15}$  cm<sup>-3</sup>, locally doped Si region **112** may be n-type doped with phosphor or arsenic to a level of about  $1x10^{18}$  cm<sup>-3</sup> and Ge seed **104** may be p-type doped with boron, gallium or aluminum to about a level of  $1x10^{17}$  cm<sup>-3</sup>.

In a particular and non-limiting example of a NPN structure 112, Si substrate 102 may be n-type doped with arsenic or phosphor to a level of about  $1x10^{15}$  cm<sup>-3</sup>, locally doped Si region 112 may be p-type doped with boron, gallium or aluminum to a level of about  $1x10^{18}$  cm<sup>-3</sup> and Ge seed 104 may be n-type doped with arsenic or phosphor to about a level of  $1x10^{17}$  cm<sup>-3</sup>.

FIG. 2A illustrates schematically an energy band profile of the PNP structure in FIG. 1A, and FIG. 2B illustrates schematically an energy band profile of the NPN structure in FIG. 1B. The energy bands are similar to those of heterojunction BJTs, except in this case a BJT structure is formed only locally in the Ge seed region and the Si substrate. The term "substrate/seed interface" in these figures is equivalent to the "locally doped region" mentioned above and below. The resulting band structure is instrumental for reducing the leakage current through the seed layer into

the Si substrate by forming two opposite PN junctions. Specifically, there will always be an energy barrier for the carriers such that the carriers cannot be transported from the Ge seed to the silicon substrate and vice versa. This is true for zero bias between the silicon substrate and the Ge seedas well as for a between bias the silicon and the Ge seed. The voltage drops on such a structure always have one junction in reverse bias mode, a feature used to block unnecessary leakage current.

5

10

15

20

25

30

FIG. 3 illustrates simulated transport current through an example of a PNP structure like structure 100a. The structure is doped as follows: The Si substrate is p-type doped to a level of  $1 \times 10^{15} \text{cm}^{-3}$ , the locally doped Si region is n-type doped to a level of  $1 \times 10^{18} \text{cm}^{-3}$ , and the Ge seed is p-type doped to a level of  $1 \times 10^{17} \text{cm}^{-3}$ . The obtained current is compared to that of a Si/Ge PN junction consisting of p-type Si (doping of  $1 \times 10^{15} \text{cm}^{-3}$ ) and n-type Ge region having doping of  $1 \times 10^{18} \text{cm}^{-3}$ . The simulated current through the PNP device shows reduced leakage current. For example, for a positive voltage (bias) of 0.1V, there is reduction of almost 7 orders of magnitude in the leakage current. Bias" refers to the difference in electric potential between the Ge and the Si substrate. For a positive 0.5V bias, the reduction is even higher, about 10 orders of magnitude. For a negative bias of -0.1V there is improvement of about 3 orders of magnitude. For a higher negative bias of about -0.3V the improvement becomes negligible. "

Moreover, if the seed (104) and the substrate (102) have the same level of doping without the additional layer (i.e. without the locally doped region 112 or 112'), e.g. pp or nn doping, the leakage current through the seed is expected to be higher and will most likely reduce the device performance.

FIG. 4 shows a flow diagram of an exemplary and non-limiting embodiment of a process (method) for fabricating a structure such as **100a** or **100b** with a desired local PNP or NPN doping profile. The process starts at step **402** with a preconditioned doped Si substrate (also referred to as "layer") serving as the carrier wafer for the epitaxy growth process. The preconditioning can include for example cleaning or adding a protection layer. A dielectric (insulator) layer, for example SiO<sub>2</sub>, is deposited on the Si wafer in step **404**. A standard lithography process defines a window in the dielectric layer in step **406** and the window is etched into the dielectric layer all the way through the dielectric layer to reach the Si wafer in step **408**. An ion implantation process followed by dopant activation (e.g. using rapid thermal annealing or diffusion) is used to form the locally doped region **112** or **112**' in the silicon in step **410**. The doping type is opposite to the

doping of the Si wafer. For example, in a PNP structure, starting with a Si wafer doped to a level of  $1x10^{15}$ cm<sup>-3</sup> with boron, the n-type locally doped region may be formed by implantation of phosphor at 30 KV and dose of  $2x10^{13}$  ions/cm<sup>2</sup>, followed by diffusion of about 10 minutes at  $1020^{0}$  C. Subsequently, in step **412**, the Ge seed is grown in the window with in-situ doping identical to that of the Si wafer. The in-situ doping provides a uniformly doped seed layer. Finally, an intrinsic or doped Ge epitaxial layer **108** is overgrown over the insulator from the seed in step **414**.

5

10

15

20

25

FIG. 5 shows an exemplary photodiode numbered **500** fabricated in a structure of Ge grown on a Si substrate by the seed layer technique. The structure is similar to that in FIG. 1A, with the addition of a n-doped region **512**, p+ doped regions **514** and electrical contacts **516** and **518**, which form exemplary biasing means for the PD. Light can arrive in both back-side illumination or front-side illumination, as shown. In general, the direction of the light entering the PD is substantially parallel to the Y axis, up to an acceptance angle of optics (not shown) coupled to the PD.

Photodiodes like PD **500** can be formed as (arranged in) an array (not shown), and be integrated with a standard read out circuitry (ROIC) to form a CMOS type imager.

Unless otherwise stated, the use of the expression "and/or" between the last two members of a list of options for selection indicates that a selection of one or more of the listed options is appropriate and may be made.

It should be understood that where the claims or specification refer to "a" or "an" element, such reference is not to be construed as there being only one of that element.

While this disclosure has been described in terms of certain embodiments and generally associated methods, alterations and permutations of the embodiments and methods will be apparent to those skilled in the art. The disclosure is to be understood as not limited by the specific embodiments described herein, but only by the scope of the appended claims.

## WHAT IS CLAIMED IS:

- 1. A semiconductor structure, comprising:

- a) a silicon (Si) substrate, a Germanium (Ge) seed layer and a Ge epitaxial layer separated by respective interfaces that share a common plane normal, wherein the Si substrate and the Ge seed layer have a same first doping type with a first doping level; and

- b) a locally doped region formed in the Si layer adjacent to the Ge seed layer and having a second doping type with a second doping level, wherein the locally doped region is designed to reduce leakage currents between the Si substrate and the Ge epitaxial layer when an electrical bias is applied to the structure.

- 2. The semiconductor structure of claim 1, wherein the first doping type is n-type and wherein the second doping type is p-type.

- 3. The semiconductor structure of claim 1, wherein the first doping type is p-type and wherein the second doping type is n-type.

- 4. The semiconductor structure of claim 1, wherein the Ge epitaxial layer has a doping type that is the same as the first doping type.

- 5. The semiconductor structure of claim 1, wherein the Ge epitaxial layer has intrinsic doping.

- 6. The semiconductor structure of claim 1, wherein the second doping level is higher than the first doping level.

- 7. An optoelectronic device, comprising:

- a) a silicon (Si) substrate, a Germanium (Ge) seed layer and a Ge epitaxial layer separated by respective interfaces that share a common plane normal, wherein the Si substrate and the Ge seed layer have a same first doping type with a first doping level;

- b) a locally doped region formed in the Si layer adjacent to the Ge seed layer and having a second doping type with a second doping level, wherein the locally doped region is designed to

reduce leakage currents between the Si substrate and the Ge epitaxial layer when an electrical bias is applied to the structure; and

- c) biasing means for applying the electrical bias between the Si substrate and the Ge epitaxial layer.

- 8. The optoelectronic device of claim 7, wherein the first doping type is n-type and wherein the second doping type is p-type.

- 9. The optoelectronic device of claim 7, wherein the first doping type is p-type and wherein the second doping type is n-type.

- 10. The optoelectronic device of claim 7, wherein the Ge epitaxial layer has a doping type that is the same as the first doping type.

- 11. The optoelectronic device of claim 7, wherein the Ge epitaxial layer has intrinsic doping.

- 12. The optoelectronic device of claim 7, wherein the second doping level is higher than the first doping level.

- 13. A method, comprising: forming a structure a silicon (Si) substrate, a Germanium (Ge) seed layer and a Ge epitaxial layer separated by respective interfaces that share a common plane normal, wherein the Si substrate and the Ge seed layer have a same first doping type with a first doping level, and a locally doped region formed in the Si layer adjacent to the Ge seed layer and having a second doping type with a second doping level, wherein the locally doped region is designed to reduce leakage currents between the Si substrate and the Ge epitaxial layer when an electrical bias is applied to the structure.

- 14. The method of claim 13, further comprising forming biasing means for applying the electrical bias between the Si substrate and the Ge epitaxial layer.

15. The method of claim 13, wherein the first doping type is n-type and wherein the second doping type is p-type.

- 16. The method of claim 13, wherein the first doping type is p-type and wherein the second doping type is n-type.

- 17. The method of claim 13, wherein the Ge epitaxial layer has a doping type that is the same as the first doping type.

- 18. The method of claim 13, wherein the Ge epitaxial layer has intrinsic doping.

- 19. The method of claim 13, wherein the second doping level is higher than the first doping level.

FIG. 1B

FIG. 3

FIG. 4

FIG. 5

#### INTERNATIONAL SEARCH REPORT

International application No.

PCT/IB19/53661

| A. CLASSIFICATION OF S | SUBJECT MATTER |

|------------------------|----------------|

|------------------------|----------------|

IPC - H01L 21/02, 21/20, 21/22, 21/74, 21/761, 29/16, 29/167 (2019.01)

CPC - H01L 21/02365, 21/02381, 21/0245, 21/02518, 21/02532, 21/0257, 21/02576, 21/02579, 21/02645, 21/2033, 21/761, 29/0607, 29/0615, 29/0619, 29/16, 29/167, 29/6609, 29/66121

According to International Patent Classification (IPC) or to both national classification and IPC

#### B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

See Search History document

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched See Search History document

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used) See Search History document

#### C. DOCUMENTS CONSIDERED TO BE RELEVANT

Further documents are listed in the continuation of Box C.

document defining the general state of the art which is not considered to be of particular relevance

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                                                                                                                                                                                                                                     | Relevant to claim No. |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| Υ _       | (OLUBUYIDE, OO) Low pressure epitaxial growth, fabrication and characterization of Ge-on-Si photodiodes, a dissertation, Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, 30 April 2007; page 57, second paragraph; page 59, second paragraph; page 68, first paragraph; page 104, first paragraph; page 109, second paragraph; page 126, figure 4.16 | 1-19                  |

| Y         | US 7,361,528 B2 (LEE, JJ et al.) 22 April 2008; column 1, lines 30-31; column 3, lines 2-11, 25-27                                                                                                                                                                                                                                                                                                     | 1-19                  |

| Y         | US 9,799,756 B1 (INTERNATIONAL BUSINESS MACHINES CORPORATION) 24 October 2017; figure 4; column 1, lines 6-9, 14-15; column 3, lines 40-41; column 6, lines 49-53                                                                                                                                                                                                                                      | 2, 8, 15              |

| Y _       | EP 1,116,269 B1 (DROBNY, VF et al.) 31 December 2008; paragraphs [0003], [0007], [0041]                                                                                                                                                                                                                                                                                                                | 6, 12, 19             |

|           |                                                                                                                                                                                                                                                                                                                                                                                                        |                       |

| ļ         |                                                                                                                                                                                                                                                                                                                                                                                                        |                       |

|           |                                                                                                                                                                                                                                                                                                                                                                                                        |                       |

|           |                                                                                                                                                                                                                                                                                                                                                                                                        |                       |

|           |                                                                                                                                                                                                                                                                                                                                                                                                        |                       |

|           |                                                                                                                                                                                                                                                                                                                                                                                                        |                       |

#### document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step "D" document cited by the applicant in the international application "X" earlier application or patent but published on or after the international filing date "E" when the document is taken alone document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) document referring to an oral disclosure, use, exhibition or other means document published prior to the international filing date but later than "&" document member of the same patent family the priority date claimed Date of mailing of the international search report Date of the actual completion of the international search 20 August 2019 (20.08.2019) 16 SEP 2019

"T"

P.O. Box 1450, Alexandria, Virginia 22313-1450 Facsimile No. 571-273-8300

Mail Stop PCT, Attn: ISA/US, Commissioner for Patents

Special categories of cited documents:

Authorized officer

Shane Thomas

later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

Telephone No. PCT Helpdesk: 571-272-4300

See patent family annex.

Name and mailing address of the ISA/US