#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

## (19) World Intellectual Property Organization

International Bureau

(10) International Publication Number WO 2014/134471 A1

(43) International Publication Date 4 September 2014 (04.09.2014)

(51) International Patent Classification: *G06F 3/00* (2006.01)

(21) International Application Number:

PCT/US2014/019462

(22) International Filing Date:

28 February 2014 (28.02.2014)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

61/770,339 28 February 2013 (28.02.2013)

\*\*\*

- (71) Applicant: E3 EMBEDDED SYSTEMS, LLC [US/US]; 2717 Wellington Drive, Augusta, Georgia 30909 (US).

- (72) Inventor: HUFFMAN, Russell Kevin; 2709 Wellington Drive, Augusta, Georgia 30909 (US).

- (74) Agent: SAWRIE, David; Baker Donelson, 211 Commerce Street, Nashville, Tennessee 37201 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN, HR, HU, ID, IL, IN, IR, IS, JP, KE, KG, KN, KP, KR, KZ, LA, LC, LK, LR, LS, LT, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

[Continued on next page]

#### (54) Title: METHOD AND APPARATUS FOR THE PROCESSOR INDEPENDENT EMBEDDED PLATFORM

**FIG. 10**

(57) Abstract: A method comprises identifying resource needs of a plurality of peripherals and resource requirements of a plurality microcontrollers. The method includes comparing the resource needs of the plurality of peripherals with the resource requirements of the plurality of microcontrollers to identify generic resources common to the plurality of microcontrollers, wherein a first microcontroller and a second microcontroller of the plurality of microcontrollers provide the generic resources to processor pin locations according to differing architectures. The method includes assigning each resource of the generic resources to a fixed motherboard location, the assigning including assigning the fixed location to an interface pin. The method includes identifying for each resource of the generic resources a processor pin location of the first microcontroller providing the resource, routing the processor pin location providing the resource to the assigned interface pin, wherein the interface pin provides the resource to the fixed motherboard location.

### Published:

— with international search report (Art. 21(3))

before the expiration of the time limit for amending the claims and to be republished in the event of receipt of amendments (Rule 48.2(h))

#### METHOD AND APPARATUS FOR THE PROCESSOR INDEPENDENT EMBEDDED PLATFORM

#### CROSS REFERENCE TO RELATED APPLICATIONS

[0001] This application claims the benefit of United States Application No. 61/770,339, dated February 28, 2013.

STATEMENT REGARDING FEDERALLY SPONSORED RESEARCH OR DEVELOPMENT

[0002] Not applicable.

THE NAMES OF THE PARTIES TO A JOINT RESEARCH AGREEMENT

[0003] Not applicable.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0004] So that the manner in which the present application can be better understood, certain illustrations and figures are appended hereto. It is to be noted, however, that the drawings illustrate only selected embodiments and elements of a method, apparatus, and platform for the processor independent embedded platform and are therefore not to be considered limiting in scope for the method, platform and apparatus as described herein may admit to other equally effective embodiments and applications.

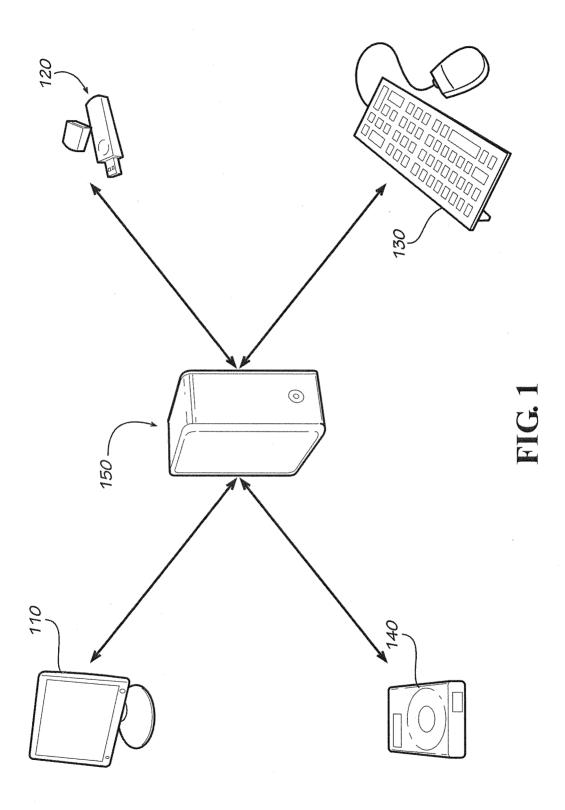

[0005] Figure 1 shows a microcomputer transferring data to and receiving data from external devices, under an embodiment.

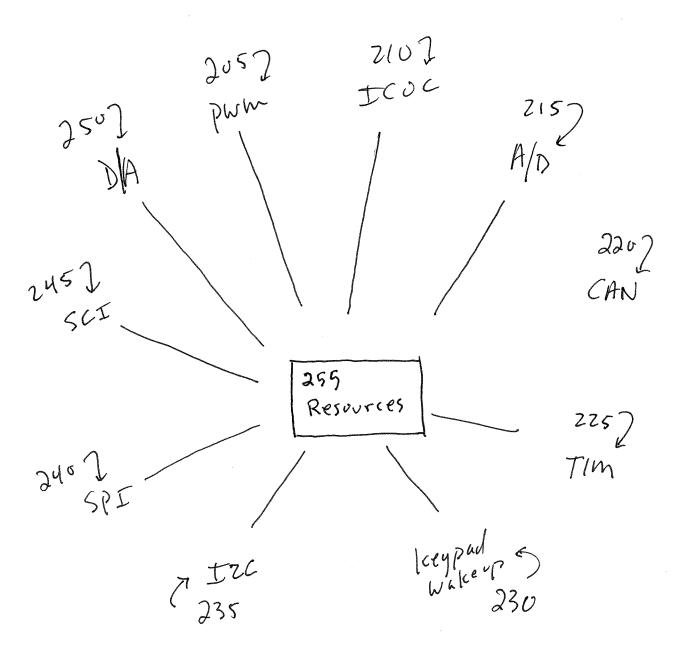

[0006] Figure 2 shows microcontroller resources, under an embodiment.

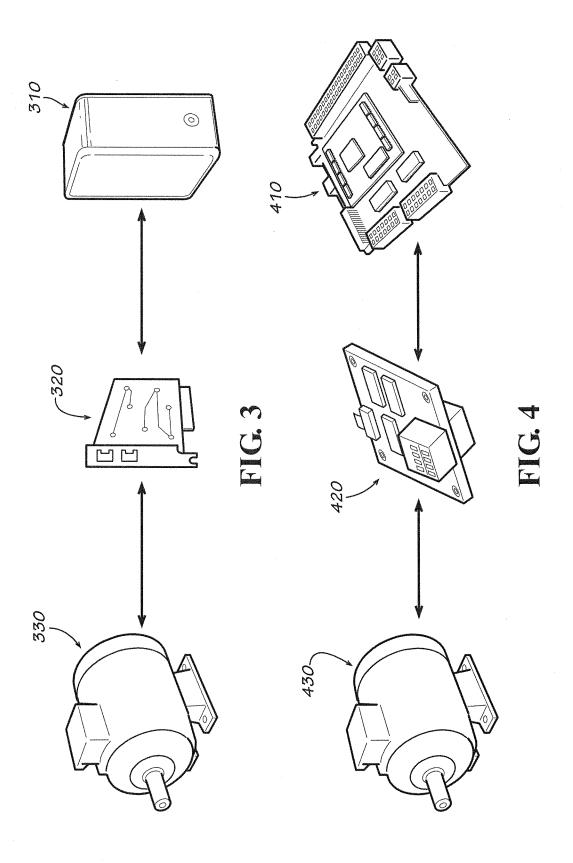

[0007] Figure 3 shows a microcomputer transferring data to and receiving data from an external device through a peripheral card, under an embodiment.

[0008] Figure 4 shows a microcontroller transferring data to and receiving data from an external device through a peripheral card, under an embodiment.

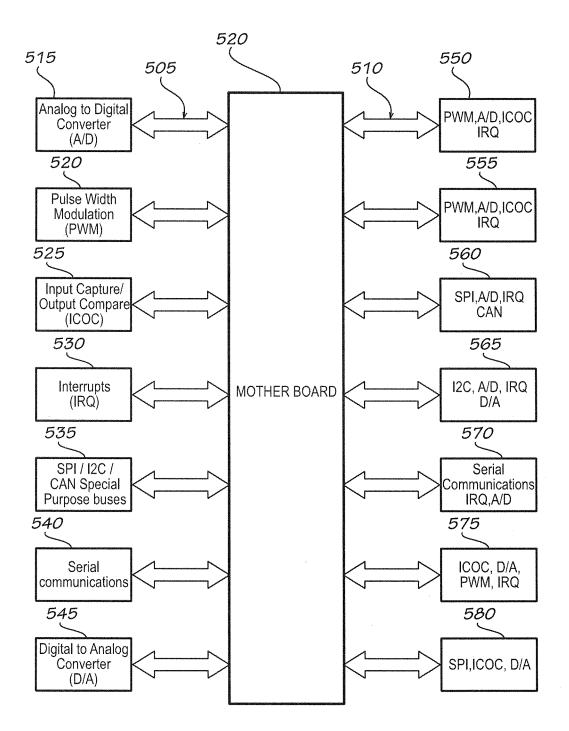

[0009] Figure 5 is a block diagram showing a microcontroller interface and a peripheral interface of a PIEP motherboard, under an embodiment.

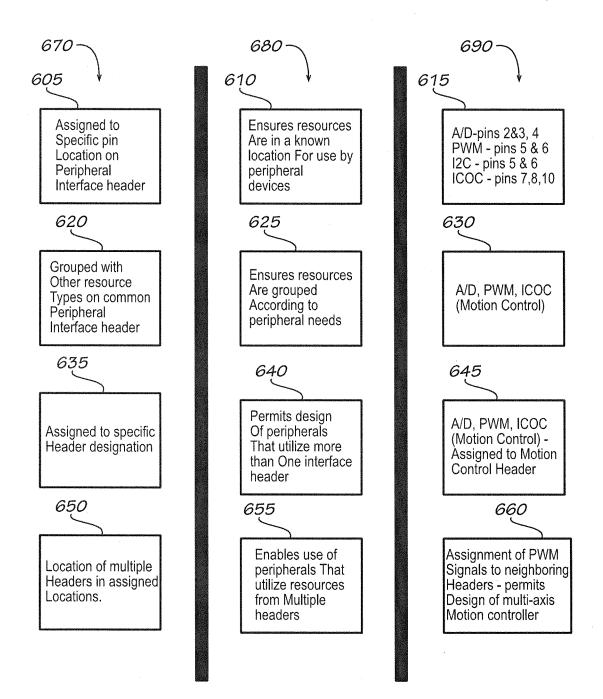

[0010] Figure 6 shows steps of a resource alignment method under an embodiment

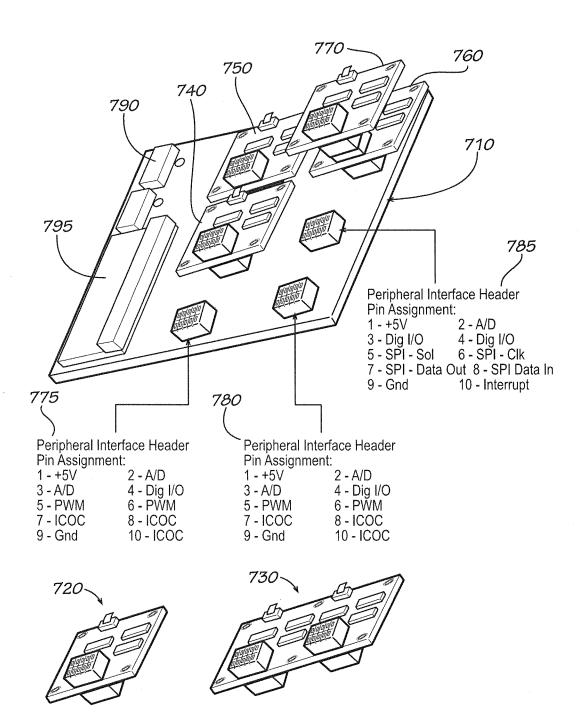

[0011] Figure 7 shows a the PIEP motherboard design, under an embodiment.

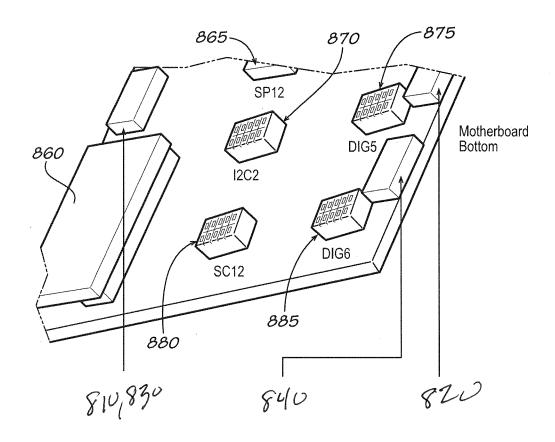

[0012] Figure 8 shows supplemental processor resources implemented on motherboard DPIP

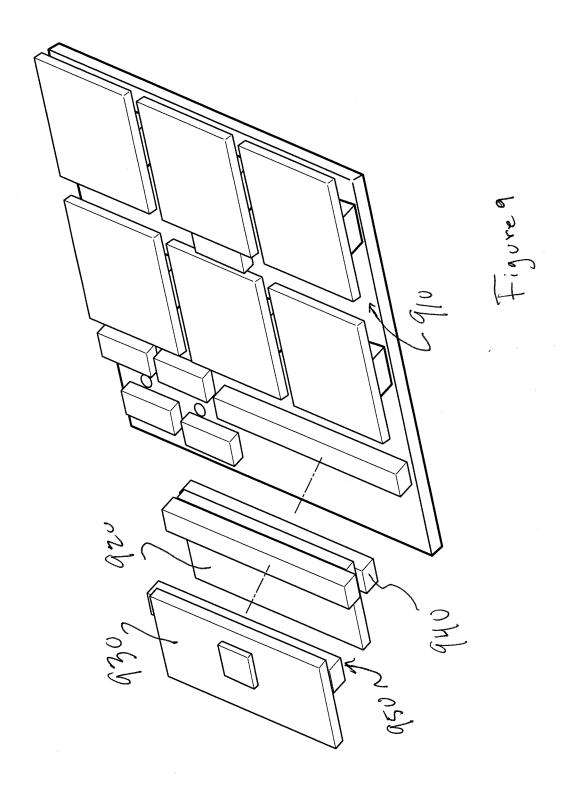

[0013] Figure 9 is an example of a remap adapter connecting between processor board and mother board, under an embodiment.

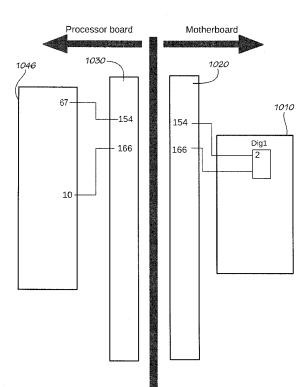

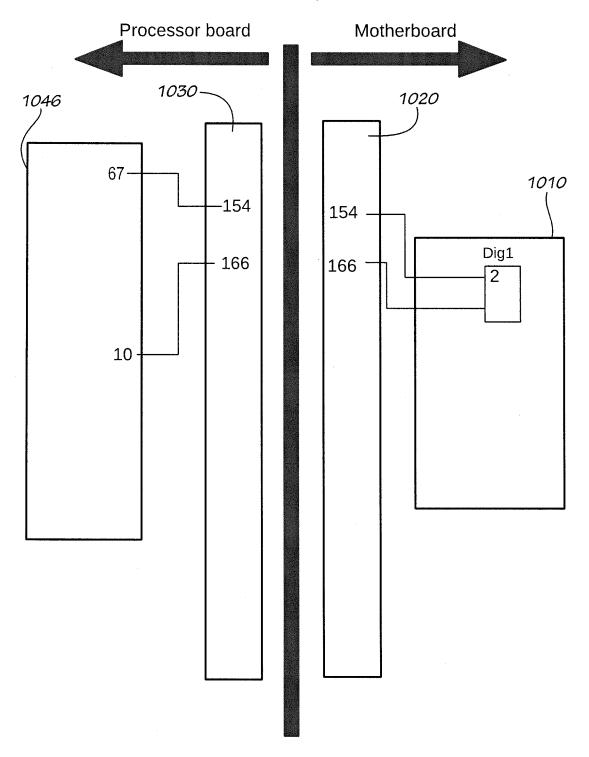

[0014] Figure 10 shows a motherboard and processor board 200 pin interface, under an embodiment, under an embodiment.

PCT/US2014/019462

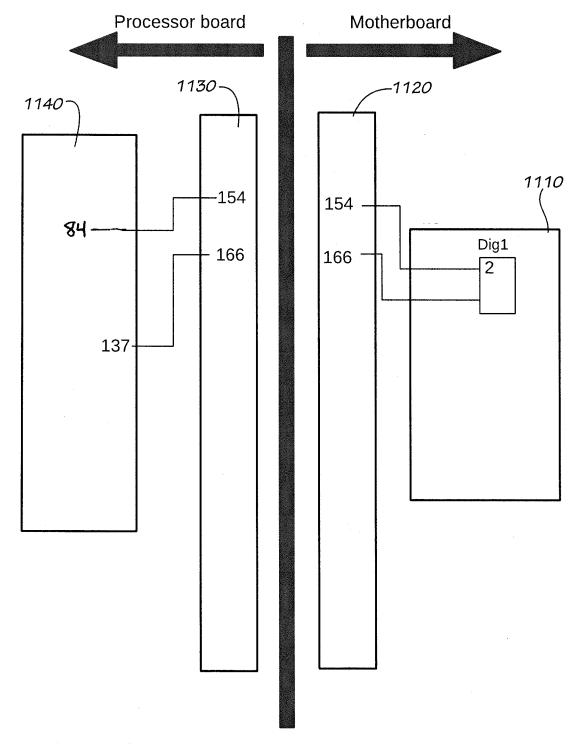

[0015] Figure 11 shows a motherboard and processor board 200 pin interface, under an embodiment, under an embodiment.

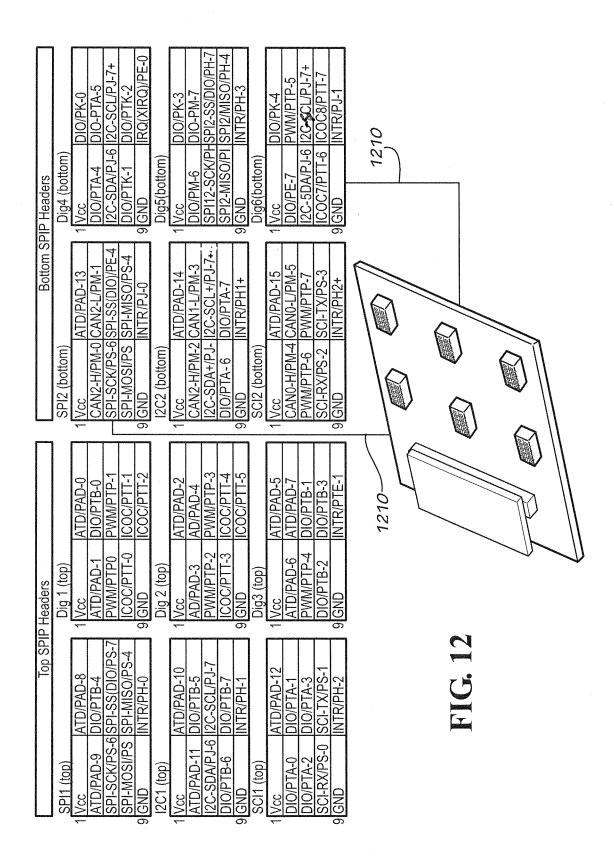

[0016] Figure 12 shows a processor map file detailing motherboard pin assignments for a specific processor, under an embodiment.

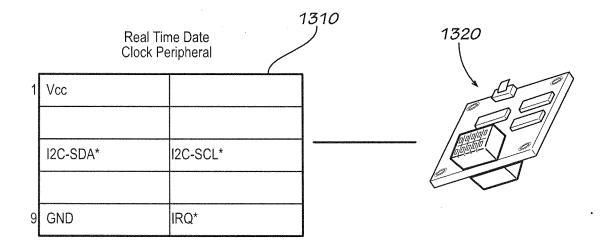

[0017] Figure 13 shows a peripheral map file showing resources needed by the peripheral, under an embodiment, under an embodiment.

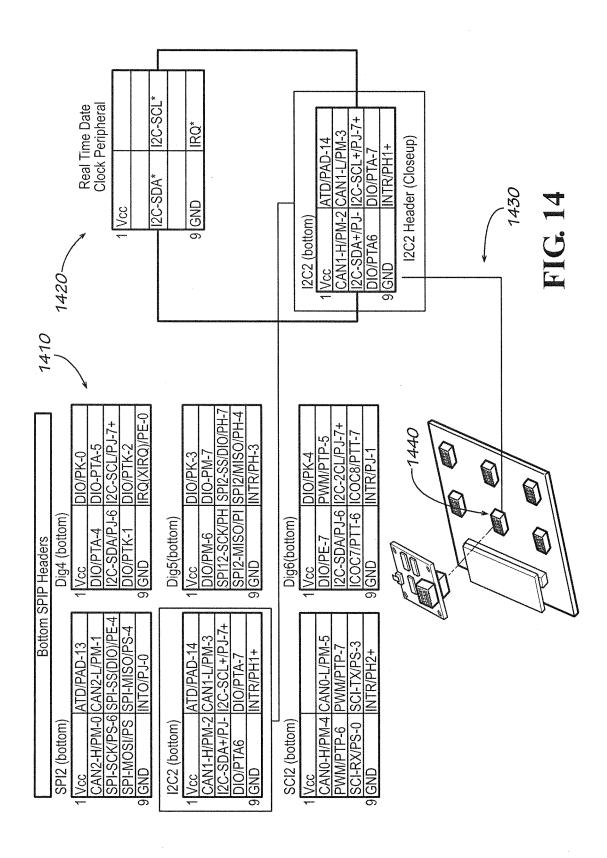

[0018] Figure 14 is an example of identifying which motherboard headers contain the resources needed by a peripheral, under an embodiment.

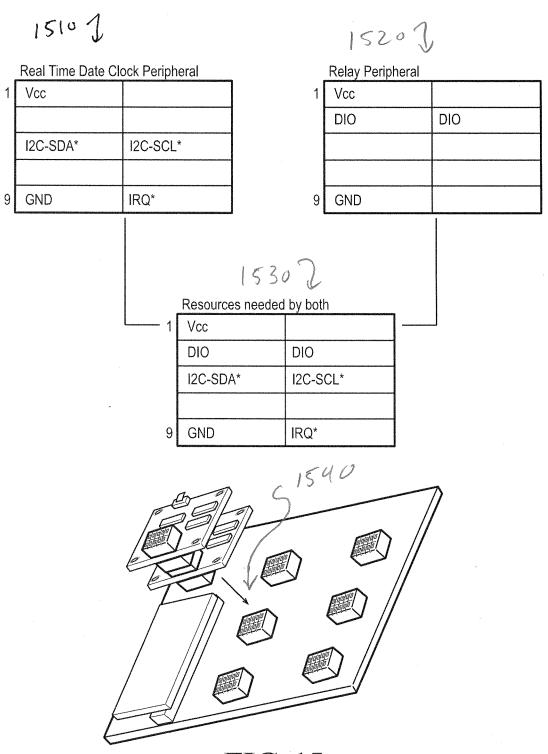

[0019] Figure 15 shows an example of identifying needed resources for and installing a stacked peripheral, under an embodiment.

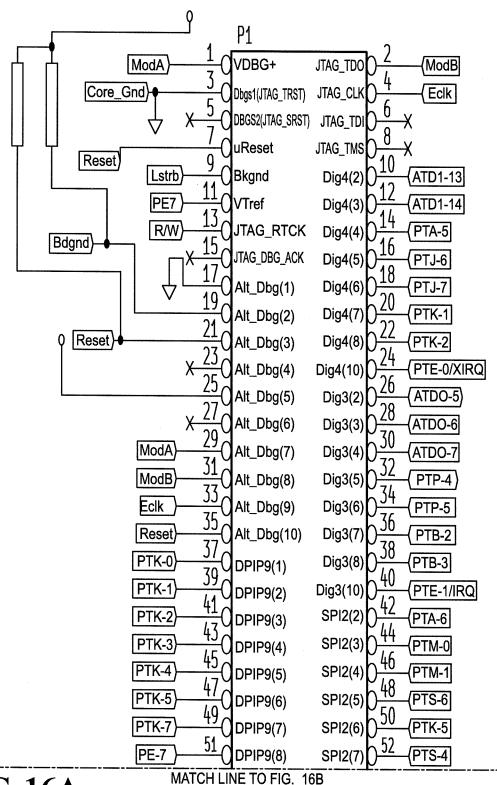

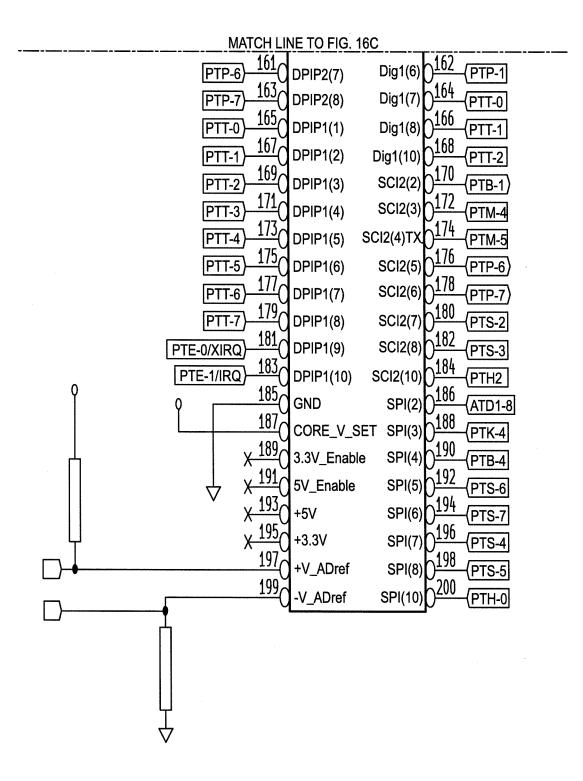

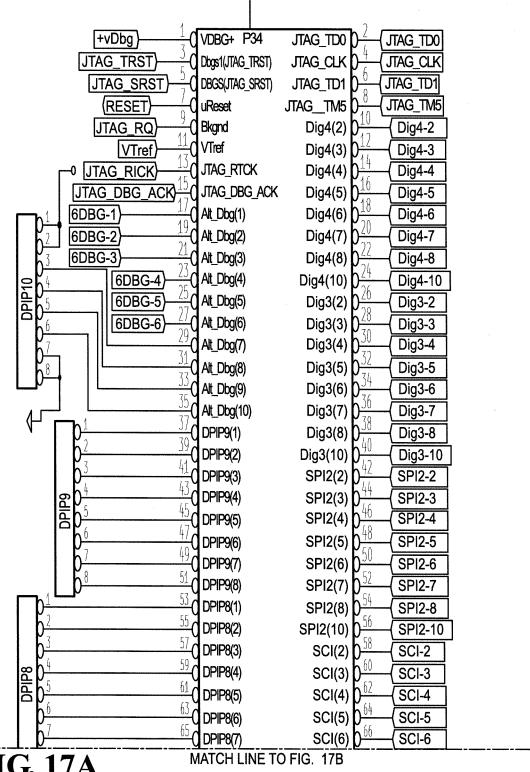

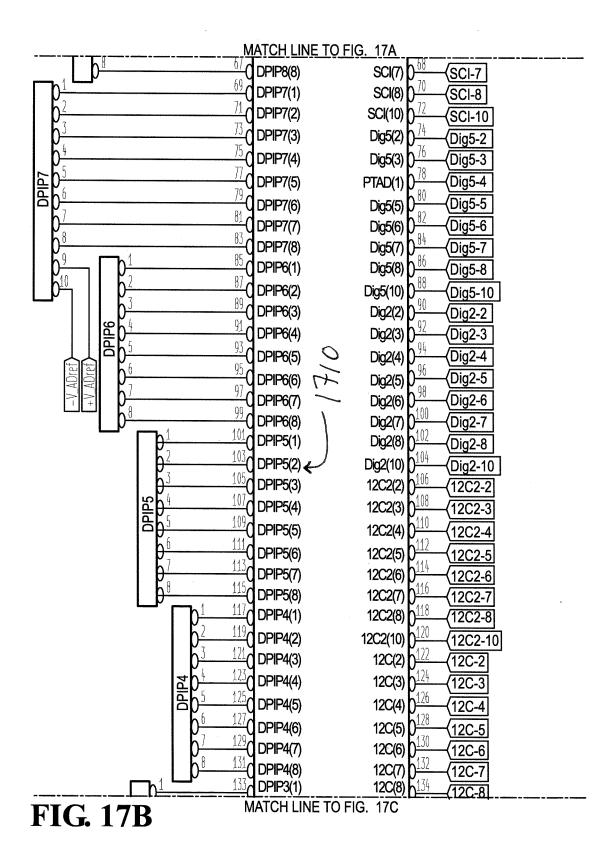

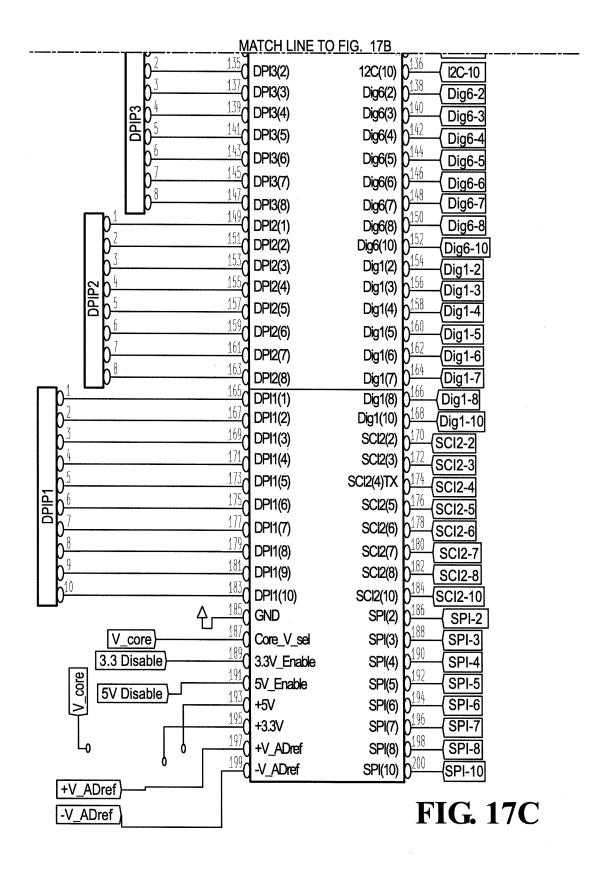

[0020] Figures 16A-16D include a 200 pin processor interface header contained within a processor circuit board module, under an embodiment.

[0021] Figures 17A-17C includes a schematic of a 200 pin processor interface header, contained within a motherboard module, under an embodiment.

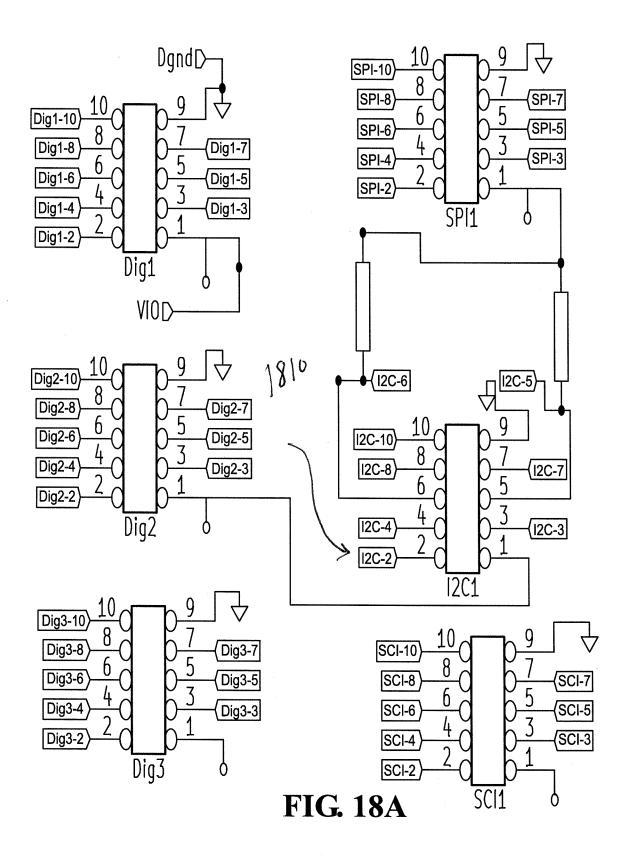

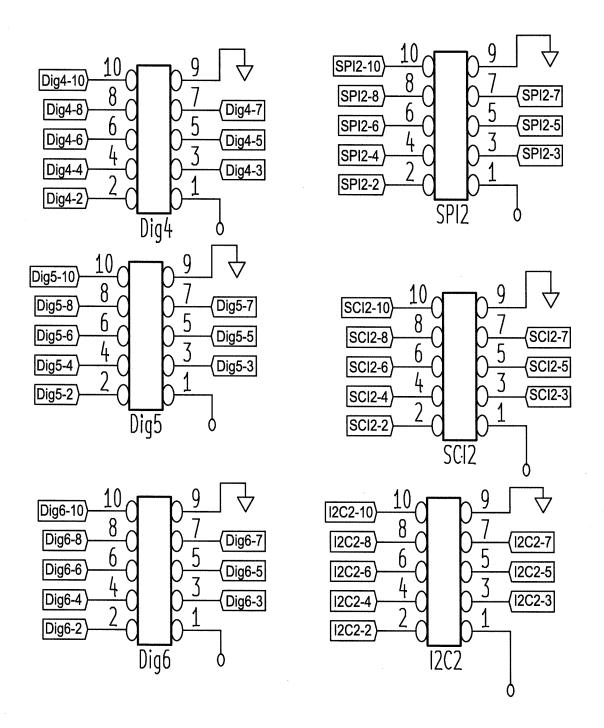

[0022] Figures 18A-18B include a schematic of SPIP header assignments, under an embodiment.

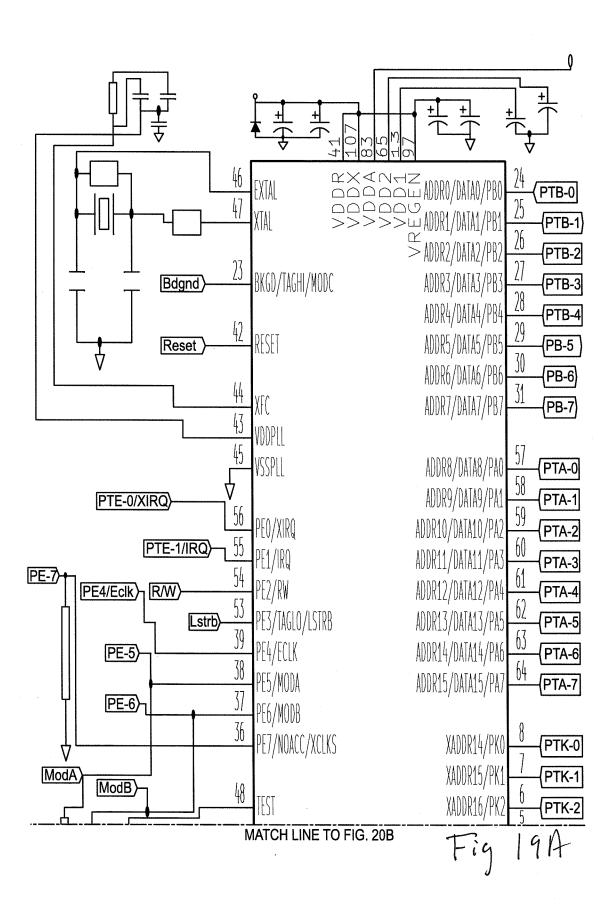

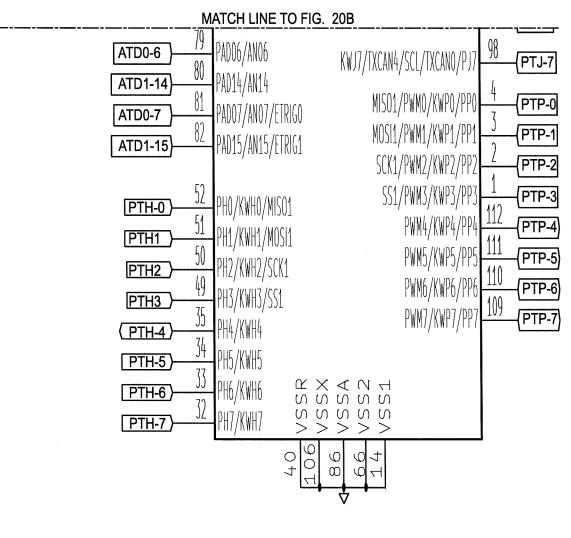

[0023] Figure 19A-C is a schematic of the MCS912 processor, under an embodiment.

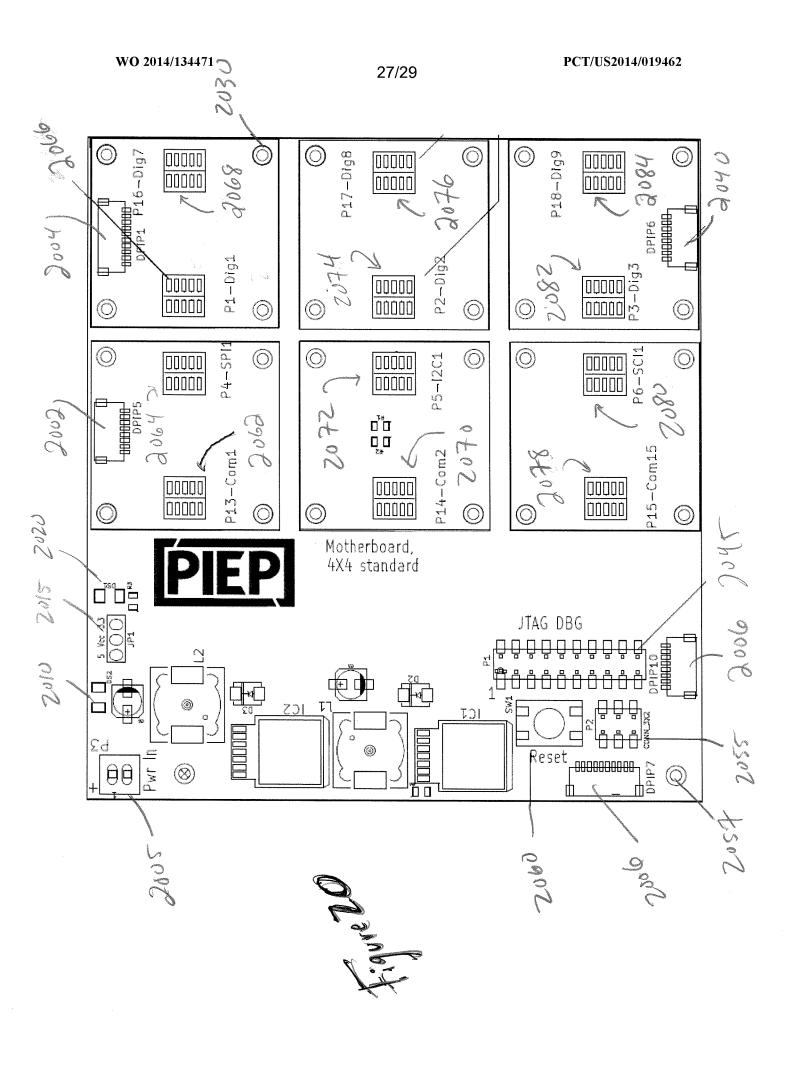

[0024] Figure 20 is a top view of a PIEP motherboard, under an embodiment.

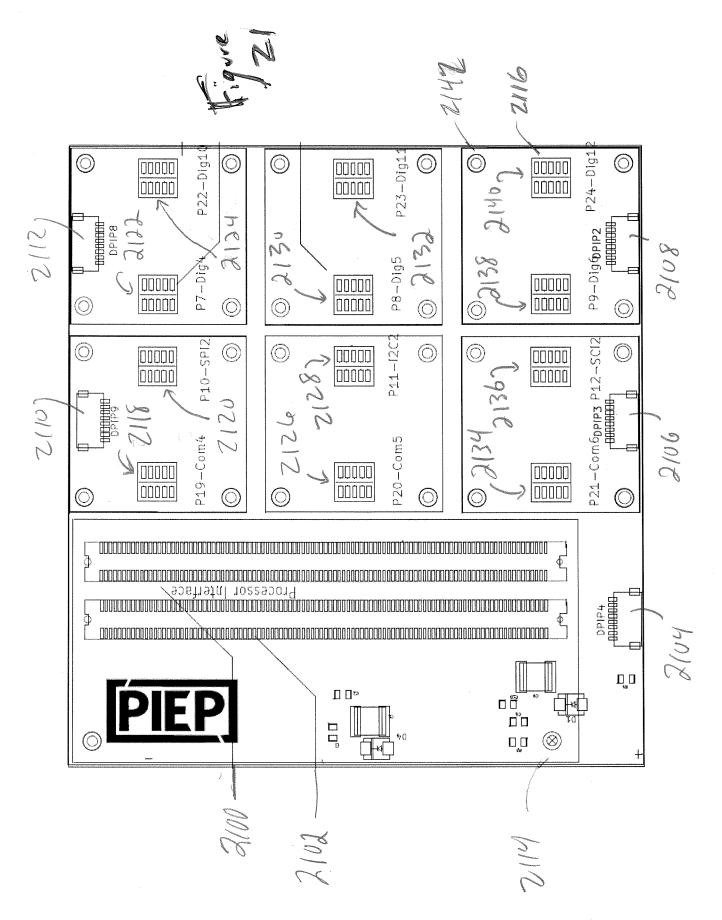

[0025] Figure 21 is a back view of a PIEP motherboard, under an embodiment

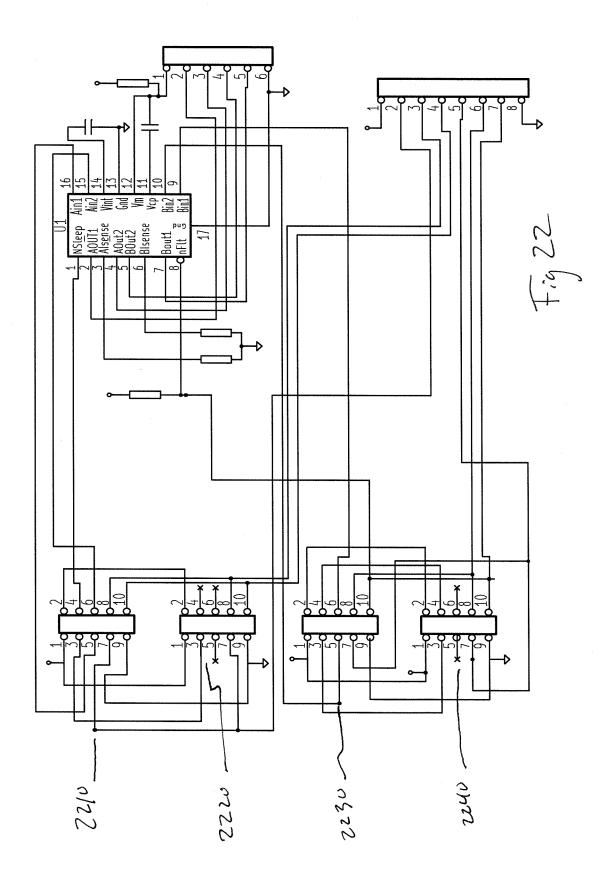

[0026] Figure 22 is a schematic of an H-Bridge peripheral, under an embodiment.

#### **DETAILED DESCRIPTION**

[0027] The Processor Independent Embedded Platform (PIEP) is under one embodiment a method and apparatus that permits a plurality of microcontroller types (processor types and architectures) to singularly interface with a plurality of peripheral devices. The PIEP was conceived with two primary objectives. The first objective was to design a system that could utilize multiple processors. This goal was established to enable the system design to maintain relevance as new microcontrollers were introduced and older processors entered into obsolescence. Secondly, a design goal was established to permit peripherals the ability to work with a multitude of processors. This second goal was established to enable a single peripheral

board the broadest possible application across a wide array of processors. From a marketing strategy, both goals are enablers of the overall marketing strategy. By allowing processors and peripherals to span the greatest market segment possible, the total sales revenue increases while per unit production costs decrease. The ability to adapt processors and peripherals to an array of motherboards of varying size and capability also contribute to the established goals. In order to explore the merits of the design, it is first necessary to fully differentiate microcontrollers from the larger class of microcomputers.

[0028] Although microcontrollers are actually a sub-class of microcomputers, the two terms are most often associated with two different types of computing devices. Microcomputers generally refer to a class of computing devices most often found in desktop computers, workstations, and servers. These computing devices are designed to process large and complex data sets (graphics data inclusive) as well as efficiently transfer data between the microcomputer and connected devices (printer, keyboard, monitor, mouse and more). In order to facilitate expected data processing needs, most microcomputers contain wide, parallel, data paths to localized memory and cache storage.

[0029] The microcomputer generally includes the following features, characteristics and/or capabilities:

[0030] -- Internal / External Peripheral interface via high speed serial buses (USB, Ethernet, SC Card reader, etc.);

[0031] -- Internal peripheral interface via high speed parallel data buses (graphics card, RAM, PIC peripheral card;

[0032] -- Integral floating point math capability;

[0033] -- Multi-level cache;

[0034] -- Wide address and data buses (64 bit, 128 bit or higher);

[0035] -- Limited, or no, special purpose control / sensor signals;

[0036] -- Operating System required: Microsoft Windows, Linux, MAC;

[0037] Microcomputers are useful as file servers, personal computers, and work stations.

Microcomputers may provide limited industrial control applications via internal peripheral cards or external devices. In contrast to the Microcomputer, a microcontroller generally includes the following features, characteristics and/or capabilities:

[0038] -- Peripheral interface via low speed specialized serial buses including CAN (automotive), SPI, I2C (local peripheral devices), I2S (audio), and USB (limited support, typically as a USB-B device).

[0039] -- Peripheral interface via specialized signal lines including PWM (proportional control for motors, heaters, etc.), ICOC (edge triggered sensor input), Timer (frequency detection, event measurement), Analog to Digital (voltage measurements), and Digital to Analog (output of analog voltage);

[0040] -- Limited integrated math capabilities;

[0041] -- No dedicated cache and limited RAM memory (programs typically stored in integral FLASH memory);

[0042] -- Narrow address / data buses (8, 16, 32 bit);

[0043] -- Operating system optional (many microcontroller implementations execute a single dedicated program).

[0044] Microcontrollers enable components of consumer electronics, robotics, industrial control systems, and automotive applications.

[0045] Microcomputers typically contain specialized capabilities, such as a floating point math processing module, to aid in data throughput. Beyond data processing, a microcomputer interfaces with its surroundings through serialized or parallel data transfer. To facilitate data transfers, a limited number of common interfaced standards have been designed (USB, SATA, Fire Wire, etc). These transfer interfaces permit a wide array of devices (printers, keyboards, mice, flash memory) to interact with the microcomputer via high speed serialized communication.

[0046] Although the microcomputer can interact with a wide array of devices, this interaction is almost exclusively in the form of data transfer. Physical manipulation of an external device is executed by specific hardware (a microcontroller) that is implemented on (or within) the connected device. For instance, a key press on a keyboard is interpreted by hardware in the keyboard. This key press is then converted to a serialized data stream that is subsequently transmitted to the host microcomputer.

[0047] Figure 1 shows one or more of a monitor 110, flash memory 120, keyboard / mouse 130, and internal hard drive 140 coupled to a microcomputer 150. The monitor may communicate with the Microcomputer through VGA, DVI, and HDMI data transfers. The flash memory and

PCT/US2014/019462

keyboard/ mouse may communicate with the Microcontroller through Serial Data Transfer via USB. The internal hard drive communicates with the Microcomputer using SATA, IDE, or SCSII serial data transfers under an embodiment. The microcomputer itself implements internal parallel and data transfers to / from RAM or graphics card.

[0048] Although most microcomputers support the installation of a limited amount of peripheral hardware, these interfaces still utilize serial or parallel data transfer as the interface mode. A very common interface example is the installation of an Ethernet (network) card in a desktop computer. This card will most likely connect to the microcomputer via a PCI slot on the computer's motherboard. The hardware needed to execute the Ethernet function is wholly contained on the peripheral card. Data processed via the Ethernet card is then transferred to the host microcomputer via the parallel data transfer on the PCI interface bus.

[0049] Unlike microcomputers, microcontrollers (by comparison) have limited data transfer and processing capabilities. However, microcontrollers do have specialized interface signals specifically designed for interaction with external devices. Direct connection to sensors, motor control circuits, and other hardware is possible with these specialized signals. Unlike microcomputers, these interfaces are typically not high speed serial or parallel data channels. For instance, a sensor that outputs a voltage, corresponding to a measured parameter, can be directly interfaced with a microcontroller input pin that is designed to receive analog voltages. Unlike microcomputers, microcontrollers have a much more active role in executing a peripheral function. While microcomputer peripherals contain all of the functionality needed to execute a task, microcontrollers often share hardware requirements with the peripheral device. In the cited example, the sensor is required to process an external measurement and convert the measurement into a voltage. The embedded controller is required to accurately measure this voltage. If this function were implemented on a microcomputer, the peripheral would typically convert the voltage to a serial data stream for transfer via a standardized communication protocol (such as USB). While microcontrollers do support a number of serial data transfer standards, most have been specifically designed to support microcontroller centric needs such as I2C (localized serial transfer) and CAN (communication bus for use in automobiles).

[0050] Figure 2 shows resources provided by a Microcontroller including Pulse Width Modulation 205, Input Capture / Output Compare (ICOC) 210, Analog to Digital Converter (A/D) 215, Controller Area Network (CAN) 220, Timers (TIM) 225, Keypay Wake-up 230,

PCT/US2014/019462

Inter-IC Bus (I2C) 235, Serial Peripheral Interface (SPI) 240, Serial Communications Interface (SCI) 245, and Digital to Analog Converter (D/A) 250. Additional resources may include Interrupts (IRQ), Byte Data Link Controller (BDLC), USB OTG, and Analog Compare. A detailed description of these resources follows.

[0051] Pulse Width Modulation (PWM) comprises a moderate to high speed switching digital signal. There is a proportional amount of time signal is logic high versus logic low (duty cycle) and timing interval between logic high transitions (period) are tightly controlled. PWM is typically used for speed control on motors, dimming function on lights, modulation of heating and cooling devices, and speed control on pumps.

[0052] Input Capture Output Compare (ICOC) detects a number in high / low logic transitions on connected signal (input capture) or changes state of an output upon a specific number of input transitions (output compare). ICOC may be used for counting of pulse events, such as pulse encoders for motors. Output compare may be used to automatically stop a motor once a desired encoder count is reached.

[0053] Digital to Analog (D/A or DAC) implements conversion of a digital value to a pseudo analog output. The output is not truly analog as the signal increments, or decrements, in discrete intervals. Interval levels are determined by the resolution of the DAC. D/A converters may be used for input signal generation to amplifiers and to interface with older analog instrumentation and control devices (such as analog flow controller setpoint adjustments). Digital to Analog converters (D/A) implement conversion of analog signals to discrete voltage (i.e. logic) levels. [0054] Controller Area Network (CAN) comprises a 2 wire differential pair communications bus (asynchronous). The CAN was developed for use in automobiles, and provides communications between a multitude of embedded controllers within an automobile (including one or more of engine control, climate control, and safety systems).

[0055] Timers (TIM) may time transition events. Input transitions may start a time capture event in which an internal counter runs upon input signal level transition. TIM may be used to measure frequency of an oscillating signal or period / duty cycle of a PWM generated signal.

[0056] Keypad Wakeup detects input signals from alpha numeric (or numeric) keypads. Keypad presses generate an interrupt via the wakeup inputs. Keypad wakeup includes user interface keypads and controls.

[0057] Inner-IC Bus (I2C and also known as TWI or two wire interface) comprises a 2 wire (clock / data) serial communications and provides communication between an embedded controller and an I2C capable integrated circuit. I2C is typically used for interface with complex Integrated Circuits (including accelerometers and nonvolatile memory).

[0058] Serial Peripheral Interface (SPI) includes a 4 wire communication (including clock, data to peripheral, data from peripheral, and device select). SPI generally has the same uses as I2C. However SPI supports much higher data rates due to bidirectional data transfer. Many integrated circuits support both I2C and SPI on the same device.

[0059] Serial Communications Interface (SCI) comprises a 2 wire asynchronous serial communication. When paired with appropriate hardware, SCI may be used to implement RS232 serial communications. SCI represents an older communications standard used in personal computers, industrial controllers, and embedded devices. Hardware transceivers are typically incorporated with SCI communications to implement RS232 data transfer or RS485 data transfer (industrial applications). Transceivers boost signal levels from logic level to voltages corresponding to RS232 or RS485 transmission standards.

[0060] Universal Serial Bus (USB) provides serial communications commonly found on many consumer devices (computers, phones, cameras, tablets). When used as a peripheral USB connection, embedded device may be interfaced with personal computers, phones or tablets for control and data transfer.

[0061] Interrupt (IRQ) provides general purpose processing interrupts. Interrupts are used to interrupt the normal microcontroller operation and address interrupt condition. One example application of an interrupt comprises a loss of power interrupt controller wherein a loss of source power may produce an interrupt on the IRQ line and redirect processing operations to initiate a loss of power shutdown sequence.

[0062] Byte Data Link Controller (BDLC) comprises an older communication standard that predates CAN and with prior uses in automobile industry. The BDLC standard has largely been replaced by CAN.

[0063] USB On The Go (USB OTG) is used on embedded devices. It can either function as a peripheral or limited host. In peripheral mode, the embedded device operates as a peripheral to a personal computer or other control device. In host mode, the device can be used to read flash memory, interface with printers, and some other limited host modes.

[0064] Analog Compare comprises two or more analog inputs compared against each other or an internal reference voltage, An output state change may occurs when the comparison exceeds a threshold. As one example, a state change occurs when an input voltage 1 becomes greater than input voltage 2. Analog compare may be used to initiate a shutdown sequence if a battery voltage drops below a prescribed threshold.

PCT/US2014/019462

[0065] In addition to the resources describe above, microcontroller interface signals may also include additional special purpose microcontroller signals. These resources or special purpose signals may function as general purpose I/O (Digital I/O) signals (Figure 2, 255) which enables the microcontroller to interface with real world devices. Special purpose pins may be dynamically repurposed as alternative resources via control registers internal to a microcontroller.

[0066] Microcontrollers tend to target price sensitive / power sensitive applications. Many microcontroller applications are battery powered and are implemented in systems that cost a fraction of microcomputer based systems.

[0067] While microcomputers are not generally preferred for instrumentation and control functions, these devices do have some limited applications in industrial settings. As shown in Figure 3, interaction with external devices can be achieved via specialized peripheral devices (either internal or external). Figure 3 show a microcomputer 310 that sends parallel data to a peripheral card 320 through an internal PCI bus. Based on the data, the peripheral card controls power to a motor 330 and then reads back motor speed in the form of pulsed digital output. Low level signal generation and control is executed by the peripheral device for this microcomputer implementation. In a microcontroller implementation, the low level control and instrumentation is executed by the microcontroller device while the peripheral serves primarily as a signal conditioning apparatus. Figure 4 shows a peripheral card 420 that conditions low level control signals from a microcontroller 410 and sensor signal from a motor 430. The low level control and instrumentation is executed by the microcontroller device.

[0068] Most embedded systems don't have interchangeable processors. They typically have the processors built into the motherboard and the only interchangeable parts are the peripheral cards. Of the few that do have interchangeable processors, the emphasis is still on the peripherals and the compatible processors tend to be very limited and not as varied as those offered by the Processor Independent Embedded Platform (PIEP) as described herein.

[0069] In designing the PIEP, specific interface requirements of the microcontroller were considered as well as interface requirements of peripheral devices. Defining specifications for both microcontroller and peripheral interface points permits optimization not only of both interface points but also the system as a whole. Figure 5 shows the motherboard 520 of the PIEP which includes a microcontroller interface 505 and a peripheral interface 510. The microcontroller interface optimizes support for a wide array of microcontroller architectures and devices including Analog to Digital Converter (A/D) 515, Pulse Width Modulation (PWM) 520, Input Capture/Output Compare (ICOC) 525, Interrupts (IRQ) 530, SPI / I2C / CAN Special Purpose buses 535, Serial communications 540, and Digital to Analog Converter (D/A) 545. The peripheral interface is optimized for support of a wide array of peripherals including support for PWM, A/D, ICOC, IRQ 550 (for motion control/data acquisition interface), PWM, A/D, D/A, IRQ 555 (for Mixed signal general purpose interface), SPI, A/D, IRQ, CAN 560, (for SPI & CAN Interface), I2C, A/D, IRQ, D/A 565 for (I2C Interface, Serial Communications) IRQ, A/D 570 (for Serial Communications Interface), ICOC, D/A, PWM, IRQ 575 (for Mixed Signal Interface), and SPI, ICOC, D/A 580 (for Alternate SPI Interface).

**[0070]** In its simplest form, the PIEP design can be evaluated based on resource needs and availabilities. This first step was accomplished by selecting a wide array of peripherals that are likely to be used, identifying specific embodiments of each peripheral function, and then identifying resource needs for each embodiment. Table 1 below shows a Peripheral Usage Resource analysis.

[0071] Table 1

Type of Resource Used

|                                       | Digital | SPI (3<br>sharable) | I2C (2<br>sharable) | SCI | A/D | PWM | ICOC | IRQ<br>(sharable) |

|---------------------------------------|---------|---------------------|---------------------|-----|-----|-----|------|-------------------|

| EEPROM                                |         |                     | 2                   |     |     |     |      |                   |

| RTC                                   |         |                     | 2                   |     |     |     |      | 1                 |

| Capacitive touch controller (AD 7147) | 2       | 4                   |                     |     |     |     |      | 1                 |

| D/A board dac8532                     |         | 4                   |                     |     |     |     |      |                   |

| Dig Port Expander                     |         | 4                   |                     |     |     |     |      |                   |

| Dual Switch Debounce<br>(Max 6817)    | 1       |                     |                     |     |     |     |      |                   |

| HART Protocol Modem<br>(Analog Devices<br>AD5735<br>Light sensor  | 1                 | 4 |   |   |   |  |   |

|-------------------------------------------------------------------|-------------------|---|---|---|---|--|---|

| Remote / Local Temp<br>Sensor bd, 5 chan, I2C<br>based (Max 1989) | 1                 |   | 2 |   |   |  | 1 |

| Resistive touch controller (AD7877)                               |                   | 4 | * |   |   |  | 1 |

| Serial Port Expander<br>(SPI based)                               |                   | 4 |   |   |   |  |   |

| USB host adapter (SPI or SCI or Digital)                          | 11(if not<br>SPI) | 4 |   | 8 |   |  |   |

| 16 seg LED driver with<br>keypad reader I2C<br>based, Max6955     | 2                 |   | 2 |   |   |  |   |

| 4-20 ma input<br>(max1400 front end)                              |                   |   |   |   | 2 |  |   |

[0072] The top row of the table includes commonly used resources (including Digital I/O, SPI, I2C, SCI, A/D, PWM, ICOC, and IRQ) while the left column indicates various peripherals including EEPROM, RTC, Capacitive touch controller (AD 7147), D/A board (dac 8532), Dig Port Expander, Dual Switch Debounce (Max 6917), Hart Protocol Modem (Analog Devices AD5735), Light Sensor, Remote/Local temp sensor, Resistive touch controller (AD7877), Serial Port Expander (SPI based), USB host adapter (SPI or SCI or Digital), 16 seg LED driver with keypad reader (I2C based, Max6955), and 4-10ma input.

[0073] Additional detail regarding the peripherals and their functions are provided below.

[0074] EEPROM comprises nonvolatile memory. Data is stored and retrieved in small intervals (typically either character or byte wide data). EEPROM is under one embodiment used to store operating parameters and calibration data.

[0075] Real time date clock (RTC) typically tracks time of day, and contains a calendar. Some devices may also include alarm functions wherein the clock will generate an output signal on a prescribed period (such as once per second) or on a specific time and date.

[0076] Dig Port Expander provides a virtual digital port. Communication between the expander and host processor is typically either SPI or IC2 based. The device outputs serve as general purpose digital signal lines, typically implementing either 8 or 16 digital I/O lines.

[0077] Dual Switch Debounce handles signal bounce during transition events. Upon actuation or deactivation of a switch, the switch contacts may momentarily "bounce" or return to their original state during transition. A switch debounce buffers out any "bounce" actuations or deactivations during the transition.

[0078] HART Protocol comprises a rugged serial protocol commonly used in industrial devices. Instruments, such as flow meters and sensors, may transmit data via the HART protocol to connected devices (such as embedded controllers).

[0079] Serial Port Expander creates a virtual SCI (serial communication interface) port. Expanders may interface via SPI or I2C interface. The virtual port may be realized (with appropriate transceivers) as RS232 serial ports or other SCI based ports.

**[0080]** Resistive Touch Controller comprises a membrane type switch controller wherein a button press changes the resistance of the membrane keypad. Detection of this event may be achieved with a resistive touch controller.

points) whereas a typical LED numerical display (with decimal point) contains 8 segments. **[0082]** A 4-20 mA input converts current level to a voltage level. Many industrial devices transmit sensor levels via a current signal that ranges from 4 mA up to 20 mA (4 mA representing the lowest level on the device scale, 20 mA the highest). Embedded controllers do not typically contain the hardware to directly measure current, therefore an interface device is needed to convert the current to a voltage.

[0081] A 16 seg LED Driver may be used to drive two digits of a numeric display (with decimal

[0083] As described above, the PIEP design can be evaluated based on resource needs and availabilities. This first step was accomplished by selecting a wide array of peripherals that are likely to be used, identifying specific embodiments of each peripheral function, and then identifying resource needs for each embodiment. As already indicated above, Table 1 above shows a Peripheral Usage Resource analysis listing common resources across the top of the table and peripherals along the left side of the table. Table entries map resources to peripherals. For example, the EEPROM row and I2C column intersect at a highlighted table entry containing the number two (2). This number indicates that the EEPROM peripheral requires two I2C resources. As another example, a capacitive touch controller requires 2 digital I/O, 4 SPI, and 1 IRQ resources. Of course, the table is representative and not all inclusive. Further, resources designated as sharable may be used by multiple peripherals.

[0084] Following identification of resource needs, a diverse group of microcontrollers (processors) were selected and analyzed. The microcontroller analysis considered resource types, the quantities of each type, as well as the commonality of resources (quantities and types) across the array of devices under consideration. Resources common to all evaluated devices were designated as the minimum acceptable level of resources that would be available in the implemented system design. Table 2 below shows the analysis of microcontroller resources common across architectures and processors.

[0085] Table 2

| Resource<br>Type        | Freescale   | Freescale<br>ARM | Intel    | Microchip       | Microchip<br>16bit | Min<br>Resource |

|-------------------------|-------------|------------------|----------|-----------------|--------------------|-----------------|

| 1 4 10 0                | MC9S12DP512 | MAC7106          | Z51F6412 | PIC24FJ256GA110 | dsPIC30F6014A      | Nesource        |

|                         |             |                  |          | 3.3 Volt part   |                    |                 |

| Total I/O               | 87          | 112              | 66       | 85              | 68                 | 66              |

| A/D                     | 16 (10 bit) | 32               | 15       | 16              | 16                 | 15              |

| PWM                     | 8           | 8                | 5        | 9               | 8                  | 5               |

| TIM                     | 8           | 8                | 6        | 5               | 5                  | 5               |

| ICOC                    | 8           | 8*               |          | 9               | 8                  |                 |

| Keypad<br>Wakeup<br>IRQ | 20          |                  |          |                 |                    |                 |

| inq                     | 20          |                  |          |                 |                    |                 |

| SCI                     | 2           | 4                | 4        | 4               | 2                  | 2               |

| SPI                     | 3           | 4                | 2        | 3               | 2                  | 2               |

| I2C                     | 1           | 1                | 1        | 3               | 1                  | 1               |

| CAN                     | 5           | 4                |          |                 | 2                  | 2               |

| BDLC                    | 1           |                  |          |                 |                    |                 |

| USB OTG                 |             |                  |          |                 |                    |                 |

[0086] Table 2 features microprocessor type across the top of the table and resources corresponding to each such processor in the left column of the table. The resources include A/D, PWM, TIM, ICOC, Keypad wake IRQ, SCI, SPI, I2C, CAN, BDLC, and USB OTG. A detailed description of such resources and corresponding functionality is set forth above. As shown in the table, the Freescale MC9S12 processor includes 87 total I/O signal points including the following type (number) of resources: PWM (8), TIM (8), ICOC (8), Keypad Wake IRQ (20), SCI (2), SPI (3), I2C (1), CAN (5), and BDLC (1).

[0087] The introduction of any subsequent microcontroller (processor) device must contain the minimum resource types and quantities identified in order to retain full compliance with PIEP design specifications. Using a resource alignment method (Figure 6), we matched the minimum resource requirements (guaranteed resources available from a microcontroller) against the resource needs of evaluated peripherals. This resulted in the creation of a generic or common alignment table. The alignment table helped us determine the optimum mix of resource types on a peripheral interface connector, the number of peripherals that could typically be stacked together (on a single interface header), and the total number of peripheral headers that should be implemented on a system.

[0088] From that we created the generic map file (see Table 3 below). The generic map file assigns specific resource types and quantities to specific peripheral interface headers. This assignment defines known resource locations and quantities that will be presented on the Motherboard. Independent of the installed processor, resources assigned by the generic map file will be presented in known locations (both interface header and pin position on the header). This knowledge enables the design of peripheral devices that can interface with the PIEP system, regardless of the specific processor installed.

[0089] Figure 6 shows the resource realignment method used to combine data from Table 1 and Table 2 in order to produce a generic map file (shown in Table 3 below) which maps specific microprocessor resources to a pin location on the PIEP board. The generic map file maps resource to pin/header locations across six top slot headers and six back slot headers. All twelve headers correspond to physical headers featured on the motherboard bottom. The top and back slot headers are referred to as Stackable Peripheral Interface Ports (SPIP). Each such header includes ten (10) pin locations.

[0090] The resource alignment method assigns resources to header/pin locations in four steps of decreasing priority. As seen in **Figure 6**, each of the four steps includes a method component **670**, a purpose component **680**, and result component **690**. The first step **605** of the alignment method assigns type of resource to pin number locations to ensure resources are in a known location across headers **610**. In other words, if the resource appears on a header, it will appear in an assigned position. As one example of this resource assignment **615**, the A/D resource is assigned to pins 2, 3 & 4. This means that if a header features three A/D resources, they will appear in position 2, 3 & 4 on such header. Step two **620** of the method includes grouping

resource types on common peripheral headers according to functional needs or end uses of peripheral devices 625. As one example 630, A/D, PWM, and ICOC resources may be grouped to provide motion control processing. The third step 635 of the alignment method assigns resources (including the grouped resources) to specific header designations to permit the design of peripherals that utilize more than one interface header 640. As one example 645, the motion control resources (A/D, PWM, and ICOC) are assigned to a particular "motion control" header. The fourth step 650 of the resource alignment method includes locating adjacent resource groups for sharing by one or more peripherals 655. As one example 660, the method may assign PWM signals to neighboring headers thereby permitting the design of a multi-axis motion controller.

[0091] Using the resource alignment method, the generic map file was created. Table 3 below shows the generic map file.

## [0092] Table 3

Top Slots

SPI1 (top)

| Vcc      | AD-9     |

|----------|----------|

| DIO      | DIO-5    |

| SPI-MOSI | SPI-MISO |

| SPI-SCK  | SPI-SS   |

| GND      | INTR1    |

Dig 1 (top)

| 1 | Vcc    | AD-1   |

|---|--------|--------|

|   | AD-2   | DIO-1  |

|   | PWM-1  | PWM-2  |

|   | ICOC-1 | ICOC-2 |

| 9 | GND    | ICOC-3 |

12C1 (top)

| Vcc     | AD-10   |

|---------|---------|

| DIO     | DIO-6   |

| I2C-SDA | I2C-SCL |

| DIO-7   | DIO-8   |

| GND     | INTR2   |

Dig2 (top)

| 1 | Vcc    | AD-3   |

|---|--------|--------|

|   | AD-4   | AD-5   |

|   | PWM-3  | PWM-4  |

|   | ICOC-4 | ICOC-5 |

| 9 | GND    | ICOC-6 |

SCI1 (top)

| Vcc    | AD-11  |

|--------|--------|

| DIO-9  | DIO-10 |

| DIO-11 | DIO-12 |

| SCI-RX | SCI-TX |

| GND    | INTR3  |

Dig3 (top)

| 1 | Vcc   | AD-6  |

|---|-------|-------|

|   | AD-7  | AD-8  |

|   | PWM-5 | DIO-2 |

|   | DIO-3 | DIO-4 |

| 9 | GND   | IRQ   |

**Back Slots**

SPI2 (bottom)

Dig4 (bottom)

| Vcc      | DIO      |

|----------|----------|

| DIO      | PS++     |

| SPI-MOSI | SPI-MISO |

| SPI-SCK  | SPI-SS   |

| GND      | INTR7    |

| 1 | Vcc  | PS++  |

|---|------|-------|

|   | PS++ | PS++  |

|   | PS++ | PS++  |

|   | PS++ | PS++  |

| 9 | GND  | INTR4 |

I2C2 (bottom)

| Vcc      | PS++     |

|----------|----------|

| PS++     | PS++     |

| I2C-SDA+ | I2C-SCL+ |

| DIO      | PS++     |

| GND      | INTR8    |

Dig5(bottom)

|   | Digo(bollott) |       |  |

|---|---------------|-------|--|

| 1 | Vcc           | PS++  |  |

|   | PS++          | PS++  |  |

|   | PS++          | PS++  |  |

|   | PS++          | PS++  |  |

| 9 | GND           | INTR5 |  |

SCI2 (Bottom)

| Vcc    | PS++   |

|--------|--------|

| PS++   | PS++   |

| DIO-22 | DIO-23 |

| SCI-RX | SCI-TX |

| GND    | INTR9  |

Dig6 (bottom)

|   | Digo (Soctoin) |       |

|---|----------------|-------|

| 1 | Vcc            | PS++  |

|   | PS++           | PS++  |

|   | PS++           | PS++  |

|   | PS++           | PS++  |

| 9 | GND            | INTR6 |

[0093] Key to Table 3:

[0094] Vcc – peripheral voltage supply pin – either 5V or 3.3V supplies are permitted, processor specific implementation determines which voltage(s) is permitted.

[0095] AD – Analog to Digital Resource.

[0096] DIO – general purpose digital input / output resource.

[0097] SPI(X) – Serial peripheral interface communication bus (requires four resource pins for implementation).

[0098] INTR(X) – General purpose interrupt.

[0099] PWM – Pulse Width Modulation Resource.

[00100] ICOC – Input capture / output compare resource.

[00101] SCI(X) – Serial communications interface resource (requires two resource pins for implementation).

[00102] I2C(X) – Inter-IC communications bus (requires two resource pins for implementation).

[00103] Gnd – peripheral power supply ground pin.

[00104] Notes for Table 3: The symbol "+" designates resources may be used by multiple devices (sharable resources). It is permissible to duplicate resources on headers if

those resources are sharable. I2C is a sharable resource. The same I2C resource pins may be used to populate both I2C1 and I2C2 header positions (I2C1 & I2C2 pins 2; I2C1 & I2C2 pins 3). The "PS++" symbol indicates Processor specific implementation meaning that the pin is reserved for needs of specific processor implementation. These fields are populated with resources per map files of individual processor types.

[00105] The generic map file assigns specific resource types and quantities to specific peripheral interface headers. This assignment defines known resource locations and quantities that will be presented on the Motherboard. Independent of the installed processor, resources assigned by the generic map file will be presented in known locations (both interface header and pin position on the header). This knowledge enables the design of peripheral devices that can interface with the PIEP system, regardless of the specific processor installed.

[00106] The generic map of Table 3 features top slot headers (SPIP slots 1-6) including the SPI1, Dig1, I2C1, Dig2, SCI1, and Dig3 header. The generic map also features back slot headers (SPIP slots 7-12) including the SPI2, Dig4, I2C2, Dig5, SCI2, and Dig6 headers. The generic map file assigns certain resources to header pin locations. As just one example, Table 3 shows that an analog to digital resource AD-1 is assigned to Dig 1 header, pin 2. This is of course consistent with the alignment method which states that an AD resource (if present on a header) must appear at pin location 2, 3 or 4.

[00107] SPIP Slots 1-6 (top slots) should maintain compliance across processors to the greatest extent possible. SPIP Slots 7-12 (back slots) are generally recommended implementations and should be adhered to as processor resources permit and may be superseded if needed by higher priority processor specific functions

[00108] The generic map defines a total of twelve generic SPIP assignments corresponding to twelve physical headers on the PIEP board. The map generally groups resources based on peripheral needs resulting in headers providing type of end use functions as follows.

Accordingly, each header serves a general purpose or provides certain functionality as follows:

[00109] Dig1, Dig 2 headers provide motion control and data acquisition.

[00110] Dig3 header provides data acquisition and general purpose control / sensing.

[00111] SPI 1 & 2 headers provide support of SPI based integrated circuits.

[00112] I2C1 & I2C2 headers provide support of I2C based integrated circuits.

[00113] SCI1 & SCI2 headers provide support of SCI devices (RS232, RS422, RS485, etc), and CAN bus devices.

[00114] Dig4 - Dig6 headers are reserved for processor specific implementations and resources that are not defined within the Generic Map File. An example is Digital to Analog converters. It is also used for additional resources (by number, not type) beyond those defined in the Generic Map File. For example, additional ATD resources may be presented on Dig4 - Dig6 headers. [00115] It should be noted that not all peripheral interface positions are defined in the generic map file. Assignments of these unallocated positions are deferred to processor specific implementations and may include additional allocation of existing resources or assignment of new resources not considered in the generic map file. If a new resource type is implemented, then the assignment (pin and header positions) should be adhered for any subsequent microcontroller implementations (pin positions required, header positions recommended). This requirement also applies to groups of resources where multiple resource types may be required in conjunction to implement a peripheral function.

[00116] Assignment of new resources is made with careful consideration of numerous factors. Inclusive in these considerations are other resources on the associated header, resources available on near neighbor peripheral connectors, and expected end use. Figure 7 is an example embodiment of the PIEP design and demonstrates the numerous considerations applicable to the assignment of new resources. The PIEP motherboard includes a processor card 795 which itself physically embodies a mapping from microprocessor resources to motherboard pin assignments. The PIEP motherboard 710 includes peripheral interface headers located in proximity to one another. Single 720 and double headed 730 peripherals may couple with peripheral interface headers. The motherboard displays peripherals 740, 750, 760, 770 attached to peripheral headers. The motherboard also shows a stacked peripheral configuration 760, 770. A first peripheral 760 attaches to the motherboard and a second peripheral 770 attaches to the first peripheral to produce the stacked configuration 760, 770. Resources not used on the first (or bottom) peripheral are passed through to the second peripheral (i.e., the peripheral above). Figure 7 displays pin assignments for three of the interface headers 775, 780, 785. It should of course be noted that under one embodiment, unassigned pin locations are available for assignment of resources. The motherboard includes supplemental processor connectors 790. Signal lines not routed from microprocessor to the peripheral headers are routed to the supplemental connectors.

[00117] While specific presentation of microcontroller signals to peripheral headers has some variability, depending upon the individual microcontroller implementations, the microcontroller to motherboard interface is more rigid. Upon assignment of the generic map file, it was possible to define the microcontroller to motherboard interface port. This port considered the number of peripheral interface signals required, the total number of signals available from microcontrollers under consideration, and any alternate presentations that may be desirable. Each peripheral interface header and pin was assigned a specific interface point on the microcontroller interface connector. Additionally, supplemental signals (power, debug interface, reset) were assigned to special purpose signal connectors not associated with the peripheral interface points.

[00118] Table 4 shows a processor specific SPIP map file for the Free Scale Processor (MC9S12DP512 processor).

Top Slots SPI1 (top)

| SETT (top) |               |

|------------|---------------|

| +5V        | ATD1-0        |

|            |               |

| ATD1-1     | DIO/PTB-4     |

|            |               |

| SPI-MOSI   | SPI-MISO      |

|            |               |

| SPI-SCK    | SPI-SS        |

|            | INTR1/KWH/PH- |

| GND        | 0             |

|            |               |

| Dig | 1 | (to | p) |

|-----|---|-----|----|

|     |   |     |    |

| 1 | +5V       | ATD0-0    |

|---|-----------|-----------|

|   |           |           |

|   | ATD0-1    | DIO/PTB-0 |

|   | PWM/PTP-  | PWM/PTP-  |

|   | 0         | 1         |

|   | ICOC/PTT- | ICOC/PTT- |

|   | 0         | 1         |

|   |           | ICOC/PTT- |

| 9 | GND       | 2         |

12C1 (top)

| ATD1-2        |

|---------------|

|               |

| DIO/PTB-5     |

|               |

| I2C-SCL       |

|               |

| DIO/PTB-7     |

|               |

| INTR2/KWH/PH1 |

|               |

Dig2 (top)

|   | +5V       | ATD0-2    |

|---|-----------|-----------|

|   |           |           |

|   | ATDO-3    | ATD0-4    |

|   | PWM/PTP-  | PWM/PTP-  |

|   | 2         | 3         |

|   | ICOC/PTT- | ICOC/PTT- |

|   | 3         | 4         |

|   |           | ICOC/PTT- |

| ) | GND       | 5         |

SCI1 (top)

| +5V       | ATD1-4         |

|-----------|----------------|

|           |                |

| DIO/PTA-0 | DIO/PTA-1      |

|           |                |

| DIO/PTA-2 | DIO/PTA-3      |

| SCI-RX    | SCI-TX         |

|           |                |

| GND       | INTR3/IKWH/PH2 |

| GND       | INTR3/IKWH/PH2 |

Dig3 (top)

| +5V       | ATD0-5    |

|-----------|-----------|

|           |           |

| ATD0-6    | ATD0-7    |

| PWM/PTP-  |           |

| 4         | DIO/PTB-1 |

| DIO/PTB-2 | DIO/PTB-3 |

|           |           |

| GND       | IRQ/PTE-1 |

### **Back Slots**

| SP | 12 | (bo | tto | m١ |

|----|----|-----|-----|----|

|    |    |     |     |    |

| SPI2 (bottom) |               |

|---------------|---------------|

| +5V           | ATD1-5        |

|               |               |

| CAN0-H/PM0    | CAN0/PM1      |

| SPI-MOSI+     | SPI-MISO+     |

| SPI-SCK+      | DIO/PE-4      |

|               |               |

| GND           | INTR7/KWJ/PJ0 |

# Dig4

|   | (polloni) |            |

|---|-----------|------------|

| l | +5V       | DIO/PTK-0  |

|   |           |            |

|   | DIO/PTA-4 | DIO/PTA-5  |

|   | I2C-SDA+  | I2C-SCL+   |

|   | DIO/PTK-1 | DIO/PTK-2  |

|   |           |            |

| ) | GND       | XIRQ/PTE-0 |

I2C2 (hottom)

| 1202 (000011) |                |

|---------------|----------------|

| +5V           | ATD1-6         |

| CANIT LI/DM O | CANOL (DM O    |

| CAN1-H/PM-2   | CAN2-L/PM-3    |

| I2C-SDA+      | I2C-SCL+       |

| DIO/PTA-6     | DIO/PTA-7      |

|               |                |

| GND           | INTR2/KWH/PH1+ |

|   | Dig5(bottom) |               |

|---|--------------|---------------|

| 1 | +5V          | DIO/PTK-3     |

|   |              |               |

|   | DIO/PM-6     | DIO/PM-7      |

|   | SPI2-        |               |

|   | MISO/PH4     | SPI2-MOSI/PH5 |

|   | SPI2-        |               |

|   | SCK/PH6      | SPI2-SS/PH7   |

|   |              |               |

| 9 | GND          | INTR5/KWH/PH3 |

SCI2 (Bottom)

| SOIZ (BOLLOITI) |                |

|-----------------|----------------|

| +5V             | ATD1-7         |

|                 |                |

| CAN2-H/PM4      | CAN2-L/PM5     |

| DIO/PWM/PTP-    |                |

| 6               | DIO/PWM/PTP-7  |

| SCI-RX          | SCI-TX         |

|                 |                |

| GND             | INTR3/KWH/PH2+ |

Dig6 (bottom)

| 1 | +5V        | DIO/PTK-4     |

|---|------------|---------------|

|   |            |               |

|   | DIO/PE7    | DIO/PWM/PTP-5 |

|   |            |               |

|   | I2C-SDA+   | I2C-SCL+      |

|   | ICOC/PTT-6 | ICOC/PTT7     |

|   |            |               |

| 9 | GND        | INTR6/KWJ/PJ1 |

|   |            |               |

A Key to Table 4: [00119]

AD – Analog to Digital Resource. [00120]

[00121] DIO – general purpose digital input / output resource.

SPI(X) – Serial peripheral interface communication bus (requires four resource [00122]

pins for implementation).

INTR(X) – General purpose interrupt. [00123]

PWM – Pulse Width Modulation Resource. [00124]

ICOC – Input capture / output compare resource. [00125]

[00126] SCI(X) – Serial communications interface resource (requires two resource pins for implementation).

[00127] I2C(X) – Inter-IC communications bus (requires two resource pins for implementation).

[00128] Gnd – peripheral power supply ground pin.

[00129] XIRQ – non-maskable interrupt, this interrupt is the highest priority and will be serviced first in the event multiple interrupt pins are activated.

[00130] CAN – Controller Area Network communications protocol. Requires two resource pins for implementation.

Notes for Table 4: The Freescale MC9S12DP512 only supports 5V operation; therefore peripherals must be powered at 5 volts. The MC9SX12DP512 is pin compatible and supports both 3.3 / 5 volt peripherals. The MC9SX12 may under one embodiment be substituted for final implementation. This is permissible as it is compliance with the Generic Map File. Resources that are followed by a "/" indicate the specific port and pin on the processor from where this resource will be supplied. For example, I2C2 CAN1H / PM-2 indicates that this can resource is supplied by processor port M pin 2 of the port. The symbol '+' designates resources may be used by multiple devices (sharable resources). It is permissible to duplicate resources on headers if those resources are sharable. I2C is a sharable resource. The same I2C resource pins may be used to populate both I2C1 and I2C2 header positions (I2C1 & I2C2 pins 2; I2C1 & I2C2 pins 3).

[00132] Considering the total resources available from a microcontroller may exceed peripheral interface availability, supplemental resource connectors were also included in the design. These supplemental connectors, while not designed to directly interface peripheral devices, can be utilized in conjunction with hardware designed to install hardware remotely. These DPIP connectors permit processor specific functionality to be presented to the motherboard and also permit alternate presentation of resources that are assigned on the SPIP connectors. Duplication of resources (presentation on both DPIP connectors and SPIP connectors are permitted). Resource mapping of processor resources on DPIP connectors is performed in a manner wherein specific types of resources may be present at known locations.

[00133] Figure 8 shows under one embodiment supplemental processor resources implemented on motherboard DPIP headers with respect to the MC9S12 processor. Figure 8 shows the processor card 860 and the SPI2 865, I2C2 870, DIG5 875, SCI2 880 and DIG 6 885 peripheral headers. The figure shows pin assignments for DPIP1 810, DPIP2 820, DPIP4 830, and DPIP5 840 headers. Details regarding the assignments are set forth in Table 5 below.

[00134] Table 5 shows under one embodiment the DPIP file for the MC9S12DP512 processor.

[00135] Table 5 (DPIP1-DPIP10 map files)

PTP-1/PWM

PTP-3/PWM

PTP-5/PWM

PTP-7/PWM

| _DPIP1/ICOC |                | _   | DPIP2/PWM |

|-------------|----------------|-----|-----------|

| PTT-0/ICOC  | PTT-<br>1/ICOC | 1   | PTP-0/PWM |

|             | PTT-           |     |           |

| PTT-2/ICOC  | 3/ICOC         | _ 3 | PTP-2/PWM |

| PTT-4/ICOC  | PTT-<br>5/ICOC | 5   | PTP-4/PWM |

| PTT-6/ICOC  | PTT-<br>7/ICOC | 7   | PTP-6/PWM |

| PE-0/XIRQ   | PE-1/IRQ       | ]   | <u> </u>  |

| DPIP5      |                |   | DPIP6               |                     |  |

|------------|----------------|---|---------------------|---------------------|--|

| PTJ-0/KWJ0 | PTJ-<br>1/KWJ1 | 1 | PH-<br>0/MISO1/KWH0 | PH-<br>1/MOSI1/KWH1 |  |

| PTJ-6/SDA  | PTJ-7/SCL      | 3 | PH-<br>2/SCK1/KWH2  | PH-<br>3/SS1/KWH3   |  |

| PTE-0/XIRQ | PE-1/IRQ       | 5 | PH-4/KWH4           | PH-5/KWH5           |  |

| PE-3/Lstrb | PE4/Eclk       | 7 | PH-6/KWH6           | PH-7/KWH7           |  |

| DPIP9             |                   |   | DPIP10    |            |

|-------------------|-------------------|---|-----------|------------|

| PTK-<br>0/XADDR14 | PTK-<br>1/XADDR15 | 1 | +Vcc      | +Vcc       |

| PTK-<br>2/XADDR16 | PTK-<br>3/XADDR17 | 3 | Alt_Dbg-7 | Alt_Dbg-8  |

| PTK-<br>4/XADDR18 | PTK-<br>5/XADDR19 | 5 | Alt_Dbg-9 | Alt_Dbg-10 |

| PTK-              |                   |   |           |            |

| 7/ECS/ROMCTL      | PTE0/XIRQ         | 7 | Gnd       | Gnd        |

WO 2014/134471 PCT/US2014/019462 22

| DPIP3      |           |     | DPIP4            |                  |

|------------|-----------|-----|------------------|------------------|

| SPI3-MISO0 | SPI3-MOSI | ] 1 | RXCAN3           | TXCAN3           |

|            |           |     |                  |                  |

|            |           |     | PTM-             | PTM-             |

| SPI3-/SCK0 | SPI3-SS   | 3   | 2/RX_BF/RXCAN1   | 3/TX_BF/TXCAN1   |

|            |           |     |                  |                  |

|            |           |     | PTM-             | PTM-             |

| SPI0-MISO0 | SPI0-MOSI | 5   | 4/BF_PSYN/RXCAN4 | 5/BF_PROK/TXCAN4 |

|            |           |     |                  |                  |

|            |           |     | PTM-             | PTM-             |

| SPI0-/SCK0 | SPI0-SS   | 7   | 6/BF_PERR/RXCAN4 | 7/BF_PSLM/TXCAN4 |

| DPIP7            |                  |

|------------------|------------------|

| :                |                  |

| PAD8/ATD1-0      | PAD9/ATD1-1      |

| PAD10/ATD1-<br>2 | PAD11/ATD1-<br>3 |

| PAD12/ATD1-<br>4 | PAD13/ATD1-<br>5 |

| PAD14/ATD1-<br>6 | PAD15/ATD1-<br>7 |

| +V_ADref         | -V_ADref         |

resources.

|   | DPIP8       |             |

|---|-------------|-------------|

| 1 | PTB-0/ADDR0 | PTB-1/ADDR1 |

| 3 | PTB-2/ADDR2 | PTB-3/ADDR3 |

| 5 | PTB-4/ADDR4 | PTB-5/ADDR5 |

| 7 | PTB-6/ADDR6 | PTB-7/ADDR7 |

| [00136] | A key for the DPIP map file of Table 5 follows.                                |

|---------|--------------------------------------------------------------------------------|

| [00137] | ICOC (X) –Input Capture / Output Compare resource.                             |

| [00138] | SPI (X) – Serial Peripheral Interface resource.                                |

| [00139] | SCI (X) – Serial Communications Interface resource type.                       |

| [00140] | CAN – Controller Area Network communication resource type.                     |

| [00141] | I2C – Inter-IC Communications resource type.                                   |

| [00142] | KW – Keypad wake-up resource type.                                             |

| [00143] | ATD – Analog to Digital Converter resource.                                    |

| [00144] | V_ADref – External voltage reference for processor Analog to Digital Converter |

[00145] ADDR – parallel data bus, may be implemented via digital I/O ports or by use of processor pins specifically designated for this purpose.

[00146] Alt\_Dbg – alternate programming / debugging interface pins, other than debug / programming supported via 6 pin debug or 20 pin JTAG programming headers.

[00147] XADDR – Expanded address bus, provides for 16 bit parallel data transfers when used in conjunction with ADDR resources.

[00148] Alt\_Dbg – alternate programming / debugging interface pins.

[00149] IRQ / XIRQ – High priority interrupt resources, take precedence over other interrupts when multiple interrupts occur.

[00150] Lstrb – Low byte strobe, indicates activity on processor data bus.

[00151] Eclk – External clock signal – can be used to monitor processor bus clock or inject an external clock onto processor internal bus clock.

[00152] ECS – controls processor clock source.

[00153] Vcc – peripheral power supply.

[00154] Gnd – peripheral power supply ground.

[00155] Referring back to the general design of the PIEP, the design may be alternatively be evaluated from the perspective of the microcontroller resources. While resource types (and quantities) vary among the different microcontroller embodiments, a core group and quantity of resources is generally expected on virtually all devices. For example, microcontrollers evaluated for use with the PIEP all contain at least eleven analog to digital resources (AD). These eleven resources have a fixed assignment on the motherboard peripheral interfaces, regardless of the connected microcontroller (see Table 3). Specifically, the resources always appear on peripheral connectors Dig1, Dig2, Dig3, SPI1, SCI1, and I2C1. Furthermore, these resources always appear on specific peripheral connector pins. If a peripheral connector contains only one AD resource, it will always appear on pin 2. Likewise, if a peripheral connector contains three AD resources, they will always appear on pins 2, 3, and 4 (see Table 3). In a similar manner, other minimum resource types and quantities are assigned specific locations on motherboard peripheral connectors. This assignment is known as the Generic Map File (see Table 3). [00156] The Generic Map File provides the minimum resources that are guaranteed to be present, regardless of the connected microcontroller. Any peripheral designed to work with the Generic Map File is likewise guaranteed to be compatible with any connected microcontroller. The Generic Map File does not assign all peripheral interface headers or pins, only those designated as the guaranteed minimum resources available across all microcontrollers. [00157] If a microcontroller contains more than the minimum number of a resource types, for instance 16 AD resources, then these resources will follow pin assignment convention as the

higher priority (see Table 3 and 4). Stated another way, the additional resources will be assigned to pin positions 2, 3, and/or 4 on additional peripheral interface headers (such as Dig4 or SCI2). Adhering to this protocol enables additional peripheral interface connectors to be compliant with peripheral devices. For instance, if a peripheral requires two AD resources and two Pulse Width Modulation (PWM) resources, this peripheral will be guaranteed to properly connect with interface headers Dig1 and Dig2 (per the Generic Map File). If the implemented processor has adequate PWM and AD resources, then the peripheral may also be compliant with Dig3 or Dig4 interface headers.

[00158] In part, the design methodology does not attempt to ensure compliance of all motherboard peripheral interface connectors across all microcontrollers and all peripherals. Compliance is achieved if each peripheral type has at least one compliant connection point on the motherboard across all implemented microcontrollers. The only exception to this compliance is for resource types not found on all microcontrollers. For example, the DAC resource (digital to analog converter) is present on some but not all PIEP microcontrollers.

[00159] The Digital to Analog (D/A) resource is implemented on some, but certainly not all, microcontrollers. For microcontrollers that contain this resource, it will appear on header pin 3, connector Dig1 (primary) or Dig6 (secondary A peripheral that requires this resource will only be compliant with microcontrollers supporting this resource. This limitation, however, is not a function of the PIEP design but rather a limitation inherent to the microcontroller.

[00160] While resource types and quantities are a function of the microcontrollers utilized, specific groupings of resources on individual motherboard peripheral interface connectors is a function of peripheral resource needs. Based on an analysis of numerous peripherals, groupings of the most probable resource types and quantities were determined. These groupings define specific resource types, quantities, and total number of resource positions needed on each motherboard peripheral interface connector. This optimized grouping, the second component utilized in creating the Generic Map File, determined the number of resources per header (8) and unique resource combinations (for instance Dig1 contains 2 AD resources, 2 PWM resources, and 3 ICOC resources). For peripherals needing more than eight resources (or needing resource combinations not supported on a single header), the peripheral may utilize more than one header to acquire the necessary resources. In this manner, resource assignment also includes the

physical grouping on adjacent motherboard peripheral headers to ensure "near neighbor" headers contain complimentary resources that may be used by these peripherals.

[00161] In limited instances, it may be desirable to reassign resources in unique configurations. For example, in a communications centric design it may be desirable to implement six SCI headers on the motherboard while other uses of the same microcontroller may need no SCI headers. Assuming the microcontroller has the resources to support these implementations; it is possible to reassign the default resource mapping for a microcontroller by use of a remapping adapter. This adapter, attaching between the motherboard and microcontroller, reroutes the microcontroller signals for alternate presentations to the motherboard thus creating a different map file. Pin level compliance on the motherboard peripheral interface connectors must generally be adhered to, but not overall motherboard peripheral header functionality. [00162] As stated above, the PIEP platform permits reassignment of default processor map files via a processor remap adapter. This is a physical device designed for installation between the processor and motherboard. This apparatus reroutes processor signals for alternate presentations to the motherboard. The most common example of this implementation is the substitution of SPIP header types. For example, if the SIP2 header is not required, a remap adapter may be utilized to assign this connector the functionality of a Dig port. Typically the new resources are allocated from a pool of resources that, by default, have been allocated to one or more DPIP headers and do not appear on other SPIP headers. Figure 9 shows the PIEP motherboard with a remap adapter board 920. The motherboard features a 200 pin header 940 routing microcontroller resources to motherboard pin locations (e.g. SPIP and DPIP headers). The processor board 930 features a processor and 200 pin interface 950 which maps microprocessor ports/resources to header pin positions. The processor board interface and the motherboard 200 pin header then couple under one embodiment to route signals to motherboard pin locations based on the processor board interface assignments. Under an alternative embodiment, Figure 9 shows a remap adapter 920 which reassigns processor map files. The adapter mounts between the motherboard and processor resources for alternate presentation, i.e. for alternate map file. [00163] The map files, both generic and specific, can most accurately be thought of as a blueprint for the physical hardware implementation of processor boards. The generic map file defines resource types and quantities that must be present on individual motherboard headers and pins. The processor specific map file is an expansion of the generic map file, assigning resources to unallocated locations within the generic map file and identifying specific pins on the microcontroller that are utilized to execute the generic map file requirements. To fully understand how this process is implemented, an example embodiment implementation will be discussed.

[00164] All interface points contained on the motherboard are derived from the processor routed through a centralized 200 position header. As the motherboard is a fixed design that doesn't vary with processor implementations, it is the responsibility of the processor board to align processor resources with the correct headers and pins on the motherboard. This alignment is achieved through the 200 pin processor to motherboard header.

[00165] Referencing Figure 10, the generic map file requires SPIP header Dig1, pin 2 on motherboard 1010 to contain an analog to digital resource. This specific header pin (Dig1, pin 2) is routed to pin position 154 on the 200 pin processor interface header 1020 (contained on the motherboard). The processor board 1046 likewise contains a mating 200 pin header 1030 wherein Dig1, pin 2, is presented on pin position 154. Evaluating the resources available on the MC9SX12DP512 processor, it can be seen that an analog to digital resource (ATD0-0) is available on pin 67 of the processor. By connecting the processor pin 67 to pin 154 on the 200 position interface header 1030, an analog to digital signal will be presented on the motherboard Dig1, pin 2, header position. In a likewise manner, the various signals from the microcontroller are assigned to specific locations on the mating 200 pin header 1030, with each header pin ultimately routing to a fixed location on the motherboard.

[00166] Referring to Figure 10, it is readily apparent how this method aids in processor independence. In the cited figures, Digital header 1, pin2, requires an analog to digital resource (per the generic map file). This pin is physically connected to position 154 on the processor interface header. Similarly, for implementation on the Freescale MC9SX12DPX512 processor, an analog to digital resource is available on the processor pin 67 of processor. By routing this processor pin (pin 67) to the interface header 1030 position 154, a connection path is established via interface header 1020 position 154 to route an analog to digital resource to the Dig1, pin 2, header position on motherboard 1010. For implementation on the Atmel SAM3X9E processor (see Figure 11), an analog to digital resource is available on processor pin 84 of processor located on processor board 1140. Likewise by routing a connection between processor pin 84 and the 200 pin position 154 on the interface header, a pathway is established to pin 154 on the

motherboard header 1120 to provide an analog to digital resource for Dig1, pin 2 on motherboard 1110, with the Atmel processor installed (Figure 11). The fact that these processors have resources assigned to different pins, are physically different sizes, have different number of total pins (112 for Freescale, 144 for Atmel ARM); doesn't impact the ability to implement the processors with the described method. By containing the processor on a separate physical board and providing a common interface point (the 200 pin header), many processor specific details can be abstracted from the design (such as physical size and processor pin assignments).

[00167] Based on the description above, it should be evident that the 200 position interface header residing between the motherboard and processor is an instrumental aspect of the processor independence component. This interface point permits alignment of various processor signals and resources such that they are presented to the correct locations on the motherboard (in accordance with the generic and processor specific map files).

[00168] Figure 12 shows how to use the PIEP design to install a peripheral onto the PIEP mother board. Figure 12 shows the Freescale 9S12 processor specific map file. The lines 1210 show the correspondence between the map file SPIP assignments and the physical SPIP headers on the motherboard. The processor map file details the motherboard pin assignments for the corresponding headers. Figure 13 shows a Real Time Date Clock Peripheral. Specifically, Figure 13 shows the peripheral map file 1310 which indicates required resources. Figure 13 also shows the peripheral device itself 1320. Figure 14 demonstrates a procedure for installing the peripheral. First, the user opens the processor map file 1410. Second, the user opens the peripheral map file 1420. Third, the user identifies which motherboard headers contain the resources needed 1430. These are the headers where peripherals may be installed on the motherboard. Figure 14 then shows installation 1440 of the peripheral. Figure 15 shows how to install stacked peripherals. The peripherals to be installed include the real time data clock peripheral and the relay peripheral. First, the user opens the processor map files. Second, the user opens the peripheral map for both peripherals (1510, 1520). Third, the user ensures that the peripherals don't need the same resources 1530 (except for sharable resources such as I2C or general interrupts). Fourth, the user identifies which motherboard headers contain the resources needed by both peripherals 1540. These are the headers where peripherals can be installed on the motherboard. Note that any processor resource type can also be used as DIO.

[00169] As already described in detail above, the PIEP design implements a mapping of resources from processor to PIEP header/pin locations through a 200 pin interface between the PIEP motherboard and the processor board. Figures 16A-16D includes a 200 pin processor interface header contained within a processor circuit board module or located on a processor board. Figures 17A-17C includes a schematic of a 200 pin processor interface header, contained within a motherboard module or located on a motherboard. Figures 18A-18B include SPIP header assignments.

[00170] Referencing Figures 16A-16D, interface header connection points 1 through 200 are represented. Connection points on the 200 pin interface header route to various DPIP, SPIP, and processor debug headers on the motherboard, along with power and ground connections. As a point of clarification, each connection point on the interface header contains a reference label indicating the intended termination points. For instance, interface header pin 103 is assigned a reference label of DPIP5(2) (Figure 16B, 1610), indicating the termination point of this pin is the DPIP5 header, position 2. As seen in Figures 17A-17C, the physical connection between the motherboard interface header pin 103 and the DPIP5 header, pin 2 is indicated by a line drawn between the two connection points (Figure 17B, 1710). For SPIP headers (with reference to Figures 18A-18B), the termination points are indicated by global labels. For instance, interface header position 122 is assigned a global label of I2C-2 (Figure 16B, 1620). This same global label can be found in Figures 18A-18B at the I2C header, pin 2 (Figure 18A, 1810). The matching global labels (in this instance I2C-2) indicate a physical connection between the two points. This is functionally equivalent to the connecting lines utilized for DPIP headers. [00171] The connection points indicated in the Motherboard schematics is not to be confused with the Map Files nor processor termination points. The Motherboard schematics indicate the physical connections between the various headers and connectors on the Motherboard solely. Assignment of actual processor resources occurs on individual processor schematics. For instance, per the Generic Map File, the Dig1 header, pin 2 is assigned an analog to digital resource. When designing the processor board, it is known that the mating Processor Interface header pin position 154 routes to the Dig1 header, pin 2 (Figure 16C, 1630). The processor board must assign an analog to digital resource to this pin position (154) in order to make the analog to digital converter resource appear on the appropriate header and pin (Dig1 / pin 2). Referencing the Freescale processor schematic shown in Figures 19A-19C, it can be seen that

the mating processor board 200 pin connector, position 154, is assigned an analog to digital resource (processor pin position 67, resource ATD0-0, **Figure 19B, 1910**).

[00172] In summary, the motherboard contains static, processor agnostic, connections with all processor related interfaces routing to a 200 pin interface connector. The mate to this 200 pin connector is attached a processor board. Resources are allocated to various motherboard connectors and headers on the processor board. It is here where specific resource types and quantities are routed to the processor board 200 pin connector. Upon mating a specific processor board with the motherboard, the circuit is completed for attachment of specific resources to various motherboard headers (SPIP) and connectors (DPIP).

[00173] Figure 20 is the front view of a PIEP motherboard, under an alternative embodiment. The top of the motherboard includes a power input (DC 9V-24V) 2005, a +5V supply indicator 2010, a +5V/+3.3V peripheral voltage select 2015, and a +3.3V supply indicator 2020. The top of the motherboard also includes SPIP peripherals 2062, 2064, 2066, 2068, 2070, 2072, 2074, 2076, 2078, 2080, 2082, and 2084. Note that under this embodiment paired headers (e.g., 2062, 2064) can not be used concurrently. The peripheral orientation determines which header (of the pair) may be utilized for specific application. The top of the motherboard also includes a JTAG-20 Debug / Programming Interface 2045, a 6 pin Debug / ICD header 2055, and a processor mounting hole 2057. The top of the motherboard includes DPIP supplemental signal connectors 2002, 2004, 2006, 2040.