## (19)中华人民共和国国家知识产权局

# (12)发明专利

(10)授权公告号 CN 106059574 B (45)授权公告日 2020.04.07

(21)申请号 201510775895.0

(22)申请日 2015.11.13

(65)同一申请的已公布的文献号 申请公布号 CN 106059574 A

(43)申请公布日 2016.10.26

(30)优先权数据 14/690,085 2015.04.17 US

(73)专利权人 台湾积体电路制造股份有限公司

(73)专利权人 台湾积体电路制造股份有限公司 地址 中国台湾新竹

(72)发明人 刘智民 张秦豪

(74)专利代理机构 北京德恒律治知识产权代理 有限公司 11409

代理人 章社杲 李伟

(51) Int.CI.

*H03L* 7/099(2006.01) *H03L* 7/18(2006.01)

(56)对比文件

JP 特开2002-314413 A,2002.10.25,全文.

CN 102422526 A,2014.04.18,全文.

US 2007/0075785 A1,2007.04.05,说明书 第[0002]-[0084]段,附图1-11.

审查员 周丹

权利要求书2页 说明书15页 附图15页

## (54)发明名称

用于数字化相位差的电路、PLL电路及用于 其的方法

#### (57)摘要

本发明公开了一种锁相环(PLL)电路。PLL电路包括:检测电路,被配置为检测数字化控制振荡器(DCO)时钟信号与参考时钟信号之间的相位差,并且基于检测的相位差来生成差分信号;数字化差分生成器,耦合至检测电路,并且被配置为基于差分信号来生成控制码;以及DCO,被配置为响应于数字化差分生成器的控制码而生成DCO输出信号;其中检测电路、数字化差分生成器和DCO形成闭合环路并且减小了DCO输出信号与参考时钟信号之间的相位差。还公开了相关的方法和电路。

1.一种锁相环(PLL)电路,包括:

检测电路,被配置为检测数字化控制振荡器 (DCO) 输出信号与参考时钟信号之间的相位差,并且基于检测的相位差生成差分信号;

数字化差分生成器,耦合至所述检测电路,并且被配置为基于所述差分信号生成控制码;以及

数字化控制振荡器,被配置为响应于所述数字化差分生成器的控制码而生成数字化控制振荡器输出信号:

其中,所述检测电路、所述数字化差分生成器和所述数字化控制振荡器形成闭合环路 并且减小所述数字化控制振荡器输出信号与所述参考时钟信号之间的相位差,

其中,所述差分信号包括信号UP和信号DN,当所述数字化控制振荡器输出信号滞后于 所述参考时钟信号时,所述信号UP用于反映所述相位差,并且当所述数字化控制振荡器输 出信号超前于所述参考时钟信号时,所述信号DN用于反映所述相位差,

其中,所述数字化差分生成器包括具有第一锁存器的UP锁存器链和具有第二锁存器的DN锁存器链,所述UP锁存器链传播所述信号UP的第一脉冲的起始沿直到所述UP锁存器链响应于所述第一脉冲的结束沿而被禁用,所述DN锁存器链传播所述信号DN的第二脉冲的起始沿直到所述DN锁存器链响应于所述第二脉冲的结束沿而被禁用,所述UP锁存器链的所述第一锁存器的输出和所述DN锁存器链的所述第二锁存器的输出形成所述控制码。

- 2.根据权利要求1所述的锁相环电路,其中,由所述数字化差分生成器引起的延时小于 所述参考时钟信号的工作周期。

- 3.根据权利要求1所述的锁相环电路,其中,由所述UP锁存器链引起的延时小于所述参考时钟信号的工作周期,并且由所述DN锁存器链引起的延时小于所述参考时钟信号的工作周期。

- 4.根据权利要求1所述的锁相环电路,其中,所述数字化差分生成器还包括耦合至所述 UP锁存器链的UP延迟链和耦合至所述DN锁存器链的DN延迟链。

- 5.根据权利要求4所述的锁相环电路,其中,所述信号UP和所述信号DN都基于置位期间的复位延迟来确定由所述UP延迟链引起的延时和由所述DN延迟链引起的延时。

- 6.根据权利要求1所述的锁相环电路,其中,当所述UP锁存器链被禁用时,所述UP锁存器链锁存UP温度计码,并且当所述DN锁存器链被禁用时,所述DN锁存器链锁存DN温度计码。

- 7.根据权利要求6所述的锁相环电路,其中,所述数字化差分生成器还包括:UP码转换器,被配置为将所述UP温度计码转换为UP二进制码;和DN码转换器,被配置为将所述DN温度计码转换为DN二进制码。

- 8.根据权利要求1所述的锁相环电路,其中,响应于所述参考时钟信号的工作周期的结束,所述UP锁存器链和所述DN锁存器链被复位。

- 9.根据权利要求1所述的锁相环电路,还包括:锁存器级,耦合在所述数字化差分生成器与所述数字化控制振荡器之间,其中,当所述锁存器级响应于所述参考时钟信号的工作周期的结束而被禁用时,所述控制码锁存在所述锁存器级中。

- 10.根据权利要求1所述的锁相环电路,还包括:环路滤波器,耦合在所述数字化差分生成器与所述数字化控制振荡器之间,其中,所述环路滤波器包括:平滑滤波电路,被配置为使所述数字化差分生成器生成的控制码平滑。

- 11.根据权利要求10所述的锁相环电路,其中,所述环路滤波器包括比例积分微分 (PID) 控制器。

- 12.根据权利要求1所述的锁相环电路,还包括:频率检测器,被配置为检测所述数字化控制振荡器输出信号与所述参考时钟信号之间的频率差,并且使所述数字化控制振荡器调节所述数字化控制振荡器输出信号,以减小所述数字化控制振荡器输出信号与所述参考时钟信号之间的频率差。

- 13.根据权利要求1所述的锁相环电路,还包括:分频器,耦合在所述数字化控制振荡器与所述检测电路之间。

- 14.一种锁相环电路的工作方法,包括:

检测数字化控制振荡器 (DC0) 输出信号与参考时钟信号之间的相位差,并且基于检测的相位差生成差分信号:

基于所述差分信号生成控制码;以及

响应于所述控制码生成所述数字化控制振荡器输出信号,

其中,所述控制码使所述数字化控制振荡器输出信号被调节,以减小所述数字化控制振荡器输出信号与所述参考时钟信号之间的相位差,

其中,基于所述差分信号生成所述控制码包括:通过锁存器链传播所述差分信号的第一脉冲的起始沿直到所述锁存器链响应于所述第一脉冲的结束沿而被禁用。

- 15.根据权利要求14所述的锁相环电路的工作方法,其中,由基于所述差分信号生成的控制码引起的延时小于所述参考时钟信号的工作周期。

- 16.根据权利要求14所述的锁相环电路的工作方法,其中,由所述锁存器链引起的延时小于所述参考时钟信号的工作周期。

- 17.根据权利要求16所述的锁相环电路的工作方法,其中,所述锁存器链锁存温度计码,并且基于所述差分信号生成所述控制码还包括将所述温度计码转换为二进制码。

- 18.一种锁相环电路,包括:

检测电路,被配置为检测第一时钟信号与第二时钟信号之间的相位差,并且基于检测的相位差生成差分信号;以及

数字化差分生成器,耦合至所述检测电路,并且被配置为基于所述差分信号生成控制码,

其中,所述差分信号包括信号UP和信号DN,当所述第一时钟信号滞后于所述第二时钟信号时,所述信号UP用于反映所述相位差,并且当所述第一时钟信号超前于所述第二时钟信号时,所述信号DN用于反映所述相位差,

其中,所述数字化差分生成器包括具有第一锁存器的UP锁存器链和具有第二锁存器的DN锁存器链,所述UP锁存器链传播所述信号UP的第一脉冲的起始沿直到所述UP锁存器链响应于所述第一脉冲的结束沿而被禁用,所述DN锁存器链传播所述信号DN的第二脉冲的起始沿直到所述DN锁存器链响应于所述第二脉冲的结束沿而被禁用,所述UP锁存器链的所述第一锁存器的输出和所述DN锁存器链的所述第二锁存器的输出形成所述控制码。

19.根据权利要求18所述的锁相环电路,其中,由所述数字化差分生成器引起的延时小于所述第二时钟信号的工作周期。

# 用于数字化相位差的电路、PLL电路及用于其的方法

#### 技术领域

[0001] 本发明一般地涉及半导体技术领域,更具体地,涉及锁相环电路及其操作方法。

## 背景技术

[0002] 在先进的高密度半导体制造工艺中,建议减少电容器和电阻器的数量。这样,因为模拟锁相环电路通常需要比数字锁相环(DPLL)电路或全数字锁相环(ADPLL)电路更多的电容器和电阻器,所以采用DPLL或ADPLL电路来代替模拟锁相环电路以用于合适的应用。ADPLL电路可以包括数字相位检测器(也被称为数字相位比较器),以检测数字化控制振荡器(DCO)信号与参考时钟信号之间的相位差。响应于检测的相位差,数字相位检测器生成调节DCO的控制信号。结果,可以在闭合环路中消除DCO信号与参考时钟信号之间的偏移(skew)。

[0003] 为了实现高精确度,诸如基于时间-数字转换器(TDC)的DPLL电路的一些现有的ADPLL或DPLL电路具有复杂的结构并且通常比PLL电路消耗更多的功率。采用继电器式(bang-bang)相位检测器(BBPD)的PLL电路易于设计并且比基于TDC的PLL电路简单,但是不幸的是,相关应用由于BBPD的较差的抖动性能而受到限制。

## 发明内容

[0004] 为了解决现有技术中所存在的缺陷,根据本发明的一方面,提供了一种锁相环(PLL)电路,包括:检测电路,被配置为检测数字化控制振荡器(DCO)时钟信号与参考时钟信号之间的相位差,并且基于检测的相位差生成差分信号;数字化差分生成器,耦合至所述检测电路,并且被配置为基于所述差分信号生成控制码;以及DCO,被配置为响应于所述数字化差分生成器的控制码而生成DCO输出信号;其中,所述检测电路、所述数字化差分生成器和所述DCO形成闭合环路并且减小所述DCO输出信号与所述参考时钟信号之间的相位差。

[0005] 在该PLL电路中,由所述数字化差分生成器引起的延时小于所述参考时钟信号的工作周期。

[0006] 在该PLL电路中,所述差分信号包括信号UP和信号DN,当所述DCO输出信号滞后于 所述参考时钟信号时,所述信号UP用于反映所述相位差,并且当所述DCO输出信号超前于所 述参考时钟信号时,所述信号DN用于反映所述相位差。

[0007] 在该PLL电路中,所述数字化差分生成器包括UP锁存器链和DN锁存器链,所述UP锁存器链传播所述信号UP的第一脉冲的起始沿直到所述UP锁存器链响应于所述第一脉冲的结束沿而被禁用,所述DN锁存器链传播所述信号DN的第二脉冲的起始沿直到所述DN锁存器链响应于所述第二脉冲的结束沿而被禁用,所述UP锁存器链的锁存器的输出和所述DN锁存器链的锁存器的输出形成所述控制码。

[0008] 在该PLL电路中,由所述UP锁存器链引起的延时小于所述参考时钟信号的工作周期,并且由所述DN锁存器链引起的延时小于所述参考时钟信号的工作周期。

[0009] 在该PLL电路中,所述数字化差分生成器还包括耦合至所述UP锁存器链的UP延迟

链和耦合至所述DN锁存器链的DN延迟链。

[0010] 在该PLL电路中,基于所述信号UP和所述信号DN都置位期间的复位延迟来确定由所述UP延迟链引起的延时和由所述DN延迟链引起的延时。

[0011] 在该PLL电路中,当所述UP锁存器链被禁用时,所述UP锁存器链保持UP温度计码,并且当所述DN锁存器链被禁用时,所述DN锁存器链保持DN温度计码。

[0012] 在该PLL电路中,所述数字化差分生成器还包括:UP码转换器,被配置为将所述UP 温度计码转换为UP二进制码;和DN码转换器,被配置为将所述DN温度计码转换为DN二进制码。

[0013] 在该PLL电路中,响应于所述参考时钟信号的工作周期的结束,所述UP锁存器链和 所述DN锁存器链被复位。

[0014] 该PLL电路还包括:锁存器级,耦合在所述数字化差分生成器与所述DCO之间,其中,当所述锁存器级响应于所述参考时钟信号的工作周期的结束而被禁用时,所述控制码维持在所述锁存器级中。

[0015] 该PLL电路还包括:环路滤波器,耦合在所述数字化差分生成器与所述DC0之间,其中,所述环路滤波器包括:平滑滤波电路,被配置为使所述数字化相位差生成器生成的控制码平滑。

[0016] 在该PLL电路中,所述环路滤波器包括比例积分微分(PID)控制器。

[0017] 该PLL电路还包括:频率检测器,被配置为检测所述DCO输出信号与所述参考时钟信号之间的频率差,并且使所述DCO调节所述DCO输出信号,以减小所述DCO输出信号与所述参考时钟信号之间的频率差。

[0018] 该PLL电路还包括:分频器,耦合在所述DCO与所述检测电路之间。

[0019] 根据本发明的另一方面,提供了一种方法,包括:检测DCO输出信号与参考时钟信号之间的相位差,并且基于检测的相位差生成差分信号;基于所述差分信号生成控制码;以及响应于所述控制码生成所述DCO输出信号,其中,所述控制码使所述DCO输出信号被调节,以减小所述DCO输出信号与所述参考时钟信号之间的相位差。

[0020] 在该方法中,由基于所述差分信号生成的控制码引起的延时小于所述参考时钟信号的工作周期。

[0021] 在该方法中,基于所述差分信号生成所述控制码包括:通过锁存器链传播所述差分信号的第一脉冲的起始沿直到所述锁存器链响应于所述第一脉冲的结束沿而被禁用,并且由所述锁存器链引起的延时小于所述参考时钟信号的工作周期。

[0022] 在该方法中,所述锁存器链保持温度计码,并且基于所述差分信号生成所述控制码还包括将所述温度计码转换为二进制码。

[0023] 根据本发明的又一方面,提供了一种电路,包括:检测电路,被配置为检测第一时钟信号与第二时钟信号之间的相位差,并且基于检测的相位差生成差分信号;以及数字化差分生成器,耦合至所述检测电路,并且被配置为基于所述差分信号生成控制码。

[0024] 在该电路中,由所述数字化差分生成器引起的延时小于所述第二时钟信号的工作周期。

## 附图说明

[0025] 当结合附图进行阅读时,根据下面详细的描述可以更好地理解本发明的各个方面。应该强调的是,根据工业中的标准实践,各种部件没有被按比例绘制。实际上,为了清楚的讨论,各种部件的尺寸可以被任意增加或减少。

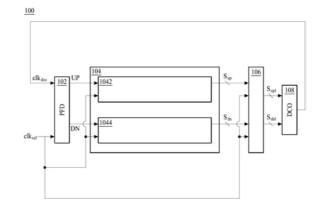

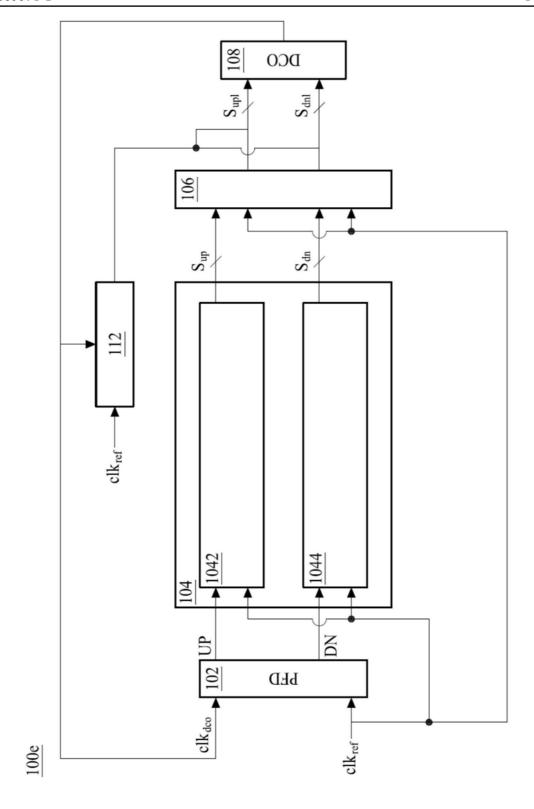

[0026] 图1是示出根据本发明的一个或多个方面的PLL电路的示图;

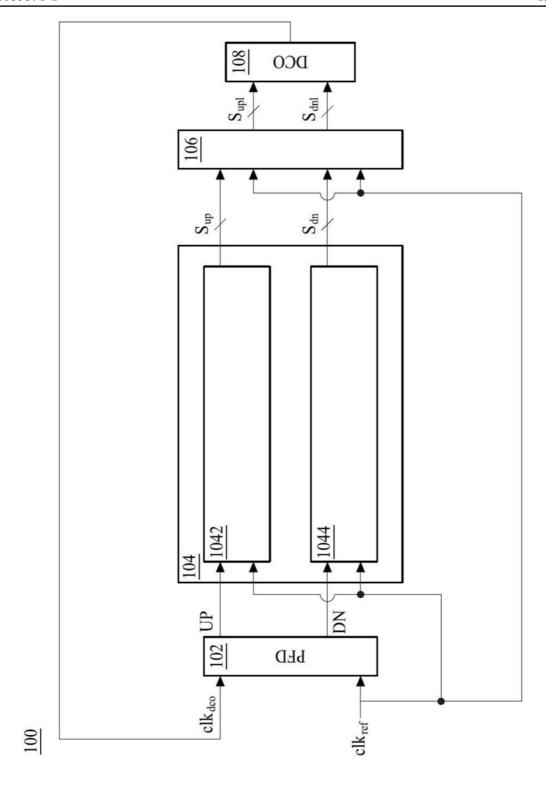

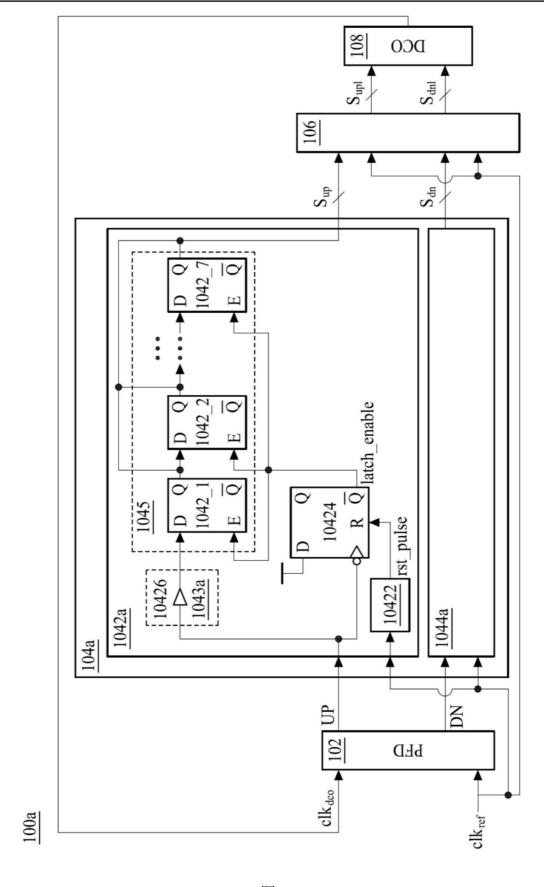

[0027] 图2是示出根据本发明的一个或多个方面的PFD的操作的时序图;

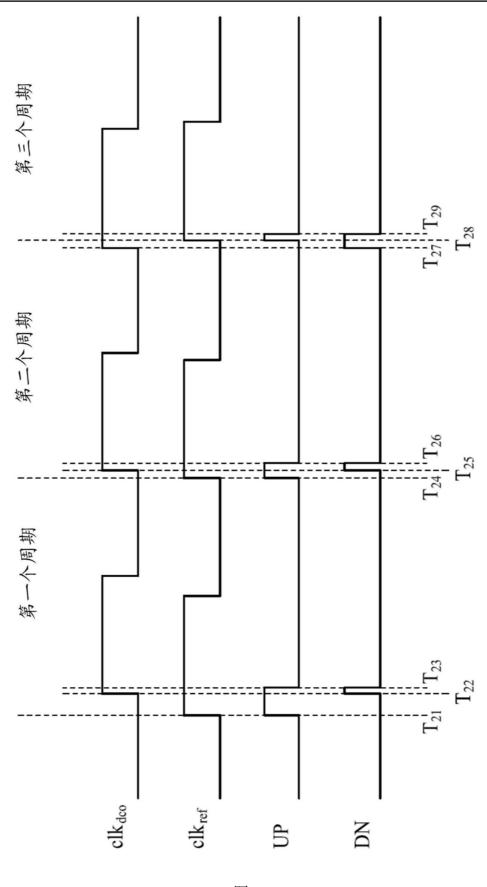

[0028] 图3是示出根据本发明的一个或多个方面的具有数字化相位差生成器的一个实施方式的PLL电路的示图:

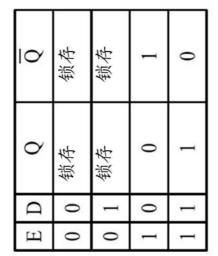

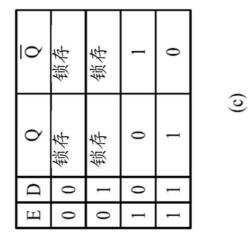

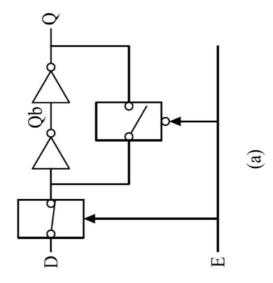

[0029] 图4-1是示出根据本发明的方面的D型锁存器的内部逻辑和真值表的示图;

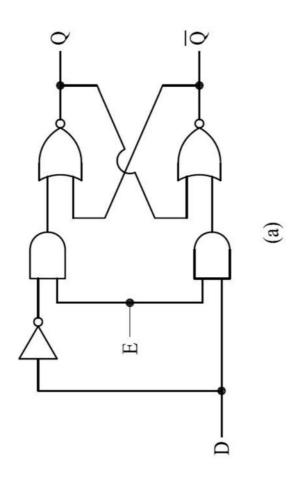

[0030] 图4-2是示出根据本发明的另一方面的D型锁存器的内部逻辑和真值表的示图;

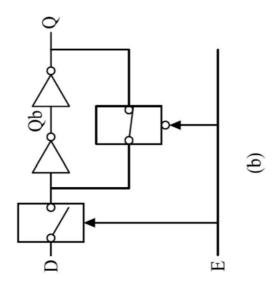

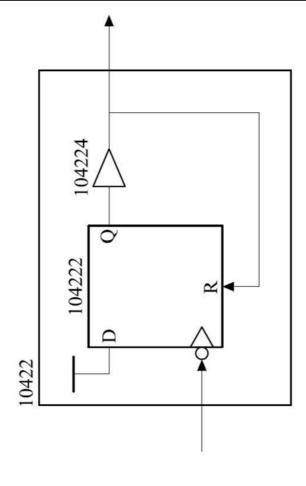

[0031] 图5是示出根据本发明的一个或多个方面的复位单元的示图;

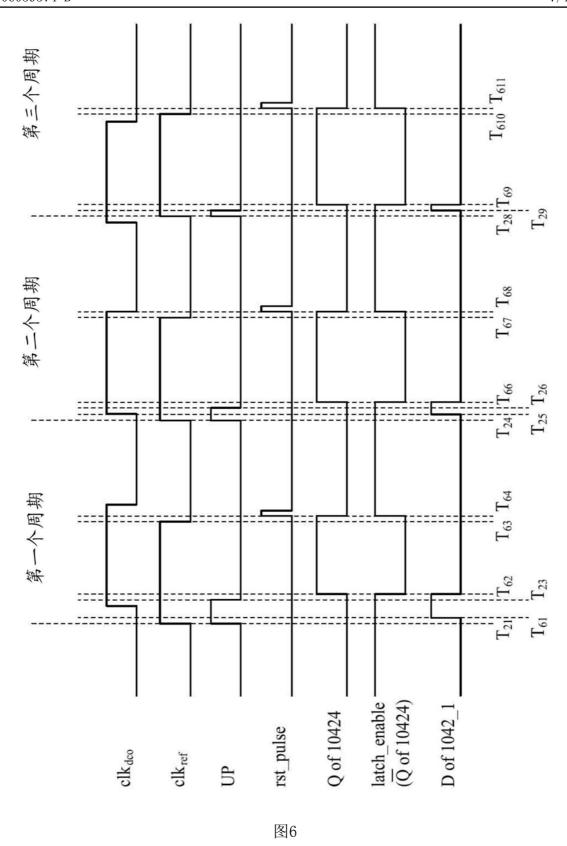

[0032] 图6是示出根据本发明一个或多个方面的复位单元、D型触发器和延迟链的操作的时序图;

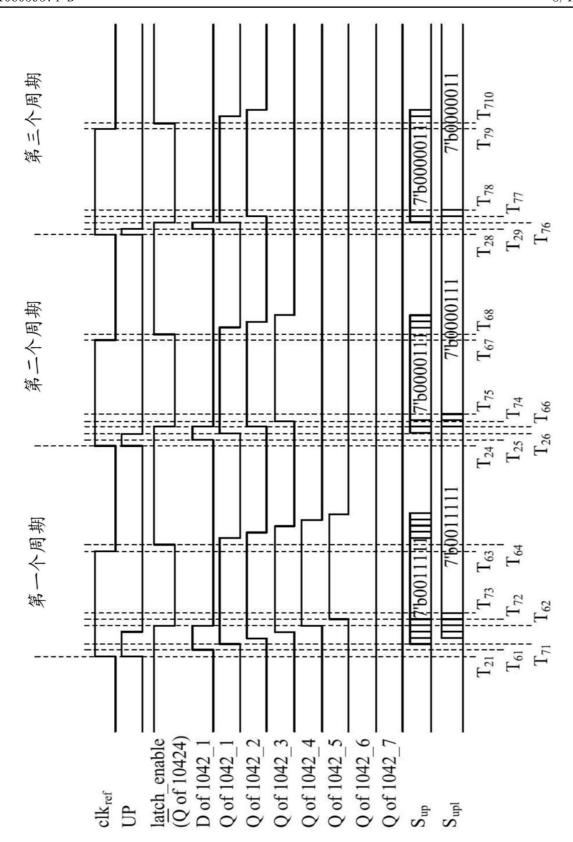

[0033] 图7是示出根据本发明的一个或多个方面的模块的锁存器链和锁存器级的操作的时序图:

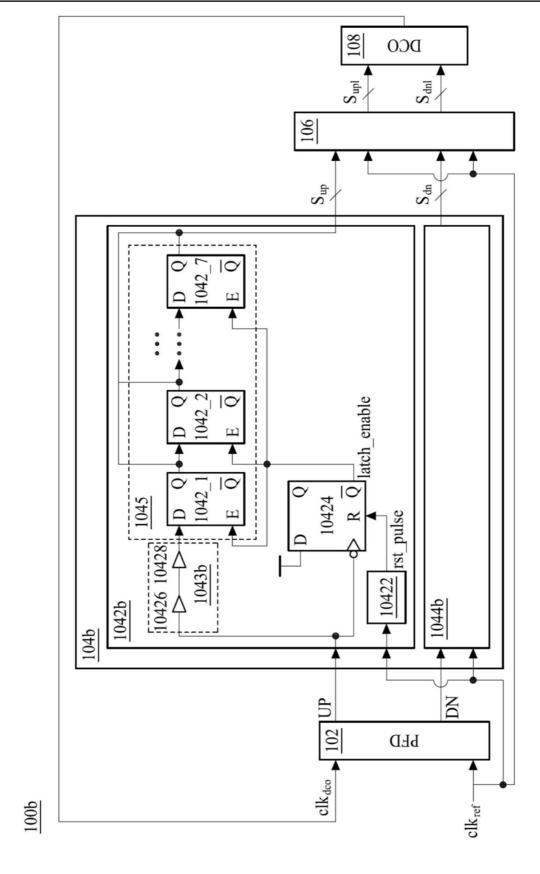

[0034] 图8是示出根据本发明的一个或多个方面的具有数字化相位差生成器的另一实施方式的PLL电路的示图:

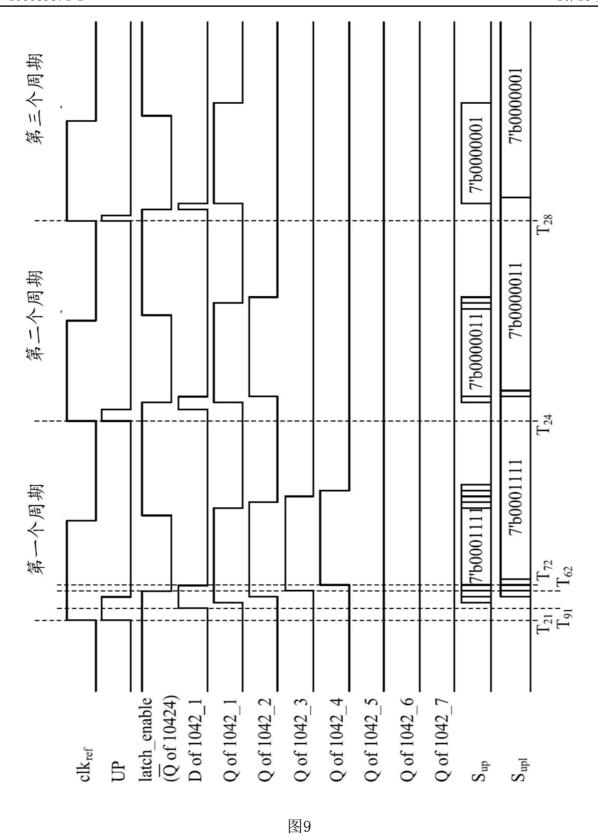

[0035] 图9是示出根据本发明的一个或多个方面的图8的模块的操作的时序图;

[0036] 图10是示出根据本发明的其他方面的PLL电路的示图:

[0037] 图11是图10中的转换器使用的温度计码至二进制码的示例性转换表;

[0038] 图12是示出根据本发明的又一方面的PLL电路的示图;

[0039] 图13是示出根据本发明的又一方面的PLL电路的示图;以及

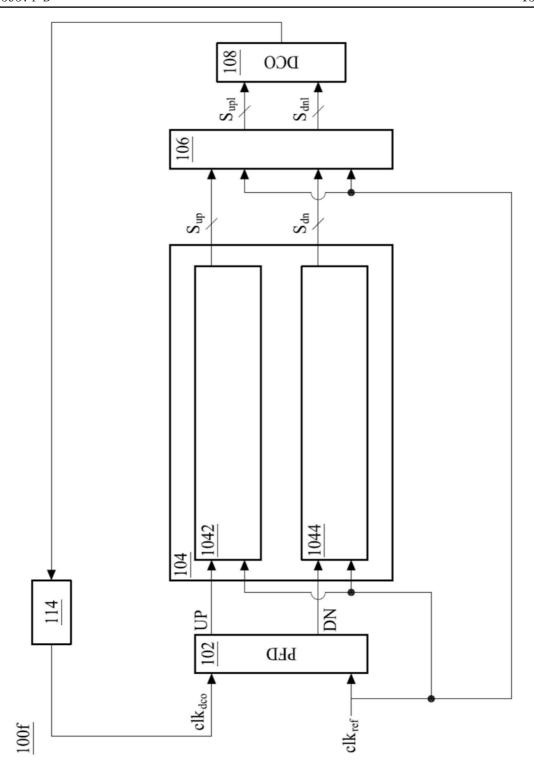

[0040] 图14是示出根据本发明的又一方面的PLL电路的示图。

## 具体实施方式

[0041] 以下公开内容提供了许多不同实施例或实例,用于实现本发明的不同特征。以下将描述组件和布置的特定实例以简化本发明。当然,这些仅是实例并且不意欲限制本发明。例如,在以下描述中,在第二部件上方或上形成第一部件可以包括第一部件和第二部件形成为直接接触的实施例,也可以包括形成在第一部件和第二部件之间的附加部件使得第一部件和第二部件不直接接触的实施例。另外,本发明可以在多个实例中重复参考标号和/或字符。这种重复是为了简化和清楚的目的,并且其本身不指示所讨论的各个实施例和/或配置之间的关系。

[0042] 此外,为了便于描述,本文中可以使用诸如"在…下方"、"在…下面"、"下部"、 "在…上面"、"上部"等空间关系术语以描述如图所示的一个元件或部件与另一个(多个)元件或部件的关系。除图中所示的方位之外,空间关系术语意欲包括使用或操作过程中的器件的不同的方位。装置可以以其它方式定位(旋转90度或在其他方位),并且在本文中使用的空间关系描述符可同样地作相应地解释。

[0043] 尽管阐述本发明的宽范围的数值范围和参数是近似值,但是尽可能精确地报告具体实例中阐述的数值。然而,由于相应的测试测量结果中存在标准偏差,所以任何数值固有

地必然包含一定误差。而且,如本文所使用的,术语"大约"通常表示在给定值10%、5%、1%或0.5%或给定范围内。可选地,在本领域的普通技术人员应该理解,术语"大约"表示在可接受的平均数的标准误差内。除了在操作/工作实例中,或者除非以其他方式明确地描述,本文所公开的诸如材料的数量、持续时间、温度、操作条件、比率的大小等的所有数值范围、数量、值和百分比应该被理解为在所有示例中通过"大约"进行修饰。因此,除非被指定为相反,否则本发明的公开内容和所附权利要求中阐述的数值参数是可以按期望变化的近似值。最起码,至少应该根据所报告的有效位的个数并且通过应用普通的四舍五入方法来解释每一个数值参数。本文可以将范围表述为从一个端点至另一个端点或介于两个端点之间。除非另有明确说明,否则本文所公开的所有范围都包括端点。

[0044] 一些实施例具有下文中的特征和/或优点的一个或组合。在各个实施例中,本发明涉及PLL的数字化结构。在一些实施例中,PLL电路包括:相位检测器,被配置为生成表示DCO输出信号与参考时钟信号之间的相位差的相位差信号;数字化相位差生成器,被配置为基于相位差信号的脉冲的脉冲宽度来生成控制码;以及DCO,被配置为生成具有与控制码相对应地调节相位的DCO输出信号。在一些实施例中,数字化相位差生成器包括:锁存器链,被配置为通过传播到达锁存器链的脉冲的起始沿生成控制码并且响应于脉冲的结束沿而停止传播起始沿。在一些实施例中,控制锁存器链的级数和每一级的延迟,使得相位差生成器的延时在参考时钟信号的半个周期内,并且PLL电路能够以适当的分辨率来测量足够的相位差的范围。例如,周期的另一半可以用于其他模块来提高PLL电路的锁定能力。因此,降低了PLL电路的环路延迟并且控制了锁存器链的级数,从而减小了电路尺寸和PLL电路的功耗。此外,在一些实施例中,使到达锁存器链的起始沿延迟,以提高测量脉冲的脉冲宽度的精确度并且增大锁存器链的表示能力。

[0045] 在与PLL的数字化结构相关的各个实施例中,可以以较高的分辨率和降低的环路延迟来执行相位调节。PLL的数字化结构能够在特定频率锁定范围内同时执行相位锁定和频率锁定。同时,所提出的结构包括具有合理级数的锁存器链,因此可以降低PLL的数字化结构的环路延迟、电路布局尺寸和功耗。下文将通过若干实施例和相关附图来更加详细地描述包括锁存器链的观点的本发明的构思。

## [0046] 数字化PLL结构的电路和操作

[0047] 图1是示出根据本发明的一个或多个方面的PLL电路100的示图。图1示出了具有数字化PLL结构的PLL电路的整体结构。在一些实施例中,PLL电路100是全数字锁相环(ADPLL)电路。术语"ADPLL"对应于采用DC0的电路,该DC0基于数字控制码产生模拟时钟信号。

[0048] PLL电路100是生成DCO输出信号c1kdco的控制系统,相对于输入参考时钟信号c1kref的相位来调节该DCO输出信号的相位。PLL电路100包括相位和频率检测器 (PFD) 102、数字化相位差生成器104、锁存器级106以及DCO 108。PFD 102用于接收DCO输出信号c1kdco和参考时钟信号c1kref,并且将DCO输出信号c1kdco的相位与参考时钟信号c1kref的相位进行比较,以及产生相位差信号。相位差信号包括一对信号,即,信号UP和信号DN,表示DCO输出时钟信号c1kdco与参考时钟信号c1kref之间的相位差的幅值和超前/滞后状态。数字化相位差生成器104用于接收信号UP和DN以及参考时钟信号c1kref,并且响应于参考时钟信号c1kref,生成与信号UP和DN相对应的一对数字化控制码 $S_{up}$ 和 $S_{dn}$ 。数字化相位差生成器104包括两个基本相同的模块1042和1044,这两个模块负责分别用于生成与信号UP相对应的数字

化控制码 $S_{up}$ 和生成与信号DN相对应的数字化控制码 $S_{dn}$ 。锁存器级106用于响应于参考时钟信号 $c1k_{ref}$ 而锁存控制码 $S_{up}$ 和 $S_{dn}$ 并且生成控制码 $S_{up1}$ 和 $S_{dn1}$ 。DCO 108用于接收控制码 $S_{up1}$ 和 $S_{dn1}$ 并且生成DCO输出信号 $c1k_{dco}$ ,其中基于控制码 $S_{up1}$ 和 $S_{dn1}$ 来调节该DCO输出信号的相位。反馈环路使DCO 108的输出信号 $c1k_{dco}$ 返回至PFD 102,以用于和参考时钟信号 $c1k_{ref}$ 进行比较并且形成如图1所示的闭合环路。以这种方式,PLL电路100能够消除DCO输出信号 $c1k_{dco}$ 与参考时钟信号 $c1k_{ref}$ 之间的偏移。将PLL电路100的DCO输出信号 $c1k_{dco}$ 的相位保持为与输入信号 $c1k_{ref}$ 匹配。

[0049] PLL电路100还保持DCO输出信号c1kdco的频率与输入信号c1kref的频率相同。可以在半导体集成电路中实施PLL电路100并且可以在诸如通信、计算机和其他的电子领域的各个应用中采用该PLL电路。PLL电路100可以用于在诸如微处理器的数字逻辑电路中解调信号、从噪声通信信道中恢复信号、生成具有多重输入频率的稳定频率(频率合成)或分配定时时钟脉冲。以上描述的PLL电路100的应用仅是示例性的,并且在本发明中,PLL电路100不限于此。其他应用中应用的类似PLL电路也落在本发明的预期范围内。

[0050] PFD 102用于检测两个输入信号clkdco与clkref之间的频率差和相位差并且产生一对信号UP和DN。在一些实施例中,基于在参考时钟信号clkref的周期内的DCO输出信号clkdco的上升沿的计数与参考时钟信号clkref的周期内的参考计数的差值来确定频率差。在一些实施例中,基于DCO输出信号clkdco的上升沿与参考时钟信号clkref的上升沿的相对到达来确定相位差。在一些实施例中,基于频率差和相位差之和来产生一对信号UP和DN。一对信号UP和DN调整DCO输出信号clkdco的频率和/或相位,以消除频率差和/或相位差。

[0051] 在示例性的情形中,消除了频率差,并且PFD 102产生表明DCO输出信号 $c1k_{dco}$ 和参考时钟信号 $c1k_{ref}$ 的上升沿的到达顺序的一对信号UP和DN,以表示相位差的超前/滞后状态。一对信号UP和DN具有与DCO输出信号 $c1k_{dco}$ 和参考时钟信号 $c1k_{ref}$ 的计时边沿之间的持续时间段正相关的脉冲宽度,以表示相位差的幅值。信号UP体现为表示DCO输出信号 $c1k_{dco}$ 的相位滞后于参考时钟信号 $c1k_{ref}$ 的相位。相反地,信号DN体现为表示DCO输出信号 $c1k_{dco}$ 的相位超前于参考时钟信号 $c1k_{ref}$ 的相位。当DCO输出信号 $c1k_{dco}$ 的相位对,信号UP的脉冲宽度与DCO输出信号 $c1k_{dco}$ 和参考时钟信号 $c1k_{ref}$ 的相位时,信号UP的脉冲宽度与DCO输出信号 $c1k_{ref}$ 的相位时,信号DN的脉冲宽度与DCO输出信号 $c1k_{ref}$ 的相位时,信号DN的脉冲宽度与DCO输出信号 $c1k_{ref}$ 的相位时,信号DN的脉冲宽度与DCO输出信号 $c1k_{ref}$

[0052] 用于减小频率差和相位差的具有不同结构的PLL电路100都在本发明的预期范围内。例如,在参考图13所要描述的其他实施例中,由相位检测器来代替PFD 102并且在PLL电路100e中附加地采用另一频率环路来减小频率差。

[0053] 图2是示出了根据本发明的一个或多个方面的PFD 102的操作的时序图。在图2所示的时序图中,假设在前两个周期处DC0输出信号clkdco滞后于参考时钟信号clkref,并且在第三个周期处DC0输出信号clkdco超前于参考时钟信号clkref。

[0054] PFD 102体现为上升沿触发。对于第一个周期,在时间 $T_{21}$ 处的参考时钟信号 $c1k_{ref}$ 的上升沿使信号UP在时间 $T_{21}$ 处被置位 (assert,又称有效)为正边沿。在时间 $T_{22}$ 处的DCO输出信号 $c1k_{dco}$ 的上升沿使信号DN在时间 $T_{22}$ 处被置位为正边沿。信号UP的置位早于信号DN的置位表明DCO输出信号 $c1k_{dco}$ 的相位滞后于参考时钟信号 $c1k_{ref}$ 的相位。时间 $T_{22}$ 处的DCO输出时钟信号 $c1k_{dco}$ 的上升沿和PFD 102的复位延迟使信号脉冲UP在时间 $T_{23}$ 处被复位

(deassert,又称清零,或者非置位)为负边沿。信号UP的脉冲宽度(即, $T_{21}$ 与 $T_{23}$ 之间的持续时间段)与时间 $T_{21}$ 与 $T_{22}$ 之间的持续时间段正相关,该时间 $T_{21}$ 与 $T_{22}$ 之间的持续时间段与DCO输出信号c1k<sub>dco</sub>和参考时钟信号c1k<sub>ref</sub>之间的相位差相对应。在一些实施例中,信号UP的脉冲宽度比时间 $T_{21}$ 与 $T_{22}$ 之间的持续时间段长介于时间 $T_{22}$ 与时间 $T_{23}$ 之间的复位延迟。复位延迟被称为信号UP和DN都保持被置位的时间段,诸如介于时间 $T_{22}$ 与时间 $T_{23}$ 之间的时间段。根据PFD 102的设计说明书(诸如,结构和元件延迟)来确定复位延迟的持续时间段。

[0055] 类似地,对于第二个周期,在时间 $T_{24}$ 处的参考时钟信号 $c1k_{ref}$ 的上升沿使信号UP在时间 $T_{24}$ 处被置位为正边沿。在时间 $T_{25}$ 处的DCO输出信号 $c1k_{dco}$ 的上升沿使信号DN在时间 $T_{25}$ 处被置位为的正边沿。信号UP的置位早于信号DN的置位表明DCO输出信号 $c1k_{dco}$ 的相位滞后于参考时钟信号 $c1k_{ref}$ 的相位。在第二个周期处,信号UP的置位时间段比参考时钟信号 $c1k_{ref}$ 与DCO输出信号 $c1k_{dco}$ 之间的相位差长介于时间 $T_{25}$ 与时间 $T_{26}$ 之间的复位延迟。与第一周期中的信号UP的脉冲宽度相比,第二周期中的信号UP的脉冲宽度(即,时间 $T_{24}$ 与时间 $T_{26}$ 之间的持续时间段)更短,这表明了DCO输出信号 $c1k_{dco}$ 与参考时钟信号 $c1k_{ref}$ 之间的相位差被减小。

[0056] 相反地,对于第三个周期,在时间 $T_{27}$ 处的DCO输出信号 $c1k_{dco}$ 的上升沿使信号DN在时间 $T_{27}$ 处被置位为正边沿。在时间 $T_{28}$ 处的参考时钟信号 $c1k_{ref}$ 的上升沿使信号UP在时间 $T_{28}$ 处被置位为正边沿。信号DN的置位早于信号UP的置位表明DCO输出信号 $c1k_{dco}$ 的相位超前于参考时钟信号 $c1k_{ref}$ 的相位。在第三个周期处,信号DN的置位时间段比参考时钟信号 $c1k_{ref}$ 与DCO输出信号 $c1k_{dco}$ 之间的相位差长介于时间 $T_{28}$ 与时间 $T_{29}$ 之间的复位延迟。

[0057] 在参考图3和图7所要描述的一些实施例中,测量复位延迟并且减去复位延迟,以确定DCO输出时钟信号 $c1k_{dco}$ 与参考时钟信号 $c1k_{ref}$ 之间的相位差。在参考图8和图9所要描述的其他实施例中,对于确定DCO输出时钟信号 $c1k_{dco}$ 与参考时钟信号 $c1k_{ref}$ 之间的相位差来说,复位延迟被抵消以避免被测量。

[0058] 具有不同结构的PFD在本发明的预期范围内。例如,PFD 102是下降沿触发的。对于另一个实例,PFD 102采用无复位延迟的结构。

[0059] 图3是示出根据本发明的一个或多个方面的具有数字化相位差生成器104的一种实施方式的PLL电路100a的示图。数字化相位差生成器104a是图1中的数字化相位差生成器104的一种实施方式。数字化相位差生成器104a包括两个基本相同的模块1042a和1044a,这两个模块负责分别用于生成与信号UP相对应的数字化控制码Sup和生成与信号DN相对应的数字化控制码Sdn。具体地,模块1042a产生温度计码Sup,其用数字码格式表示置位信号UP的脉冲宽度;并且模块1044a产生温度计码Sdn,其用数字码格式表示置位信号DN的脉冲宽度。数字化相位差生成器104a产生其他类型的编码以表示数字化相位差的PLL电路100a在本发明的预期范围内。例如,在参考图10所要描述的一些实施例中,数字化相位差生成器104c产生二进制码以表示数字化相位差。

[0060] 在一些实施例中,模块1042a包括复位单元10422、D型触发器10424、包括缓冲器10426的延迟链1043a和与延迟链1043a延迟链接的锁存器链1045。复位单元10422用于接收参考时钟信号clkref并且响应于参考时钟信号clkref的负边沿而生成复位脉冲rst\_pulse。D型触发器10424用于在复位输入端子R处接收复位脉冲rst\_pulse、在负边沿触发的时钟输入端子处接收信号UP并且在数据输入端子D处结接收高参考电压,以及在反相输出端子 $\overline{O}$

处生成锁存器使能信号latch\_enable。有效地,信号latch\_enable响应于信号UP的负边沿进行复位,并且响应于复位脉冲rst\_pulse的到达进行置位。与在基于信号UP来生成信号latch\_enable的延迟相对应地,延迟链1043a对发送至锁存器链1045的信号UP进行延迟。锁存器链1045用于通过延迟链1043a来接收信号UP并且接收信号latch\_enable,并且生成数字化控制码 $S_{up}$ ,该数字化控制码随着信号latch\_enable使能用于传播信号UP的置位的锁存器链1045而增大并且当信号latch\_enable禁用用于传播的锁存器链1045时而停止增大。

[0061] 在锁存器链1045中,D型锁存器1042\_1至1042\_7是串行级联的。D型锁存器1042\_1和1042\_7分别在输入端子E处接收信号1atch\_enable并且通过信号1atch\_enable共同使能/禁用以用于传递数据。D型锁存器1042\_1通过延迟链1043a接收信号UP。从D型锁存器1042\_1至1042\_7的端子Q处产生的输出总线连接在一起,以形成温度计控制码Sup。在一些实施例中,仅从D型锁存器1042\_1至1042\_7的端子Q处产生的部分输出形成控制码Sup。在一些实施例中,当温度计码Sup和Sdn进一步被转换为二进制码时,串行级联的锁存器的数量被配置为2<sup>n</sup>-1,其中n是正整数。以这种方式,温度计码Sup或Sdn的表示能力与二进制码的表示能力相对应。

[0062] 根据本发明的一个或多个方面,图4-1中(a)和(b)分别示出了图3中的诸如D型锁存器1042\_1至1042\_7的D型锁存器的内部逻辑和真值表。当D型锁存器被使能时,即,当输入端子E处的信号处于逻辑高电平状态,即二进制数"1"时,D型锁存器将输入端子D处的数据传播至输出端子Q。在本发明的一些实施例中所提及的D型锁存器的延迟是将来自输入端子D的数据传播至输出端子Q的延迟。当D型锁存器禁用时,即当输入端子E处的信号处于逻辑低电平状态,即二进制数"0"时,D型锁存器不允许输入端子D处的数据传播至输出端子Q并且响应于输入端子E处的信号从高至低的转变而在输出端子Q处提供锁存在输入端子D处的数据。然而,这并不是对本发明的限制。

[0063] 根据本发明的其他方面,图4-2示出了D型锁存器的内部逻辑和真值表。如图4-2中(a)所示,当通过使D型锁存器的输入端子E从逻辑低电平状态置位为逻辑高电平状态来使能D型锁存器时,响应于通过其中的两个反相器的另一个输入端子D,输出端子Q将会动作(act)。在本发明的一些实施例中所提及的D型锁存器的延迟是将来自输入端子D的数据传播至输出端子Q的延迟。此外,如图4-2中(b)所示,当通过使D型锁存器的输入端子E从逻辑高电平状态复位为逻辑低电平状态而禁用D型锁存器时,两个反相器和相关的电路形成闭合环路,以保持先前锁存的值。在图4-2中(c)中示出的对应的真值表与图4-1中(b)中的真值表基本相同。在一些实施例中,锁存器是门控SR锁存器。在一些实施例中,从其他类型的锁存器中选择该锁存器。

[0064] 锁存器链1045中其他类型的锁存器1042\_1、……或1042\_7或串行级联的级数在本发明的预期范围内。在一些实施例中,基于通过PLL电路100要覆盖的DCO输出信号c1kdco与参考时钟信号c1kref之间的相位差的范围来确定锁存器1042\_1、……或1042\_7的类型或串行级联的锁存器1042\_1至1042\_7的级数。在一些实施例中,通过每一个锁存器1042\_1、……或1042\_7的延迟来确定最小相位差。选择锁存器1042\_1至1042\_7的类型,使得PLL电路100将DCO输出信号c1kdco和参考时钟信号c1kref的相位与特定分辨率匹配。考虑到锁存器1042\_1至1042\_7的类型,通过锁存器链1045的级数来确定最大相位差。确定锁存器链1045的级数,使得PLL电路100在正常情况下在特定时间内实现频率和相位锁定。

[0065] 图5是示出根据本发明的一个或多个方面的复位单元10422的示图。复位单元10422包括D型触发器104222和延迟缓冲器104224。通过参考时钟信号 $c1k_{ref}$ 的负边沿来触发D型触发器104222。由复位单元10422产生的复位脉冲rst\_pulse具有通过延迟缓冲器104224的延迟所确定的宽度。参考图1描述的锁存器级106包括与参考图4—1和图4—2所描述的锁存器类似的锁存器,以响应于参考时钟信号 $c1k_{ref}$ 而锁存控制码 $S_{up}$ 和 $S_{dn}$ 。锁存器级106中的每一个锁存器都在输入端子D处接收控制码 $S_{up}$ 和 $S_{dn}$ 的比特位并且在输入端子E处接收参考时钟信号 $c1k_{ref}$ 。

[0066] 图6是示出根据本发明的一个或多个方面的模块1042a的复位单元10422、D型触发器10424和延迟链1043a的操作的时序图。对应于图2,在第一个周期和第二个周期中,DCO输出信号clkdco超前于参考时钟信号clkref,并且在第三个周期中,DCO输出信号clkdco超前于参考时钟信号clkref。在前两个周期中,生成信号UP的脉冲,以具有与DCO输出信号clkdco和参考时钟信号clkref的相位差正相关的脉冲宽度。在第三个周期中,生成信号UP的脉冲,以具有反映复位延迟的脉冲宽度。在信号UP的脉冲宽度的起始沿到达之前,由D型触发器10424生成的信号latch\_enable使能锁存器链1045以用于数据传播。响应于信号UP的脉冲宽度的结束沿,信号latch\_enable禁用用于数据传播的锁存器链1045。通过延迟要到达锁存器链1045的信号UP的延迟链1043a来抵消由于D型触发器10424的延迟而导致的信号UP脉冲的被测量的脉冲宽度的增大。通过复位单元10422来生成复位脉冲,以使信号latch\_enable被使能以用于能够测量信号UP的下一个脉冲宽度。

[0067] 对于第一个周期,使信号UP在时间T21处置位,并且在时间T23处复位。有效地,在时间T21处出现信号UP脉冲的起始沿,并且在时间T23处出现信号UP脉冲的结束沿。在时间T61处,D型触发器10424的输出端子Q处的信号处于低电平状态,并且D型触发器10424的反相输出端子 $\overline{Q}$ 处的信号(也是信号1atch\_enable)处于高电平状态。锁存器链1045被使能用于数据传播,以用于测量信号UP的脉冲宽度。响应于时间T23处的信号UP的下降沿,D型触发器10424在时间T62处使信号1atch\_enable复位,从而使用于数据传播的锁存器链1045禁用。介于时间T23与时间T62之间的延迟时间大约等于D型触发器10424的传播延迟时间。通过使用延迟链1043a将时间T21处置位的信号UP延迟为在时间T61处到达锁存器1042\_1的输入端子D来抵消这种延迟时间。响应于时间T63处的参考时钟信号clkref的下降沿,复位单元10422在时间T64处使复位脉冲rst\_pulse置位。响应于时间T64处的复位脉冲rst\_pulse的置位,D型触发器10424在时间T64处使信号1atch\_enable置位,从而使能锁存器链1045,以用于第二个周期中的数据传播。

[0068] 对于第二个周期,使信号UP在时间 $T_{24}$ 处置位,并且在时间 $T_{26}$ 处复位。有效地,在时间 $T_{24}$ 处出现信号UP的脉冲的起始沿,并且在时间 $T_{26}$ 处出现信号UP的脉冲的结束沿。在时间 $T_{24}$ 处,D型触发器 $T_{24}$ 处的信号处于低电平状态,并且D型触发器 $T_{24}$ 处的信号(也是信号 $T_{24}$ 处的信号处于低电平状态。锁存器链 $T_{24}$ 处的信号(也是信号 $T_{24}$ 处的信号(也是信号 $T_{26}$ 处的信号UP的下降沿,D型触发器 $T_{26}$ 处的信号UP的下降沿,D型触发器 $T_{26}$ 处的信号UP的下降沿,D型触发器 $T_{26}$ 处的信号UP的下降沿,D型触发器 $T_{26}$ 处的信号 $T_{26}$ 处使信号 $T_{26}$ 处使信号 $T_{26}$ 处的信号UP的传播延迟时间。通过使用延迟链 $T_{26}$ 与时间 $T_{26}$ 处信号UP的置位延迟为在时间 $T_{25}$ 处到达锁存器 $T_{26}$ 042  $T_{26}$ 04

来抵消这种延迟时间。响应于时间 $T_{67}$ 处的参考时钟信号 $c1k_{ref}$ 的下降沿,复位单元10422在时间 $T_{68}$ 处使复位脉冲 $rst_pulse$ 置位。响应于时间 $T_{68}$ 处的复位脉冲 $rst_pulse$ 的置位,D型触发器10424在时间 $T_{68}$ 处使信号 $latch_enable$ 置位,从而使能锁存器链1045,以用于第三个周期中的数据传播。

[0069] 对于第三个周期,使信号UP在时间 $T_{28}$ 处置位,并且在时间 $T_{29}$ 处复位。有效地,在时间 $T_{28}$ 处出现信号UP的脉冲的起始沿,并且在时间 $T_{29}$ 处出现信号UP的脉冲的结束沿。在时间 $T_{28}$ 处,D型触发器 $T_{28}$ 处的信号处于低电平状态,并且D型触发器 $T_{28}$ 处的信号(也是信号 $T_{28}$ 处的信号处于低电平状态,并且D型触发器 $T_{28}$ 处的信号(也是信号 $T_{28}$ 处的信号以外的信号UP的下降沿,D型触发器 $T_{28}$ 处的信号(也是信号 $T_{29}$ 处的信号UP的下降沿,D型触发器 $T_{29}$ 处的信号UP的下降沿,D型触发器 $T_{29}$ 处的信号UP的下降沿,D型触发器 $T_{29}$ 处的信号 $T_{29}$ 处的信号UP的严险。响应于时间 $T_{29}$ 处的信号UP的置位延迟为在时间 $T_{29}$ 处到达锁存器 $T_{28}$ 处的信号 $T_{29}$ 处的参考时钟信号 $T_{29}$ 处到达锁存器 $T_{29}$ 处的流域存器 $T_{29}$ 处的流域存器 $T_{29}$ 处的流域存器 $T_{29}$ 处的流域存器位的 $T_{29}$ 处的流域的 $T_{29}$ 处的

[0070] 在图3的实施例中,由于从PFD 102的输出到D型锁存器1042\_1的输入端子E的路径具有由D型触发器10424引起的附加延迟时间,所以延迟链1043a还用于平衡D型锁存器1042\_1的输入端子D和E之间的计时。换句话说,由于采用了具有与D型触发器10424大约相同的延迟时间的延迟链1043a来平衡两个计时路径的结构,所以更加精确地测量信号UP的脉冲宽度。请注意,这并不是对本发明的限制。在一些实施例中,通过其他的延迟元件来实施延迟链1043a。在一些实施例中,省略延迟链1043a。

[0071] 图7是示出根据本发明的一个或多个方面的模块1042a的锁存器链1045和锁存器级106的操作的时序图。对应于图6,信号UP的脉冲宽度从第一个周期至第三个周期减小,并且对于每一个周期,在信号UP的脉冲宽度的起始沿之前使能信号latch\_enable并且响应于信号UP的脉冲宽度的结束沿而禁用该信号。当信号latch\_enable使能用于数据传播的锁存器链1045时,到达锁存器1042\_1的输入端子D处的信号UP的脉冲宽度的起始沿沿着参考图3所描述的串行级联的锁存器1042\_1至1042\_7进行传播直到信号latch\_enable使用于数据传播的锁存器链1045禁用。随后,在锁存器1042\_1至1042\_7的输出端子Q处的控制码Sup可用。因此,与信号UP的脉冲宽度相对应地增大的控制码Sup是信号UP的脉冲宽度的数字化表示。响应于参考时钟信号clkref,锁存器级106锁存控制码Sup,使得控制码Sup在信号latch\_enable被使能之后仍然可用。锁存器级106为数字化相位差生成器104与DC0 108之间的附加的数字信号处理电路(诸如平滑滤波电路和/或比例积分微分(PID)控制器)提供更大的裕度(margin),将参考图12对其进行描述。

[0072] 对于第一个周期,在时间 $T_{61}$ 处到达锁存器 $1042_1$ 的输入端子D处的上升沿在时间  $T_{71}$ 处被传播至锁存器 $1042_1$ 的输出端子Q,该锁存器 $1042_1$ 的输出端子Q耦合至锁存器  $1042_2$ 的输入端子D。锁存器 $1042_1$ 至 $1042_2$ 7中的每一个的延时都基本上彼此相同。与锁存器  $1042_1$ 类似地,该上升沿通过锁存器 $1042_2$ 、 $1042_3$ 、 $1042_4$ 和 $1042_5$ 进行传播。在时间  $T_{62}$ 处,信号 1atch enable使用于数据传播的锁存器链1045禁用。另外,在时间162处,上升沿

到达锁存器1042\_5的输入端子D,该锁存器1042\_5的输入端子D耦合至锁存器1042\_4的输出端子Q。在时间 $T_{72}$ 处,上升沿传播至锁存器 $1042_{5}$ 的输出端子Q。因为锁存器链1045被禁用,所以未通过锁存器 $1042_{6}$ 和 $1042_{7}$ 传播上升沿。从锁存器 $1042_{7}$ 的Q、锁存器 $1042_{6}$ 的Q、锁存器 $1042_{5}$ 的输出端子Q,以形成控制码 $1042_{5}$ 以及实现,具有值 $1042_{5}$ 的位置的控制码 $1042_{5}$ 以形成控制码 $1042_{5}$ 以开始有效。在时间 $1042_{5}$ 以开始有效。在时间 $1042_{5}$ 以开始有效。在时间 $1042_{5}$ 以开始有效。在时间 $1042_{5}$ 以开始有效。在时间 $1042_{5}$ 以中的数据传播。

[0073] 对于第二个周期,时间T25处到达锁存器1042\_1的输入端子D处的上升沿在时间T26处传播至锁存器1042\_1的输出端子Q,该锁存器1042\_1的输出端子Q耦合至锁存器1042\_2的输入端子D。锁存器1042\_1至1042\_7中的每一个的延时都基本上彼此相同。与锁存器1042\_1类似地,上升沿通过锁存器1042\_2和1042\_3进行传播。在时间T66处,信号latch\_enable使用于数据传播的锁存器链1045禁用。另外,在时间T66处,上升沿到达锁存器1042\_3的输入端子D,该耦合锁存器1042\_3的输入端子D至锁存器1042\_2的输出端子Q。在时间T74处,上升沿传播至锁存器1042\_3的输出端子Q。因为锁存器链1045禁用,所以未通过锁存器1042\_4、1042\_5、1042\_6和1042\_7传播上升沿。从锁存器1042\_7的Q、锁存器1042\_6的Q、锁存器1042\_5的Q、锁存器1042\_7的输出端子Q,以形成控制码Sup。具有值7'b0000111的控制码Sup(其是温度计码)在时间T74处开始有效。在时间T75处,将控制码Sup传播至锁存器级106的输出以作为控制码Sup1。在时间T74处开始有效。在时间T75处,将控制码Sup传播至锁存器级106锁存控制码Sup1。在时间T65处,响应于参考时钟信号clkref的下降沿,锁存器级106锁存控制码Sup1。在时间T68处,信号latch\_enable使能锁存器链1045以用于第三个周期中的数据传播。

[0075] 在一些实施例中,例如,在第一个周期中,从所得到的信号UP的脉冲宽度中减去 PFD 102的复位延迟,还得到了图2中所示的第一个周期中的信号DN的脉冲宽度。类似地,如上所述,从图2中所示的第三个周期中所得到的信号DN的脉冲宽度中减去PFD 102的复位延

迟,得到第三个周期中的信号UP的脉冲宽度。在一些实施例中,DCO 108执行从控制码Sup或 Sdn中减去控制码Sdn1或Sup1。在其他实施例中,DCO 108之前的另一个模块(未在图1中示出)执行该减法。

[0076] 对于图7中的第一个周期、第二个周期和第三个周期中的每一个,在锁存器级106响应于参考时钟信号clkref的下降沿锁存控制码Sup之前,控制码Sup是有效的。另外,响应于参考时钟信号clkref的下降沿,信号latch\_enable使能锁存器链1045以用于下一周期中的数据传播。因此,参考图3所描述的数字化相位差生成器104的延时在参考时钟信号clkref的正工作周期(positive duty of a cycle)内,或者在参考时钟信号clkref的半个周期内。在一些实施例中,数字化相位差生成器104的延时包括延迟链1043a的延时和锁存器链1045。具体地,从参考时钟信号clkref的上升沿到信号UP的上升沿传播至锁存器链1045中的诸如锁存器1042\_7的最后一级的输出端子Q来测量数字化相位差生成器104的延时。在一些实施例中,DC0 108是生成模拟信号的数字化振荡器电路,通过供给DC0 108的数字控制码Supl和Sdnl来控制该数字化振荡器电路的频率和相位。在一些实施例中,DC0 108是压控振荡器和数字一模拟转换器的组合,其中通过由数字一模拟转换器从数字控制码Supl和Sdnl转换的控制信号来驱动压控振荡器。DC0 108的其他实施方式在本发明的预期范围内。例如,DC0 108包括可以根据数字控制码Supl和Sdnl来闭合或断开的串行级联的延迟级。

[0077] 在参考图1至图7所述的实施例中,控制锁存器链1045的级数和每一级的延迟,使得数字化相位差生成器104的延时小于参考时钟信号clkref的半个周期,并且所公开的结构能够测量从PFD 102产生的相位差的特定范围。由于控制了锁存器链1045中的级数,所以降低了功耗和硬件成本。此外,通过控制数字化相位差生成器104的延时,在闭合环路中,诸如PFD 102和DCO 108的其他现有模块的计时或参考图12所要描述的插接诸如平滑滤波电路的附加模块的计时是宽松的(relaxed),从而允许PLL电路100的进一步优化。

## [0078] 不测量复位延迟的配置

[0079] 图8是示出根据本发明的一个或多个方面的具有数字化相位差生成器104的另一实施方式的PLL电路100b的示图。数字化相位差生成器104b是图1中的数字化相位差生成器104的一种实施方式。数字化相位差生成器104b包括模块1042b和模块1044b。与图3中的数字化相位差生成器104a相比,数字化相位差生成器104b的延迟链1043b包括另一个缓冲器10428,使得消除参考图2所描述的复位延迟以避免测量用于确定DC0输出时钟信号clkdco与参考时钟信号clkref之间的相位差。在一些实施例中,缓冲器10428的延迟时间与信号UP和DN的复位延迟基本相同。

[0080] 图9是示出根据本发明的一个或多个方面的模块1042b的操作的时序图。与图7中的时序图相比,由于附加的缓冲器10428,所以时间 $T_{21}$ 处的信号UP的上升沿在图7中的时间 $T_{61}$ 之后的时间 $T_{91}$ 处到达锁存器 $1042_{-}$ 1的输入端子D。在与图7中的时间相同的时间 $T_{62}$ 处,信号1atch\_enable使用于数据传播的锁存器链禁用。因为延迟到达的信号UP的上升沿和未延迟的信号1atch\_enable与图7中所示出的相比较,上升沿仅传播至锁存器 $1042_{-}$ 4的输出端子Q。结果,图9的控制码 $S_{up}$ 具有值7'b0001111,其比图7的控制码 $S_{up}$ 7'b0011111小一个比特位。通过复位延迟抵消开始测量信号UP的脉冲宽度的时间,控制码 $S_{up}$ 中的用于表示信号UP的脉冲宽度中的复位延迟的一个比特位被释放,从而增大了控制码 $S_{up}$ 的表示能力。

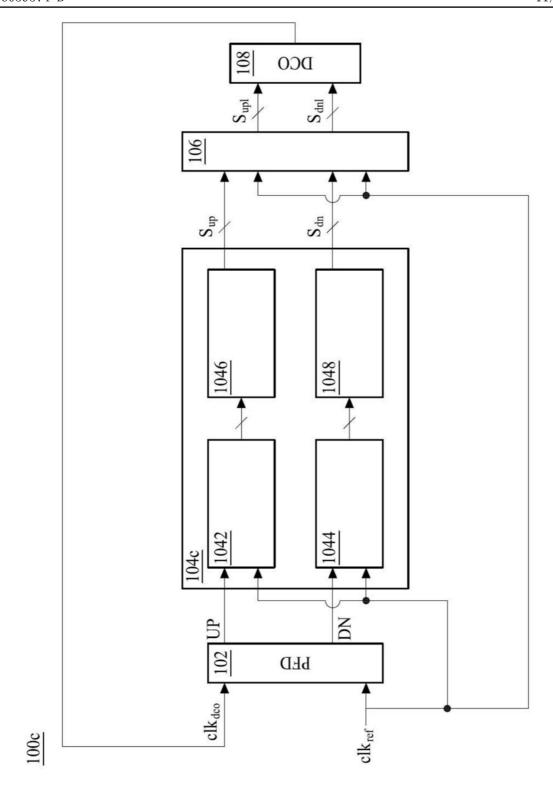

## [0081] 用于控制码转换的配置

[0082] 图10是示出根据本发明的其他方面的PLL电路100c的示图。与图1中的PLL电路100相比,PLL电路100c还包括温度计码-二进制码转换器1046和1048。温度计码-二进制码转换器1046耦合在模块1042的输出与接收控制码Sup的锁存器级106的输入之间。温度计码-二进制码转换器1048耦合在模块1044的输出与接收控制码Sdn的锁存器级106的输入之间。图11是图10中的转换器1046和1048使用的温度计码-二进制码的示例性转换表。在一些实施例中,为了将温度计码转换为二进制码,首先使用等式(1)将温度计码转换为独热码(one-hot code):

$$[0083] b_i = a_i \bullet \overline{a_{i+1}} (1)$$

[0084] 其中a是温度计码,b是独热码,并且i是第i个比特位。然后使用基于一组等式(2)的平顶树编码器(flat tree encoder)将独热码转换为二进制码:

$$c_0 = b_0 + b_2 + b_4 + b_6$$

[0085]

$$c_1 = b_1 + b_2 + b_5 + b_6$$

$$c_2 = b_3 + b_4 + b_5 + b_6$$

(2)

[0086] 其中b是独热码,c是二进制码,并且下标是比特位位置。

[0087] 其他的转换方法在本发明的预期范围内。例如,使用基于ROM的编码器将独热码转换为二进制码。用于表示控制码的其他格式在本发明的预期范围内。采用除了二进制码之外的编码(如,格雷码)作为DCO 108的输入数据格式。

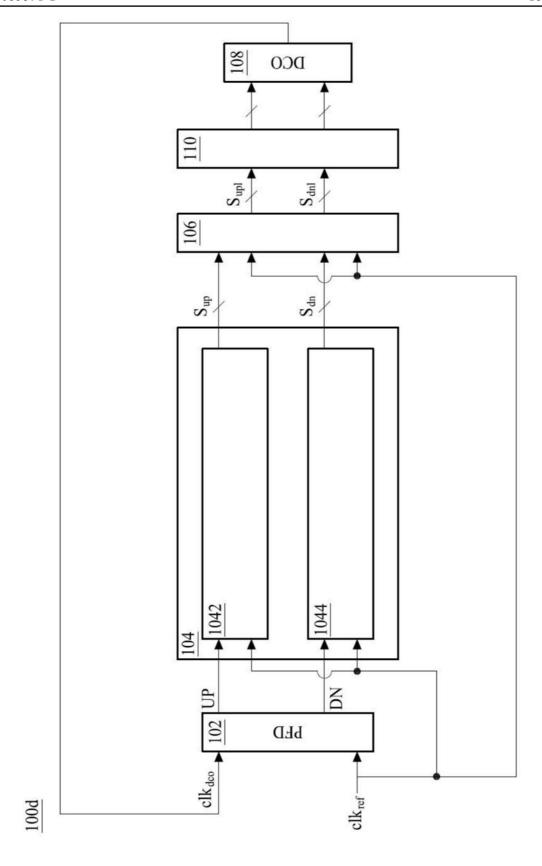

[0088] 用于环路滤波的配置

[0089] 图12是示出了根据本发明的又一其他方面的PLL电路100d的示图。与图1中的PLL电路100相比,PLL电路100d还包括耦合在锁存器级106与DC0 108之间的环路滤波器110。环路滤波器110用于接收控制码Supl和Sdnl,并且生成调节的控制码。在一些实施例中,环路滤波器110包括比例积分 (PI) 控制器。PI控制器中的比例路径使控制码Supl和Sdnl与比例增益相乘。PI控制器中的积分路径在一时间段内对控制码Supl和Sdnl进行积分并且使积分结果与积分增益相乘。对比例路径和积分路径的结果进行求和,以产生到达DCO 108的调节的控制码。当基于DCO输出信号clkdco与参考时钟信号clkref之间的频率差和相位差的和而确定的相位误差大于阈值时,控制环路滤波器110,以仅使能比例路径。通过禁用积分路径并且增大比例增益,在使DCO输出信号clkdco与参考时钟信号clkref的频率和相位相匹配的较早的阶段中实现了更快的锁定时间和更宽的环路带宽。当DCO输出信号clkdco与参考时钟信号clkref的频率和相位相匹配的较早的添加积分路径并且减小比例增益,在用于使DCO输出信号clkdco与参考时钟信号clkref的频率和相位匹配的较晚的阶段中实现了更小的环路带宽和更高的消除相位误差的能力。在一些实施例中,调整积分增益还有助于消除相位误差。

[0090] 环路滤波器的其他实施方式在本发明的预期范围内。例如,环路滤波器110还包括耦合在锁存器级106与PI控制器之间的平滑滤波电路。在一些实施例中,平滑滤波电路包括低通滤波器,该低通滤波器减弱寄生信号(spurious)(诸如通过数字化期间的量化导致的)和较高频率的相位噪声(诸如通过生成参考时钟信号clkref的晶体振荡器产生的)。又例如,环路滤波器110包括PID控制器。与PI控制器相比,PID控制器还包括微分路径。在一些实施例中,微分路径得到控制码Supl和Sdnl的变化速率并且使变化速率与微分增益相乘。对比例

路径、积分路径和微分路径的结果进行求和,以产生到达DCO 108的调节的控制码。在一些实施例中,通过添加微分路径,提高了PLL电路100d的稳定性。

[0091] 在一些实施例中,环路滤波器110在参考时钟信号clk<sub>ref</sub>的负工作周期期间完成目前周期(instant cycle)的工作。在实施例中,数字化相位差生成器104、锁存器级106和环路滤波器110的总延时在参考时钟信号clk<sub>ref</sub>的一个周期内,因此实现了小环路延迟。小环路延迟提高了闭合环路的稳定性。

[0092] 用于初始频率引入的不同配置

[0093] 图13是示出根据本发明的又一其他方面的PLL电路100e的示图。与图3中的PLL电路100相比,PLL电路100e还包括耦合在DC0 108的输入与输出之间的频率检测器112并且形成了除了主环路(即,穿过数字化相位差生成器104的环路)之外的另一个辅助闭合环路。在一些实施例中,频率检测器112用于接收DCO输出信号clkdco和参考时钟信号clkref,检测DCO输出信号clkdco与参考时钟信号clkref之间的频率差,以及生成输入至DC0 108的控制码Supl和Sdnl。由于表示频率差的控制码的不同分辨率,所以频率检测器112在与PFD 102相比能够在相对较短的时间内实现初始频率引入。另外,诸如当剧烈的温度变化引起劣化的抖动性能时,频率检测器112在引入较大的捕获范围方面的能力减少了主环路摆脱捕获范围的任何可能。在一些实施例中,在锁定的初始阶段或当PLL电路100e摆脱捕获范围时激活频率检测器112。在一些实施例中,当主环路稳定时,不激活频率检测器112。

[0094] 频率合成器的不同配置

[0095] 图14是示出根据本发明的又一其他的方面的PLL电路100f的示图。在一些实施例中,PLL电路100f用作频率合成器。与图1中的PLL电路100相比,PLL电路100f还包括添加在DC0 108与PFD 102之间的分频器114(也被称为时钟分频器)。分频器用于接收来自DC0 108的输出信号,用因子划分输出信号的频率,以及生成到达PFD 102的反馈输入信号。通过将来自DC0 108的输出信号的分频频率与参考时钟信号clkref的频率相匹配,DC0 108产生的输出信号的频率与参考时钟信号clkref以因子倍频的频率相等。在一些实施例中,分频器114的因子是可编程的,从而允许PLL电路110f合成不同的频率。

[0096] 本发明的一些实施例提供了锁相环(PLL)电路。PLL电路包括:检测电路,被配置为检测数字化控制振荡器(DCO)时钟信号与参考时钟信号之间的相位差,并且基于检测的相位差生成相位差信号;数字化差分生成器,耦合至检测电路,并且被配置为基于差分信号生成控制码;以及DCO,被配置为响应于数字化差分生成器的控制码而生成DCO输出信号;其中检测电路、数字化差分生成器和DCO形成闭合环路并且减小了DCO输出信号与参考时钟信号之间的相位差。

[0097] 在本发明的一些实施例中,由数字化差分生成器引起的延时小于参考时钟信号的工作周期(duty of cycle)。

[0098] 在本发明的一些实施例中,差分信号包括信号UP和信号DN,当DCO输出信号滞后于参考时钟信号时,信号UP用于反映相位差,并且当DCO输出信号超前于参考时钟信号时,信号DN用于反映相位差。

[0099] 在本发明的一些实施例中,数字化差分生成器包括UP锁存器链和DN锁存器链,UP锁存器链传播信号UP的第一脉冲的起始沿直到UP锁存器链响应于第一脉冲的结束沿而被禁用,DN锁存器链传播信号DN的第二脉冲的起始沿直到DN锁存器链响应于第二脉冲的结束

沿而被禁用,并且UP锁存器链的锁存器的输出和DN锁存器链的锁存器的输出形成控制码。

[0100] 在本发明的一些实施例中,由UP锁存器链引起的延时小于参考时钟信号的工作周期,并且由DN锁存器链引起的延时小于参考时钟信号的工作周期。

[0101] 在本发明的一些实施例中,数字化差分生成器还包括耦合至UP锁存器链的UP延迟链,和耦合至DN锁存器链的DN延迟链。

[0102] 在本发明的一些实施例中,基于信号UP和信号DN都置位期间的复位延迟来确定由UP延迟链引起的延时和由DN延迟链引起的延时。

[0103] 在本发明的一些实施例中,当UP锁存器链被禁用时,UP锁存器链保持UP温度计码,并且当DN锁存器链被禁用时,DN锁存器链保持DN温度计码。

[0104] 在本发明的一些实施例中,数字化差分生成器还包括:UP码转换器,被配置为将UP温度计码转换为UP二进制码;和DN码转换器,被配置为将DN温度计码转换为DN二进制码。

[0105] 在本发明的一些实施例中,响应于参考时钟信号的工作周期的结束,UP锁存器链和DN锁存器链被复位。

[0106] 在本发明的一些实施例中,PLL电路还包括耦合在数字化差分生成器与DCO之间的锁存器级,其中当响应于参考时钟信号的工作周期的结束而禁用锁存器级时,控制码维持在锁存器级中。

[0107] 在本发明的一些实施例中,PLL电路还包括耦合在数字化差分生成器与DC0之间的环路滤波器,其中环路滤波器包括:平滑滤波电路,被配置为使通过数字化相位差生成器生成的控制码平滑。

[0108] 在本发明的一些实施例中,环路滤波器包括比例积分微分(PID)控制器。

[0109] 在本发明的一些实施例中,PLL电路还包括:频率检测器,被配置为检测DCO输出信号与参考时钟信号之间的频率差,并且使DCO调节DCO输出信号,以减小DCO输出信号与参考时钟信号之间的频率差。

[0110] 在本发明的一些实施例中,PLL电路还包括耦合在DCO与检测电路之间的分频器。

[0111] 本发明的一些实施例提供一种方法。方法包括:检测DCO输出信号与参考时钟信号之间的相位差,并且基于检测的相位差来生成差分信号;基于差分信号来生成控制码;以及响应于控制码生成DCO输出信号,其中控制码使DCO输出信号被调节,以减小DCO输出信号与参考时钟信号之间的相位差。

[0112] 在本发明的一些实施例中,由基于差分信号生成的控制码引起的延时小于参考时钟信号的工作周期。

[0113] 在本发明的一些实施例中,基于差分信号生成控制码包括通过锁存器链传播差分信号的第一脉冲的起始沿,直到锁存器链响应于第一脉冲的结束沿而被禁用,并且由锁存器链引起的延时小于参考时钟信号的工作周期。

[0114] 在本发明的一些实施例中,锁存器链保持温度计码,并且基于差分信号生成控制码还包括将温度计码转换为二进制码。

[0115] 本发明的一些实施例提供一种电路。电路包括:检测电路,被配置为检测第一时钟信号与第二时钟信号之间的相位差,并且基于检测的相位差生成差分信号;以及数字化差分生成器,耦合至检测电路,并且被配置为基于差分信号生成控制码。

[0116] 在本发明的一些实施例中,由数字化差分生成器引起的延时小于参考时钟信号的

工作周期。

[0117] 上面论述了若干实施例的部件,使得本领域普通技术人员可以更好地理解本发明的各个方面。本领域普通技术人员应该理解,可以很容易地使用本发明作为基础来设计或更改其他用于达到与这里所介绍实施例相同的目的和/或实现相同优点的处理和结构。本领域普通技术人员也应该意识到,这种等效构造并不背离本发明的精神和范围,并且在不背离本发明的精神和范围的情况下,可以进行多种变化、替换以及改变。

图1

图3

图4-1

图4-2

图5

图7

图8

图10

| 二进制码 | 温度计码    |

|------|---------|

| 000  | 0000000 |

| 001  | 0000001 |

| 010  | 0000011 |

| 011  | 0000111 |

| 100  | 0001111 |

| 101  | 0011111 |

| 110  | 0111111 |

| 111  | 1111111 |

图11

图12

图13

图14