#### (19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第4825459号 (P4825459)

(45) 発行日 平成23年11月30日(2011.11.30)

(24) 登録日 平成23年9月16日 (2011.9.16)

| (51) Int.Cl. |        |           | FΙ   |        |      |         |          |

|--------------|--------|-----------|------|--------|------|---------|----------|

| HO1L         | 21/22  | (2006.01) | HO1L | 21/22  | 501L |         |          |

| HO1L         | 21/26  | (2006.01) | HO1L | 21/26  | J    |         |          |

| HO1L         | 21/268 | (2006.01) | HO1L | 21/26  | G    |         |          |

|              |        |           | HO1L | 21/268 | G    |         |          |

|              |        |           | HO1L | 21/268 | J    |         |          |

|              |        |           |      |        |      | 請求項の数 5 | (全 14 頁) |

特願2005-188209 (P2005-188209) ||(73)特許権者 000003078 (21) 出願番号 (22) 出願日 平成17年6月28日 (2005.6.28) 株式会社東芝 (65) 公開番号 特開2007-12675 (P2007-12675A) 東京都港区芝浦一丁目1番1号 (43) 公開日 平成19年1月18日 (2007.1.18) ||(74)代理人 100083806 平成20年6月5日(2008.6.5) 弁理士 三好 秀和 審査請求日 |(74)代理人 100100712 弁理士 岩▲崎▼ 幸邦 (74)代理人 100100929 弁理士 川又 澄雄

弁理士 中村 友之 (74)代理人 100095500

弁理士 伊藤 正和

|(74)|代理人 100101247 | 弁理士 高橋 俊一

最終頁に続く

(54) 【発明の名称】熱処理装置、熱処理方法及び半導体装置の製造方法

# (57)【特許請求の範囲】

### 【請求項1】

半導体基板を載置する基板ステージと、

前記半導体基板の表面を区分する複数の区域の<u>いくつか</u>を、前記基板ステージを通して 選択的に予備加熱する複数の加熱部を有する加熱源と、

前記基板ステージに対向して配置され、前記表面全体に 0 . 1 m 秒 ~ 1 0 0 m 秒のパルス幅の光を照射する光源

とを備えることを特徴とする熱処理装置。

#### 【請求項2】

前記加熱源が、前記半導体基板の中央の第1区域を予備加熱する第1加熱部、及び前記第1区域の外側で前記半導体基板の外縁を含む第2区域を予備加熱する第2加熱部を含むことを特徴とする請求項1に記載の熱処理装置。

【請求項3】

半導体基板の表面を区分する複数の区域のいくつかを選択的に予備加熱し、

前記複数の区域の<u>いくつか</u>を選択的に予備加熱するたびに、前記表面全体に 0 . 1 m秒 ~ 1 0 0 m秒のパルス幅の光を照射する

ことを含むことを特徴とする熱処理方法。

### 【請求項4】

前記複数の区域が、前記半導体基板の中央の第1区域、及び前記第1区域の外側で前記半導体基板の外縁を含む第2区域を含むことを特徴とする請求項3に記載の熱処理方法。

#### 【請求項5】

第1の工程で処理された半導体基板の表面を複数の区域に区分し、

前記複数の区域のいくつかを選択的に予備加熱し、

前記複数の区域の<u>いくつか</u>を選択的に予備加熱するたびに、前記表面全体に 0 . 1 m秒 ~ 1 0 0 m秒のパルス幅の光を照射し、

前記半導体基板を第2の工程で処理する

ことを含むことを特徴とする半導体装置の製造方法。

### 【発明の詳細な説明】

### 【技術分野】

### [0001]

本発明は、半導体装置の熱処理方法に関し、特に高輝度光源を用いる熱処理装置、熱処理方法及び半導体装置の製造方法に関する。

#### 【背景技術】

# [0002]

大規模集積回路(LSI)等の半導体装置の性能向上は、集積度を高めること、即ち半導体装置を構成する素子の微細化により実現できる。このため、LSIはますます大規模化し、金属・酸化膜・半導体(MOS)トランジスタ等の素子の微細化もさらに勢いを増して進んできている。素子が微細化されるに伴い、MOSトランジスタ等の寄生抵抗及びショートチャネル効果は大きくなる。そのため、低抵抗層及び浅いpn接合の形成はその重要性を増してきている。

#### [0003]

例えば、20nm以下の浅いpn接合を形成するためには、まず、浅い不純物添加領域を形成する。浅い不純物添加領域の形成には、低加速エネルギで不純物を半導体基板にイオン注入する方法がある。半導体基板に添加された不純物を熱処理により活性化して、浅い不純物拡散領域が形成される。不純物拡散領域の拡散層抵抗を下げるためには、不純物の活性化熱処理を高温で行うことが必要である。

### [0004]

しかし、不純物としてイオン注入されたボロン(B)等のp型不純物、及びリン(P)や砒素(As)等のn型不純物は、半導体基板のシリコン(Si)結晶中での拡散係数が大きい。現行のハロゲンランプを用いた急速熱処理(RTA)で要する処理時間では、不純物が半導体基板の内方及び外方へ拡散してしまう。その結果、高濃度の不純物を有する浅い不純物拡散領域を半導体基板に形成することができない。また、不純物の拡散を抑制するために、RTAの熱処理温度を下げると、高濃度の不純物の活性化は望めない。このように、高濃度の不純物が活性化した低抵抗の浅い不純物拡散領域を半導体基板に形成することは困難である。

### [0005]

近年、RTAの問題を解決するために、不純物の活性化に必要な熱エネルギを瞬時に供給することができる、フラッシュランプやヤグ(YAG)レーザ等のパルス光源を用いたパルス光アニール法が検討されている(例えば、特許文献1参照。)。キセノン(Xe)フラッシュランプは、Xeガスを封入した石英管を有し、コンデンサ等に蓄えられた電荷を管内で瞬時に放電させる。その結果、例えば数100μs~数100msの時間の範囲で高輝度の白色光を発光させることが可能である。フラッシュランプ光を吸収した半導体基板は瞬時に発熱し、不純物の活性化に必要な熱エネルギを瞬時に得ることができる。したがって、フラッシュランプアニール法では、半導体基板に注入された不純物の濃度プロファイルをほとんど変化させずに、高濃度の不純物を活性化することができる。

# [0006]

しかし、フラッシュランプアニール法により不純物を均一性良く高濃度に活性化させるためには、20J/cm²以上の大きな照射エネルギが必要となる。そして、半導体基板表面には急激な温度上昇が生じる。その結果、半導体基板の表面側と裏面側との間に温度差が発生し、半導体基板内部では熱応力が増加する。特に、大面積を有する半導体基板に

10

20

30

40

対しては、発生する熱応力の総量が増加する。熱応力により誘起されたスリップ等のダメージにより半導体基板の破損が生じ易く、生産歩留りの低下を招く。このように、現状のフラッシュランプアニール法では、半導体基板に発生するダメージを抑制して熱処理を行うことは困難である。

【特許文献1】米国特許第4151008号明細書

### 【発明の開示】

【発明が解決しようとする課題】

### [0007]

本発明は、半導体基板に発生するダメージを抑制して熱処理を行うことが可能な熱処理装置、熱処理方法及び半導体装置の製造方法を提供することを目的とする。

【課題を解決するための手段】

### [0008]

本発明の第1の態様によれば、(イ)半導体基板を載置する基板ステージと、(ロ)半導体基板の表面を区分する複数の区域の<u>いくつか</u>を、基板ステージを通して選択的に予備加熱する複数の加熱部を有する加熱源と、(ハ)基板ステージに対向して配置され、表面全体に0.1m秒~100m秒のパルス幅の光を照射する光源とを備える熱処理装置が提供される。

#### [0009]

本発明の第2の態様によれば、(イ)半導体基板の表面を区分する複数の区域の<u>いくつか</u>を選択的に予備加熱し、(ロ)複数の区域の<u>いくつか</u>を選択的に予備加熱するたびに、表面全体に0.1m秒~100m秒のパルス幅の光を照射することを含む熱処理方法が提供される。

### [0010]

本発明の第3の態様によれば、(イ)第1の工程で処理された半導体基板の表面を複数の区域に区分し、(ロ)複数の区域の<u>いくつか</u>を選択的に予備加熱し、(ハ)複数の区域の<u>いくつか</u>を選択的に予備加熱するたびに、表面全体に0.1m秒~100m秒のパルス幅の光を照射し、(二)半導体基板を第2の工程で処理することを含む半導体装置の製造方法が提供される。

### 【発明の効果】

# [0011]

本発明によれば、半導体基板に発生する結晶欠陥を抑制して熱処理を行うことが可能な 熱処理装置、熱処理方法及び半導体装置の製造方法を提供することができる。

【発明を実施するための最良の形態】

### [0012]

以下図面を参照して、本発明の形態について説明する。以下の図面の記載において、同一または類似の部分には同一または類似の符号が付してある。但し、図面は模式的なものであり、厚みと平面寸法との関係、各層の厚みの比率等は現実のものとは異なることに留意すべきである。したがって、具体的な厚みや寸法は以下の説明を参酌して判断すべきものである。また図面相互間においても互いの寸法の関係や比率が異なる部分が含まれていることは勿論である。

# [0013]

また、本発明の実施の形態では、イオン注入された不純物の活性化熱処理工程を用いて説明する。注入する不純物は、例えば n 型不純物としては P あるいは A s が、 p 型不純物としては B が用いられる。しかし、本発明の第 1 ~第 3 の実施の形態に係る熱処理工程は、不純物活性化熱処理工程に限定されない。例えば、酸化膜、窒化膜等の絶縁膜形成や損傷層等の再結晶化等の熱処理工程に適用できることは勿論である。

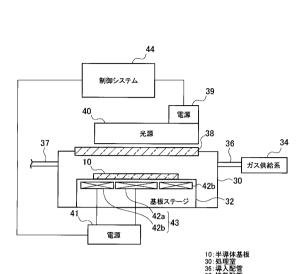

#### [0014]

本発明の実施の形態に係る熱処理装置は、図1に示すように、処理室30と、ガス供給系34と、光源40と、制御システム44とを備えている。処理室30には、ガス供給系34に接続された導入配管36、及び排気配管37が設けられている。処理室30の上部

10

20

30

40

には、透明窓38が光源40に対向して配置されている。処理室30内の底部には、半導体基板10を載置する基板ステージ32が配置されている。

#### [0015]

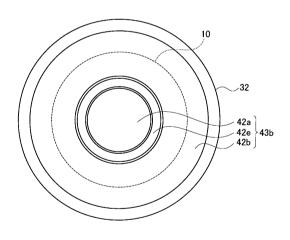

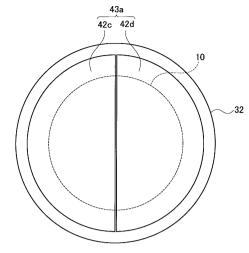

基板ステージ32の内部には、基板ステージ32を通して半導体基板10を予備加熱する加熱源43が設けられている。加熱源43は、第1加熱部42a及び第2加熱部42bを有する。光源40、加熱源43の第1及び第2加熱部42a、42bはそれぞれ、電源39、41を介して制御システム44に接続されている。

### [0016]

S i 等の半導体基板 1 0 に注入された不純物を活性化するための熱処理を行う処理室 3 0 は、例えばステンレススチール等の金属製である。基板ステージ 3 2 には、ステンレススチール、アルミニウムナイトライド(A 1 N )、セラミックスあるいは石英等が用いられる。加熱源 4 3 としては、ニクロム線等の埋め込み金属ヒータや加熱ランプ等が用いられる。予備加熱は、制御システム 4 4 により温度制御される。

### [0017]

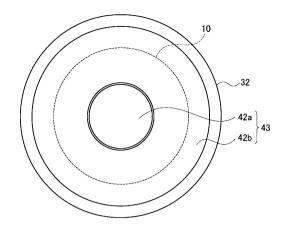

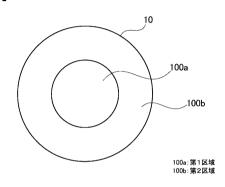

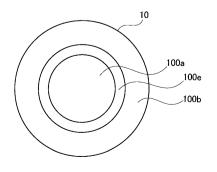

加熱源43の第1加熱部42 a は、図2に示すように、基板ステージ32上の半導体基板10の中央部に対向して設けられる。第2加熱部42 b は、第1加熱部42 a の外側で半導体基板10の外縁を含む区域に対向して設けられる。第1及び第2加熱部42 a、42 b により、図3に示すように、半導体基板10の表面において、中央の第1区域100 a 及び第1区域100 a の外側で半導体基板10の外縁を含む第2区域100 b のそれぞれが、基板ステージ32を通して選択的に予備加熱される。

#### [0018]

半導体基板10の熱処理時には、ガス供給系34から導入配管36を通して、窒素(N2)、アルゴン(Ar)等の不活性ガス等が処理室30に導入される。処理室30に導入された不活性ガスは、排気配管37から排気される。

#### [0019]

フラッシュランプ等の光源 4 0 は、合成石英等の透明窓 3 8 を介して、半導体基板 1 0 表面をパルス状に光照射して加熱する。パルス電源等の電源 3 9 は、光源 4 0 を約 0 . 1 m秒  $\sim$  1 0 0 m秒の極短パルス幅で駆動する。電源 3 9 は、制御システム 4 4 により、光源 4 0 の出射光のパルス幅及び照射エネルギを制御する。光源 4 0 の照射エネルギ密度は、例えば 1 5 J / c m²から 4 0 J / c m²の範囲、望ましくは 2 0 J / c m²から 3 4 J / c m²の範囲である。なお、透明窓 3 8 は、半導体基板 1 0 を照射する光源 4 0 の出射光を透過させると共に、処理室 3 0 を光源 4 0 から隔離して気密保持の働きもする。

#### [0020]

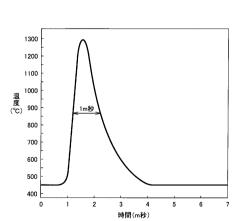

光源 4 0 に用いられる X e フラッシュランプによる加熱では、図 4 に示すように、例えば最高到達温度が約 1 3 0 0 で、半値幅が約 1 m秒の温度プロファイルが得られる。 X e フラッシュランプでは、R T A で使用されるハロゲンランプ等の赤外線ランプに比べて急峻な温度上昇と温度降下が実現できる。例えば、ハロゲンランプ光では、 450 ~ 1 3 0 0 間の昇降温時間は 1 0 秒以上、例えば約 1 5 秒である。その上、 9 0 0 ~ 1 3 0 0 の 1 0 0 間の昇 / 降温時間が 2 ~ 3 秒必要である。一方、フラッシュランプ光では、 450 ~ 1 3 0 0 間の昇降温時間は、 0 . 1 m秒~ 1 0 0 m秒、望ましくは 0 . 5 m秒~ 5 0 m秒の間である。なお、半導体基板 1 0 の表面温度は、高速パイロメータにより測定している。

### [0021]

イオン注入された不純物の活性化熱処理において、昇/降温時間が0.1 m秒未満では、最高到達温度が900 未満となり、半導体基板10に注入された不純物の活性化が不十分となる。また、昇/降温時間が100m秒を越えると、到達温度が1400 を越えてしまう。半導体基板10が1400 を越えて加熱されると、注入された不純物の拡散が顕著となる。その結果、半導体基板10に注入された不純物の拡散のために、半導体基板10の表面近傍に浅いpn接合を形成することが困難となる。

# [0022]

30

10

20

10

20

30

40

50

また、活性化熱処理では、基板ステージ32に載置された半導体基板10は、加熱源43により、例えば300~600、望ましくは400~500 の範囲で予備加熱されている。予備加熱時間は、例えば10秒~120秒程度が望ましい。予備加熱は、半導体基板10にダメージが誘起されない温度と時間に設定されている。予備加熱温度が300より低いと、最高到達温度が900 未満となる場合がある。また、予備加熱温度が600 を越えると、到達温度が1400 より高くなる場合がある。

#### [0023]

本発明の実施の形態に係る熱処理装置では、図4に示したように、450~1300間の昇降温時間は、約3m秒である。また、900~1300の間の昇/降温時間は、例えば約1m秒である。本発明の実施の形態によれば、半導体基板10に注入された不純物の活性化熱処理を、例えば900以上の高温で極短時間で実施することができる。したがって、活性化熱処理による不純物の拡散長を5nm以下に抑制して、浅いpn接合の形成が可能になる。

# [0024]

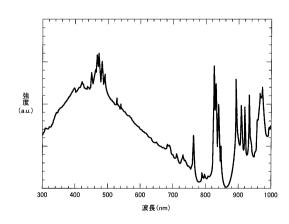

しかし、900 以上の高温で極短時間の昇/降温サイクルでは、半導体基板10に熱応力によるスリップや転位等の結晶欠陥が発生し易い。更に、光源40のXeフラッシュランプの発光スペクトルは白色光に近く、図5に示すように、主な強度ピーク波長は、400nm~500nmである。フラッシュランプ光の強度ピークを含む波長の範囲、例えば1µm以下の範囲の光は、半導体基板10表面から約0.1µmの深さの範囲の領域で吸収される。半導体基板10表面から数10µmの深さの範囲の領域では局所的に急激な温度上昇が生じる。その結果、半導体基板10の表面側と裏面側との間に約300 から1000 の温度差が発生し、半導体基板10内部では熱応力が増加する。その結果、熱応力に起因する結晶欠陥により半導体基板10にダメージが発生し、半導体基板10が破損してしまう。このように、光源40による極短時間の加熱処理では、熱応力で発生するダメージのため半導体基板10の割れ耐性が不十分である。

### [0025]

本発明の実施の形態に係る熱処理装置には、図1に示したように、半導体基板10の面に区分された第1及び第2区域100a、100bのそれぞれを、基板ステージ32を通して選択的に予備加熱する第1及び第2加熱部42a、42bを有する加熱源43が設けられている。第1及び第2加熱部42a、42bにより、第1及び第2区域100a、100bのそれぞれを選択的に予備加熱するたびに、半導体基板10の表面全体に光源40から放射されるフラッシュランプ光が照射される。

### [0026]

例えば、第1加熱部42aにより半導体基板10の第1区域100aが選択的に予備加熱される時には、第2区域100bは予備加熱されない。したがって、半導体基板10の表面にフラッシュランプ光を照射して第1区域100aを活性化熱処理しても、予備加熱されていない第2区域100bでは活性化熱処理に必要な高温まで加熱されることはない。同様に、第2加熱部42bにより第2区域100bが選択的に予備加熱されるときには、第1区域100aは予備加熱されない。したがって、フラッシュランプ光を照射して第2区域100bを活性化熱処理しても、第1区域100aでは活性加熱処理に必要な高温まで加熱されることはない。このように、本発明の実施の形態に係る熱処理装置では、半導体基板10の第1及び第2区域100a、100bを選択的に予備加熱しながら活性化熱処理を実施することができる。その結果、半導体基板10内部の熱応力の総量を低減することができ、半導体基板10に発生するダメージを抑制して活性化熱処理を行うことが可能となる。

# [0027]

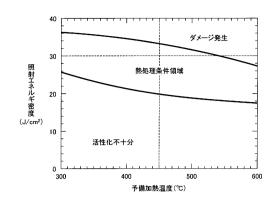

本発明の実施の形態に係る処理装置によるイオン注入不純物の活性化熱処理では、図 6に示すように、ダメージの発生を抑制し所望の活性化率を達成するために、半導体基板 10の予備加熱温度に依存するフラッシュランプ光の照射エネルギ密度の熱処理条件領域が与えられる。予備加熱温度は、第 1 又は第 2 加熱部 4 2 a、 4 2 bにより加熱された第 1

又は第 2 区域 1 0 0 a 、 1 0 0 b で測定される。即ち、フラッシュランプ光の照射エネルギ密度が熱処理条件領域の下限以下では不純物の活性化が不十分となり、低抵抗層を形成することができない。照射エネルギ密度が熱処理条件領域の上限以上では半導体基板 1 0 にダメージが発生してしまう。例えば、フラッシュランプ光の照射エネルギ密度の熱処理条件領域は、半導体基板 1 0 の 6 0 0 及び 3 0 0 の予備加熱温度に対し、それぞれ約 1 8 J / c  $m^2$  から 2 7 J / c  $m^2$  及び約 2 6 J / c  $m^2$  から 3 6 J / c  $m^2$  で与えられる。また、予備加熱温度が 4 5 0 の近傍では、照射エネルギ密度の熱処理条件領域が約 2 0 J / c  $m^2$  から 3 4 J / c  $m^2$  で与えられる。

#### [0028]

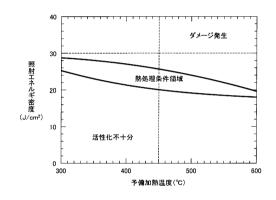

比較例として、図1に示した熱処理装置の加熱源43により半導体基板10全体を予備加熱して通常の活性化熱処理が実施されている。比較例においては、半導体基板10の全領域が一括してフラッシュランプ光で活性化熱処理温度まで加熱される。例えば、直径が約200mmのSi半導体基板10を全面予備加熱して、フラッシュランプ光により半導体基板10の表面層を1300 に加熱する。Si結晶の熱膨張率は、約3.5×10~6 K~1 であるため、加熱された表面層のSi結晶は表面に平行な方向に約1mm膨張する。このように、半導体基板10の加熱区域を限定せずに半導体基板10全面を予備加熱する場合は、半導体基板10の熱膨張量が大きくなるため、熱応力がSi結晶の脆性破壊なる場合は、半導体基板10の熱膨張量が大きくなるため、熱応力がSi結晶の脆性破壊なる場合は、半導体基板10が破損してしまう。比較例では、図7に示すように、熱処理条件領域の下限は、本発明の実施の形態に係る熱処理条件領域の下限とほぼ同様である。しかし、比較例の熱処理条件領域の上限は第1の実施の形態に係る熱処理条件領域の上限とは、対している。このように、熱処理条件領域が約1/2以下に縮小している。

### [0029]

本発明の実施の形態では、図2に示したように、第1及び第2加熱部42a、42bにより半導体基板10の予備加熱区域が限定される。例えば、半導体基板10の第1区域100aの直径を約100mmとする。第1又は第2区域100a、100bの活性化熱処理において、Si結晶の熱膨張を約0.5mmまで抑制することができる。その結果、半導体基板10の内部の熱応力は減少する。したがって、半導体基板10に生じるダメージが抑制され、半導体基板10の割れ耐性が向上する。このように、本発明の実施の形態に係る熱処理装置では、図6に示したように、熱処理条件領域が拡大し、半導体基板10の破損を防止することができ、低抵抗層を安定して形成することが可能となる。

# [0030]

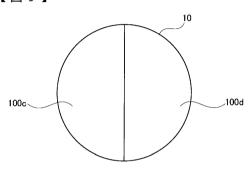

なお、本発明の実施の形態に係る熱処理装置では、図2に示したように、円状の第1加熱部42a及び環状の第2加熱部42bを有する加熱源43が用いられている。しかし、加熱源43は限定されない。例えば、図8に示すように、半円状に分割された第1及び第2加熱部42c、42dを有する加熱源43aであってもよい。図9に示すように、第1及び第2加熱部42c、42dにより、直径方向に区分された半導体基板10の第1及び第2区域100c、100dがそれぞれ選択的に予備加熱される。したがって、活性化熱処理による半導体基板10の内部の熱応力を低減することができる。

### [0031]

また、本発明の実施の形態に係る熱処理装置では、2分割された加熱源43が用いられている。しかし、3以上の複数の加熱部を有する加熱源を用いてもよい。例えば、図10に示すように、第1及び第2加熱部42 a、42 bの間に第3加熱部42 eを有する加熱源43 bであってもよい。第3加熱部42 eは、図11に示すように、半導体基板10の第1及び第2区域100a、100 bの間の第3区域100 eを選択的に予備加熱する。

# [0032]

加熱源43では、第1及び第2加熱部42a、42bのそれぞれで選択的に予備加熱する場合、熱の拡散等により半導体基板10の第1及び第2区域100a、100bの境界を越えた領域も予備加熱される。その結果、第1及び第2区域100a、100bの境界近傍で活性化ぞれの活性化熱処理において、第1及び第2区域100a、100bの境界近傍で活性化

10

20

30

40

10

20

30

40

50

不純物濃度が高くなる場合がある。例えば、加熱源43bを用いて、第1及び第2加熱部42a、42bのそれぞれにより予備加熱するときに、第3加熱部42eによる予備加熱を同時に行う。第1及び第2区域100a、100bのそれぞれ二比べ、第3区域100eの予備加熱温度を少し低く調整することにより、均一な活性化不純物濃度分布を実現することができる。

# [0033]

次に、本発明の実施の形態に係る熱処理方法及び半導体装置の製造方法を、相補型MOS(CMOS)トランジスタの製造工程を例にして説明する。なお、半導体装置としては、CMOSトランジスタに限定されない。例えば、nMOSトランジスタやpMOSトランジスタ等であってもよい。また、酸化(SiO2)膜に代えて、酸窒化シリコン(SiON)膜、窒化シリコン(Si3N4)膜等の絶縁膜や、SiO2膜と、SiON膜、Si3N4膜、及び各種の金属酸化膜等との複合絶縁膜を用いた金属・絶縁膜・半導体(MIS)トランジスタであってもよいことは勿論である。

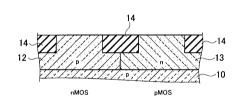

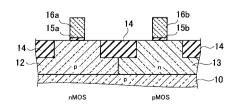

# [0034]

(イ)図12に示すように、半導体基板10のnMOS領域にpウェル12を形成する。また、pMOS領域にnウェル13を形成する。フォトリソグラフィ、反応性イオンエッチング(RIE)、化学気相成長(CVD)等により、pウェル12の周囲とnウェル13の周囲に素子分離領域14を形成する。素子領域として、nMOS領域及びpMOS領域が素子分離領域14により分離される。

### [0035]

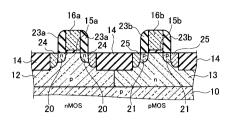

(ロ)半導体基板10の素子領域表面に、例えば熱酸化膜等の絶縁膜が形成される。絶縁膜上に、低圧(LP)CVD等により、多結晶Si(poly-Si)膜が堆積される。図13に示すように、poly-Si膜及び絶縁膜をパターニングしてpウェル12及びnウェル13それぞれに、ゲート電極16a及び16bと、ゲート絶縁膜15a及び15bとが形成される。

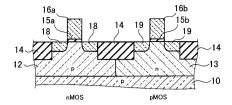

### [0036]

(ハ)イオン注入工程(第1の工程)で、フォトリソグラフィ等により、 pMOS 領域をレジスト膜で被覆する。レジスト膜及びゲート電極16aをマスクとして、 nMOS 領域に n 型不純物となる V 族原子、 例えば A s イオンを選択的に注入する。 剥離液等により、 pMOS 領域のレジスト膜を剥離する。フォトリソグラフィ等により、 nMOS 領域をレジスト膜で被覆する。レジスト膜及びゲート電極16bをマスクとして、 pMOS 領域に p 型不純物となる III 族原子、 例えば B イオンを選択的に注入する。 剥離液等により、 nMOS 領域のレジスト膜を剥離する。その結果、 図14に示すように、 ゲート絶縁膜15aの両端部及び素子分離領域14の間に不純物注入層18、 及びゲート絶縁膜15bの両端部及び素子分離領域14の間に不純物注入層18、 及びゲート絶縁膜15bの両端部及び素子分離領域14の間に不純物注入層18、 及びゲートによる。 F は、 F ないて、 加速エネルギが約2keV、 F である。 F については、 加速エネルギが約0.5keV、 F である。 F については、 加速エネルギが約0.5keV、 F である。 F を F が F ない F の深さは、 F の F ない F の F ない F

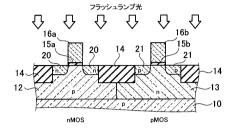

### [0037]

(二)半導体基板10を、図1に示した熱処理装置の基板ステージ32に載置する。基板ステージ32を通して、加熱源43の第1加熱部42aにより半導体基板10が裏面側から、例えば約450 で予備加熱される。図3に示した第1区域100aを約450の予備加熱温度で維持しながら、光源40のフラッシュランプ光を半導体基板10の表面側から、例えばパルス幅が約1ms及び照射エネルギが約30J/cm²の条件で照射して活性化熱処理が行われる。次いで、第2加熱部42bにより半導体基板10が裏面側から、例えば約450 で予備加熱される。第2区域100bを約450 の予備加熱温度で維持しながら、光源40のフラッシュランプ光を半導体基板10の表面側から、例えばパルス幅が約1ms及び照射エネルギが約30J/cm²の条件で照射して活性化熱処理が行われる。活性化熱処理により、イオン注入により不純物注入層18、19に注入され

たAs及びBが格子位置に置換して取り込まれ、活性化する。その結果、図15に示すように、ゲート絶縁膜15a、15bのそれぞれの両端及び素子分離領域14の間にn型のエクステンション領域20及びp型のエクステンション領域21が形成される。

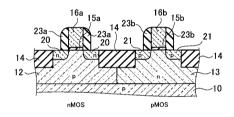

#### [0038]

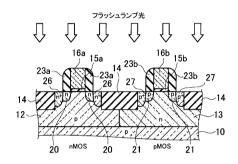

(ホ)側壁スペーサ形成工程(第2の工程)で、半導体基板 10上に、 $SiO_2$ 膜及び  $Si_3N_4$ 膜等の絶縁膜を LPCVD等により順次堆積する。RIE等の指向性エッチングにより、 $SiO_2$ 膜及び $Si_3N_4$ 膜等の絶縁膜をエッチバックする。その結果、絶縁膜が、ゲート電極 16 a、 16 b 及びゲート絶縁膜 15 a、 15 b の側面にそれぞれ選択的に残る。図 16 に示すように、 $Si_3N_4$ 膜及び $SiO_2$ 膜の多層構造の側壁スペーサ 23 a 及び 23 b がそれぞれ形成される。

# [0039]

(へ)イオン注入工程(第1の工程)で、フォトリソグラフィ等により、pMOS領域をレジスト膜で被覆する。レジスト膜、ゲート電極16a及び側壁スペーサ23aをマスクとして、nMOS領域にn型不純物となるV族原子、例えばPイオンを選択的に注入する。剥離液等により、pMOS領域のレジスト膜を剥離する。フォトリソグラフィ等により、nMOS領域をレジスト膜で被覆する。レジスト膜、ゲート電極16b及び側壁スペーサ23bをマスクとして、pMOS領域にp型不純物となるIII族原子、例えばBイオンを選択的に注入する。剥離液等により、nMOS領域のレジスト膜を剥離する。イオン注入条件は、Pについて、加速エネルギが約10keV、ドーズ量が約3×10<sup>15</sup> c m<sup>-2</sup>である。Bについては、加速エネルギが約10keV、ドーズ量が3×10<sup>15</sup> c m<sup>-2</sup>である。その結果、図17に示すように、側壁スペーサ23a、23bの端部及び素子分離領域14の間に、エクステンション領域20、21より深く、不純物注入層24及び25が、pウェル12及びnウェル13それぞれに形成される。また、イオン注入により、ゲート電極16a、16b中にも、Pイオン及びBイオンがそれぞれ注入される。

[0040]

(ト)半導体基板10を、図1に示した熱処理装置の基板ステージ32に載置する。活性化熱処理では、基板ステージ32を通して加熱源43の第1加熱部42aにより半導体基板10が裏面側から、例えば約450 に予備加熱される。図3に示した第1区域100aを約450 の予備加熱温度で維持しながら、光源40のフラッシュランプ光が半導体基板10の表面側から、例えばパルス幅が約1ms及び照射エネルギが約30J/cm²の条件で照射されて活性化熱処理が行われる。次いで、第2加熱部42bにより半導体基板10が裏面側から、例えば約450 で予備加熱される。第2区域100bを約450 の予備加熱温度で維持しながら、光源40のフラッシュランプ光を半導体基板10の表面側から、例えばパルス幅が約1ms及び照射エネルギが約30J/cm²の条件で照射して活性化熱処理が行われる。その結果、図18に示すように、側壁スペーサ23aの端部及び素子分離領域14の間に、エクステンション領域20に接してn⁺型のソース/ドレイン領域26が形成される。また、側壁スペーサ23bの端部及び素子分離領域14の間に、エクステンション領域21に接してp⁺型のソース/ドレイン領域27が形成される。

### [0041]

その後、層間絶縁膜形成工程(第2の工程)で、例えば、CVD等により、成膜温度 400 で、半導体基板 10にSiO<sub>2</sub>膜等の層間絶縁膜を形成する。層間絶縁膜にコンタクトホールを開口し、ソース / ドレイン領域 26、27及びゲート電極 16a、16bに配線等を形成する。このようにして、半導体装置が製造される。

### [0042]

本発明の実施の形態に係る熱処理方法では、イオン注入の過程で形成された不純物注入層7に注入された不純物は、所望の活性化率を達成するのに十分な照射エネルギ密度で活性化熱処理される。また、活性化熱処理では、第1及び第2加熱部42a、42bにより半導体基板10の予備加熱が第1及び第2区域100a、100bにそれぞれ限定される。例えば、半導体基板10の第1区域100aの直径を約100mmとする。第1又は第

10

20

30

40

2 区域 1 0 0 a、 1 0 0 bの活性化熱処理において、半導体基板 1 0 の内部の熱応力は減少する。したがって、半導体基板 1 0 に発生するダメージを抑制して、浅い p n 接合を形成することが可能となる。このように、本発明の実施の形態によれば、半導体基板 1 0 の割れ耐性を向上させ、半導体装置の製造を高歩留りで行うことが可能となる。

### [0043]

上記の説明では、第1及び第2区域100a、100bの予備加熱温度は、約450としている。しかし、予備加熱温度は、第1及び第2区域100a、100bで異なっていてもよい。例えば、予め測定されたシート抵抗の面内分布の傾向に基づいて、予備加熱条件を調整しても良い。

### [0044]

一般に、半導体基板10の外縁側では熱が逃げやすく、加熱効率が低下してしまう。例えば、半導体基板1の中央側の第1区域100aに対して、外縁側の第2区域100bの予備加熱温度を、約20 高くする。その結果、シート抵抗の半導体基板10の面内分布の標準偏差 が約1%未満まで低減している。このように、本発明の実施の形態では、必要に応じて第1及び第2加熱部42a、42b毎に予備加熱温度を調整することができるため、熱処理温度の面内均一性の向上が可能となる。したがって、半導体装置の電気的特性のばらつきを抑制して、熱処理工程の歩留まりを向上させることが可能となる。

### [0045]

(その他の実施の形態)

上記のように、本発明の実施の形態を記載したが、この開示の一部をなす論述及び図面はこの発明を限定するものであると理解すべきではない。この開示から当業者にはさまざまな代替実施の形態、実施例及び運用技術が明らかとなろう。

### [0046]

本発明の実施の形態においては、図1の光源40としてXeフラッシュランプをもちいている。しかし、光源40はXeフラッシュランプに限定されるものではなく、例えば、他の希ガス、水銀、及び水素等を用いたフラッシュランプ、エキシマレーザ、YAGレーザ、一酸化炭素ガス(CO)レーザ、及び二酸化炭素(CO₂)レーザ等のレーザ、あるいはXeアーク放電ランプ等のような高輝度発光が可能な光源であってもよいことは勿論である。

# [0047]

このように、本発明はここでは記載していないさまざまな実施の形態等を含むことは勿論である。したがって、本発明の技術的範囲は上記の説明から妥当な特許請求の範囲に係わる発明特定事項によってのみ定められるものである。

### 【図面の簡単な説明】

[0048]

- 【図1】本発明の実施の形態に係る熱処理装置の一例を示す概略図である。

- 【図2】本発明の実施の形態に係る熱処理装置の加熱源の一例を示す図である。

- 【図3】本発明の実施の形態に係る熱処理装置の加熱源による予備加熱区域の一例を示す 図である。

- 【図4】本発明の実施の形態に係る熱処理装置の光源の加熱特性の一例を示す図である。

- 【図 5 】本発明の実施の形態に係る熱処理装置の光源の発光スペクトルの一例を示す図である。

- 【図 6 】本発明の実施の形態に係る熱処理装置の予備加熱温度及び照射エネルギ密度の熱処理条件領域の一例を示す図である。

- 【図7】比較例による予備加熱温度及び照射エネルギ密度の熱処理条件領域の一例を示す 図である。

- 【図8】本発明の実施の形態に係る熱処理装置の加熱源の他の例を示す図である。

- 【図9】本発明の実施の形態に係る熱処理装置の加熱源による予備加熱区域の他の例を示す図である。

- 【図10】本発明の実施の形態に係る熱処理装置の加熱源の他の例を示す図である。

10

20

30

40

- 【図11】本発明の実施の形態に係る熱処理装置の加熱源による予備加熱区域の他の例を示す図である。

- 【図12】本発明の実施の形態に係る熱処理方法の説明に用いる半導体装置の製造工程の 一例を示す工程断面図(その1)である。

- 【図13】本発明の実施の形態に係る熱処理方法の説明に用いる半導体装置の製造工程の 一例を示す工程断面図(その2)である。

- 【図14】本発明の実施の形態に係る熱処理方法の説明に用いる半導体装置の製造工程の 一例を示す工程断面図(その3)である。

- 【図15】本発明の実施の形態に係る熱処理方法の説明に用いる半導体装置の製造工程の 一例を示す工程断面図(その4)である。

- 【図16】本発明の実施の形態に係る熱処理方法の説明に用いる半導体装置の製造工程の 一例を示す工程断面図(その5)である。

- 【図17】本発明の実施の形態に係る熱処理方法の説明に用いる半導体装置の製造工程の 一例を示す工程断面図(その6)である。

- 【図18】本発明の実施の形態に係る熱処理方法の説明に用いる半導体装置の製造工程の 一例を示す工程断面図(その7)である。

### 【符号の説明】

- [0049]

- 1 0 ... 半導体基板

- 3 0 ... 処理室

- 3 2 ... 基板ステージ

- 4 0 ... 光源

- 4 2 a ... 第 1 加熱部

- 4 2 b ... 第 2 加熱部

- 4 3 ... 加熱源

- 100a...第1区域

- 1 0 0 b ... 第 2 区域

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図10】

【図11】

【図8】

【図9】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

# フロントページの続き

(74)代理人 100098327

弁理士 高松 俊雄

(72)発明者 伊藤 貴之

神奈川県横浜市磯子区新杉田町8番地 株式会社東芝 横浜事業所内

審査官 太田 一平

(56)参考文献 特開2004-303921(JP,A)

特開平03-023629(JP,A)

特開2005-136395(JP,A)

(58)調査した分野(Int.CI., DB名)

H01L 21/26 - 21/268

H01L 21/322 - 21/326

H01L 21/42 - 21/428

H01L 21/477 - 21/479

H01L 21/20

H01L 21/22 - 21/24

H01L 21/38 - 21/40

H01L 21/205

H01L 21/31

H01L 21/365

H01L 21/469

H01L 21/86