# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

| (51) Int. CI. <sup>6</sup><br>_H01L 21/66 | (11) 공개번호 특1995-0015694<br>(43) 공개일자 1995년06월17일 |

|-------------------------------------------|--------------------------------------------------|

| (21) 출원번호<br>(22) 출원일자                    | 특 1993-0025324<br>1993년 11월26일                   |

| (71) 출원인                                  | 삼성전자 주식회사 김광호                                    |

| (72) 발명자                                  | 경기도 수원시 팔달구 매탄동 416번지<br>이승근                     |

|                                           | 서울특별시 중랑구 면목 4동 349-23                           |

|                                           | 곽충근                                              |

| (74) 대리인                                  | 서울특별시 노원구 중계 2동 중계 2단지 아파트 112블럭 212-313<br>이건주  |

| 심사청구 : 있음                                 |                                                  |

# (54) 번-인회로를 가지는 반도체메모리장치 및 그 번-인방법

#### 요약

본 발명은 반도체메모리장치에서 특히 스테이틱램에서의 신뢰성 개선을 위한 번-인회로를 가지는 반도체메모리장치 및 그 번-인 방법에 관한 것으로, 본 발명은 [메모리쎌이 행과 열방향으로 각각 다수개로씩저장되는 메모리쎌어레이와, 상기 메모리쎌어레이의 행을 선택하는 행디코오더와, 상기 메모리쎌어레이의 열을 선택하는 열디코오더를 가지는 반도체메모리장치에 있어서, 동일칩상에 형성되는 데이타 입출력 핀과 상기 메모리쎌어레이의 열과의 사이에 형성되고 상기 데이타입출력핀을 통해 입출력되는 데이타를 전송하는 입출력라인제어회로와, 상기 메모리쎌어레이내의 데이타의 입출력을 제어하기 위한 신호를 상기 입출력라인으로 공급하는 리드/라이트제어회로와, 상기 리드/라이트제어회로의 출력신호를 입력하고이 입력에 대응하여 상기 입출력라인제어회로를 통해 입력되는 데이타입력에 응답된 번-인신호를 상기행디코오더와 열디코오더에 공급하여 동일칩의 번-인테스트를 인에이블시키는 번-인제어회로를 구비하여, 칩의 번-인테스트가 패키지공정 후에 이루어지는 반도체메모리장치]를 개시하고 있다. 이와같은 본 발명에 의한 번-인회로 및 방법은 패키지완성 후에 번-인을 실시하며 동시에 동일칩상에 존재하는 모든 메모리쎌의 번-인테스트를 동시에 수행할 수 있어 번-인테스트에 소모되는 테스트시간을 대폭 감소할 수있는 효과가 있다. 또한 패키지공정후에 번-인테스트를 함에 의해 웨이퍼상태에서 번-인테스트를 할 시필요로 되는 별도의 테스트장비가 필요하지 않은 잇점이 있다. 또한 본 발명은 스테이틱램과 같은 반도체메모리장치를 패키지 상태에서 신뢰성있게 번-인테스트를 수행할 수 있게 된다.

#### 出丑도

# 명세서

[발명의 명칭]

번-인회로를 가지는 반도체메모리장치 및 그 번-인방법

[도면의 간단한 설명]

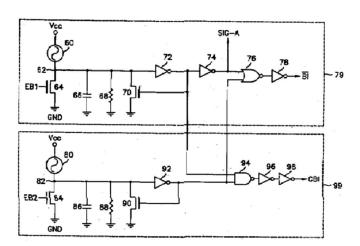

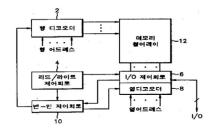

제1도는 본 발명에 의한 번-인회로가 구비된 반도체메모리장치의 개략적 블럭구성을 보여주는 도면

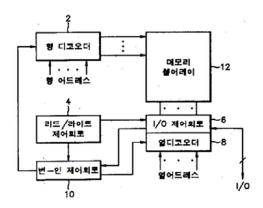

제2도는 본 발명에 의한 번-인회로내의 입력스위칭부의 실시예를 보여주는 회로도

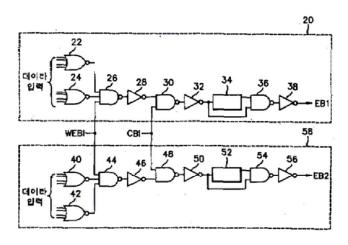

제3도는 본 발명에 의한 번-인회로내의 번-인제어부의 실시예를 보여주는 회로도

본 내용은 요부공개 건이므로 전문내용을 수록하지 않았음

# (57) 청구의 범위

#### 청구항 1

메모리쎌이 행과 열방향으로 각각 다수개로씩 저장되는 메모리쎌어레이와, 상기 메모리쎌어레이의 행을 선택하는 행디코오더와, 상기 메모리쎌어레이의 열을 선택하는 열디코오더를 가지는 반도체메모리장치에 있어서, 동일칩상에 형성되는 데이타 입출력핀과 상기 메모리쎌어레이의 열과의 사이에 형성되고 상기 데이타입출력핀을 통해 입출력되는 데이타를 전송하는 입출력라인제어회로와, 상기 메모리쎌어레이내의 데이타의 입출력을 제어하기 위한 신호를 상기 입출력라인으로 공급하는 리드/라이트제어회로와, 상기 리드/라이트제어회로의 출력신호를 입력하고 이 입력에 대응하여 상기 입출력라인제어회로를 통해 입력 되는 데이타입력에 응답된 번-인신호를 상기 행디코오더와 열디코오더에 공급하여 동일칩의 번-인데스트 를 인에이블시키는 번-인제어회로를 구비하여, 칩의 번-인테스트가 패키지공정 후에 이루어지도록 함을 특징으로 하는 반도체메모리장치.

# 청구항 2

제1항에 있어서, 상기 번-인제어회로가 상기 번-인신호를 동일칩상의 모든 행디코더오더와 열디코오더에 공급하여 번-인테스트시 상기 메모리쎌어레이에 저장된 모든 메모리쎌의 번-인테스트가 동시에 이루어지도록 함을 특징으로 하는 반도체메모리장치.

#### 청구항 3

제1항에 있어서, 상기 번-인제어회로가, 상기 입출력라인제어회로를 통해 공급되는 데이타를 입력하고 이 입력에 응답하여 출력신호를 상기 리드/라이트제어회로의 출력신호에 대응하여 출력하는 입력스위칭 부와, 상기 입력스위칭부의 출력신호에 대응하여 절단동작이 이루어지는 퓨우즈를 포함하고 상기 퓨우즈 의 절단동작에 대응하여 번-인신호를 발생시키는 번-인제어부로 이루어짐을 특징으로 하는 반도체메모리 장치.

### 청구항 4

메모리쎌이 행과 열방향으로 각각 다수개로씩 저장되는 메모리쎌어레이와, 상기 메모리쎌어레이의 행을 선택하는 행디코더와, 상기 메모리쎌어레이의 열을 선택하는 열디코오더와, 동일칩상에 형성되는 데이터 입출력핀과 상기 메모리쎌어레이의 열과의 사이에 형성되고 상기 데이타입출력핀을 통해 입출력되는 데이타를 전송하는 입출력라인제어회로와, 상기 메모리쎌어레이내의 데이타의 입출력을 제어하기 위한 신호를 상기 입출력라인으로 공급하는 리드/라이트제어회로를 가지는 반도체메모리장치에 있어서, 상기 입출력라인제어회로를 통해 공급되는 데이타를 입력하고 이 입력에 응답하여 번-인모드인에이블신호를 상기 리드/라이트제어회로의 출력신호에 대응하여 출력하는 번-인모드인에이블부와, 상기 입출력라인제어회로를 통해 공급되는 테이타를 입력하고 이 입력에 응답하여 노멀모드인에이블신호를 상기 리드/라이트 제어회로의 출력신호에 대응하여 출력하는 보멀모드인에이블와, 상기 번-인모드인에이블신호의 출력신호의 입력에 대응하여 절단되는 제1퓨우즈를 포함하고 이 제1퓨우즈의 절단동작에 대응하여 번-인신호를 발생시켜 상기 행디코오더와 열디코오더로 공급하는 번-인신호발생부와, 상기 노멀모드인에이블신호의 출력신호의 입력에 대응하여 절단되는 제2퓨우즈를 포함하고 이 제2퓨우즈의 절단동작에 대응하여 번-인 제어신호를 발생시켜 상기 번-인모드인에이블부와 노멀모드인에이블부로 공급하는 번-인제어신호발생부를 구비함을 특징으로 하는 반도체메모리장치.

#### 청구항 5

제4항에 있어서, 상기 번-인신호발생부가 상기 번-인신호를 동일칩상의 모든 행디코오더와 열디코오더에 공급하여 번-인테스트시 상기 메모리쎌어레이에 저장된 모든 메모리쎌의 번-인테스트가 동시에 이루어지도록 함을 특징으로 하는 반도체메모리장치.

#### 청구항 6

제4항에 있어서, 상기 반도체메모리장치가, 상기 제1퓨우즈가 상기 번-인모드인에이블신호에 대응하여 절단될시에는 번-인테스트가 이루어지고, 상기 제2퓨우즈가 상기 노멀모드인에이블신호에 대응하여 또한 절단될시에는 노멀모드로 진행됨을 특징으로 하는 반도체메모리장치.

#### 청구항 7

제6항에 있어서, 상기 반도체메모리장치가, 상기 제1퓨우즈와 제2퓨우즈가 모두 절단되지 않을 시에는 노멀모드로 진행됨을 특징으로 하는 반도체메모리장치.

#### 청구항 8

제4항에 있어서, 상기 번-인모드인에이블부가, 복수개의 입력핀으로부터 입력되는 상기 복수개의 데이타입력신호중 소정갯수의 신호를 입력하는 제1노아게이트와, 상기 복수개의 데이타입력신호중 소정갯수를 제외한 나머지 갯수의 데이타입력신호를 입력하는 제2노아게이트와, 라이트인에이블신호에 의해 발생되고 번-인모드로의 진입을 알리는 제어신호와 상기 제1노아게이트 및 제2노아게이트의 각 출력신호를 입력하는 제1번드게이트와, 상기 제1번드게이트의 출력신호를 입력하는 제1인버터와, 상기 번-인제어신호와 상기 제1인버터의 출력신호를 입력하는 제2번드게이트와, 상기 제2인버터의 출력신호를 입력하는 제2인버터와, 상기 제2인버터의 출력신호를 입력하는 제2인버터와, 상기 제2인버터의 출력신호를 입력하는 제3번드게이트와, 상기 제3번드게이트의 출력신호를 입력하여 제3 낸드게이트와, 상기 제3번드게이트의 출력신호를 입력하는 제3 낸드게이트와, 상기 제3번드게이트와 출력신호를 입력하는 제3

인버터로 이루어짐을 특징으로 하는 반도체메모리장치.

### 청구항 9

제4항에 있어서, 상기 노멀모드인에이블부가, 복수개의 입력핀으로부터 입력되는 상기 복수개의 데이타입력신호중 소정갯수의 신호를 입력하는 제1노아게이트와, 상기 복수개의 데이타입력신호중 소정갯수를 제외한 나머지갯수의 데이타입력신호를 입력하는 제2노아게이트와, 라이트인에이블신호에 의해 발생되고 번-인모드로의 진입을 알리는 제어신호와 상기 제1노아게이트 및 제2노아게이트의 각 출력신호를 입력하는 제1번드게이트의, 상기 제1번드게이트의 출력신호를 입력하는 제1인버터와, 상기 번-인제어신호와 상기 제1인버터의 출력신호를 입력하는 제2번드게이트와, 상기 제2번드게이트의 출력신호를 입력하는 제2인버터와, 상기 제2번드게이트의 출력신호를 입력하는 제2인버터와, 상기 제2번드게이트의 출력신호를 입력하는 제2인버터와, 상기 제2번드게이트의 출력신호를 입력하는 제3번드게이트와, 상기 제3번드게이트의 출력신호를 입력하여 상기 노멀모드 인에이블신호를 출력하는 제3인버터로 이루어짐을 특징으로 하는 반도체메모리장치.

#### 청구항 10

제4항에 있어서, 상기 번-인제어부가, 전원전압단과 제1접속노드와의 사이에 접속된 제1퓨우즈와, 상기 제1접속노드와 접지전원단과의 사이에 접속된 채널과 상기 번-인모드인이이블신호가 공급되는 게이트단자로 이루어지는 제1트랜지스터와, 상기 제1접속노드에 입력단자가 접속된 제1인버터와, 상기 제1접속노드와 접지전압단과의 사이에 접속된 채널과 상기 제1인버터의 출력신호가 공급되는 게이트단자로 이루어지는 제2트랜지스터와, 상기 제1인버터의 출력신호를 입력하는 제2인버터와, 상기 제2인버터의 출력신호를 일입력하는 노아게이트와, 상기 노아게이트의 출력신호를 입력하여 상기 번-인신호를 출력하는 제3인버터로 이루어짐을 특징으로 하는 반도체메모리장치.

#### 청구항 11

제10항에 있어서, 상기 번-인제어신호발생부가, 전원전압단과 제2접속노드와의 사이에 접속된 제2퓨우즈와, 상기 제2접속노드와 접지전원단과의 사이에 접속된 채널과 상기 노멀모드인에이블신호가 공급되는 게이트단자로 이루어지는 제3트랜지스터와, 상기 제2접속노드에 입력단자가 접속되어 출력신호가 상기노아게이트의 일입력으로 공급되는 제4인버터와, 상기 제2접속노드와 접지전압단과의 사이에 접속된 채널과 상기 제4인버터의 출력신호가 공급되는 게이트단자로 이루어지는 제4트랜지스터와, 상기 제4인버터의 출력신호가 공급되는 게이트단자로 이루어지는 제4트랜지스터와, 상기 제4인버터의 출력신호을 입력하여 상기 번-인제어신호를 출력하는 낸드게이트로 이루어짐을 특징으로 하는 반도체메모리장치.

# 청구항 12

메모리쎌이 행과 열방향으로 각각 다수개로씩 저장되는 메모리쎌어레이와, 상기 메모리쎌어레이의 행을 선택하는 행디코오더와, 상기 메모리쎌어라이의 열을 선택하는 열디코오더와, 동일칩상에 형성되는 데이 타 입출력교과 상기 메모리쎌어레이의 열과의 사이에 형성되고 상기 데이타입출력핀을 통해 입출력되는 데이타를 전송하는 입출력라인제어회로와, 상기 메모리쎌어레이내의 데이탸의 입출력을 제어하기 위한 신호를 상기 입출력라인으로 공급하는 리드/라이트제어회로를 가지는 반도체메모리장치에 있어서, 상기 입출력라인제어회로를 통해 공급되는 데이타를 입력하고 이 입력에 응답하는 출력신호를 상기 리드/라이 트제어 회로의 출력신호에 대응하여 출력하는 입력스위칭부와, 상기 입력스위칭부의 출력신호에 대응하여 절단동작이 이루어지는 퓨우즈를 포함하고, 상기 퓨우즈의 절단동작에 대응하여 번-인신호를 발생시 키는 번-인 제어부를 포함하는 번-인제어회로와, 제1패드와, 제2패드와, 제3패드와, 상기 제1패드와 제2 패드와의 사이에 전류경로가 형성된 제1다이오드군과, 상기 제1패드와 제3패드와의 사이에 전류경로가 형성된 제2다이오드군을 포함하고, 상기 제1패드와 제2패드와 제3패드에 각각 전압을 공급하여 발생되는 누수전류를 통해서 동일칩의 번-인모드진입여부를 판독하는 모드판독회로를 구비함을 특징으로 하는 반 도체메모리장치.

#### 청구항 13

제12항에 있어서, 상기 번-인제어회로가 상기 번-인신호를 동일칩상의 모든 행디코오더와 열디코오더에 공급하여 번-인테스트시 상기 메모리쎌어레이에 저장된 모든 메모리쎌의 번-인테스트가 동시에 이루어지도록 함을 특징으로 하는 반도체메모리장치

# 청구항 14

제12항에 있어서, 상기 입력스위칭부가, 상기 입출력라인제어회로를 통해 공급되는 데이타를 입력하고 이 입력에 응답하여 번-인모드인에이블신호를 상기 리드/라이트제어회로의 출력신호에 대응하여 출력하는 번-인모드인에이블부와, 상기 입출력라인제어회로를 통해 공급되는 데이타를 입력하고 이 입력에 응답하여 노멀모드인에이블신호를 상기 리드/라이트제어회로의 출력신호에 대응하여 출력하는 노멀모드인에이블부로 이루어짐을 특징으로 하는 반도체메모리장치

# 청구항 15

제14항에 있어서, 상기 번-인제어부가, 상기 번-인모드인에이블신호의 출력신호의 입력에 대응하여 절단되는 제1퓨우즈를 포함하고 이 제1퓨우즈의 절단동작에 대응하여 번-인신호를 발생시키 상기 행디코오더와 열디코오더로 공급하는 번-인신호발생부와, 상기 노멀모드인에이블신호의 출력신호의 입력에 대응하여 절단되는 제2퓨우즈를 포함하고 이 제2퓨우즈의 절단동작이 대응하여 번-인제어신호를 발생시켜 상기 번-인모드인에이블부와 노멀모드인에이블부로 공급하는 번-인제어신호발생부로 이루어짐을 특징으로 하는 반도체메모리장치.

### 청구항 16

제12항에 있어서, 상기 제1다이오드군과 제2다이오드군이 각각 서로 직렬연결된 다수개의 엔모오스트랜 지스터들로 이루어짐을 특징으로 하는 반도체메모리장치.

#### 청구항 17

메모리쎌이 행과 열방향으로 각각 다수개로써 저장되는 메모리쎌어레이와, 상기 메모리쎌어레이의 행을 선택하는 행디코오더와, 상기 메모리쎌어레이의 열을 선택하는 열디코더와, 동일칩상에 형성되는 데이타입출력핀과 상기 메모리쎌어레이의 열과의 사이에 형성되고 상기 데이타입출력핀을 통해 입출력되는 데이타를 전송하는 입출력라인제어회로와, 상기 메모리쎌어레이내의 데이타의 입출력을 제어하기 위한 신호를 상기 입출력라인으로 공급하는 리드/라이트제어회로를 가지는 반도체메모리장치에 있어서, 상기 입출력 라인제어회로를 통해 공급되는 데이타를 입력하고 이 입력에 응답하여 번-인모드인에이블부가 번-인모드 인에이볼신호를 상기 리드/라이트제어회로의 출력신호에 대응하여 출력하는 제1과정과, 상기 입출력라인제어회로를 통해 공급되는 테이타를 입력하고 이 입력에 응답하여 노멀모드인에이블부가 노멀모드인에이블신호를 상기 리드/라이트제어회로의 출력신호에 대응하여 출력하는 제2과정과, 상기 번-인모드인에이블신호를 상기 리드/라이트제어회로의 출력신호에 대응하여 출력하는 제2과정과, 상기 번-인모드인에이블신호의 출력신호의 입력에 대응하여 절단되는 제1퓨우즈를 포함하는 번-인신호발생부가 상기제1퓨우즈의 절단동작에 대응하여 절단되는 제2퓨우즈를 포함하는 번-인제어신호발생부가 상기 제2퓨우즈의 절단동작에 대응하여 번-인제어신호를 발생시켜 상기 번-인모드인에이블부와 노멀모드인에이블부로 공급하는 제4과정을 구비하여 동일칩상의 번-인테스트를 칩의 패키지공정 후에 수행함을 특징으로 하는 반도체메모리장치의 번-인방법

#### 청구항 18

제17항에 있어서, 상기 번-인신호발생부가 상기 번-인신호를 동일칩상의 모든 행디코오더와 열디코오더에 공급하여 번-인테스트시 상기 메모리쎌어레이에 저장된 모든 메모리쎌의 번-인테스트가 동시에 이루어지도록 함을 특징으로 하는 반도체메모리장치의 번-인방법.

#### 청구항 19

제17항에 있어서, 상기 반도체메모리장치가, 상기 제1퓨우즈가 상기 번-인모드인에이블신호에 대응하여 절단될시에는 번-인테스트가 이루어지고, 상기 제2퓨우즈가 상기 노멀모드인에이블신호에 대응하여 또한 절단될시에는 노멀모드로 진행됨을 특징으로 하는 반도체메모리장치의 번-인방법

### 청구항 20

제19항에 있어서, 상기 반도체메모리장치가, 상기 제1퓨우즈와 제2퓨우즈가 모두 절단되지 않을 시에는 노멀모드로 진행됨을 특징으로 하는 반도체메모리장치의 번-인방법.

### 청구항 21

메모리쎌이 행과 열방향으로 각각 다수개로씩 저장되는 메모리쎌어레이와, 상기 메모리쎌어레이의 행을 선택하는 행디코오더와, 상기 메모리쎌어레이의 열을 선택하여 열디코오더와, 동일칩상에 형성되는 데이 타 입출력핀과 상기 메모리쎌어레이의 열과의 사이에 형성되고 상기 데이타입출력핀을 통해 입출력되는 데이타를 전송하는 입출력라인제어회로와, 상기 메모리쎌어레이내의 데이타의 입출력을 제어하기 위한 신호를 상기 입출력라인으로 공급하는 리드/라이트제어회로를 가지는 반도체메모리장치에 있어서, 상기 입출력라인제어회로를 통해 공급되는 데이타를 입력하고 이 입력에 응답하여 번-인모드인에이블부가 번-인모드인에이블신호를 상기 리드/라이트제어회로의 출력신호에 대응하여 출력하는 제1과정과, 상기 입출 력라인 제어회로를 통해 공급되는 데이타를 입력하고 이 입력에 응답하여 노멀모드인에이블가 노멀모드 인에이블신호를 상기 리드/라이트제어회로의 출력신호에 대응하여 출력하는 제2과정과, 상기 번-인모드 인에이볼신호의 출력신호의 입력에 대응하여 절단되는 제1퓨우즈를 포함하는 번-인신호발생부가 상기 제1퓨우즈의 절단동작에 대응하여 번-인신호를 발생시켜 상기 행디코오더와 열코오더로 공급하는 제3과 정과. 상기 노멀모드인에이블신호의 출력신호의 입력에 대응하여 절단되는 제2퓨우즈를 포함하는 번-인 제어신호발생부가 상기 제2퓨우즈의 절단동작에 대응하여 번-인제어신호를 발생시켜 상기 번-인모드인에 불부와 노멀모드인에이블부로 공급하는 제4과정과, 제1패드와 제2때드와의 사이에 전류경로가 형성된 제1다이오드군과 상기 제1패드와 제3패드와의 사이에 전류경로가 형성된 제2다이오드군을 포함하는 모드 판독회로를 가지고 상기 제1패드와 제2패드와 제3패드에 각각 전압을 공급하여 발생되는 누수전류를 통 해서 동일칩의 번-인모드진입여부를 판독하는 제5과정을 구비함을 특징으로 하는 반도체메모리장치의 번-인방법

#### 청구항 22

제21항에 있어서, 제21항에 있어서, 상기 번-인신호발생부가 상기 번-인신호를 동일칩상의 모든 행디코 오더와 열디코오더에 공급하여 번-인테스트시 상기 메모리쎌어레이에 저장된 모든 메모리쎌의 번-인 테 스트가 동시에 이루어지도록 함을 특징으로 하는 반도체메모리장치의 번-인방법

#### 청구항 23

제21항에 있어서, 상기 반도체메모리장치가, 상기 제1퓨우즈가 상기 번-인모드인에이블신호에 대응하여 절단될시에는 번-인테스트가 이루어지고, 상기 제2퓨우즈가 상기 노멀모드인에이블신호에 대응하여 또한 절단될시에는 노멀모드로 진행됨을 특징으로 하는 반도체메모리장치의 번-인방법.

# 청구항 24

제23항에 있어서, 상기 반도체메모리장치가, 상기 제1퓨우즈와 제2퓨우즈가 모두 절단되지 않을 시에는

노멀모드로 진행됨을 특징으로 하는 반도체메모리장치의 번-인방법.

※ 참고사항 : 최초출원 내용에 의하여 공개하는 것임.

# 도면

# 도면1

# 도면2

# 도면3