# (19)대한민국특허청(KR) (12) 공개특허공보(A)

(51) . Int. Cl. *GO2F 1/1343* (2006.01)

(11) 공개번호

10-2007-0076791

(43) 공개일자

2007년07월25일

(21) 출원번호10-2006-0006091(22) 출원일자2006년01월20일

심사청구일자

없음

(71) 출원인 삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자 이홍우

충남 천안시 봉명동 청솔3차아파트 301동 906호

이계헌

충남 천안시 불당동 대원칸타빌아파트 608동 302호

이종화

경기 안양시 동안구 달안동 샛별아파트 602동 1705동

송선옥

충남 천안시 성정동 610-1

(74) 대리인 박영우

전체 청구항 수 : 총 8 항

## (54) 표시 기판

#### (57) 요약

표시 패널의 상,하단간 게이트 신호의 RC 릴레이 편차를 개선하기 위한 표시 기판이 개시된다. 본 발명에 따른 표시 기판은 게이트 회로부, 배선부, 제1 추가 배선 및 제2 추가 배선, 제1 내지 제4 연결 배선을 포함한다. 게이트 회로부는 복수의스테이지로 이루어진다. 배선부는 접지 전압이 인가되는 접지 배선과, 각각 제1 클럭 신호 및 제2 클럭 신호가 인가되는 제1 클럭 배선 및 제2 클럭 배선를 포함한다. 제1 연결 배선 및 제2 연결 배선은 제1 클럭 배선의 상,하단에서 제1 클럭 배선과 제1 추가 배선을 전기적으로 연결하고, 제3 연결 배선 및 제4 연결 배선은 제2 클럭 배선의 상,하단에서 제2 클럭 배선과 제2 추가 배선을 전기적으로 연결한다. 이에 따라 제1 클럭 신호 및 제2 클럭 신호는 클럭 배선의 상단과 함께 하단으로도 입력됨으로써, 클럭 신호의 RC 딜레이 편차를 개선하여 상,하단간 게이트 신호의 RC 딜레이 편차를 개선할 수 있다.

#### 대표도

도 2

### 특허청구의 범위

## 청구항 1.

게이트 배선들과 데이터 배선들에 의해 정의되는 복수의 화소부들;

상기 게이트 배선들에 게이트 신호를 출력하는 게이트 회로부;

상기 게이트 회로부와 인접하여 형성되며, 제1 클럭 배선, 제2 클럭 배선, 접지 배선을 포함하는 배선부;

상기 배선부의 일측에 형성되는 제1 추가 배선 및 제2 추가 배선; 및

상기 제1 추가 배선과 상기 제1 클럭 배선을 전기적으로 연결하는 제1 연결 배선 및 제2 연결 배선과, 상기 제2 추가 배선과 상기 제2 클럭 배선을 전기적으로 연결하는 제3 연결 배선 및 제4 연결 배선을 포함하는 것을 특징으로 하는 표시 기판.

## 청구항 2.

제 1항에 있어서, 상기 제1 연결 배선 및 제3 연결 배선은 상기 제1 클럭 배선 및 제2 클럭 배선의 상단부에 연결되고, 상기 제2 연결 배선 및 제4 연결 배선은 상기 제1 클럭 배선 및 제2 클럭 배선의 하단부에 연결되는 것을 특징으로 하는 표시기판.

## 청구항 3.

제 2항에 있어서, 상기 제1 추가 배선 및 제2 추가 배선은 상기 제1 클럭 배선 및 제2 클럭 배선과 동일 층에 형성되는 것을 특징으로 하는 표시 기판.

### 청구항 4.

제 2항에 있어서, 상기 제1 추가 배선 및 제2 추가 배선은 상기 접지 배선과 동일 층에 형성되는 것을 특징으로 하는 표시 기판.

## 청구항 5.

제 2항에 있어서, 상기 제2 연결 배선 및 제4 연결 배선은 상기 제1 추가 배선 및 제2 추가 배선과 동일 층에 형성되고, 제1 연결 배선 및 제3 연결 배선은 상기 제1 클럭 배선, 제2 클럭 배선 및 접지 배선과 다른 층에 형성되는 것을 특징으로 하는 표시 기판.

## 청구항 6.

제 1항에 있어서, 상기 회로부는 중속적으로 연결된 복수의 스테이지들을 포함하는 것을 특징으로 하는 표시 기판.

#### 청구항 7.

제 6항에 있어서, 상기 제1 클럭 배선은 제1 인가 배선을 통해 상기 스테이지들 중 홀수 번째 스테이지들에 제1 클럭 신호를 전달하고, 상기 제2 클럭 배선은 제2 인가 배선을 통해 상기 스테이지들 중 짝수 번째 스테이지들에 제2 클럭 신호를 전달하며, 상기 접지 배선은 제3 인가 배선을 통해 각 스테이지들에 접지 전압을 전달하는 것을 특징으로 하는 표시 기판.

## 청구항 8.

제 7항에 있어서, 상기 제1 내지 제3 인가 배선은 상기 접지 배선과 동일 층에 형성되는 것을 특징으로 하는 표시 기판.

#### 명세서

## 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 액정표시장치에 관한 것으로, 보다 상세하게는 패널 상,하단 간에 발생하는 게이트 신호의 딜레이 편차를 개선하기 위한 액정표시장치에 관한 것이다.

일반적으로 표시장치는 표시 패널, 표시 패널의 게이트 배선으로 게이트 신호를 출력하는 게이트 구동부, 게이트 신호에 동기하여 표시패널의 데이터 배선으로 데이터 신호를 출력하는 데이터 구동부를 포함한다. 일반적으로 게이트 및 데이터 드라이버는 집적화 하여 칩(Chip)형태로 형성된다.

최근에는 칩 형태의 게이트 구동부를 표시패널에 실장하는 과정에서 발생하는 불량을 감소시키기 위하여, 게이트 구동부 (예컨대 게이트 구동회로)를 표시패널에 직접 형성하는 구조를 채택하고 있다.

이러한 게이트 구동회로는 클럭신호 배선, 클럭바신호 배선, 접지 배선으로 이루어지는 배선부와, 종속적으로 연결된 복수의 스테이지를 갖는 하나의 쉬프트 레지스터로 이루어져 배선부로부터 제공되는 각종 신호에 응답하여 게이트 신호를 출력하는 회로부를 포함한다. 각 스테이지들은 배선들에서 연장 형성된 복수의 연결배선을 통해 배선들과 전기적으로 연결된다.

복수의 연결배선과 클럭신호 배선, 클럭바신호 배선, 접지 배선과의 사이(예컨대 오버랩 영역)에는 기생 용량이 생성되고, 기생 용량에 의해 클럭신호 및 클럭바신호에 RC 딜레이(Delay)가 발생한다. 따라서 클럭신호 및 클럭바신호에 기초하여 출력되는 게이트 신호에도 RC 딜레이가 발생하며, 이러한 RC 딜레이는 누적되는 특성이 있으므로 표시패널의 상하단간 게이트 신호의 RC 딜레이에 편차가 발생한다.

이러한 RC 딜레이 편차는 표시장치를 대형화, 고해상도화 및 고주파 구동 등을 적용함에 있어 패널을 특성을 저하시키는 문제점이 있다.

#### 발명이 이루고자 하는 기술적 과제

이에 본 발명의 기술적 과제는 이러한 종래의 문제점을 해결하기 위한 것으로, 본 발명의 목적은 게이트 신호의 상,하단간 RC 딜레이 편차를 개선하기 위한 표시 기판을 제공하는 것이다.

#### 발명의 구성

상기한 본 발명의 목적을 실현하기 위한 하나의 실시예에 따른 표시 기판은 복수의 화소부들, 게이트 회로부, 배선부, 제1추가 배선 및 제2추가 배선, 제1연결 배선, 제2연결 배선, 제3연결 배선 및 제4연결 배선을 포함한다. 상기 복수의 화소부들은 게이트 배선들과 데이터 배선들에 의해 정의되고, 상기 게이트 회로부는 상기 게이트 배선들에 게이트 신호를 출력한다. 상기 배선부는 상기 게이트 회로부와 인접하여 형성되며, 제1클릭 배선, 제2클릭 배선, 접지 배선을 포함한다. 상기제1추가 배선 및 제2추가 배선은 상기배선부의 일측에 형성된다. 상기제1연결 배선 및 제2연결 배선은 상기제1추가 배선과 제1클릭 배선을 전기적으로 연결하고, 제3연결 배선 및 제4연결 배선은 상기제2추가 배선과 제2클릭 배선을 전기적으로 연결하고, 제3연결 배선 및 제4연결 배선은 상기제2추가 배선과 제2클릭 배선을 전기적으로 연결한다.

이러한 표시 기판에 의하면, 클럭 신호를 클럭 배선의 상단 및 하단으로 인가함으로써, 상하단간 클럭 신호의 RC 딜레이 편차를 개선하여 상,하단간 게이트 신호의 RC 딜레이 편차를 개선 할 수 있다.

이하, 첨부한 도면들을 참조하여, 본 발명을 보다 상세하게 설명하고자 한다.

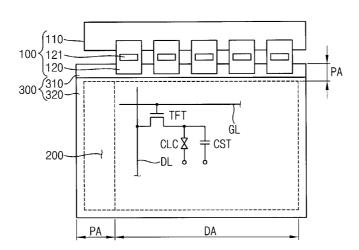

도 1은 본 발명에 따른 표시장치를 개략적으로 도시한 도면이다.

도시한 바와 같이, 본 발명에 따른 표시장치는 표시 패널(300), 게이트 구동부(200) 및 데이터 구동부(100)를 포함한다.

데이터 구동부(100)는 구동회로가 실장된 인쇄회로기판(110), 인쇄회로기판(110)과 표시 패널(300)을 전기적으로 연결하는 연성인쇄회로기판(120)을 포함한다. 연성인쇄회로기판(120)에는 데이터 구동칩(130)이 탑재되어 데이터 배선(DL)들에 데이터 신호를 출력한다.

표시 패널(300)은 대향하는 제1 기판 및 제2 기판(310, 320)과, 제1 기판 및 제2 기판(310, 320) 사이에 개재된 액정층 (미도시)을 포함하며, 표시 영역(DA)과 표시 영역(DA)을 둘러싸는 비표시 영역(PA)으로 이루어진다. 표시 영역(DA)에는 교차 형성되는 게이트 배선들 및 데이터 배선들(GL, DL)에 의해 복수개의 화소부가 형성되다. 각 화소부에는 박막트랜지 스터(TFT), 액정 커패시터 및 스토리지 커패시터(CLC, CST)가 형성되며, 액정 커패시터 및 스토리지 커패시터(CLC, CST)는 박막트랜지스터(TFT)와 전기적으로 연결된다.

게이트 구동부(200)는 제1 기판(310)의 비표시 영역(PA)에 실장되며, 복수의 스테이지들이 종속적으로 연결된 하나의 쉬프트 레지스터로 이루어져, 게이트 배선들(GL)에 게이트 신호를 출력한다.

이하, 첨부된 도면을 참조하여 각 실시예에 따른 표시 기판(예컨대 제1 기판)에 대하여 상세히 설명한다.

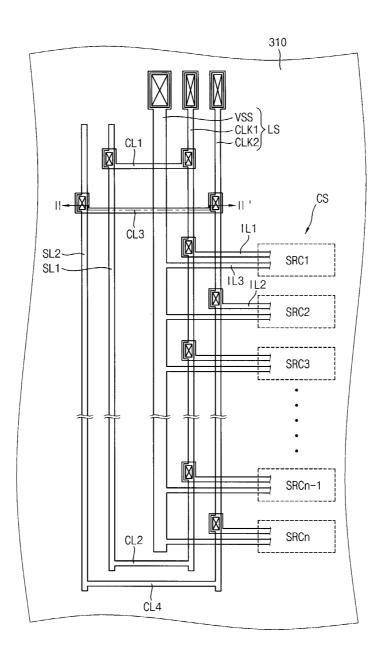

도 2는 본 발명의 제1 실시예에 따른 표시 기판 일부의 개략적인 평면도이다.

도 1 및 도 2를 참조하면, 본 발명의 제1 실시예에 따른 표시 기판은 게이트 회로부(CS), 배선부(LS), 제1 추가 배선 및 제 2 추가 배선(SL1, SL2), 제1 연결 배선(CL1), 제2 연결 배선(CL2), 제3 연결 배선 및 제4 연결 배선(CL3, CL4)을 포함한 다.

게이트 회로부(CS)는 종속적으로 연결된 복수의 스테이지(SRC1 ~ SRCn)를 포함한다. 각 스테이지(SRC1 ~ SRCn)는 게이트 배선(GL)들과 일대일 대응하여 연결되며, 입력받은 클럭 신호에 기초하여 게이트 배선(GL)으로 게이트 신호를 출력한다. 구체적으로는 홀수 번째 스테이지들은 제1 클럭 신호를 입력받고, 짝수 번째 스테이지들은 제1 클럭 신호와 위상이반대(예컨대 위상차가 180°)인 제2 클럭 신호를 입력받는다. 즉, 홀수 번째 스테이지들은 제1 클럭 신호에 기초하여 홀수번째 게이트 배선(GL)들에 게이트 신호를 출력하고, 짝수 번째 스테이지(SRC)들은 제2 클럭 신호에 기초하여 짝수 번째 게이트 배선(GL)들에 게이트 신호를 출력한다. 한편, 각 스테이지(SRC1 ~ SRCn)들은 접지 전압을 비롯한 제어신호들을 입력받아 순차적으로 구동한다.

배선부(LS)는 게이트 회로부(CS)의 일측으로 인접하여 형성되며, 제1 클럭 신호가 인가되는 제1 클럭 배선(CLK1), 제2 클럭 신호가 인가되는 제2 클럭 배선(CLK2), 접지 전압이 인가되는 접지 배선(VSS)을 포함한다. 제1 클럭 배선(CLK1)은 제1 인가 배선(IL1)을 통해 홀수 번째 스테이지들에 제1 클럭 신호를 제공하고, 제2 클럭 배선(CLK2)은 제2 인가 배선 (IL2)을 통해 짝수 번째 스테이지들에 제2 클럭 신호를 제공한다. 접지 배선(VSS)은 연장 형성되는 제3 인가 배선(IL3)을 통해 각 스테이지(SRC1 ~ SRCn)에 접지 전압을 제공한다.

제1 추가 배선 및 제2 추가 배선(SL1, SL2)은 배선부(LS)의 일측으로 형성되며, 제1 추가 배선(SL1)은 제1 클릭 배선 (CLK1)과 전기적으로 연결되고, 제2 추가 배선(SL2)은 제2 클릭 배선(CLK2)과 전기적으로 연결된다. 구체적으로는 제1 추가 배선(SL1)은 제1 연결 배선 및 제2 연결 배선(CL1, CL2)을 통해 제1 클릭 배선(CLK1)과 전기적으로 연결되고, 제2 추가 배선(SL2)은 제3 연결 배선 및 제4 연결 배선(CL3, CL4)을 통해 제2 클릭 배선(CLK2)과 전기적으로 연결된다.

즉, 제1 내지 제4 연결 배선(CL1, CL2, CL3, CL4)은 추가 배선(SL1, SL2)과 클릭 배선(CLK1, CLK2)을 전기적으로 연결 시키며, 제1 연결 배선 및 제3 연결 배선(CL1, CL3)은 각각 제1 클릭 배선(CLK1) 및 제2 클릭 배선(CLK2)의 상단부(예 컨대 최전단 스테이지 이전)에 연결되고, 제2 연결 배선 및 제4 연결 배선(CL2, CL4)은 각각 제1 클릭 배선(CLK1) 및 제2 클릭 배선(CLK2)의 하단부(예컨대 마지막단 스테이지 이후)에 연결된다.

따라서 제1 클럭 신호는 제1 클럭 배선(CLK)의 상단으로 인가됨과 아울러 제1 추가 배선(SL1)과 제1 연결 배선 및 제2 연결 배선(CL1, CL2)을 통해 제1 클럭 배선(CLK1)의 하단으로도 인가된다. 마찬가지로 제2 클럭 신호는 제2 클럭 배선 (CLK2)의 상단으로 인가됨과 아울러 제2 추가 배선(SL2)과 제3 연결 배선 및 제4 연결 배선(CL3, CL4)을 통해 제2 클럭 배선(CLK2)의 하단으로도 인가된다. 이 때, 추가 배선들(SL1, SL2) 및 연결 배선들(CL1, CL2, CL3, CL4)의 자체 저항은 클럭 신호에 거의 영향을 미치지 못하므로, 제1 클럭 신호 및 제2 클럭 신호는 각각 제1 클럭 배선 및 제2 클럭 배선 (CLK1, CLK2)의 상단 및 하단으로 동일하게 인가되는 것과 같아진다.

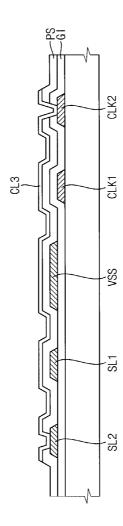

도 3은 도 2의 Ⅱ-Ⅱ'선을 따라 자른 단면도이다.

도 2 및 도 3을 참조하면, 기판 상에 제1 클릭 배선(CLK1), 제2 클릭 배선(CLK2), 제1 추가 배선(SL1), 제2 추가 배선 (SL2), 제2 연결 배선 및 제4 연결 배선(CL2, CL4)은 제1 금속물질로 이루어져 제1 층에 형성된다. 제1 인가 배선(IL1), 제2 인가 배선(IL2), 제3 인가 배선(IL3) 및 접지 배선(VSS)은 제2 금속물질로 이루어져 제1 층과 다른 제2 층에 형성된다. 제1 연결 배선 및 제3 연결 배선(CL1, CL3)은 제3 금속물질로 이루어져 제1 층 및 제2 층과 다른 제3 층에 형성된다.

구체적으로는 기판 상에 제1 금속물질로 이루어진 제1 클릭 배선(CLK1), 제2 클릭 배선(CLK2), 제1 추가 배선(SL1), 제2 추가 배선(SL2), 제2 연결 배선 및 제4 연결 배선(CL2, CL4)이 형성되며, 일 예로 제1 금속물질은 알루미늄(AI) 또는 알루미늄 합금을 포함한다. 여기서 제2 연결 배선(CL2)은 제1 추가 배선(SL1)에서 연장 형성되어 제1 클릭 배선(CLK1)과 직접 연결되며, 제4 연결 배선(CL2)은 제2 추가 배선(SL2)에서 연장 형성되어 제2 클릭 배선(CLK2)과 직접 연결된다. 이후 기판의 전면에 걸쳐 게이트 절연막(GI)이 형성되어 제1 클릭 배선(CLK1), 제2 클릭 배선(CLK2), 제1 추가 배선(SL1), 제2 추가 배선(SL2), 제2 연결 배선 및 제4 연결 배선(CL2, CL4)은 게이트 절연막(GI)에 의해서 커버된다.

게이트 절연막(GI) 상에 제2 금속물질로 이루어진 접지 배선(VSS), 제1 인가 배선(IL1), 제2 인가 배선 및 제3 인가 배선 (IL2, IL3)이 형성되며, 일 예로 제2 금속물질은 크롬(Cr)을 포함한다. 이 때, 도시하진 않았지만 제1 인가 배선(IL1)은 제1 클럭 배선(CLK1)의 일부가 노출된 컨택홀을 통해 제1 클럭 배선(CLK1)과 연결되어 제1 클럭 배선(CLK1)과 홀수 번째 스테이지를 전기적으로 연결한다. 또한, 제2 인가 배선(IL2)은 제2 클럭 배선(CLK2)의 일부가 노출된 컨택홀을 통해 제2 클럭 배선(CLK2)과 연결되어 제2 클럭 배선(CLK2)과 짝수 번째 스테이지를 전기적으로 연결한다. 제3 인가 배선(IL3)은 접지 배선(VSS)에서 연장 형성되어 접지 배선(VSS)과 각 스테이지(SRC1 ~ SRCn)를 전기적으로 연결한다. 접지 배선 (VSS)과 제1 내지 제3 인가 배선(IL1, IL2, IL3)은 기판의 전면에 걸쳐 형성되는 보호막(PS)에 의해 커버된다.

보호막(PS) 상에 제3 금속물질로 이루어진 제1 연결 배선 및 제3 연결 배선(CL1, CL3)이 형성되며, 일 예로 제3 금속물질은 인듐 틴 옥사이드(ITO)를 포함한다. 제1 연결 배선(CL1)은 제1 클럭 배선(CLK1)의 일부가 노출되는 컨택홀과, 제1 추가 배선(SL1)의 일부가 노출되는 컨택홀을 통해 제1 클럭 배선(CLK1)과 제1 추가 배선(SL1)을 전기적으로 연결한다. 제3 연결 배선(CL3)은 제2 클럭 배선(CLK2)의 일부가 노출되는 컨택홀과, 제2 추가 배선(SL2)의 일부가 노출되는 컨택홀을 통해 제2 클럭 배선(CLK2)과 제2 추가 배선(SL2)을 전기적으로 연결한다.

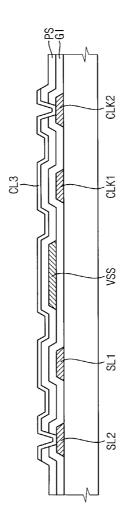

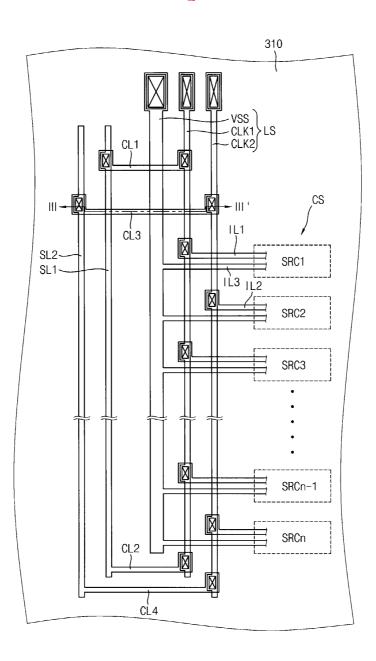

도 4는 본 발명의 제2 실시예에 따른 표시 기판 일부의 개략적인 평면도이고, 도 5는 도 4의 Ⅲ-Ⅲ'선을 따라 자른 단면도이다.

도시한 바와 같이, 본 발명의 제2 실시예에 따른 표시 기판은 게이트 회로부(CS), 배선부(LS), 제1 추가 배선 및 제2 추가 배선(SL1, SL2), 제1 연결 배선(CL1), 제2 연결 배선(CL2), 제3 연결 배선 및 제4 연결 배선(CL3, CL4)을 포함한다.

이하, 설명의 편의를 위하여 제1 실시예와의 차이점 위주로 제2 실시예를 설명한다.

도 4 및 도 5를 참조하면, 기판 상에 제1 클럭 배선 및 제2 클럭 배선(CLK1, CLK2)은 제1 금속물질로 이루어져 제1 층에 형성된다. 접지 배선(VSS), 제1 인가 배선(IL1), 제2 인가 배선(IL2), 제3 인가 배선(IL3), 제1 추가 배선(SL1), 제2 추가 배선(SL2), 제2 연결 배선 및 제4 연결 배선(CL2, CL4)은 제2 금속물질로 이루어져 제1 층과 다른 제2 층에 형성된다. 제1 연결 배선 및 제3 연결 배선(CL1, CL3)은 제3 금속물질로 이루어져 제1 층 및 제2 층과 다른 제3 층에 형성된다.

이 때, 제2 연결 배선(CL2)은 제1 추가 배선(SL1)에서 연장 형성되어 제1 클럭 배선(CLK1)의 일부가 노출되는 컨택홀을 통해 제1 추가 배선(SL1)과 제1 클럭 배선(CLK1)을 전기적으로 연결한다. 제4 연결 배선(CL4)은 제2 추가 배선(SL2)에서 연장 형성되어 제2 클럭 배선(CLk2)의 일부가 노출되는 컨택홀을 통해 제2 추가 배선(SL2)과 제2 클럭 배선(CLK2)을 전기적으로 연결한다.

구체적으로는 기판 상에 제1 금속물질로 이루어진 제1 클럭 배선 및 제2 클럭 배선(CLK1, CLK2)이 형성되며, 일 예로 제1 금속물질은 알루미늄(Al) 또는 알루미늄 합금을 포함한다. 제1 클럭 배선 및 제2 클럭 배선(CLK1, CLK2)은 이후 기판 전면에 걸쳐 형성되는 게이트 절연막(GI)에 의해 커버된다.

게이트 절연막(GI) 상에 제2 금속물질로 이루어진 접지 배선(VSS), 제1 내지 제3 인가 배선(IL1, IL2, IL3), 제1 추가 배선(SL1), 제2 추가 배선(SL2), 제2 연결 배선 및 제4 연결 배선(CL2, CL4)이 형성되며, 일 예로 제2 금속물질은 크롬(Cr)을 포함한다. 제1 내지 제3 인가 배선(IL1, IL2, IL3)은 제1 실시예의 경우와 동일하게 구성된다.

여기서, 제2 연결 배선(CL2)은 제1 추가 배선(SL1)에서 연장 형성되며, 제1 클릭 배선(CLK1)의 일부가 노출되는 컨택홀을 통해 제1 클릭 배선(CLK2)과 연결됨으로써, 제1 추가 배선(SL1)과 제1 클릭 배선(CLK1)을 전기적으로 연결한다. 제4 연결 배선(CL4)은 제2 추가 배선(SL2)에서 연장 형성되며, 제2 클릭 배선(CLK2)의 일부가 노출되는 컨택홀을 통해 제2 클릭 배선(CLK2)과 연결됨으로써, 제2 추가 배선(SL2)과 제2 클릭 배선(CLK2)을 전기적으로 연결한다.

제1 추가 배선 및 제2 추가 배선(SL1, SL2)이 형성된 기판의 전면에 걸쳐서 보호막(PS)이 형성되어, 접지 배선(VSS), 제1 내지 제3 인가 배선(SL1, SL2), 제1 추가 배선(SL1), 제2 추가 배선(SL2), 제2 연결 배선 및 제4 연결 배선(CL2, CL4)은 보호막(PS)에 의해 커버된다.

보호막(PS) 상에 제3 금속물질로 이루어진 제1 연결 배선 및 제3 연결 배선(CL1, CL3)이 형성되며, 일 예로 제3 금속물질은 인듐 틴 옥사이드(ITO)를 포함한다. 제1 연결 배선(CL1)은 컨택홀들을 통해 제1 추가 배선(SL1)과 제1 클럭 배선(CLK1)을 전기적으로 연결하며, 제3 연결 배선(CL3)은 컨택홀들을 통해 제2 추가 배선(SL2)과 제2 클럭 배선(CL2)을 전기적으로 연결한다.

#### 발명의 효과

이상에서 설명한 바와 같이, 본 발명에 따르면 클럭 배선의 상단으로만 입력되는 클럭 신호를 추가 배선 및 연결 배선을 이용하여 클럭 배선의 상단 및 하단으로 입력함으로써, 패널의 상,하단간 게이트 신호의 RC 딜레이 편차를 개선한다.

이상에서는 실시예를 참조하여 설명하였지만, 해당 기술 분야의 숙련된 당업자는 하기의 특허 청구의 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

## 도면의 간단한 설명

도 1은 본 발명에 따른 표시장치를 개략적으로 도시한 도면이다.

도 2는 본 발명의 제1 실시예에 따른 표시 기판 일부의 개략적인 평면도이다.

도 3은 도 2의 Ⅱ-Ⅱ'선을 따라 자른 단면도이다.

도 4는 본 발명의 제2 실시예에 따른 표시 기판 일부의 개략적인 평면도이다.

도 5는 도 4의 Ⅲ-Ⅲ'선을 따라 자른 단면도이다.

<도면의 주요부분에 대한 부호의 설명>

CLK1: 제1 클럭 배선 CLK2: 제2 클럭 배선

VSS: 접지 배선 SL1:제1 추가 배선

SL2: 제2 추가 배선 CL1: 제1 연결 배선

CL2: 제2 연결 배선 CL3: 제3 연결 배선

CL4: 제4 연결 배선 IL1: 제1 인가 배선

IL2: 제2 인가 배선 IL3: 제3 인가 배선

SRC1 ~ SRCn: 스테이지

도면5