# (19) World Intellectual Property **Organization**

International Bureau

(10) International Publication Number WO 2020/147545 A1

- (51) International Patent Classification: H04N 19/117 (2014.01)

- (21) International Application Number:

PCT/CN2019/128631

(22) International Filing Date:

26 December 2019 (26.12.2019)

(25) Filing Language:

English

(26) Publication Language:

English

(30) Priority Data:

62/791,963 14 January 2019 (14.01.2019) US 62/792,489 15 January 2019 (15.01.2019) US

- (71) Applicant: MEDIATEK INC. [CN/CN]; No. 1, Dusing 1st Rd., Hsinchu Science Park, Hsinchu City, Taiwan 30078

- (72) Inventors: LIN, Sheng-Yen; No. 1, Dusing 1st Rd., Hsinchu Science Park, Hsinchu City, Taiwan 30078 (CN). LIN, Jian-Liang; No. 1, Dusing 1st Rd., Hsinchu Science Park, Hsinchu City, Taiwan 30078 (CN). LIU, Lin; No. 6 Park, Jiuxianqiao Road, Chaoyang District Building 1-B, Beijing 100015 (CN).

- (74) Agent: BEIJING SANYOU INTELLECTUAL PROP-ERTY AGENCY LTD.; 16th Fl., Block A, Corporate Square, No. 35 Jinrong Street, Beijing 100033 (CN).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AO, AT, AU, AZ, BA, BB, BG, BH, BN, BR, BW, BY, BZ, CA, CH, CL, CN, CO, CR, CU, CZ, DE, DJ, DK, DM, DO, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, GT, HN. HR, HU, ID, IL, IN, IR, IS, JO, JP, KE, KG, KH, KN, KP, KR, KW, KZ, LA, LC, LK, LR, LS, LU, LY, MA, MD, ME, MG, MK, MN, MW, MX, MY, MZ, NA, NG, NI, NO, NZ, OM, PA, PE, PG, PH, PL, PT, QA, RO, RS, RU, RW, SA, SC, SD, SE, SG, SK, SL, SM, ST, SV, SY, TH, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LR, LS, MW, MZ, NA, RW, SD, SL, ST, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, RU, TJ, TM), European (AL, AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HR, HU, IE, IS, IT, LT, LU, LV, MC, MK, MT, NL, NO, PL, PT, RO, RS, SE, SI, SK, SM, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, KM, ML, MR, NE, SN, TD, TG).

#### (54) Title: METHOD AND APPARATUS OF IN-LOOP FILTERING FOR VIRTUAL BOUNDARIES

**~** 1310

**~** 1320

Signalling a first syntax in a bitstream at an encoder side or parsing the first syntax from the bitstream at a decoder side, wherein the first syntax indicates whether a loop filtering process is disabled for one or more virtual boundaries in a corresponding region

Receiving a reconstructed filtered unit in a current picture, wherein the reconstructed filtered unit is associated with a loop filter and the reconstructed filtered unit comprises reconstructed pixels for applying the loop filtering process associated with the loop filter to a current reconstructed pixel: wherein when the first syntax is true, the loop filter processing is disabled when the reconstructed filter unit is across said one or more virtual boundaries in the corresponding region; and when the first syntax is false, the loop filter processing is not disabled when the reconstructed filter unit is across the virtual boundary

Fig. 13

(57) Abstract: Method and apparatus of coding a video sequence are disclosed. According to this method, a first syntax is signalled in or parsed from a bitstream, where the first syntax indicates whether a loop filtering process is disabled for one or more virtual boundaries in a corresponding region. A reconstructed filter unit in a current picture is received, wherein the reconstructed filter unit is associated with the loop filter and the reconstructed filter unit comprises reconstructed pixels for applying a loop filtering process associated with the loop filter to a current reconstructed pixel. When the first syntax is true, the loop filter processing is disabled when the reconstructed filter unit is across said one or more virtual boundaries in the corresponding region. When the first syntax is false, the loop filter processing is not disabled when the reconstructed filter unit is across the virtual boundary.

#

## Published:

— with international search report (Art. 21(3))

# METHOD AND APPARATUS OF IN-LOOP FILTERING FOR VIRTUAL BOUNDARIES

# CROSS REFERENCE TO RELATED APPLICATIONS

[0001] The present invention claims priority to U.S. Provisional Patent Application, Serial No. 62/791,963, filed on January 14, 2019 and U.S. Provisional Patent Application, Serial No. 62/792,489, filed on January 15, 2019. The U.S. Provisional Patent Applications are hereby incorporated by reference in their entireties.

# **TECHNICAL FIELD**

10 **[0002]** The present invention relates to picture processing for pictures containing one or more virtual boundaries such as 360-degree virtual reality (VR360) pictures. In particular, the present invention relates to syntax design for in-loop filtering process at discontinued edges or virtual boundaries for pictures containing one or more virtual boundaries such as VR360 video.

15

20

25

5

## **BACKGROUND**

[0003] The 360-degree video, also known as immersive video is an emerging technology, which can provide "feeling as sensation of present". The sense of immersion is achieved by surrounding a user with wrap-around scene covering a panoramic view, in particular, 360-degree field of view. The "feeling as sensation of present" can be further improved by stereographic rendering. Accordingly, the panoramic video is being widely used in Virtual Reality (VR) applications.

[0004] The 360-degree virtual reality (VR) pictures may be captured using a 360-degree spherical panoramic camera or multiple pictures arranged to cover all field of views around 360 degrees. The three-dimensional (3D) spherical picture is difficult to process or store using the conventional picture/video processing devices. Therefore, the 360-degree VR pictures are often converted to a two-dimensional (2D) format

using a 3D-to-2D projection method, such as EquiRectangular Projection (ERP) and CubeMap Projection (CMP). Besides the ERP and CMP projection formats, there are various other VR projection formats, such as OctaHedron Projection (OHP), icosahedron projection (ISP), Segmented Sphere Projection (SSP) and Rotated Sphere Projection (RSP) that are widely used in the field.

5

20

25

30

[0005] The VR360 video sequence usually requires more storage space than the conventional 2D video sequence. Therefore, video compression is often applied to VR360 video sequence to reduce the storage space for storage or the bit rate for streaming/transmission.

10 [0006] The High Efficiency Video Coding (HEVC) standard is developed under the joint video project of the ITU-T Video Coding Experts Group (VCEG) and the ISO/IEC Moving Picture Experts Group (MPEG) standardization organizations, and is especially with partnership known as the Joint Collaborative Team on Video Coding (JCT-VC). VR360 video sequences can be coded using HEVC. However, the present invention may also be applicable for other coding methods.

[0007] In HEVC, one slice is partitioned into multiple coding tree units (CTU). For colour pictures, a colour slice may be partitioned into multiple coding tree blocks (CTB). The CTU is further partitioned into multiple coding units (CUs) to adapt to various local characteristics. HEVC supports multiple Intra prediction modes and for Intra coded CU, the selected Intra prediction mode is signalled. In addition to the concept of coding unit, the concept of prediction unit (PU) is also introduced in HEVC. Once the splitting of CU hierarchical tree is done, each leaf CU is further split into one or more prediction units (PUs) according to prediction type and PU partition. After prediction, the residues associated with the CU are partitioned into transform blocks, named transform units (TUs) for the transform process.

[0008] While the coding process can effectively reduce required bandwidth for transmission or required capacity for storage, the coding process often introduces coding noise referred as coding artefacts. In order to alleviate the coding artefact, various filtering techniques, such as de-blocking filter, SAO (sample adaptive offset) and ALF (adaptive loop filter), have been introduced. The filtering process is often applied to reconstructed pictures that are later used as reference pictures. In other words, the filtering process is inside the coding loop. Accordingly, such filtering process is also referred as in-loop filtering.

[0009] In HEVC, de-blocking filter is applied after the picture is reconstructed.

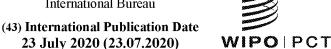

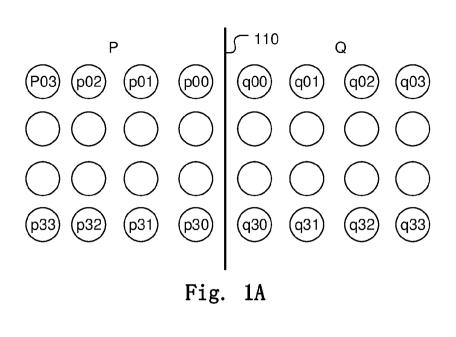

The boundaries between coding units, prediction units or transform units are filtered to alleviate the blocking artefacts caused by the block-based coding. The boundary can be a vertical or horizontal boundary. The boundary pixels involved in de-blocking filtering process for the vertical boundary (110) and horizontal boundary (120) as shown in Fig. 1A and Fig. 1B respectively. For a vertical boundary (i.e., line 110 in Fig. 1A), a horizontal filter is applied to some boundary samples in each horizontal line. For example, the horizontal de-blocking filter may be applied to p00, p01 and p02 on the left side of the vertical boundary and q00, q01 and q02 on the right side of the vertical boundary. Similarly, for a horizontal boundary (i.e., line 120 in Fig. 1B), a vertical filter is applied to some boundary samples in each vertical line. For example, the vertical de-blocking filter may be applied to p00, p01 and p02 on the top side of the horizontal boundary and q00, q01 and q02 on the bottom side of the horizontal boundary. In other words, the de-blocking filter is applied in a direction perpendicular to the boundary.

5

10

25

30

15 **[0010]** A boundary strength value, Bs is calculated for each four-sample length boundary and can take 3 possible values. Luma and chroma components are processed separately in the de-blocking process. For the Luma component, only block boundaries with Bs values equal to 1 or 2 can be filtered. In the case of chroma components, only boundaries with Bs value equal to 2 can be filtered.

20 **[0011]** For luma component, additional conditions are checked for each four-sample length boundary to determine whether de-blocking filtering should be applied and to further determine whether a normal filter or a strong filter should be applied if de-blocking is applied.

[0012] For the luma component in the normal filtering mode, two samples at each side of the boundary can be modified. In the strong filtering mode, three samples at each side of the boundary can be modified.

[0013] For the chroma component, only one sample at each side of the boundary can be modified when the boundary strength is greater than 1.

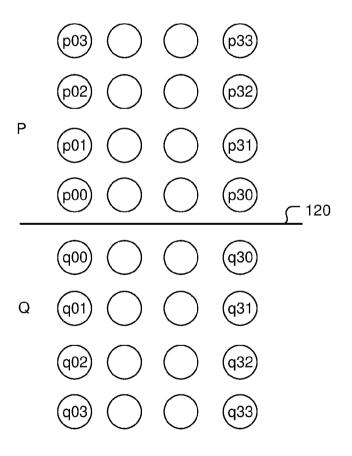

[0014] SAO processing is developed to compensate intensity level offset caused by the coding process. SAO processing adopted by HEVC consists of two methods. One is Band Offset (BO), and the other is Edge Offset (EO). BO is used to classify pixels into multiple bands according to pixel intensities and an offset is applied to pixels in one or more bands. EO is used to classify pixels into categories according to relations between a current pixel and respective neighbours and an offset is applied to

pixels in each category. There are 4 EO directional patterns (0°, 90°, 135°, and 45°) and no processing (OFF). The four EO types are shown in Fig. 2.

5

10

15

20

25

[0015] Upon classification of all pixels in a region, one offset is derived and transmitted for pixels in each category. SAO processing is applied to luma and chroma components, and each of the components is independently processed. One offset is derived for all pixels of each category except for category 4 of EO, where Category 4 is forced to use zero offset. Table 1 below lists the EO pixel classification, where "C" denotes the pixel to be classified. As shown in Table 1, the conditions associated with determining a category are related to comparing the current pixel value with two respective neighbour values according to the EO type. The category can be determined according to the comparison results (i.e., ">", "<" or "="). Each category has a special meaning in relative intensity between the current pixel and neighbouring pixels. For example, category 0 corresponds to a "valley", where the intensity of the centre pixel is lower than two neighbouring pixels. Category 3 corresponds to a "peak", where the intensity of the centre pixel is higher than two neighbouring pixels. Categories 1 and 2 correspond to a flat segment with an upward slope (Category 2) or a downward slope (Category 1).

Table 1.

| Category | Condition                               |

|----------|-----------------------------------------|

| 0        | C < two neighbours                      |

| 1        | C < one neighbour && C == one neighbour |

| 2        | C > one neighbour&& C == one neighbour  |

| 3        | C > two neighbours                      |

| 4        | None of the above                       |

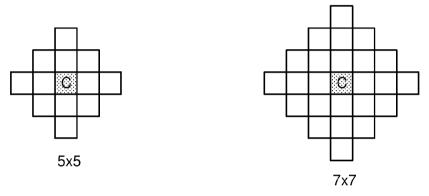

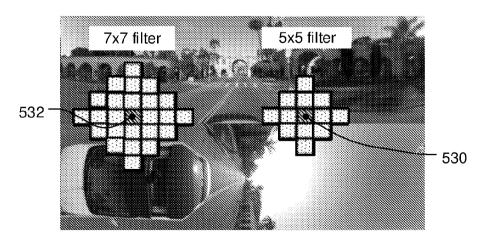

[0016] Adaptive Loop Filter (ALF) is a filter with adaptive filter size applied to the reconstructed pixels. ALF was evaluated during the HEVC standard development, but not adopted for HEVC. However, ALF is being considered by the emerging video coding standard, named VVC (Versatile Video Coding). To optimize the performance, ALF uses Wiener filtering techniques to derive filter coefficients. Furthermore, multiple filters are allowed for different picture regions. For example, the ALF can be a 5x5 filter or a 7x7 filter as shown in Fig. 3, where "C" indicates a current reconstructed pixel being filtered.

[0017] According to a conventional approach, the loop filters such as de-blocking,

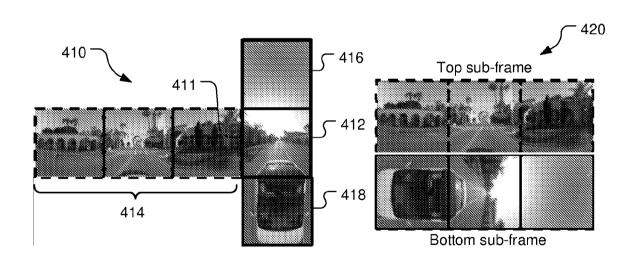

SAO and ALF will be applied to a reconstructed VR360 picture without considering the possible discontinued edges within the VR360 picture. For example, the cubemap based projection uses six faces on a cube to represent one frame in the VR360 video. The six faces corresponds to faces lifted off from the cube and fitted into different layouts, such as 1x6, 6x1, 2x3 or 3x2 layout. Among various cubemap layouts, the 3x2 layout is often used due to its coding efficiency. Fig. 4 illustrates an example of 3x2 cubemap layout formation. The layout 410 corresponds to six faces lifted off from a cube, where image412 corresponds to a front face, the three images 414 connected to the left of image 412 correspond to the other three faces connected to the front face 412 in the horizontal direction, image 416 corresponds to the face on the top of the cube and image 418 corresponds to the face on the bottom of the cube. Accordingly, the fours images including images 414 and image 412 are continuous in the horizontal direction and the three images includes image 416, image 412 and image 418 are continuous in the vertical direction. The 4x3 layout 410 contains some blank areas, which is not efficient for coding. The layout 420 corresponds to a 3x2 cubemap layout, where the three images 414 and the three vertically connected images (images 416, 412 and 418) are abutted. The top sub-frame corresponding to the three images 414 are continuous in the horizontal direction. Also, the bottom subframe corresponding to the three images 412, 416 and 418 are continuous in the horizontal direction. However, the edges 422 between the top sub-frame and the bottom sub-frame is discontinuous. In other words, a VR360 picture corresponding to a layout format from a 3D projection may contain discontinuous edge within the picture.

5

10

15

20

25

30

[0018] Besides the VR360 pictures, other picture formats may also contain discontinuous edges within the picture. For example, the Picture-In-Picture (PIP) format is a popular format to display two videos (e.g. a main video and a sub-video) on the same screen simultaneously. Therefore, for each PIP frame, discontinuity may exist between the pictures associated with the two videos. The issues of loop filtering process across the discontinuous edge exist in the VR360 pictures as well as the PIP frames.

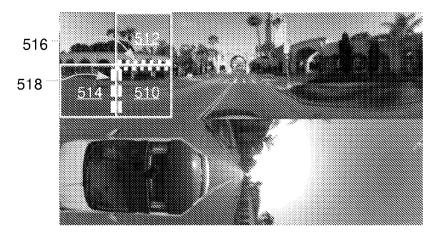

[0019] Fig. 5A to Fig. 5C illustrate examples of in-loop filters applied to a reconstructed VR360 picture. Fig. 5A illustrates an example of de-blocking filter, where the de-blocking filter is applied to a current block 510. The de-blocking filter is applied to the horizontal boundary 516 between the current block 510 and the

neighbouring block 512 above. The de-blocking filter is also applied to the vertical boundary 518 between the current block 510 and the neighbouring block 514 on the left.

[0020] Fig. 5B illustrates an example of SAO processing. The offset compensation parameters are derived based on the statistics of each coding tree unit (CTU) 520. During the statistic derivation, the BO and EO classification is applied to all pixels. For each BO and EO category, an offset value is determined. After the statistics for the CTU are collected, the SAO can be applied to reconstructed pixels in the CTU.

5

20

25

30

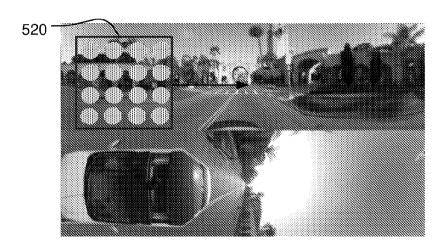

10 [0021] Fig. 5C illustrates an example of ALF process for a reconstructed VR360 picture. A reconstructed pixel 530 may be filtered by a 5x5 filter or a reconstructed pixel 532 may be filtered by a 7x7 filter. As mentioned before, the filter parameters may be designed using Wiener filter technique to minimize the error between the original picture and the reconstructed picture. For each reconstructed pixel, the filter size is adaptively selected to achieve the best performance.

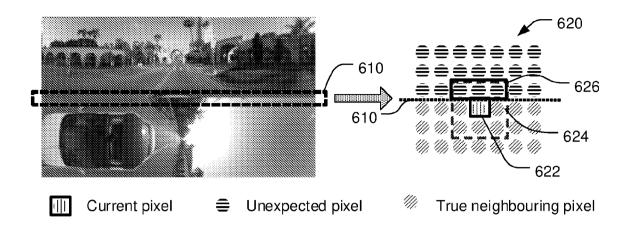

[0022] As illustrated in layout 420 in Fig. 4, the 3x2 layout for cubemap contains a discontinuous edge between the top sub-frame and the bottom sub-frame. The pixels on one side of the boundary 422 may be quite different from the pixels on the other side of the boundary 422. Therefore, when an in-loop filter is applied to reconstructed pixels next to the boundary or close to the boundary, it may cause undesirable result. Fig. 6 illustrates an example of SAO filter applied to a reconstructed pixel 622, where the discontinuous edge 610 is indicated. SAO operation 620 at the discontinuous edge is illustrated for the reconstructed pixel 622. The 3x3 SAO window is indicated by the dash-lined box 624. For the horizontal boundary 610, the SAO filtering process for 90°, 135°, and 45° will utilise a reference pixel from the other side of the discontinuous boundary. The neighbouring pixels 626 on the other side of discontinuous edge (named unexpected pixels) may be very different from the reconstructed pixel 622 being filtered though they are close to the reconstructed pixel 622. In this case, the SAO processing for the boundary pixels may produce undesirable results.

[0023] Therefore, it is desirable to develop techniques to overcome the issues related to in-loop filter for VR360 pictures.

## **SUMMARY**

[0024] Method and apparatus of coding a videosequence are disclosed, wherein the reconstructed filter unit comprises a plurality of reconstructed pixels for loop filtering process. According to this method, a first syntax is signalled in a bitstream at an encoder side or the first syntax is parsed from the bitstream at a decoder side. A reconstructed filter unit in a current picture is received, wherein the reconstructed filter unit is associated with a loop filter and the reconstructed filter unit comprises reconstructed pixels for applying a loop filtering process associated with the loop filter to a current reconstructed pixel. The first syntax indicates whether the loop filtering process is disabled for one or more virtual boundaries in a corresponding region. When the first syntax is true, the loop filter processing is disabled when the reconstructed filter unit is across said one or more virtual boundaries in the corresponding region. When the first syntax is false, the loop filter processing is not disabled when the reconstructed filter unit is across the virtual boundary.

5

10

15

20

25

30

[0025] The first syntax can be signalled in or parsed from the bitstream at a syntax level comprising SPS (Sequence Parameter Set), PPS (Picture Parameter Set), APS (Application Parameter Set), slice, tile, picture, CTU (Coding Tree Unit), CU (Coding Unit), PU (Prediction Unit) or TU (Transform Unit) level for the corresponding region.

[0026] In one embodiment, if the first syntax is true, one or more second syntaxes are signalled at the encoder side or parsed at the decoder side to indicate virtual boundary information in the corresponding region. The second syntaxes comprise a first number to indicate a number of vertical virtual boundaries and a second number to indicate a number of horizontal virtual boundaries in the corresponding region. In one example, each vertical virtual boundary is from a top edge to a bottom edge of the corresponding region and each horizontal virtual boundary is from a left edge to a right edge of the corresponding region. In this case, when the first number is greater than 0, locations of each vertical virtual boundary are transmitted in or parsed from the bitstream. When the second number is greater than 0, locations of each horizontal virtual boundary are transmitted in or parsed from the bitstream.

[0027] In another example, the vertical virtual boundaries are not necessarily from a top edge to a bottom edge of the corresponding region and the horizontal virtual

boundaries are not necessarily from a left edge to a right edge of the corresponding region. In this case when the first number is greater than 0, locations of x-position, y starting position and y ending position for each vertical virtual boundary are transmitted in or parsed from the bitstream; and when the second number is greater than 0, locations of y-position, x starting position and x ending position for each horizontal virtual boundary are transmitted in or parsed from the bitstream.

5

10

15

20

25

30

[0028] In yet another example, length of the vertical virtual boundaries and the length of the horizontal virtual boundaries is fixed. In this case, when the first number is greater than 0, location of starting point for each vertical virtual boundary is transmitted in or parsed from the bitstream. When the second number is greater than 0, the location of starting point for each horizontal virtual boundary is transmitted in or parsed from the bitstream.

[0029] In one embodiment, if the first syntax is true, one or more second syntaxes are signalled at the encoder side or parsed at the decoder side, where said one or more second syntaxes indicate a number of said one or more virtual boundaries in the corresponding region. When the number of said one or more virtual boundaries is greater than 0, locations of starting points and ending points of said one or more virtual boundaries are transmitted in or parsed from the bitstream. Said one or more virtual boundaries may correspond to one or more rectangle boxes and starting points and ending points correspond to left-top positions and right-bottom positions of said one or more rectangle boxes.

[0030] In one embodiment, if the first syntax is true, a second syntax is signalled at the encoder side or parsed at the decoder side, and wherein said the second syntax indicates a shape of at least one virtual boundary in the corresponding region. For example, the shape of at least one virtual boundary in the corresponding region comprises a straight-line virtual boundary and a circular virtual boundary. When the second syntax indicates a circular virtual boundary, one or more third syntaxes are signalled at the encoder side or parsed at the decoder side to indicate location of centre and radius of at least one circle.

[0031] In one embodiment, one or more second syntaxes are signalled at the encoder side or parsed at the decoder side to indicate difference values between a current virtual boundary and a previous virtual boundary. For example, when the current virtual boundary is a first virtual boundary in the corresponding region, absolute position of the first virtual boundary is signalled directly at the encoder side

8

or parsed directly at the decoder side. In another example, when the current virtual boundary is a first virtual boundary in the corresponding region, difference between the first virtual boundary and a starting point of the corresponding region is signalled directly at the encoder side or parsed at the decoder side.

- 5 [0032] In one embodiment, if the first syntax is true, one or more second syntaxes are signalled at the encoder side or parsed at the decoder side to indicate locations of said one or more virtual boundaries, and the locations of said one or more virtual boundaries are measured in terms of width and/or height of processing unit. For example, the processing unit is set to a region comprising a picture, a slice, a tile, a CTU (coding tree unit), a CU (coding unit), a PU (prediction unit), a TU (transform unit), a pre-defined value, or a combination thereof.

- [0033] In one embodiment, if a target corresponding region have same virtual boundaries as a previous corresponding region, the target corresponding region inherits the same virtual boundaries as the previous corresponding region. For example, the target corresponding region comprises a picture, a slice, a tile, a CTU (coding tree unit), a CU (coding unit), a PU (prediction unit), a TU (transform unit). Furthermore, a second syntax can be signalled at the encoder side or parsed at the decoder side to indicate whether the target corresponding region inherits the same virtual boundaries as the previous corresponding region.

15

30

- 20 [0034] In one embodiment, the video sequence corresponds to a 360-degree virtual reality (VR360) video. The VR360 video comprises Equirectangular projection (ERP), Padded Equirectangular projection (PERP), Octahedron Projection, Icosahedron Projection, Truncated Square Pyramid (TSP), Segmented Sphere Projection (SSP) or Rotated Sphere Projection (RSP).

- 25 [0035] In one embodiment, the loop filter belongs to a group comprising deblocking filter, SAO (Sample Adaptive Offset) filter and ALF (Adaptive Loop Filter).

# **BRIEF DESCRIPTION OF DRAWINGS**

[0036] Fig. 1A illustrates an example of the boundary pixels involved in deblocking filtering process for the vertical boundary.

[0037] Fig. 1B illustrates an example of the boundary pixels involved in deblocking filtering process for the horizontal boundary.

[0038] Fig. 2 shows the 4 EO (Edge Offset) directional patterns (0°, 90°, 135°, and 45°) for SAO (Sample Adaptive Offset).

- [0039] Fig. 3 illustrates an example of the ALF comprising a 5x5 filter and a 7x7 filter, where "C" indicates a current reconstructed pixel being filtered.

- 5 [0040] Fig. 4 illustrates an example of 4x3 and 3x2 cubemap layout formations.

- [0041] Fig. 5A illustrates an example of de-blocking filter applied to a block of a VR360 picture in the 3x2 layout.

- [0042] Fig. 5B illustrates an example of SAO processing applied to pixels of a VR360 picture in the 3x2 layout.

- 10 [0043] Fig. 5C illustrates an example of ALF process using a 5x5 or 7x7 filter for a reconstructed VR360 picture.

- [0044] Fig. 6 illustrates an example of SAO filter applied to a reconstructed pixel at the discontinuous edge.

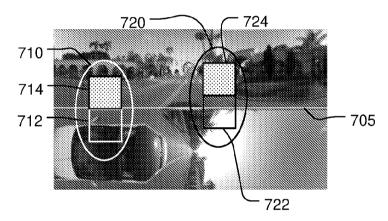

- [0045] Fig. 7A illustrates examples of de-blocking filtering process being applied across the discontinuous boundary or applied to a block boundary close to the discontinuous boundary.

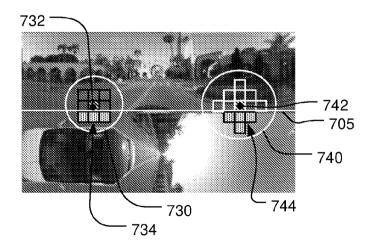

- [0046] Fig. 7B illustrates examples of SAO (Sample Adaptive Offset) and ALF (Adaptive Loop Filter) filtering processes being applied across the discontinuous boundary.

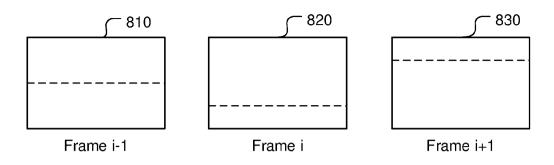

- 20 [0047] Fig. 8A illustrates an example where three frames (i-1, i and i+1) have different virtual boundaries as indicated by dash lines.

- [0048] Fig. 8B illustrates an example of different CTUs (Coding Tree Units) that have different virtual boundaries as indicated by dash lines.

- [0049] Fig. 8C illustrates an example of the starting point or end point of a virtual boundary is located inside a picture.

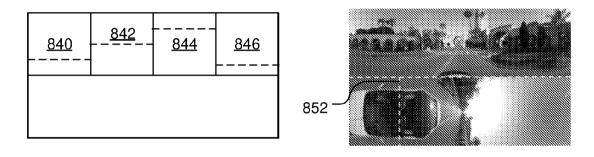

- [0050] Fig. 9 illustrates an example of reference pixels extension for loop filtering process across a discontinuous edge or virtual boundary according to embodiments of the present invention.

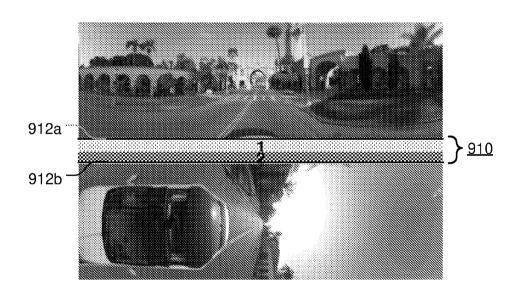

- [0051] Fig. 10 illustrates various examples of VR360 projection including Equirectangular projection (ERP), Padded Equirectangular Projection (PERP), Octahedron Projection, Octahedron Projection in compact option 1, and Octahedron Projection in compact option 2 are shown in Fig. 10.

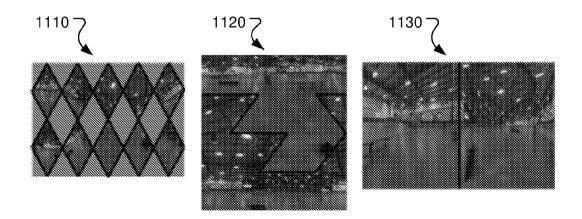

- [0052] Fig. 11 illustrates various examples of VR360 projection including

Icosahedron Projection, Icosahedron Projection in compact option 1, and Truncated Square Pyramid (TSP).

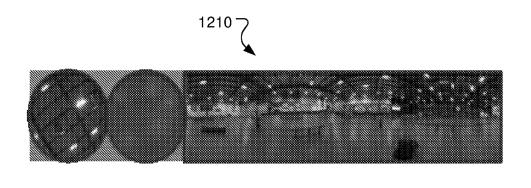

[0053] Fig. 12 illustrates various examples of VR360 projection including Segmented Sphere Projection (SSP) and Rotated Sphere Projection (RSP).

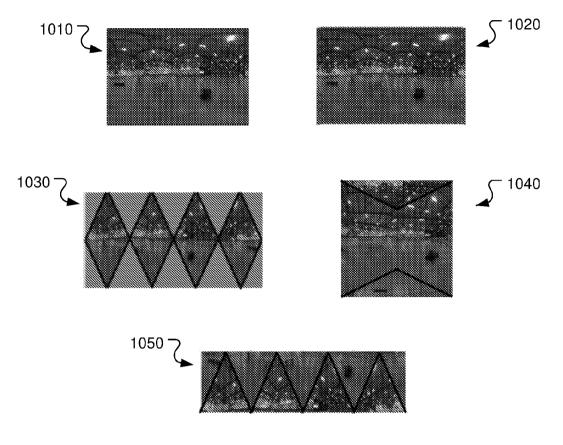

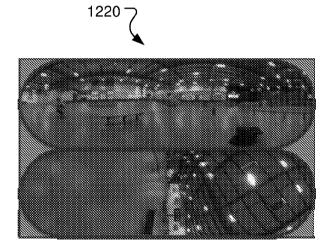

5 [0054] Fig. 13 illustrates an exemplary flowchart of a coding system for video according to an embodiment of the present invention, where a first syntax is signalled to indicate whether the loop filtering process is disabled for one or more virtual boundaries in a corresponding region.

## **DETAILED DESCRIPTION**

10

15

20

25

30

[0055] The following description is of the best-contemplated mode of carrying out the invention. This description is made for the purpose of illustrating the general principles of the invention and should not be taken in a limiting sense. The scope of the invention is best determined by reference to the appended claims.

[0056] It will be readily understood that the components of the present invention, as generally described and illustrated in the figures herein, may be arranged and designed in a wide variety of different configurations. Thus, the following more detailed description of the embodiments of the systems and methods of the present invention, as represented in the figures, is not intended to limit the scope of the invention, as claimed, but is merely representative of selected embodiments of the invention.

[0057] Reference throughout this specification to "one embodiment," "an embodiment," or similar language means that a particular feature, structure, or characteristic described in connection with the embodiment may be included in at least one embodiment of the present invention. Thus, appearances of the phrases "in one embodiment" or "in an embodiment" in various places throughout this specification are not necessarily all referring to the same embodiment.

[0058] Furthermore, the described features, structures, or characteristics may be combined in any suitable manner in one or more embodiments. One skilled in the relevant art will recognize, however, that the invention can be practiced without one or more of the specific details, or with other methods, components, etc. In other instances, well-known structures, or operations are not shown or described in detail to

avoid obscuring aspects of the invention.

5

10

15

20

25

30

[0059] The illustrated embodiments of the invention will be best understood by reference to the drawings, wherein like parts are designated by like numerals throughout. The following description is intended only by way of example, and simply illustrates certain selected embodiments of apparatus and methods that are consistent with the invention as claimed herein.

[0060] In the description like reference numbers appearing in the drawings and description designate corresponding or like elements among the different views.

[0061] As mentioned before, when an in-loop filter is applied to a discontinuous boundary in VR360 videos, the filtering process for a reconstructed pixel on one side of the discontinuous boundary may need to use one or more reconstructed pixels on the other side of the discontinuous boundary (referred as unexpected pixels). Due to the discontinuity between the pixels on two sides of the discontinuous boundary, use of the unexpected pixels for the in-loop filtering processing may cause noticeable artefacts. Therefore, according to a method of the present invention, the in-loop filtering process is disabled or a smaller size filter is used if the in-loop filtering process is across the discontinuous boundary. The discontinuous boundary or edge in VR360 video or PIP is also referred as virtual boundary in this disclosure. The in-loop filter may be referred as loop filter in this disclosure. The in-loop filtering process may be referred as loop filtering process in this disclosure.

[0062] Fig. 7A illustrates de-blocking filtering process being applied across the discontinuous boundary 705. In Fig. 7A, the de-blocking filtering process 710 is applied to a current block 712, where the block boundary is aligned with the discontinuous boundary 705. The de-blocking filtering process for the current block 712 involves unexpected pixels as indicated by the dots-filled area 714. Since the de-blocking filtering process is applied across the discontinuous boundary, the method according to the present invention disables the de-blocking filtering process for the current block. The de-blocking filtering process 720 is applied to a current block 722, where the discontinuous boundary 705 is located inside the current block. The de-blocking filtering process for the current block 722 may involve unexpected pixels, where some of pixels in the current block may be on a different side of the virtual boundary from the neighbouring reference block as indicated by the dots-filled area 724. A method according to the present invention disables the de-blocking filtering process for the current block or uses a de-blocking filter with a smaller filter size. In

addition, when the virtual boundary is located inside a neighbouring reference block, a method according to the present invention disables the de-blocking filtering process for the current block or uses a de-blocking filter with a smaller filter size. In the HEVC, the de-blocking filter may use up to 4 pixels on each side of the block boundary. According to embodiments of the present invention, the de-blocking filter may use less pixels on at least one side of the block boundary.

5

10

15

20

25

30

[0063] The de-blocking filter may be applied to a block such as the transform block boundary, sub-block boundary or other types of block. Accordingly, in one embodiment, the loop filtering process is disabled for a block (e.g. a sub-block or a transform block) if the block (e.g. a sub-block edge or a transform block edge associated with the sub-block or the transform block for the de-blocking filter) is aligned with the virtual boundary or the virtual boundary is located inside the block or neighbouring block.

In Fig. 7B, the SAO filtering process 730 is applied to a current pixel 732 [0064] adjacent to the discontinuous boundary 705. The SAO filtering process for the current pixel 732 involves unexpected pixels as indicated by the dots-filled squares 734. Since the SAO filtering process is applied across the discontinuous boundary, the method according to the present invention disables the SAO filtering process for the current pixel. In Fig. 7B, the ALF filtering process 740 is applied to a current pixel 742 adjacent to the discontinuous boundary 705. The ALF filtering process for the current pixel 742 involves unexpected pixels as indicated by the dots-filled squares 744. Since the ALF filtering process is applied across the discontinuous boundary, the method according to the present invention disables the ALF filtering process for the current pixel or use a smaller ALF if the smaller ALF is available. For example, if both 7x7 and 5x5 ALF are available, when the 7x7 ALF is across the virtual boundary, the 5x5 ALF may be used. The ALF filtering process includes determination of filter coefficients and applying the filter. While, de-blocking, SAO and ALF in-loop filters are used as examples for the method of disabling in-loop filtering process across the discontinuous boundary, the method may also be applied to other types of in-loop filtering process.

[0065] According to embodiments of the present invention, a syntax (e.g. control flag or enable flag) can be transmitted in the bitstream at a syntax level such as the SPS, PPS, APS, slice, tile, picture, CTU, CU, PU or TU level to indicate whether the filters are disabled for virtual boundaries in the corresponding region (e.g. picture,

slice, tile, CTU, CU, TU or PU). For example, a control flag sps\_loop\_filter\_disabled\_across\_virtual\_boundaries\_flag can be signalled in the sequence level to indicate whether the filters are disabled for virtual boundaries in the frames of the sequence.

[0066] The virtual boundaries can be different in different pictures, slices, tiles, CTUs, CUs, PUs or TUs. For example, three frames (i-1, i and i+1) are shown in Fig. 8A, where the three frames have different virtual boundaries as indicated by dash lines. Fig. 8B illustrates an example of different CTUs (i.e., 840, 842, 844 and 846) that have different virtual boundaries as indicated by dash lines.

10 **[0067]** In the following, various syntax structures according to embodiments of the present invention are disclosed.

# [0068] Syntax Structure Design I

15

20

[0069] In one embodiment, if the syntax (e.g. control flag or enable flag) is true, then the in-loop filters are disabled across the virtual boundaries; and if the syntax (e.g. control flag or enable flag) is false, then the in-loop filters are not disabled when the reconstructed filter unit is across the virtual boundaries.

[0070] In one embodiment, if the syntax (e.g.an control flag orenable flag) is equal to True, two syntaxes can be also signalled in the bitstream to indicate the number of the vertical and horizontal virtual boundaries, respectively. If the number of vertical virtual boundaries is greater than 0, the locations of all of the vertical virtual boundaries are signalled in the bitstream. Similarly, if the number of horizontal virtual boundaries is greater than 0, the locations of all of the horizontal virtual boundaries are signalled in the bitstream.

[0071] An exemplary SPS syntax table incorporating an embodiment of the present invention is shown in Table 2.

Table 2.

| seq_parameter_set_rbsp( ) {                                     | Descriptor |

|-----------------------------------------------------------------|------------|

|                                                                 |            |

| sps_loop_filter_disabled_across_virtual_boundaries_flag         | u(1)       |

| if( sps_loop_filter_disabled_across_virtual_boundaries_flag ) { |            |

| sps_num_ver_virtual_boundaries                                  | ue(v)      |

| if( sps_num_ver_virtual_boundaries != 0 ) {                     |            |

| for( i = 0; i < sps_num_ver_virtual_boundaries; i++ ) {         |            |

| sps_virtual_boundaries_pos_x[ i ]                       | ue(v) |

|---------------------------------------------------------|-------|

| }                                                       |       |

| }                                                       |       |

| sps_num_hor_virtual_boundaries                          | ue(v) |

| if( sps_num_hor_virtual_boundaries != 0 ) {             |       |

| for( i = 0; i < sps_num_hor_virtual_boundaries; i++ ) { |       |

| sps_virtual_boundaries_pos_y[ i ]                       | ue(v) |

| }                                                       |       |

| }                                                       |       |

| }                                                       |       |

|                                                         |       |

| }                                                       |       |

[0072] Since the virtual boundaries are not always set from the leftmost position to the rightmost position of a region (e.g. picture, slice, tile, CTU, CU, PU, or TU) or from the topmost positions to the bottommost positions of a region. The starting point or end point of a virtual boundary can locate inside a picture. For example, the starting point or end point of a virtual boundary is located inside a picture as shown in Fig. 8C, where the vertical virtual boundary 852 has a top end inside the picture(i.e., in the middle of the picture) while the horizontal virtual boundary is from the left side to the right side of the picture. Therefore, the virtual boundary starting and ending positions are also specified in the syntax Table 3.

[0073] In another embodiment, if the syntax (i.e., control flag or enable flag) is equal to True, two syntaxes can be also signalled in the bitstream to indicate the number of the vertical and horizontal virtual boundaries, respectively. If the number of vertical virtual boundaries is greater than 0, the x position and y starting point and y ending point for each vertical virtual boundary are signalled in the bitstream. If the number of horizontal virtual boundaries is greater than 0, the y position and x starting point and x ending point for each horizontal virtual boundary are signalled in the bitstream.

[0074] An exemplary SPS syntax table incorporating the above embodiment of the present invention is shown in Table 3.

20 **Table 3.**

5

10

15

| seq_parameter_set_rbsp() { | Descriptor |  |

|----------------------------|------------|--|

| sps_loop_filter_disabled_across_virtual_boundaries_flag         | u(1)  |

|-----------------------------------------------------------------|-------|

| if( sps_loop_filter_disabled_across_virtual_boundaries_flag ) { |       |

| sps_num_ver_virtual_boundaries                                  | ue(v) |

| if( sps_num_ver_virtual_boundaries != 0 ) {                     |       |

| for( i = 0; i < sps_num_ver_virtual_boundaries; i++ ) {         |       |

| sps_virtual_boundaries_pos_x[ i ]                               | ue(v) |

| sps_virtual_boundaries_start_pos_y[ i ]                         | ue(v) |

| sps_virtual_boundaries_end_pos_y[ i ]                           | ue(v) |

| }                                                               |       |

| }                                                               |       |

| sps_num_hor_virtual_boundaries                                  | ue(v) |

| <pre>if( sps_num_hor_virtual_boundaries != 0 ) {</pre>          |       |

| for( i = 0; i < sps_num_hor_virtual_boundaries; i++ ) {         |       |

| sps_virtual_boundaries_pos_y[ i ]                               | ue(v) |

| sps_virtual_boundaries_start_pos_x[ i ]                         | ue(v) |

| sps_virtual_boundaries_end_pos_x[ i ]                           | ue(v) |

| }                                                               |       |

| }                                                               |       |

| }                                                               |       |

|                                                                 |       |

| }                                                               |       |

[0075] In another embodiment, the length of the virtual boundaries is fixed. In this case, the above syntax table can be changed as shown in Table 4. Again, a syntax (e.g. control flagor enable flag) can be transmitted in the bitstream at the SPS, PPS, APS, slice, tile, picture, CTU, CU, PU or TU level to indicate whether the in-loop filters are disabled for virtual boundaries. If the syntax is true, then the in-loop filters are disabled when the reconstructed filter unit is across the virtual boundaries. If the syntax is false, then the in-loop filters are not disabled when the reconstructed filter unit is across the virtual boundaries.

5

10

[0076] If the syntax (e.g. control flag or enable flag) is equal to true, the following syntax can be also transmitted in the bitstream. Two syntaxes can be transmitted into bitstream to indicate the number of the vertical and horizontal virtual boundaries are set, respectively. If the number of vertical virtual boundaries is greater than 0, the starting points(x positions and y positions) for each vertical virtual boundary are

transmitted into bitstream. If the number of horizontal virtual boundaries is greater than 0, the starting points (x positions and y positions) for each horizontal virtual boundary are transmitted into bitstream.

Table 4.

| seq_parameter_set_rbsp( ) {                                     | Descriptor |

|-----------------------------------------------------------------|------------|

|                                                                 |            |

| sps_loop_filter_disabled_across_virtual_boundaries_flag         | u(1)       |

| if( sps_loop_filter_disabled_across_virtual_boundaries_flag ) { |            |

| sps_num_ver_virtual_boundaries                                  | ue(v)      |

| if( sps_num_ver_virtual_boundaries != 0 ) {                     |            |

| for( i = 0; i < sps_num_ver_virtual_boundaries; i++ ) {         |            |

| sps_ver_virtual_boundaries_pos_x[ i ]                           | ue(v)      |

| sps_ver_virtual_boundaries_pos_y[ i ]                           | ue(v)      |

| }                                                               |            |

| }                                                               |            |

| sps_num_hor_virtual_boundaries                                  | ue(v)      |

| if( sps_num_hor_virtual_boundaries != 0 ) {                     |            |

| for( i = 0; i < sps_num_hor_virtual_boundaries; i++ ) {         |            |

| sps_hor_virtual_boundaries_pos_x[ i ]                           | ue(v)      |

| sps_hor_virtual_boundaries_pos_y[ i ]                           | ue(v)      |

| }                                                               |            |

| }                                                               |            |

| }                                                               |            |

|                                                                 |            |

| }                                                               |            |

# 5 [0077] Syntax Structure Design II

[0078] A more flexible syntax structure to signal various types of virtual boundaries is also disclosed. The virtual boundaries are not always set from the leftmost positions to the rightmost positions of a region (picture, slice, tile, CTU, CU, PU, TU) or from the topmost positions to the bottommost positions of a region.

10 **[0079]** Two location starting point and ending point for each virtual boundary are signalled in the bitstream so that the virtual boundaries can be set as rectangle boxes or straight lines. The stating point indicates the left-top position of the box and the

ending point indicates the right-bottom position of the box.

all of the virtual boundaries are signalled in the bitstream.

5

[0080] If the syntax (i.e., control flag or enable flag) is equal to True, the following syntax can be also signalled in the bitstream. One syntax can be signalled in the bitstream to indicate the number of the virtual boundaries. If the number of virtual boundaries is greater than 0, the locations of the starting points and the end points of

[0081] An exemplary syntax table incorporating the above embodiment is shown in Table 5.

Table 5.

| seq_parameter_set_rbsp( ) {                                     | Descriptor |

|-----------------------------------------------------------------|------------|

|                                                                 |            |

| sps_loop_filter_disabled_across_virtual_boundaries_flag         | u(1)       |

| if( sps_loop_filter_disabled_across_virtual_boundaries_flag ) { |            |

| sps_num_virtual_boundaries                                      | ue(v)      |

| if( sps_num_virtual_boundaries != 0 ) {                         |            |

| for( i = 0; i < sps_num_virtual_boundaries; i++ ) {             |            |

| sps_virtual_boundaries_start_pos_x[ i ]                         | ue(v)      |

| sps_virtual_boundaries_start_pos_y[ i ]                         | ue(v)      |

| sps_virtual_boundaries_end_pos_x[ i ]                           | ue(v)      |

| sps_virtual_boundaries_end_pos_y[ i ]                           | ue(v)      |

| }                                                               |            |

| }                                                               |            |

| }                                                               |            |

|                                                                 |            |

| }                                                               |            |

- 10 **[0082]** In another example, the syntax structure is similar to that in Table 5. However, the virtual boundaries can be signalled by locations of their corresponding starting points and the offset values between starting points and ending points:

- virtual\_boundaries\_end\_pos\_x[i] = virtual\_boundaries\_start\_pos\_x[i] +

virtual\_boundaries\_offset\_x[i],

- virtual\_boundaries\_end\_pos\_y[i] = virtual\_boundaries\_start\_pos\_y[i] + virtual\_boundaries\_offset\_y[i],

- where  $i = 0, ...num\_virtual\_boundaries -1$ .

- [0083] Again, a syntax (e.g. control flag or enable flag) can be transmitted in

bitstream at the SPS, PPS, APS, slice, tile, picture, CTU, CU, PU or TU level to indicate whether the in-loop filters are disabled for virtual boundaries. If the syntax is true, then the in-loop filters are disabled when the reconstructed filter unit is across the virtual boundaries. If the syntax is false, then the in-loop filters are not disabled when the reconstructed filter unit is across the virtual boundaries.

[0084] If the syntax (e.g. control flag or enable flag) is equal to true, the following syntax can be also signalled in bitstream. One syntax can be signalled in the bitstream to indicate the number of the virtual boundaries existing in the corresponding region. If the number of virtual boundaries is greater than 0, the locations of the starting points and the offset values of all of the virtual boundaries are signalled in the bitstream.

[0085] An exemplary syntax table incorporating the above embodiment is shown in Table 6.

Table 6.

| seq_parameter_set_rbsp( ) {                                     | Descriptor |

|-----------------------------------------------------------------|------------|

|                                                                 |            |

| sps_loop_filter_disabled_across_virtual_boundaries_flag         | u(1)       |

| if( sps_loop_filter_disabled_across_virtual_boundaries_flag ) { |            |

| sps_num_virtual_boundaries                                      | ue(v)      |

| if( sps_num_virtual_boundaries != 0 ) {                         |            |

| for( i = 0; i < sps_num_virtual_boundaries; i++ ) {             |            |

| sps_virtual_boundaries_start_pos_x[ i ]                         | ue(v)      |

| sps_virtual_boundaries_start_pos_y[ i ]                         | ue(v)      |

| sps_virtual_boundaries_offset_x[ i ]                            | se(v)      |

| sps_virtual_boundaries_offset_y[ i ]                            | se(v)      |

| }                                                               |            |

| }                                                               |            |

| }                                                               |            |

|                                                                 |            |

| }                                                               | _          |

[0086] Syntax Structure Design III

5

10

15 [0087] For some VR projection pictures, the layout may include virtual boundaries in various angles beside the vertical and horizontal directions and multiple virtual boundaries can form a non-square shape, such as a triangle or a rectangle. Furthermore, the virtual boundary can be a straight line or a shape such as a circle.

According to some embodiments of the present invention, the syntax structure is designed to support such cases.

[0088] Again, a syntax (e.g. control flag or enable flag) can be transmitted in bitstream at the SPS, PPS, APS, slice, tile, picture, CTU, CU, PU or TU level to indicate whether the in-loop filters are disabled for virtual boundaries. If the syntax is true, then the in-loop filters are disabled when the reconstructed filter unit is across the virtual boundaries. If the syntax is false, then the in-loop filters are not disabled when the reconstructed filter unit is across the virtual boundaries.

5

10

15

20

[0089] In one embodiment, if the syntax (e.g.control flag or enable flag) is equal to True, the following syntax can be also signalled in the bitstream. For example, one syntax can be signalled in the bitstream to indicate the number of the virtual boundaries. If the number of virtual boundaries is greater than 0, a syntax (e.g. shape flag) can be signalled in the bitstream to indicate the shape of each virtual boundary. For example, if the shape flag is equal to a first value (e.g. 0), the virtual boundary is a straight line. The location of the starting and end points are signalled in the bitstream. If the shape flag is equal to a second value (e.g. 1), the virtual boundary is a circle. The position of the centre of the circle and the radius of the circle can be signalled in the bitstream.

[0090] An exemplary syntax table corresponding to the above embodiment based on syntax table in Table 5 for syntax structure II is shown in Table 7.

Table 7.

| seq_parameter_set_rbsp( ) {                                     | Descriptor |

|-----------------------------------------------------------------|------------|

|                                                                 |            |

| sps_loop_filter_disabled_across_virtual_boundaries_flag         | u(1)       |

| if( sps_loop_filter_disabled_across_virtual_boundaries_flag ) { |            |

| sps_num_virtual_boundaries                                      | ue(v)      |

| if( sps_num_virtual_boundaries != 0 ) {                         |            |

| for( i = 0; i < sps_num_virtual_boundaries; i++ ) {             |            |

| sps_virtual_boundaries_shape[ i ]                               | u(1)       |

| if (sps_virtual_boundaries_shape[ i ] == 0 ) { // straight line |            |

| sps_virtual_boundaries_start_pos_x[ i ]                         | ue(v)      |

| sps_virtual_boundaries_start_pos_y[ i ]                         | ue(v)      |

| sps_virtual_boundaries_end_pos_x[ i ]                           | ue(v)      |

| sps_virtual_boundaries_end_pos_y[ i ]                    | ue(v) |

|----------------------------------------------------------|-------|

| }                                                        |       |

| if (sps_virtual_boundaries_shape[ i ] == 1 ) { // circle |       |

| sps_virtual_boundaries_center_pos_x[ i ]                 | ue(v) |

| sps_virtual_boundaries_centerpos_y[ i ]                  | ue(v) |

| sps_virtual_boundaries_radius[ i ]                       | ue(v) |

| }                                                        |       |

| }                                                        |       |

| }                                                        |       |

| }                                                        |       |

|                                                          |       |

| }                                                        |       |

[0091] An exemplary syntax table corresponding to the above embodiment based on syntax table in Table 6 for syntax structure II is shown in Table 8.

Table 8.

| seq_parameter_set_rbsp( ) {                                     | Descriptor |

|-----------------------------------------------------------------|------------|

|                                                                 |            |

| sps_loop_filter_disabled_across_virtual_boundaries_flag         | u(1)       |

| if( sps_loop_filter_disabled_across_virtual_boundaries_flag ) { |            |

| sps_num_virtual_boundaries                                      | ue(v)      |

| if( sps_num_virtual_boundaries != 0 ) {                         |            |

| for( $i = 0$ ; $i \le sps_num\_virtual\_boundaries$ ; $i++$ ) { |            |

| sps_virtual_boundaries_shape[ i ]                               | u(1)       |

| if (sps_virtual_boundaries_shape[ i ] == 0 ) { // straight line |            |

| sps_virtual_boundaries_start_pos_x[ i ]                         | ue(v)      |

| sps_virtual_boundaries_start_pos_y[ i ]                         | ue(v)      |

| sps_virtual_boundaries_offset_x[ i ]                            | se(v)      |

| sps_virtual_boundaries_offset_y[ i ]                            | se(v)      |

| }                                                               |            |

| if (sps_virtual_boundaries_shape[ i ] == 1 ) { // circle        |            |

| sps_virtual_boundaries_center_pos_x[ i ]                        | ue(v)      |

| sps_virtual_boundaries_centerpos_y[ i ]                         | ue(v)      |

| sps_virtual_boundaries_radius[ i ]                              | ue(v)      |

| }                                                               |            |

| }                                                               |            |

| } |  |

|---|--|

| } |  |

|   |  |

| } |  |

[0092] Reducing the Bit Number for Signalling

[0093] In order to reduce the bit number in the bitstream, the locations of the virtual boundaries can be derived from the previous virtual boundaries and the difference values between previous and current virtual boundaries.

5 [0094] According to one method of the present invention, only the difference values are signalled in the bitstream. The locations of the first virtual boundary can be derived as follows:

virtual\_boundaries\_pos\_ $x[0] = 0 + virtual_boundaries_diff_x[0],$  virtual\_boundaries\_pos\_ $y[0] = 0 + virtual_boundaries_diff_y[0].$

10 **[0095]** For the first virtual boundary, the location may also be derived from the starting positions of current region:

virtual\_boundaries\_pos\_ $x[0] = (x position of starting point of current region) + virtual_boundaries_diff_<math>x[0]$ ,

virtual\_boundaries\_pos\_y[0] = (y position of starting point of current region) + virtual\_boundaries\_diff\_y[0].

[0096] The locations of other virtual boundaries can be derived as follows:

where i = 1, ... num virtual boundaries -1

15

20

[0097] This method can be combined with the syntax structure I, II and III to reduce the bit number of bitstream.

[0098] An exemplary syntax table incorporating the above embodiment to reduce the bit number is shown in Table 9.

Table 9.

| <pre>seq_parameter_set_rbsp( ) {</pre> | Descriptor |

|----------------------------------------|------------|

|                                        |            |

| sps_loop_filter_disabled_across_virtual_boundaries_flag         | u(1)  |

|-----------------------------------------------------------------|-------|

| if( sps_loop_filter_disabled_across_virtual_boundaries_flag ) { |       |

| sps_num_ver_virtual_boundaries                                  | ue(v) |

| if( sps_num_ver_virtual_boundaries != 0 ) {                     |       |

| for( i = 0; i < sps_num_ver_virtual_boundaries; i++ ) {         |       |

| sps_virtual_boundaries_diff_x[i] // difference                  | se(v) |

| }                                                               |       |

| }                                                               |       |

| sps_num_hor_virtual_boundaries                                  | ue(v) |

| if( sps_num_hor_virtual_boundaries != 0 ) {                     |       |

| for( i = 0; i < sps_num_hor_virtual_boundaries; i++ ) {         |       |

| sps_virtual_boundaries_diff_y[ i ] // difference                | se(v) |

| }                                                               |       |

| }                                                               |       |

| }                                                               |       |

|                                                                 |       |

| }                                                               |       |

[0099] According to another embodiment, the absolute location of the first virtual boundary and the difference values of other virtual boundaries are signalled in the bitstream. The location of the other virtual boundaries can be derived from the previous virtual boundaries and the difference values between previous and current virtual boundaries.

[00100] Except for the first virtual boundary, the locations of other virtual boundaries can be derived as before as shown below.

virtual\_boundaries\_pos\_y[i] = virtual\_boundaries\_pos\_y [i-1]+ virtual\_boundaries\_diff\_y[i].

where  $i = 1, ... num_virtual_boundaries -1$

5

[00101] An exemplary syntax table incorporating the above embodiment to reduce the bit number is shown in Table 10.

15 **Table 10.**

| seq_parameter_set_rbsp() { | Descriptor |

|----------------------------|------------|

|----------------------------|------------|

| sps_loop_filter_disabled_across_virtual_boundaries_flag                      | u(1)  |

|------------------------------------------------------------------------------|-------|

| $if(\ sps\_loop\_filter\_disabled\_across\_virtual\_boundaries\_flag\ )\ \{$ |       |

| sps_num_ver_virtual_boundaries                                               | ue(v) |

| if( sps_num_ver_virtual_boundaries != 0 ) {                                  |       |

| sps_virtual_boundaries_pos_x[ 0 ]                                            | ue(v) |

| for( i = 1; i < sps_num_ver_virtual_boundaries; i++ ) {                      |       |

| sps_virtual_boundaries_diff_x[i] // difference                               | se(v) |

| }                                                                            |       |

| }                                                                            |       |

| sps_num_hor_virtual_boundaries                                               | ue(v) |

| if( sps_num_hor_virtual_boundaries != 0 ) {                                  |       |

| sps_virtual_boundaries_pos_y[ 0 ]                                            | ue(v) |

| for( $i = 1$ ; $i \le sps_num_hor_virtual_boundaries$ ; $i++$ ) {            |       |

| sps_virtual_boundaries_diff_y[ i ] // difference                             | se(v) |

| }                                                                            |       |

| }                                                                            |       |

| }                                                                            |       |

|                                                                              |       |

| }                                                                            |       |

[00102] To reduce the bit number, the locations of the virtual boundaries can be set to multiple of minimum width/height of processing unit. Therefore, the locations of virtual boundaries can be signalled in the bitstream in units of minimum processing unit.

- 5 [00103] For example, the minimum processing unit in the emerging VVC (Versatile Video Coding) standard is 4x4 block; therefore, the location of the virtual boundaries is set to multiple of 4.

- [00104] To further reduce the bit number, the locations of virtual boundaries could be signalled in the bitstream in units of slice, tile, CTU, CU, PU, TU, other predefined values or a combination thereof. For example, the location of a vertical virtual boundary can be 3-CTU width plus 5-block width.

10

- [00105] This method can be combined with the syntax structure I, II and III to reduce the bit number of bitstream. This method can also be combined with other bit number reduction methods.

- 15 [00106] The bit number reduction method can also be applied to the offset and

difference values in the syntax structures.

5

10

The virtual boundary position can be inherited from previous region (e.g. [00107] picture, slice, tile, CTU, CU, TU, PU, etc.) and, therefore, the number of bits can be reduced for the current region (e.g. picture, slice, tile, CTU, CU, TU, PU, etc.). For example, if the positions of virtual boundaries in the current frame are the same as previous frame, the virtual boundaries can be inherited from the previous frame. In another example, if the positions of virtual boundaries in the current CTU are the same as the previous CTU, the virtual boundaries can be inherited from the previous CTU.For the region, addition current one syntax (e.g. sps\_virtual\_boundary\_inherit\_flag) can be used to identify whether the virtual boundaries are inherited from a previous region or not.

[00108] An exemplary syntax table incorporating the above embodiment to reduce the bit number is shown in Table 11.

Table 11.

| seq_parameter_set_rbsp() {                                         | Descriptor |

|--------------------------------------------------------------------|------------|

|                                                                    |            |

| sps_loop_filter_disabled_across_virtual_boundaries_flag            | u(1)       |

| if( sps_loop_filter_disabled_across_virtual_boundaries_flag ) {    |            |

| sps_virtual_boundary_inherit_flag                                  | u(1)       |

| if (!sps_virtual_boundary_inherit) {                               |            |

| sps_num_ver_virtual_boundaries                                     | ue(v)      |

| if( sps_num_ver_virtual_boundaries != 0 ) {                        |            |

| for<br>( $i = 0$ ; $i \le sps_num_ver_virtual_boundaries; i++ ) {$ |            |

| sps_virtual_boundaries_pos_x[ i ]                                  | ue(v)      |

| }                                                                  |            |

| }                                                                  |            |

| sps_num_hor_virtual_boundaries                                     | ue(v)      |

| if( sps_num_hor_virtual_boundaries != 0 ) {                        |            |

| for<br>( $i = 0$ ; $i \le sps_num_hor_virtual_boundaries; i++ ) {$ |            |

| sps_virtual_boundaries_pos_y[ i ]                                  | ue(v)      |

| }                                                                  |            |

| }                                                                  |            |

| }                                                                  |            |

| } |  |

|---|--|

|   |  |

| } |  |

[00109] Fig. 9 illustrates an example of reference pixels extension 910 for loop filtering process across a discontinuous edge or virtual boundary according to embodiments of the present invention. In Fig. 9, pixels from the top sub-frame are extended to form alternative reference pixels (labelled as dot-filled area 1) and pixels from the bottom sub-frame are extended to form alternative reference pixels (labelled as dot-filled area 2). In Fig. 9, the virtual boundary (912a and 912b) are shown for the top sub-frame and the bottom sub-frame. When the pixels on the same side of the virtual boundary are extended to form the alternative reference pixels, the nearest pixels in the current sub-frame are used. In other words, the bottom line of the top sub-frame is extended downward to form the reference pixel area 1 and the top line of the bottom sub-frame is extended upward to form the reference pixel area 2. When a reference pixel from the other side of the discontinuous edge or virtual boundary is required for the loop filtering process, the nearest pixels in the current sub-frame (i.e., on the same side of discontinuous edge/virtual boundary as the current pixel) are used as the alternative referenced pixels. In Fig. 9, the VR360 picture consists of a top subframe and a bottom sub-frame. As is understood, the 3x2 cubemap layout is intended as an example to illustrate the reference pixel extension according to embodiment of the present invention.

5

10

15

20

25

30

[00110] The reference pixel extension can be applied to other VR360 layout formats, such as the layout formats derived from OctaHedron Projection (OHP), icosahedron projection (ISP), Segmented Sphere Projection (SSP) and Rotated Sphere Projection (RSP). There may be more than one virtual boundaries in the VR360 pictures. Furthermore, the virtual boundaries may be in other directions instead of vertical/horizontal. When the loop filtering process involves unexpected reference pixels (i.e., reference pixels on the other side of the virtual boundary), the nearest pixels on the same side as the current reconstructed pixel to be filtered can be extended to form the alternative reference pixels.

[00111] The filtering control (i.e., enable or disable) across virtual boundary has been shown based on the 3x2 cubemap layout. However, the filtering process across virtual boundaries described above is also applicable to other VR formats such as OctaHedron Projection (OHP), icosahedron projection (ISP), Segmented Sphere

Projection (SSP) and Rotated Sphere Projection (RSP). Pictures corresponding to Equirectangular projection (ERP) 1010, Padded Equirectangular Projection (PERP)1020, Octahedron Projection 1030, Octahedron Projection 1040 in compact option 1, and Octahedron Projection 1050 in compact option 2 are shown in Fig. 10.

Pictures corresponding to Icosahedron Projection 1110, Icosahedron Projection 1120 in compact option 1, and Truncated Square Pyramid (TSP) 1130 are shown in Fig. 11. Pictures corresponding to Segmented Sphere Projection (SSP) 1210 and Rotated Sphere Projection (RSP) 1220 are shown in Fig. 12.

5

10

15

20

25

30

[00112] This method is not only applicable to the de-blocking filter, ALF and SAO filters but also applicable to the other filters.

Fig. 13 illustrates an exemplary flowchart of a coding system for video [00113] according to an embodiment of the present invention, where a first syntax is signalled to indicate whether the loop filtering process is disabled for one or more virtual boundaries in a corresponding region. The steps shown in the flowchart, as well as other following flowcharts in this disclosure, may be implemented as program codes executable on one or more processors (e.g., one or more CPUs) at the encoder side and/or the decoder side. The steps shown in the flowchart may also be implemented based hardware such as one or more electronic devices or processors arranged to perform the steps in the flowchart. According to this method, a first syntax is signalled in a bitstream at an encoder side or the first syntax is parsed from the bitstream at a decoder side in step 1310, wherein the first syntax indicates whether a loop filtering process is disabled for one or more virtual boundaries in a corresponding region. A reconstructed filter unit for a current reconstructed pixel in a picture is received in step 1320, wherein the reconstructed filter unit is associated with a loop filter and the reconstructed filter unit comprises reconstructed pixels for applying a loop filtering process associated with the loop filter to the current reconstructed pixel. When the first syntax is true, the loop filter processing is disabled when the reconstructed filter unit is across said one or more virtual boundaries in the corresponding region. When the first syntax is false, the loop filter processing is not disabled when the reconstructed filter unit is across the virtual boundary.

[00114] The flowchart shown above is intended for serving as examples to illustrate embodiments of the present invention. A person skilled in the art may practice the present invention by modifying individual steps, splitting or combining steps with departing from the spirit of the present invention.

[00115] The above description is presented to enable a person of ordinary skill in the art to practice the present invention as provided in the context of a particular application and its requirement. Various modifications to the described embodiments will be apparent to those with skill in the art, and the general principles defined herein may be applied to other embodiments. Therefore, the present invention is not intended to be limited to the particular embodiments shown and described, but is to be accorded the widest scope consistent with the principles and novel features herein disclosed. In the above detailed description, various specific details are illustrated in order to provide a thorough understanding of the present invention. Nevertheless, it will be understood by those skilled in the art that the present invention may be practiced.

5

10

15

20

25

30

Embodiment of the present invention as described above may be [00116] implemented in various hardware, software codes, or a combination of both. For example, an embodiment of the present invention can be one or more electronic circuits integrated into a video compression chip or program code integrated into video compression software to perform the processing described herein. An embodiment of the present invention may also be program code to be executed on a Digital Signal Processor (DSP) to perform the processing described herein. The invention may also involve a number of functions to be performed by a computer processor, a digital signal processor, a microprocessor, or field programmable gate array (FPGA). These processors can be configured to perform particular tasks according to the invention, by executing machine-readable software code or firmware code that defines the particular methods embodied by the invention. The software code or firmware code may be developed in different programming languages and different formats or styles. The software code may also be compiled for different target platforms. However, different code formats, styles and languages of software codes and other means of configuring code to perform the tasks in accordance with the invention will not depart from the spirit and scope of the invention.

[00117] The invention may be embodied in other specific forms without departing from its spirit or essential characteristics. The described examples are to be considered in all respects only as illustrative and not restrictive. The scope of the invention is therefore, indicated by the appended claims rather than by the foregoing description. All changes which come within the meaning and range of equivalency of the claims are to be embraced within their scope.

# **CLAIMS**

1.A method of coding a video sequence, wherein pictures from the video sequence include one or more discontinuous edges, the method comprising:

signalling a first syntax in a bitstream at an encoder side or parsing the first syntax from the bitstream at a decoder side, wherein the first syntax indicates whether a loop filtering process is disabled for one or more virtual boundaries in a corresponding region;

5

10

15

20

25

30

receiving a reconstructed filter unit in a current picture, wherein the reconstructed filter unit is associated with a loop filter and the reconstructed filter unit comprises reconstructed pixels for applying the loop filtering process associated with the loop filter to a current reconstructed pixel;

wherein when the first syntax is true, the loop filter processing is disabled when the reconstructed filter unit is across said one or more virtual boundaries in the corresponding region; and

when the first syntax is false, the loop filter processing is not disabled when the reconstructed filter unit is across the virtual boundary in the corresponding region.

2. The method of Claim 1, wherein the first syntax is signalled in or parsed from the bitstream at a syntax level comprising SPS (Sequence Parameter Set), PPS (Picture Parameter Set), APS (Application Parameter Set), slice, tile, picture, CTU (Coding Tree Unit), CU (Coding Unit), PU (Prediction Unit) or TU (Transform Unit) level for the corresponding region.

3. The method of Claim 1, wherein if the first syntax is true, one or more second syntaxes are signalled at the encoder side or parsed at the decoder side, and wherein said one or more second syntaxes indicate virtual boundary information in the corresponding region.

4. The method of Claim 3, wherein said one or more second syntaxes comprise a first number to indicate a number of vertical virtual boundaries and a second number to indicate a number of horizontal virtual boundaries in the corresponding region.

5. The method of Claim 4, wherein each vertical virtual boundary is from a top edge to a bottom edge of the corresponding region and each horizontal virtual boundary is from a left edge to a right edge of the corresponding region; when the first number is greater than 0, locations of each vertical virtual boundary are