(à n'utiliser que pour les commandes de reproduction)

(21) N° d'enregistrement national :

96 08678

(51) Int CI<sup>6</sup>: H 04 L 12/56

(12)

## **DEMANDE DE BREVET D'INVENTION**

**A1**

- (22) Date de dépôt : 11.07.96.

- (30) Priorité: 11.07.95 GB 9514093.

- 71) Demandeur(s): FUJITSU LIMITED JP.

- 43 Date de la mise à disposition du public de la demande : 17.01.97 Bulletin 97/03.

- 56 Liste des documents cités dans le rapport de recherche préliminaire : Ce dernier n'a pas été établi à la date de publication de la demande.

- Références à d'autres documents nationaux apparentés :

- (72) Inventeur(s) : SMITH GRAEME ROY.

- 73 Titulaire(s) :

- (74) Mandataire : CABINET BEAU DE LOMENIE.

(54) APPAREIL DE COMMUTATION DE DONNEES ,PAR EXEMPLE DANS DES RESEAUX A MODE DE TRANSPORT ASYNCHRONE.

Un appareil de commutation, uesuire a curo asservation de commutation, uesuire a curo asservation (20 à 20 ) comportant chacune un moyen de mémorisation (24, à 24,) qui possède des régions de stockage telles qu'elles correspondent respectivement aux autres unités de commutation de la pluralité. Lors d'une phase d'écriture, où des données sont reçues par une première unité de commutation pour être délivrée par une deuxième unité de commutation, la première unité de commutation stocke les données reçues dans la région de stockage de son moyen de mémorisation qui correspond à la deuxième unité de commutation. Dans une phrase de lecture, la deuxième unité de commutation extrait les données stockées dans sa région de stockage correspondante du moyen de mémorisation de la première unité de commutation. Les unités de commutation fonctionnent simultanément sous commande d'une unité de commande (30) qui contrôle les conditions d'intensité du trafic et sélectionne des trajets de transfert de données à l'intérieur des commutateurs afin d'obtenir le débit optimal.

La présente invention concerne un appareil de commutation destiné à être utilisé par exemple pour la commutation de données dans des réseaux à mode de transport asynchrone (ATM).

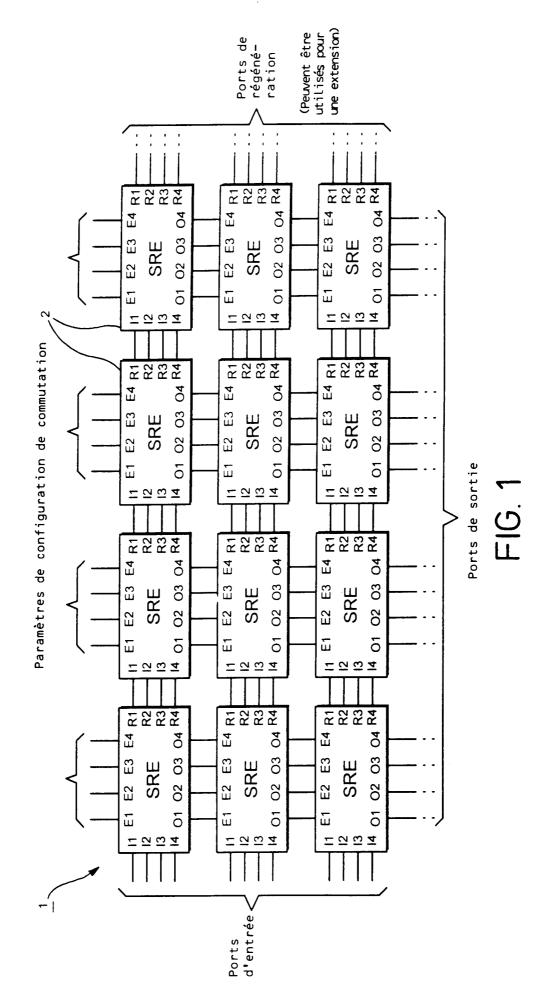

La figure 1 des dessins annexés représente le schéma fonctionnel d'un appareil de commutation classique 1 destiné à être utilisé dans un réseau ATM. Dans l'appareil de la figure 1, plusieurs éléments de commutation d'auto-acheminement (SRE) 2 sont connectés ensemble sous forme matricielle. Chaque SRE 2 possède quatre ports d'entrée I1 à I4 et quatre ports de sortie O1 à O4. A l'intérieur de chaque SRE 2, des cellules ATM, reçues sur n'importe quel port d'entrée I1 à I4 peuvent être acheminées sur n'importe quel port de sortie O1 à O4, et une étiquette d'acheminement associée à chaque cellule ATM traversant un SRE 2 est utilisée pour déterminer à quel port de sortie la cellule considérée sera transmise. Chaque port de sortie possède un tampon de cellules du type "premier entré, premier sorti" qui présente une capacité de stockage de 75 cellules par exemple.

Comme on peut le voir sur la figure 1, les SRE 2 sont disposés suivant une matrice, de sorte que, dans cet exemple, l'appareil de commutation possède, dans son ensemble, 12 ports d'entrée et 16 ports de sortie. Pour faciliter cette connexion sous forme matricielle, chaque SRE 2 possède quatre sorties de régénération R1 à R4, qui sont respectivement associées aux ports d'entrée I1 à I4 du SRE 2 considéré, et possède également quatre entrées d'extension E1 à E4, qui sont respectivement associées aux ports de sorties O1 à O4 du SRE 2 considéré. Les cellules reçues en l'un des ports d'entrée I1 à I4 sont régénérées et repositionnées dans le temps pour être délivrées par la sortie de régénération associée R1 à R4. Les cellules reçues en l'un des ports d'extension E1 à E4 sont insérées dans le tampon de cellules du port de sortie associé O1 à O4.

Les SRE 2 de l'appareil de la figure 1 conviennent pour l'utilisation sous forme matricielle qui est représentée, puisque chaque SRE produit des signaux de sortie actifs repositionnés dans le temps qui permettent une connexion directe avec les SRE constituant ses plus proches voisins. Ceci élimine la nécessité de bus passifs et réduit les problèmes d'interconnexion entre SRE adjacents au niveau de la carte de circuit imprimé.

Le nombre d'éléments de commutation nécessaires pour former un commutateur qui possède N ports d'entrée associés à N ports de sortie est proportionnel à N<sup>2</sup> et, par conséquent, la configuration en matrice n'est réellement appropriée que pour des appareils de commutation relativement petits, par exemple

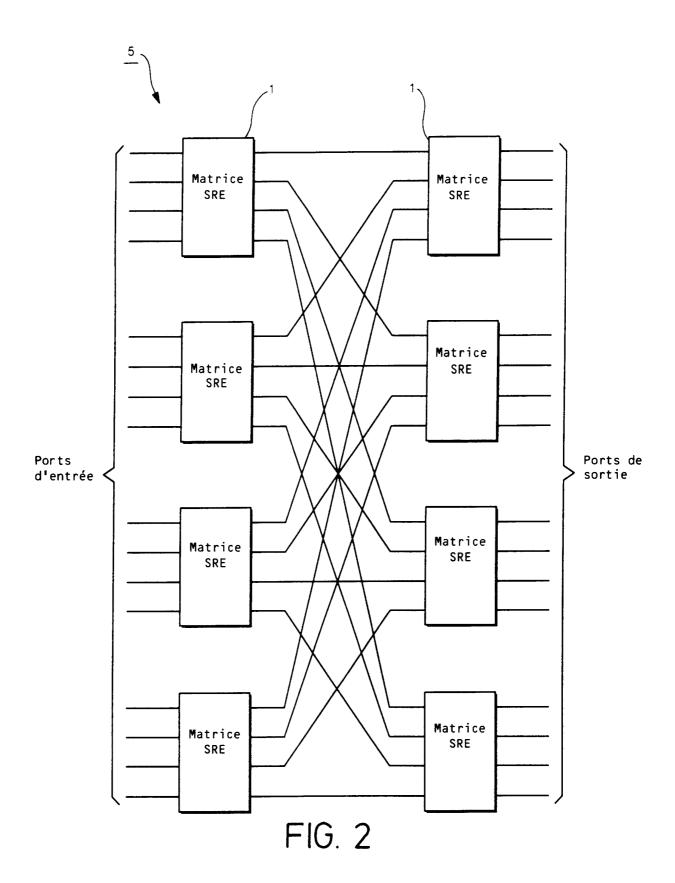

jusqu'à 32 ports d'entrée pour 32 ports de sortie. Dans le cas de commutateurs plus grands, il est possible d'interconnecter des matrices particulières telles que désignées par le numéro de référence 1 sur la figure 1, au moyen d'un montage du type delta à plusieurs trajets, comme représenté sur la figure 2 des dessins annexés.

5

Sur la figure 2, l'appareil de commutation 5 comprend huit matrices de SRE 1 du type présenté sur la figure 1. Ainsi, chacune des matrices 1 de SRE de la figure 2 contient plusieurs SRE 2, disposés en matrice. Les matrices 1 de la figure 2 sont disposées en deux colonnes, et chaque matrice de la colonne gauche comporte des ports de sortie qui sont respectivement connectés au port d'entrée de chaque matrice 1 de SRE de la colonne de droite, et inversement.

10

15

Les matrices de SRE employées dans les appareils de commutation des figures 1 et 2 présentent des montages de transmission par bus fixes et des quantités de mémoire fixes (typiquement, le tampon de cellules associé à chaque port de sortie d'un SRE 2 présente une capacité de stockage de 75 cellules). Toute augmentation de la taille de l'appareil de commutation amène une augmentation, suivant une loi en carré, du nombre des SRE et, aussi, une augmentation en carré du volume de "statistiques" (c'est-à-dire les informations sur l'intensité du trafic) nécessaires pour contrôler les différents noeuds de commutation présents à l'intérieur de l'appareil de commutation. Cette augmentation du volume de statistiques augmente inévitablement les demandes de traitement faites au dispositif de commande de commutation.

20

De plus, lorsque le nombre de noeuds de commutation augmente, il existe un plus grand nombre de points où des phénomènes d'embouteillage peuvent survenir. Il est difficile de contrôler tous ces points en même temps pour fixer l'intensité du trafic et établir quels sont les ports sources qui provoquent l'embouteillage.

25

De plus, la variation du retard des cellules (CDV) d'un commutateur fonctionnant sur la base d'une matrice de SRE est proportionnelle à la taille du commutateur.

30

Un autre problème est que la capacité de mémorisation de chaque SRE est fixée à une certaine valeur, relativement limitée, et ne peut pas être étendue pour aller avec des architectures de commutation différentes.

35

Selon l'invention, il est proposé un appareil de commutation qui comprend une pluralité d'unités de commutation, comportant chacune un moyen de mémorisation qui possède des régions de stockage correspondant respectivement aux autres unités de commutation de ladite pluralité, l'appareil possédant une

phase d'écriture au cours de laquelle, lorsque des données sont reçues par une première des unités de commutation en vue de leur délivrance par une deuxième des unités de commutation, la première unité de commutation stocke les données reçues dans la région de stockage de son moyen de mémorisation qui correspond à la deuxième unité de commutation, et possédant également une phase de lecture au cours de laquelle la deuxième unité de commutation extrait les données stockées dans sa région de stockage correspondante du moyen de mémorisation de la première unité de commutation et elle délivre ces données.

Dans cet appareil de commutation, les données reçues sont transférées directement de l'unité de commutation dans laquelle elles ont été reçues jusqu'à l'unité de commutation par laquelle elles doivent être délivrées. Ainsi, les données sont "stationnaires" une fois stockées dans l'appareil de commutation et ne seront pas transférées d'une unité à une autre un certain nombre de fois, comme dans l'appareil de commutation de la technique antérieure précédemment décrit qui utilise des éléments d'auto-acheminement. Ceci peut éviter les retards de commutation et les problèmes d'embouteillage et, par conséquent, réduit également la variation de retard des cellules (CDV) lorsque l'appareil de commutation est utilisé dans un réseau ATM.

De plus, le transfert de données de l'unité de commutation de réception à l'unité de commutation de délivrance est entièrement interne à l'appareil et peut être effectué à des débits supérieurs aux débits de données des lignes/réseaux de télécommunications avec lesquels l'appareil de commutation est connecté. Ainsi, les retards de commutation et les phénomènes d'embouteillage en sont encore réduits.

De plus, le nombre de noeuds d'entrée/sortie de l'appareil de commutation est simplement égal (ou proportionnel) au nombre d'unités de commutation, de sorte que, si plus de noeuds d'entrée/sortie sont nécessaires, l'augmentation du nombre des unités de commutation nécessaires sera linéaire et ne suivra pas une loi en carré, comme dans l'appareil de commutation de forme matricielle selon la technique antérieure. Le nombre de noeuds de commutation compris à l'intérieur de l'appareil n'augmente aussi que linéairement et, par conséquent, le volume des données statistiques ne subit également qu'une augmentation linéaire (et non une augmentation suivant une loi en carré). Ainsi, l'appareil de commutation constituant un mode de réalisation de l'invention est particulièrement avantageux et rentable sur le plan économique lorsque des nombres relativement importants de noeuds d'entrée/sortie sont nécessaires.

Au cours de ladite phase d'écriture, les unités de commutation sont de préférence activables simultanément, chacune d'elles mémorisant les données qu'elle a reçues, en vue de leur délivrance par une autre des unités de commutation, dans la région de stockage de son moyen de mémorisation qui correspond à cette autre unité de commutation. De la même façon, dans ladite phase de lecture, deux unités de commutation quelconques, ou plus, sont de préférence activables simultanément pour extraire de leurs régions de stockage correspondantes respectives situées dans le moyen de mémorisation de l'autre unité de commutation les données qui sont stockées. Puisque les unités de commutation fonctionnent en parallèle de cette manière, le débit des données peut être aussi élevé qu'on le souhaite.

L'appareil comprend en outre de préférence un moyen de commande qui est connecté à chacune des unités de commutation et qui peut être activé pour sélectionner plusieurs paires moyens de mémorisation—unité de commutation en vue de les utiliser dans ladite phase de lecture, l'unité de commutation de chaque paire étant ainsi conçue pour extraire les données mémorisées de sa région de stockage correspondante du moyen de mémorisation de la paire considérée pendant la phase de lecture. Ceci permet à l'appareil de sélectionner les paires de façon intelligente et adaptive pour réaliser le débit maximal de données et pour éviter les phénomènes d'embouteillage.

Ladite phase de lecture peut comprendre un certain nombre de cycles de lecture. Dans ce cas, les moyens de préférence peuvent être de préférence activés pour sélectionner des paires moyen de mémorisation-unité de commutation différentes au cours de cycles de lecture différents de la même phase de lecture afin de permettre à chaque unité de commutation d'extraire les données qui lui sont destinées de toutes les autres unités de commutation à leur tour. Ledit moyen de commande peut également sélectionner au moins une des paires moyen de mémorisation-unité de commutation dans plus d'un cycle de lecture de la même phase de lecture afin de doter cette paire (ayant par exemple un niveau de trafic plus élevé que d'autres paires) d'une durée de transfert de données plus longue et, par conséquent, permettre que plus de données soient transférées par l'intermédiaire de cette paire que par les autres paires.

Les dites phases d'écriture et de lecture peuvent avoir lieu en alternance, ou bien il peut y avoir une phase d'écriture entre deux cycles de lecture de la même phase de lecture. Il n'est pas nécessaire que les durées des phases respectives, ou des cycles respectifs, soient égales et elles peuvent être modifiées, par exemple par

le moyen de commande, comme cela est nécessaire pour l'obtention d'un débit optimal de données.

De préférence, lesdits moyens de commande peuvent être activés pour sélectionner les paires moyen de mémorisation-unité de commutation en fonction des conditions d'intensité du trafic dans l'appareil. Par exemple, les moyens de commande peuvent comporter des moyens de contrôle d'intensité de trafic qui sont activés pour contrôler les quantités de données stockées dans chaque région de stockage du moyen de mémorisation des unités de commutation, les moyens de commande employant les quantités contrôlées lors de l'exécution de la sélection des paires moyen de mémorisation-unité de commutation. Cette approche offre un autre avantage en ce que des statistiques de commutation sont également produites automatiquement du fait de la fonction de contrôle des moyens de commande.

Lorsque l'appareil est utilisé dans un réseau ATM, les moyens de commande peuvent également tenir compte des priorités des cellules lors de l'établissement des sélections de paires moyen de mémorisation-unité de commutation. De plus, en utilisant sa connaissance des intensités du trafic, lorsque l'appareil est utilisé dans un réseau ATM, le moyen de commande peut également faire que l'une des unités de commutation envoie des cellules de gestion de trafic appropriées à la source de données envoyant des données à cette unité de commutation afin d'amener la source à "couper" son débit de cellules. Ainsi, on peut éviter les situations potentielles d'embouteillage.

L'appareil comprend en outre de préférence un moyen faisant fonction de bus qui interconnecte les unités de commutation, ledit moyen bus comportant une pluralité d'unités de lignes de bus distinctes, les unités de lignes de bus étant aussi nombreuses que les unités de commutation, et chaque unité de commutation étant connectée à toutes les unités de lignes de bus, tandis que les moyens de mémorisation respectifs des unités de commutation ne sont connectés qu'à des unités de lignes de bus respectives différentes. Puisqu'il y a autant d'unités de lignes de bus qu'il y a d'unités de commutation, un fonctionnement simultané (en parallèle) de toutes les unités de commutation est possible. Ce moyen bus peut fournir des connexions simples entre les différentes unités de commutation qui peuvent aisément être mises en oeuvre au niveau de la carte de circuit imprimé. Les unités de commutation peuvent par exemple être disposées l'une après l'autre suivant la direction des colonnes, les lignes de bus s'étendant côte à côte dans cette direction des colonnes via les unités de commutation ou jusqu'à un côté de celles-ci.

Le moyen de commande synchronise de préférence le fonctionnement des unités de commutation de manière qu'on obtienne des performances générales efficaces de l'appareil de commutation. Dans la phase de lecture, ledit moyen de commande peut de préférence être activé pour sélectionner les paires moyen de mémorisation—unité de commutation de façon que, au cours de cette phase, toutes les unités de commutation qui extraient des données mémorisées de manière simultanée dans leurs moyens de mémorisation appariés respectifs le fassent via des unités de lignes de bus différentes, afin d'éviter les collisions de bus au cours de ce fonctionnement simultané des unités de commutation. Ceci évite la nécessité d'un circuit logique distinct servant à éviter les collisions, lequel circuit serait nécessaire si les différentes unités de commutation pouvaient commander leurs accès aux bus respectifs indépendamment les uns des autres et de manière asynchrone.

Lesdits moyens de mémorisation de chaque unité de commutation sont de préférence employés pour produire des blocs de mémorisation du type "premier entré, premier sorti" virtuels correspondant respectivement auxdites régions de stockage, chaque bloc ayant des pointeurs d'écriture et de lecture respectifs, qui sont également stockés dans le moyen de mémorisation de l'unité de commutation considérée, et qui sont destinés à être utilisés par les unités de commutation lors du stockage de données et de l'extraction de données dans la région de stockage correspondante. Ceci permet qu'un dispositif de mémorisation à accès direct simple (et peu coûteux même pour une grande capacité de stockage) soit utilisé comme moyen de mémorisation à la place d'un dispositif spécialisé du type "premier entré, premier sorti" par exemple.

Dans un mode de réalisation préféré, chaque unité de commutation

possède un moyen de manipulation multidestinataire ayant pour fonction, lorsque des données multidestinataire sont reçues par l'unité de commutation considérée en vue d'être délivrées par une pluralité d'autres unités de commutation désignées, de mémoriser les données multidestinataire reçues dans la région de stockage de son moyen de mémorisation qui correspond, simplement, à une première de ces unités de commutation désignées et de mémoriser dans les régions de stockage correspondant respectivement aux unités de commutation désignées restantes un pointeur d'adresse multidestinataire indiquant l'emplacement des données multidestinataire dans la région de stockage correspondante de la première unité de commutation désignée. Ceci permet d'éviter de devoir écrire les données multi-

destinataire plusieurs fois dans les différentes unités de stockage correspondant

respectivement aux unités de commutation multidestinataire désignées et, par conséquent, d'améliorer le rendement. Au lieu de cela, une région de stockage multidestinataire spécialisée peut être prévue dans chaque moyen de mémorisation, des données multidestinataire quelconques étant écrites dans cette région seule et des pointeurs d'adresse multidestinataire étant stockés dans les régions de stockage de toutes les unités de commutation multidestinataire désignées.

5

10

15

20

25

30

35

Dans un autre mode de réalisation, lesdits moyens de mémorisation possèdent chacun des ports respectifs d'écriture et de lecture et sont conçus de façon que des données puissent être écrites sur ledit port d'écriture en même temps que des données sont extraites dudit port de lecture; le port de lecture du moyen de mémorisation de chaque unité de commutation étant connecté à toutes les autres unités de commutation, mais le port d'écriture du moyen de mémorisation de chaque unité de commutation n'étant pas connecté à toutes les autres unités de commutation. Ainsi, au cours de ladite phase de lecture, des données reçues par chaque unité de commutation peuvent être stockées dans le moyen de mémorisation de l'unité considérée tandis que des données précédemment stockées sont extraites de ce moyen de mémorisation par une autre unité de commutation. Par conséquent, la phase d'écriture peut se chevaucher avec la phase de lecture.

Chaque unité de commutation peut comporter une partie de commande de ports de commutation, connectée à des ports respectifs d'entrée et de sortie de l'unité de commutation, et ayant pour fonction, lorsque des données sont reçues sur ledit port d'entrée, de produire une étiquette d'acheminement identifiant la région de stockage dudit moyen de mémorisation de l'unité de commutation où les données reçues doivent être stockées. Cette étiquette d'acheminement est utilisée par l'unité de commutation pour stocker les données dans la région de stockage voulue de son moyen de mémorisation, mais il n'est toutefois pas nécessaire que l'étiquette d'acheminement elle-même soit stockée dans la région de stockage (aussi bien que les données) puisque les données sont stationnaires une fois stockées dans la région de stockage et ne passent pas par de nombreuses unités de commutation différentes comme dans les éléments d'auto-acheminement de la technique antérieure ci-dessus décrits. Ainsi, on augmente le rendement de transfert et on réduit les signaux auxiliaires de servitude d'acheminement et les conditions liées au stockage.

De préférence, chaque unité de commutation comporte un élément de commutation adaptatif qui est connecté audit moyen de commande afin de recevoir de celui-ci des informations de commande de bus, identifiant les paires moyen de mémorisation-unité de commutation sélectionnées, et ayant pour fonction, selon cette information de commande, d'activer les unités de lignes de bus appropriées à leur tour pendant le cours de la phase de lecture afin de faciliter le transfert des données du moyen de mémorisation à l'unité de commutation de chaque paire sélectionnée de l'unité de commutation concernée. En prévoyant un tel élément de commutation adaptatif dans chaque unité de commutation, pour effectuer un séquencement de bus de bas niveau et d'autres opérations au nom du moyen de commande, on peut laisser le moyen de commande effectuer les tâches de haut niveau nécessaires et contrôler les intensités de trafic.

5

10

15

20

25

30

35

La description suivante, conçue à titre d'illustration de l'invention, vise à donner une meilleure compréhension de ses caractéristiques et avantages ; elle s'appuie sur les dessins annexés, parmi lesquels :

la figure 1, qui a été décrite précédemment, montre un schéma de principe d'un appareil de commutation ATM classique;

la figure 2, également décrite ci-dessus, montre un autre exemple d'appareil de commutation classique;

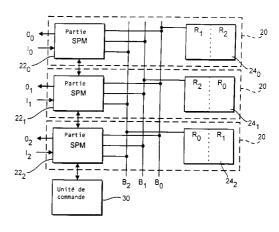

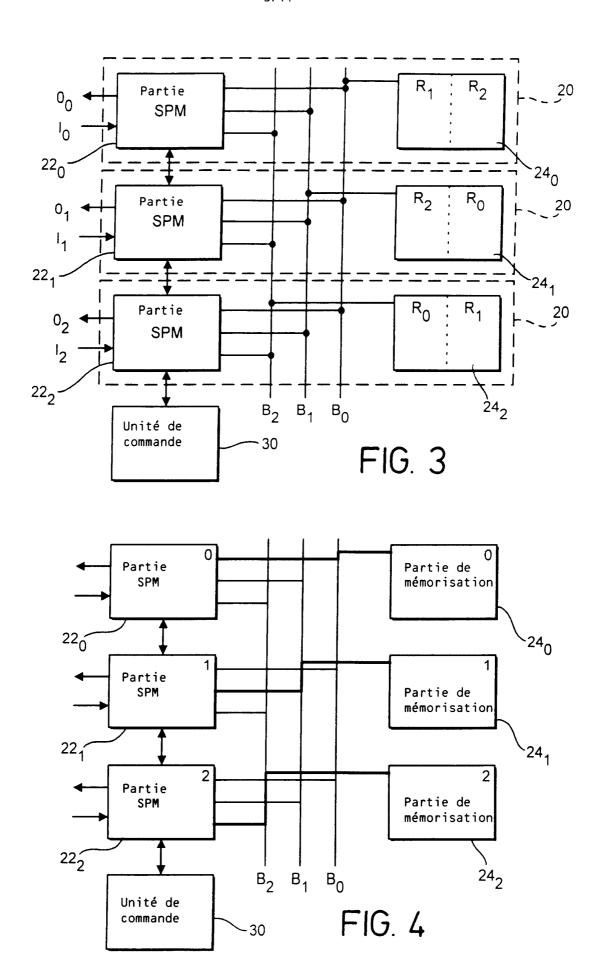

la figure 3 représente un schéma de principe d'un appareil de commutation ATM qui constitue un mode de réalisation de l'invention;

les figures 4 à 6 sont des schémas fonctionnels illustrant le fonctionnement de l'appareil de la figure 3, à différentes phases de fonctionnement;

la figure 7 représente un schéma fonctionnel qui illustre, de manière plus détaillée que la figure 3, une partie de l'appareil de la figure 3;

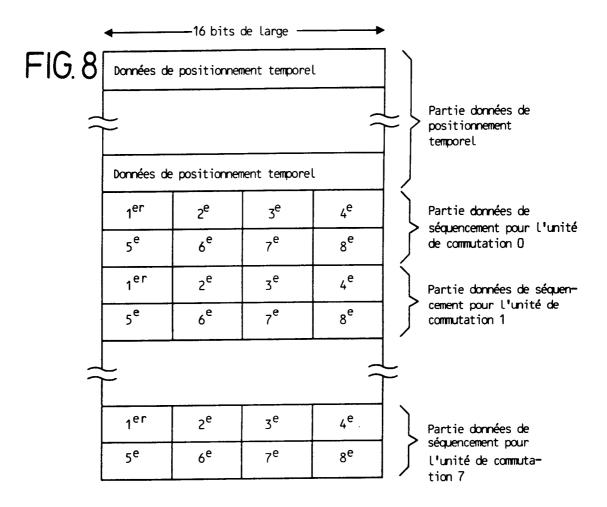

la figure 8 représente un exemple du format d'informations de commande utilisé dans l'appareil de la figure 3;

les figures 9(A) à 9(C) représentent des tables destinées à être utilisées pour expliquer comment le fonctionnement de l'appareil de la figure 3 se modifie en fonction des conditions d'intensité du trafic ;

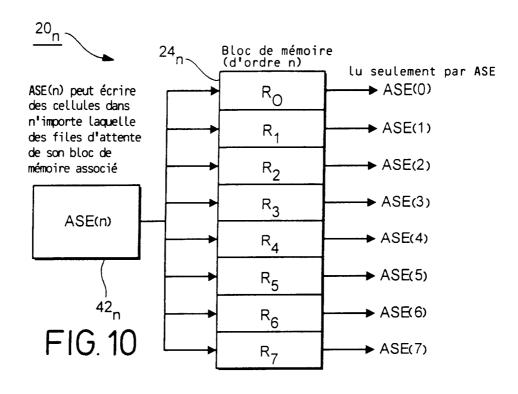

la figure 10 représente un schéma simplifié d'une partie de l'appareil de la figure 3 ;

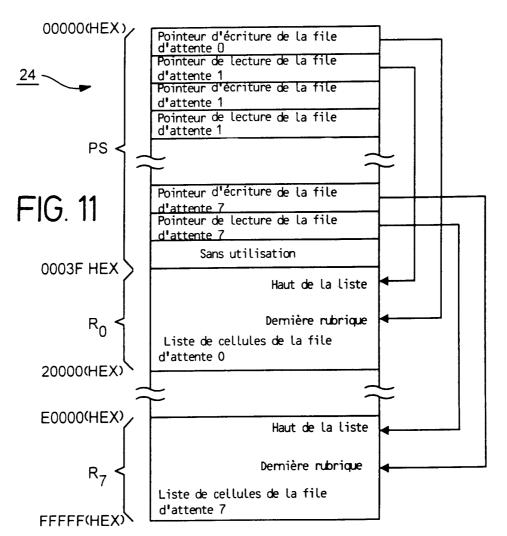

la figure 11 représente un exemple du format sous lequel des données sont mémorisées dans la partie de la figure 10;

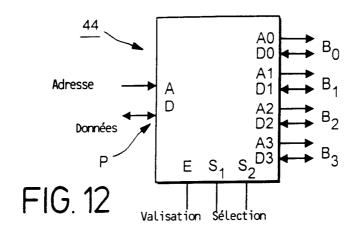

la figure 12 représente un schéma fonctionnel d'un élément de circuit apparaissant sur la figure 7;

la figure 13 représente un schéma de circuit détaillé d'un autre élément de circuit apparaissant sur la figure 7;

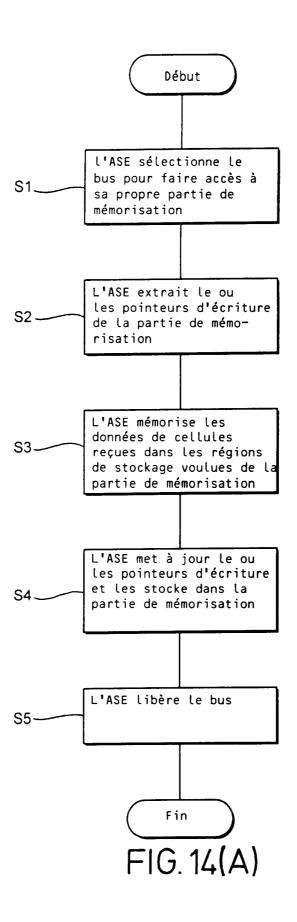

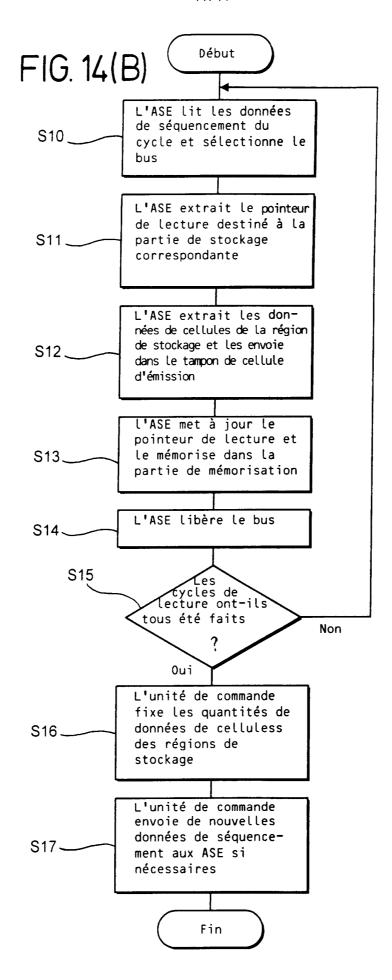

les figures 14(A) et 14(B) représentent respectivement des organigrammes associés au fonctionnement de l'appareil de la figure 3; et

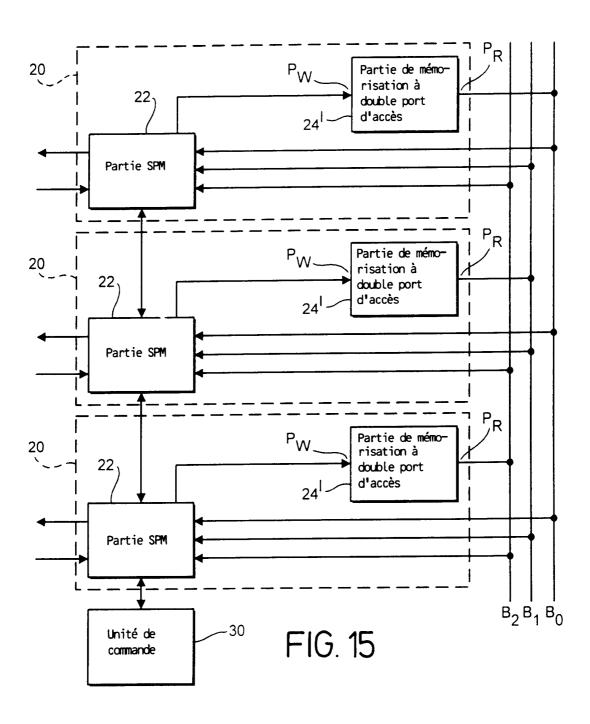

la figure 15 représente un schéma fonctionnel d'un autre appareil de commutation ATM constituant un mode de réalisation de l'invention.

5

10

15

20

25

30

35

On se reporte à la figure 3. Un appareil de commutation ATM 10, constituant un mode de réalisation de l'invention, comporte une pluralité d'unités de commutation 200 à 202 et une unité de commande 30. Les unités de commutation 200 à 202 possèdent des ports d'entrée respectifs I0 à I2 et des ports de sortie respectifs O<sub>0</sub> à O<sub>2</sub>. Chaque unité de commutation 20<sub>0</sub> à 20<sub>2</sub> comporte une partie 22 (notée respectivement 22<sub>0</sub> à 22<sub>1</sub>) de gestion des ports du commutateur (notée SPM), qui est connectée au port d'entrée I (respectivement I<sub>0</sub> à I<sub>1</sub>) et au port de sortie O (respectivement O<sub>0</sub> à O<sub>1</sub>) de l'unité de commutation considérée, et comporte également une partie de mémorisation 24 (notée respectivement 240 à 24<sub>1</sub>). Des lignes de bus B<sub>0</sub> à B<sub>2</sub>, qui comprennent chacune des lignes de données, d'adressage et de commande, servent à interconnecter les parties SPM 220 à 222 et les parties de mémorisation 240 à 242. Alors que chaque partie SPM 22 est connectée aux trois lignes de bus B<sub>0</sub> à B<sub>2</sub>, chaque partie de mémorisation 24 n'est connectée qu'à une seule des lignes de bus. On aura compris que les références 200 à  $20_2$ ,  $22_0$  à  $22_2$ ,  $24_0$  à  $24_2$ ,  $I_0$  à  $I_2$ ,  $O_0$  à  $O_2$ , de même que  $B_0$  à  $B_2$  et  $R_0$  à  $R_2$ , sont respectivement désignées par 20, 22, 24, I, O, B et R, dans un soucis de brièveté pour éviter des répétitions inutiles (voir aussi les figures 5, 11 et 15).

Comme on peut le voir sur la figure 3, chaque partie de mémorisation 24 est divisée en deux régions de stockage. Dans le cas de la partie de mémorisation 240 de la première unité de commutation 200, les deux régions sont désignées par les références R<sub>1</sub> et R<sub>2</sub> et correspondent respectivement aux ports de sortie O<sub>1</sub> et O<sub>2</sub> des deuxième et troisième unités de commutation 20<sub>1</sub> et 20<sub>2</sub>. Dans le cas de la partie de mémorisation 24<sub>1</sub> de la deuxième unité de commutation 20<sub>1</sub>, les deux régions de stockage sont désignées par les références R<sub>2</sub> et R<sub>0</sub> et correspondent respectivement aux ports de sortie O<sub>2</sub> et O<sub>0</sub> des troisième et première unités de commutation 20<sub>2</sub> et 20<sub>0</sub>. Dans le cas de la partie de mémorisation 24<sub>2</sub> de la troisième unité de commutation 20<sub>2</sub>, les deux régions de stockage sont désignées par les références R<sub>0</sub> et R<sub>1</sub> et correspondent respectivement aux ports de sortie O<sub>0</sub> et O<sub>1</sub> des première et deuxième unités de commutation 20<sub>0</sub> et 20<sub>1</sub>. Par conséquent, on peut voir que la partie de mémorisation 24 de chaque unité de commutation 20 possède des régions de stockage qui correspondent respectivement aux autres unités de commutation de l'appareil.

Chaque région de stockage R fait fonction de liste séquentielle ou d'unité FIFO (premier entré, premier sorti).

L'appareil présenté à titre d'exemple sur la figure 3 a été simplifié, dans un but illustratif, et il ne comporte que trois unités de commutation et trois lignes de bus. En pratique, il y a plus d'unités de commutation et de lignes de bus que cela, par exemple huit lignes de bus au total.

5

10

15

20

25

30

35

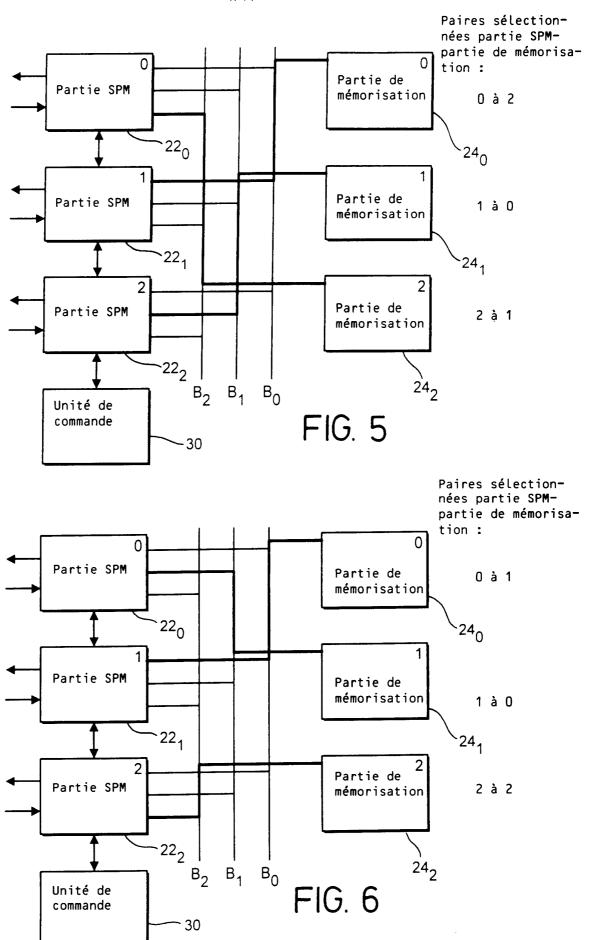

On va maintenant expliquer le fonctionnement de la figure 3 en liaison avec les figures 4 à 6. Au cours d'une première phase de fonctionnement (phase d'écriture), représentée sur la figure 4, la partie SPM 22 de chaque unité de commutation 20 reçoit des cellules de la part de son port d'entrée I associé. Ces cellules auront un indicateur de numéro de port annexé, qui identifie le port de sortie sur lequel la cellule doit être acheminée, ou bien, un indicateur multidestinataire. Cet indicateur multidestinataire est utilisé quand des cellules reçues sur un port d'entrée doivent être acheminées sur plusieurs ports de sortie différents, au lieu d'un seul port de sortie simplement. En réponse à la réception de chaque cellule, la partie SPM 22 écrit la cellule aux emplacements libres consécutifs suivants de la région de stockage R appropriée de la partie de mémorisation 24 de sa propre unité de commutation 20. Ce processus est effectué simultanément par les autres parties SPM, chaque partie SPM utilisant une ligne différente parmi les lignes de bus B<sub>0</sub> à B2, comme représenté par les lignes en trait gras de la figure 4. Par exemple, lorsqu'une cellule est reçue dans un port d'entrée I<sub>1</sub> et est destinée à un canal de sortie O<sub>2</sub>, la partie SPM 22<sub>1</sub> de l'unité de commutation 20<sub>1</sub> stocke la cellule considérée dans la région de stockage R2 de la partie de mémorisation 241 de l'unité de commutation de sa propre unité de commutation 20<sub>1</sub>.

Ensuite, le fonctionnement passe à la phase de lecture. Au cours d'un premier cycle de la phase de lecture, comme représenté sur la figure 5, l'unité de commande 30 de l'appareil fait que chaque partie SPM 22 reconfigure sa sélection de bus de façon à faire accès à d'autres parties de mémorisation 24 appartenant à d'autres unités de commutation que la sienne propre. Par exemple, comme représenté sur la figure 5, chaque partie SPM 22 adresse maintenant la partie de mémorisation 24 de l'unité de commutation précédente. Chaque partie SPM 22 lit donc alors des données de cellules venant de sa région de stockage correspondante de cette partie de mémorisation, et, par exemple, la partie SPM 220 lit des données de cellules dans la région de stockage R<sub>0</sub> de la partie de mémorisation 24<sub>1</sub>, la partie SPM 22<sub>1</sub> lit les données de cellules dans sa région de stockage correspondante R<sub>1</sub> de la partie de mémorisation 24<sub>2</sub>, et la partie SPM 22<sub>2</sub> lit les

données de cellules dans la région de stockage R<sub>2</sub> de la partie de mémorisation 24<sub>0</sub>.

Ainsi, plusieurs paires unité de commutation-partie de mémorisation sont sélectionnées par l'unité de commande pour être utilisées pour la lecture de données de cellules, chaque paire ayant son propre trajet de transfert de données qui utilise une ligne différente parmi les lignes de bus B<sub>0</sub> à B<sub>2</sub>.

5

10

15

20

25

30

35

Sous commande de l'unité de commande 30, au cours de cycles ultérieurs successifs de la phase de lecture, les parties SPM 22<sub>0</sub> à 22<sub>2</sub> pourraient alors être programmées pour lire les parties de mémorisation 24<sub>0</sub> à 24<sub>2</sub> en séquence sur la base modulo n (ici n est petit et vaut 3).

Toutefois, selon un mode de réalisation préféré de l'invention, l'unité de commande 30 commande l'accès fait par les parties SPM aux parties de mémorisation en fonction des intensités de trafic à un instant donné quelconque. En contrôlant le nombre de cellules écrites dans les régions de stockage et le nombre de cellules qui y sont lues, l'unité de commande 30 est en mesure de prévoir où des sources éventuelles d'embouteillage apparaîtront et de programmer les parties SPM de façon à permettre à certains trajets partie SPM-partie de mémorisation d'être établis pour des périodes plus longues, de façon à réduire des situations éventuelles d'embouteillage.

Par exemple, la figure 6 illustre un scénario de trafic possible, dans lequel il existe une quantité relativement importante de trafic arrivant sur le port d'entrée I<sub>0</sub> et destinée à être délivrée via le port de sortie O<sub>1</sub>. Dans ce cas, l'unité de commande 30 détermine que le trafic s'accumule de manière non souhaitable dans la région de stockage R<sub>1</sub> de la partie de mémorisation 24<sub>0</sub>. Pour traiter ce cas, l'unité de commande permet que le trajet entre la partie SPM 22<sub>1</sub> et la partie de mémorisation 24<sub>0</sub> reste "ouvert" lorsque le cycle de lecture suivant commence à la suite du premier cycle de lecture présenté sur la figure 5. Ainsi, même si la partie SPM 22<sub>0</sub> cesse de faire accès à la partie de mémoire 24<sub>2</sub> pour faire accès à la partie de mémoire 24<sub>1</sub>, et que la partie SPM 22<sub>2</sub> cesse de faire accès à la partie de mémoire 24<sub>1</sub>, le trajet établi dans le premier cycle de lecture de la figure 5, allant de la partie SPM 22<sub>1</sub> à la partie de mémorisation 24<sub>0</sub>, reste ouvert sur la figure 6. De ce fait, un plus grand nombre de cellules peuvent être transférées de la partie de mémorisation 24<sub>0</sub> à la partie SPM 22<sub>1</sub> pour tenir compte de l'intensité chargée du trafic.

Par conséquent, l'unité de commande 30 peut contrôler les quantités de données de cellules stockées dans les différentes régions de stockage et calculer

quels trajets partie SPM-partie de mémorisation doivent être établis dans la phase de lecture pour transférer la quantité optimale de données de cellules et, par conséquent, réduire les problèmes éventuels d'embouteillage. L'unité de commande 30 comprend par exemple un microprocesseur.

On va maintenant donner des détails sur la structure et le fonctionnement de l'appareil de la figure 3.

5

10

15

20

25

30

35

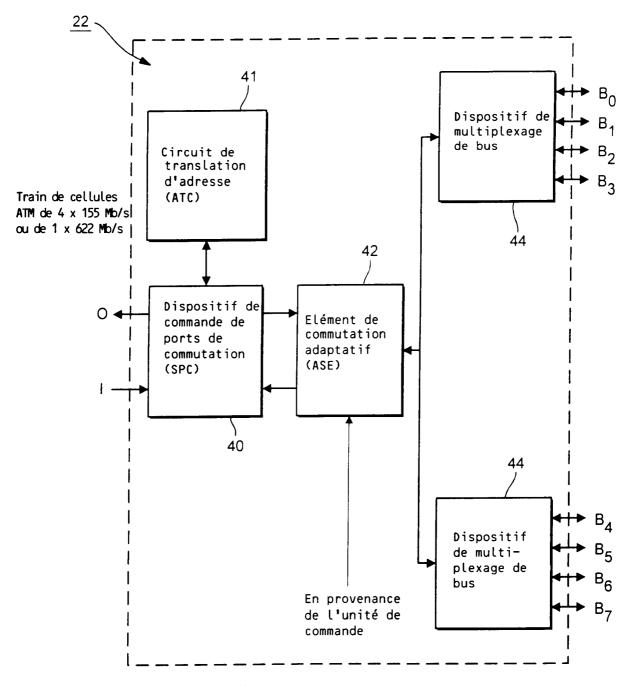

La figure 7 représente un schéma fonctionnel d'une structure possible pour chaque partie SPM 22. Dans l'exemple de la figure 7, la partie SPM 22 est destinée à être utilisée dans un appareil de commutation ayant huit unités de commutation au total, et huit lignes de bus B<sub>0</sub> à B<sub>7</sub>.

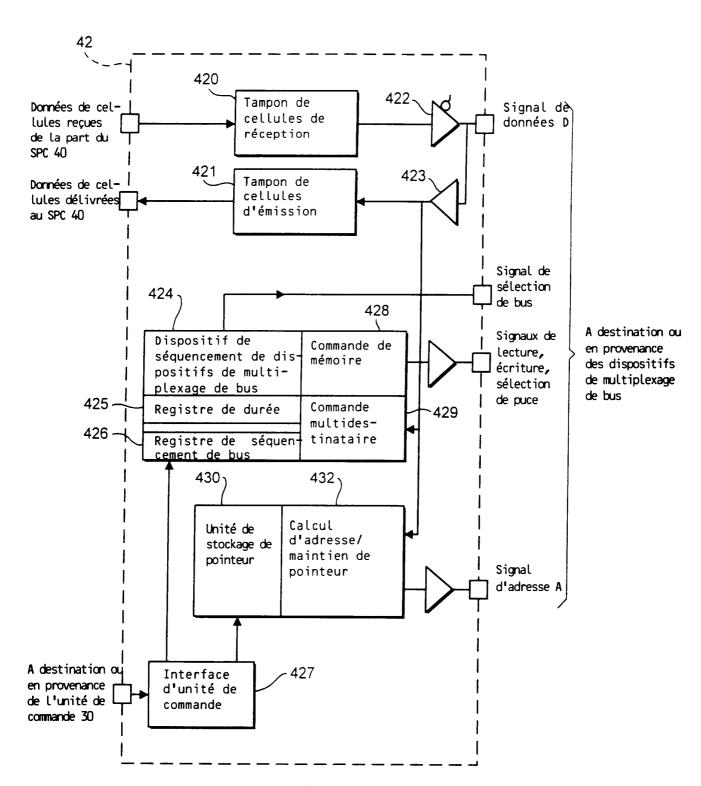

La partie SPM 22 de la figure 7 comporte une unité dispositif de commande de ports de commutation (SPC) 40, un circuit de translation d'adresse (ATC) 41, un élément de commutation adaptatif (ASE) 42, et deux unités dispositif de multiplexage de bus 44. L'unité SPC 40 est connectée directement aux ports d'entrée I et de sortie O du commutateur considéré. Chaque port peut recevoir, ou émettre, selon le cas, un unique courant de cellules ATM de 622 Mb/s ou quatre courants de cellules particuliers de 155 Mb/s.

Lorsqu'une cellule ATM est reçue par l'unité SPC 40, l'unité ATC 41 examine l'information d'adressage (zones d'identification de trajet virtuel (VPI) et identification de canal virtuel (VCI) de la partie en-tête de la cellule) transportée par la cellule et effectue une opération de translation d'adresse appropriée afin de déterminer à quel port de sortie la cellule doit être acheminée. En fonction de l'information de translation d'adresse, l'unité SPC 40 affecte à la cellule l'indicateur de numéro de port ci-dessus mentionné et, ou bien, l'indicateur multidestinataire.

L'ASE 42 reçoit ensuite la cellule considérée et ajuste son transfert à la partie de mémorisation 24 de sa propre unité de commutation. Dans la phase d'écriture, l'ASE 42 applique des signaux de sélection de bus appropriés aux unités 44 dispositif de multiplexage de bus afin de sélectionner la seule ligne de bus B à laquelle la propre partie de mémorisation de l'unité de commutation est connectée. L'unité dispositif de multiplexage de bus 44 supérieure de la figure 7 est associée aux quatre premières lignes de bus B<sub>0</sub> à B<sub>3</sub>, tandis que l'unité dispositif de multiplexage de bus 44 inférieure de la figure 7 est associée aux quatre lignes de bus B<sub>4</sub> à B<sub>7</sub> restantes. Par exemple, si la partie SPM montrée sur la figure 7 est comprise dans l'unité de commutation 20<sub>2</sub>, la ligne de bus voulue est B<sub>2</sub> si bien que l'ASE 42 invalide l'unité dispositif de multiplexage de bus inférieure 44 et valide l'unité dispositif de multiplexage de bus supérieure 44, et elle donne

instruction à l'unité dispositif de multiplexage de bus supérieure 44 d'effectuer le transfert de données entre la ligne de bus B<sub>2</sub> et l'ASE 42. Dès que la sélection du bus a été effectuée de cette manière, la cellule reçue est transférée par l'ASE à la région de stockage de la propre partie de mémorisation de l'unité de commutation qui correspond au port de sortie voulu.

5

10

15

20

25

30

35

Une fois terminée la phase d'écriture, l'ASE 42 commute dans la phase de lecture. L'ASE 42 reçoit de la part de l'unité de commande 30 des informations de commande qui spécifient les parties de mémorisation auxquelles elle doit effectuer l'adressage à chaque cycle de la phase de lecture. L'ASE 42 emploie cette information pour sélectionner les bus B<sub>0</sub> à B<sub>7</sub> voulus qui seront nécessaires dans chaque cycle différent pour faciliter le transfert de données de la partie de mémorisation spécifiée à l'ASE 42. L'ASE 42 effectue les sélections appropriées à l'aide des unités dispositif de multiplexage de bus 44. Les données lues dans les parties de mémorisation sont transférées par l'ASE 42 à l'unité SPC 40 et sont délivrées via le port de sortie O de l'unité de commutation considérée.

Par conséquent, dans la phase de lecture, l'unité de commande 30 commande effectivement, via l'ASE 42 de chaque partie SPM 22, le fonctionnement des unités dispositif de multiplexage de bus 44 dans la partie SPM considérée. L'unité de commande 30 fait que la commutation de tous les bus par les différentes parties SPM 22 a lieu en même temps de façon à empêcher des collisions de bus et les détériorations éventuelles de données qui peuvent en résulter.

Comme précédemment indiqué, l'unité de commande 30 détermine une sélection des paires partie SPM-partie de mémorisation qui sont destinées à être utilisées dans chaque cycle de la phase de lecture. La figure 8 montre un exemple de l'information de commande produite par l'unité de commande 30 et envoyée à chaque unité de commutation afin de commander son fonctionnement pendant la phase de lecture.

L'information de commande comporte une partie données de positionnement temporel initial. La partie données de positionnement temporel contient des données de positionnement temporel qui sont utilisées pour déterminer la durée de chaque cycle particulier de la phase de lecture. Par exemple, cette durée peut être spécifiée comme étant de 10 ou 20 cellules. Ces données de positionnement temporel sont les mêmes pour toutes les unités de commutation. Les durées des cycles particuliers pourraient être toutes les mêmes, auquel cas les données de positionnement temporel sont brèves, ou pourraient être différentes les unes des autres.

L'information de commande comporte en outre des parties de données de séquencement se rapportant à chaque unité de commutation. Dans l'exemple de la figure 8, chaque partie de données de séquencement possède huit rubriques. Par conséquent, l'exemple de la figure 8 correspond à la partie SPM 22 de la figure 7, où il y a huit parties de mémorisation différentes si bien que chaque phase de lecture comprend huit cycles de lecture. Les huit rubriques différentes correspondent respectivement aux huit cycles de lecture, et chaque rubrique indique par conséquent à quelle partie de mémorisation l'unité de commutation considérée doit faire accès au cours du cycle considéré.

5

10

15

20

25

30

35

L'information de commande est envoyée périodiquement aux ASE 42 des unités de commutation par l'unité de commande, ce qui permet de modifier les sélections des paires partie SPM-partie de mémorisation en fonction des conditions d'intensité du trafic.

Comme cela sera décrit ultérieurement de manière plus détaillée, chaque unité ASE 42 comporte un registre de séquencement de bus servant à stocker les données de séquencement qui se rapportent à sa propre unité de commutation, ainsi qu'un registre de positionnement temporel servant à stocker les données de positionnement temporel.

La capacité de l'unité de commande à modifier dynamiquement les sélections des paires partie SPM-partie de mémorisation en réponse aux conditions d'intensité du trafic est un avantage principal de l'appareil de commutation présenté sur la figure 3.

Les figures 9(A) à 9(C) montrent d'autres exemples de possibilités de sélections de paires partie SPM-partie de mémorisation dans différents scénarios d'intensité du trafic. Sur la table de la figure 9(A), il existe quatre parties SPM qui sont notées A à D et quatre parties de mémorisation qui sont notées W à Z. Ainsi la partie SPM notée A et la partie de mémorisation notée W font partie de la même unité de commutation (20 sur la figure 3), la partie SPM notée B et la partie de mémorisation notée X font partie d'une autre unité de commutation, et ainsi de suite.

On se reporte maintenant à la figure 9(B), qui montre, dans un premier des deux scénarios d'intensité de trafic, une intensité de trafic intense du port d'entrée I<sub>B</sub> de la partie SPM B ou du port de sortie O<sub>D</sub> de la partie SPM D. Dans ce cas, la phase de lecture comprend trois cycles de lecture ayant les tranches de

temps T<sub>1</sub> à T<sub>3</sub> respectives. L'unité de commande 30 détermine qu'une grande quantité de données de cellules s'accumule dans la région de stockage R<sub>D</sub> de la partie de mémorisation X correspondant à la partie SPM D et, par conséquent, maintient ouvert le trajet entre la partie de mémorisation X et la partie SPM D pendant les trois tranches de temps T<sub>1</sub> à T<sub>3</sub>. Les sélections de paires relatives aux parties SPM restantes A à C et aux parties de mémorisation associées W, Y et Z changent à chaque cycle de lecture de manière cyclique, comme représenté sur la figure 9(B).

La figure 9 (C) montre un deuxième scénario d'intensités de trafic, au cours duquel il existe deux intensités de trafic dominantes, à savoir celle allant du port d'entrée I<sub>C</sub> de la partie SPM C au noeud de sortie O<sub>A</sub> de la partie SPM A et celle allant du noeud d'entrée I<sub>B</sub> de la partie SPM B au noeud de sortie O<sub>D</sub> de la partie SPM D. Dans ce cas, l'unité de commande 30 maintient ouverts pendant les trois tranches de temps T1 à T3 le trajet allant de la partie de mémorisation Y à la partie SPM A et le trajet allant de la partie de mémorisation X à la partie SPM D. Les trajets reliant les deux autres parties SPM B et C et les deux autres parties de mémorisation W et Z varient cycliquement sur les trois tranches de temps, les tranches de temps T1 et T3 ayant, dans cet exemple, des sélections de trajets identiques.

Enfin, si un embouteillage est inévitable, l'unité de commande 30 peut donner instruction à la partie SPM concernée de délivrer des cellules de notification explicite d'embouteillage vers l'avant (FECN), des cellules de notification explicite d'embouteillage vers l'arrière (BECN) ou des cellules de gestion de ressources (RM) à destination de la source qui est en train de fournir les données allant au port d'entrée de la partie SPM considérée, de façon que la source puisse alors "couper" temporairement la production de cellules.

La figure 10 est une vue simplifiée de l'une des unités de commutation 20 de la figure 3, indiquant des transferts de données. L'espace de stockage de la partie de mémorisation 24 de chaque unité de commutation 20 est divisé de façon égale par le nombre N d'unités de commutation existant dans l'appareil. Par exemple, s'il y a huit unités de commutation dans l'appareil, alors chaque partie de mémorisation sera divisée en huit régions de stockage distinctes  $R_0$  à  $R_7$  d'une même longueur. Plus exactement, l'espace de stockage de chaque partie de mémorisation 24 doit être divisé en N-1 régions de stockage, puisqu'une partie SPM n'a pas besoin de région de stockage pour sa propre unité de commutation de sa propre partie de mémorisation, puisque ceci amènerait que des cellules écrites dans cette

région de stockage seraient lues par la même unité de commutation. De telles opérations d'écriture et de lecture peuvent être utiles dans un mode d'essai, ou bien s'il faut stocker des cellules bouclant sur elles-mêmes. Toutefois, ces modes de fonctionnement seront de préférence réalisés par l'unité SPC 40 de chaque partie SPM 22.

Chaque région de stockage R<sub>0</sub> à R<sub>7</sub> de la figure 10 constitue une unité FIFO (premier entré, premier sorti) virtuelle, l'unité FIFO produisant une file d'attente de données pour son unité de commutation correspondante de l'appareil de commutation. Comme on peut le voir sur la figure 10, une partie SPM n'est autorisée qu'à écrire les données de cellules dans sa partie de mémorisation associée, à savoir la partie de mémorisation se trouvant dans sa propre unité de commutation, tandis qu'une partie SPM peut lire des données dans n'importe quelle partie de mémorisation, mais seulement dans les régions de stockage de ces parties de mémorisation qui correspondent à la partie SPM considérée.

La figure 11 montre de manière plus détaillée une structure d'organisation possible de chaque partie de mémorisation 24. Pour chaque file d'attente, il existe des pointeurs de lecture et d'écriture du registre FIFO correspondant. Ces pointeurs sont stockés dans une partie PS de stockage de pointeurs de la partie de mémorisation elle-même, car ils doivent être disponibles à toutes les parties SPM de l'appareil de commutation. Ces pointeurs sont initialisés, lus et mis à jour par les ASE 42 des parties SPM 22. Les pointeurs sont stockés aux mêmes emplacements dans chaque partie de mémorisation afin de faciliter un fonctionnement cohérent entre toutes les unités de commutation 20. Ceci rend en outre plus facile la programmation par l'unité de commande 30.

Initialement, les pointeurs et la taille de chaque file d'attente (région de stockage) se trouvant à l'intérieur d'une partie de mémorisation sont déterminés par l'unité de commande 30. L'unité de commande 30 initialise les pointeurs de lecture et d'écriture pour chaque file d'attente via les ASE 42 respectifs des unités de commutation.

Après cette initialisation, les ASE 42 contrôlent et mettent à jour les pointeurs, de la manière suivante. Tout d'abord, tous les ASE lisent simultanément tous les pointeurs de lecture et d'écriture dans leurs parties de mémorisation associées. Les ASE stockent intérieurement ces pointeurs. En deuxième lieu, chaque ASE utilise les pointeurs pour établir l'adresse suivante de lecture ou d'écriture pour les cellules qu'il est en train de traiter. Lorsque les transferts de cellules sont achevés pour une phase particulière d'écriture ou un cycle particulier

d'écriture (cycle de bus), l'ASE écrit la nouvelle valeur de chaque pointeur dans la partie de mémorisation appropriée. Ceci assure le maintien de l'intégrité des pointeurs.

L'unité de commande 30 contrôle les niveaux des files d'attente en lisant les valeurs des pointeurs mémorisées dans chaque ASE. L'unité de commande calcule ensuite les performances de l'appareil de commutation et détermine les sélections (optimales) des paires partie SPM-partie de mémorisation destinées à être utilisées dans la phase de lecture et il envoie une information de commande appropriée aux ASE afin de provoquer les sélections de paires voulues.

5

10

15

20

25

30

35

Bien que ceci ne soit pas montré sur les figures 10 et 11, il serait possible de subdiviser chaque région de stockage en files d'attente distinctes sur la base de priorités de trafic, où par exemple les services à débits binaires constants (CBR) auraient une file d'attente à priorité maximale, les services à débits binaires variables (VBR) auraient la file d'attente de la deuxième priorité maximale et les services à débits binaires disponibles (ABR) auraient la file d'attente de priorité minimale. Une telle subdivision n'est toutefois pas nécessaire ; une approche plus efficace consiste à faire que l'unit SPC 40 de chaque partie SPM programme le trafic pour l'ASE 42 de la partie SPM considérée sur la base des priorités de trafic, l'ASE manipulant ensuite le trafic sur une base FIFO en liaison avec son port particulier.

Selon un exemple, chaque partie de mémorisation 24 possède 2<sup>20</sup> emplacements de stockage (c'est-à-dire que le bus d'adressage de chaque ligne de bus B a une largeur de 20 bits), et chaque emplacement de stockage possède 32 bits de données (c'est-à-dire que le bus de données de chaque ligne de bus B a une largeur de 32 bits). Ainsi, chaque partie de mémorisation 24 pourrait être mise en oeuvre dans ce cas au moyen d'une mémoire vive (RAM) de 4 Mo, qui pourrait être une mémoire statique ou une mémoire dynamique. S'il y a huit régions de stockage R<sub>0</sub> à R<sub>7</sub> dans la partie de mémorisation, alors, puisque chaque cellule ATM a une longueur de 53 octets, chaque région de stockage R<sub>0</sub> à R7 peut stocker jusqu'à 9 892 cellules ATM. La capacité de stockage totale d'un appareil de commutation ayant huit unités de commutation, comportant chacune une partie de mémorisation de 4 Mo, est de 8 x 8 x 9 892 = 633 088 cellules. On comparera cette valeur, par simple curiosité, avec la capacité de stockage, valant seulement 19 200 cellules, d'une matrice de commutation du type 32 x 32, construite à partir d'éléments d'auto-acheminement (SRE), comme représenté sur la figure 1.

La figure 12 montre de manière plus détaillée une mise en oeuvre possible de chaque unité dispositif de multiplexage de bus 44 représentée sur la figure 7. Cette unité dispositif de multiplexage de bus doit répondre à des instructions provenant de l'ASE 42 avec lequel elle est connectée afin de donner accès aux parties de mémorisation servant à la lecture et à l'écriture de données de cellules. Typiquement, le nombre de lignes de bus sera un multiple de 4. Pour cette raison, la mise en oeuvre préférée de l'unité dispositif de multiplexage de bus 44 représentée sur la figure 11 est une unité dispositif de multiplexage de bus à extension quadruple. Cette unité 44 est conçue pour assurer l'acheminement par n'importe laquelle des quatre lignes de bus B<sub>0</sub> à B<sub>3</sub>, chaque ligne de bus comprenant des bus d'adresse A et de données D, jusqu'à un port P unique connecté avec l'ASE 42. L'unité 44 doit manipuler le transfert d'adresses dans une direction seulement (du port P à celui des bus B<sub>0</sub> à B<sub>3</sub> qui a été sélectionné), mais elle doit permettre un transfert bidirectionnel des données.

5

10

15

20

25

30

35

La ligne de bus B<sub>0</sub>, B<sub>1</sub>, B<sub>2</sub> ou B<sub>3</sub> qui sera utilisée pour le transfert de l'adresse et des données est sélectionnée par l'ASE 42, qui applique un signal de sélection de 2 bits aux entrées de sélection S<sub>1</sub> et S<sub>2</sub> de l'unité.

Si plus de quatre lignes de bus sont nécessaires, on peut alors disposer deux unités dispositif de multiplexage de bus 44, ou plus de deux semblables unités, parallèlement, comme représenté sur la figure 7. Chaque unité possède alors une entrée de validation E destinée à recevoir un signal de validation E utilisé pour sélectionner l'unité considérée.

Le port P de l'ASE de chaque unité dispositif de multiplexage de bus 44 est positionné sur l'état circuit ouvert lorsque l'unité n'est pas sélectionnée. Ceci assure que seule une unité dispositif de multiplexage de bus 44 peut appliquer des signaux de données à l'ASE à n'importe quel moment.

Bien que ceci ne soit pas représenté sur la figure 12, les signaux utilisés par l'ASE pour commander le transfert de données entre l'ASE et les parties de mémorisation (par exemple des signaux de lecture, d'écriture et de sélection de puce) transitent également par l'unité dispositif de multiplexage de bus.

La figure 13 représente un schéma fonctionnel des parties de l'ASE 42. L'ASE 42 comporte des tampons de cellules respectifs de réception 420 et d'émission 421, qui sont respectivement connectés à des ports de sortie et d'entrée du SPC 40 (figure 7). Chaque tampon 420 ou 421 est un dispositif FIFO possédant une capacité de stockage de plusieurs cellules ATM. Des données de cellules reçues venant du SPC 40 peuvent être délivrées sur un port de signaux de données

bidirectionnel de l'ASE, via une unité de sortie à trois états 422, à destination du dispositif de multiplexage de bus (ou de chaque dispositif de multiplexage de bus) 44. De même, les données reçues sur ce port de la part d'un dispositif 44 de multiplexage de bus peuvent arriver, via une unité d'entrée 423, au tampon de cellules d'émission 421 pour être délivrées au SPC 40.

5

10

15

20

25

30

35

L'ASE 42 comporte en outre une unité dispositif de séquencement de dispositif de multiplexage de bus et des registres associés de durée 425 et de séquencement de bus 426. Les registres 425 et 426 de durée et de séquencement de bus sont connectés à un circuit d'interface d'unité de commande 427 de façon que l'unité de commande puisse envoyer une information de commande (figure 8) à l'unité 424 dispositif de séquencement de dispositif de multiplexage de bus. Les données de positionnement temporel de cette information de commande sont stockées dans le registre de durée 425 et les données de séquencement relatives à l'unité de commutation (ASE) considérée sont stockées dans le registre de séquencement de bus 426. Deux registres de séquencement pourraient être prévus dans l'ASE au lieu d'un seul, afin de permettre à l'unité de commande de mettre à jour un registre pendant que l'autre registre est en train d'être utilisé par l'ASE au cours du cycle de lecture courant.

L'unité 424 dispositif de séquencement de dispositif de multiplexage de bus produit des signaux de sélection de bus appropriés qui sont appliqués au dispositif de multiplexage de bus 44 afin de sélectionner les bus voulus pour les transferts en mémoire et il effectue les opérations de lecture et d'écriture en utilisant la partie de mémorisation sélectionnée.

Une unité 428 de commande de mémoire produit les signaux appropriés d'écriture, de lecture et de sélection de puce permettant de commander la partie de mémorisation à laquelle il est fait accès.

Une unité 429 de commande multidestinataire est également prévue pour commander le fonctionnement de l'ASE 42 en réponse à la réception de donnée multidestinataire. Cette opération sera décrite ultérieurement en liaison avec la figure 14(A).

L'ASE 42 comporte en outre une unité 430 de stockage de pointeur qui est connectée au circuit 427 d'interface d'unité de commande qui est également connectée, via une unité 432 de calcul d'adresse/maintien de pointeur, au port de signaux de données de l'ASE. L'unité 432 de calcul d'adresse/maintien de pointeur produit également des signaux d'adresse A destinés à être appliqués à l'unité dispositif de multiplexage de bus, ou à chaque semblable unité, 44.

Lorsqu'une opération de lecture ou d'écriture doit être effectuée au moyen de l'ASE 42, l'ASE extrait de la partie de mémorisation devant être utilisée pour le transfert de données le pointeur de lecture ou d'écriture voulu qui est mémorisé dans la région PS de stockage de pointeurs (figure 10) de la partie de mémorisation considérée. Ce pointeur est stocké temporairement dans l'unité 430 de stockage de pointeur. L'unité 432 de calcul d'adresse/maintien de pointeur emploie alors le pointeur pour produire les signaux d'adresse nécessaires destinés à être appliqués à la partie de mémorisation en vue de la lecture ou de l'écriture des données de cellules. Après que l'opération a été complètement réalisée, le pointeur de lecture ou d'écriture considéré qui est maintenu dans l'unité 430 de stockage de pointeur est mis à jour par l'unité 432 de calcul d'adresse/maintien de pointeur, et le pointeur mis à jour est réécrit dans la région PS de stockage de pointeurs de la partie de mémorisation considérée.

5

10

15

20

25

30

35

Les figures 14(A) et 14(B) sont des organigrammes illustrant respectivement le fonctionnement de l'appareil de la figure 3 dans la phase d'écriture et dans la phase de lecture. Comme représenté sur la figure 14(A), dans la phase d'écriture, l'ASE 42 de chaque unité de commutation 20 sélectionne sa propre partie de mémorisation et effectue la sélection de bus voulue pour cette partie de mémorisation (étape S1). Ensuite, à l'étape S2, l'ASE lit le pointeur d'écriture considéré dans sa propre partie de mémorisation et le stocke temporairement dans l'unité 430 de stockage de pointeur. Ensuite, à l'étape S3, les données de cellules reçues de la part du SPC 40, qui sont, à ce moment là, stockées dans le tampon de cellules de réception 420, sont écrites dans la région de stockage appropriée se trouvant à l'intérieur de l'unité de commutation dans sa propre partie de mémorisation. L'étiquette d'acheminement affectée à chaque cellule par le SPC 40 pour indiquer le numéro du port de sortie de destination est enlevé par l'ASE 42 et seule la cellule ATM elle-même est stockée dans la partie de mémorisation. L'enlèvement de l'étiquette d'acheminement est possible puisque les données de cellules restent "stationnaires" dans l'appareil de commutation et, dans la phase de lecture, l'ASE qui lit sait que les données qu'il doit délivrer se trouveront toujours dans son emplacement de stockage correspondant à l'intérieur de la partie de mémorisation des autres unités de commutation. Ainsi, les signaux auxiliaires de transfert sont diminués et le rendement des bus est augmenté.

Une fois achevée l'opération d'écriture, à l'étape S4, le pointeur d'écriture est mis à jour et est réécrit dans la région de stockage de pointeur de

l'unité dans sa propre partie de mémorisation. Ensuite, à l'étape S5, l'ASE libère le bus et la phase d'écriture prend fin.

5

10

15

20

25

30

L'étape S3 ci-dessus mentionnée varie dans le cas où les données de cellules reçues sont des données multidestinataire, c'est-à-dire sont destinées à être envoyées à un certain nombre d'unités de commutation différentes. Dans ce cas, l'unité SPC 40 de l'unité de commutation réceptrice pourrait simplement reproduire à répétition les données de cellules pour chaque unité de commutation de sortie voulue et affecter une étiquette d'acheminement différente à chaque lot de données de cellules. Les mêmes données de cellules pourraient alors être écrites à leur tour par l'ASE dans chaque région de stockage concernée de la partie de mémorisation de l'unité de commutation. Selon une autre possibilité, l'unité SPC 40 pourrait appliquer une étiquette "indicatrice d'acheminement multidestinataire" aux données de cellules reçues et l'unité de commande multidestinataire 429 de l'ASE 42 pourra effectuer une écriture de données répétée dans les différentes régions de stockage. Toutefois, dans l'un et l'autre cas, l'ASE doit occuper la partie de mémorisation de sa propre unité de commutation pendant une période égale au produit du temps nécessaire pour écrire les données de cellules multidestinataire tout entières une seule fois dans le bloc de mémoire, par nombre d'unités de commutation de sortie multidestinataire.

Pour réduire le temps d'occupation de la partie de mémorisation dans le cas d'opérations multidestinataire, dans un mode de réalisation préféré de la présente invention, l'unité de commande multidestinataire 429 de l'ASE 42 répond à l'étiquette indicatrice de données multidestinataire en écrivant les données multidestinataire dans une seule région de stockage "primaire", qui est la région de stockage (de sa propre partie de mémorisation) qui correspond à simplement une seule des unités de commutation de sortie multidestinataire, et, dans les régions de stockage correspondant respectivement aux unités de commutation de sortie multidestinataire restantes, de simples pointeurs d'adresse d'écriture indiquant l'emplacement de la région de stockage primaire des données multidestinataire. Il serait également possible de prévoire une région de stockage multidestinataire spéciale à l'intérieur de chaque partie de mémorisation pour y stocker des données multidestinataires.

La figure 14(B) illustre le fonctionnement de l'appareil de commutation de la figure 3 dans la phase de lecture.

Au début de la phase de lecture, l'unité de commande 31 envoie aux ASE 42 des différentes unités de commutation les données nécessaires de positionnement temporel et de séquencement pour chaque cycle de la phase de lecture.

Par conséquent, au début d'un cycle de lecture, à l'étape S10, l'ASE 42 de chaque unité de commutation sélectionne la partie de mémorisation d'une autre unité de commutation selon les données de séquencement maintenues dans son propre registre 426 de séquencement de bus se rapportant au cycle considéré. La sélection du bus voulu dans cette partie de mémorisation est effectuée.

5

10

15

20

25

30

35

Ensuite, à l'étape S11, l'ASE extrait de la région de stockage de pointeurs PS de la partie de mémorisation sélectionnée le pointeur de lecture se rapportant à la région de stockage de la partie de mémorisation sélectionnée qui correspond à l'unité de commutation de l'ASE.

A l'étape S12, l'ASE 42 lit ensuite les données de cellules dans la région de stockage considérée et transfère les données au tampon de cellules d'émission 421 à partir duquel elles doivent être délivrées à l'unité SPC 40.

A l'étape S13, le pointeur de lecture est mis à jour et réécrit dans la région de stockage de pointeur de la partie de mémorisation sélectionnée. A l'étape S14, l'ASE 42 libère le bus, et le cycle de lecture courant prend fin.

A l'étape S15, l'ASE 42 vérifie si tous les cycles de lecture prévus pour la phase de lecture courante ont été réalisés. Si ce n'est pas le cas, l'organigramme revient à l'étape S10 pour faire commencer le cycle de lecture suivant.

Sinon, s'il est déterminé, à l'étape S15, que la phase de lecture est achevée, alors, à l'étape S16, l'unité de commande 31 fixe les quantités de données des régions de stockage de toutes les parties de mémorisation et détermine si des paires différentes partie SPM-partie de mémorisation doivent être sélectionnées pour la phase de lecture suivante. Tout changement voulu de la sélection s'effectue à l'étape S17 par envoi de nouvelles informations de commande aux ASE 42. Il serait également possible que l'unité de commande modifie les sélections de paires pendant le cours d'une phase de lecture, si les conditions d'intensité du trafic demandaient une modification urgente de ces sélections.

La figure 15 représente un autre exemple d'appareil de commutation constituant un mode de réalisation de l'invention. Comme pour l'appareil de la figure 3, chaque unité de commutation 20 comporte une partie SPM 22 et une partie de mémorisation 24'. Dans ce cas, la partie de mémorisation 24' est une mémoire à port double, par exemple une mémoire vive statique à port double, telle que IDT 7026S/L 16K X 16, fabriquée par la société Integrated Device

Technologies, Inc. Chaque semblable partie de mémorisation à double port 24' possède un premier port P<sub>W</sub> qui est utilisé exclusivement pour l'écriture de données de cellules dans la partie de mémorisation et un deuxième port P<sub>R</sub> qui est utilisé exclusivement pour la lecture de données de cellules dans la partie de mémorisation. Le port d'écriture P<sub>W</sub> n'est connecté qu'à la partie SPM 22 de l'unité de commutation 20 dans laquelle la partie de mémorisation 24' est située. C'est parce que des données de cellules reçues sont toujours écrites dans la propre partie de mémorisation de l'unité de commutation. D'autre part, pour valider l'une quelconque des parties SPM à lire chaque partie de mémorisation 24', le port de lecture P<sub>R</sub> de chaque partie de mémorisation à double port 24' est connecté à une ligne différente parmi les lignes de bus B<sub>0</sub> à B<sub>2</sub>, et chacune des parties SPM 22 a accès à l'ensemble des trois lignes de bus.

10

15

20

25

Alors que les modes de réalisation qui ont été décrits ci-dessus sont destinés à être utilisés pour la commutation de données ATM, on aura compris qu'il est possible de produire un appareil de commutation destiné à être utilisé dans n'importe quelle application où des ports d'entrée et de sortie multiples sont nécessaires.

Il est possible, à l'unité de commutation, qui est utilisée afin de déterminer les sélections de paires partie SPM-partie de mémorisation, de tenir compte des priorités des cellules ainsi que de l'importance du trafic. De plus, l'unité de commande peut être mise en oeuvre sous la forme d'un réseau neural ou d'un autre système d'apprentissage, de sorte que l'unité de commande peut apprendre comment traiter différentes conditions d'intensité du trafic et appliquer le savoir qu'elle a accumulé lorsque des situations analogues se produisent à l'avenir.

Bien entendu, l'homme de l'art sera en mesure d'imaginer, à partir de l'appareil dont la description vient d'être donnée à titre simplement illustratif et nullement limitatif, diverses variantes et modifications ne sortant pas du cadre de l'invention.

## **REVENDICATIONS**

1. Appareil de commutation, caractérisé en ce qu'il comprend une pluralité d'unités de commutation (20<sub>0</sub> à 20<sub>2</sub>), qui comportent chacune un moyen de mémorisation (24<sub>0</sub> à 24<sub>2</sub>) ayant des régions de stockage qui correspondent respectivement aux autres unités de commutation de ladite pluralité, l'appareil ayant une phase d'écriture au cours de laquelle, lorsque des données sont reçues par une première des unités de commutation pour être délivrées par une deuxième des unités de commutation, la première unité de commutation stocke les données reçues dans la région de stockage de son moyen de mémorisation qui correspond à la deuxième unité de commutation, et ayant également une phase de lecture au cours de laquelle la deuxième unité de commutation extrait les données stockées de sa région de stockage correspondante du moyen de mémorisation de la première unité de commutation et délivre ces données.

5

10

15

20

25

30

- 2. Appareil selon la revendication 1, caractérisé en ce que, au cours de ladite phase d'écriture, les unités de commutation peuvent être activées simultanément, chacune d'elles stockant des données reçues, en vue de la délivrance par une autre des unités de commutation, dans la région de stockage de son moyen de mémorisation qui correspond à cette autre unité de commutation.

- 3. Appareil selon la revendication 1 ou 2, caractérisé en ce que, au cours de ladite phase de lecture, deux quelconques ou plus de deux des unités de commutation peuvent être activées simultanément pour extraire de leurs régions de stockage correspondantes respectives du moyen de mémorisation d'une autre unité de commutation les données qui y sont stockées.

- 4. Appareil selon la revendication 3, caractérisé en ce qu'il comporte en outre un moyen de commande (30) connecté à chacune des unités de commutation et ayant pour fonction de sélectionner plusieurs paires unité de commutation-moyen de mémorisation afin de les utiliser au cours de ladite phase de lecture, l'unité de commutation de chaque paire étant donc destinée à extraire les données stockées dans sa région de stockage correspondante du moyen de mémorisation de la paire considérée pendant la phase de lecture.

- 5. Appareil selon la revendication 4, caractérisé en ce que ladite phase de lecture comprend un certain nombre de cycles de lecture et en ce que le moyen de commande a pour fonction de sélectionner différentes paires unité de commutation-moyen de mémorisation lors de cycles de lecture différents de la même phase de lecture.

- 6. Appareil selon la revendication 4 ou 5, caractérisé en ce que ledit moyen de commande a pour fonction de sélectionner au moins une des paires unité de commutation-moyen de mémorisation pendant plus d'un cycle de lecture de la même phase de lecture.

- 7. Appareil selon l'une quelconque des revendications 3 à 6, caractérisé en ce que lesdites phases d'écriture et de lecture se présentent en alternance.

10

15

20

25

- 8. Appareil selon la revendication 5 ou 6, caractérisé en ce qu'il existe une phase d'écriture entre deux cycles de lecture de la même phase de lecture.

- 9. Appareil selon l'une quelconque des revendications 4 à 8, caractérisé en ce que ledit moyen de commande a pour fonction de sélectionner les paires unité de commutation-moyen de mémorisation en fonction des conditions d'intensité du trafic existant dans l'appareil.

- 10. Appareil selon la revendication 9, caractérisé en ce que ledit moyen de commande comporte un moyen de contrôle d'intensité de trafic ayant pour fonction de contrôler les quantités de données stockées dans chaque région de stockage des moyens de mémorisation des unités de commutation, le moyen de commande employant les quantités ainsi contrôlées lorsqu'il effectue la sélection des paires unité de commutation-moyen de mémorisation.

- 11. Appareil selon l'une quelconque des revendications 1 à 10, caractérisé en ce qu'il comprend en outre des moyens constituant des bus, qui connectent entre elles les unités de commutation, lesdits moyens bus comportant une pluralité d'unités de lignes de bus distinctes, le nombre des unités de lignes de bus étant le même que celui des unités de commutation, et chaque unité de commutation étant connectée à toutes les unités de lignes de bus, tandis que les moyens de mémorisation respectifs des unités de commutation ne sont connectés qu'à des unités respectives différentes parmi les unités de lignes de bus.

- 12. Appareil selon la revendication 11 prise en liaison avec l'une quelconque des revendications 4 à 10, caractérisé en ce que ledit moyen de commande a pour fonction de sélectionner les paires unité de commutation-moyen de mémorisation de façon que, lors de la phase de lecture, toutes les unités de commutation qui extraient des données stockées de manière simultanée dans leurs moyens de mémorisation appariés respectifs le fassent via des unités de lignes de bus différentes.

- 13. Appareil selon l'une quelconque des revendications 1 à 12, caractérisé en ce que ledit moyen de mémorisation de chaque unité de commutation est employé pour produire des blocs de mémorisation virtuels du type premier entré,

premier sorti qui correspondent respectivement auxdites régions de stockage, chaque bloc ayant des pointeurs d'écriture et de lecture respectifs, également mémorisés dans le moyen de mémorisation de l'unité de commutation considérée, qui sont destinés à être utilisés par les unités de commutation lors du stockage de données et de l'extraction de données dans la région de stockage correspondante.

14. Appareil selon l'une quelconque des revendications 1 à 13, caractérisé en ce que chaque unité de commutation possède un moyen de traitement multidestinataire ayant pour fonction, lorsque des données multidestinataire sont reçues par l'unité de commutation considérée en vue d'être délivrées par une pluralité d'autres unités de commutation désignées, de stocker les données multidestinataire reçues dans la région de stockage de son moyen de mémorisation qui correspond à seulement une première des unités de commutation ainsi désignée et de stocker dans les régions de stockage correspondant respectivement aux unités de commutation restantes un pointeur d'adresse multidestinataire qui indique l'emplacement des données multidestinataire dans la région de stockage correspondant à la première unité de commutation désignée.

15. Appareil selon l'une quelconque des revendications 1 à 14, caractérisé en ce que lesdits moyens de mémorisation possèdent chacun des ports d'écriture et de lecture respectifs et sont conçus de façon que des données puissent être écrites sur ledit port d'écriture en même temps que des données sont extraites sur ledit port de lecture;

le port de lecture du moyen de mémorisation de chaque unité de commutation étant connecté à toutes les autres unités de commutation, tandis que le port d'écriture du moyen de mémorisation de chaque unité de commutation n'est pas connecté à une quelconque autre unité de commutation, de sorte que, lors de ladite phase de lecture, les données reçues par chaque unité de commutation peuvent être stockées dans le moyen de mémorisation de l'unité considérée tandis que des données préalablement stockées sont extraites de ce moyen de mémorisation par une autre unité de commutation.

16. Appareil selon l'une quelconque des revendications 1 à 15, caractérisé en ce que chaque unité de commutation comporte une partie de commande de port de commutation, connectée à des ports d'entrée et de sortie respectifs de l'unité de commutation, et ayant pour fonction, lorsque des données sont reçues sur ledit port d'entrée, de produire une étiquette d'acheminement qui identifie la région de stockage du moyen de mémorisation de l'unité de commutation où les données reçues doivent être stockées.

17. Appareil selon la revendication 12, caractérisé en ce que chaque unité de commutation comporte un élément de commutation adaptatif connecté audit moyen de commande afin de recevoir de celui-ci une information de commande, identifiant les paires sélectionnées unité de commutation-moyen de mémorisation se rapportant à cette unité de commutation lors de ladite phase de lecture, et ayant pour fonction, selon cette information de commande, d'activer les unités de lignes de bus appropriées à leur tour pendant le déroulement de la phase de lecture afin de faciliter le transfert de données du moyen de mémorisation de l'unité de commutation de chaque paire sélectionnée pour l'unité de commutation considérée.

18. Appareil selon la revendication 17, caractérisé en ce que chaque unité de commutation comporte en outre un moyen dispositif de multiplexage de bus qui possède un premier port connecté audit élément de commutation adaptatif de l'unité considérée et une pluralité de ports supplémentaires connectés respectivement auxdites unités de lignes de bus, l'un quelconque de ces ports supplémentaires pouvant être désigné pour le transfert de signaux de données et de signaux d'adresse entre lui et le premier port par application, au moyen dispositif de multiplexage de bus, d'un signal de sélection produit par l'élément de commutation adaptatif de l'unité considérée.

19. Appareil selon l'une quelconque des revendications 1 à 18, caractérisé en ce que lesdites données sont des données de cellules d'un réseau à mode de transfert asynchrone.

2/11 **2736779**

FIG. 7

FIG. 9(A)

| Partie SPM | Partie de<br>mémorisation |

|------------|---------------------------|

| А          | W                         |

| В          | Х                         |

| С          | Y                         |

| D          | Z                         |

Tranches de temps

Paires sélectionnées partie SPM-partie de mémorisation

| T1    | T2    | T3    |

|-------|-------|-------|

| A - W | A - Y | A - Z |

| B - Y | B - Z | B - W |

| C - Z | C - W | C - Y |

| D - X | D - X | D - X |

FIG. 9(B)

Tranches de temps

| T1    | T2    | T3    |

|-------|-------|-------|

| A - Y | A - Y | A - Y |

| B - W | B - Z | B - W |

| C - Z | C - W | C - Z |

| D - X | D - X | D - X |

FIG. 9(C)

FIG. 13