(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第3684902号 (P3684902)

(45) 発行日 平成17年8月17日(2005.8.17)

(24) 登録日 平成17年6月10日 (2005.6.10)

(51) Int.C1.7

F I

GO6F 3/06

GO6F 3/06 3O1G GO6F 3/06 54O

請求項の数 12 (全 17 頁)

(21) 出願番号 特願平11-55079

(22) 出願日 平成11年3月3日(1999.3.3)

(65) 公開番号 特開2000-250713 (P2000-250713A)

(43) 公開日 平成12年9月14日 (2000. 9.14) 審査請求日 平成15年1月15日 (2003. 1.15) |(73)特許権者 000005108

株式会社日立製作所

東京都千代田区丸の内一丁目6番6号

||(74)代理人 100075096

弁理士 作田 康夫

(72) 発明者 藤本 和久

東京都国分寺市東恋ケ窪一丁目280番地 株式会社日立製作所中央研究

所内

審査官 木村 貴俊

最終頁に続く

#### (54) 【発明の名称】ディスクアレイ制御装置

### (57)【特許請求の範囲】

#### 【請求項1】

ホストコンピュータとのインターフェース部とを含むチャネルインタフェース部と、 ディスク装置とのインターフェース部を含むディスクインタフェース部と、

前記ディスク装置に格納するデータの一部を一時的に格納するキャッシュメモリ部と、

1 つの前記チャネルインターフェース部と1 つの前記キャッシュメモリ部との間を1対 1 に接続する第1のアクセスバスと、

<u>1 つの</u>前記ディスクインターフェース部と<u>1 つの</u>前記キャッシュメモリ部との間を<u>1 対</u> <u>1 に</u>接続する<u>第 2 の</u>アクセスパスと、

前記第1のアクセスバスのアクセス回数と前記第2のアクセスバスのアクセス回数の比 に基いて、前記<u>第1の</u>アクセスパス<u>の駆動周波数及び前記第2のアクセスバスの駆動周波</u> 数を制御する制御手段とを有することを特徴とするディスクアレイ制御装置。

### 【請求項2】

前記制御手段は、複数の前記第1のアクセスバスのアクセス回数と複数の前記第2のアクセスバスのアクセス回数の比に基いて、各第1のアクセスパスの駆動周波数及び各第2のアクセスバスの駆動周波数を制御することを特徴とする請求項1に記載のディスクアレイ制御装置。

### 【請求項3】

<u>前記制御手段は、前記第1のアクセスパスの駆動周波数及び前記第2のアクセスバスの</u> 駆動周波数を設定したテーブルを有し、前記第1のアクセスバスのアクセス回数と前記第

2 のアクセスバスのアクセス回数の比を計算し、前記第 1 のアクセスバスのアクセス回数と前記第 2 のアクセスバスのアクセス回数の比に応じた前記第 1 のアクセスパスの駆動周波数及び前記第 2 のアクセスバスの駆動周波数を前記テーブルから選択することを特徴とする請求項1

に記載のディスクアレイ制御装置。

#### 【請求項4】

前記チャネルインターフェース部<u>は、前記第1のアクセスバスに対し、前記制御手段で</u> 制御された前記第1のアクセスパスの駆動周波数で、データを送出し、

前記ディスクインターフェース部は、前記<u>第2の</u>アクセスパスに対し、<u>前記制御手段で</u>制御された前記2のアクセスパスの</u>駆動周波数で、データを送出することを特徴とする請求項1に記載のディスクアレイ制御装置。

#### 【請求項5】

前記キャッシュメモリ部は、前記<u>第1の</u>アクセスパスに対し、前記制御手段で<u>制御され</u>た前記第1のアクセスパスの駆動周波数で、データを送出し、

前記キャッシュメモリ部は、前記第2のアクセスパスに対し、前記制御手段で制御された前記第2のアクセスパスの駆動周波数で、データを送出することを特徴とする請求項<u>1</u>に記載のディスクアレイ制御装置。

### 【請求項6】

ホストコンピュータとのインターフェース部とを含むチャネルインタフェース部と、 ディスク装置とのインターフェース部を含むディスクインタフェース部と、

前記ディスク装置に格納するデータの一部を一時的に格納するキャッシュメモリ部と、

1 つの前記チャネルインターフェース部と 1 つの前記キャッシュメモリ部との間を 1 対 1 に接続する第 1 のアクセスパスと、

1 つの前記ディスクインターフェース部と 1 つの前記キャッシュメモリ部との間を 1 対 1 に接続する第 2 のアクセスパスと、

前記第1のアクセスバスのアクセス回数と前記第2のアクセスバスのアクセス回数の比に基いて、前記第1のアクセスパスの駆動周波数及び前記第2のアクセスバスの駆動周波数を制御する制御手段とを有し、

前記第1のアクセスパスの駆動周波数と前記第2のアクセスパスの駆動周波数とが異なることを特徴とするディスクアレイ制御装置。

### 【請求項7】

前記第2のアクセスパスの駆動周波数は、前記第1のアクセスパスの駆動周波数よりも高いことを特徴とする請求項6に記載のディスクアレイ制御装置。

# 【請求項8】

ホストコンピュータとのインターフェース部とを含むチャネルインタフェース部と、 ディスク装置とのインターフェース部を含むディスクインタフェース部と、

前記ディスク装置に格納するデータの一部を一時的に格納するキャッシュメモリ部と、 前記チャネルインタフェース部及び前記ディスクインタフェース部と前記キャッシュメ モリ部との間の接続を切り替えるセレクタ部と、

1 つの前記チャネルインターフェース部と 1 つの前記セレクタ部との間を 1 対 1 に接続 40 する第 1 のアクセスパスと、

1 つの前記ディスクインターフェース部と1 つの前記セレクタ部との間を1対1に接続する第2のアクセスパスと、

1つの前記セレクタ部と1つの前記キャッシュメモリ部とを接続する第3のアクセスパスと、

前記第1のアクセスバスのアクセス回数と前記第2のアクセスバスのアクセス回数の比に基いて、前記第1のアクセスパスの駆動周波数及び前記第2のアクセスパスの駆動周波数を制御する制御手段とを有することを特徴とするディスクアレイ制御装置。

### 【請求項9】

前記キャッシュメモリ部は、複数の前記第3のアクセスバスのアクセス回数の比に基い

20

10

30

て、各第3のアクセスバスの動作周波数を制御する他の制御手段を有することを特徴とする請求項8に記載のディスクアレイ制御装置。

### 【請求項10】

前記チャネルインターフェース部は、前記第1のアクセスバスに対し、前記制御手段で 制御された前記第1のアクセスパスの駆動周波数で、データを送出し、

前記ディスクインターフェース部は、前記第2のアクセスパスに対し、前記制御手段で 制御された前記第2のアクセスバスの駆動周波数で、データを送出し、

前記セレクタ部は、各第3のアクセスパスに対し、前記キャッシュメモリ部の前記他の 制御手段で制御された各第3のアクセスバスの駆動周波数で、データを送出することを特 徴とする請求項9に記載のディスクアレイ制御装置。

#### 【請求項11】

前記キャッシュメモリ部は、各第3のアクセスパスに対し、前記キャッシュメモリ部の前記他の制御手段で制御された各第3のアクセスバスの駆動周波数で、データを送出することを特徴とする請求項9又は10に記載のディスクアレイ制御装置。

### 【請求項12】

前記セレクタ部は、前記第1のアクセスパスに対し、前記制御手段で制御された前記第 1のアクセスバスの駆動周波数で、データを送出し、

前記セレクタ部は、前記第2のアクセスパスに対し、前記制御手段で制御された前記第2のアクセスバスの駆動周波数で、データを送出することを特徴とする請求項8~11の何れかに記載のディスクアレイ制御装置。

### 【発明の詳細な説明】

### [0001]

### 【発明の属する技術分野】

本発明は、データを分割して複数の磁気ディスク装置に格納するディスクアレイ装置の制御装置に関する。

#### [0002]

### 【従来の技術】

コンピュータの主記憶の I / O性能に比べて、 2 次記憶装置として用いられる磁気ディスク装置を使ったサブシステムの I / O性能は 3 ~ 4 桁程度小さく、従来からこの差を縮めること、すなわちサブシステムの I / O性能を向上する努力が各所でなされている。サブシステムの I / O性能を向上させるための 1 つの方法として、複数の磁気ディスク装置でサブシステムを構成し、データを分割して複数の磁気ディスク装置に格納する手段、いわゆるディスクアレイと呼ばれるシステムが知られている。

### [0003]

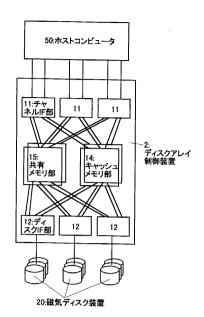

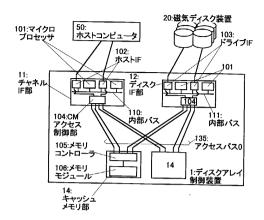

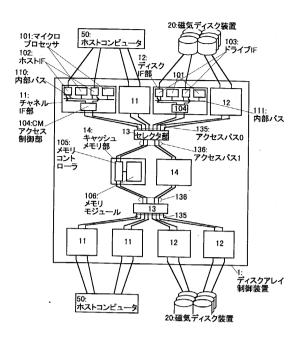

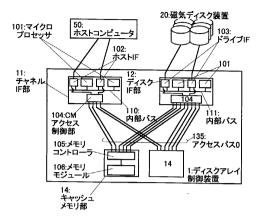

例えば、従来技術では、図2に示すようにホストコンピュータ50とディスクアレイ制御装置2間のデータ転送を実行する複数のチャネルIF部11と、磁気ディスク装置20とディスクアレイ制御装置2間のデータ転送を実行する複数のディスクIF部12と、磁気ディスク装置20のデータを一時的に格納するキャッシュメモリ部14と、磁気ディスク装置20のデータ及びディスクアレイ制御装置2に関する制御情報を格納する共有メモリ部15を備え、キャッシュメモリ部14および共有メモリ部15は全チャネルIF部11及びディスクIF部12からアクセス可能な構成となっている。この従来技術では、チャネルIF部11及びディスクIF部12と共有メモリ部15、またチャネルIF部11及びディスクIF部12とキャッシュメモリ部14間は1:1に接続されている。

### [0004]

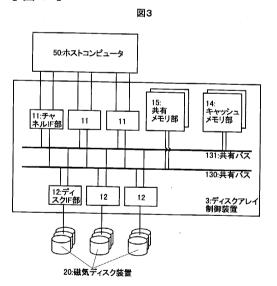

また、他の従来技術では、図3に示すようにホストコンピュータ50とディスクアレイ制御装置3間のデータ転送を実行する複数のチャネルIF部11と、磁気ディスク装置20とディスクアレイ制御装置3間のデータ転送を実行する複数のディスクIF部12と、磁気ディスク装置20のデータを一時的に格納するキャッシュメモリ部14と、磁気ディスク装置20のデータ及びディスクアレイ制御装置3に関する制御情報を格納する共有メモリ部15を備え、各チャネルIF部11及びディスクIF部12と共有メモリ部15間は

10

20

30

40

共有バス 1 3 0 で接続され、各チャネルIF 1 1 部及びディスクIF部 1 2 とキャッシュ メモリ部 1 4 間は共有バス 1 3 1 により接続されている。

#### [0005]

### 【発明が解決しようとする課題】

ディスクアレイシステムに対する高性能化要求に対して、これまでは、ディスクアレイ制御装置の大規模化や構成要素の高速化、例えばチャネルIF部内のプロセッサ数やキャッシュメモリ容量の増大、高性能プロセッサの適用、内部バス幅の拡大やバス転送能力の向上などで対応してきた。しかしながら、図3に示した従来技術では、内部バスの転送能力がシステムの大規模化および性能向上に追従するのが困難になりつつある。

#### [0006]

そこで内部バス性能を向上させて高いメモリアクセス性能を得るために、図2に示した従来技術のように、チャネルIF部及びディスクIF部と共有メモリ及びキャッシュメモリ間を1:1に接続する方法が考えられる。この方法によれば、メモリに接続したアクセスパス数に比例して内部バス性能が増加する。しかしながら、搭載するプロセッサ数の増大に比例して、共有メモリおよびキャッシュメモリへのアクセス要求も増加する。そのため、内部バス性能を最大限に引き出すために、各チャネルIF部、ディスクIF部・共有メモリ、キャッシュメモリ間のアクセスを効率的に制御する必要がある。

### [0007]

本発明の目的は上述の課題を解消し、チャネルIF部、ディスクIF部 - キャッシュメモリ間のアクセスパスを効率的に使用し、キャッシュメモリへのデータ転送スループットの高いディスクアレイ制御装置を提供することにある。

### [ 8000 ]

### 【課題を解決するための手段】

上記目的は、ホストコンピュータとのインターフェース部とを含むチャネルインタフェース部と、ディスク装置とのインターフェース部を含むディスクインタフェース部と、<u>前</u>記ディスク装置に格納するデータの一部を一時的に格納するキャッシュメモリ部と、<u>1つ</u>の前記チャネルインターフェース部と1つの前記キャッシュメモリ部との間を1対1に接続する第1のアクセスバスと、1つの前記ディスクインターフェース部と1つの前記キャッシュメモリ部との間を1対1に接続する第2のアクセスパスと、<u>前記第1のアクセスバスのアクセスに</u>ないた。前記第1のアクセスバスのアクセス回数の比に基いて、前記第1のアクセスパスの駆動周波数及び前記第2のアクセスバスの駆動周波数を制御する制御手段とを有することを特徴とするディスクアレイ制御装置により達成される。

#### [0020]

また、上記目的は、ホストコンピュータとのインターフェース部とを含むチャネルインタフェース部と、ディスク装置とのインターフェース部を含むディスクインタフェース部と、前記ディスク装置に格納するデータの一部を一時的に格納するキャッシュメモリ部と、前記チャネルインタフェース部及び前記ディスクインタフェース部と前記キャッシュメモリ部との間の接続を切り替えるセレクタ部と、1つの前記チャネルインターフェース部と1つの前記セレクタ部との間を1対1に接続する第1のアクセスパスと、1つの前記セレクタ部との間を1対1に接続する第2のアクセスパスと、1つの前記セレクタ部と1つの前記キャッシュメモリ部とを接続する第3のアクセスパスと、前記第1のアクセスバスのアクセス回数と前記第2のアクセスバスのアクセス回数の比に基いて、前記第1のアクセスパスの駆動周波数及び前記第2のアクセスパスの駆動周波数を制御する制御手段とを有することを特徴とするディスクアレイ制御装置によっても達成される。

## [0026]

### 【発明の実施の形態】

以下、本発明の実施例を、図面を用いて説明する。

### [0027]

### (実施例1)

10

20

30

30

40

50

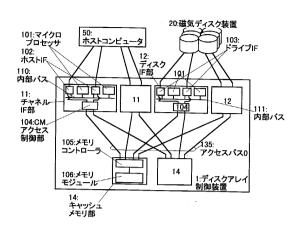

図1に、本発明の一実施例を示す。

### [0028]

ディスクアレイ制御装置 1 は、ホストコンピュータ 5 0 との 2 つのインターフェース部(チャネル I F 部) 1 1、磁気ディスク装置 2 0 との 2 つのインターフェース部(ディスク I F 部) 1 2、 2 つのキャッシュメモリ部 1 4 と、 8 本のアクセスパス 0 : 1 3 5 とを有する。

#### [0029]

チャネルIF部11は、ホストコンピュータ50との2つのIF(ホストIF)102、2つのマイクロプロセッサ101、キャッシュメモリ部14への1つのアクセス制御部(СMアクセス制御部)104を有し、ホストコンピュータ50とキャッシュメモリ部14間のデータ転送を実行する。マイクロプロセッサ101及びホストIF102は内部バス110によって接続され、СMアクセス制御部104は2つのホストIF102へ直接接続されている。

### [0030]

ディスクIF部12は、磁気ディスク装置20との2つのIF(ドライブIF)103、 2つのマイクロプロセッサ101、キャッシュメモリ部14への1つのアクセス制御部( CMアクセス制御部)104を有し、磁気ディスク装置20とキャッシュメモリ部14間 のデータ転送を実行する。マイクロプロセッサ101及びドライブIF103は内部バス 111によって接続され、CMアクセス制御部104は2つのドライブIF102へ直接 接続されている。

#### [0031]

キャッシュメモリ部14は、メモリコントローラ105とメモリモジュール106を有し、磁気ディスク装置20へ記録するデータや、そのデータ及びシステム内の管理情報等を格納する。

### [0032]

1 つのチャネルIF部11と1つのキャッシュメモリ部14間、及び1つのディスクIF部12と1つのキャッシュメモリ部14間は1本のアクセスパス0:135で接続する。ここで、各アクセスパス0:135の幅は同じである。また、上記個数は一実施例に過ぎず、個数を上記に限定するものではない。

### [0033]

### [0034]

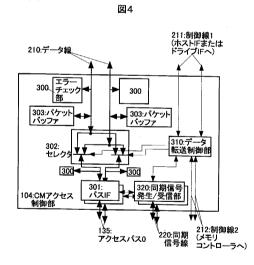

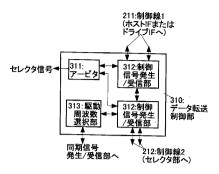

図6は、CMアクセス制御部104内のデータ転送制御部310内の構成を示している。 データ転送制御部310は、アービタ311、2つの制御信号発生/受信部312、駆動 周波数選択部313を有する。1つの制御信号発生/受信部312は、制御線1:211 により、ホストIF102またはドライブIF103と接続され、アービトレーションに

データと並送されてきた同期信号を使用してデータを取り込む。

20

30

40

50

必要な情報をアービタ3 1 1 に送る。アービタ3 1 1 は、アービトレーションを行い、セレクタ切り替え信号をセレクタ3 0 2 へ送出する。もう 1 つの制御信号発生 / 受信部 3 1 2 は、制御線2:2 1 2 により、メモリコントローラ1 0 5 と接続される。また、アービタ3 1 1 からセレクタ切り替え完了の信号を受け、制御線2:2 1 2 によってアクセス開始信号を送出する。さらに、制御線2:2 1 2 によって、メモリコントローラ1 0 5 から送られてきたアクセスパス0:1 3 5 の駆動周波数変更を指示する信号を駆動周波数選択部3 1 3 へ送出する。駆動周波数選択部3 1 3 は、同期信号発生 / 受信部3 2 0 が設定可能な駆動周波数のテーブルを持っており、駆動周波数変更を指示する信号によりテーブルから駆動周波数の値を選択し、その値を同期信号発生 / 受信部3 2 0 へ送る。

#### [0035]

図5は、キャッシュメモリ部14内の構成を示している。キャッシュメモリ部14は、メモリコントローラ105とメモリモジュール106を有する。メモリコントローラ105は、チャネルIF部11及びディスクIF部12に繋がるアクセスパス0:135との4つのパスIF301、セレクタ304、アドレス、コマンド、データを一時格納するパケットバッファ303、データのエラーチェック部300、メモリモジュール106へのアクセスを制御するメモリ制御部307、CMアクセス制御部104から送出されたアレス及びコマンドを解析するアドレス・コマンド(adr、cmd)解析部305、データ転送制御部315、データ転送時にデータと並送する同期信号の発生/受信部320をデータ転送制御部310に接続される。また、データ転送制御部315は、セレクタ304の切り替えを行う。また、同期信号発生/受信部320は、同期信号線220でCMアクセス制御部104内の同期信号発生/受信部320に接続される。データの送信時には、データを設制御部315から指示された駆動周波数で、パスIF301と同期してデータ転送同期信号を並送する。またデータの受信時には、データと並送されてきた同期信号を使用してデータを取り込む。

### [0036]

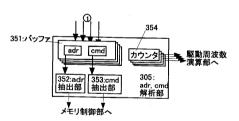

図8は、メモリコントローラ105内のアドレス(adr)、コマンド(cmd)解析部305の構成を示している。adr、cmd解析部305は、バッファ351、アドレス(adr)抽出部352、コマンド(cmd)抽出部353、カウンタ354を有する。adr、cmd解析部305では、メモリコントローラ105に接続される4本のアクセスパス0:135それぞれに1つずつ割り当てられたバッファ351に、アドレス、コマンドを格納する。adr抽出部352及びcmd抽出部353では、アクセスするメモリのアドレスとアクセスの種類を割り出し、メモリ制御部307へ送出する。また、バッファ351にアドレス及びコマンドを格納する毎に、バッファ毎に割り当てたカウンタをカウントアップする。

### [0037]

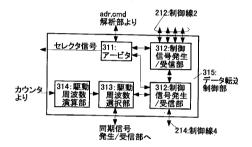

図7は、メモリコントローラ105のデータ転送制御部315内の構成を示している。データ転送制御部315は、アービタ311、2つの制御信号発生/受信部312、駆動周波数選択部313を有する。1つの制御信号発生/受信部312は、制御線2:212により、CMアクセス制御部104内のデータ転送制御部310と接続され、CMアクセス制御部104からのアクセス要求をアービタ311に伝える。アービタ311は、アービトレーションを行い、セレクタ切り替え信号をセレクタ304へ送出する。もう1つの制御信号発生/受信部312は、制御線4:214により、よモリ制御部307と接続され、アービタ311からセレクタ切り替え完了の信号を受けけ、即制御部307と接続され、アービタ311からセレクタ切り替え完了の信号を受けけ、駆動周波数演算部314は、adr、cmd解析部305内のカウンタのカウント数を読み出し、4本のアクセスパス0:135のアクセス回数の比を計算し、駆動周波数選択部313は、同期信号発生/受信部320が設置可能な数のように各アクセスパスの駆動周波数を選択し、その駆動周波数のテーブルを持っており、そのテーブルを参照して各アクセスパスの駆動周波数を選択し、その駆動周

30

40

50

波数の値を同期信号発生/受信部320へ送る。また駆動周波数選択部313は、制御信号発生/受信部312、制御線2:212を介して、アクセスパス0:135の駆動周波数変更を指示する信号をデータ転送制御部310内の駆動周波数選択部313へ送出する

[0038]

チャネルIF部11からキャッシュメモリ部14へのアクセス回数及びディスクIF部12からキャッシュメモリ部14へのアクセス回数は、ホストコンピュータからのアクセスの種類によって変化する。このため、アクセス回数の多いアクセスパスのスループットは下がり、それがネックとなって装置全体のスループットが制限される。上記のようにアクセス回数の比をもとにアクセスパス0:135毎にデータ転送速度を変えることにより、アクセス回数の多いアクセスパスのスループットが高まる。これにより、アクセス回数の多いアクセスパスのスループットが高まる。これにより、アクセス回数の多いアクセスパスのスループットのネックが解消され、装置全体のスループットの向上が可能となる。

[0039]

また、アクセスパスの物理的な駆動周波数は固定しておき、データ転送制御部315のアービタ311において、アクセス回数の多い順にアクセスパスに優先度を設定してアービトレーションを行うことにより、アクセス回数の多いアクセスパスの実効的なデータ転送速度を上げることが可能となる。これによっても、アクセス回数の多いアクセスパスのスループットを高めることができ、装置全体のスループットの向上が可能となる。

[0040]

通常アクセス回数の差は、チャネルIF部11とキャッシュメモリ部14間のアクセスパスと、ディスクIF部12とキャッシュメモリ部14間のアクセスパスの間で生じる。したがって、チャネルIF部11とキャッシュメモリ部14間のアクセスパスと、ディスクIF部12とキャッシュメモリ部14間のアクセスパスの間で、データ転送速度を等しくしたり、異ならせたりすることにより、アクセスパス毎にデータ転送速度を制御する場合に比べて、データ転送速度の制御が容易になる。

[0041]

本実施例では、チャネルIF部11あるいはディスクIF部12に繋がるアクセスパス0:135とのパスIF301の数を4つとした。上記個数は一実施例に過ぎず、個数を上記に限定するものではない。

[0042]

次に、キャッシュメモリ部 1 4 へのアクセス時の手順について述べる。キャッシュメモリ部 1 4 ヘアクセスする場合、マイクロプロセッサ 1 0 1 は、ホストIF 1 0 2 あるいはドライブIF 1 0 3 へ、キャッシュメモリ部 1 4 へのアクセス開始を指示する。

[0043]

アクセス開始の指示を受けたホストIF102あるいはドライブIF103は、制御線1:211によりCMアクセス制御部104内のデータ転送制御部310ヘアクセス開始を示す信号と、アクセス先のメモリコントローラ105を示す信号を送出する。それとともに、データ線210を通してアドレス、コマンド、データ(データの書き込み時のみ)を送出する。

[0044]

CMアクセス制御部104は、データ線210を通して送られてきたアドレス、コマンド、データ(データの書き込み時のみ)をパケットバッファ303に格納する。データ転送制御部310はアービトレーションを行ってパスIF301の使用権を決定し、セレクタ302を切り替えるとともに、制御線2:212によってメモリコントローラ105内のデータ転送制御部315へアクセス開始を示す信号と、アクセス先のメモリコントローラ105を示す信号を出す。

[0045]

メモリコントローラ 1 0 5 内のデータ転送制御部 3 1 5 は、制御線 2 : 2 1 2 によってアクセス開始の信号と、アクセス先のメモリコントローラ 1 0 5 を示す信号を受けると、 C

30

40

50

Mアクセス制御部104へ、制御線2:212によってアクセス承認を返す。

[0046]

C M ア ク セ ス 制 御 部 1 0 4 は ア ク セ ス 承 認 を 受 け る と 、 パ ケ ッ ト バ ッ フ ァ 3 0 3 か ら ア ド レ ス 、 コ マ ン ド 、 デ ー タ ( デ ー タ の 書 き 込 み 時 の み ) を 読 み 出 し 、 セ レ ク タ 3 0 2 、 パ ス I F 3 0 1 を 介 し て ア ク セ ス パ ス 0 : 1 3 5 へ 送 出 す る 。

[0047]

メモリコントローラ 1 0 5 は、アクセスパス 0 : 1 3 5 を通して送られてきたアドレス、コマンド、データ(データの書き込み時のみ)をパケットバッファ 3 0 3 に格納する。また、送られてきたアドレス、コマンドは、アドレス(adr)、コマンド(cmd)解析部 3 0 5 へ取り込み、解析の結果得られたメモリの制御情報をメモリ制御部 3 0 7 へ送出する。また、アクセス先メモリコントローラ 1 0 5 を調べ、自メモリコントローラと異なる場合はエラーとみなし障害処理を行う。

[0048]

メモリコントローラ 1 0 5 内のデータ転送制御部 3 1 5 は、アービトレーションを行って メモリアクセス権を決定し、セレクタ 3 0 4 を切り替える。

[0049]

データの書き込み時は、パケットバッファ 3 0 3 からデータを読み出し、セレクタ 3 0 4 を介してメモリモジュール 1 0 6 へ書き込む。データの読み出し時は、メモリモジュール 1 0 6 からデータを読み出し、セレクタ 3 0 4、パスIF 3 0 1を介してアクセスパス 0 : 1 3 5 へ送出する。

[0050]

メモリモジュール 1 0 6 へのアクセスが終了すると、データ転送制御部 3 1 5 においてアクセス状況を示すステータスを生成し、CMアクセス制御部 1 0 4 を経由して、ホストIF 1 0 2 またはドライブ IF 1 0 3 へ送出する。

[0051]

また図10に示すように、 1つのCMアクセス制御部104からキャッシュメモリ部1 4 へ接続されるアクセスパス0:135の本数が多いディスクアレイ制御装置1において も、本実施例を実施する上で問題はない。ホストIF及びドライブIFとして、今後はファイバーチャネル等のスループットが100MB/s以上の高速IFが使用されることが 多くなると考えられる。アクセスパス0:135のスループットは、ホストIF及びドライブIFのスループットと同等にする必要がある。このため上記のように高速IFを使用する場合、1つのCMアクセス制御部104からキャッシュメモリ部14へ接続されるアクセスパス0:135の本数が多い図10の構成が有効となる。

[0052]

(実施例2)

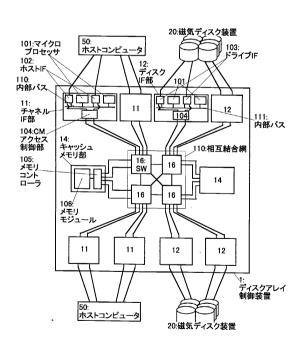

図11に、本発明の他の実施例を示す。

[0053]

ディスクアレイ制御装置1は、チャネルIF部11、ディスクIF部12、セレクタ部13、キャッシュメモリ部14と、アクセスパス0:135、アクセスパス1:136を有する。

[0054]

チャネルIF部11、ディスクIF部12、及びキャッシュメモリ部14は、図1に示す 実施例1の構成と同様である。

[0055]

セレクタ部 1 3 には、 2 つのチャネル I F 部 1 1 、 2 つのディスク I F 部 1 2 からそれぞれ 2 本ずつ、計 8 本のアクセスパス 0 : 1 3 5 が接続される。また、セレクタ部 1 3 には、 2 つのキャッシュメモリ部 1 4 へのアクセスパス 1 : 1 3 6 が 2 本ずつ、計 4 本接続される。

[0056]

アクセスパス0:135とアクセスパス1:136の間には上記のようなパス数の関係が

30

40

50

あるため、セレクタ部13ではチャネルIF部11及びディスクIF部12からの8本のアクセスパス0:135からの要求の内、キャッシュメモリ部14へのアクセスパス1: 136の数に相当する4個だけを選択して実行する機能を持つ。

#### [0057]

ここで、上記個数は一実施例に過ぎず、個数を上記に限定するものではない。 1 つのセレクタ部 1 3 からキャッシュメモリ部 1 4 へ接続されるアクセスパスの数を、チャネルIF部 1 1 及びディスクIF部 1 2 から 1 つのセレクタ部 1 3 に接続されるアクセスパスの数より少なくし、チャネルIF部 1 1 とディスクIF部 1 2 の合計数よりもセレクタ部 1 3 の数が少なくなるように上記個数を設定すると、キャッシュメモリ部 1 4 のLSIピンネック及びパッケージのコネクタネックという問題が生じた場合、上記のようにすることで、LSIのピンネック及びパッケージのコネクタネックを解消することができる。

#### [0058]

CMアクセス制御部104は、図4に示す構成と同様であるが、制御線2:212は、セレクタ部13内のデータ転送制御部315に接続される。

#### [0059]

図9は、セレクタ部13内の構成を示している。セレクタ部13は、チャネルIF部11 及びディスクIF部12に繋がるアクセスパス0:135との8つのパスIF301、メ モリコントローラ 1 0 5 に繋がるアクセスパス 1 : 1 3 6 との 4 つのパス I F 3 0 1、両 者間を互いに接続するセレクタ306、パケットバッファ303、データのエラーチェッ ク部300、CMアクセス制御部104から送出されたアドレス及びコマンドを解析する アドレス ( a d r ) 、コマンド ( c m d ) 解析部 3 0 5 、データ転送制御部 3 1 5 、デー 夕転送時にデータと並送する同期信号の発生/受信部320を有する。データ転送制御部 3 1 5 は、制御線 2 : 2 1 2 で C M アクセス制御部 1 0 4 内のデータ転送制御部 3 1 0 に 接続され、制御線3:213でメモリコントローラ105内のデータ転送制御部315に 接続される。また、データ転送制御部315は、セレクタ306の切り替えを行う。パケ ットバッファ303は、アクセスパス0:135側のパスの駆動周波数とアクセスパス1 :136側の駆動周波数が異なる場合、周波数の差を吸収するために、転送するデータの 一部または全部をバッファリングする。アクセスパス0:135側の同期信号発生/受信 部 3 2 0 は、同期信号線 2 2 0 で C M アクセス制御部 1 0 4 内の同期信号発生 / 受信部 3 20に接続され、アクセスパス1:136側の同期信号発生/受信部320は、同期信号 線220でメモリコントローラ105内の同期信号発生/受信部320に接続される。デ ータの送信時には、データ転送制御部315から指示された駆動周波数で、パスIF30 1と同期してデータと同期信号を並送する。またデータの受信時には、データと並送され てきた同期信号を使用してデータを取り込む。

### [0060]

adr、cmd解析部305は、図8に示す構成と同様に、バッファ351、アドレス(adr)抽出部352、コマンド(cmd)抽出部353、カウンタ354を有する。adr、cmd解析部305では、メモリコントローラ105に接続される8本のアクセスパス0:135それぞれに1つずつ割り当てられたバッファ351に、アドレス、コマンドを格納する。adr抽出部352及びcmd抽出部353では、アクセスするメモリコントローラ105とアクセスの種類を割り出し、データ転送制御部315内のアービタ311へ送出する。また、バッファ351にアドレス及びコマンドを格納する毎に、バッファ毎に割り当てたカウンタをカウントアップする。

#### [0061]

データ転送制御部 3 1 5 は、図 7 に示す構成と同様に、アービタ 3 1 1、 2 つの制御信号発生 / 受信部 3 1 2、駆動周波数演算部 3 1 4、駆動周波数選択部 3 1 3 を有する。 1 つの制御信号発生 / 受信部 3 1 2 は、制御線 2 : 2 1 2 で C M アクセス制御部 1 0 4 内のデータ転送制御部 3 1 0 に接続される。また、 C M アクセス制御部 1 0 4 からのアクセス要求をアービタ 3 1 1 に伝える。アービタ 3 1 1 は、 a d r 、 c m d 解析部 3 0 5 からの情

30

40

50

報に基づいてアービトレーションを行い、セレクタ切り替え信号をセレクタ306へ送出 する。もう1つの制御信号発生/受信部312は、図7とは異なり、制御線3:213で メモリコントローラ105内のデータ転送制御部315に接続される。また、アービタ3 11からセレクタ切り替え完了の信号を受け、制御線3:213によってメモリコントロ ーラ105内のデータ転送制御部315にアクセス開始信号を送出する。駆動周波数演算 部 3 1 4 は、 a d r 、 c m d 解析部 3 0 5 内のカウンタのカウント数を読み出し、 8 本の アクセスパス0:135のアクセス回数の比を計算し、駆動周波数選択部313へ送る。 駆動周波数選択部313は、同期信号発生/受信部320が設定可能な駆動周波数のテー ブルを持っており、そのテーブルを参照して各アクセスパスの駆動周波数の比がアクセス 回数の比に近くなるように各アクセスパスの駆動周波数を選択し、その駆動周波数の値を アクセスパス0:135側の同期信号発生/受信部320へ送る。また駆動周波数選択部 3 1 3 は、アクセスパス 0 : 1 3 5 の制御信号発生 / 受信部 3 1 2 、制御線 2 : 2 1 2 を 介して、アクセスパス0:135の駆動周波数変更を指示する信号をデータ転送制御部3 10内の駆動周波数選択部313へ送出する。また、駆動周波数選択部313は、アクセ スパス 1 : 1 3 6 側の制御信号発生 / 受信部 3 1 2 を介してメモリコントローラ 1 0 5 か ら駆動周波数変更を示す信号を受け、設定可能な駆動周波数のテーブルから駆動周波数の 値を選択し、その値をアクセスパス1:136側の同期信号発生/受信部320へ送る。

[0062]

チャネルIF部11からキャッシュメモリ部14へのアクセス回数及びディスクIF部12からキャッシュメモリ部14へのアクセス回数は、ホストコンピュータからのアクセスの種類によって変化する。このため、アクセス回数の多いアクセスパスのスループットは下がり、それがネックとなって装置全体のスループットが制限される。上記のようにアクセス回数の比をもとにアクセスパス0:135毎にデータ転送速度を変えることにより、アクセス回数の多いアクセスパスのスループットが高まる。これにより、アクセス回数の多いアクセスパスのスループットが高まる。これにより、アクセス回数の多いアクセスパスのスループットのネックが解消され、装置全体のスループットの向上が可能となる。

[0063]

メモリコントローラ 1 0 5 は、図 5 に示す構成と同様で、その中のデータ転送制御部 3 1 5 は、図 7 に示す構成と同様で、実施例 1 と同様の処理を行う。

[0064]

セレクタ部13とキャッシュメモリ部14間の各アクセスパス1:136それぞれのアクセス回数が、各キャッシュメモリ部へのアクセスの偏りによって変化する場合、上記のようにアクセスパス1:136毎にデータ転送速度を可変にし、アクセス回数の多いアクセスパスのスループットを高めることによって、装置全体のスループットの向上が可能となる。図11に示すディスクアレイ制御装置1では、この制御を、上記のチャネルIF部11及びディスクIF部12とセレクタ部13間での制御と合わせて行うことにより、どちらか一方だけ制御を行う場合より、装置全体のスループットの向上が可能となる。

[0065]

また、アクセスパスの物理的な駆動周波数は固定しておき、データ転送制御部315のアービタ311において、アクセス回数の多い順にアクセスパスに優先度を設定してアービトレーションを行うことにより、アクセス回数の多いアクセスパスの実効的なデータ転送速度を上げることが可能となる。これによっても、アクセス回数の多いアクセスパスのスループットを高めることができ、装置全体のスループットの向上が可能となる。

[0066]

図12に示すように、チャネルIF部11及びディスクIF部12とキャッシュメモリ部14間をスイッチ(SW)16を用いた相互結合網110で接続するディスクアレイ制御装置1では、SW16内に図9に示すセレクタ部13内のデータ転送制御部315及び同期信号発生/受信部320の機能を持たせることにより、各アクセスパス毎に駆動周波数を可変にすることが可能となる。それによって、図12に示すディスクアレイ制御装置1においても、装置全体のデータ転送スループットを向上することが可能となる。

50

### [0067]

(実施例3)

実施例1または2において、ディスクIF部12とキャッシュメモリ部14間のデータ転送速度をチャネルIF部11とキャッシュメモリ部14間のデータ転送速度より大きくする。また、アクセスパスのデータ転送速度は可変とせずに、固定する。

[0068]

ディスクアレイ制御装置では、一般的にディスクIF部12からキャッシュメモリ部14へのアクセス回数は、チャネルIF部11からキャッシュメモリ部14へのアクセス回数以上となる。ディスクアレイではデータに冗長性を持たせるため、データの書き込み時にパリティを生成して、データとともに磁気ディスク装置に記録する。したがって、データの書き込み時には、ディスクIF部12とキャッシュメモリ部14間でパリティ生成のためのアクセスが発生する。これは、一般的にライトペナルティと呼ばれている。このため、ディスクIF部12からキャッシュメモリ部14へのアクセス回数は、チャネルIF部11からキャッシュメモリ部14へのアクセス回数以上となる。

[0069]

通常、ディスクIF部12とキャッシュメモリ部14間のアクセス回数とチャネルIF部11とキャッシュメモリ部14間のアクセス回数の比が最大で約3:1となるため、本実施例では、ディスクIF部12とキャッシュメモリ部14間のデータ転送速度がチャネルIF部11とキャッシュメモリ部14間のデータ転送速度の3倍になるように設定する。

[0070]

上記のように、アクセス回数の多いアクセスパスのデータ転送速度をアクセス回数の少ないアクセスパスのデータ転送速度より大きく設定しておくことにより、 アクセス回数の多いアクセスパスのスループットが装置全体のスループットを制限することがなくなり、 装置全体のスループットの向上が可能となる。

[0071]

(実施例4)

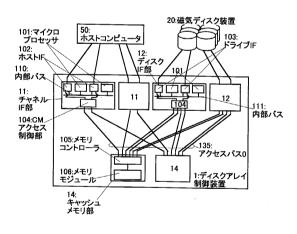

図13に、本発明の他の実施例を示す。

[0072]

ディスクアレイ制御装置1は、ホストコンピュータ50との2つのインターフェース部(チャネルIF部)11、磁気ディスク装置20との2つのインターフェース部(ディスク 30IF部)12、2つのキャッシュメモリ部14と、12本のアクセスパス0:135を有する。

[0073]

チャネルIF部11は、図1に示す実施例1の構成と同様である。

[0074]

ディスク I F 部 1 2 は、 C M アクセス制御部 1 0 4 からキャッシュメモリ部 1 4 へのアクセスパス 0 : 1 3 5 が 4 本に増えている以外は、図 1 に示す実施例 1 の構成と同様である

[0075]

キャッシュメモリ部 1 4 は、メモリコントローラ 1 0 5 に接続されるアクセスパス 0 : 1 40 3 5 の本数が 6 本に増えている以外は、図 1 に示す実施例の構成と同様である。

[0076]

ここで、上記個数は一実施例に過ぎず、個数を上記に限定するものではない。

[0077]

本実施例の特徴は、ディスクIF部12とキャッシュメモリ部14間のアクセスパス0: 135の本数をチャネルIF部11とキャッシュメモリ部14間のアクセスパス0:13 5の本数より多くするということである。

[0078]

ディスクアレイ制御装置では、一般的にディスクIF部12からキャッシュメモリ部14 へのアクセス回数は、チャネルIF部11からキャッシュメモリ部14へのアクセス回数

30

40

以上となる。ディスクアレイではデータに冗長性を持たせるため、データの書き込み時にパリティを生成して、データとともに磁気ディスク装置に記録する。したがって、データの書き込み時には、ディスクIF部12とキャッシュメモリ部14間でパリティ生成のためのアクセスが発生する。これは、一般的にライトペナルティと呼ばれている。このため、ディスクIF部12からキャッシュメモリ部14へのアクセス回数は、チャネルIF部11からキャッシュメモリ部14へのアクセス回数以上となる。

[0079]

実施例 1 で説明した方法により、アクセスパスのデータ転送速度を可変にできない場合には、アクセス回数の多いアクセスパスの本数をアクセス回数の少ないアクセスパスの本数より多くすることにより、アクセス回数の多いアクセスパスのスループットを高くすることができる。これにより、アクセス回数の多いアクセスパスのスループットのネックが解消され、装置全体のスループットの向上が可能となる。

[0800]

また図14に示すように、 1つのCMアクセス制御部104からキャッシュメモリ部14へ接続されるアクセスパス0:135の本数が多いディスクアレイ制御装置1においても、本実施例を実施する上で問題はない。ホストIF及びドライブIFとして、今後はファイバーチャネル等のスループットが100MB/s以上の高速IFが使用されることが多くなると考えられる。アクセスパス0:135のスループットをホストIF及びドライブIFのスループットと同等にする必要がある。このため上記のように高速IFを使用する場合、1つのCMアクセス制御部104からキャッシュメモリ部14へ接続されるアクセスパス0:135の本数が多い図14の構成が有効となる。

[0081]

【発明の効果】

本発明によれば、アクセス回数の多いアクセスパスのスループットによって、ディスクアレイ装置全体のスループットが制限されることを防ぐことが可能となる。それによって、ディスクアレイ制御装置のデータ転送スループットが向上する。

【図面の簡単な説明】

- 【図1】本発明によるディスクアレイ制御装置の構成を示す図。

- 【図2】従来のディスクアレイ制御装置の構成を示す図。

- 【図3】従来のディスクアレイ制御装置の構成を示す図。

- 【図4】本発明によるディスクアレイ制御装置内のCMアクセス制御部の構成を示す図。

- 【図5】本発明によるディスクアレイ制御装置内のキャッシュメモリ部の構成を示す図。

- 【図6】本発明によるディスクアレイ制御装置内のデータ転送制御部の構成を示す図。

- 【図7】本発明によるディスクアレイ制御装置内のデータ転送制御部の他の構成を示す図

- 【図8】本発明によるディスクアレイ制御装置内のアドレス(adr)、コマンド(cmd)解析部の構成を示す図。

- 【図9】本発明によるディスクアレイ制御装置内のセレクタ部の構成を示す図。

- 【図10】本発明によるディスクアレイ制御装置の他の構成を示す図。

- 【図11】本発明によるディスクアレイ制御装置の他の構成を示す図。

- 【図12】本発明によるディスクアレイ制御装置の他の構成を示す図。

- 【図13】本発明によるディスクアレイ制御装置の他の構成を示す図。

- 【図14】本発明によるディスクアレイ制御装置の他の構成を示す図。

【符号の説明】

1 … ディスクアレイ制御装置、 1 1 … チャネルIF部、 1 2 … ディスクIF部、 1 4 … キャッシュメモリ部、 2 0 …磁気ディスク装置、 5 0 … ホストコンピュータ、 1 0 1 … マイクロプロセッサ、 1 0 2 … ホストIF、 1 0 3 … ドライブIF、 1 0 4 … C M アクセス制御部、 1 0 5 … メモリコントローラ、 1 0 6 … メモリモジュール、 1 1 0 、 1 1 1 … 内部バス、 1 3 5 … アクセスパス 0 。

【図1】

【図2】

【図3】

【図4】

### 【図5】

212:制御線2 (CMアクセス ) (CMPアクセス ) (CMP )

図5

### 【図6】

図6

# 【図7】

図7

### 【図8】

図8

### 【図9】

212:制御線2 (CMアクセス 制御部へ) 135:アクセスパス0 220: 同期信号線 301 ×8 320 A 320 300 ► チェック 部\_\_\_\_\_ 300 300 ×8 **►**① ,305 315 **►**① • × 4 ×4 306:セレクタ 303:パケット バッファ 303 ×4 300 300 320 320 ×4 301 13:セレクタ部 226 136:アクセスパス1

【図10】

図10

### 【図11】

図11

【図12】

図12

# 【図14】

# フロントページの続き

# (56)参考文献 特開平05-158797(JP,A)

特開平07-020994(JP,A)

特開平06-019627(JP,A)

特開平09-034646(JP,A)

特開平09-231158(JP,A)

特開平10-333836(JP,A)

# (58)調査した分野(Int.CI.<sup>7</sup>, DB名)

G06F 3/06-3/08

G06F 12/00-12/16

G06F 13/10-13/38