# (19)대한민국특허청(KR) (12) 공개특허공보(A)

(51) 。Int. Cl.

*H01L 21/3205* (2006.01) *H01L 21/768* (2006.01) *H01L 21/822* (2006.01) (11) 공개번호 10-2006-0102343

(43) 공개일자 2006년09월27일

(21) 출원번호 10-2006-7010517

(22) 출원일자 2006년05월29일

번역문 제출일자 2006년05월29일 (86) 국제출원번호 PCT/JP2005/01

(86) 국제출원번호PCT/JP2005/018396국제출원일자2005년09월28일

(87) 국제공개번호 WO 2006/036000 국제공개일자 2006년04월06일

(30) 우선권주장 JP-P-2004-00289182 2004년09월30일 일본(JP)

(71) 출원인 가부시키가이샤 리코

일본 도쿄도 오다꾸 나가마고메 1쵸메 3-6

(72) 발명자 다이닌 마사노리

일본 6691321 효고켄 산다시 게야키다이 4-36-2

(74) 대리인 김진환

송승필

심사청구: 있음

## (54) 반도체장치 및 그 제조방법

#### 요약

반도체장치는 반도체기판, 절연막을 통해 반도체기판 상에 형성된 다결정 실리콘 패턴, 다결정 실리콘 패턴을 피복하도록 반도체기판 상에 형성된 층간 절연막, 및 층간 절연막 상에 형성된 금속 배선층 패턴을 포함하고, 금속 배선층 패턴은 그 상부 표면, 하부 표면 및 측벽 표면 상에 각각 실리콘 질화막을 가진다.

#### 대표도

도 1

## 명세서

#### 기술분야

본 발명은 일반적으로 반도체장치에 관한 것으로, 더욱 상세하게는, 저항 및/또는 게이트 전극으로 사용되는 다결정 실리콘 패턴을 포함하는 반도체장치 및 그 제조방법에 관한 것이다.

#### 배경기술

최근, 특히 아날로그 집적회로(IC: Integrated Circuit) 장치의 분야에서 개선된 장치 특성에 대한 요구가 증가하고 있다. 예를 들어, 아날로그 반도체 집적회로 장치는 그 안에 형성된 트랜지스터에 대한 임계 특성과 저항 소자에 대한 저항값의 높은 안정성 및 제어성을 보장해야 한다는 점을 감안하여, 아날로그 반도체 집적회로 장치에서는, 특히 임계 전압과 저항 값의 관점에서 동작 특성의 높은 정밀도에 대한 엄격한 요구가 있다. 높은 정밀도의 아날로그 반도체 집적회로 장치에서는, 긴 시간 동안의 안정된 트랜지스터 특성 및 안정된 저항값이 특히 중요하다.

한편, 매우 미세화된 반도체 집적회로 장치에서는, 그 안에 형성된 반도체 소자들간의 전기 배선으로서 다층 배선구조가 최근에 폭넓게 사용되고 있다. 다층 배선구조에서는, 층간 절연막 또는 SOG(Spin On Glass)막을 사이에 둔 상태에서, 서로 적충된 다수의 층의 형태로 배선 패턴이 형성되며, 층간 절연막은 배선 패턴간의 전기 절연을 위해 제공됨과 동시에, 현재의 층의 배선 배턴을 매립함으로써 다음 배선 패턴을 형성하기 위한 평탄화된 표면을 제공하기 위한 것이다.

이들 층간 절연막은 그 형성 공정과 관련하여 다량의 수소 및 수분을 함유하고 있는 것으로 알려져 있다. 따라서, 반도체 집적회로 장치의 제조공정 도중에 행해지는 열처리에 의해 이러한 수소 또는 수분이 층간 절연막으로부터 방출되고, 방출된 수소 또는 물 분자가 저항소자 또는 트랜지스터의 게이트 전극을 구성하는 하층에 배치된 다결정 실리콘 패턴에 도달하면, 저항소자의 저항값 또는 트랜지스터의 임계 전압에 있어서 실질적인 변동이 발생한다.

이와 같이 방출된 수소 분자 또는 물 분자가 다결정 실리콘 패턴의 입자 경계에 의해 트랩(trap)될 경우, 입자 경계에서의 변경된 장벽 높이로 인해 다결정 실리콘의 저항소자 또는 게이트 전극의 특성에 있어서 중요한 변경이 발생하는 한편, 이러한 장벽 높이의 변경에 의해 다결정 실리콘 패턴에서의 캐리어 농도 레벨이 증가 또는 감소하게 됨에 유의해야 한다. 수소 또는 수분에 의해 발생한 영향은 다결정 실리콘 패턴에 도입된 불순물 원소의 농도 레벨에 의존하므로, 그 영향의 정도는 다결정 실리콘 패턴에 대해 의도된 저항값에 의존한다. 또한, 다결정 실리콘 패턴에 포함된 수소의 양은, 수소 장벽으로서 작용하는 금속 배선배턴의 바로 아래에 다결정 실리콘 패턴이 배치되는지 아닌지에 의존한다.

특허문헌 1은 다결정 실리콘 게이트 전극을 각각 갖는 복수의 MOS(metal-oxide-semiconductor) 트랜지스터를 포함하는 전압 발생회로를 개시하고 있다. 특허문헌 1에서, MOS 트랜지스터는 소스 영역, 드레인 영역 및 채널 영역간에 공통의 캐리어 농도 레벨을 가지며, 각각의 상이한 불순물 농도 레벨 및/또는 각각의 상이한 도전형에 의해 형성된 상이한 게이트 전극간의 일함수(work function)의 차이를 이용하여 전압이 생성된다.

특허문헌 1은 고온에서도 안정적으로 동작하는 MOS 트랜지스터 회로에 관한 것이지만, MOS 트랜지스터에 대해 다결정 실리콘 게이트를 이용하는 이러한 회로에서는, 게이트 전극의 저항값 변동이 MOS 트랜지스터의 임계 특성의 변동을 유도함을 유의해야 한다.

또한, 이러한 회로에는 다결정 실리콘 패턴으로 형성된 저항체도 구비되어 있고, 저항체로서 사용되는 이러한 다결정 실리콘 패턴은 게이트 전극으로서 사용되는 다결정 실리콘 패턴의 불순물 농도 레벨과 상이한 불순물 농도 레벨을 가진다. 따라서, 제조공정 중의 수소의 영향은 상이한 다결정 실리콘 패턴간에 서로 다르다.

비특허문헌 1은 다결정 실리콘 패턴으로 형성된 게이트 전극의 에너지 밴드를 개시한 것으로, 비특허문헌 1은 MOS 구조의 게이트 전극에서의 불순물 농도 레벨(캐리어 농도 레벨)과 기판의 일함수간의 관계를 서술하고 있다.

비특허문헌 1에 따르면, 캐리어 농도 레벨의 증가와 함께 일함수는 증가하며, 불순물 농도 레벨이  $5 \times 10^{19} {\rm cm}^{-3}$ 에 도달할 경우에 일함수는 최대값을 가진다. 다른 한편으로, 불순물 농도 레벨이 위의 값을 초과하면, 일함수는 감소한다. 다결정실리콘 패턴의 불순물 농도가 위의 값  $5 \times 10^{19} {\rm cm}^{-3}$  보다도 작고, 이에 따라, 다결정 실리콘 패턴이 증가된 저항값을 갖는 상태에서는, 입자 경계에서 수소 원자가 용이하게 트랩되어, 저항값의 변동이 커지는 경향이 있다.

다결정 실리콘 패턴이 저항소자로서 사용될 경우에도 유사한 저항값의 변동이 발생한다.

수소의 영향을 크게 받을 수 있는 그러한 불순물 농도 레벨을 갖는 다결정 실리콘 패턴을 사용할 경우와 관련하여, 예를 들어, 특허문헌 2에 기재된 것과 같이, 장치 제조공정 중에 저항값에 대한 수소의 작용을 억제하기 위한 기술이 제안되어 있으며, 특허문헌 2에서는, 플라즈마 질화막과 금속 배선 패턴이 저항값에 걸쳐 피복 영역의 비율이 동일하도록 배치되어 있다.

또한, 저항체의 영역을 금속 배선층 패턴에 의해 피복하여, 그 위에 형성된 플라즈마 질화막으로부터의 다결정 실리콘 저항체에 대한 수소의 작용이 차단되도록 하는 방법이 개시되어 있다. 특허문헌 3을 참조해야 한다.

그러나, 이들 종래기술의 어느 것도 다결정 실리콘 저항체 상에 금속 배선층 패턴을 배치하기 위한 충분한 자유도를 허용하지 않으며, 저항체 상의 영역이 배선 패턴을 제공하도록 사용될 수 없다고 하는 문제가 있었다.

또한, 다결정 실리콘 저항체에 대해 서로 상이한 불순물 농도 레벨의 복수의 다결정 실리콘 패턴을 사용할 경우, 수소의 영향 정도가 다결정 실리콘 패턴의 불순물 농도 레벨에 따라 변한다고 하는 문제도 있었다.

[특허문헌 1] 일본 특허출원공개 제2001-284464호 공보

[특허문헌 2] 일본 특허출원공개 평6-112410호 공보

[특허문헌 3] 일본특허 제3195828호 공보

[특허문헌 4] 일본 특허출원공개 제2003-152100호 공보

[비특허문헌 1] Dependence of the Work-Function Difference between the Polysilicon Gate and Silicon Substrate on the Doping Level in Polysilicon(IEEE 1985)

#### 발명의 상세한 설명

상술한 것과 같이, 다결정 실리콘 저항체나, MOS 트랜지스터의 다결정 실리콘 게이트 전극에서는, 그 저항값이 시간에 따라 변화하거나, 층간 절연막으로부터의 수소 가스 또는 물의 방출 때문에, 그리고, 저항값의 변화 정도가 다결정 실리콘 저항체 또는 다결정 실리콘 게이트 전극 상에 금속 배선 패턴이 제공되는지 아닌지에 의존한다는 사실 때문에, 장치의 제조 공정 중에 그 저항값이 변화한다는 문제점이 있었다. 이러한 저항값의 변화가 발생하면, 저항체의 저항값 또는 MOS 트랜지스터의 임계값이 이례적으로 변화하는 문제가 발생한다.

또한, 종래기술은 다결정 실리콘 패턴 상에 금속 배선층 패턴의 형성을 금지하거나, 다결정 실리콘 패턴 상에 제공된 금속 배선층 패턴과 다결정 실리콘 패턴의 중첩을 회피하는 점을 고려하면, 배선 패턴으로서 다결정 실리콘 패턴 상의 영역을 자유롭게 사용하는 것이 가능하지 않다는 점에서, 종래기술의 설계 자유도가 제약되는 문제점이 있었다.

본 발명의 목적은, 다결정 실리콘 패턴의 저항값을 제어하면서, 다결정 실리콘 패턴 상에 금속 배선층을 배치하는 것이 가능한 반도체장치 및 그 제조방법을 제공하는 것이다.

본 발명은 이하의 반도체장치를 제공하며, 이 반도체장치는,

반도체기판;

절연막을 통해 상기 반도체기판 상에 형성된 다결정 실리콘 패턴;

상기 다결정 실리콘 패턴을 피복하도록 상기 반도체기판 상에 형성된 층간 절연막; 및

상기 층간 절연막 상에 형성된 금속 배선층 패턴을 포함하고,

상기 금속 배선층 패턴은 그 상부 표면, 하부 표면 및 측벽 표면 상에 각각 실리콘 질화막을 갖는다.

본 발명에 따르면, 다결정 실리콘 패턴 상에 금속 배선층 패턴이 제공되는지 아닌지에 관계없이, 여러 다결정 실리콘 패턴에 대해 동일한 저항값을 달성하는 것이 가능해진다.

바람직한 실시예에서, 실리콘 질화막은, 층간 절연막의 표면 상에 형성되어 금속 배선층 패턴의 하부 표면과 접촉하는 제1 질화막과, 금속 배선층 패턴의 측벽 표면 및 상부 표면을 피복하는 제2질화막을 포함한다. 이에 따라, 제1질화막 및 제2질화막은 각각 상이한 두께를 가질 수도 있다.

또한, 바람직한 실시예에서는, 금속 배선층 패턴의 아래에 배치된 제1질화막을 제외하고, 제1질화막 및 제2질화막이 제거되어 있는 영역이 제공될 수도 있다.

또한, 반도체장치는 다결정 실리콘 패턴으로 이루어진 게이트 전극을 갖는 p-채널 MOS 트랜지스터를 포함하고, p-채널 MOS 트랜지스터 상의 영역에는, 금속 배선층 패턴, 제1질화막 및 제2질화막의 형성이 억제될 수도 있다.

또한, 다결정 실리콘 패턴과 충간 절연막 사이에, 다결정 실리콘 패턴측으로부터 순서대로 산화막 및 제3질화막을 포함하도록 한 적충막을 제공하는 것이 가능하다.

또한, 반도체장치는 상술한 다결정 실리콘 패턴을 게이트 전국으로서 갖는 p-채널 MOS 트랜지스터를 포함하고, p-채널 MOS 트랜지스터 상에는 상술한 제3질화막이 형성되도록 하는 것이 가능하다.

하나의 예로서, 본 발명은 2개 이상의 저항소자에 의해 공급 전압을 분할하여 출력전압을 형성하는 전압 분할회로를 갖는 반도체장치를 제공하고, 전압 분할회로는 퓨즈소자의 절단에 의해 출력전압을 조정할 수 있으며, 앞서 설명한 다결정 실리 콘 패턴은 저항소자로서 사용된다.

다른 예로서, 본 발명은 입력전압을 분할하여 분할된 전압출력을 생성하는 전압 분할회로와, 기준전압을 생성하는 기준전압 발생기와, 전압 분할회로의 분할된 전압출력 및 기준전압 발생기의 기준전압을 비교하는 비교회로를 갖는 전압 검출회로를 포함하고, 전압 분할회로는 상술한 바와 같은 다결정 실리콘 패턴을 포함한다.

본 발명의 반도체장치의 또 다른 예는, 입력전압의 출력을 제어하는 출력 드라이버와, 출력전압을 분할하여 분할된 전압을 생성하는 전압 분할회로와, 기준전압을 생성하는 기준전압 발생기와, 비교 결과에 응답하여 출력 드라이버를 제어하는 비교회로를 갖는 정전압 발생기를 포함하고, 본 발명의 다결정 실리콘 패턴은 전압 분할회로로서 사용된다.

또한, 본 발명의 반도체장치의 제조방법에 따르면, 절연막을 통해 반도체기판 상에 다결정 실리콘 패턴을 형성하는 단계; 다결정 실리콘 패턴을 피복하도록 반도체기판 상에 충간 절연막을 형성하는 단계; 충간 절연막 상에 제1질화막을 형성하는 단계; 제1질화막 상에 금속 배선층 패턴을 형성하는 단계; 및, 금속 배선층을 피복하도록 제1질화막 상에 제2질화막을 형성하는 단계가 제공된다.

본 발명의 제조방법에 따르면, 제2질화막을 형성하는 단계 이후에, 소정의 영역으로부터 제2질화막 및 제1질화막을 선택적으로 제거하는 단계가 제공될 수도 있다.

본 발명의 반도체장치에 따르면, 다결정 실리콘 패턴 상부의 층간 절연막 상에 형성된 금속 배선층 패턴이 실리콘 질화막에 의해 피복되어 있으며, 이러한 다결정 실리콘 패턴의 상부에 금속 배선층 패턴이 제공되는지 아닌지에 관계없이, 여러다결정 실리콘 패턴에 대해 동일한 저항값을 얻는 것이 가능해진다. 이에 따라, 다결정 실리콘 패턴의 저항값을 의도하는 대로 제어하면서, 다결정 실리콘 패턴의 상부에 금속 배선층 패턴을 자유롭게 배치하는 것이 가능해진다.

또한, 제1질화막이 금속 배선층 패턴의 하부 표면에 접촉하고, 제2질화막이 금속 배선 패턴의 측벽 표면 및 상부 표면을 피복하도록, 실리콘 질화막을 형성함으로써, 제1질화막 및 제2질화막 사이의 질화막의 두께를 변화시키는 것이 가능해진다. 이에 따라, 다결정 실리콘 패턴의 불순물 농도 레벨에 따라, 제1질화막 및 제2질화막의 막 두께 비율을 선택하는 것이 가능해진다. 이것에 의해, 그 불순물 농도 레벨에 관계없이, 그리고, 다결정 실리콘 패턴 상부의 금속 배선층 패턴이 형성되는지 아닌지에 관계없이, 다결정 실리콘 저항 패턴 또는 게이트 전극 패턴을 형성하는 것이 가능해진다.

또한, 금속 배선층 아래의 제1질화막을 제외하고, 금속 배선층 패턴을 둘러싸는 제1질화막 및 제2질화막을 제거함으로써, 이러한 구성으로 배치된 다결정 실리콘 패턴과, 제1 및 제2질화막이 형성되어 있는 다결정 실리콘 패턴 사이에서, 이들 다 결정 실리콘 패턴으로 동일한 불순물 농도 레벨이 사용될 경우에도, 저항값을 변화시키는 것이 가능해진다.

또한, p-채널 MOS 트랜지스터는, 금속 배선층 패턴의 형성 직후에 행해지는 금속 합금 공정시에 게이트/산화막 계면에 존재하는 트랩 준위(trapping level)가 안정화되지 않으면, 임계 특성이 불안정해지는 경향이 있다는 문제를 가지고 있지만 (특허문헌 4 참조), 본 발명은, 제1 및 제2질화막이 제거되어 있는 영역에 p-채널 MOS 트랜지스터를 배치함으로써, 상술한 다결정 실리콘 패턴을 전극으로 사용하는 p-채널 MOS 트랜지스터의 임계 제어성의 열화를 성공적으로 회피한다.

또한, 상술한 다결정 실리콘 패턴이 p-채널 MOS 트랜지스터의 게이트 전극으로 사용되도록 하고, 상술한 금속 배선층, 제 1질화막 및 제2질화막의 어느 것도 p-채널 MOS 트랜지스터 상에 형성되지 않도록 반도체장치를 구성함으로써, 트랩 준위를 안정화시키는 것이 가능해지고, p-채널 MOS 트랜지스터의 열악한 임계 제어성의 문제가 성공적으로 회피된다.

또한, 다결정 실리콘 패턴과 층간 절연막 사이에, 다결정 실리콘 패턴에 더 근접한 측으로부터 산화막 및 제3질화막의 순서로 적충막을 제공함으로써, 제3질화막에 의해 다결정 실리콘 패턴으로의 수소의 확산을 방지하는 것이 가능해지고, 다결정 실리콘 패턴의 저항값에 대해 양호한 안정성이 달성된다.

또한, 이러한 제3질화막을 사용하는 구조의 경우, 다결정 실리콘 패턴을 게이트 전극으로서 사용하는 p-채널 MOS 트랜지스터의 상부의 영역으로부터 제3질화막의 형성을 억제함으로써, 트랩 준위에 대해 양호한 안정성이 달성되고, p-채널 MOS 트랜지스터에 대해 양호한 임계 제어가 달성된다.

또한, 2개 이상의 저항소자에 의해 전압을 분할하여 전압출력을 얻고 퓨즈소자의 절단에 의해 전압출력을 조정할 수 있는 전압 분할회로를 갖는 반도체장치에 있어서, 본 발명의 다결정 실리콘 패턴에 저항소자를 형성함으로써, 다결정 실리콘 패턴의 저항값을 제어하면서, 다결정 실리콘 패턴 상에 금속 배선 패턴을 배치하는 것이 가능해진다. 이에 따라, 설계의 자유도가 향상된다.

또한, 입력전압을 분할하여 분할된 전압을 공급하는 전압 분할회로와, 기준전압을 발생하는 기준전압 발생기와, 전압 분할 회로로부터의 분할된 전압과 기준전압 발생기로부터의 기준전압을 비교하는 비교회로를 갖는 반도체장치에서는, 본 발명의 다결정 실리콘 패턴을 전압 분할기로서 사용하는 전압 분할회로를 제공함으로써, 설계의 자유도를 증가시키는 것이 가능해진다.

또한, 입력전압의 출력을 제어하는 출력 드라이버와, 출력전압을 분할하여 분할된 전압을 생성하는 전압 분할회로와, 기준전압을 생성하는 기준전압 발생기와, 비교 결과에 응답하여 출력 드라이버를 제어하는 비교회로를 갖는 정전압 발생기를 포함하고, 본 발명의 다결정 실리콘 패턴이 전압 분할회로로 사용되는 본 발명의 반도체장치에 있어서, 전압 분할기가 본 발명의 다결정 실리콘 패턴을 사용하도록 하는 전압 분할회로를 제공함으로써, 설계의 자유도를 증가시키는 것이 가능해진다.

또한, 본 발명의 반도체장치의 제조방법에 따르면, 절연막을 통해 반도체기판 상에 다결정 실리콘 패턴을 형성하는 단계와, 다결정 실리콘 패턴을 피복하도록 반도체기판 상에 충간 절연막을 형성하는 단계와, 충간 절연막 상에 제1질화막을 형성하는 단계와, 제1질화막 상에 금속 배선층 패턴을 형성하는 단계와, 금속 배선층을 피복하도록 제1질화막 상에 제2질화막을 형성하는 단계가 제공되고, 그 상부에 금속 배선층 패턴이 배치되어 있는지 아닌지에 관계없이, 다결정 실리콘 패턴에 대해 동일한 저항값을 달성하는 것이 가능해진다. 이에 따라, 다결정 실리콘 패턴의 저항값을 제어하면서, 다결정 실리콘 패턴 상에 금속 배선층 패턴을 배치하는 것이 가능해진다. 또한, 제1질화막 및 제2질화막의 막 두께를 변화시키는 것이가능하고, 다결정 실리콘 패턴의 불순물 농도 레벨에 따라 제1질화막 및 제2질화막 사이의 막 두께 비율을 선택하는 것이가능해진다. 이것에 의해, 다결정 실리콘 패턴의 불순물 농도 레벨에 관계없이, 그 위의 금속 배선층 패턴의 존재 또는 부재에 의해 영향을 받지 않는 다결정 실리콘 패턴을 형성하는 것이가능해진다.

또한, 본 발명에 따른 반도체장치의 제조방법에 있어서, 제2질화막의 형성 후에, 소정의 영역으로부터 제2질화막 및 제1질화막을 제거하는 공정을 제공함으로써, 제1 및 제2질화막이 제거되어 있는 영역에 배치된 다결정 실리콘 패턴과, 제1 및 제2질화막 양자가 존재하는 영역에 배치된 다결정 실리콘 패턴에 대하여, 양 다결정 실리콘 패턴이 동일한 불순물 농도 레벨을 갖는 경우에도, 상이한 저항값을 실현하는 것이 가능해진다. 이에 따라, 제1질화막 및 제2질화막이 제거되어 있는 영역에 p-채널 MOS 트랜지스터를 배치함으로써, 다결정 실리콘 패턴을 게이트 전극으로 사용하는 p-채널 MOS 트랜지스터의 임계 전압 제어성의 열화가 발생하지 않음에 유의해야 한다.

본 발명의 다른 목적, 특징 및 장점은 첨부 도면을 참조하여 판독할 경우에 아래의 상세한 설명으로부터 더욱 명확하게 될 것이다.

#### 도면의 간단한 설명

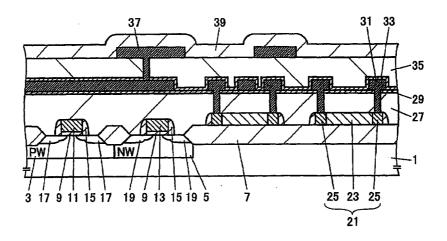

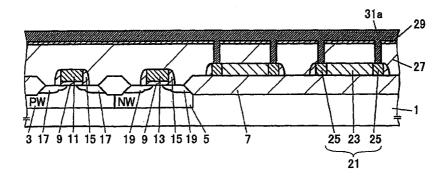

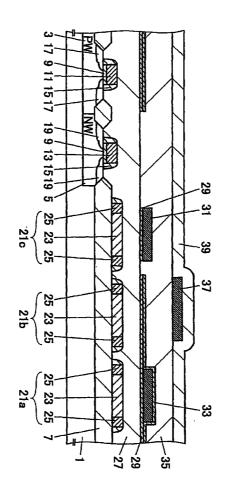

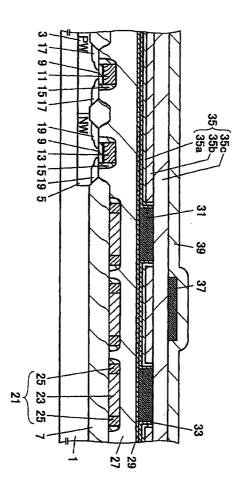

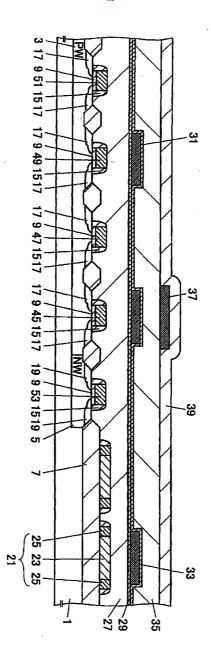

도 1은 본 발명의 반도체장치의 일 실시예를 도시하는 단면도이다.

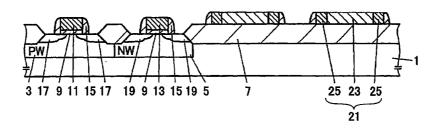

도 2a 내지 도 2e는 본 발명의 일 실시예에 따른 반도체장치의 제조방법을 도시하는 단면도이다.

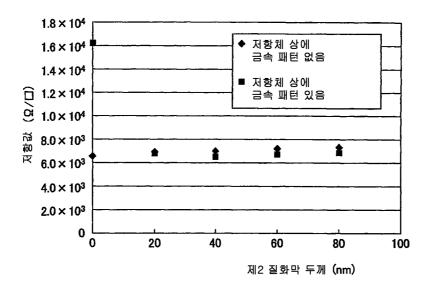

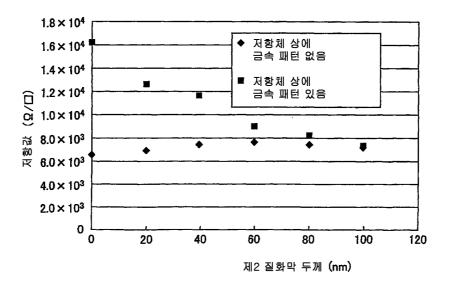

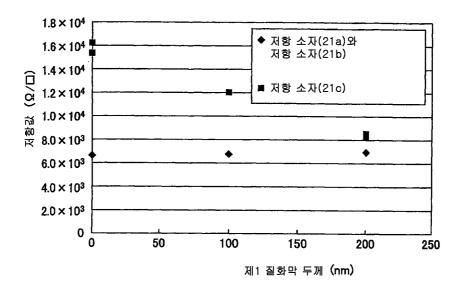

도 3은, 다결정 실리콘 패턴 상에 금속 배선층 패턴이 제공되어 있는 경우와, 다결정 실리콘 패턴 상에 이러한 금속 배선층 패턴이 제공되지 않을 경우의 양자에 대하여, 제1질화막의 막 두께를 20nm로 유지하면서, 제2질화막의 두께에 따른 다결정 실리콘 패턴의 저항값의 변화를 도시하는 도면이다.

도 4는, 다결정 실리콘 패턴 상에 금속 배선층 패턴이 제공되어 있을 경우와, 다결정 실리콘 패턴 상에 이러한 금속 배선층 패턴이 제공되지 않을 경우의 양자에 대하여, 제1질화막의 막 두께를 5nm로 유지하면서, 제2질화막의 두께에 따른 다결 정 실리콘 패턴의 저항값의 변화를 도시하는 도면이다.

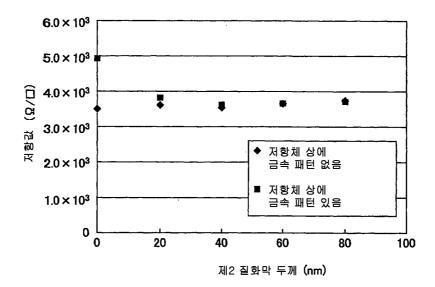

도 5는, 도 3의 경우에 비해 다결정 실리콘 패턴의 저항값이 감소되어 있다는 점을 제외하고는, 도 3과 동일한 조건 하에서, 제2질화막의 막 두께에 따른 다결정 실리콘 패턴의 저항 변화를 도시하는 도면이다.

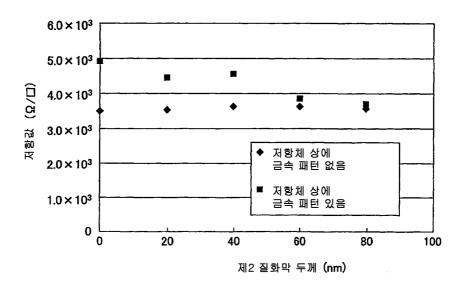

도 6은, 도 4의 경우에 비해 다결정 실리콘 패턴의 저항값이 감소되어 있다는 점을 제외하고는, 도 4와 동일한 조건 하에서, 제2질화막의 막 두께의 변화에 따른 다결정 실리콘 패턴의 저항값의 변화를 도시하는 도면이다.

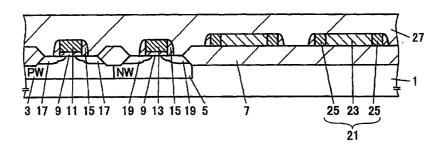

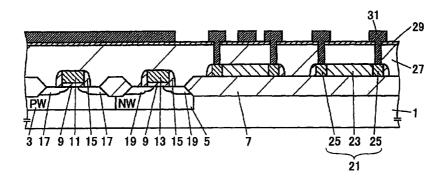

도 7은 본 발명의 반도체장치의 다른 실시예를 도시하는 단면도이다.

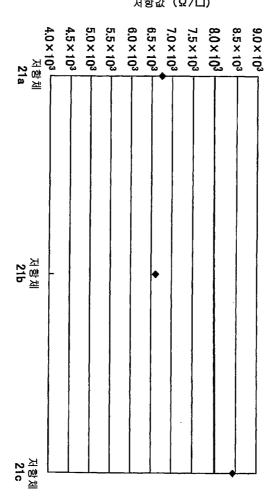

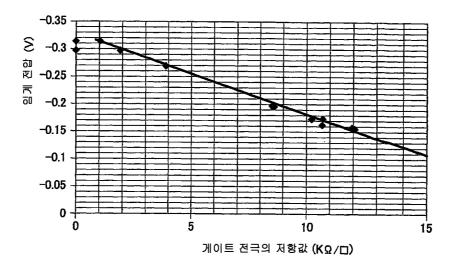

도 8은 도 7의 저항소자(21a, 21b 및 21c)를 구성하는 저항체(23)의 저항값을 도시하는 도면이다.

도 9는, 제1질화막(29)의 막 두께를 변화시키는 경우에 대해, 도 7의 저항소자(21a, 21b 및 21c)의 임의의 것의 저항체 (23)의 저항값을 도시하는 도면이다.

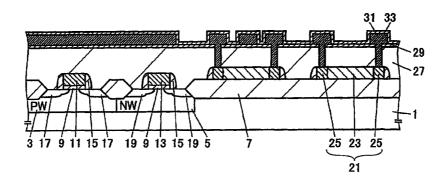

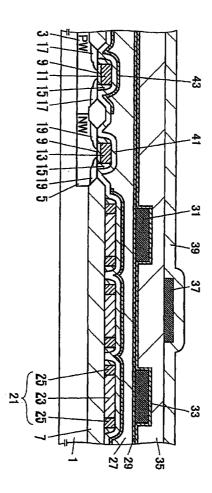

도 10은 본 발명의 반도체장치의 또 다른 실시예를 도시하는 단면도이다.

도 11은 본 발명의 또 다른 실시예를 도시하는 단면도이다.

도 12는 본 발명의 또 다른 실시예를 도시하는 단면도이다.

도 13은 P(인)이 도핑(doping)된 게이트 전극을 갖는 n-채널 MOS 트랜지스터의 게이트 전극의 저항값과, 이러한 n-채널 MOS 트랜지스터의 임계 전압 사이의 관계를 도시하는 도면이다.

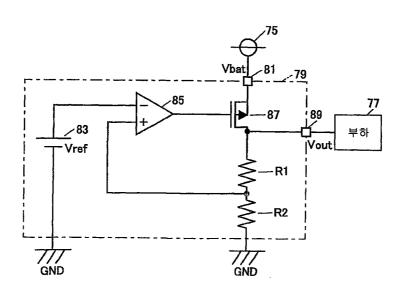

도 14는 아날로그 회로의 형태로 구성된 정전압 발생회로를 갖는 반도체장치의 일 실시예를 도시하는 회로도이다.

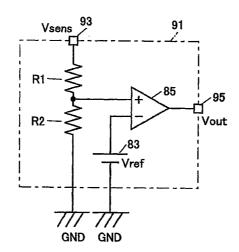

도 15는 아날로그 회로의 형태로 구성된 전압 검출회로를 갖는 반도체장치의 일 실시예를 도시하는 회로도이다.

도 16은 아날로그 회로의 형태로 구성된 전압 분할회로를 갖는 반도체장치의 일 실시예를 도시하는 회로도이다.

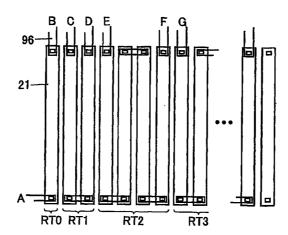

도 17은 전압 분할회로의 퓨즈소자 부분의 레이아웃 예를 도시하는 레이아웃 도면이다.

도 18은 전압 분할회로의 금속 박막 저항 부분의 레이아웃 예를 도시하는 레이아웃 도면이다.

#### 실시예

#### [제 1 실시예]

도 1은 본 발명의 일 실시예에 따른 반도체장치의 일 실시예를 도시하는 단면도이다.

도 1을 참조하면, 반도체장치는 p-형 실리콘기판(반도체기판)(1)에 구성되어 있고, p-형 불순물 원소가 도입된 p-형 웰영역(PW)(3)과, n-형 불순물 원소가 도입된 n-형 웰영역(NW)(5)을 포함하고, p-형 웰영역(3) 및 n-형 웰영역(5)은 실리콘기판(1)의 표면에 큰 두께로 형성된 소자분리 산화막(7)에 의해 서로 분리되어 있다.

p-형 웰 영역(3) 상에는, 약 15nm(나노미터)의 두께를 갖는 게이트 산화막(9)을 그 중간에 끼운 상태에서, n-형 불순물 원소의 혼합(incorporation)에 의해 n<sup>+</sup>-형으로 도핑된 다결정 실리콘막의 게이트 전극(11)이 형성되어 있다.

이와 유사하게, n-형 웰 영역(5) 상에는, 게이트 산화막(9)을 통해 다결정 실리콘막의 게이트 전극(13)이 형성되어 있고, 게이트 전극(13)을 구성하는 다결정 실리콘막은 p-형 불순물 원소의 혼합에 의해 p<sup>+</sup>-형으로 도핑되어 있다.

대표적으로,  $n^+$ -형의 게이트 전극(11) 및  $p^+$ -형의 게이트 전극(13)은 약 400nm의 두께로 형성되어 있다. 또한, 게이트 산화막(9), 게이트 전극(11) 및 게이트 전극(13)의 좌우 측벽 표면에는 측벽 절연막(15)이 형성되어 있다.

p-형 웰 영역(3)에는, 게이트 전극(11)을 가로질러서 LDD(lightly doped drain)를 구성하는 한 쌍의 n-형 확산영역(17)이 형성되고, 게이트 산화막(9), 게이트 전극(11) 및 n-형 확산영역(17)은 모두 함께 p-형 웰 영역(3)에서의 n-채널 MOS 트랜지스터를 구성한다. 또한, 임계 제어를 위하여, 게이트 전극(11) 바로 아래의 p-형 웰 영역(3)의 일부에 대해 채널 도핑이 행해짐을 유의해야 한다.

이와 유사하게, n-형 웰 영역(5)에는,  $p^+$ -형의 게이트 전극(13)을 가로질러서 LDD(lightly doped drain)를 구성하는 한 쌍의 p-형 확산영역(19)이 형성되고, 게이트 산화막(9), 게이트 전극(13) 및 p-형 확산영역(19)은 모두 함께 n-형 웰 영역(5)에서의 p-채널 MOS 트랜지스터를 구성한다. 또한, 임계 제어를 위하여, 게이트 전극(13) 바로 아래의 n-형 웰 영역(5)의 일부에 대해 채널 도핑이 행해짐을 유의해야 한다.

소자분리 막(7)은 다결정 실리콘 패턴으로 이루어진 저항소자(21)를 그 위에 가지고 있고, 저항소자(21)는 의도하는 저항 값에 의해 결정된 농도 레벨을 갖는 n-형 불순물 원소가 도입된 다결정 실리콘 저항체(23)를 포함함을 유의해야 한다. 또한, 저항체(23)의 양단에는, 고농도 레벨을 갖는 n-형 불순물 원소가 도핑된 저저항 다결정 실리콘막(25)이 제공된다.

또한, 실리콘기판(1)의 전면에는, n-채널 MOS 트랜지스터 및 p-채널 MOS 트랜지스터 양쪽과 소자분리 막(7) 상의 저항소자(21)를 피복하도록 한 층간 절연막(27)이 형성되어 있고, 층간 절연막(27)은 300nm의 두께를 갖는 NSG(non-doped silicate glass)막과 500nm의 두께를 갖는 BPSG(boro-phosphosilicate glass)를 포함한다. 이와 같이 형성된 층간 절연막(27)은 평탄화된 상부 표면을 가지지만, 층간 절연막(27)의 평탄화된 상부 표면은 본 발명의 필수 요소는 아님을 유의해야 한다. 도 1에서, NSG막 및 BPSG막은 단층으로 표시되어 있다. 또한, 층간 절연막(27)은 NSG막 및 BPSG막의 적층막에 한정되지 않으며, 단층막 또는 적층막 형태의 다른 절연막 또는 막들을 사용하는 것이 가능하다는 점을 유의해야 한다. 예를 들어, 층간 절연막(27)을 NSG막 및 PSG(phosphosilicate glass)막의 적층으로서 형성하는 것이 가능하다.

충간 절연막(27) 상에는, 예를 들어, 20nm의 두께를 갖는 제1질화막(29)이 형성되어 있고, 충간 절연막(27) 및 제1질화막(29)에는, 게이트 전극(11 및 13), 확산영역(17 및 19) 및 다결정 실리콘막(15)에 각각 대응하여 전기적인 접속을 위한 컨택 홀(contact hole)이 형성되어 있음을 유의해야 한다. 도 1에서는 일부 컨택 홀의 표시가 생략되어 있음에 유의해야 한다.

따라서, 제1질화막(29) 상에는 이와 같이 형성된 컨택 홀을 채우도록 한 제1금속 배선층 패턴(31)이 제공되고, 제1금속 배선층 패턴(31)은 약 40nm의 두께를 갖는 Ti 등의 장벽 금속층과, 80-100nm의 두께를 갖는 Al 층 또는 Al 합금층이 그 하부로부터 그 상부까지 순차적으로 적층되어 있는 적층 구조를 가진다. 여기서, 제1금속 배선층 패턴(31)의 재료는 상술한 것에 한정되지 않고, Al, AlCu, AlSi, Cu 등과, Ti, TiN, TiW, W 등의 적층막을 사용하는 것도 가능하다는 점에 유의해야한다. 또한, 상기 중 임의의 것의 단일층 막을 사용할 수 있다.

충간 절연막(27) 및 제1금속 배선층 패턴(31) 상에는, 예를 들어, 60nm 두께를 갖는 제2질화막(33)이 형성되어 있다. 따라서, 제1질화막(29)의 두께와 제2질화막(33)의 두께는 본 실시예에서 상이하지만, 이것이 본 발명에서 필수적인 것은 아니며, 제1 및 제2질화막(29 및 33)이 동일한 막 두께를 가지도록 형성하는 것도 가능하다.

제2질화막(33) 상에는, TEOS(tetraethyl orthosilicate) 층 및 그 위에 형성된 SOG(spin-on-glass)층의 적층 행태로 금속-금속 층간 절연막(35)이 형성되어 있다. 또한, 층간 절연막(35)에는, 제1금속 배선층 패턴(31) 상부의 영역에, 제1금속 배선층 패턴(31)을 층간 절연막(35) 상에 형성된 제2금속 배선층 패턴(37)과 전기적으로 접속하기 위한 관통 홀(through hole)이 형성되어 있다. 도 1은 층간 절연막(35)에 형성된 모든 관통 홀을 나타내지 않고 있음에 유의해야 한다. 여기서, 층간 절연막(35)은 TEOS 및 SOG의 적층막에 한정되지 않으며, SOG 막 상에 TEOS막, NSG막 또는 BPSG막 등의 절연막을 갖는 것과 같은 다른 구성의 층간 절연막을 사용하는 것도 가능하다는 점에 유의해야 한다.

또한, 제2금속 배선층 패턴(37)은 약 1500nm의 두께를 갖는 AlSiCU 층의 형태로, 그 내부에 형성된 관통 홀을 채우도록 층간 절연막(35)에 형성된다. 또한, 플라즈마 질화막(39)은 약 100nm의 두께를 갖는 보호막으로서, 제2금속 배선층 패턴 (37)을 피복하도록 층간 절연막(35) 상에 형성된다.

도 2a 내지 도 2e는 도 1의 반도체장치의 제조방법을 도시한 것이다.

(1) 도 2a를 참조하면, 실리콘기판(1)에는, n-채널 MOS 트랜지스터가 형성될 영영에 대응하여 p-형 웰 영역(3)이 형성된다. 이와 유사하게, 실리콘기판(1)에는, p-채널 MOS 트랜지스터가 형성될 영역에 대응하여 n-형 웰 영역(5)이 형성된다. 또한, p-채널 MOS 트랜지스터를 위한 n-형 웰(5)의 형성 후에는, 실리콘기판(1)의 표면 상에, 공지된 LOCOS(local oxidation of silicon) 법에 따라 두꺼운 산화막의 형태로 소자분리 산화막(7)이 형성된다.

또한, p-형 웰 영역(3)의 표면 및 n-형 웰 영역(5)의 표면 상에는, 게이트 산화막(9)이 약 15nm의 두께로 형성되고, 이와 같이 게이트 산화막(9)이 형성된 실리콘기판(1)의 전면에는, 저압 CVD 처리 등에 의해 약 400nm의 두께로 비도핑 다결정 실리콘막이 증착되고, 이와 같이 증착된 비도핑 다결정 실리콘막에 대해서는 이어지는 패터닝 처리가 행해지며, 이것에 의하여, 게이트 전극 및 저항소자를 위한 다결정 실리콘 패턴이 형성된다. 또한, 포토리소그래피(photolithography) 및 이온 주입이 행해지고, n-형 확산영역(17) 및 p-형 확산영역에는 LDD 부분이 형성된다. 또한, 이러한 이온 주입 처리의 결과로 저항체(23)가 형성된다.

또한, 산화막의 증착 및 에치백(etchback) 처리에 의해 측벽 절연막(15)이 형성되고, 포토리소그래피 및 이온 주입 처리에 의해 게이트 전극(11)이  $n^+$ -형으로 도핑된다. 이와 동시에, n-형 확산 영역(17)은 LDD 영역 외부에 위치한 그 일부에서  $n^+$ -형으로 도핑된다. 이와 유사하게, 포토리소그래피 및 이온 주입 처리에 의해 게이트 전극(13)이  $p^+$ -형으로 도핑되고, 이와 동시에, p-형 확산 영역(19)은 LDD 영역 외부에 위치한 그 일부에서  $p^+$ -형으로 도핑된다. 또한, 저저항 영역(25)은 다결정 실리콘 패턴(21)에 형성된다.

다음으로, 저항값을 제어하기 위한 불순물 원소를, 저항체(23)를 구성하는 다결정 실리콘 막의 영역에 도입하기 위하여 이온 주입 처리가 행해진다. 예를 들어, n-형 불순물 원소인 인(P)의 혼합에 의해 다결정 실리콘 패턴의 저항률(resistivity)을  $10~\mathrm{k}\Omega/\Box$ 으로 조정할 경우,  $3.0\times10^{14}\sim6.0\times10^{14}/\mathrm{cm}^{-2}$ 의 도스량(dose)을 갖는 이온 주입이 필요하다. 또한, 인(P)의 혼합에 의해 다결정 실리콘 패턴의 저항률을  $2\mathrm{k}\Omega/\Box$ 으로 조정할 경우,  $1.0\times10^{15}\sim1.5\times10^{15}/\mathrm{cm}^{-2}$ 의 도스량을 갖는 이온 주입이 필요하다.

또한, 저항체(23)는 p-형 불순물 원소가 도입된 다결정 실리콘막으로도 형성될 수 있다. 이러한 경우, 붕소(boron)가 p-형 불순물 원소로서 도입될 수도 있다. 저항체(23)의 불순물 농도 레벨의 제어는, n-형의 확산 영역(17) 또는 p-형의 확산 영역(19)에 LDD 영역을 형성하기 위한 이온 주입 처리와 동시에 행해질 수도 있다. 이와 달리, 전용의 이온 주입 처리를 이용하여 이러한 제어를 달성하는 것도 가능하다. 또한, 다결정 실리콘막을 패터닝하기 전에 이온 주입 처리를 행함으로 써, 저항체(23)의 불순물 농도 레벨의 제어를 달성하는 것이 가능하다.

(2) 다음으로, 도 2b의 단계에서는, 실리콘기판(1)의 전면에 NSG막이 약 300nm의 두께로 증착되고, 그 위에 BPSG막이 약 500nm의 두께로 증착된다. 이에 따라, 충간 절연막(27)이 형성된다.

그 후, 800~900℃의 온도로 열 어닐링(annealing) 처리가 가해지고, 평탄화가 행해져서 층간 절연막(27)을 형성한다. 여기서, 평탄성을 향상시키기 위하여, 층간 절연막(27) 상에 SOG 등의 평탄화막을 도포하는 것도 가능하다.

(3) 다음으로, 도 2c의 단계에서는, 층간 절연막(29) 상에 제1질화막(29)이 예를 들어, 20nm의 두께로 형성되고, SiH<sub>2</sub>Cl<sub>2</sub> 또는 NH<sub>3</sub>을 원료 가스로 사용하면서 약 700℃의 온도에서 저압 CVD 처리에 의해 제1질화막(29)이 형성될 수도 있다.

다음으로, 포토리소그래피 처리 및 에칭 처리를 이용함으로써, 제1질화막(29) 및 충간 절연막(27)의 각각의 소정의 영역에는 컨택 홀이 형성된다. 여기서,  $\mathrm{CF_4}$  및  $\mathrm{CHF_3}$ 를 에칭 가스로서 이용하면서,  $\mathrm{ECR}$ (electron cyclotron resonance) 플라즈마 에칭 처리에 의해, 제1질화막(29) 및 충간 절연막(27)을 동시에 에칭하는 것이 가능하고, 추가적인 처리 단계 없이도 접촉 홀이 형성될 수 있다.

또한, 접촉 홀을 포함하는 제1질화막(29) 상에는 Ti 등의 장벽 금속이 약 40nm의 두께로 증착되고, 그 다음, 스퍼터링 처리에 의해, Cu 등을 함유하는 알루미늄 합금이 800 내지 1000nm의 두께로 그 위에 증착된다. 이에 따라, 적층 금속막 (31a)이 얻어진다.

(4) 다음으로, 도 2d의 단계에서는, 포토리소그래피 및 에칭에 의해 적층 금속막(31a)이 패터닝되고, 이것에 의하여, 제1 금속 배선층 패턴(31)의 형성이 달성된다.

여기서, BCl $_3$  및 Cl $_2$ 를 에칭 가스로 이용하면서, ECR 처리에 의해 에칭이 행해질 수도 있다. 이 에칭 처리에서는, 제1질화막(29)이 제1금속 배선층 패턴의 아래에 위치한 일부분에만 남거나, 예시된 예의 경우와 같이, 제1질화막(29)이 충간 절연막(27)의 전면에 남도록, 에칭 조건을 설정하는 것이 가능하다.

(5) 다음으로, 도 2e의 단계에서는, 제1질화막(29) 및 제1금속 배선층 패턴(31) 상에 제2질화막(33)이 예를 들어, 60nm의 두께로 형성된다. 이러한 제2질화막(33)의 형성은,  $SiH_2Cl_2$  및  $NH_3$ 을 원료 가스로서 공급하면서, 약 700 ℃의 온도에서 행해지는 저압 CVD 처리에 의해 수행될 수도 있음에 유의해야 한다.

이러한 실시예에서는, 제1금속 배선층 패턴(31) 아래의 질화막 두께를, 제1질화막(29) 및 제2질화막(33)이 적층되어 있는 영역으로부터 변화시키는 것이 가능하다.

(6) 그 다음, 제2질화막(33) 상에는 플라즈마 CVD 처리에 의해 TEOS막이 증착되고, SOG막을 그 위에 형성하여 평탄화처리가 행해진다. 이것에 의하여, 도 1에 도시된 층간 절연막(35)이 얻어진다.

다음으로, 제1금속 배선 패턴 상의 소정의 영역의 층간 절연막(35)에는 관통 홀이 형성되며, 스퍼터링 처리에 의해 AlSiCu 막을 약 1500nm의 두께로 증착하고, 이와 같이 증착된 AlSiCu막을 포토리소그래피 및 에칭 처리에 의해 패터닝함으로써, 관통 홀을 포함하는 층간 절연막(35) 상에는 제2금속 배선층 패턴(35)이 형성된다. 이것에 의하여, 제2금속 배선층 패턴(37)이 형성된다.

마지막으로, 도 1에 도시된 것과 같이, 플라즈마 질화막(39)은 보호막으로서 약 100nm의 두께로 형성된다.

도 3은, 다결정 실리콘 패턴(23) 상에 금속 배선 패턴(31)이 제공될 경우와, 이러한 금속 배선 패턴이 제공되지 않을 경우에 대해, 제2질화막(33)의 두께를 변화시키면서, 다결정 실리콘 패턴(23)이 20nm 두께의 제1질화막(29)에 의해 피복되어 있는 구조의 다결정 실리콘 패턴(23)의 저항 변화를 도시한 것이다. 도 3에서는, 세로축은 Ω/□로 표현된 저항률을 나타내고, 가로축은 나노미터(nanometer)에 의하여 제2질화막(33)의 두께를 나타내고 있음을 유의해야 한다.

도 3을 참조하면, 다결정 실리콘 패턴(23)은, 금속 배선 패턴(31)이 제공되지 않을 경우에는 7000 Ω/□의 저항값을 나타내고, 이러한 금속 배선층 패턴(31)이 제공될 경우에는 1600 Ω/□의 저항값을 나타낸다는 점에서, 제2질화막(33)이 제공되어 있지 않은 종래기술(제2질화막(33)의 두께가 0nm)에서는, 금속 배선층 패턴(31)이 제공될 경우와, 금속 배선층 패턴 (31)이 제공되지 않을 경우 사이에 큰 차이가 존재한다는 점을 알 수 있다. 다른 한편으로, 도 3은 또한, 제2질화막(33)이 20nm 이상의 두께로 형성될 경우, 이들 두 경우에 동일한 저항값이 얻어지는 것을 도시하고 있다.

이 결과로부터, 다결정 실리콘 패턴 상부의 충간 절연막 상에 제공된 금속 배선충 패턴을 실리콘 질화막에 의해 피복함으로써, 다결정 실리콘 패턴 상부에 금속 배선충 패턴이 배치되어 있는지 아닌지에 관계없이, 다결정 실리콘 패턴에 대해 동일한 저항값이 얻어진다는 것을 명확하게 알 수 있다.

따라서, 본 발명에 따르면, 다결정 실리콘 패턴의 저항을 의도하는 값으로 제어하면서, 다결정 실리콘 패턴 상부에 금속 배선층 패턴을 배치하는 것이 가능해진다.

도 4는, 다결정 실리콘 패턴(23) 상부에 금속 배선 패턴(31)이 제공될 경우와, 이러한 금속 배선 패턴이 제공되지 않을 경우에 대하여, 제2질화막(33)의 두께를 변화시키면서, 다결정 실리콘 패턴(23)이 5nm 두께의 제1질화막(29)에 의해 피복되어 있는 구조의 다결정 실리콘 패턴(23)의 저항 변화를 도시한 것이다. 도 4에서는, 세로축은 Ω/□로 표현된 저항률을 나타내고, 가로축은 나노미터(nanometer)에 의해 제2질화막(33)의 두께를 나타내고 있음에 유의해야 한다.

도 4로부터, 다결정 실리콘 패턴(33)의 상부에 금속 배선층 패턴(31)이 배치되어 있는지 아닌지에 관계없이, 제2질화막 (33)의 두께가 60nm 이상일 경우, 다결정 실리콘 패턴의 저항은 영향을 받지 받으며 다결정 실리콘 패턴은 동일한 저항값을 나타낸다는 점을 알 수 있다.

도 5는, 다결정 실리콘 패턴(23)의 저항값이 감소된 것을 제외하고는, 도 3과 동일한 조건 하에서, 제2질화막(33)의 여러 두께에 대한 다결정 실리콘 패턴의 저항 변화를 도시한 것이다. 도 5에서, 가로축은 나노미터에 의하여 제2질화막(33)의 두께를 나타내고, 세로축은 Ω/□로 표현된 다결정 실리콘 패턴(23)의 저항을 나타낸다.

도 5로부터, 제2질화막(33)이 60nm 이상의 두께로 형성될 경우, 상부에 배치되는 금속 배선층 패턴(31)의 존재 또는 부재에 의해 다결정 실리콘 패턴(23)의 저항값이 영향을 받지 않는다는 것을 알 수 있다.

도 6은, 도 4의 경우에 비해 다결정 실리콘 패턴(23)의 저항값이 감소된 것을 제외하고는, 도 4의 경우와 동일한 조건 하에서, 제2질화막의 여러 두께에 대한 다결정 실리콘 패턴(23)의 저항 변화를 도시한 것이며, 가로축은 나노미터에 의하여 제2질화막(33)의 두께를 나타내고, 세로축은 Ω/□로 표현된 다결정 실리콘 패턴(23)의 저항을 나타낸다.

도 6으로부터, 제2질화막(33)이 80nm 이상의 두께를 가지기만 하면, 다결정 실리콘 패턴(23)의 저항은 상부의 금속 배선 층 패턴에 의해 영향을 받지 않으며, 대체로 동일한 값을 가지게 됨을 알 수 있을 것이다.

따라서, 본 발명에서는, 제1질화막 및 제2질화막의 두께를 변화시킴으로써, 다결정 실리콘 패턴의 상부에 금속 배선층 패턴이 배치되어 있는지 아닌지에 관계없이, 여러 다결정 실리콘 패턴에 대해 동일한 저항값을 얻는 것이 가능해진다. 그 결과, 다결정 실리콘 저항 패턴의 저항값을 의도하는 대로 제어하면서, 기판 상부에 금속 배선층 패턴을 자유롭게 배치하는 것이 가능해진다.

#### [제 2 실시예]

도 7은 본 발명의 제2실시예에 따른 반도체장치를 도시하는 단면도이고, 앞서 설명한 부품에 대응하는 부품은 동일한 참조 번호에 의해 표시되고, 그 설명은 생략할 것이다.

본 실시예에서는, 소자분리 막(7) 상에, 저항소자(21)와 동일한 구조를 각각 갖는 3개의 저항소자(21a, 21b 및 21c)가 제공되어 있음을 알 수 있다.

또한, 2개의 금속 배선층 패턴(31)은 층간 절연막(27) 및 제1질화막(29)을 통해 저항소자(21a) 및 저항소자(21c)의 상부에 각각 형성되어 있다.

도 7에서는, 제1금속 배선층 패턴(31)이 형성되어 있는 부분을 포함하는 층간 절연막(27)의 부분 상부의 제1질화막(29) 상에 제2질화막(33)이 형성되어 있음에 유의해야 한다. 다른 한편으로, 제1금속 배선층 패턴(29) 바로 아래에 형성된 제1질화막(29)을 제외하고는, 저항소자(21c) 상부의 영역의 층간 절연막(27)의 표면으로부터 제1질화막(29) 및 제2질화막(33)이 제거되어 있다. 또한, 제1질화막(29) 및 제2질화막(33)은 p-채널 MOS 트랜지스터 상부의 영역으로부터 제거되어 있음에 유의해야 한다.

본 실시예에서는, 제1질화막(29) 및 제2질화막(33)이 p-채널 MOS 트랜지스터 상부의 영역으로부터 제거되어 있으며, p-채널 MOS 트랜지스터의 게이트 산화막 계면에 존재하는 트랩 준위를 안정화시키는 것이 가능해진다. 이에 따라, p-채널 MOS 트랜지스터에 대한 임계 특성의 제어성의 열화가 회피된다.

도 8은 도 7의 저항소자(21a, 21b 및 21c)에 대한 다결정 실리콘 패턴(23)의 저항값을 도시하는 도면이고, 가로축은 저항소자(21a, 21b 및 21c)를 나타내고, 세로축은 Ω/□에 의하여 각각의 다결정 실리콘 패턴의 저항값을 나타낸다.

이러한 구성을 갖는 제1금속 배선층 패턴(31) 바로 아래의 제1질화막(29)을 제외하고는, 제1배선층(31) 주위의 제1질화막(29) 및 제2질화막(33)이 저항소자(21c) 상부의 제1금속 배선층 패턴(31)의 근처에서 제거되어 있으므로, 저항소자(21c)의 다결정 실리콘 패턴(23)이 저항소자(21a 및 21b)의 다결정 실리콘 패턴(23)과 동일한 불순물 농도 레벨을 가지더라도, 저항소자(21c)를 구성하는 다결정 실리콘 저항체(23)에 대한 저항값을 변화시키는 것이 가능해진다.

도 9는, 제1질화막(29)의 두께를 변화시키는 경우에 대하여, 도 7의 저항소자(21a, 21b 및 21c)에 대한 다결정 실리콘 저항체(23)의 저항값을 도시한 것이며, 가로축은 제1질화막(29)의 두께를 나타내고, 세로축은 Ω/□에 의하여 다결정 실리콘 저항체(23)의 저항값을 나타낸다.

제1질화막(29)의 두께를 변화시킴으로써, 저항소자(21a 및 21b)에 대해 동일한 저항값을 유지하면서, 저항소자(21c)의 저항을 선택적으로 변화시키는 것이 가능하다.

제2질화막(33)을 형성하기 위한 도 2e의 단계에서 제2질화막(33)을 형성한 이후에, 그리고, 그 위에 층간 절연막(35)을 형성하는 단계 이전에, 포토리소그래피 및 에칭에 의해 제2질화막(33) 및 제1질화막(29)을 선택적으로 제거함으로써, 도 7의 실시예에 따른 반도체장치가 형성될 수 있음에 유의해야 한다.

## [제 3 실시예]

도 10은 본 발명의 제3실시예에 따른 반도체장치를 도시하는 단면도이며, 앞서 설명한 부품에 대응하는 부품은 동일한 참조 번호에 의해 표시되고, 그 설명은 생략한다.

본 실시예에서, 층간 절연막(35)은, 그 막(35)의 하부 측으로부터 상부 측으로 순서대로 TEOS막(35a), SOG막(35b) 및 TEOS막(35c)을 적층한 적층 구조를 가지며, 제1금속 배선층 패턴(31)의 상부 표면을 피복하는 제2질화막(33)은 본 실시 예에서 제거되어 있음에 유의해야 한다. 제2질화막(33)의 제거는 SOG막(35)의 에치백 처리시에 달성될 수 있다.

이 실시예에서는, SOG막(35b)이 제1금속 배선층 패턴(31)의 상부 표면으로부터 제거되어 있으며, 제1금속 배선층 패턴 (31)을 제2금속 배선층 패턴(37)과 전기적으로 확실하게 접속하기 위한 관통 홀을 형성하는 것이 가능해지고, 제1금속 배선층 패턴(31)과 제2금속 배선층 패턴(37) 사이의 불량한 전기 접촉이 방지될 수 있다. 또한, 층간 절연막(35)의 평탄성이 향상된다.

또한, 제1금속 배선층 패턴(31)의 아래에 제1질화막(29)이 존재함으로 인해, 다결정 실리콘 저항체(23)의 저항값의 변화 또는 MOS 트랜지스터의 임계 전압의 변동이 효과적으로 방지될 수 있다. 또한, 제1질화막(29) 및 제2질화막(33)의 두께를 독립적으로 제어하는 것이 가능하므로, 다결정 실리콘 저항체(23)의 의도하는 저항값에 따라, 제1 및 제2질화막(29 및 33)의 막 두께를 최적화하는 것이 가능하다.

또한, 본 실시예에서는, 도 7을 참조하여 설명한 실시예와 유사하게, 제1질화막(29) 및 제2질화막을 선택적으로 제거하는 것이 가능하다. 이것에 의하여, 도 7을 참조하여 설명한 것과 동일한 효과가 달성된다.

#### [제 4 실시예]

도 11은 본 발명의 제4실시예에 따른 반도체장치를 도시하는 단면도이며, 앞서 설명한 부품은 동일한 참조 번호에 의해 표시되고, 그 설명은 생략한다.

이 실시예에서는, 저항소자(21)와 p-채널 및 n-채널 MOS 트랜지스터 상에,  $5\sim80$ nm 두께의 열 산화막(41)이 형성되어 있다. 또한, 열 산화막(41) 상에는,  $5\sim30$ nm 두께의 제3질화막(43)이 저항소자(21)와 n-채널 MOS 트랜지스터를 피복하 도록 형성되어 있으며, p-채널 MOS 트랜지스터가 형성되어 있는 영역에는 제3질화막(43)이 형성되지 않는다. 그러나, 이 것은 p-채널 MOS 트랜지스터 상에 제3질화막(43)을 형성하는 것이 금지되는 것을 의미하지는 않으며, p-채널 MOS 트랜지스터 상에도 제3질화막(43)을 형성하는 것이 가능하다.

본 실시예에서는, 제3질화막(32)의 형성에 의해,  $n^+$ -형의 다결정 실리콘 게이트 전극(11) 또는  $p^+$ -형의 다결정 실리콘 게이트 전극(13)과 다결정 실리콘 저항체(23)로의 수소 분자의 확산을 억제하는 것이 가능해지고, 다결정 실리콘 패턴에 대한 저항값의 안정성이 향상된다.

또한, p-채널 MOS 트랜지스터 상에는 제3질화막(43)이 형성되지 않으므로, p-채널 트랜지스터에 대한 트랩 준위의 형성이 안정화되고, p-채널 MOS 트랜지스터의 임계 전압 제어성에 있어서의 열화가 발생하지 않는다.

또한, 본 실시예에서는, 도 7을 참조하여 설명한 제2실시예와 유사하게, 소정의 영역으로부터 제1질화막(29) 및 제2질화막(33)이 제거되도록 구성하는 것이 가능하다. 이것에 의하여, 도 7의 실시예와 유사한 효과가 본 실시예에서도 달성된다.

#### [제 5 실시예]

도 12는 본 발명의 제5실시예를 도시하는 단면도이며, 도 1을 참조하여 앞서 설명한 부품은 동일한 참조 번호에 의해 표시되고, 그 설명은 생략한다.

p-형 웰 영역(3)에는, 한 쌍의 n-형 확산 영역(17)이 각각 형성된 4개의 MOS 트랜지스터 영역이 제공된다. 또한, 각 쌍의 확산 영역(17) 사이에는, 각각의 게이트 산화막(9)을 통해, 인(P)이 도핑된 n<sup>-</sup>-형의 게이트 전극(45), 인(P)이 도핑된 n<sup>-</sup>-형의 게이트 전극(47), 인(P)이 도핑된 n<sup>+</sup>-형의 게이트 전극(49) 및 붕소(B)가 도핑된 p<sup>-</sup>-형의 게이트 전극(49)이 제공된다. 전형적인 예에서는, 게이트 전극(45, 47, 49 및 51)의 불순물 농도가 각각  $7\times10^{18}\sim5\times10^{19}/\text{cm}^3$ ,  $7\times10^{18}\sim5\times10^{19}/\text{cm}^3$ ,  $2\times10^{19}\sim1\times10^{20}/\text{cm}^3$  및  $1\times10^{18}\sim2\times10^{19}/\text{cm}^3$ 로 설정된다.

또한, n-형 웰 영역(5)에는, 한 쌍의 p-형 확산 영역(19)이 형성되고, 게이트 산화막(9)을 통해, 확산 영역(19) 사이에 인 (P)이 도핑된 n<sup>+</sup>-형의 게이트 전극(53)이 형성된다. 게이트 전극(53)은  $1\times10^{20}/\mathrm{cm}^3$  이상의 농도 레벨로 도핑될 수도 있다.

이들 트랜지스터의 채널 영역에 대하여 서로 동일하게 불순물 농도 레벨을 설정함으로써, 게이트 전극에서의 불순물 농도 레벨의 차이를 반영하는 일함수의 차이를 이용하여, 온도 특성 및 임계 전압의 변동성이 감소된 전압 발생회로를 구현하는 것이 가능해진다.

도 13은 인(P)이 도핑된 게이트 전극을 갖는 n-채널 MOS 트랜지스터의 게이트 전극의 저항값과 임계 전압 사이의 관계를 도시한 것이다. 도 13에서, 가로축은 게이트 전극의 저항값(kΩ/□)을 나타내고, 세로축은 임계 전압 Vth(V)를 나타낸다.

도 13을 참조하면, 게이트 전극의 저항값의 변화는 n-채널 MOS 트랜지스터의 임계 전압에 대해 큰 효과를 제공함을 알 수있다.

이 실시예에서는, 제1질화막(29) 및 제2질화막(33)의 양자가 도 1의 실시예와 유사하게 형성되며, 다결정 실리콘 패턴의 저항값을 동일하게 설정하는 것이 가능해진다. 따라서, 다결정 실리콘 패턴의 저항값을 제어하면서, 다결정 실리콘 패턴의 상부에 제1금속 배선층 패턴을 배치하는 것이 가능해진다.

또한, 이 실시예에서는, 도 7을 참조하여 설명한 실시예와 유사하게, 소정의 영역으로부터 제1질화막 및 제2질화막(33)을 선택적으로 제거하는 것이 가능하다. 이것에 의하여, 도 7의 실시예의 경우와 유사한 효과가 달성된다.

본 발명의 반도체장치를 구성하는 금속 박막 저항소자는 예를 들어, 아날로그 회로를 갖는 반도체장치에서 사용될 수 있다. 이하, 이러한 금속 박막 저항을 사용하는 아날로그 회로를 갖는 반도체장치의 실시예에 대해 설명한다.

도 14는 정전압 발생기를 구성하는 아날로그 회로를 갖는 반도체장치의 일 실시예를 도시하는 회로도이다.

도 14를 참조하면, DC 전원(75)으로부터의 안정된 전원을 부하(77)에 공급하기 위한 정전압 발생기(79)가 제공된다. 이에 따라, 정전압 발생기(79)는, DC 전원(75)이 접속되는 입력단자(Vbat)(81), 기준전압 발생기(Vref)(83), 연산 증폭기(비교기)(85), 출력 드라이버를 구성하는 p-채널 MOS 트랜지스터(이하, 'PMOS'라 함)(87), 전압 분할기 R1 및 R2, 출력단자 (Vout)(39)를 포함하는 것에 유의해야 한다.

정전압 발생기(79)의 연산 증폭기(85)에서는, 그 출력단자가 PMOS(87)의 게이트 전극에 접속되고, 기준전압 발생기(83)의 기준전압 Vref는 그 반전 입력단자(-)에 공급된다. 또한, 출력전압 Vout을 저항소자 R1 및 R2에 의해 분할하여 얻어진 전압은 그 비반전 입력단자 (+)에 공급되고, 저항소자 R1 및 R2에 의해 분할된 전압은 기준전압 Vref와 동일해지도록 제어된다.

도 15는 아날로그 전압 검출기를 갖는 반도체장치의 일 실시예를 도시하는 회로도이다.

도 15를 참조하면, 전압 검출기(91)는 기준전압 발생기(83)에 접속된 반전 입력단자 (-)를 갖는 연산 증폭기(85)를 포함하고, 반전 입력단자에는 기준전압 발생기(83)로부터의 기준전압 Vref가 공급된다. 또한, 전압 검출을 위해 공급되는 입력단자(93)의 전압은 저항 R1 및 R2에 의해 분할되고, 분할된 전압은 연산 증폭기(85)의 비반전 입력단자 (+)에 공급된다. 연산 증폭기(85)의 출력은 출력단자(Vout)(95)를통해 출력된다.

이러한 전압 검출기(91)에서는, 전압 검출을 위한 입력단자의 입력전압이 높고 저항 R1 및 R2에 의해 분할된 분할전압이 기준전압 Vref보다 높을 경우, 연산 증폭기(85)의 출력은 하이레벨 상태(H)를 유지하는 것에 유의해야 한다. 다른 한편으로, 측정할 전압이 하강하여 저항소자 R1 및 R2에 의해 분할된 전압이 기준전압 Vref 아래로 감소하면, 연산 증폭기(85)의 출력은 로우레벨 상태(L)로 된다.

일반적으로, 도 14의 정전압 발생기 또는 도 15의 전압 검출기는, 제조 공정에서의 변동에 의해 발생하는 기준전압 발생기의 기준전압 Vref의 변동을 고려하여, 전압 분할기를 구성하는 퓨즈소자에 의해 그 저항값을 변화시킬 수 있는 조정 가능한 저항회로(전압 분할기라고 함)를 이용함으로써, 전압 분할기를 구성하는 저항소자의 저항값을 조정한다.

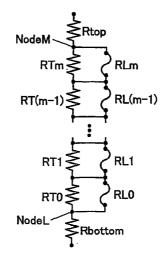

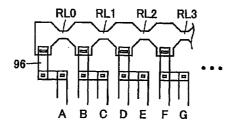

도 16은 본 발명의 박막 저항소자가 적용되는 전압 분할회로의 일례를 도시하는 회로도이다. 또한, 도 17 및 도 18은 전압 분할회로의 예를 도시하는 레이아웃 도면이며, 도 17은 퓨즈소자가 형성되어 있는 부분에 대한 레이아웃 예를 도시한 것이 고, 도 18은 저항소자가 형성되어 있는 레이아웃 예를 도시한 것이다.

도 16을 참조하면, 전압 분할회로는 저항소자 Rbttom 및 저항소자 Rtop 사이에 직렬로 접속된 m+ 1(m은 양의 정수) 개의 저항소자 RTO, RT1, ..., RTm을 포함하고, 각각의 저항소자 RTO, RT1, ..., RTm에 대하여 병렬로 퓨즈소자 RLO, RL1, ..., RLm이 제공된다.

도 17에 도시한 것과 같이, 퓨즈소자 RL0, RL1, ..., RLm은  $20\sim40\Omega$ 의 저항값을 갖는 다결정 실리콘 패턴으로 형성된다. 이에 따라, 저항소자 RT0, RT1, ..., RTm의 저항값은 저항소자 Rbottom으로부터 저항소자 Rtop의 방향으로 2의 배수로 증가하도록 설정되어 있다. 따라서, 저항소자 RTn의 저항값은 저항소자 RT0의 저항값보다 2n배 큰 값을 가진다.

예를 들어, 저항소자(21)를 이용하여, 단일 저항소자(21)가 저항소자 RT0을 구성하도록 전압 분할회로가 형성된다. 이에 따라, 저항소자 RTn은 2n개의 저항소자(21)에 의해 형성된다. 저항소자(21)로서는, 앞의 실시예에 의해 설명한 저항소자가 사용될 수 있다.

도 17 및 도 18에서는, A 및 A 사이의 부분, B 및 B 사이의 부분, C 및 C 사이의 부분, D 및 D 사이의 부분, F 및 F 사이의 부분과, G 및 G 사이의 부분이 금속 배선 패턴(96)에 의해 전기적으로 접속되어 있음에 유의해야 한다.

저항소자 사이의 저항값의 비율이 중요한 전압 분할회로에서는, 각 저항소자가 퓨즈소자에 의해 결합되어 단위 저항소자가 형성되고, 전압 분할회로는 복수의 단위 저항소자를 직렬로 접속하여 형성되며, 이와 같이 직렬로 접속된 단위 저항소자는 반도체기판에 사다리 형태로 배치된다.

이러한 구성의 전압 분할회로에서는, 퓨즈소자 RLO, RL1, ..., RLm을 레이저 빔에 의해 필요에 따라 절단함으로써, 의도하는 저항값을 달성하는 것이 가능하다.

본 발명의 반도체장치에서는, 다결정 실리콘 패턴의 저항값을 제어하면서, 다결정 실리콘 패턴의 상부에 금속 배선층 패턴을 자유롭게 배치하는 것이 가능해지며, 반도체장치의 설계 자유도가 매우 향상된다.

도 16의 전압 분할회로를 도 14의 정전압 발생기(79)의 저항소자 R1 및 R2에 적용할 경우, 저항소자 Rbottom의 일 단부는 접지되고, 저항소자 Rtop의 일 단부는 PMOS(87)의 드레인에 접속된다. 또한, 저항소자 Rbottom 및 미세조정(fine adjustment) 저항소자(99) 사이의 노드 NodeL, 또는 저항소자 Rtop 및 개략조정(coarse adjustment) 저항소자(97) 사이의 노드 NodeM는 연산 증폭기(85)의 비반전 입력단자에 접속된다.

금속 박막 저항 및 레이저 빔 차단막을 전압 분할기의 저항소자 R1 및 R2에 적용함으로써, 전압 분할회로의 자유도가 향상되므로, 정전압 발생기(79)의 출력전압을 안정화시키는 것이 가능해진다.

도 16의 전압 분할회로를 도 15에 도시된 전압 검출기(91)의 저항소자 R1 및 R2에 적용할 경우, 저항소자 Rbottom의 일 단부는 접지되고, 저항소자 Rtop의 일 단부는 입력단자(93)에 접속된다. 또한, 저항소자 Rbottom 및 미세조정 저항소자 (99) 사이의 노드 NodeL, 또는 저항소자 Rtop 및 개략조정 저항소자(97) 사이의 노드 NodeM는 연산 증폭기(85)의 비반 전 입력단자에 접속된다.

본 발명에 따른 전압 분할회로에서는, 전압 분할회로에 대한 설계의 자유도가 향상되므로, 전압 검출회로의 설계의 자유도를 증가시키는 것이 가능해진다.

도 14 내지 도 17을 참조하여, 반도체장치를 구성하는 다결정 실리콘 패턴을 사용하는 전압 분할회로가 적용되고 있는 전압 분할기를 갖는 반도체장치의 예에 대하여 설명하였지만, 이러한 전압 분할회로가 적용되는 반도체장치는 정전압 발생기를 갖는 반도체장치, 또는 전압 검출기를 갖는 반도체장치에 한정되는 것이 아니며, 본 발명은 전압 분할회로를 갖는 임의의 반도체장치에 적용될 수 있다.

또한, 본 발명을 구성하는 다결정 실리콘 패턴이 적용되는 반도체장치는 전압 분할회로를 갖는 반도체장치에 결코 한정되지 않으며, 본 발명은 금속 박막 저항을 갖는 임의의 반도체장치에 적용 가능하다.

또한, 본 발명은 여기서 설명한 실시예에 결코 한정되지 않으며, 발명의 범위에서 벗어나지 않고도 다양한 변동 및 변형이 이루어질 수 있다. 여기서 설명한 치수, 형상, 재료 및 배치는 단지 예를 들기 위한 것이라는 점에 유의해야 한다.

#### (57) 청구의 범위

# 청구항 1.

반도체기판;

절연막을 통해 상기 반도체기판 상에 형성된 다결정 실리콘 패턴;

상기 다결정 실리콘 패턴을 피복하도록 상기 반도체기판 상에 형성된 충간 절연막; 및

상기 층간 절연막 상에 형성된 금속 배선층 패턴을 포함하고,

상기 금속 배선층 패턴은 그 상부 표면, 하부 표면 및 측벽 표면 상에 각각 실리콘 질화막을 가지는 것인 반도체장치.

# 청구항 2.

제 1 항에 있어서, 상기 실리콘 질화막은, 상기 층간 절연막의 표면 상에 형성되며 상기 금속 배선층 패턴의 하부 표면과 접촉하는 제1질화막과, 상기 금속 배선층 패턴의 상기 측벽 표면 및 상부 표면을 피복하는 제2질화막을 포함하는 것인 반도체장치.

#### 청구항 3.

제 2 항에 있어서, 상기 제1질화막 및 상기 제2질화막은 각각 상이한 두께를 가지는 것인 반도체장치.

#### 청구항 4.

제 2 항에 있어서, 상기 금속 배선층 패턴의 아래에 배치된 상기 제1질화막을 제외하고, 상기 제1질화막 및 상기 제2질화막이 제거되어 있는 영역이 제공되는 것인 반도체장치.

# 청구항 5.

제 1 항에 있어서, 상기 반도체장치는 상기 다결정 실리콘 패턴으로 이루어진 게이트 전극을 갖는 p-채널 MOS 트랜지스터를 더 포함하고, 상기 p-채널 MOS 트랜지스터 상의 영역에는, 상기 금속 배선층 패턴, 상기 제1질화막 및 상기 제2질화막의 형성이 억제되는 것인 반도체장치.

# 청구항 6.

제 1 항에 있어서, 상기 다결정 실리콘 패턴 및 상기 충간 절연막 사이에는 적충막이 제공되고, 상기 적충막은 상기 다결정 실리콘으로부터 상기 충간 절연막의 방향으로 연속적으로 적충된 산화막 및 제3질화막을 포함하는 것인 반도체장치.

#### 청구항 7.

제 6 항에 있어서, 상기 반도체장치는 상기 다결정 실리콘 패턴의 게이트 전극을 갖는 p-채널 MOS 트랜지스터를 더 포함하고, 상기 p-채널 MOS 트랜지스터 상에는 상기 제3질화막이 형성되는 것인 반도체장치.

## 청구항 8.

공급되는 전압을 분할하여 출력전압을 생성하는 전압 분할회로를 갖는 반도체장치로서,

상기 전압 분할회로는 둘 이상의 저항소자를 포함하고, 상기 전압 분할기의 출력전압은 퓨즈소자의 절단에 의해 조정 가능하고,

상기 저항소자는 절연막을 통해 반도체기판 상에 형성된 다결정 실리콘 패턴을 포함하며,

상기 반도체기판 상에는, 상기 다결정 실리콘 패턴을 피복하도록 층간 절연막이 형성되며,

상기 층간 절연막 상에는 금속 배선층 패턴이 형성되며,

상기 금속 배선층 패턴은 그 상부 표면, 하부 표면 및 측벽 표면 상에 각각 실리콘 질화막을 가지는 것인 반도체장치.

#### 청구항 9.

공급되는 전압을 분할하여 출력전압을 생성하는 전압 분할회로;

기준전압을 공급하는 기준전압 발생기; 및

상기 전압 분할회로의 상기 출력전압과, 상기 기준전압 발생기의 상기 기준전압을 비교하는 비교회로를 포함하고,

상기 전압 분할회로는 둘 이상의 저항소자를 포함하고, 상기 전압 분할기의 상기 출력전압은 퓨즈소자의 절단에 의해 조정 가능하며,

상기 저항소자는 절연막을 통해 반도체기판 상에 형성된 다결정 실리콘 패턴을 포함하며,

상기 반도체기판 상에는, 상기 다결정 실리콘 패턴을 피복하도록 층간 절연막이 형성되며,

상기 층간 절연막 상에는, 금속 배선층 패턴이 형성되며,

상기 금속 배선층 패턴은 그 상부 표면, 하부 표면 및 측벽 표면 상에 각각 실리콘 질화막을 가지는 것인 반도체장치.

## 청구항 10.

입력전압의 출력을 제어하는 출력 드라이버;

상기 출력전압을 분할하여 분할전압을 생성하는 전압 분할회로;

기준전압을 생성하는 기준전압 발생기; 및

상기 전압 분할회로로부터의 상기 분할전압과 상기 기준전압 발생기로부터의 상기 기준전압을 비교하는 비교회로를 가지며, 상기 비교회로는 비교 결과에 응답하여 상기 출력 드라이버를 제어하는 것인 정전압 발생기를 포함하고,

상기 전압 분할회로는 둘 이상의 저항소자를 포함하고, 상기 전압 분할기의 상기 출력전압은 퓨즈소자의 절단에 의해 조정 가능하며.

상기 저항소자는 절연막을 통해 반도체기판 상에 형성된 다결정 실리콘 패턴을 포함하며,

상기 반도체기판 상에는, 상기 다결정 실리콘 패턴을 피복하도록 층간 절연막이 형성되며,

상기 층간 절연막 상에는, 금속 배선층 패턴이 형성되며,

상기 금속 배선층 패턴은 그 상부 표면, 하부 표면 및 측벽 표면 상에 각각 실리콘 질화막을 가지는 것인 반도체장치.

## 청구항 11.

절연막을 통해 반도체기판 상에 다결정 실리콘 패턴을 형성하는 단계;

상기 다결정 실리콘 패턴을 피복하도록, 상기 반도체기판 상에 충간 절연막을 형성하는 단계;

상기 층간 절연막 상에 제1질화막을 형성하는 단계;

상기 제1질화막 상에 금속 배선층 패턴을 형성하는 단계; 및

상기 금속 배선층을 피복하도록, 상기 제1질화막 상에 제2질화막을 형성하는 단계를 포함하는 반도체장치의 제조방법.

# 청구항 12.

제 11 항에 있어서, 상기 제2질화막을 형성하는 단계 이후에, 소정의 영역으로부터 상기 제2질화막 및 상기 제1질화막을 선택적으로 제거하는 단계를 더 포함하는 것인 반도체장치의 제조방법.

도면2a

도면2b

도면2c

# 도면2d

도면2e

도면3

도면7

도면8

저항값 (Ω/ロ)

도면11

도면14

도면15

도면17

도면18