# (19) **日本国特許庁(JP)**

# (12)公開特許公報(A)

(11)特許出願公開番号

特開2006-211737 (P2006-211737A)

(43) 公開日 平成18年8月10日 (2006.8.10)

(51) Int.C1. F I テーマコード (参考) **HO2H 9/02 (2006.01)** HO2H 9/02 E 5GO13

**GO5F** 1/10 (2006.01) HO2H 9/02 E 5GO13

### 審査請求 有 請求項の数 6 OL (全 9 頁)

| 特願2005-16398 (P2005-16398)<br>平成17年1月25日 (2005.1.25) | (71) 出願人                              | 000006507<br>横河電機株式会社             |  |  |

|------------------------------------------------------|---------------------------------------|-----------------------------------|--|--|

|                                                      |                                       | 東京都武蔵野市中町2丁目9番32号                 |  |  |

|                                                      | (72) 発明者                              | 青山 公英                             |  |  |

|                                                      |                                       | 東京都武蔵野市中町2丁目9番32号 横               |  |  |

|                                                      |                                       | 河電機株式会社内                          |  |  |

|                                                      | (72) 発明者                              | 関野 宏美                             |  |  |

|                                                      |                                       | 東京都武蔵野市中町2丁目9番32号 横               |  |  |

|                                                      | 河電機株式会社内                              |                                   |  |  |

|                                                      | Fターム (参                               | 考) 5G013 AA02 BA01 CA10           |  |  |

|                                                      | ·                                     | 5H410 BB05 CC02 EA11 EB01 EB21    |  |  |

|                                                      |                                       | FF03 FF22 GG05 LL06               |  |  |

|                                                      |                                       |                                   |  |  |

|                                                      |                                       |                                   |  |  |

|                                                      | · · · · · · · · · · · · · · · · · · · | 平成17年1月25日 (2005. 1. 25) (72) 発明者 |  |  |

### (54) 【発明の名称】過電流制限回路

# (57)【要約】

【課題】 過電流発生時の発熱による素子の損傷を防止すると共に1故障が発生しても確実に過電流の制限が可能な過電流制限回路を実現する。

【解決手段】 過電流を制限する過電流制限回路において、外部電源の出力電圧が一端にそれぞれ接続される第1及び第2の抵抗と、第2の抵抗の他端に接続される第3の抵抗と、第1の抵抗の他端がソース端子に接続され、ドレイン端子が外部負荷に接続され、第2及び第3の抵抗の接続点がゲート端子に接続される電界効果トランジスタと、第1の抵抗の他端が接続され第1の抵抗における電圧降下を監視して過電流が流れていると判断した場合に電圧効果トランジスタをオフにする信号を出力する第1及び第2の電流制限手段と、これら第1及び第2の電流制限手段と、これら第1及び第2の電流制限手段の何れかの出力が電圧効果トランジスタをオフにする信号である場合に第3の抵抗の他端をハイインピーダンスにする論理回路とを設ける。

【選択図】

図 1

#### 【特許請求の範囲】

### 【請求項1】

過電流を制限する過電流制限回路において、

外部電源の出力電圧が一端にそれぞれ接続される第1及び第2の抵抗と、

前記第2の抵抗の他端に接続される第3の抵抗と、

前記第1の抵抗の他端がソース端子に接続され、ドレイン端子が外部負荷に接続され、前記第2及び前記第3の抵抗の接続点がゲート端子に接続される電界効果トランジスタと

前記第1の抵抗の他端が接続され前記第1の抵抗における電圧降下を監視して過電流が流れていると判断した場合に前記電圧効果トランジスタをオフにする信号を出力する第1 及び第2の電流制限手段と、

これら第1及び第2の電流制限手段の何れかの出力が前記電圧効果トランジスタをオフにする信号である場合に前記第3の抵抗の他端をハイインピーダンスにする論理回路と を備えたことを特徴とする過電流制限回路。

### 【請求項2】

前記第1の電流制限手段が、

前記第1の抵抗における電圧降下をディジタル信号に変換するA/D変換回路と、

この A / D 変換回路の出力を取り込み予め設定されている過電流検出のための閾値とを比較し、比較結果によって過電流が流れていると判断した場合には前記電圧効果トランジスタをオフにする信号を出力する制御回路と

から構成されることを特徴とする

請求項1記載の過電流制限回路。

### 【請求項3】

前記第2の電流制限手段が、

ラッチ回路と、

前記第1の抵抗における電圧降下を予め設定されている過電流検出のための閾値とを比較し、比較結果によって過電流が流れていると判断した場合には前記ラッチ回路から前記電圧効果トランジスタをオフにする信号を出力させるレベル比較回路と

から構成されることを特徴とする

請求項1記載の過電流制限回路。

### 【請求項4】

前記制御回路が、

定周期、或いは、任意のタイミングで前記ラッチ回路の状態をクリアすることを特徴と する

請求項2記載の過電流制限回路。

### 【請求項5】

前記外部負荷に電流を供給するソース型の回路構成であることを特徴とする請求項1乃至請求項4のいずれかに記載の過電流制限回路。

#### 【請求頃6】

前記外部負荷から流れ出す電流を取り込むシンク型の回路構成であることを特徴とする 40請求項1乃至請求項4のいずれかに記載の過電流制限回路。

【発明の詳細な説明】

### 【技術分野】

### [0001]

本発明は、外部負荷の短絡等に起因して生じる過電流を制限する過電流制限回路に関し、特に過電流発生時の発熱による素子の損傷を防止すると共に1故障が発生しても確実に過電流の制限が可能な過電流制限回路に関する。

### 【背景技術】

### [0002]

従来の外部負荷の短絡等に起因して生じる過電流を制限する過電流制限回路に関連する

20

10

30

先行技術文献としては次のようなものがある。

#### [0003]

【特許文献 1 】特開平 0 5 - 1 2 2 8 3 9 号公報

【特許文献2】特開平05-211715号公報

【特許文献3】特開平06-232646号公報

【特許文献4】特開平08-149684号公報

【特許文献 5 】特開 2 0 0 0 - 0 1 3 9 9 1 号公報

【特許文献 6 】特開 2 0 0 0 - 0 9 2 8 2 3 号公報

#### [0004]

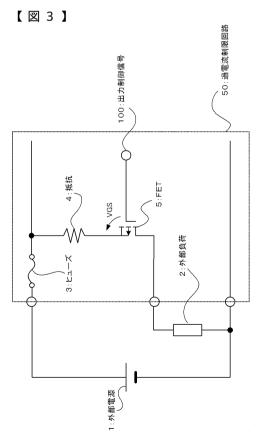

図3はこのような従来の過電流制限回路の一例を示す構成回路図である。図3において 1は外部電源、2は外部負荷、3はヒューズ、4は外部負荷2に流れる電流を検出する抵 抗、 5 は過電流を制限する F E T (Feild Effect Transistor:電界効果型トランジスタ :以下、単にFETと呼ぶ。)、100は過電流の制限電流を制御する出力制御信号であ る。また、3,4及び5は過電流制限回路50を構成している。

#### [00005]

外 部 電 源 1 の 一 端 は ヒュ ー ズ 3 を 介 し て 抵 抗 4 の 一 端 に 接 続 さ れ 、 外 部 電 源 1 の 他 端 は 外部負荷2の一端に接続される。抵抗4の他端はFET5のソース端子に接続され、FE T5のドレイン端子は外部負荷2の他端に接続される。また、FET5のゲート端子には 出力制御信号100が印加される。

### [0006]

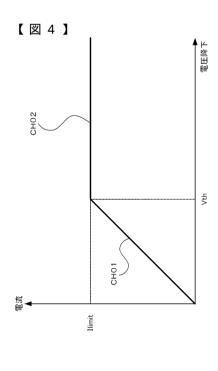

ここで、図3に示す従来例の動作を図4を用いて説明する。図4は抵抗4における電圧 降下と流れる電流の関係を示す特性曲線図である。図4中 " C H 0 1 " に示すように流れ る電流の値に比例して抵抗4における電圧降下の値も増加して行く。

#### [0007]

そして、図 4 中 " C H 0 2 "に示すように抵抗 4 における電圧降下の値が図 4 中 " V t h " に示す閾値を超えると、流れる電流は図4中 " Ilimt " のように制限される。

### [00008]

例えば、外部電源1の出力電圧値を "Vcc ",外部制御信号100の電圧値を "Vc tr"、FET5のカットオフ電圧を"VGS"とした場合、

> Vth = Vcc - (Vref + VGS)(1)

で 求 め ら れ る 閾 値 を 抵 抗 4 に お け る 電 圧 降 下 の 値 が 超 過 し た 場 合 に 、 流 れ る 電 流 は 図 4 中 "Ilimit"のように制限される。

#### [0009]

すなわち、外部負荷2の短絡等に起因して過電流が抵抗4に流れた場合、抵抗4におけ る電圧降下によってFET5を "ON"させるためのカットオフ電圧 "VGS"を維持で きなくなってFET5は " OFF " になり、過電流制御回路50は、図4中 " Ilimi t "の電流値以上の電流が流れないように制御することが可能になる。

### 【発明の開示】

【発明が解決しようとする課題】

### [0010]

しかし、図3に示す従来例では、過電流発生によって流れる電流を制限した場合であっ ても、図4中"Ⅰlimit"に示すような電流が常時流れているので、図4中"Ⅰli mit "に示す制限電流の値によっては発熱によりFET5等の素子を損傷してしまう危 険性があると言った問題点があった。

#### [ 0 0 1 1 ]

また、出力制御信号100の電圧値の異常やFET5の動作不良等の不具合が発生した 場合には過電流の制限が確実に動作しなくなってしまうと言った問題点があった。特に、 過 電 流 制 限 回 路 5 0 が プ ロ セ ス 制 御 機 器 に 適 用 さ れ て い た 場 合 に は 、 1 故 障 に よ っ て 過 電 流の制限が出来なくなってしまうことはプロセス制御機器の信頼性が低下して重要な問題 となってしまう。

20

従って本発明が解決しようとする課題は、過電流発生時の発熱による素子の損傷を防止すると共に1故障が発生しても確実に過電流の制限が可能な過電流制限回路を実現することにある。

【課題を解決するための手段】

#### [ 0 0 1 2 ]

このような課題を達成するために、本発明のうち請求項1記載の発明は、

過電流を制限する過電流制限回路において、

外部電源の出力電圧が一端にそれぞれ接続される第1及び第2の抵抗と、前記第2の抵抗の他端に接続される第3の抵抗と、前記第1の抵抗の他端がソース端子に接続され、ドレイン端子が外部負荷に接続され、前記第2及び前記第3の抵抗の接続点がゲート端子に接続される電界効果トランジスタと、前記第1の抵抗の他端が接続され前記第1の抵抗における電圧降下を監視して過電流が流れていると判断した場合に前記電圧効果トランジスタをオフにする信号を出力する第1及び第2の電流制限手段と、これら第1及び第2の電流制限手段の何れかの出力が前記電圧効果トランジスタをオフにする信号である場合に前記第3の抵抗の他端をハイインピーダンスにする論理回路とを備えたことにより、発熱による素子の損傷を防止することが可能になり、1故障が発生しても確実に過電流を制限することが可能になる。

### [0013]

請求項2記載の発明は、

請求項1記載の発明である過電流制限回路において、

前記第1の電流制限手段が、

前記第1の抵抗における電圧降下をディジタル信号に変換するA/D変換回路と、このA/D変換回路の出力を取り込み予め設定されている過電流検出のための閾値とを比較し、比較結果によって過電流が流れていると判断した場合には前記電圧効果トランジスタをオフにする信号を出力する制御回路とから構成されることにより、発熱による素子の損傷を防止することが可能になる。

### [ 0 0 1 4 ]

請求項3記載の発明は、

請求項1記載の発明である過電流制限回路において、

前記第2の電流制限手段が、

ラッチ回路と、前記第 1 の抵抗における電圧降下を予め設定されている過電流検出のための閾値とを比較し、比較結果によって過電流が流れていると判断した場合には前記ラッチ回路から前記電圧効果トランジスタをオフにする信号を出力させるレベル比較回路とから構成されることにより、発熱による素子の損傷を防止することが可能になる。

### [0015]

請求項4記載の発明は、

請求項2記載の発明である過電流制限回路において、

前記制御回路が、

定周期、或いは、任意のタイミングで前記ラッチ回路の状態をクリアすることにより、 その後過電流が検出されなければ正常状態に復帰し、もし、過電流が継続して検出されれ ば再び電流を " O F F " にする動作を繰り返すことになる。

#### [0016]

請求項5記載の発明は、

請求項1乃至請求項4のいずれかに記載の発明である過電流制限回路において、

前記外部負荷に電流を供給するソース型の回路構成であることにより、発熱による素子の損傷を防止することが可能になる。

### [0017]

請求項6記載の発明は、

請求項1乃至請求項4のいずれかに記載の発明である過電流制限回路において、

前記外部負荷から流れ出す電流を取り込むシンク型の回路構成であることにより、発熱

20

30

40

による素子の損傷を防止することが可能になる。

### 【発明の効果】

#### [0018]

本発明によれば次のような効果がある。

請求項1,2,3,5及び請求項6の発明によれば、電流検出用の抵抗における電圧降下を監視して過電流が流れていると判断した場合に論理回路の出力をハイインピーダンスにすることで、FETのゲート端子を外部電源の電圧値と同電位にして確実に"OFF"にすることにより、制御信号を"High"に戻さない限り、或いは、ラッチ信号がクリアされない限りFET等の素子に流れる電流は"0"になるので、発熱による素子の損傷を防止することが可能になる。

### [0019]

また、電流検出用の抵抗における電圧降下を監視する第1の電流制限手段と、第2の電流制限手段との2系統の電流制限手段を設けることにより、1故障が発生しても確実に過電流を制限することが可能になる。

### [0020]

また、請求項4の発明によれば、制御回路が、定周期、或いは任意のタイミングでラッチ回路の状態をクリアすることにより、その後過電流が検出されなければ正常状態に復帰し、もし、過電流が継続して検出されれば再び電流を "OFF"にする動作を繰り返すことになる。

# 【発明を実施するための最良の形態】

#### [0021]

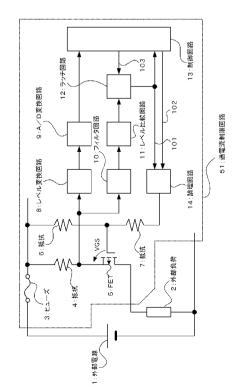

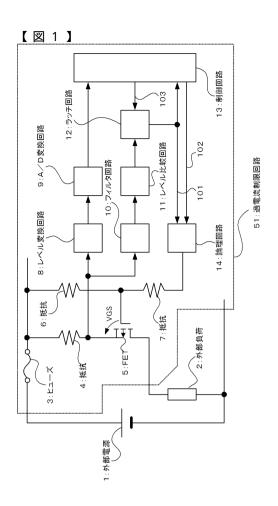

以下本発明を図面を用いて詳細に説明する。図1は本発明に係る過電流制限回路の一実施例を示す構成プロック図である。

#### [0022]

図1において1,2,3,4及び5は図3と同一符号を付してあり、6及び7は分圧用の抵抗、8は抵抗4で検出される電圧降下値のレベルを変換するレベル変換回路、9はアナログ信号をディジタル信号に変換するA/D変換回路、10はノイズ成分を除去するRCフィルタ等のフィルタ回路、11は抵抗4で検出される電圧降下値のレベルを閾値と比較するレベル比較回路、12はレベル比較回路11の出力をラッチして出力するラッチ回路、13はCPU(Central Processing Unit)等のファームウェアにより制御動作を行う制御回路、14は論理回路、101はラッチ回路12の出力であるラッチ信号、102は制御回路からの制御信号、103は制御回路13からのクリア信号である。

### [0023]

また、3,4,5,6,7,8,9,10,11,12,13及び14は過電流制限回路51を、8,9及び13は制御手段13に組み込まれたファームウェアで動作する第1の電流制限手段、10,11及び12はハードウェアのみで動作する第2の電流制限手段をそれぞれ構成している。

### [0024]

外部電源1の一端はヒューズ3を介して抵抗4及び抵抗6の一端に接続され、外部電源1の他端は外部負荷2の一端に接続される。抵抗4の他端はFET5のソース端子、レベル変換回路8及びフィルタ回路10にそれぞれ接続され、FET5のドレイン端子は外部負荷2の他端に接続される。また、抵抗6の他端はFET5のゲート端子及び抵抗7の一端にそれぞれ接続される。

# [0025]

レベル変換回路 8 の出力は A / D 変換回路 9 に接続され、 A / D 変換回路 9 の出力は制御回路 1 3 に接続される。一方、フィルタ回路 1 0 の出力はレベル比較回路 1 1 に接続され、レベル比較回路 1 1 の出力はラッチ回路 1 2 に接続される。

#### [0026]

ラッチ回路12の出力であるラッチ信号101は制御回路13及び論理回路14の一方の入力端子にそれぞれ接続され、制御回路13からの制御信号102は論理回路14の他

10

20

30

40

20

30

40

50

方の入力端子に接続される。最後に、制御回路13からのクリア信号103がラッチ回路 12のクリア端子に接続され、論理回路14の出力が抵抗7の他端に接続される。

[0027]

ここで、図1に示す実施例の動作を図2を用いて説明する。図2は論理回路14の動作を示す真理値表である。図2において、ラッチ信号101が"Low"の場合は異常状態(過電流検出)、ラッチ信号101が"High"の場合は正常状態として定義される。また、制御信号102が"Low"の場合はFET5のON制御を行うものと定義される。

[0028]

すなわち、正常状態(言い換えれば、過電流が流れていない状態)では論理回路14の出力は或る所定電圧値となり、分圧用の抵抗6及び抵抗7によって外部電源1の電圧値(例えば、Vcc)と前記所定電圧値との電位差が分圧されてFET5のゲート端子に印加される。

[0029]

このとき、FET5のカットオフ電圧 "VGS"が十分確保されるように、分圧用の抵抗 6 及び抵抗 7 の抵抗値や前記所定電圧値を適宜選択すると共にラッチ信号 1 0 1 及び制御信号 1 0 2 をそれぞれ " High "にしておくことにより図 2 示す真理値表から論理回路 1 4 が前記所定電圧値を出力し、FET5が "ON"になって外部負荷 2 に対して外部電源 1 からの電流が供給される。

[0030]

一方、前記第1の電流制限手段では、外部負荷2に流れる電流で抵抗4に生じた電圧降下はレベル変換回路8で後段のA/D変換回路9の入力レベルに適合した値に変換され、A/D変換回路9は入力されるアナログ信号をディジタル信号に変換されて制御回路13に供給される。

[0031]

そして、制御回路13はA/D変換回路9からのディジタル信号(具体的には、抵抗4における電圧降下の値)と予め設定されている過電流検出のための閾値とを比較し、もし、制御回路13は比較結果によって過電流が流れていると判断した場合には制御信号102を"Low(FET5をOFFにする信号)"にする。

[ 0 0 3 2 ]

この場合、図 2 に示す真理値表( 1 行目及び 3 行目)から分かるように、論理回路 1 4 の出力は " O N (前記所定電圧値) "から"ハイインピーダンス状態"に遷移する。

[0033]

論理回路14の出力が"ハイインピーダンス状態 "になるとFET5のゲート端子は外部電源の電圧値(例えば、Vcc)と同電位となってしまい、カットオフ電圧 "VGS "を維持することが不可能になり "OFF "になる。

[0034]

このとき、FET5は制御回路13が制御信号102を"High"に戻さない限り" OFF"が継続、言い換えれば、FET5等の素子に流れる電流は"0"になるので、発 熱による素子の損傷を防止することが可能になる。

[0035]

他方、前記第2の電流制限手段では、外部負荷2に流れる電流で抵抗4に生じた電圧降下はフィルタ回路10でノイズ成分等を除去され、後段のレベル比較回路11に供給される。レベル比較回路11はフィルタ回路10からの信号(具体的には、抵抗4における電圧降下の値)と予め設定されている過電流検出のための閾値とを比較し、もし、レベル比較回路11は比較結果によって過電流が流れていると判断した場合にはラッチ回路12の出力であるラッチ信号101を"Low(FET5をOFFにする信号)"にさせる。

[0036]

この場合、図 2 に示す真理値表( 1 行目及び 2 行目)から分かるように、論理回路 1 4 の出力は " O N (前記所定電圧値) "から"ハイインピーダンス状態"に遷移する。

20

30

40

50

[0037]

論理回路14の出力が"ハイインピーダンス状態 "になるとFET5のゲート端子は外部電源の電圧値(例えば、Vcc)と同電位となってしまい、カットオフ電圧 "VGS"を維持することが不可能になり"OFF"になる。

[0038]

このとき、FET5はラッチ回路12のラッチ信号101がクリアされない限り "OFF"が継続、言い換えれば、FET5等の素子に流れる電流は "0 "になるので、発熱による素子の損傷を防止することが可能になる。

[0039]

また、制御回路13は、ラッチ回路12の出力であるラッチ信号101の状態を監視して"Low"であると判断した場合には、自らの制御信号102を"Low"するように動作する。

[0040]

また、制御回路13は上位ホスト(図示せず。)からの命令によってラッチ回路12の 状態をクリア(言い換えれば、"High"に戻す。)することが可能である。

[0041]

この結果、電流検出用の抵抗4における電圧降下を監視して過電流が流れていると判断した場合にラッチ信号または制御信号を "Low"にすることで、FET5のゲート端子を外部電源の電圧値(例えば、Vcc)と同電位にして確実に"OFF"にすることにより、FET5等の素子に流れる電流は"0"になるので、発熱による素子の損傷を防止することが可能になる。

[0042]

また、電流検出用の抵抗4における電圧降下を監視する第1の電流制限手段と、第2の電流制限手段との2系統の電流制限手段を設けることにより、1故障が発生しても確実に過電流を制限することが可能になる。

[0043]

なお、図1に示す実施例では説明の簡単のために、第1の電流制限手段の構成要素としてレベル変換回路8を例示しているが、レベル変換回路8は必須の構成要素ではない、同様に、第2の電流制限手段の構成要素として例示したフィルタ回路10もまた必須の構成要素ではない。

[0044]

また、図1に示す実施例ではFET5から外部負荷2に電流を供給するソース型の回路構成を例示しているが、勿論、外部負荷2から流れ出す電流を取り込むシンク型の回路構成にすることも容易である。

[0045]

また、図1に示す実施例では過電流を検出した場合に、説明の簡単のために、例えば、第1及び第2の電流制限手段が"Low(FET5をOFFにする信号)"を出力している旨例示しているが、勿論、FET5をOFFにする信号として"High "として定義して過電流を検出した場合に、第1及び第2の電流制限手段が"High(FET5をOFFにする信号)"を出力しても構わない。

[0046]

また、図1に示す実施例では過電流を検出するとFET5のゲート端子を外部電源の電圧値(例えば、Vcc)と同電位にして確実に "OFF"にして状態を維持しているが、制御回路13が、定周期、或いは、任意のタイミングでラッチ回路12の状態をクリアすることも可能である。

[0047]

この場合には、その後過電流が検出されなければ正常状態に復帰し、もし、過電流が継続して検出されれば再び電流を "OFF"にする動作を繰り返すことになる。

[0048]

また、ヒューズ3と電流検出用の抵抗4との間に別途スイッチ回路を備え、ラッチ信号

1 0 1 若しくは制御信号 1 0 2 によって当該スイッチ回路の " O N / O F F "を制御することにより、さらに確実に過電流の制限が可能になる。また、この場合には、 1 故障によって O N 固着となる不具合も防止することができる。

#### [0049]

複数出力を有するモジュールを構成する場合には、ラッチ回路12を共通化することが可能であり、A/D変換回路9に関してもマルチプレクサ等で時分割で電圧降下の値を監視することによりA/D変換回路を共通化することも可能である。

# 【図面の簡単な説明】

- [0050]

- 【図1】本発明に係る過電流制限回路の一実施例を示す構成ブロック図である。

- 【図2】論理回路の動作を示す真理値表である。

- 【図3】従来の過電流制限回路の一例を示す構成回路図である。

- 【図4】電圧降下と流れる電流の関係を示す特性曲線図である。

### 【符号の説明】

- [0051]

- 1 外部電源

- 2 外部負荷

- 3 ヒューズ

- 4,6,7 抵抗

- 5 F E T

- 8 レベル変換回路

- 9 A / D 変換回路

- 10 フィルタ回路

- 11 レベル比較回路

- 12 ラッチ回路

- 1 3 制御回路

- 1 4 論理回路

- 50,51 過電流制限回路

- 100 出力制御信号

- 101 ラッチ信号

- 1 0 2 制御信号

- 103 クリア信号

10

20

| 【図2】   |                |                |                |        |  |

|--------|----------------|----------------|----------------|--------|--|

| FETの状態 | OFF            | OFF            | OFF            | ON     |  |

| 論理出力   | High Impedance | High Impedance | High Impedance | 所定電圧出力 |  |

| 制御信号   | Low            | High           | Pow            | High   |  |

| ラッチ信号  | Low            | Low            | High           | High   |  |