(19) **日本国特許庁(JP)**

# (12) 特 許 公 報(B2)

(11)特許番号

特許第5479225号 (P5479225)

(45) 発行日 平成26年4月23日(2014.4.23)

(24) 登録日 平成26年2月21日 (2014.2.21)

(51) Int.Cl. F 1

**HO4N** 1/387 (2006.01) HO4N 1/387 **HO4N** 1/41 (2006.01) HO4N 1/41

請求項の数 6 (全 16 頁)

(21) 出願番号 特願2010-122029 (P2010-122029) (22) 出願日 平成22年5月27日 (2010.5.27)

(65) 公開番号 特開2011-250199 (P2011-250199A)

(43) 公開日 平成23年12月8日 (2011.12.8) 審査請求日 平成25年5月27日 (2013.5.27) (73)特許権者 000001007 キヤノン株式会社

Z

東京都大田区下丸子3丁目3〇番2号

||(74)代理人 100076428

弁理士 大塚 康徳

(74)代理人 100112508

弁理士 高柳 司郎

|(74)代理人 100115071

弁理士 大塚 康弘

||(74)代理人 100116894

弁理士 木村 秀二

(74)代理人 100130409

弁理士 下山 治

|(74)代理人 100134175

弁理士 永川 行光

最終頁に続く

(54) 【発明の名称】画像処理装置、画像処理方法及びプログラム

### (57)【特許請求の範囲】

### 【請求項1】

画像データを、複数個の予め定めたサイズのブロックで構成されるタイル毎に符号化する符号化手段と、

前記画像データにおいて削除を指定された画素行又は画素列が前記タイル内に含まれるか否かを各タイル毎に判定し、含まれる場合に、該当するタイル内の対応する画素行又は画素列が削除指定されていることを示す削除情報を、前記符号化されたタイルのヘッダ情報に保存する保存手段と

を備えることを特徴とする画像処理装置。

### 【請求項2】

前記符号化されたタイル内に含まれる各ブロックを順に処理対象のブロックとして復号 化する復号化手段を更に備え、

前記復号化手段は、前記処理対象のブロックの全画素が前記削除情報で削除指定されている場合に、当該処理対象のブロックを復号化しないことを特徴とする請求項1に記載の画像処理装置。

### 【請求項3】

前記復号化手段は、前記処理対象のブロックの一部の画素行又は一部の画素列が前記削除情報で削除指定されている場合に、削除指定されていない画素を復号化し、削除指定されている画素を復号化しないことを特徴とする請求項2に記載の画像処理装置。

#### 【請求項4】

20

前記ブロックは2×2画素のサイズで構成され、

前記符号化手段は、

タイル内の各ブロックを順に処理対象にして、当該処理対象のブロック内の各画素の画素値を比較することにより、各ブロックに含まれる画素値の配置パターンを示すパターン情報を特定し、

前記各ブロックの予め定めた位置の画素に対応する画素値から第1色の色情報を抽出し、更に、前記ブロックに含まれる色の数が2乃至4のいずれかであると判断したブロックから、当該特定されたパターン情報で定義されている配置パターンに対応する第2色乃至第4色の色情報を抽出し、

前記特定された各ブロックのパターン情報と、前記抽出された第1色の色情報と、前記抽出された第2色乃至第4色の色情報とをメモリに保持させることにより、前記タイルの符号化データを生成することを特徴とする請求項1乃至3のいずれか1項に記載の画像処理装置。

# 【請求項5】

コンピュータを用いて、

前記コンピュータが備える復号化手段が、画像データを、複数個の予め定めたサイズの ブロックで構成されるタイル毎に符号化する符号化工程と、

前記コンピュータが備える保存手段が、前記画像データにおいて削除を指定された画素行又は画素列が前記タイル内に含まれるか否かを各タイル毎に判定し、含まれる場合に、該当するタイル内の対応する画素行又は画素列が削除指定されていることを示す削除情報を、前記符号化されたタイルのヘッダ情報に保存する保存工程と、

を実行することを特徴とする画像処理方法。

#### 【請求項6】

コンピュータを、

画像データを、複数個の予め定めたサイズのブロック<u>で構成されるタイル毎に</u>符号化する符号化手段、

前記画像データにおいて削除を指定された画素行又は画素列が前記タイル内に含まれるか否かを各タイル毎に判定し、含まれる場合に、該当するタイル内の対応する画素行又は画素列が削除指定されていることを示す削除情報を、前記符号化されたタイルのヘッダ情報に保存する保存手段、

として機能させるためのプログラム。

【発明の詳細な説明】

# 【技術分野】

[0001]

本発明は、画像データを予め定めたサイズのブロック毎に符号化する画像処理装置、画像処理方法及びプログラムに関する。

### 【背景技術】

#### [00002]

デジタル複合機等の画像処理装置が扱う画像データは、カラー化、高解像度化の要求に伴ってそのサイズが増大している。このため、画像処理装置では、内部的に画像データを符号化して扱うことで、メモリやハードディスクに対する画像データスプール時の容量節約やアクセス時間短縮を行っている。また、内部バスの帯域負荷を減らし、システムにおけるデータ処理効率化を行っている。

### [0003]

カラー静止画像の符号化方式としては、離散コサイン変換を用いたJPEG方式や、Wavelet変換を用いた方式が使われている。これらの符号化方式は、画像を所定のブロック単位(例えば、8×8画素や16×16画素)で符号化し、離散コサイン変換、量子化及びエントロピー符号化を行うことで高い符号化効率を実現している。これらの符号化方式は、符号化対象の画像毎に符号量が変化する可変長符号化方式である。また、符号化前のデータと、符号化、復号化を経たデータとが完全には一致しない非可逆な符号化方

10

20

30

40

式である。

### [0004]

画素そのものではなく、画像の特徴量を符号化する技術としては、公知の、画素データとその連続数を記憶するランレングス符号化方式や、低解像度画像の符号化データから差分符号化を繰り返し行うJBIG方式がある。これらの符号化方式は、符号化前データと、符号化、復号化を経たデータとが完全に一致する可逆な符号化方式である。

#### [0005]

ところで、画像処理装置において符号化された画像データに対して、所定の画像処理(例えば、画素削除等)を行うには、一度復号化を行い符号化されていない元画像データを取得した後に行う必要がある。例えば、上述したJPEG方式であれば、離散コサイン変換で符号化した画像データを逆離散コサイン変換で復号化することで元画像データが得られ、当該元画像データに対して画像処理を行うことが可能となる。そして、画像処理終了後、必要に応じて再度符号化を行った後にスプール処理を行う。画像処理を複数回行う場合は、復号化、画像処理、符号化の一連の処理を必要回数だけ繰り返して行う。

### [0006]

また、特許文献1のように非可逆な符号化方式を用いる場合は、局部的に復号化処理を行うための処理リソースが必要であり、また、局部的ではあるが符号化・復号化処理を行うので画質が劣化してしまう。一方、ランレングス方式等の可逆な符号化方式を用いる場合は、画像処理を複数回行うため、符号化、復号化を繰り返すことによる画質劣化は発生しないが、画像処理を行うために少なくとも一度復号化処理を行う必要があり、その分の処理リソースが必要となってしまう。また、画像処理のパフォーマンス性能を向上させるため、画像処理部に加え、符号化処理部及び復号化処理部の双方が、画像処理に要求されるパフォーマンスと同等の性能を有する必要がある。例えば、JBIG方式等のような複雑な符号化方式を用いた場合、処理回路の多重化や並列化が必要となるため、回路規模が増大してしまう。

【先行技術文献】

### 【特許文献】

#### [0007]

【特許文献1】特開平09-261632号公報

# 【発明の概要】

【発明が解決しようとする課題】

# [0008]

本発明は、上記問題点に鑑みてなされたものであり、符号化された画像データを復号化することなく、削除対象の画素行又は画素列を指定可能である画像処理装置、画像処理方法及びプログラムを提供するものである。

【課題を解決するための手段】

# [0009]

上記課題を解決するため、本発明に係る画像処理装置は、画像データを、複数個の予め定めたサイズのプロックで構成されるタイル毎に符号化する符号化手段と、前記画像データにおいて削除を指定された画素行又は画素列が前記タイル内に含まれるか否かを各タイル毎に判定し、含まれる場合に、該当するタイル内の対応する画素行又は画素列が削除指定されていることを示す削除情報を、前記符号化されたタイルのヘッダ情報に保存する保存手段とを備える。

【発明の効果】

### [0010]

本発明によれば、符号化された画像データを復号化することなく、削除対象の画素行又は画素列を指定可能である画像処理装置、画像処理方法及びプログラムを提供することができる。

【図面の簡単な説明】

### [0011]

40

20

10

30

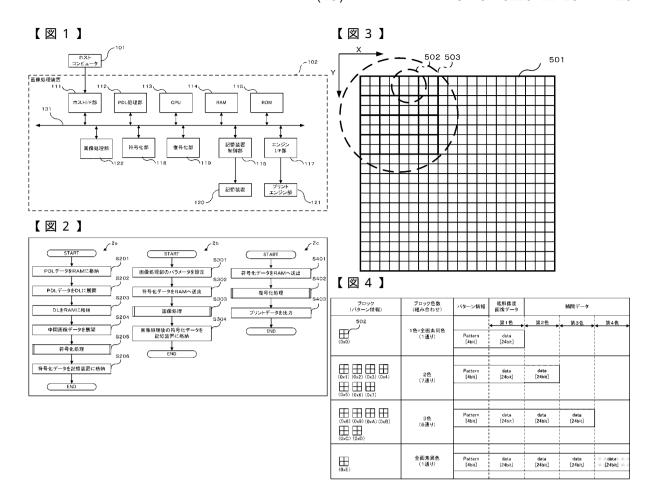

- 【図1】本発明の一実施形態に係る画像処理システムの全体構成を示す図である。

- 【図2】画像処理装置の全体的な処理手順を示すフローチャートである。

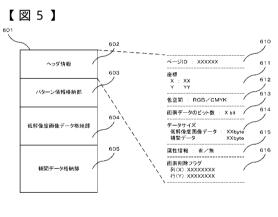

- 【図3】ページ画像、ブロック及びタイルの関係を示す図である。

- 【図4】ブロック、ブロック色数、低解像度画像データ、補間データの関係を示す図である。

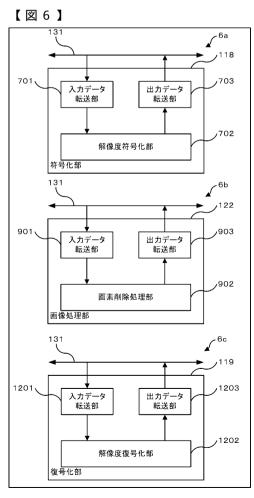

- 【図5】タイルのデータ構造を示す図である。

- 【図6】符号化部、画像処理部及び復号化部の構成を示す図である。

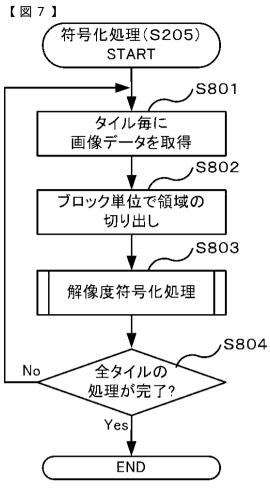

- 【図7】符号化処理(S205)の詳細な処理手順を示すフローチャートである。

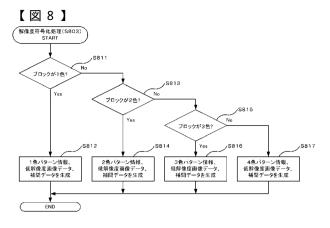

- 【図8】解像度符号化処理(S803)の詳細な処理手順を示すフローチャートである。

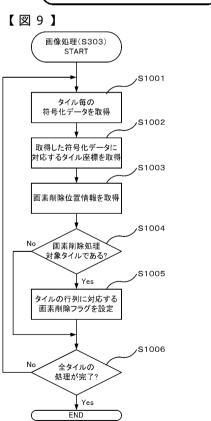

- 【図9】画素削除処理(S303)の詳細な処理手順を示すフローチャートである。

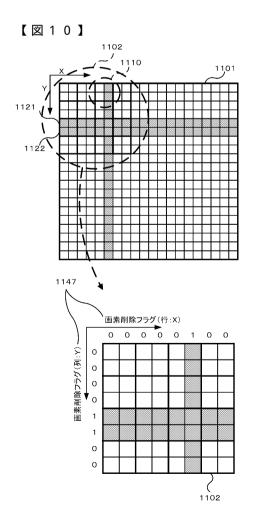

- 【図10】画素削除処理を模式的に示す図である。

- 【図11】タイルのデータ構造を示す図である。

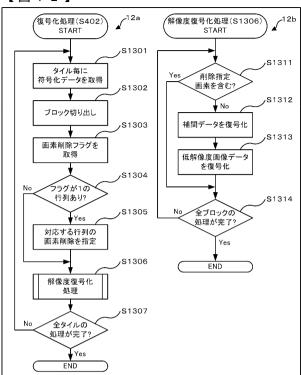

- 【図12】復号化処理(S402)及び解像度復号化処理(S1306)の詳細な処理手順を示すフローチャートである。

### 【発明を実施するための形態】

#### [0012]

本出願人は、特願2009-221444で以下に示す解像度符号化処理を提案してい る。この技術は、まず、画像データをブロック(例えば2×2画素サイズのブロック)毎 に分割し、ブロック内の各画素の色データを比較することにより、注目ブロックに含まれ る色データの配置パターン情報と、着目ブロックに含まれる色数分の色データ情報とを出 力する。そして、出力された色データ情報のうち、ブロックにおける予め定めた位置の画 素に対応する第1の色データ情報(例えば2×2画素サイズのブロックにおける左上の画 素の色データ情報)と、それ以外の色データ情報(第2色乃至第4色の色データ情報)と に分けてメモリ領域に格納する。すなわち、各ブロックから得られる配置パターン情報と 第1の色データ情報とそれ以外の色データ情報とを、それぞれ異なるメモリ領域にまとめ て格納することを特徴としている。各ブロック内には同色の画素が存在する場合が多いの で、メモリ領域に格納されたデータは、元画像のデータよりもデータサイズが小さい圧縮 データとなる。また、第1の色データ情報は、各ブロックの予め定めた位置の画素の画素 値であるので、連続メモリ領域に格納されている第1の色データ情報は、元画像を単純間 引き処理して生成される低解像度画像に等しい。したがって、低解像度画像データも容易 に得ることができる。また、各ブロックの第1の色データ情報からなる低解像度画像デー タを連続メモリ領域に置くことで、符号化データのままでの処理を容易化し、復号化する ことなく低解像度画像に対する画素処理も可能となる。

### [0013]

以下、図面を参照して本発明の実施形態を詳細に説明する。なお、以下の実施形態は特許請求の範囲を限定するものでなく、また、実施形態で説明される特徴の組み合わせの全てが発明の解決手段に必須のものとは限らない。

### [0014]

# (第1の実施形態)

[画像処理システムの全体構成(図1)]

本実施形態に係る画像処理システムは、ホストコンピュータ101と、画像処理装置102とを備える。

### [0015]

ホストコンピュータ101は、一般のPC(Personal Computer)やWS(Work Station)等のコンピュータであり、これらのコンピュータ上で作成された画像や文書は、PDLデータとして画像処理装置102に入力される。

#### [0016]

画像処理装置102は、ホストコンピュータ101から出力されたデータを受信する。 即ち、画像処理装置102とホストコンピュータ101との間でデータ通信可能なネット ワークが形成されていることを意味するが、このネットワークの構成については特に限定 10

20

30

するものではない。

### [0017]

画像処理装置102は、ホストコンピュータ101から受信したデータに基づいて各種の画像処理を施し、画像処理済みのデータをプリントエンジン部121へ出力する。プリントエンジン部121は、画像処理装置102から出力された画像処理済みのデータに基づいて、紙等の記憶媒体上に印刷処理を行う。なお、本実施形態では、画像処理装置102にデータを入力するのはホストコンピュータ101としたが、これ以外の装置であっても良く、例えば、不図示のスキャナ入力部から出力されたデータを画像処理装置102に入力するようにしても良い。

### [0018]

画像処理装置102は、図示しないコントローラ部を備える。コントローラ部は、ホストI/F部111と、PDL処理部112と、CPU113と、RAM114と、ROM115と、記憶装置制御部116と、エンジンI/F部117と、符号化部118と、復号化部119と、記憶装置120と、プリントエンジン部121と、画像処理部122とを備える。

#### [0019]

ホストI/F部111は、ホストコンピュータ101から出力されたPDLデータを受信するためのインタフェースとして機能する。なお、ホストI/F部111は、画像処理 装置102とホストコンピュータ101とを繋ぐネットワークに応じて異なり、例えば、イーサネット(登録商標)やシリアルインターフェース等で構成される。

#### [0020]

PDL処理部112は、ホストI/F部111が受信したPDLデータを展開する処理を行う。CPU113は、RAM114やROM115に格納されているプログラムやデータを用いて画像処理装置102全体の制御を行うと共に、画像処理装置102が行う後述の各処理を実行する。

### [0021]

RAM114は、ホストI/F部111を介して、ホストコンピュータ101から受信したデータを一時的に記憶するためのエリアを備える。また、CPU113が各種処理を実行する際に用いるワークエリアを備える。ROM115は、CPU113が画像処理装置102全体を制御する際に実行するプログラムやデータ及び画像処理装置102の設定データ等が格納されている。

# [0022]

記憶装置制御部116は、画像処理装置102が扱う画像データを記憶装置120に記憶するための制御を行う。エンジンI/F部117は、画像処理装置102による画像処理済みのデータをプリントエンジン部121に出力するための一連の処理を行う。

#### [0023]

符号化部 1 1 8 は、 P D L 処理部 1 1 2 において展開された画像に対して符号化処理を行う。本実施形態における符号化方法は、解像度符号化とする。復号化部 1 1 9 は、符号化部 1 1 8 で生成した符号化データを復号化し、符号化前の元データを生成する。本実施形態における復号化方法は、解像度復号化とする。

# [0024]

記憶装置120は、大容量記憶媒体(例えば、ハードディスク)であり、画像処理装置 102がホストコンピュータ101から受信した画像データや、処理時に生成する中間画 像データを記憶する。画像処理部122は、ホストコンピュータ101から出力されたデ ータから成る画像に対して画像処理を行う。

# [0025]

上述した各部は、画像処理装置102の内部バス131によって、互いに接続される。各部間のデータ転送は、各部と内部バス131との間に設けられたDMAC(Direct Memory Access Controller)からなる不図示のデータ転送部を用いて行う。

10

20

30

40

#### [0026]

「画像処理装置の全体的な処理手順(図2)]

まず、画像処理装置102がホストコンピュータ101から印刷データ(PDLデータ)を受信した場合に、印刷データを符号化して格納する処理について、図2の2aのフローチャートを用いて説明する。同図のフローチャートに示す処理は、ホストI/F部111を介して、ホストコンピュータ101から出力されたPDLデータの受信をCPU113が検知することで開始される。

### [0027]

まず、CPU113は、受信したPDLデータを一時的にRAM114に格納する(S201)。次に、CPU113が、受信したPDLデータをDL(Disp1ay List)に展開した後、一時的にRAM114に格納する(S202)。具体的には、PDLデータが有する画像情報とそれに対応する属性情報が生成され、DLとして格納される。生成する属性情報としては、PDL入力の文字、ライン及び写真等がある。

# [0028]

そして、PDL処理部112が、格納したDLに基づいて、画像展開処理を行い、中間画像データを生成する(S204)。画像展開処理は、予め定めたサイズのブロック毎(以下、この単位をタイルと呼ぶ)に行うものとする。タイルサイズは、後述する符号化処理における、2×2画素のブロックを複数個まとめた領域サイズと等しいことが望ましく、本実施形態では、タイルサイズを8×8画素単位とする。また、中間画像データには、DLが有する画像情報とそれに対応する属性情報とが、画素単位で対応付けされた状態で格納される。

#### [0029]

そして、中間画像データは、符号化部118において、タイル単位でパターン情報(配置パターン)、低解像度画像データ(所定位置の画素の画素値に対応する第1色の色データ)及び補間データ(第2~4色の色データ)からなる符号化データに変換される(S205)。なお、符号化部118における処理の詳細は後述する。

### [0030]

符号化データは、記憶装置制御部116が有する不図示のデータ転送部を介して記憶装置120へ出力され、保存される(S206)。このとき、タイル毎に所定の固定長のヘッダ情報を付与する。なお、ヘッダ情報の詳細は後述する。

# [0031]

次に、記憶装置120に保存された符号化データを読み出し、符号化データを画像処理して再スプールする処理について、図2の2bに示すフローチャートを用いて説明する。同図のフローチャートに示す処理は、CPU113が、記憶装置制御部116への符号化データのスプール処理に係る終了通知を受信後に、プリント開始命令を復号化部119に指示することで開始される。

# [0032]

まず、画像処理部122のパラメータ設定を行う(S301)。具体的には、CPU1 13が、画像処理部122が有する不図示の画像処理モジュールの各レジスタに対して、 必要なパラメータ設定を行う。そして、CPU113は、記憶装置120に保存されてい る符号化データを、RAM114へ読み出すよう記憶装置制御部116へ指示する(S3 02)。

### [0033]

次に、画像処理部122は、内部に有する後述の入力データ転送部901(図6の6b参照)を用いてRAM114から符号化データを読み出し、元画像へ復号化しないで、当該符号化データに対して所定の画像処理を行う(S303)。なお、符号化データの中で行う所定の画像処理の詳細については後述する。

### [0034]

そして、 C P U 1 1 3 は、後述の出力データ転送部 9 0 3 (図 6 の 6 b 参照)に対して S 3 0 3 で画像処理した符号化データを R A M 1 1 4 へ格納するよう指示する ( S 3 0 4

10

20

30

40

)。 C P U 1 1 3 は、更に、 R A M 1 1 4 へ格納された符号化データを、記憶装置 1 2 0 へ格納するよう、不図示のデータ転送部へ指示する。 C P U 1 1 3 は、不図示のデータ転送部からの全ての符号化データを記憶装置 1 2 0 へ格納し終えたことを示す終了通知を受信後にアイドル状態に移行する。

### [0035]

次に、記憶装置120に保存された画像処理済みの符号化データを読み出し、その符号化データを復号化し、プリントデータとして出力する処理について、図2の2cに示すフローチャートを用いて説明する。同図のフローチャートに示す処理は、CPU113が、S304での終了通知を受信後に、プリント開始に係る処理命令を記憶装置制御部116に指示することで開始される。

[0036]

まず、CPU113は、記憶装置120に保存されている符号化データを、RAM114へ読み出すよう、記憶装置制御部116へ指示する(S401)。次に、復号化部119は、内部に有する後述の入力データ転送部1201(図6の6c参照)を用いて、RAM113から符号化データを読み出し、復号化処理を行う(S402)。なお、復号化処理の詳細は後述する。

[0037]

次に、復号化して得られた画像データを、内部に有する後述の出力データ転送部1203(図6の6c参照)を用いて、RAM114へ出力する(S403)。その後、エンジンI/F部117が内部に有する不図示のデータ転送部を用いて、RAM114からプリントエンジン部121へ画像データを出力する。

[0038]

以上の各処理により、ホストコンピュータ101から受信したデータを符号化し、パターン情報と低解像度画像データと補間データとからなる符号化データを生成することができる。また、符号化データを復号化せずに画像処理し、記憶装置120へ再スプールすることができる。そして、画像処理後の符号化データを復号化してプリンタエンジン部104に出力することができる。

[0039]

以上の説明では、データのスプールをRAM114を経由して記憶装置120に保持することとしたが、記憶装置120を用いずにRAM114にスプールするようにしても良い。

[0040]

[符号化部118の詳細構成(図3、図4、図5)]

図3は、入力画像であるページ画像501、ページ画像501から抽出される2×2画素のブロック502及び8×8画素のタイル503の関係を示している。図4は、ブロック、ブロックを構成するブロック色数、対応する低解像度画像データ及び補間データの関係を示している。

[0041]

まず、ブロック502を構成するブロック色数について説明する。ブロック色数505 が1色で全画素が同色である場合の組み合わせは1通りである。これに対応するパターン 情報を0×0(0×は16進数を示す。以下同様)とする。

[0042]

ブロック色数505が2色である場合の組み合わせは、左上の画素の色(画素値)を第1色、他の画素に存在する第1色以外の色を第2色として考えると、左上以外残りの3画素へ第1色又は第2色が入るので、4画素同色の場合を除くと、全部で7通りである。これに対応するパターン情報を0×1~0×7とする。

[0043]

ブロック色数505が3色である場合の組み合わせは、3色のうち1色だけ2度使われる場合の数と言い換える事が可能で、4画素の座標のうち、2画素が同じ色になる場合の数を求めればよい。つまり、3色の場合の数は、4つの座標から2つの座標を取る組み合

10

20

30

40

わせとなり、全部で6通りとなる。これに対応するパターン情報を0 x 8 ~ 0 x D とする。このとき、左上の画素の色を第1色とし、右上・左下・右下の画素順で走査したときに新たな色が出現するごとに、第2色、第3色として定義する。

#### [0044]

ブロック色数 5 0 5 が 4 色である場合の組み合わせは、1 色の場合と同様 1 通りとなる。これに対応するパターン情報を 0 x E とする。このとき、左上の画素の色を第 1 色、右上の画素の色を第 2 色、左下の画素の色を第 3 色、右下の画素の色を第 4 色として定義する。

# [0045]

以上より、ブロック色数 5 0 5 は、 1 ~ 4 色の場合を合計すると 1 5 通りの組合せが存在する。

#### [0046]

タイル 5 0 3 は、 2 × 2 画素サイズのブロック 5 0 2 を複数まとめた領域である。本実施形態では、 2 × 2 画素サイズのブロックが 4 × 4 個(画像の X 方向に 4 個、 Y 方向に 4 個、計 1 6 個)から構成される領域をタイルとする。これは、上述した中間画像データ展開におけるブロック単位と同じサイズである。

### [0047]

次に、各ブロック色数505に対応する低解像度画像データ506及び補間データ507の構成について説明する。

# [0048]

低解像度画像データ506は、 $2 \times 2$  画素からなるブロック502の予め定めた位置(左上)の画素の色情報とする。例えば、色空間がRGBで、各色コンポーネントのデータ長が8ビットの画素の場合、各色情報のビット長は24 ビットで表現可能である。この左上画素の色情報を第1色とし、更に、右上画素・左下画素・右下画素の順に走査した場合に、新たな色が出現するたびに第2色~第4色(補間データ)を順に定義する。なお、本実施形態では、左上の画素の色を第1色として定義したが、これに限るものではない。また、第2~4色を定める画素の走査順も予め定義しておけばよい。例えば、右下画素を予め定めた位置の画素として定義して、第1色を定め、その他の位置の画素を所定の順に走査して第2~4色の補間データとして定めるようにしてもよい。

### [0049]

すなわち、補間データ507は、左上画素以外の画素の色情報のうち、第1色以外の色情報(つまり、第2色乃至第4色の色情報)を、パターンごとに定義された順で格納したものである。ブロック色数505が1色の場合、該ブロック内には第1色以外の色が存在しないので、補間データは不要となり、パターン情報として全画素同色を示す0×0と、第1色を表現する低解像度画像データとから構成されるデータで再現可能となる。

#### [0050]

ここで、パターン情報のビット長は4であり、ブロック色数505の全組み合わせ15通りを表現する最小のビット長である。

### [0051]

また、色空間がRGBで、各色コンポーネントのデータ長が8ビットの画素の場合、補間データの各色情報のビット長は24であるので、各ブロックに対する補間データのデータサイズは、0、24、48、72ビットのいずれかとなる。

### [0052]

以上説明した、パターン情報と低解像度画像データ506と補間データ507とを用いることで、2×2画素からなるブロック502を符号化し、データ量を低減することが可能となる。

#### [0053]

例えば、全画素同色であるブロックの場合、符号化前のデータ量は(RGB各色8ビット)×(4画素分)の計96ビットである。これを符号化した場合、左上画素の色情報(第1色)を示す低解像度画像データが24ビットと、全色同色画素であることを示すパタ

20

10

30

40

ーン情報である 4 ビットとの合計 2 8 ビットとなる。この符号化データは、パターン情報と色情報とから元データである 2 × 2 画素のブロック 5 0 2 に復号化することができる。

### [0054]

従って、ブロックに含まれる各画素の色数が1色である場合に、予め定めた位置の画素(着目画素)の色データ及び当該ブロックにおける色の配置パターンを符号化し、また、ブロックに含まれる各画素の色数が2色以上である場合に、予め定めた位置の画素の色データ及び色の配置パターンに加えて、色数に応じた着目画素以外の画素の色データを符号化することとなる。各ブロックから求めたパターン情報と、低解像度画像データ(第1色の色情報)と、補間データ(第2~4色の色情報)とは、それぞれ異なるメモリ領域(パターン情報格納部、低解像度画像データ格納部、補間データ格納部)に、各タイル内のブロックの並び順にしたがって格納する。

#### [0055]

次に、タイル503を符号化した後のデータ構造について図5を用いて説明する。タイル503のデータ構造601は、ヘッダ情報602、パターン情報格納部603、低解像度画像データ格納部604及び補間データ格納部605から構成される。

#### [0056]

ヘッダ情報602は、ページ画像501に対するタイル503の管理情報から構成される。本実施形態では、ページID610、タイル座標611、色空間612、画像データのビット数613、低解像度画像データ及び補間データ格納部のデータサイズ614、属性情報の有無615、及び画素削除フラグ616(削除情報)等を含む。

#### [0057]

ページID610は、ページ単位にユニークとなるタイルのID番号を示す。タイル座標611は、ページ単位のラスタ画像上におけるタイル位置を示す。本実施形態では、X座標とY座標と2次元で座標指定するものとする。色空間612は、タイルを構成する画像の色空間(RGB、CMYK等)を指定する識別子を示す。画素データのビット数613は、タイル内の1画素あたりのビット長(色深度)を示す。データサイズ614は、タイルを構成する画素の低解像度画像データ及び補間データのデータサイズを示す。属性情報の有無615は、タイルを構成する各画素が属性情報を有しているか否かを示す。

# [0058]

画素削除フラグ616は、本発明の画像処理における特徴であり、画素を行列単位で削除するための画素削除位置を指定するものである。画素削除フラグ616は、行(X方向)及び列(Y方向)をそれぞれ独立に指定するものであり、タイルのX方向及びY方向の画素数分のデータ長で構成される。本実施形態では、タイルが8×8画素であり、画素削除フラグ長は、行、列共にそれぞれ8ビットである。

# [0059]

[符号化処理(S205)の詳細な処理手順(図6の6a、図7、図8)]まず、図6の6aに示す入力データ転送部701は、内部バス131に接続され、RAM114又は記憶装置120に予め保持された処理対象データを取得する(S801)。処理対象データは、本実施形態では、PDL処理部112で生成されたタイル形式の中間画像データである。すなわち、タイル毎に抽出した画像データを取得する。また、の力である。すなわち、タイル毎に抽出した画像データを取得する。また、の力での上がスタ設定は、予めCPU113が行うものとする。そして、タイルから2×2両素のブロックを切り出し(S802)、図6の6aに示す解像度符号化部702は、入力データ転送部701から2×2両よりする。そして、解像度符号化部702は、入力データ転送部701から2×2両出らなるブロックが入力されると解像度符号化処理を行う(S803)。具体的に画素を定は表づし、解像度符号化部702は、入力されたブロック内の各両素の色(画素をとし、各ブロックが何色(1色、2色、3色のいずれ)で構成されているかを対定するで、各ブロックが何色(1色、3色、4色のいずれ)で構成されているかを定し、各ブロックが何色(1色、3色、4色のいずれ)で構成されているかを対定する画素値から第1色の色情報を抽出し、更に、前記ブロックに含まれる色

10

20

30

40

10

20

30

40

50

の数が2乃至4のいずれかであると判断したブロックからは、当該特定されたパターン情報で定義されている配置パターンに対応する第2~4色の色情報を抽出する。そして、各ブロックのパターン情報と、第1色の色情報(低解像度画像データ)と、第2~4色の色情報(補間データ)とを、それぞれのメモリ領域に順に格納していくことにより、当該タイルの符号化データを生成する(S812、S814、S816、S817)。なお、ブロック内が1色で構成される場合、第2~4色は存在しないので、補間データはゼロになる。また、S803では、タイル内に含まれる各ブロックに対して、S811~S817の処理が行われることになる。

#### [0060]

図6の6aに示す出力データ転送部703は、内部バス131に接続され、解像度符号化部702で生成される符号化データを、内部バス131に接続されるRAM114へ出力する。出力データ転送部703の動作に必要な、RAM114上の画像書き出しアドレス番地、出力データ長等の不図示のレジスタ設定は、CPU113が予め行うものとする

#### [0061]

上述した処理を、全てのタイルに対して繰り返し行い、全てのタイルの処理が終了した ら符号化処理を終了する(S 8 0 4 )。

#### [0062]

[画像処理(S303)の詳細な処理手順(図6の6b、図9、図10、図11)] ここで、本実施形態における画像処理部122の画像処理としての画素削除処理は、行列単位で行うものである。タイル単位で入力される符号化データに対して、タイルのヘッダ情報に画素削除すべき旨を示すフラグを付与することで、復号化することなく仮想的に画素削除処理を行う。

#### [0063]

まず、図6の6bに示す入力データ転送部901は、内部バス131に接続され、RAM114又は記憶装置120に予め保持された処理対象データを取得する(S1001)。本実施形態における処理対象データは、符号化部118でタイル単位に符号化され、低解像度画像データ及び補間データからなる符号化データである。また、入力データ転送部901の動作に必要となる、データ転送開始アドレス番地、データ長等の不図示のレジスタ設定は、予めCPU113が行うものとする。そして、取得したタイル単位の符号化データを図6の6bに示す画素削除処理部902へ出力する。

# [0064]

そして、画素削除処理部902は、タイルの座標を取得する(S1002)。座標取得は、タイルのヘッダ情報が有するタイル座標611を参照することで行う。次に、ページ画像に対する画素削除位置情報を取得する(S1003)。画素削除位置情報は、ページ画像で削除すべき行、列を一行一列単位で指定したものである。画素削除位置情報は、予め指定された設定に応じて、CPU113により画像処理部122が有する不図示のレジスタに設定されているものとする。

### [0065]

そして、S1003で取得したページ画像における画素削除位置情報に応じて、取得した符号化データに対応するタイル内に削除すべき行、列が含まれるか否かを判定する(S1004)。即ち、S1002で取得したタイル座標からページ画像におけるタイルの位置を算出し、S1003で取得したページの画素削除位置情報と座標比較し、タイル内に画素削除位置が含まれるか否かを判定する。タイル内に画素削除位置が含まれていれば、画素削除処理対象タイルと判定し、画素削除位置情報に従って、そのタイルの画素行及び画素列に対応する画素削除フラグの設定を行う(S1005)。すなわち、画素削除対象の画素行及び画素列に対応する画素削除フラグをON(1)に設定する。一方、タイル内に画素削除位置が含まれていない場合には、そのタイルに対する画素削除処理に従った設定は行わない。すなわち、タイル内に画素削除位置が含まれていない場合、画素削除フラグは全てOFF(0)のままになる。

#### [0066]

画素削除フラグ設定の具体例を、図10及び図11を用いて説明する。ページ画像1101に含まれるタイル1102に対して画素削除処理を行う場合を考える。ページ画像に対する画素削除位置情報として、ページのX座標の6行目1110とY座標の5、6列目1121、1122が設定されているものとする。これらの画素削除位置情報は、タイル1101においても、X座標の6行目と、Y座標の5、6列目が画素削除位置となる。よって、タイル1101のデータ構造1131に関して、ヘッダ情報1132の画素削除フラグ1147は、行Xが00001100、列Yが00001100となる。画素削除フラグ1147を参照することで、タイル1102が符号化されている場合でも、どの画素が削除されるかを判定することが可能となる。

[0067]

図6の6 bに示す出力データ転送部903は、内部バス131に接続され、画像処理部122で処理済みのタイル単位の画像データを、内部バス131に接続されるRAM114へ出力する。出力データ転送部903の動作に必要な、RAM114上の画像書き出しアドレス番地、出力データ長、等の不図示のレジスタ設定は、CPU113が予め行うものとする。

[0068]

上述した処理を全てのタイルに対して繰り返し行い、全てのタイルの処理が終了したら 画素削除処理を終了する(S1006)。

[0069]

「復号化処理(S402)の詳細な処理手順(図6の6c、図12))

まず、内部バス131に接続された入力データ転送部1201(図6の6c)は、RAM114又は記憶装置120に予め保持された処理対象データを取得する(S1301)。本実施形態における処理対象データは、符号化部118でタイル単位に符号化された後に、画像処理部122で画素行又は画素列が削除指定された符号化データとする。入力データ転送部1201の動作に必要となる、データ転送開始アドレス番地、データ長等の不図示のレジスタ設定は、予めCPU113が行うものとする。そして、タイルから2×2画素のブロックを切り出し(S1302)、解像度復号化部1202(図6の6c)へ出力する。

[0070]

解像度復号化部1202では、入力されたタイルのヘッダ情報が有する画素削除フラグを取得し(S1303)、入力されたタイルに対して画素の行、列を削除するか否かを判定する(S1304)。つまり、各行又は列に対応する画素削除フラグに有効ビット1があるか否かを判定する。有効ビット1がある場合には、画素削除フラグが指定する画素行又は画素列の削除指定を行う(S1305)。即ち、画素削除フラグとブロックとの関連付けを行って、各ブロック毎の削除位置の指定を行う。一方、有効ビット1が無い場合には、当該削除指定は行わない。そして、解像度復号化処理を行う(S1306)。

[0071]

S1306では、図12の12bに示すように、まず、S1305で為された削除指定に基づいて、復号化を行う2×2画素を構成する各ブロック内の画素行又は画素列が削除指定されているか否かを判定する(S1311)。2×2画素ブロック全体が削除指定されている場合、当該ブロックの復号化処理を行わない。

[ 0 0 7 2 ]

一方、削除指定されている画素行又は画素列を全く含まないブロックに対しては、パターン情報を参照し、補間データ格納部 1 1 3 5 から当該ブロックの補間データ(第 2 色乃至第 4 色の色情報)を読み出して復号化(S 1 3 1 2 )し、低解像度画像データ格納部 1 1 3 4 から当該ブロックの低解像度画像データ(第 1 色の色情報)の復号化(S 1 3 1 3 )を行う。

[0073]

また、削除指定された画素行または画素列を一部含むブロックの場合は、削除指定され

10

20

30

40

10

20

ていない画素行または画素列に対応する画素の復号化処理を行う。このとき、処理対象ブロックのパターン情報と削除指定されている画素行または画素列とに応じて、当該ブロックの補間データと低解像度画像データとのそれぞれに関して読み込む必要があるか判断する。例えば、図4に示されるように、パターン情報が「0×4」のブロックの場合、第1色の色情報は左上の画素でだけ使用するので、当該左上の画素が削除対象の画素行または画素列に含まれる場合は、低解像度画像データ格納部1134から当該ブロックの低解像度画像データ(第1色の色情報)を読み込む必要がないと判断し、S1312で当該ブロックの補間データのみを読み込んで復号化し、S1313の処理はスキップする。また、ブロックのパターン情報が「0×3」で且つ右上と右下の画素が削除対象であった場合、第2色の色情報は不要であるので、補間データを読み込む必要がないと判断し、S1313の処理はスキップし、S1313で当該ブロックの低解像度画像データを読み込んで左上と左下の画素を復号化する。

[0074]

そして、タイル内に含まれる全てのブロックにおける画素の復号化が終了したら解像度 復号化処理を終了する(S1314)。

[0075]

上述した処理を、入力画像に含まれる全てのタイルに対して繰り返し行い、全タイルに対する処理が終了したら復号化処理を終了する(S1307)。この復号化処理済みの画像データは、図6の6cに示す出力データ転送部903を介して、内部バス131に接続されるRAM114へ出力される。出力データ転送部903の動作に必要な、RAM114上の画像書き出しアドレス番地、出力データ長等の不図示のレジスタ設定は、CPU113が予め行うものとする。

[0076]

以上述べた通り、本実施形態によれば、符号化された画像データを復号化することなく、削除対象の画素行又は画素列を指定することが可能となる。また、復号化を行う際に削除指定がなされた画素行又は画素列を含むブロックを復号化することなく、削除指定がなされた画素行又は画素列を含まないブロックのみを復号化することが可能となる。

[0077]

(他の実施形態)

本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)をネットワーク又は各種記憶媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(又はCPUやMPU等)がプログラムコードを読み出して実行する処理である。この場合、そのプログラム、及び該プログラムを記憶した記憶媒体は本発明を構成することになる。

【図12】

# フロントページの続き

(72)発明者 蓮井 樹生 東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 堀井 啓明

(56)参考文献 特開2007-243889(JP,A) 特開2004-023316(JP,A)

(58)調査した分野(Int.CI., DB名)

H 0 4 N 1 / 3 8 - 1 / 3 9 3 H 0 4 N 1 / 4 1 - 1 / 4 1 9